# HIGH PERFORMANCE VLSI ARCHITECTURES IMPLEMENTING STRONG CRYPTOGRAHIC PRIMITIVES

## THÈSE N° 2561 (2002)

PRÉSENTÉE À LA FACULTÉ SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES TECHNIQUES

DANS LE DOMAINE D'ÉLECTRICITÉ

#### PAR

#### Feth Allah CHERIGUI

ingénieur électricien diplômé EPF et de nationalité algérienne

acceptée sur proposition du jury:

Prof. D. Mlynek, directeur de thèse Prof. Y. Leblebici, rapporteur Prof. Ch. Piguet, rapporteur Dr A. Vachoux, rapporteur M. P. Mercier, rapporteur

> Lausanne, EPFL 2002

## **ACKNOWLEDGEMENTS**

This work has been accomplished during the years 1999 to 2001 at the Integrated System Laboratory (ISL) of the Swiss Federal Institute of Technology (EPFL) at Lausanne, Switzerland.

Firstly I wish to express my gratitude to my advisor Professor Mlynek (EPFL) for giving me the opportunity of pursuing a PhD research in his laboratory. I am thankful to Prof. Yusuf Leblebici (WPI/EPFL), Prof. Christian Piguet (CSEM) and Dr. Alain Vachoux (Antrim Design Systems), and Mr. Philippe Mercier (TranSwitch Europe) who do me the honour of accepting to take part in the thesis jury.

I express my thanks to people of ISL who were working with me in the RPK Project: Stephan Bories, Antonio Romeo and Geovani Romolotti. I am grateful to Dr. Alain Vachoux for giving me the necessary packages and sub-micron technology libraries.

Special thanks go to Dr. Paul Debefve for his availability and willingness to solve the numerous CAD-problems that arose during the years, and his assistance for providing the necessary literature. Sincere acknowledgements go to my colleagues of the ISL: Yves Pizzuto, Sergio Lopez, Alexandre Schmid, Leonel Comminilli and Seong Garin for their friendship. I would like to address a further acknowledgements, specially to people who contribute to this work: Alexandre Fotinos, Luc Piguet, Silvain Aguirre and Olivier Croset, many thanks for their valuable work.

Last but certainly not least, I wish to express my deepest gratitude to my parents who enabled me to pursue all my studies and to Monika who did support me for all these years of study. This thesis would have certainly not been accomplished without her help and her love.

|  | • |  |  |  |

|--|---|--|--|--|

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

TABLE OF CONTENTS IV

# TABLE OF CONTENTS

|         |                    | rs                                         |

|---------|--------------------|--------------------------------------------|

|         |                    | s                                          |

|         |                    | XVI                                        |

| ACRONYM | ıs                 | xviii                                      |

|         |                    |                                            |

|         |                    |                                            |

| 1.1 N   | <b>1</b> OTIVATION |                                            |

| 1.2     | CURRENT AN         | D FUTURE TRENDS FOR CRYPTOGRAPHY           |

| 1.2.1   | Designin           | g Cryptographic Primitives                 |

| 1       | .2.1.1 Block       | la Ciphers                                 |

| 1       | .2.1.2 Strea       | m Ciphers                                  |

| 1       | .2.1.3 Sync        | hronous Stream Ciphers                     |

| 1       | .2.1.4 Publ        | ic-Key Cryptosystems                       |

| 1.2.2   | 2 Crypto s         | tandardization                             |

| 1.3 S   | ECURITY AN         | d Cryptanalysis                            |

| 1.4 S   | YSTEM DESI         | GN AND IMPLEMENTATION                      |

| 1.4.1   | Performa           | ance versus security                       |

| 1.4.2   | 2 Performa         | ance Evaluation and Optimization           |

| 1.4.3   | 3 ASIC ve          | rsus FPGA Design                           |

| 1.5 L   | OW POWER           | HARDWARE DESIGN                            |

| 1.5.1   | Low-pov            | ver design for SOC                         |

| 1.6 F   | łigh Perfo         | RMANCE VLSI ARCHITECTURES FOR CRYPTOGRAPHY |

| 1.7 S   | COPE OF TH         | IS WORK                                    |

| 1.8     | COMPLEXITY         | 31                                         |

| 1.9 S   |                    | OF THIS THESIS                             |

| CHAPTER | 2 DESIG            | NING FOR LOW-POWER/LOW-ENERGY              |

| 2.1 N   | <b>M</b> OTIVATION | FOR LP DESIGN                              |

| 2.2 S   | OURCE OF I         | POWER IN CMOS CIRCUIT                      |

| 2.3     | CMOS Low           | Power Design Techniques                    |

| 2.3.1   | l Power St         | apply and Technology                       |

| 2       | 2.3.1.1 Voli       | tage scaling                               |

| 2       | 2.3.1.2 Tech       | nology mapping                             |

| 2     | 2.3.2 | Rec  | ducing the activity factor                              |

|-------|-------|------|---------------------------------------------------------|

|       | 2.3.  | .2.1 | Glitch avoidance                                        |

|       | 2.3.  | .2.2 | Clock and Signal Gating                                 |

|       | 2.3.  | .2.3 | Power-down modes of global clock gating                 |

|       | 2.3.  | .2.4 | Algorithm Optimization (reviewing)                      |

| 2     | .3.3  | Rec  | ducing the Capacitive Load                              |

|       | 2.3.  | 3.1  | Partitioning into Blocks                                |

|       | 2.3.  | 3.2  | Locality of reference                                   |

|       | 2.3.  | 3.3  | Clock and control signals distribution                  |

|       | 2.3.  | 3.4  | Buffering the Heavily Loaded lines                      |

| 2     | .3.4  | Rec  | ducing the Short Circuit Current                        |

|       | 2.3.  | 4.1  | Resistive networks                                      |

|       | 2.3.  | 4.2  | Switching current                                       |

|       | 2.3.  | 4.3  | Glitch propagation                                      |

| 2.4   | Pov   | WER  | ESTIMATION AND OPTIMIZATION                             |

| 2     | .4.1  | Pov  | wer Analysis and optimization Tools                     |

| 2.    | .4.2  | LP   | Automated design Methodology                            |

|       | 2.4   | 2.1  | Preparing for RTL Design                                |

|       | 2.4   | 2.2  | Pre-synthesis design impact                             |

| 2.5   | Lov   | w Pc | OWER DESIGN FLOW                                        |

| 2.    | .5.1  | Sim  | nulation Based Power Estimation and Optimization        |

|       | 2.5.  | 1.1  | Selecting the best Vector Set                           |

|       | 2.5.  | 1.2  | ASIC Libraries                                          |

|       | 2.5.  | 1.3  | VSS-FAIF interface                                      |

| 2.    | 5.2   | Fro  | nt-end or Logical Design                                |

|       | 2.5.  | 2.1  | Behavioural/RT Power Estimation/Reduction               |

|       | 2.5.  | 2.2  | Gate level Power Calculation and Optimization           |

| 2.    | 5.3   | Bac  | k-end or Physical design                                |

|       | 2.5.  | 3.1  | Timing and parasitics back-annotation                   |

|       | 2.5.  | 3.2  | Priority in Back annotation                             |

| Снарт | ER 3  | ST   | TATE OF THE ART IN DESIGNING CRYPTOGRAPHIC PRIMITIVES48 |

| 3.1   |       |      | GRAPHIC PRIMITIVES                                      |

| 3.2   | INF   |      | ATION SECURITY OBJECTIVES                               |

| 3.    | 2.1   |      | a confidentiality or privacy                            |

|       | 3.2.  | 1.1  | Encryption/Decryption process                           |

TABLE OF CONTENTS VI

| 3.2.1.2 Cryptosystem                                        | 49         |

|-------------------------------------------------------------|------------|

| 3.2.2 Data Integrity and Authentication                     | 49         |

| 3.2.3 Digital Signature and Verification                    | <b>5</b> 0 |

| 3.2.4 Entity Authentication and Key Establishment Protocols | 51         |

| 3.3 SECURITY CONSTRAINTS                                    | 52         |

| 3.3.1 Cryptanalysis (Attack Strategies)                     | 52         |

| 3.3.1.1 Attacks Classification                              | 52         |

| 3.3.2 Asymmetric vs Symmetric primitive security            | 54         |

| 3.3.2.1 Brute-Force or Exhaustive Key Search                | 54         |

| 3.3.2.2 Codebook Attack                                     | 54         |

| 3.4 BUILDING CRYPTOGRAPHIC PRIMITIVES WITH THE CFSM MODEL   | 55         |

| 3.4.1 Block ciphers (Substitution permutation ciphers)      | 55         |

| 3.4.1.1 Block Cipher Properties                             | 55         |

| 3.4.1.1.1 Data Diffusion                                    | 55         |

| 3.4.1.1.2 Avalanche effect:                                 | 56         |

| 3.4.1.1.3 Completeness effect:                              | 56         |

| 3.4.1.2 Block ciphers construction                          | 56         |

| 3.4.1.3 Mode of operations                                  | 56         |

| 3.4.2 Stream ciphers                                        | 57         |

| 3.4.2.1 Properties                                          | 58         |

| 3.4.2.1.1 Stream Cipher Diffusion                           | 58         |

| 3.4.2.2 Stream Cipher Construction                          | 58         |

| 3.4.2.2.1 Confusion Sequence                                | 58         |

| 3.4.2.2.2 Combiner                                          | 59         |

| 3.4.2.3 Security of Stream Cipher                           | 59         |

| 3.4.2.4 LFSRs based stream ciphers                          | 60         |

| 3.4.3 Public Key Ciphers                                    | 62         |

| 3.4.3.1 Certification                                       | 62         |

| 3.4.3.2 Public Key Cryptosystems Properties                 | 63         |

| 3.4.3.2.1 Exponential versus Polynomial time Algorithms     | 63         |

| 3.4.3.2.2 DLP versus IFP                                    | 63         |

| 3.4.3.3 DLP in GF(p) and GF( $2^m$ )                        | 64         |

| 3.4.3.4 DLP based Cryptosystems Construction                | 64         |

| 3.4.4 Cryptographic Hash Functions (CHF)                    | 65         |

| 3.4.4.1 Security Properties                                 | . 66       |

VII TABLE OF CONTENTS

| 3.4.5 Keyed Hash Functions (KHF)                                             | 67 |

|------------------------------------------------------------------------------|----|

| 3.4.5.1 Requirements for Keyed Hash Functions                                | 67 |

| 3.4.5.1.1 Security requirements                                              | 67 |

| 3.4.5.1.2 Design Heuristics                                                  | 67 |

| 3.4.5.2 Construction of Keyed Hash Functions                                 | 68 |

| 3.4.5.2.1 The Secret Prefix Method                                           | 68 |

| 3.4.5.2.2 The Secret Suffix Method                                           | 68 |

| 3.4.5.2.3 The Envelope Method                                                | 68 |

| 3.4.5.2.4 New Construction                                                   | 68 |

| CHAPTER 4 FINITE FIELD ARITHMETIC FOR CRYPTOGRAPHY                           | 70 |

| 4.1 Finite Field Architectures for Cryptography                              | 70 |

| 4.2 Finite Field Fundamentals                                                | 71 |

| 4.2.1 Finite fields                                                          | 71 |

| 4.2.2 Galois Fields                                                          | 71 |

| 4.2.3 The extension field $GF(2''')$                                         | 72 |

| 4.2.4 The polynomial basis and primitive elements                            | 72 |

| 4.2.5 The Dual Basis                                                         | 73 |

| 4.2.6 Normal basis                                                           | 74 |

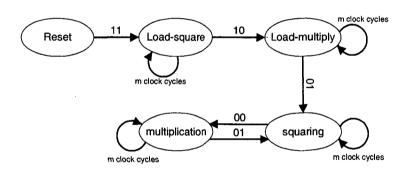

| 4.2.7 Exponentiation Over GF(2"): S&M Algorithm                              | 74 |

| 4.3 Primitive Polynomials and Field Size for Finite Field based Cryptosystem | MS |

|                                                                              |    |

| 4.4 Architectures for Multiplication over Large $GF(2^m)$                    |    |

| 4.4.1 Bit-serial PB Multipliers                                              |    |

| 4.4.2 Architecture Level Transformation                                      |    |

| 4.4.2.1 Digit-Serial MSR Multiplier                                          |    |

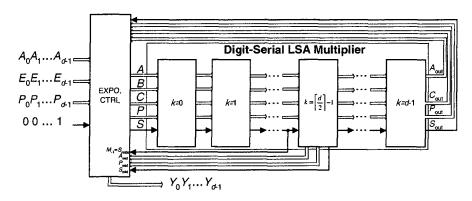

| 4.4.2.2 Linear Digit-Serial Systolic Array Multiplier                        | 80 |

| 4.4.3 Implementation Issues and Comparison                                   | 84 |

| 4.5 Exponentiation over Large $GF(2^m)$                                      | 87 |

| 4.5.1 Low Power Architectures for Large GF(2") Exponentiation                | 87 |

| 4.5.1.1 Reducing number of operations                                        | 87 |

| 4.5.1.2 Speeding up the computation                                          | 88 |

| 4.5.1.3 Bases choice                                                         | 88 |

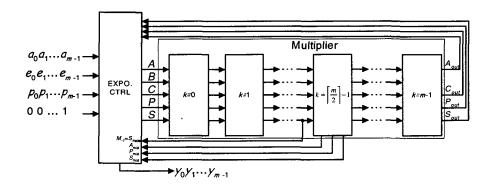

| 4.5.2 LSA Based Architecture for GF(2M) Exponentiation                       | 89 |

| 4.5.2.1 Linear Systolic Array Exponentiator                                  | 89 |

| 4.5.2.2 Dioit-Serial Linear Systolic Array Exponentiator                     | 91 |

TABLE OF CONTENTS VIII

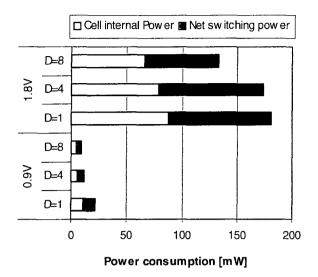

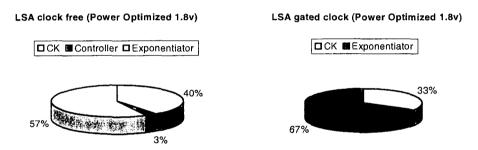

| 4.5.3 Implementation results and Comparison           |             |

|-------------------------------------------------------|-------------|

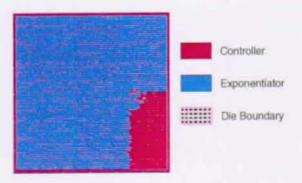

| 4.6 PHYSICAL DESIGN: LSA EXPONENTIATOR (PLACEMENT AND | ROUTING) 96 |

| CHAPTER 5 SELF-SYNCHRONIZING STREAM CIPHERS (SSSC)    | 98          |

| 5.1 SSSC Design Parameters                            |             |

| 5.1.1 Cipher Feedback Approach                        |             |

| 5.1.2 Fault Tolerance                                 | 100         |

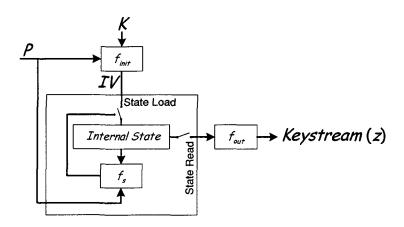

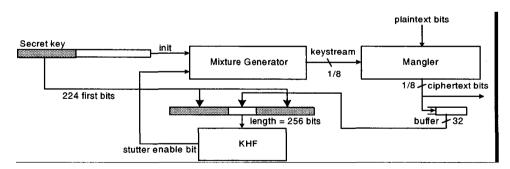

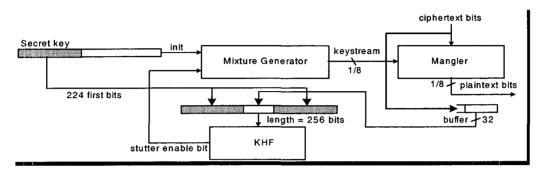

| 5.2 Frame Based SSSC (SSMG Principle)                 |             |

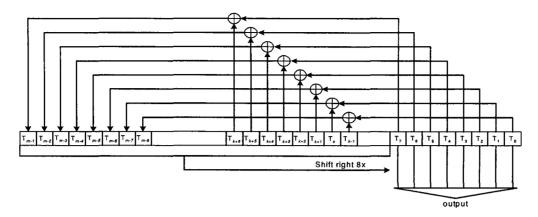

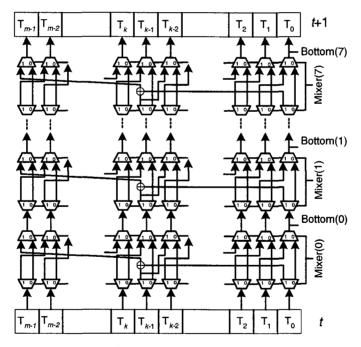

| 5.2.1 Mixture Generator MG                            |             |

| 5.2.1.1 Bit and Byte Granularity                      |             |

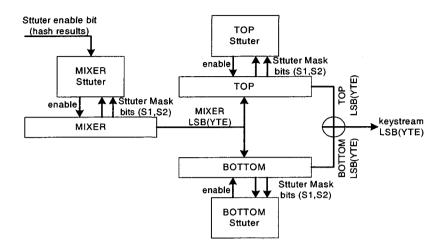

| 5.2.1.2 MG Stuttering                                 |             |

| 5.2.1.3 MG Initialization                             |             |

| 5.2.2 Mangler                                         |             |

| 5.2.3 Keyed Hash Function (KHF)                       |             |

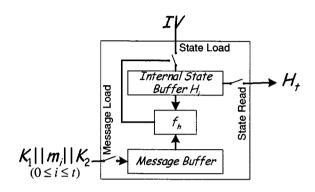

| 5.2.3.1 Implementation of the Hash Function           |             |

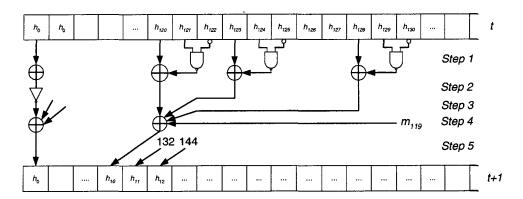

| 5.2.3.2 Diffusion and Confusion                       |             |

| 5.2.3.3 Collision free                                |             |

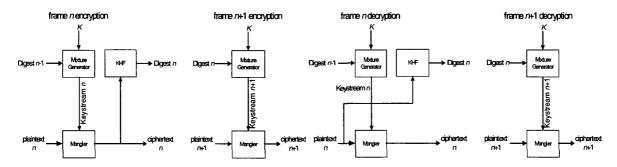

| 5.3 SSMG: OPERATIONS OF THE CIPHER                    |             |

| 5.4 SSMG: Cryptographic Security                      |             |

| 5.4.1 Repeated Occurrences                            |             |

| 5.4.2 Period of the SSCS and Hash Result Size         |             |

| CHAPTER 6 SECURING MPEG-2 STREAM IN DVB               |             |

| 6.1 MPEG-2 STREAM SOFTWARE ENCRYPTION                 |             |

| 6.1.1 Cryptographic Primitives                        |             |

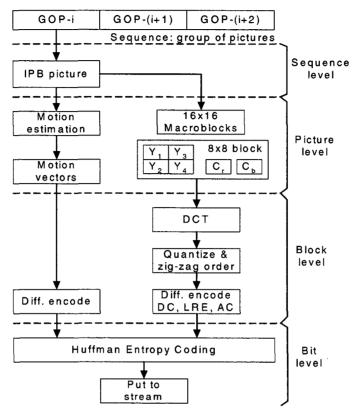

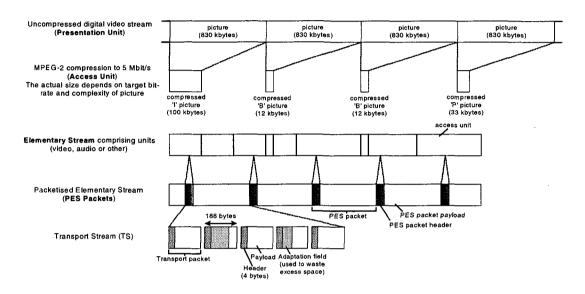

| 6.1.2 Structure of the MPEG-2 Codec                   |             |

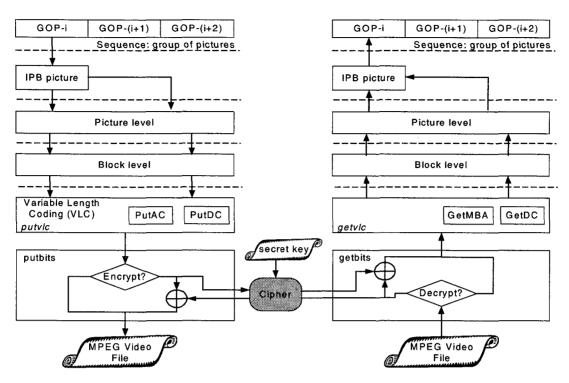

| 6.1.3 MPEG-2 Stream Encryption                        |             |

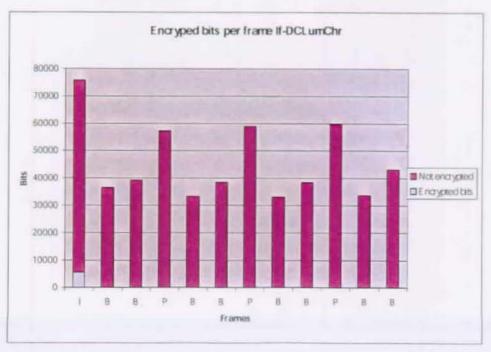

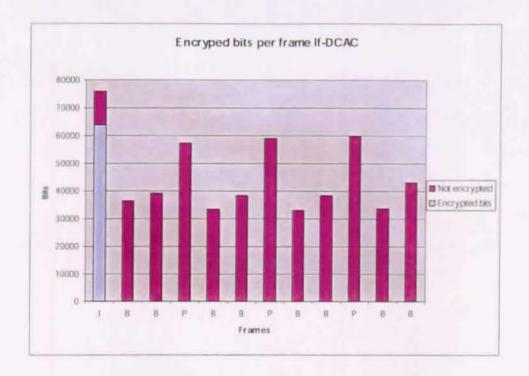

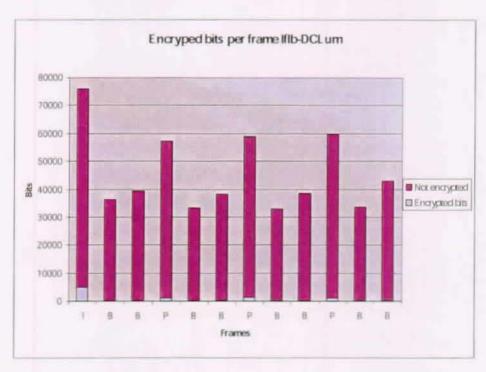

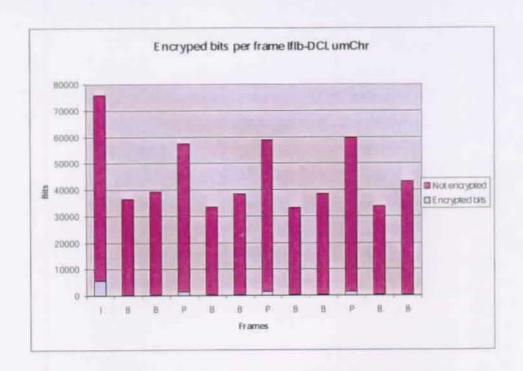

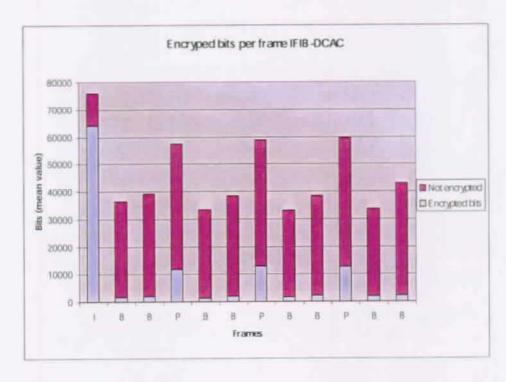

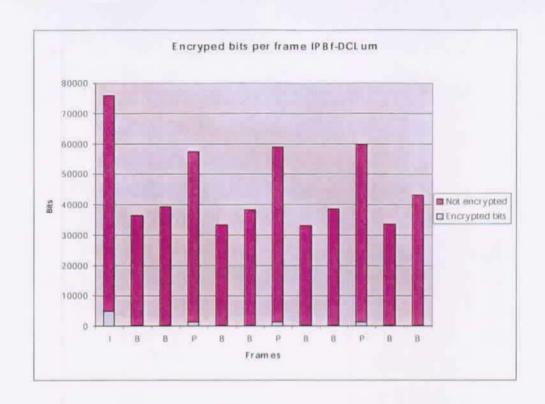

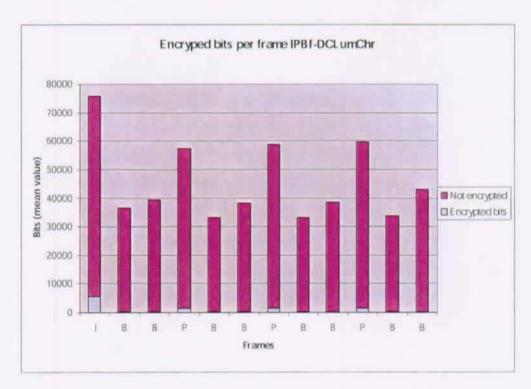

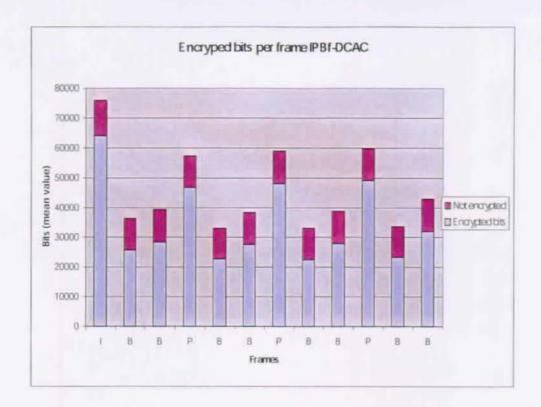

| 6.1.3.1 MPEG-2 selective encryption scheme            |             |

| 6.1.3.2 Quality of selective encryption               |             |

| 6.1.4 Encryption/Decryption Process                   |             |

| 6.1.4.1 Constraints                                   |             |

| 6.1.4.2 Design choices                                |             |

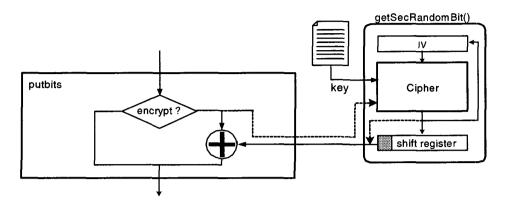

| 6.1.4.3 Interface functions                           |             |

| 6.1.4.4 SSMG Software Implementation                  |             |

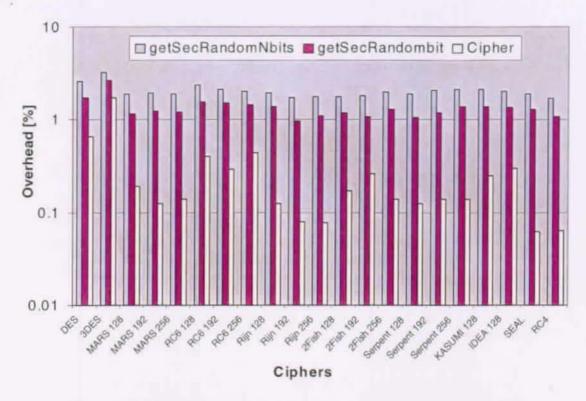

| 6.1.5 Implementation and Analysis                     |             |

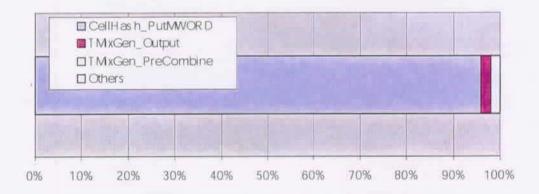

| 6.1.5.1 Performance profile of the MPEG encoder       |             |

| 6.1.5.2 Performance of the ciphers during encryption  |             |

|        | 6.1.5.3  | Performance profile of the SSMG                  | 117 |

|--------|----------|--------------------------------------------------|-----|

|        | 6.1.5.4  | Decryption and Real-time Playback                | 117 |

| 6.     | .1.6 Mai | n results                                        | 118 |

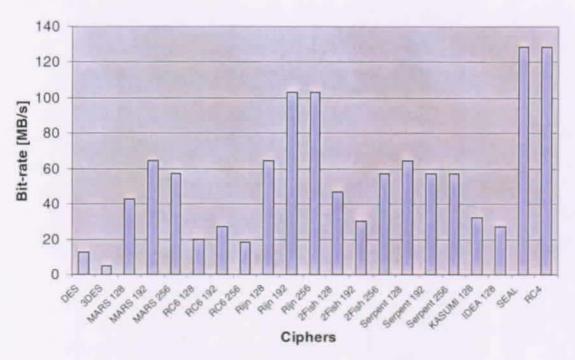

|        | 6.1.6.1  | Fastest ciphers                                  | 118 |

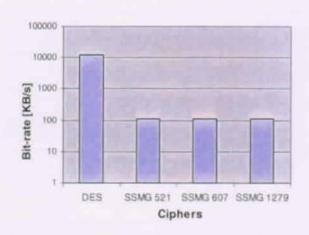

|        | 6.1.6.2  | Measuring one sequence                           | 118 |

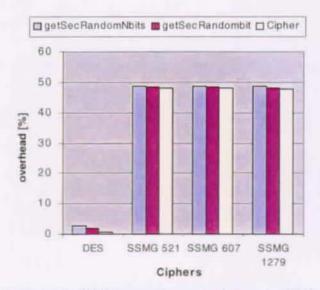

|        | 6.1.6.3  | Encryption overhead                              | 118 |

|        | 6.1.6.4  | Interfacing the ciphers                          | 118 |

|        | 6.1.6.5  | Weaknesses of the encryption scheme              | 118 |

| 6.2    | PART2: I | MPEG-2 Stream Hardware Encryption                | 119 |

| 6.     | 2.1 Pro  | gram Stream and Transport Stream                 | 119 |

| 6.     | 2.2 MP   | EG-2 Transmission using DVB standards            | 119 |

|        | 6.2.2.1  | Transmission of the Mpeg-TS                      | 119 |

|        | 6.2.2.2  | DVB Bearer Networks                              | 120 |

|        | 6.2.2.3  | FEC and Channel Coding                           | 120 |

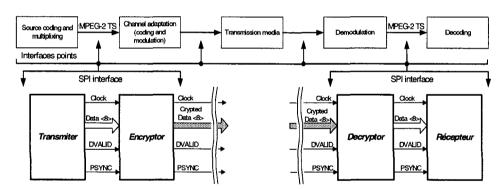

| 6.     | 2.3 DV   | B Encryption System                              | 121 |

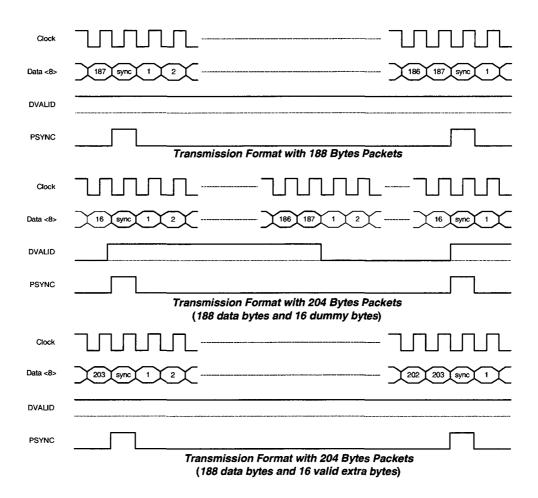

|        | 6.2.3.1  | Baseband MPEG-2 Interfaces                       | 122 |

|        | 6.2.3.1  | .1 Asynchronous Serial Interface (ASI)           | 123 |

|        | 6.2.3.1  | .2 Synchronous Serial Interface (SSI)            | 123 |

|        | 6.2.3.1  | .3 Synchronous Parallel Interface (SPI)          | 124 |

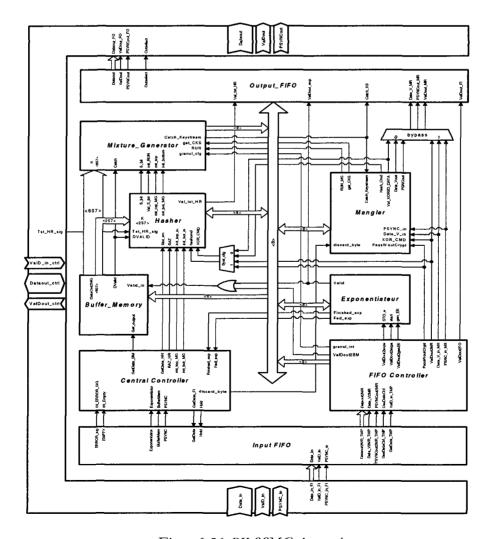

|        | 6.2.3.2  | Cryptosystem Structure                           | 124 |

|        | 6.2.3.2  | .1 PK-SSMG Interface                             | 124 |

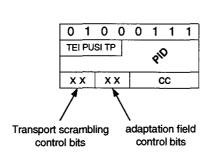

|        | 6.2.3.2  | .2 MPEG-TS Parsing (frame decoding)              | 126 |

|        | 6.2.3.2  | .3 Mixture Generator                             | 126 |

|        | 6.2.3.2  | .4 Exponentiator                                 | 126 |

|        | 6.2.3.2  | .5 Input/Output Fifos                            | 127 |

|        | 6.2.3.2  | .6 Bus Multiplexing                              | 128 |

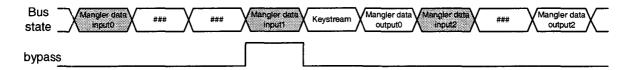

|        | 6.2.3.2  | .7 Mangler                                       | 129 |

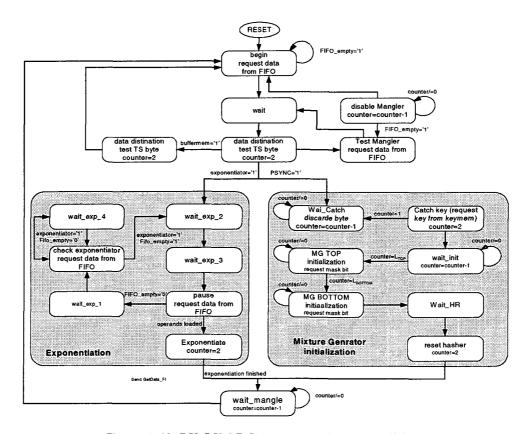

|        | 6.2.3.3  | PK-SSMG Controller                               | 129 |

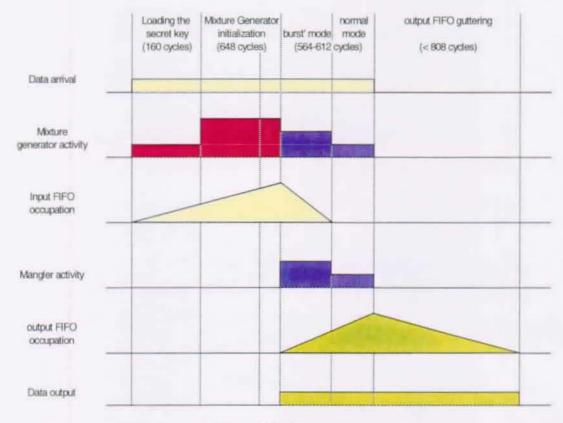

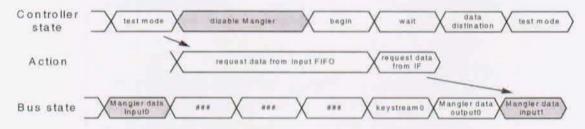

|        | 6.2.3.3  | .1 The Burst Mode                                | 130 |

|        | 6.2.3.3  | .2 Exponentiation Phase                          | 130 |

|        | 6.2.3.3  | .3 MG Initialization and Combining Phases        | 131 |

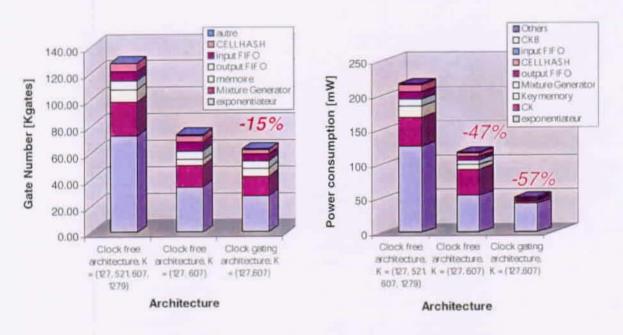

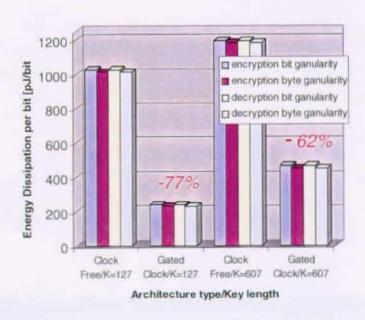

| 6      | 2.4 Perf | Formance Measurement and Results                 | 131 |

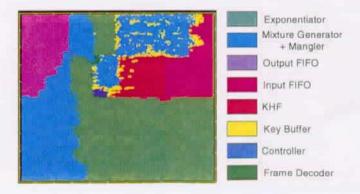

|        | 6.2.4.1  | Physical Design                                  | 133 |

| Снарті | ER 7 EI  | FFICIENT IMPLEMENTATION OF RIJNDAEL BLOCK CIPHER | 134 |

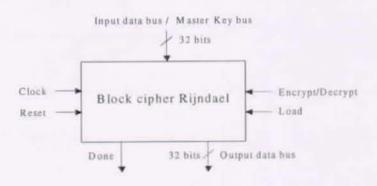

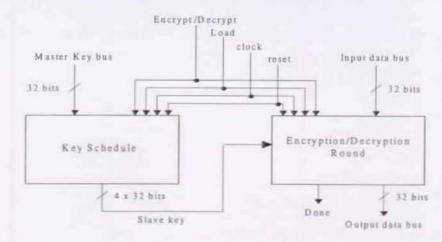

| 7.1    | Сноісе   | OF AN ARCHITECTURE                               | 134 |

|        |          |                                                  |     |

TABLE OF CONTENTS X

| 7.1.1                | Mode of operation                                         |

|----------------------|-----------------------------------------------------------|

| 7.1.2                | Hardware Parameters                                       |

| 7.1.3                | Cipher Architectures for Feedback modes                   |

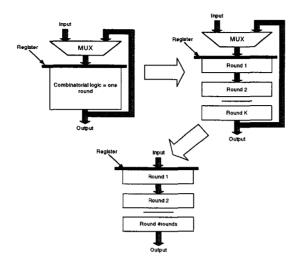

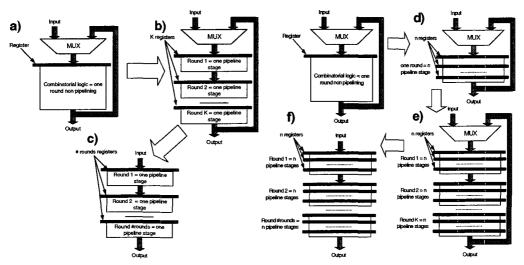

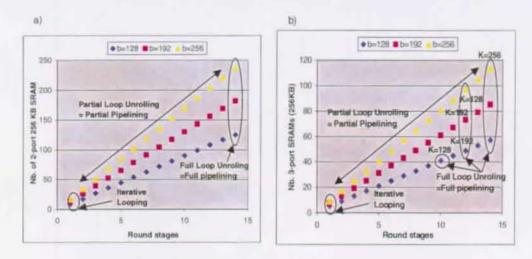

| 7.1.                 | 3.1 Basic Iterative Looping                               |

| 7.1.                 | 3.2 Partial and Full Loop Unrolling                       |

| 7.1.4                | Cipher Architectures for Non-Feedback Mode                |

| 7.1.                 | 4.1 Partial/Full Pipelining                               |

| 7.1.                 | .4.2 Partial/Full Pipelining with Sub-Pipelining          |

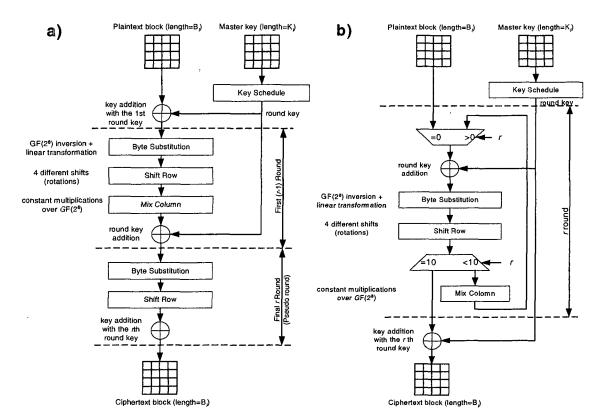

| 7.2 Sti              | RUCTURE AND PARAMETERS OF RIJNDAEL BLOCK CIPHER           |

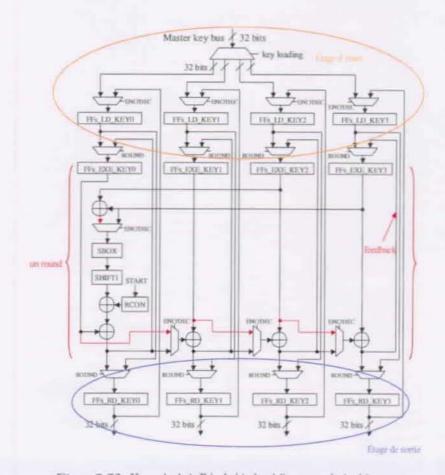

| 7.3 Rij              | NDAEL ITERATIVE LOOP UNROLLING                            |

| 7.3.1                | Interface                                                 |

| 7.3.2                | Key schedule                                              |

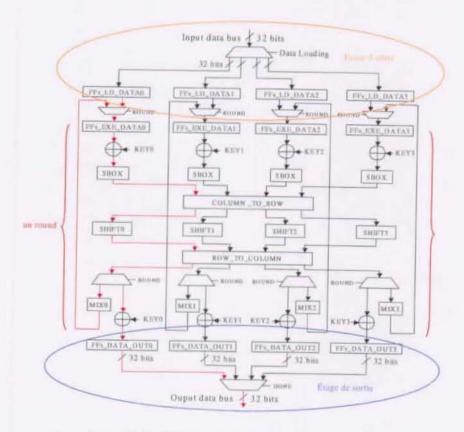

| 7.3.3                | Data Flow                                                 |

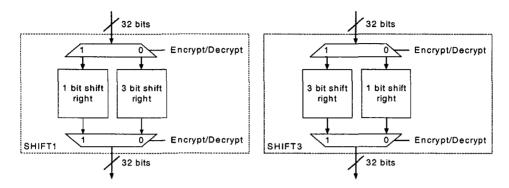

| 7.3.                 | .3.1 Shift Row Function                                   |

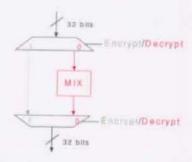

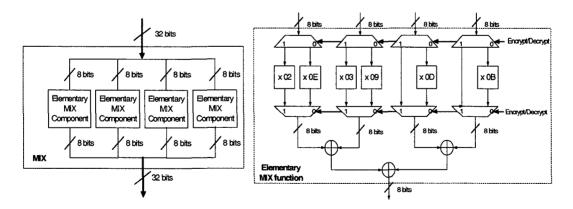

| 7.3.                 | .3.2 MIX Column Function                                  |

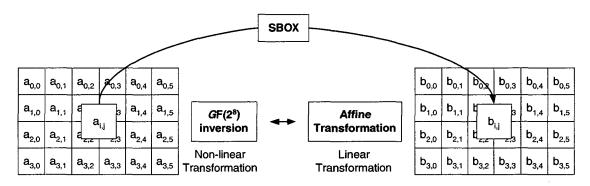

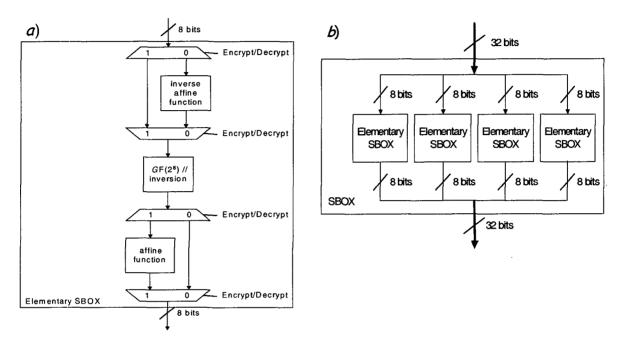

| 7.4 Rij              | NDAEL SBOXES                                              |

| 7.4.1                | Algorithm of Morii-Kasahara 144                           |

| 7.4.2                | $GF(2^8)$ as an Extension of $GF(2^4)$                    |

| 7.4.3                | Transition Between Representations of GF(2 <sup>8</sup> ) |

| 7.4.4                | An inverter over $GF(2^8)$                                |

| 7.4.5                | Rijndael SBOX Configuration                               |

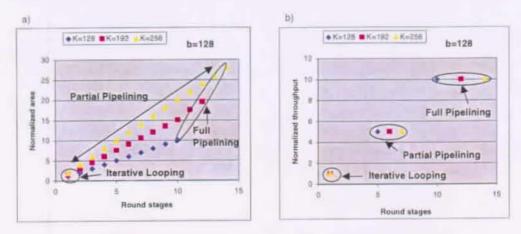

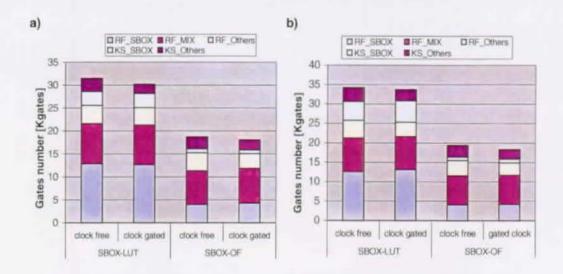

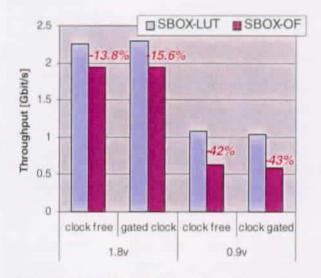

| 7.5 IMI              | PLEMENTATION RESULTS                                      |

| 7.5.1                | ASIC Implementation                                       |

| 7.5.2                | FPGA IMPLEMENTATION                                       |

| Chapter 8            | SUMMARY AND CONCLUSIONS                                   |

| 8.1 MA               | IN CONTRIBUTIONS                                          |

| 8.1.1                | Arithmetic in Large GF(2")                                |

| 8.1.2                | Self-Synchronizing Mixture Generator                      |

| 8.1.3                | Securing MPEG-2 Bitstream                                 |

| 8.1.4                | Efficient Implementation of Rijndael Block Cipher         |

| 8.2 Fu               | RTHER WORK                                                |

| Referenc<br>Appendix | ES                                                        |

| A.1 DE               | EFINITIONS                                                |

| A.1.1                | Maximal Length                                            |

| A.1.2                | Linear Complexity                                         |

| A.2    | LFS   | SR THEORY                                                          |

|--------|-------|--------------------------------------------------------------------|

| A      | .2.1  | Golomb's Principles                                                |

| A      | .2.2  | Some Facts and Definitions From Algebra                            |

| A.3    | DIS   | CRETE LOGARITHM PROBLEM (DLP)                                      |

| A      | .3.1  | Diffie-Hellman Key Exchange                                        |

| A      | .3.2  | El-Gamal Cryptosystem                                              |

| A      | .3.3  | Shank's Algorithm for Solving the Discrete Logarithm Problem       |

| A      | .3.4  | Pohlig-Hellman Algorithm                                           |

| A      | .3.5  | Chinese Remainder Theorem                                          |

| Appeni | DIX B | BIT PARALLEL ARITHMETICS IN $GF(2^4)$                              |

| B.1    | REP   | resentations of $GF(2^4)$                                          |

| B.2    | STA   | ndard Multiplication in $GF(2^4)$                                  |

| B.3    | STA   | ndard Multiplication by Constant ${\it w}^{14}$ in ${\it GF}(2^4)$ |

| B.4    |       | ndard Squaring in $GF(2^4)$                                        |

| B.5    | Dir   | ect Inversion in $GF(2^4)$                                         |

| Appeni | OIX C | <b>\</b>                                                           |

|        |       |                                                                    |

| C.1    | GF(   | 2 <sup>607</sup> ) Multiplication                                  |

| C.2    | GF(   | 2 <sup>607</sup> ) Exponentiation                                  |

| Appeni | нх Г  | SELECTIVE ENCRYPTION BITS FOR A SEQUENCE 178                       |

LIST OF FIGURES XII

# LIST OF FIGURES

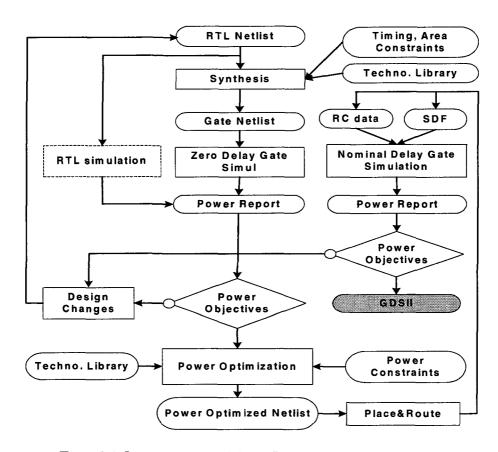

| Low-power oriented design flow using sub-micron processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

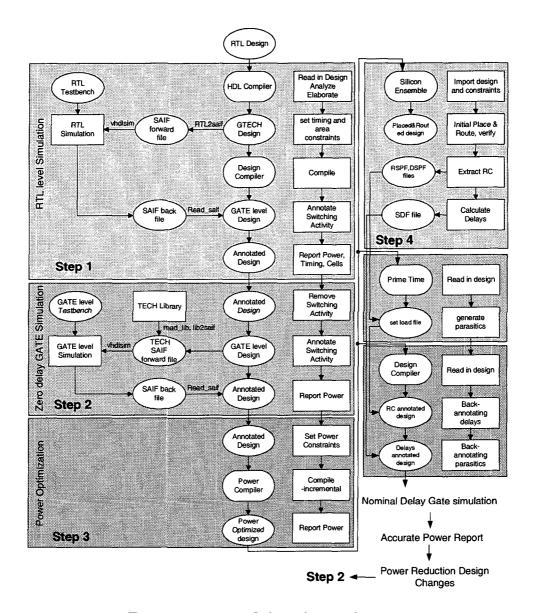

| Detailed LP deep submicron design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45  |

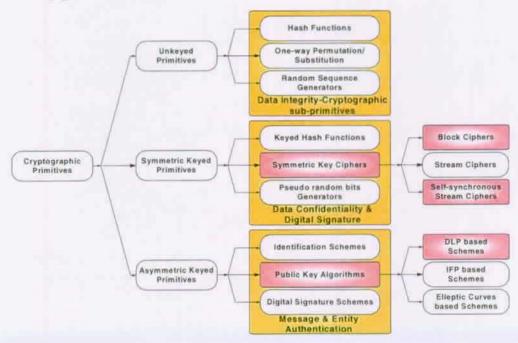

| Cryptographic primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48  |

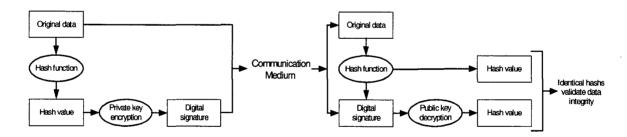

| Digital signature for data integrity validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50  |

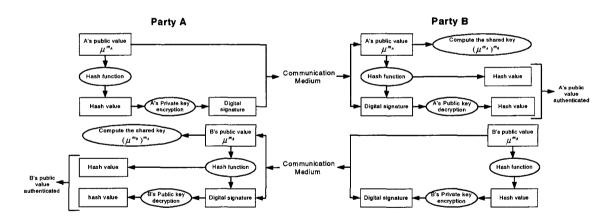

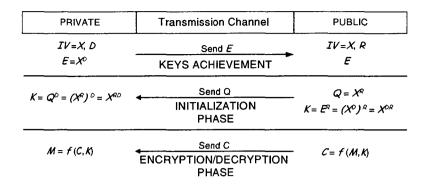

| Diffie-Hellman Key establishment protocols (key authentication and key agreement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51  |

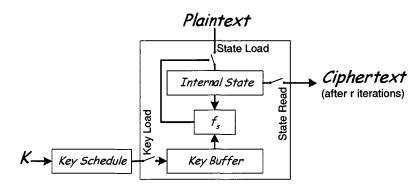

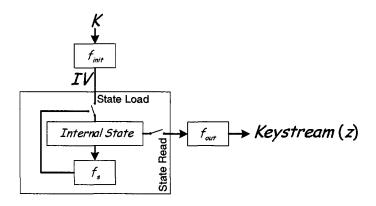

| Cryptographic finite state machine: implementing of a Block Cipher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55  |

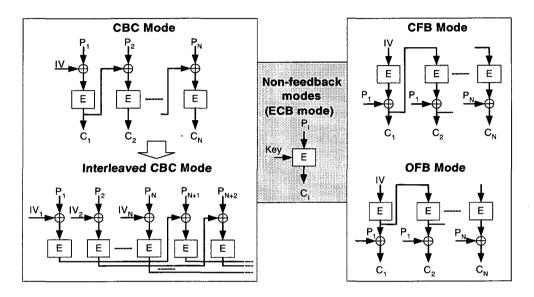

| Block Cipher operating mode (encryption)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57  |

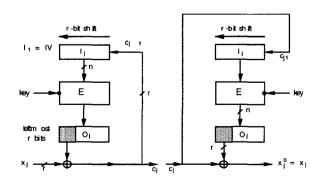

| Streaming using Block Cipher in CFB mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57  |

| Cryptographic finite state machine: implementation of a PRG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58  |

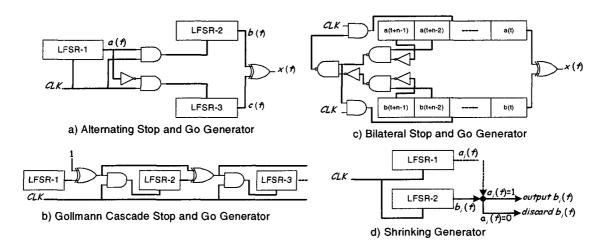

| Examples of LFSR based Stream Cipher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61  |

| Public and Private Operation Scheme of DLP based Cryptosystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65  |

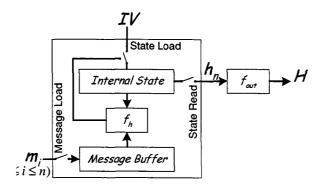

| Cryptographic finite state machine: implementation of a CHF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66  |

| MSR m-bit multiplier architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76  |

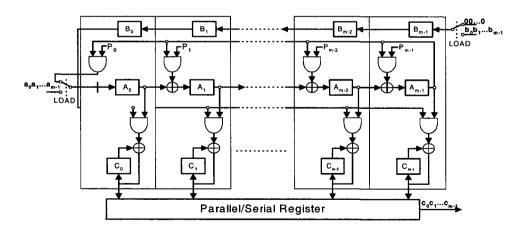

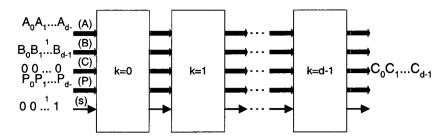

| Linear systolic array multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77  |

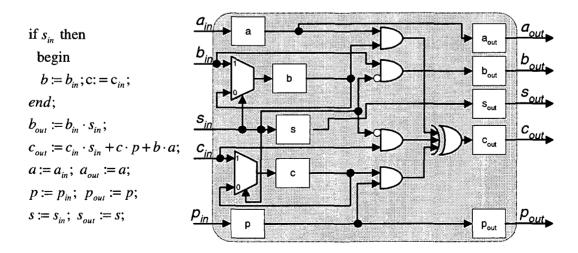

| LSA basic processing cell and its algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77  |

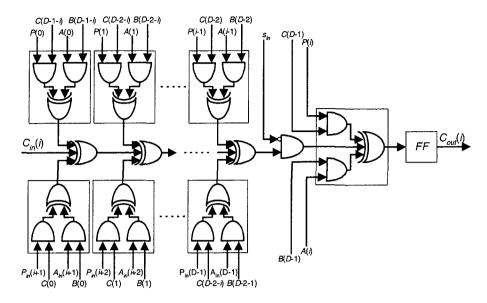

| Digit-serial MSR multiplier for field-generating polynomial $p(x)=1+x^k+x^m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79  |

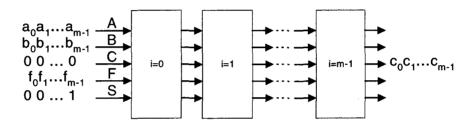

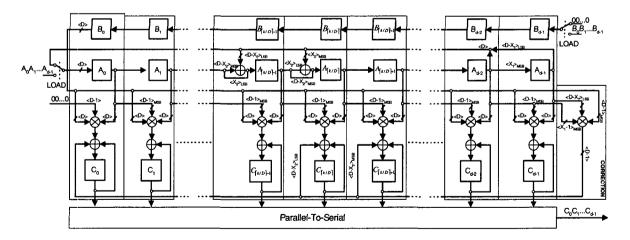

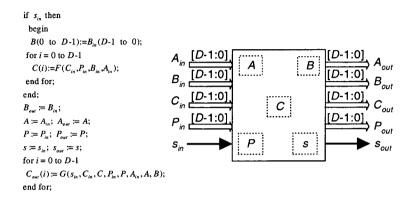

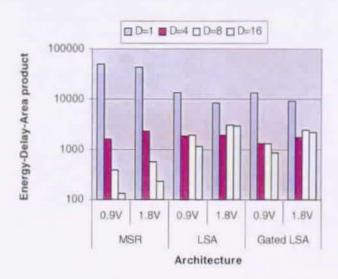

| Digit-serial, linear systolic array multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| LSA digit-serial basic processing cell and its algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81  |

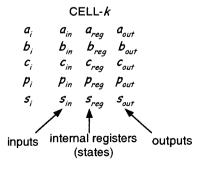

| LSA CELL-K multiplier representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81  |

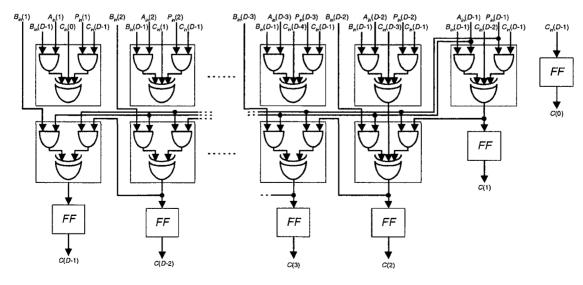

| Circuit diagram of the F function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82  |

| Folding bit-serial computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83  |

| Circuit diagram of the G function for one bit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

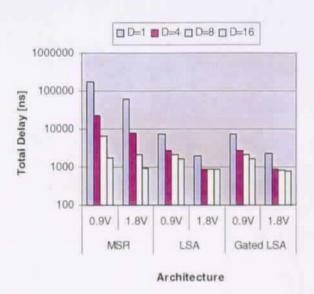

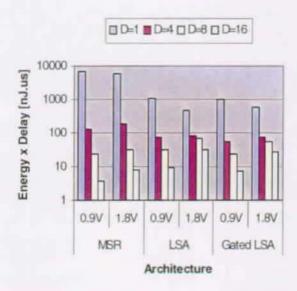

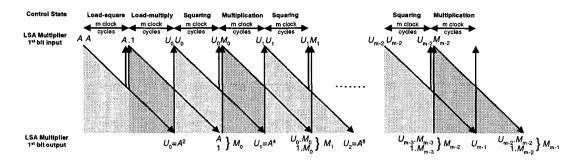

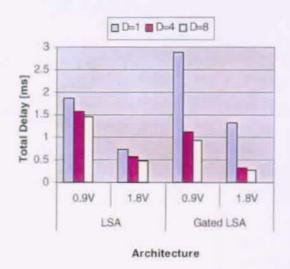

| Total delay comparison as function of the digit-size for one $GF(2^{607})$ multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85  |

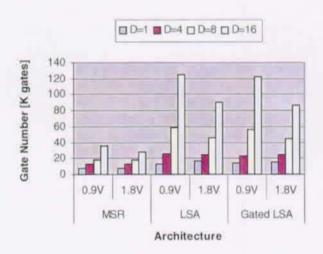

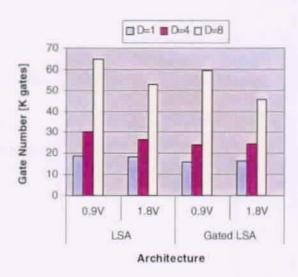

| Area in gates of the MSR, LSA and clock gating LSA digit-serial $GF(2^{607})$ multipliers as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| function of the digit size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |