# SPYDER: A RECONFIGURABLE PROCESSOR DEVELOPMENT SYSTEM

#### THÈSE Nº 1476 (1996)

PRÉSENTÉE AU DÉPARTEMENT D'INFORMATIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉBALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES TECHNIQUES

#### PAR

#### Christian ISELI

Ingénieur informaticien diplômé EPF originaire de Messen (SO)

acceptée sur proposition du jury:

Prof. E. Sanchez, directeur de thèse Dr R. Beuchat, corapporteur Prof. A. A. Jerraya, corapporteur Dr T. Kean, corapporteur Dr C. Piguet, corapporteur Dr R. Taylor, corapporteur

> Lausanne, EPFL 1996

# A Reconfigurable Processor Development System

#### THÈSE № 1476

### Présentée au Département d'informatique ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE pour l'obtention du grade de Docteur ès sciences techniques

par

### Christian Iseli

ingénieur informaticien diplômé EPF originaire de Messen (SO)

### acceptée sur proposition du jury:

| Prof. E. Sanchez    | directeur de thèse |

|---------------------|--------------------|

| Dr R. Beuchat       | corapporteur       |

| Prof. A. A. Jerraya | corapporteur       |

| Dr T. Kean          | corapporteur       |

| Dr C. Piguet        | corapporteur       |

| Dr R. Taylor        | corapporteur       |

Lausanne, EPFL 1996

### **Abstract**

he Spyder project consists of the development of a reconfigurable processor as well as its application development environment. The name Spyder is an anagram of the first letters of "REconfigurable Processor Development SYstem", where the term reconfigurable means that the hardware of the processor can be specifically tailored for each application.

Augmenting the performance of a processor implies either increasing its clock frequency or modifying its architecture. In the latter case, the solution usually adopted is to endow the processor with multiple execution units working in parallel (superscalar processors). The main problem with this kind of processors is to locate, in the sequential list of instructions of a program, batches of instructions susceptible of being executed in parallel by the different execution units of the processor.

Thanks to the advent of field-programmable gate array (FPGA) circuits, new kind of superscalar processor architectures can be considered. In particular, the Spyder processor features multiple reconfigurable execution units, which can be redesigned to fit each application, a feature which greatly increases the opportunities to perform parallel computations, particularly when working with small data elements (e.g., 16 Boolean data can be packed into a single 16-bit data word and processed in parallel by a specifically designed operation in the execution unit).

All the resources of the Spyder processor operate in parallel and are controlled by a very large instruction word (VLIW) 128 bits wide. The VLIW architecture allows the use of the full parallelism available to superscalar processors without requiring the complex dispatch unit needed by such processors to handle sequential scalar instructions.

The goal of the Spyder project is to design and implement a superscalar processor with multiple reconfigurable execution units, as well as the software development tools (i.e., C<sup>++</sup> compilers and a VLIW assembler) necessary to generate applications for this processor.

A prototype of the Spyder processor has been implemented on a VME board, which has been installed in a VME rack along with a SPARC board acting as host computer. A C++ compiler generating netlist files for the ViewLogic CAD tools has been developed and has generated a lot of interest in the scientific community. It is now available by anonymous ftp on the Internet.

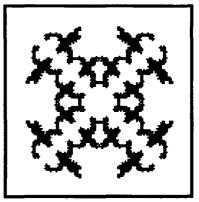

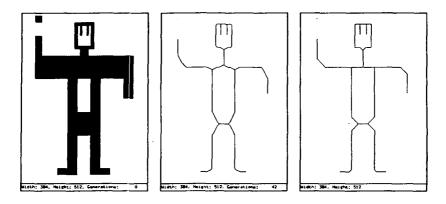

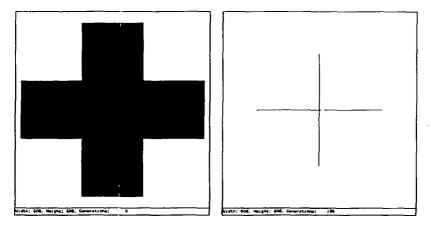

Image processing applications and cellular automata simulations have been programmed on the Spyder processor. The Spyder prototype has demonstrated its ability to achieve a high level of performance with these applications.

### Résumé

e projet Spyder (SYstème de Développement à Processeur REconfigurable) vise à développer un processeur reconfigurable, adaptable à chaque application, ainsi que son environnement de programmation.

Pour augmenter la puissance de calcul d'un processeur sans changer sa fréquence d'horloge, il est nécessaire de modifier son architecture. L'approche généralement choisie est l'exécution de plusieurs opérations en parallèle. Cette approche superscalaire présente certains problèmes particuliers telle que la détection, dans un programme donné, des opérations susceptibles d'être effectuées en parallèle par les différentes unités de traitement du processeur.

L'apparition récente d'un nouveau type de circuit programmable à haute complexité, le FPGA (Field-Programmable Gate Array), permet d'envisager une nouvelle solution: la conception d'un processeur superscalaire avec des unités de traitement reconfigurables, taillées sur mesure pour chaque application. Cette capacité de reconfiguration des unités de traitement permet également d'augmenter le parallélisme lorsque le processeur travaille avec des données de petite taille (par exemple des valeurs booléennes) qui sont compactées sur des mots de données de taille standard (16 valeurs booléennes par mot de 16 bits, par exemple).

Les différentes unités de traitement sont commandées en parallèle, directement par les bits de l'instruction: on parle alors d'une architecture de type VLIW (Very Large Instruction Word). Aussi, on peut assurer une occupation maximale des unités de traitement sans avoir à lire plusieurs instructions consécutives et à les réordonner (tâche effectuée par une unité spécialisé complexe dans les processeurs superscalaires standards).

Le but du projet Spyder est d'une part la conception et réalisation d'un processeur superscalaire avec plusieurs unités de traitement reconfigurables travaillant en parallèle, et d'autre part le développement de compilateurs spécialisés traduisant un programme écrit dans un langage de haut niveau, en l'occurrence C++, en code objet et fichiers de configuration pour les unités de traitement.

Le processeur Spyder a été réalisé sur une carte VME implantée dans une station de travail qui sert de machine hôte. Un compilateur, transformant du code C++ en schémas logiques directement utilisables par les outils de conception assistée par ordinateur de type ViewLogic, a été développé et, vu l'intérêt manifesté, est distribué sur Internet. Des algorithmes de traitement d'images, ainsi qu'un simulateur du jeu de la vie ont été implémentés sur le processeur Spyder avec de très bons résultats quant à la vitesse d'exécution des algorithmes.

.

# Acknowledgments.

Preparing a Ph.D. thesis is a long and time consuming process. During this period I have received a lot of help and support from my family and colleagues, and I would like to take this opportunity to express my gratitude towards them.

First, I want to thank my wife Christina and my son Abraham for their love, support, patience, and understanding for the long hours I spent away from them.

I thank my parents, Fritz and Rosemarie, and the other members of my family for their love, support, and for providing me with a good and broad education.

I thank Eduardo Sanchez, my thesis advisor, for his advice, help, trust, friendship, and good humor.

I thank Gianluca Tempesti, my friend, colleague, and English language expert, for the time and effort spent proofreading the manuscript of this thesis.

I thank André Badertscher, my friend, colleague, soldering wizard, and wildlife expert, for his help building the prototype boards of the Spyder processor, and for his enthusiastic descriptions of bobcats, beavers, falcons...

I thank the ACORT team, Peter Brühlmeier and Georges Vaucher, for their help in the design of the prototype Spyder boards.

I thank Daniel Mange, our lab director, Marlyse Taric, our dedicated and charming secretary, and all my other colleagues at the Logic Systems Laboratory for their friendship, help, and support.

I thank René Beuchat, Ahmed Jerraya, Tom Kean, Christian Piguet, and Richard Taylor for the time and effort spent as experts for this Ph.D. thesis.

I thank Nelly and Jacques Lesne for their love, for helping me balance physical and mental exercising, and for teaching me what "martial arts" really means. Tai Chi helped me relax during these stressful times.

## Remerciements

elle l'ascension d'une montagne, la préparation d'une thèse de doctorat est un travail de longue haleine, avec sa marche d'approche, ses haltes pour reprendre des forces, et finalement l'escalade des dernières pentes abruptes qui mènent au sommet. Maintenant que j'ai gravi les derniers mètres, je veux prendre le temps de remercier tous ceux qui, de près ou de loin, m'ont aidé, encouragé et soutenu tout au long de ce parcours.

Tout d'abord, je remercie ma femme Christina et mon fils Abraham pour l'amour et le soutien qu'ils m'ont témoigné, ainsi que la patience et la compréhension dont ils ont fait preuve durant mes longues absences de la maison familiale.

Je remercie mes parents, Fritz et Rosemarie, ainsi que tous les membres de ma famille pour leur amour, leur soutien, et pour m'avoir offert la possibilité de recevoir une éducation solide et ouverte d'esprit.

Je remercie mon directeur de thèse, Eduardo Sanchez, pour son aide, ses conseils éclairés, sa confiance, son amitié et sa bonne humeur permanente et contagieuse.

Je remercie mon ami, collègue et expert de langue anglaise, Gianluca Tempesti, pour tout le temps qu'il a passé à relire et corriger le manuscrit de cette thèse.

Je remercie mon ami, collègue, artiste du fer à souder et expert de nos contrées sauvages, André Badertscher, pour son aide dans la construction des cartes prototypes du processeur Spyder, ainsi que pour ses discussions enthousiastes et ses superbes photos de lynx, castors, faucons et autres hérons de nos régions.

Je remercie l'équipe de l'ACORT, Peter Brühlmeier et Georges Vaucher, pour leur aide dans la conception des cartes prototypes du processeur Spyder.

Je remercie Daniel Mange, le directeur du Laboratoire de Systèmes Logiques, Marlyse Taric, notre dévouée et charmante secrétaire, ainsi que tous mes autres collègues pour leur aide, leur soutien et leur amitié.

Je remercie René Beuchat, Ahmed Jerraya, Tom Kean, Christian Piguet et Richard Taylor qui ont très aimablement accepté la charge d'expert lors de mon examen de doctorat.

Je remercie Nelly et Jacques Lesne pour leur affection, leur aide dans la recherche d'un équilibre entre le travail corporel et mental, ainsi que pour leur enseignement des valeurs authentiques des arts martiaux. Le Tai Chi m'a aidé à me détendre durant les périodes les plus éprouvantes.

# Contents

|    |       |         |                                  |      |   |       |  | <i>,</i> • |

|----|-------|---------|----------------------------------|------|---|-------|--|------------|

|    |       |         |                                  |      |   |       |  | •••        |

| A  | bstra | ct      |                                  |      |   |       |  | iii        |

| R  | ésum  | é       |                                  |      |   |       |  | v          |

| A  | cknov | wledgn  | nents                            |      |   |       |  | vii        |

| R  | emer  | ciemer  | ets                              |      |   |       |  | ix         |

| Li | st of | Figure  | es                               |      |   |       |  | xvii       |

| Li | st of | Tables  |                                  |      |   |       |  | xxi        |

| 1  | Intr  | oducti  | on                               |      |   |       |  | 1          |

| 2  | Δn    | Introd  | uction to FPGA Circuits          |      |   |       |  | 3          |

| _  | 2.1   |         | al Aspects of FPGA Architectures |      |   |       |  | 3          |

|    | 2.2   |         | ation Design Process             |      |   |       |  | 4          |

|    | 2.3   | • •     | XC4000 FPGA Circuits             |      |   |       |  | 4          |

|    | 2.4   |         | ACT2 FPGA Circuits               |      |   |       |  | 6          |

| 3  | Pro   | cessors | and Performance                  |      |   |       |  | 9          |

|    | 3.1   | Genera  | al-Purpose Processors            | <br> |   |       |  | 9          |

|    | 3.2   | CISC    | and RISC Processors              | <br> |   |       |  | 10         |

|    | 3.3   | Pipelii | ning                             | <br> |   |       |  | 10         |

|    | 3.4   | Multip  | le-Issue Processors              | <br> |   |       |  | 12         |

|    | 3.5   | Specia  | l-Purpose Processors             | <br> | • | <br>٠ |  | 13         |

| 4  | Spy   | der Ba  | sics                             |      |   |       |  | 15         |

|    | 4.1   | The S   | oyder Processor                  | <br> |   |       |  | 15         |

|    |       | 4.1.1   | Multiple Execution Units         |      |   |       |  | 16         |

|    |       | 4.1.2   | Register Windowing               |      |   |       |  | 16         |

|    |       | 4.1.3   | Programming                      | <br> |   |       |  | 16         |

|    |       | 4.1.4   | Host Workstation Coupling        | <br> |   |       |  | 17         |

|    | 4.2   | The D   | evelopment Environment           | <br> |   |       |  | 17         |

|    |       | 4.2.1   | Host Workstation Program         | <br> |   |       |  | 17         |

|    |       | 422     | Execution Units Configuration    |      |   |       |  | 17         |

|   |     | 4.2.3   | VLIW Program                                   |

|---|-----|---------|------------------------------------------------|

| 5 | Spy |         | rchitecture 19                                 |

|   | 5.1 | Princi  | ple of Operation                               |

|   | 5.2 | Struct  | ure of an Instruction                          |

|   |     | 5.2.1   | Sequencer                                      |

|   |     | 5.2.2   | Load and Store                                 |

|   |     | 5.2.3   | Register Window Control                        |

|   |     | 5.2.4   | Execution Units                                |

|   |     | 5.2.5   | Special                                        |

|   | 5.3 | Hardw   | vare Implementation                            |

|   |     | 5.3.1   | The VME Controller                             |

|   |     | 5.3.2   | The Sequencer                                  |

|   |     | 5.3.3   | The Program Memory                             |

|   |     | 5.3.4   | The Load and Store Unit                        |

|   |     | 5.3.5   | The Data Memory                                |

|   |     | 5.3.6   | The Register Banks                             |

|   |     | 5.3.7   | The Register Window Controller                 |

|   |     | 5.3.8   | The Execution Units                            |

| 3 | A   | الممداد | on Development Overview 41                     |

| , | 6.1 |         | eation Overview                                |

|   | 6.2 |         | ng the Application                             |

|   | 0.2 | 6.2.1   | Accessing Spyder                               |

|   | 6.3 | -       | Workstation Program                            |

|   | 0.0 | 6.3.1   | Sharing Data                                   |

|   | 6.4 |         | amming Spyder                                  |

|   | 0.1 | 6.4.1   | Scanning Window Algorithm                      |

|   |     | 6.4.2   | Splitting Again                                |

|   | 6.5 |         | tion Units Configuration                       |

|   | 0.0 | 6.5.1   | Testing the Hardware Operators                 |

|   | 6.6 |         | ating the VLIW Object Code using C++           |

|   |     | 6.6.1   | Using the Compiler                             |

|   |     | 6.6.2   | Simulating the Whole Program                   |

|   | 6.7 | Writin  | g Real VLIW Assembler                          |

|   |     | 6.7.1   | Hardware Operator Assignment                   |

|   |     | 6.7.2   | Writing the Assembler Source File              |

|   |     |         | 6.7.2.1 Defining the Opcode Masks              |

|   |     | 6.7.3   | Assembler Structure                            |

|   |     |         | 6.7.3.1 Memory Transfers                       |

|   |     |         | 6.7.3.2 Execution Units Operations             |

|   |     |         | 6.7.3.3 Sequencer Operations                   |

|   |     | 6.7.4   | Implementation of the Windowing Algorithm 60   |

|   |     |         | 6.7.4.1 First Instruction of the Main Loop 61  |

|   |     |         | 6.7.4.2 Second Instruction of the Main Loop 62 |

|   |     | 6.7.5  | Using th   | e Assembler                           |

|---|-----|--------|------------|---------------------------------------|

|   | 6.8 | Synthe | sizing the | Execution Units                       |

|   | 6.9 |        |            | ogram                                 |

|   |     |        | _          |                                       |

| 7 |     |        | -          | nthesizer nlc 65                      |

|   | 7.1 |        |            | nesis: an Example                     |

|   |     | 7.1.1  |            | e Operators                           |

|   |     |        | 7.1.1.1    | The Symbol of a Hardware Operator 65  |

|   |     |        | 7.1.1.2    | The Netlist of a Hardware Operator 66 |

|   |     | 7.1.2  | Hardwar    | e Operators Library                   |

|   |     | 7.1.3  | Example    | ÷                                     |

|   | 7.2 | The L  | anguage .  |                                       |

|   |     | 7.2.1  |            | pes                                   |

|   |     | 7.2.2  | Hardwar    | re Operators Description              |

|   |     |        | 7.2.2.1    | Basic Logic Gates                     |

|   |     |        | 7.2.2.2    | Buffers and Inverters                 |

|   |     |        | 7.2.2.3    | Numerical Comparators                 |

|   |     |        | 7.2.2.4    | Multiplexers                          |

|   |     |        | 7.2.2.5    | Registers                             |

|   |     |        | 7.2.2.6    | Constant Values                       |

|   |     |        | 7.2.2.7    | Adders                                |

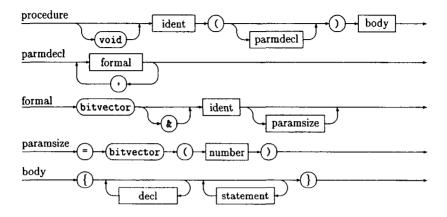

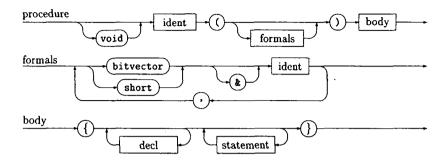

|   |     | 7.2.3  | Procedu    | re Description                        |

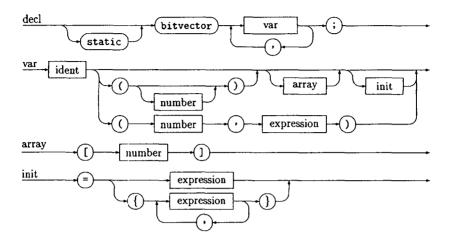

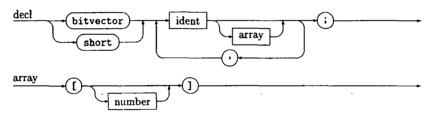

|   |     | 7.2.4  | Variable   | Declarations                          |

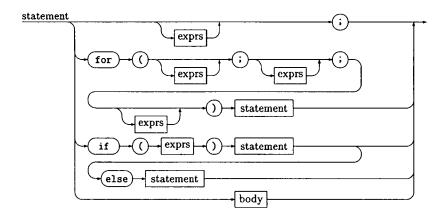

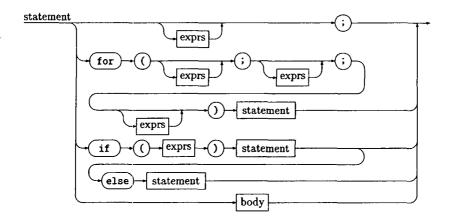

|   |     | 7.2.5  | Stateme    | nts                                   |

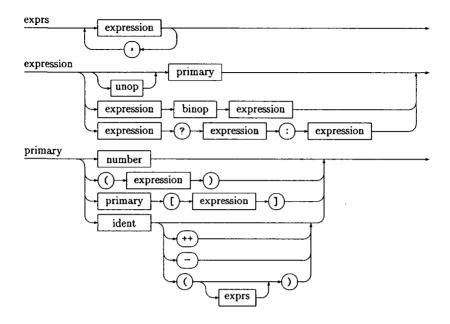

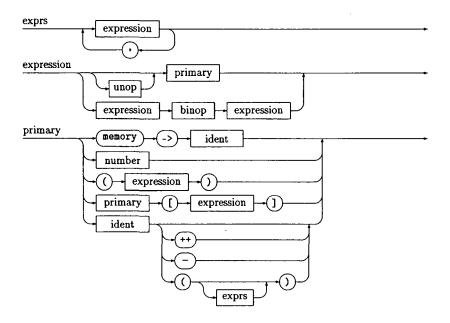

|   |     | 7.2.6  | Expressi   | ons                                   |

|   | 7.3 | The C  | compiler   |                                       |

|   |     | 7.3.1  | Parsing    | and Tree Construction                 |

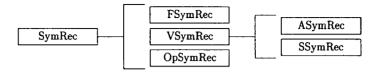

|   |     |        | 7.3.1.1    | The Symbol Table                      |

|   |     |        | 7.3.1.2    | Hardware Library Components 79        |

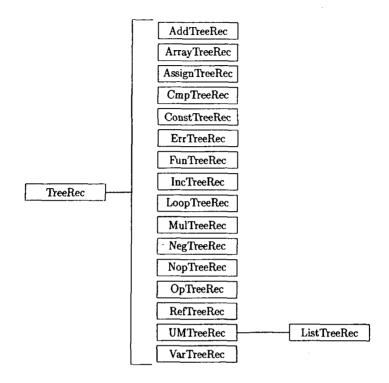

|   |     |        | 7.3.1.3    | The Parse Tree                        |

|   |     |        | 7.3.1.4    | Data Components                       |

|   |     |        | 7.3.1.5    | Operators                             |

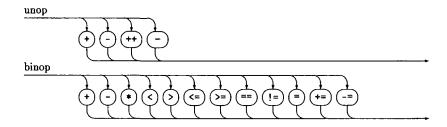

|   |     |        | 7.3.1.6    | Unary Operators                       |

|   |     |        | 7.3.1.7    | Binary Associative Operators 83       |

|   |     |        | 7.3.1.8    | Statements                            |

|   |     |        | 7.3.1.9    | Other Tree Components                 |

|   |     | 7.3.2  | Partial l  | Evaluation                            |

|   |     | 7.3.3  | Prepara    | tions for Hardware Synthesis          |

|   |     |        | 7.3.3.1    | Expression Width Computation 85       |

|   |     |        | 7.3.3.2    | Variables Initialization              |

|   |     | 7.3.4  | Hardwa     | re Synthesis                          |

|   |     |        | 7.3.4.1    | Hardware Operator Selection           |

|   |     |        | 7.3.4.2    | Shift Operators Synthesis             |

|   |     |        | 7.3.4.3    | Simple Logic Gates Synthesis          |

|   |     |        | 7.3.4.4    | Truth Conditions Synthesis            |

|   |     |        |            |                                       |

|   |     |               | 7.3.4.5 Arithmetic Expressions Synthesis 87 |

|---|-----|---------------|---------------------------------------------|

|   |     |               | 7.3.4.6 Arithmetic Comparisons Synthesis    |

|   |     |               | 7.3.4.7 Conditional Expression Synthesis    |

|   |     |               | 7.3.4.8 Conditional Statement Synthesis     |

|   |     |               | 7.3.4.9 Function Call Synthesis             |

|   |     | 7.3.5         | Feedback of Static Variables                |

|   |     | 7.3.6         | Hardware Optimizations                      |

|   |     | 7.3.7         | Output Wiring and Netlist Cleanup           |

|   |     | 7.3.8         | Symbol and Netlist Output 91                |

|   |     | 7.3.9         | Concluding Remarks                          |

|   | 7.4 | Compa         | arison with VHDL                            |

|   |     | -             |                                             |

| 8 |     |               | V Compiler mcc 95                           |

|   | 8.1 | _             | ole of Control Program                      |

|   | 8.2 |               | anguage                                     |

|   |     | 8.2.1         | Hardware Operators Definition               |

|   |     | 8.2.2         | Memory Content Definition                   |

|   |     | 8.2.3         | Variable Declaration                        |

|   |     | 8.2.4         | Procedure Definition                        |

|   |     | 8.2.5         | Statements                                  |

|   |     | 8.2.6         | Expressions                                 |

|   | 8.3 |               | ompiler                                     |

|   |     | 8.3.1         | Parsing and Tree Construction               |

|   |     |               | 8.3.1.1 The Symbol Table                    |

|   |     |               | 8.3.1.2 The Parse Tree                      |

|   |     |               | 8.3.1.3 Data Components                     |

|   |     |               | 8.3.1.4 Operators                           |

|   |     |               | 8.3.1.5 Statements                          |

|   |     |               | 8.3.1.6 Other Tree Components               |

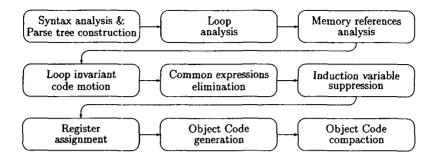

|   |     | 8.3.2         | Source Level Optimizations                  |

|   |     |               | 8.3.2.1 Loop Analysis                       |

|   |     |               | 8.3.2.2 Memory References Analysis          |

|   |     |               | 8.3.2.3 Loop Invariant Code Motion          |

|   |     |               | 8.3.2.4 Common Expressions Elimination      |

|   |     |               | 8.3.2.5 Induction Variable Suppression      |

|   |     | 8.3.3         | Register Assignment                         |

|   |     | 8.3.4         | Hardware Operator Assignment                |

|   |     | 8.3.5         | Object Code Generation                      |

|   |     | 8.3.6         | Object Code Compaction                      |

| 9 | The | <b>3/1 13</b> | Assembler imac 115                          |

| J | 9.1 |               | Seembler Source Syntax                      |

|   | 9.1 | 9.1.1         | The Execution Units Command Masks           |

|   |     | 9.1.1         | Instruction Syntax                          |

|   |     | 9.1.2         | The Data Transfer Commands                  |

|   |     | J. I.O        | THE Data Hansiel Colliniands                |

|              |        | 9.1.4   | The Execution Unit Commands     |   |   |    |         |

|--------------|--------|---------|---------------------------------|---|---|----|---------|

|              | 9.2    | 9.1.5   | The Sequencer Commands          |   |   |    |         |

|              | 9.2    |         | ssembler                        |   |   |    |         |

|              | 9.3    | Relate  | ed Tools                        | • | ٠ | ٠. | <br>121 |

| 10           | The    | UNIX    | K Interface                     |   |   |    | 123     |

|              | 10.1   | The Sp  | pyder Device Driver             |   |   |    | <br>123 |

|              |        | 10.1.1  | The Data Memory                 |   |   |    | <br>123 |

|              |        | 10.1.2  | The Program Memory              |   |   |    | <br>124 |

|              |        |         | The FPGA Configuration          |   |   |    |         |

|              |        | 10.1.4  | The Control and Status Register |   |   |    | <br>124 |

|              | 10.2   |         | ling the Spyder Board           |   |   |    |         |

|              |        |         | Installing the Driver Files     |   |   |    |         |

|              |        | 10.2.2  | Configuring the Entry Points    |   |   |    | <br>125 |

|              |        | 10.2.3  | Configuring the System          |   |   |    | <br>125 |

| 11           | Eva    | luation | n                               |   |   |    | 127     |

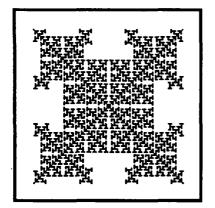

|              |        |         | <br>Cellular Automaton          |   |   |    |         |

|              |        |         | rite Growth Modeling            |   |   |    |         |

|              |        |         | ing                             |   |   |    |         |

|              |        |         | Detection                       |   |   |    |         |

| 12           | Con    | clusio  | ns                              |   |   |    | 133     |

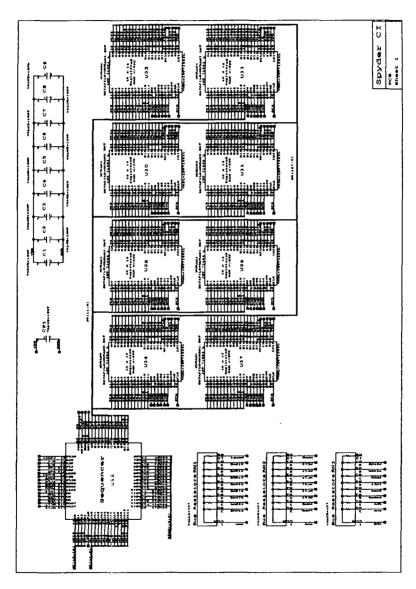

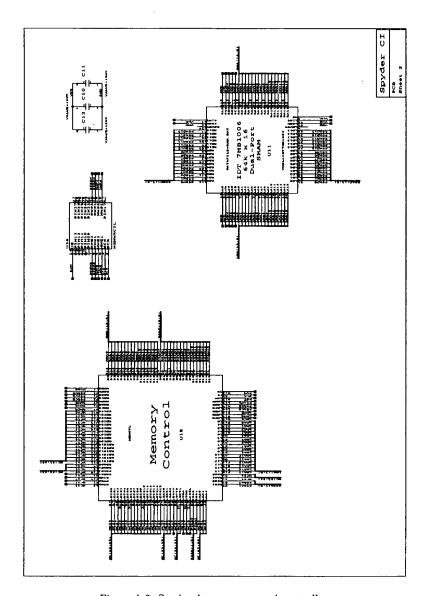

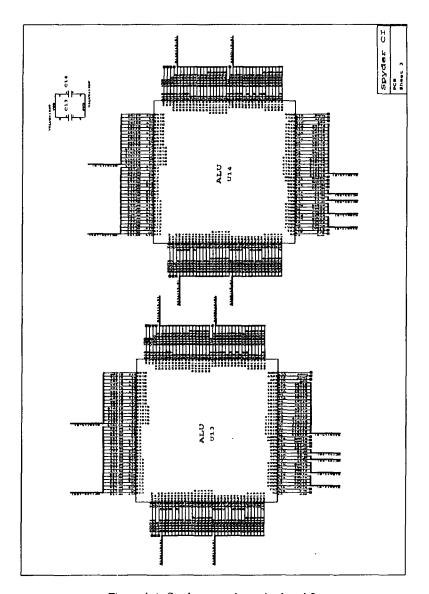

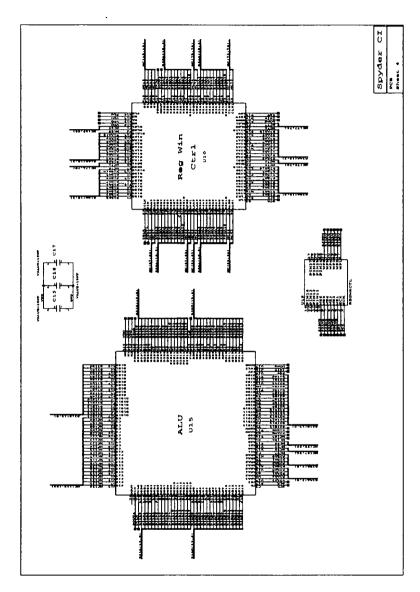

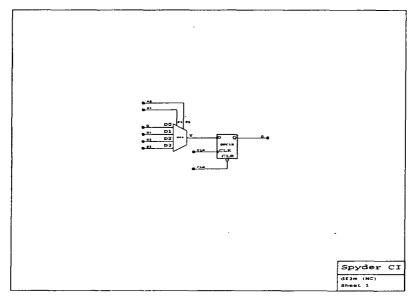

| A            | Spy    | der Sci | chematic                        |   |   |    | 135     |

|              |        |         |                                 |   |   |    | 100     |

| В            | Seq    | uencer  | Schematic                       |   |   |    | 145     |

| $\mathbf{C}$ | Loa    | d and   | Store Unit Schematic            |   |   |    | 153     |

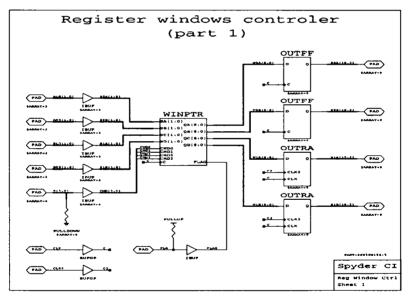

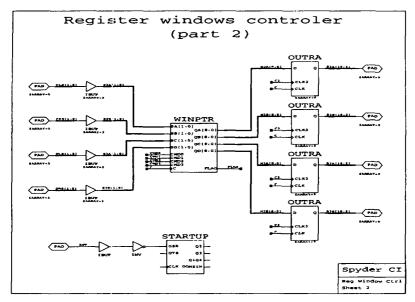

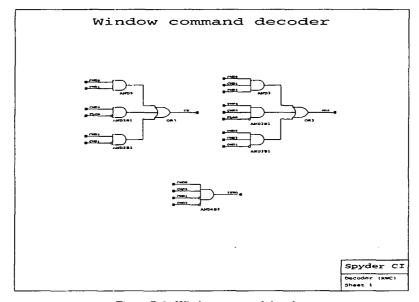

| D            | Reg    | ister V | Window Controller Schematic     |   |   |    | 157     |

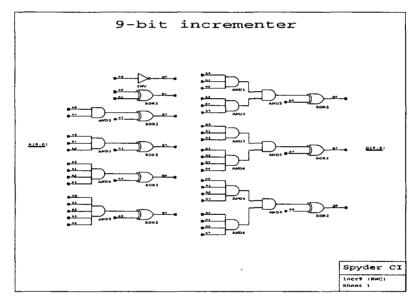

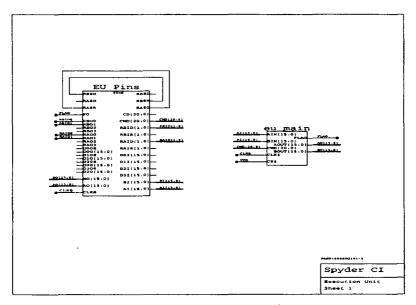

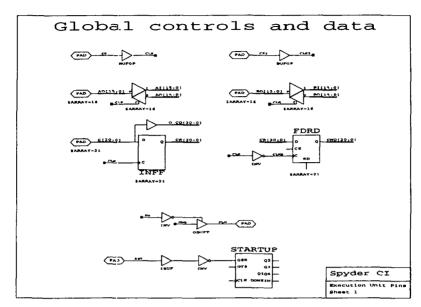

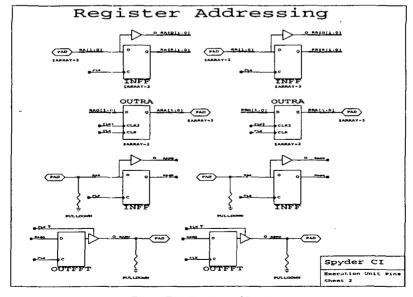

| E            | Exe    | cution  | Unit Schematic                  |   |   |    | 163     |

| Ri           | hling  | Taphy   |                                 |   |   |    | 167     |

|              | _      |         |                                 |   |   |    | 101     |

| Cı           | ırricı | ulum \  | Vitæ                            |   |   |    | 173     |

# List of Figures\_\_\_\_\_

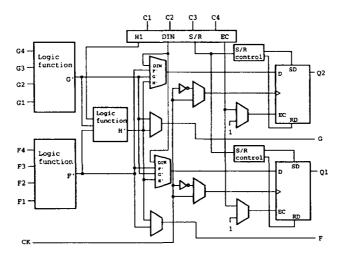

| 2.1  | XC4000 logic cell architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

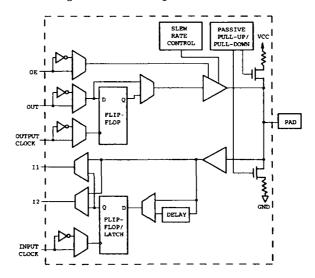

| 2.2  | XC4000 input/output cell architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5          |

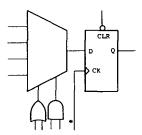

| 2.3  | ACT2 logic cell architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6          |

| 2.4  | ACT2 logic cell inputs and output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7          |

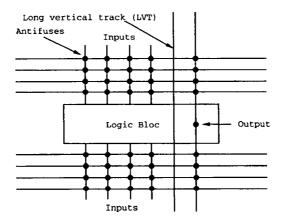

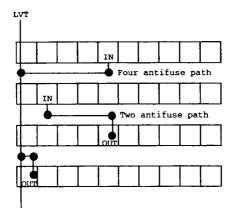

| 2.5  | ACT2 signal routing examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7          |

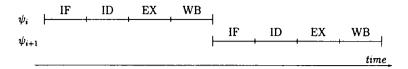

| 3.1  | Sequential execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11         |

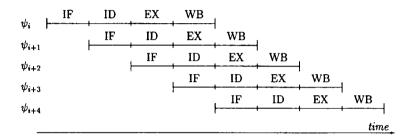

| 3.2  | Pipelined execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11         |

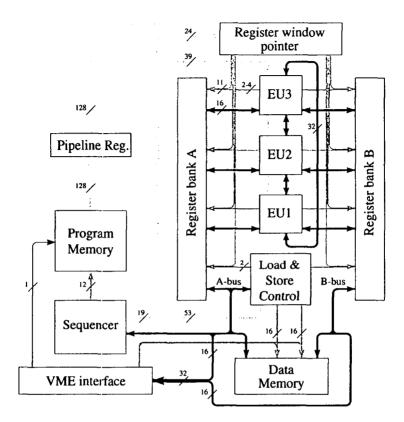

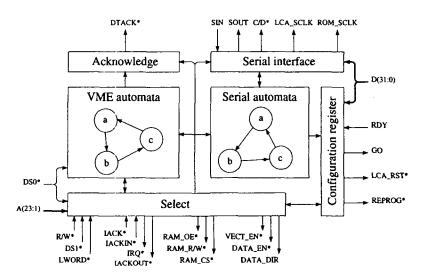

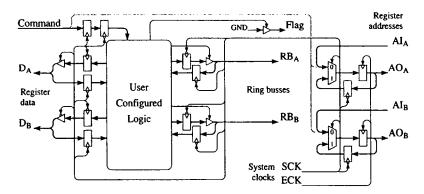

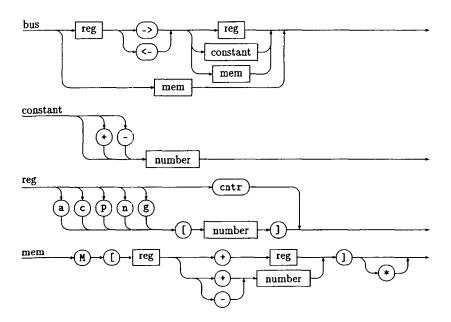

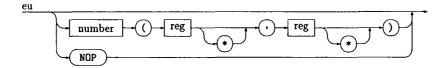

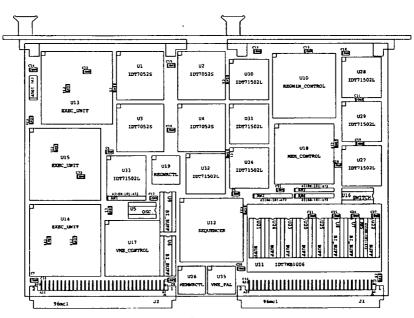

| 5.1  | Spyder architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20         |

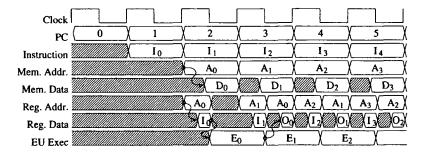

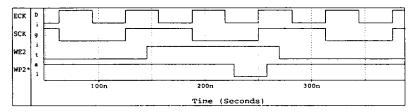

| 5.2  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21         |

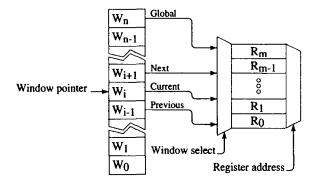

| 5.3  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21         |

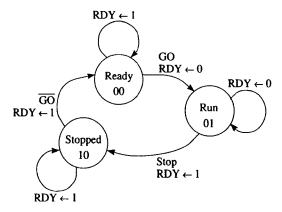

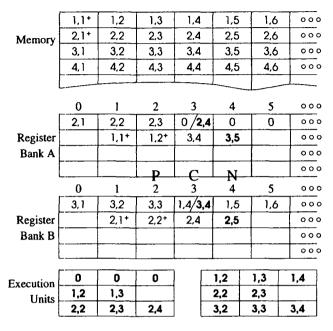

| 5.4  | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25         |

| 5.5  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27         |

| 5.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28         |

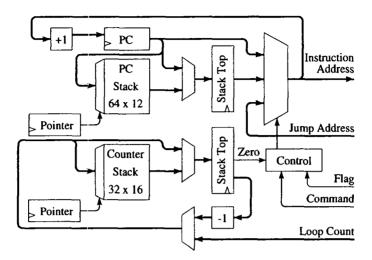

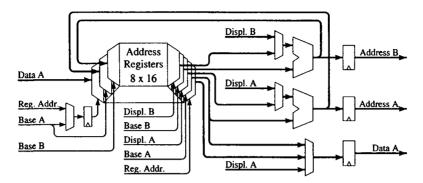

| 5.7  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31         |

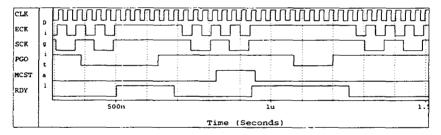

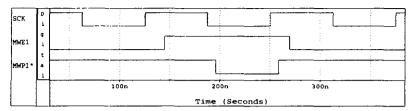

| 5.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32         |

| 5.9  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32         |

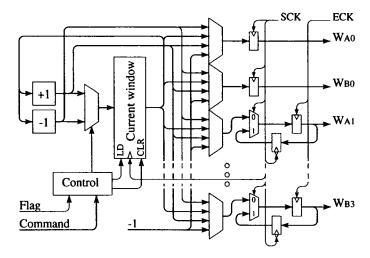

| 5.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36         |

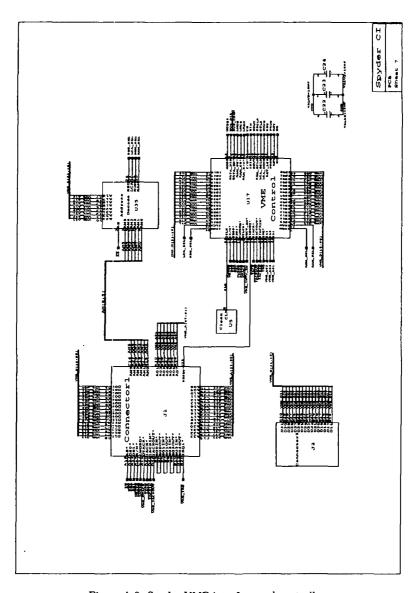

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37         |

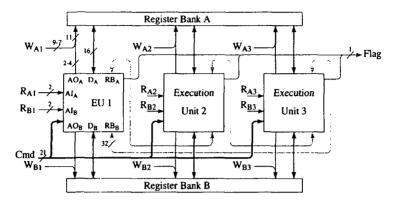

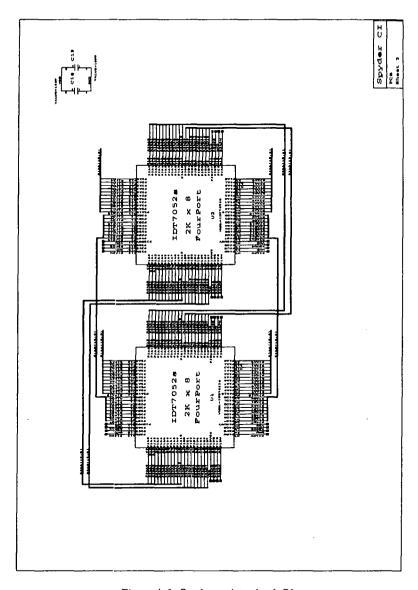

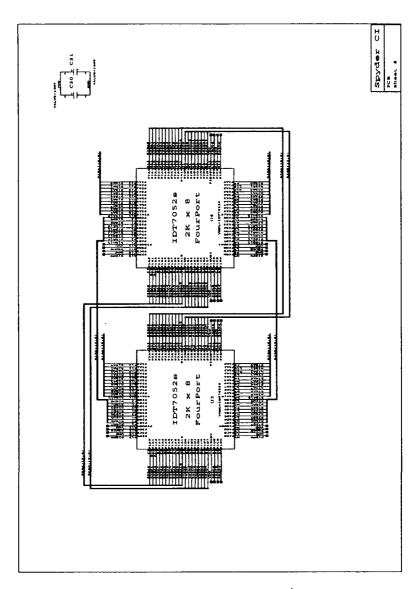

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38         |

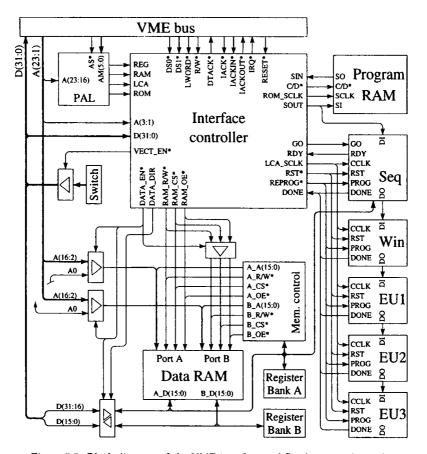

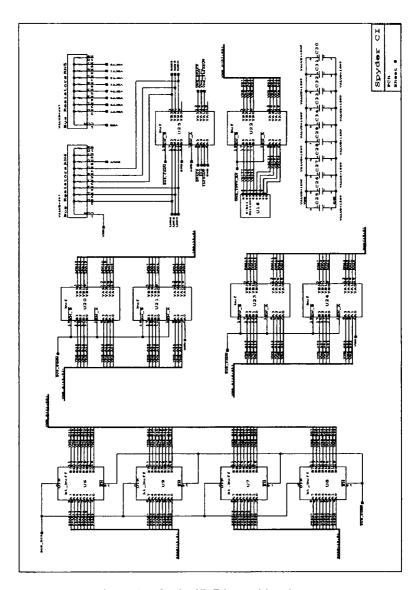

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39         |

| 0.20 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

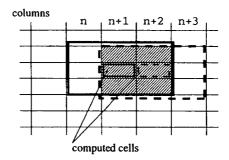

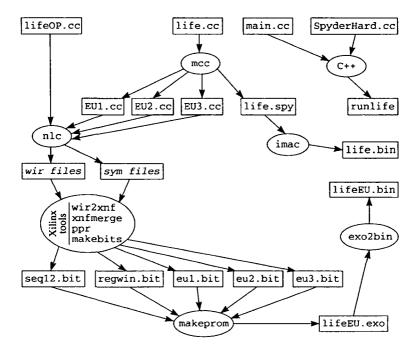

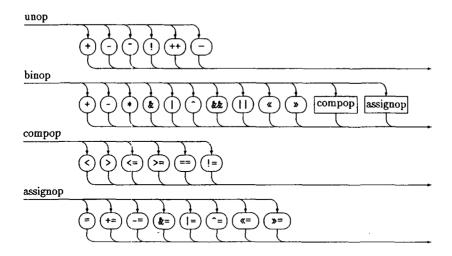

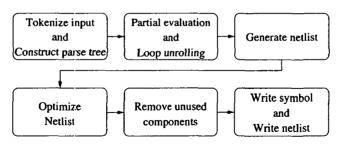

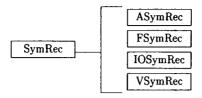

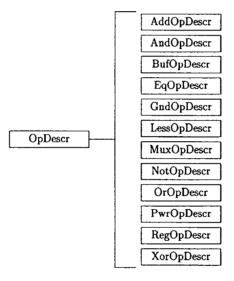

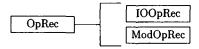

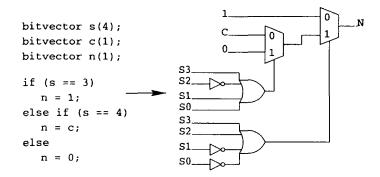

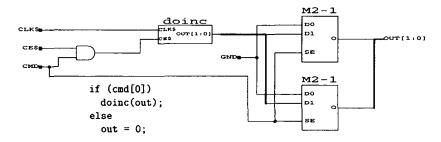

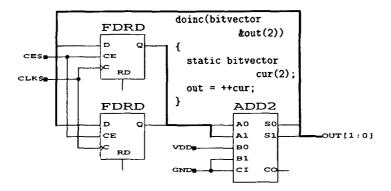

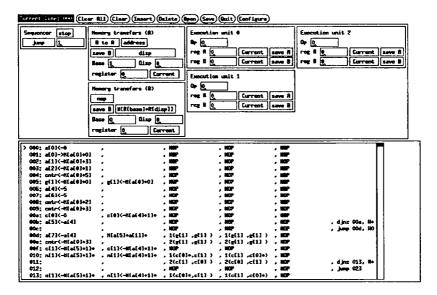

| 6.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42         |