Thèse n° 10 515

# EPFL

# Contemporary Logic Synthesis: with an Application to AQFP Circuit Optimization

Présentée le 4 juin 2024

Faculté informatique et communications Laboratoire des systèmes intégrés (IC/STI) Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Siang-Yun LEE

Acceptée sur proposition du jury

Prof. V. Kuncak, président du jury Prof. G. De Micheli, directeur de thèse Prof. W. Burleson, rapporteur Prof. U. Schlichtmann, rapporteur Prof. P. Ienne, rapporteur

École polytechnique fédérale de Lausanne

2024

The pursuit of knowledge and understanding is a lifelong journey. — Claude Shannon

## Acknowledgements

The PhD is a long learning road. At school, teachers may have been obligated to teach us knowledge because they get a salary explicitly for this. (Not saying we shouldn't be thankful to them, though!) But along the PhD journey, there have been so many people who helped us, directly or implicitly, without having an obligation to do so.

I would like to start by thanking my advisor, Prof. Giovanni (Nanni) De Micheli, who gave me great freedom and support, allowing me to freely try whatever I found interesting without having to worry about resources. I would also like to thank my jury committee, who spent the time and effort to read my thesis, traveled to attend my defense, and gave valuable feedback. Moreover, I want to thank Dr. Heinz Riener and Dr. Alan Mishchenko, who are not officially my advisors but have taught me a lot through our continuous collaboration.

A famous Taiwanese author wrote, *"For everything in life, we've got so much from others but used so little effort of ourselves; there are too many people to thank, so I would rather simply be grateful to God (to the world)."* (陳之藩〈謝天〉) Indeed, it would be too long to exhaustively list everyone I should thank, and even such a list may still be incomplete. Hence, I would refrain from enumerating more names to thank, such that no one would be disappointed. Nevertheless, please accept my sincere appreciation to every one of you whom I have met during these 4.5 years, both in academic and personal life. I truly believe that each one of the tiny interactions integrates into who I am today. Thank you.

Last but not least, I would like to thank myself. The journey to a PhD degree was not always easy and joyful; there were times of stress and disappointment. Nevertheless, I never really gave up trusting myself, which has been hard for someone with imposter syndrome. I have learned to accept imperfection, to encourage myself, and to acknowledge what I have accomplished. Thus, I want to thank myself for having grown into a better person through the PhD journey.

Munich, 18 April 2024

Siang-Yun (Sonia) Lee

### Abstract

Electronic devices play an irreplaceable role in our lives. With the tightening time to market, exploding demand for computing power, and continuous desire for smaller, faster, less energy-consuming, and lower-cost chips, computer-aided design for electronics, or *electronic design automation* (EDA), becomes not only inevitable but also critical in the semiconductor industry. Being responsible for the transformation and optimization of switching circuits at the level of logic gates, logic synthesis plays a central role in modern EDA flows and is key to bringing up the *quality of results* (QoR). For several decades, logic synthesis techniques have been developed based on the properties and needs of *complementary metal-oxide-semiconductor* (CMOS) digital circuits and according to the available computing power. Recently, new challenges as well as opportunities have appeared and influenced the research directions of logic synthesis.

The development of logic synthesis and the advancement of *very-large-scale integration* (VLSI) designs are both enablers and challengers of each other. The up-scaling of computing systems stresses logic synthesis algorithms for their scalability, efficiency, and QoR. Conversely, better computing systems make computationally intensive strategies in logic synthesis affordable. A major part of contemporary logic synthesis research lies in its synergy with the exponential scaling of VLSI systems. Moreover, emerging alternatives to CMOS-based technologies pose new problems to be solved in EDA and logic synthesis. As an example, *adiabatic quantum-flux parametron* (AQFP) is a promising superconducting electronic technology featuring ultra-low switching energy dissipation. However, it has unconventional path-balancing and fanout-branching constraints to be considered in EDA.

This thesis presents a collection of novel approaches, demonstrating various aspects of contemporary logic synthesis. In the first part, we focus on technology-independent logic optimization with an emphasis on scalability while pushing the limits on QoR. In the second part, we show how new problems in EDA for emerging technologies like AQFP are approached, as well as how techniques presented in the first part are applied in AQFP circuit optimization.

The main technical proposals of this thesis are as follows. First, the proposal of a simulationguided logic synthesis paradigm (a) sets the tone of the thesis, emphasizing additional QoR improvements with manageable runtime overhead. Then, the presentation of a family of heuristic resynthesis algorithms (b) complements the high-effort peephole optimization framework. At a higher level, we demonstrate that a simple design space exploration strategy (c), which discovers good optimization sequences on the fly, outperforms human-designed flows. To fulfill the special constraints imposed by the AQFP technology, we study possible constraint relaxations and their tradeoffs (d) and propose an AQFP technology legalization flow (e). Finally, by combining the proposed high-effort optimization (a, b) and other existing optimization algorithms with AQFP legalization (e) in the design space exploration framework (c), we achieve a significant 44% improvement over the state-of-the-art in the problem of AQFP circuit optimization.

To sum up, this thesis presents the essence of contemporary logic synthesis with an application in AQFP circuit optimization as an example. Indeed, in present days, the major challenge in logic synthesis lies in finding a "good-enough" local optimal in the huge design space while maintaining reasonable efficiency, as well as inventing or re-designing novel methods to tackle unconventional constraints imposed by emerging technologies.

**Keywords:** Electronic design automation, logic synthesis, superconducting electronics, adiabatic quantum-flux parametron

## Zusammenfassung

Elektronische Geräte spielen eine unersetzliche Rolle in unserem Leben. Angesichts der immer kürzer werdenden Markteinführungszeiten, der explodierenden Nachfrage nach Rechenleistung und des ständigen Wunsches nach kleineren, schnelleren, weniger Energie verbrauchenden und kostengünstigeren Chips ist computergestütztes Design für Elektronik oder Elektronische Entwurfsautomatisierung (electronic design automation, EDA) in der Halbleiterindustrie nicht nur unvermeidlich, sondern auch entscheidend. Da die Logiksynthese für die Umwandlung und Optimierung von Schaltkreisen auf der Ebene von Logikgattern verantwortlich ist, spielt sie eine zentrale Rolle in modernen EDA-Abläufen und ist der Schlüssel zur Verbesserung der Qualität der Ergebnisse. Seit mehreren Jahrzehnten werden Logiksynthesetechniken auf der Grundlage der Eigenschaften und Anforderungen komplementärer Metall-Oxid-Halbleiter (complementary metal-oxide-semiconductor, CMOS)-Digitalschaltungen und entsprechend der verfügbaren Rechenleistung entwickelt. In letzter Zeit sind neue Herausforderungen und Möglichkeiten entstanden, die die Forschungsrichtungen der Logiksynthese beeinflussen.

Die Entwicklung der Logiksynthese und die Weiterentwicklung von VLSI-Designs (very large scale integration) sind sowohl förderlich als auch herausfordernd für beide Seiten. Die Aufwärtsskalierung von Rechensystemen stellt die Algorithmen der Logiksynthese in den Mittelpunkt ihrer Skalierbarkeit, Effizienz und QoR. Umgekehrt machen bessere Rechnersysteme rechenintensive Strategien in der Logiksynthese erschwinglich. Ein großer Teil der aktuellen Logiksyntheseforschung liegt in der Synergie mit der exponentiellen Skalierung von VLSI-Systemen.

Darüber hinaus werfen aufkommende Alternativen zu CMOS-basierten Technologien neue Probleme auf, die in EDA und Logiksynthese gelöst werden müssen. Ein Beispiel dafür ist das adiabatische Quantenfluss-Parametron (adiabatic quantum-flux parametron, AQFP), eine vielversprechende supraleitende elektronische Technologie, die sich durch einen äußerst geringen Energieverlust beim Schalten auszeichnet. Sie hat jedoch unkonventionelle Pfadausgleichsund Fanout-Verzweigungsbeschränkungen, die in der EDA berücksichtigt werden müssen.

Diese These präsentiert eine Sammlung neuartiger Ansätze, die verschiedene Aspekte der modernen Logiksynthese aufzeigen. Im ersten Teil konzentrieren wir uns auf die technologieunabhängige Logikoptimierung mit dem Schwerpunkt auf Skalierbarkeit, während wir die Grenzen der QoR verschieben. Im zweiten Teil zeigen wir, wie neue Probleme in der EDA für aufkommende Technologien wie AQFP angegangen werden und wie die im ersten Teil vorgestellten Techniken in der AQFP-Schaltungsoptimierung angewendet werden. Die wichtigsten technischen Vorschläge dieser Arbeit sind wie folgt. Zunächst gibt der Vorschlag eines simulationsgeführten Logiksynthese-Paradigmas (a) den Ton der Arbeit an und betont zusätzliche QoR-Verbesserungen mit überschaubarem Laufzeit-Overhead. Dann wird eine Familie von heuristischen Resynthese-Algorithmen (b) vorgestellt, die das aufwändige Peephole-Optimierungsverfahren ergänzen. Auf einer höheren Ebene zeigen wir, dass eine einfache Strategie zur Erkundung des Entwurfsraums (c), die gute Optimierungssequenzen im laufenden Betrieb entdeckt, die von Menschen entworfenen Abläufe übertrifft. Um die speziellen Einschränkungen, die durch die AQFP-Technologie auferlegt werden, zu erfüllen, untersuchen wir mögliche Lockerungen von Einschränkungen und deren Kompromisse (d) und schlagen einen Legalisierungsfluss für die AQFP-Technologie vor (e). Durch die Kombination der vorgeschlagenen High-Effort-Optimierung (a, b) und anderer bestehender Optimierungsalgorithmen mit der AQFP-Legalisierung (e) im Rahmen der Entwurfsraumerforschung (c) erreichen wir schließlich eine signifikante Verbesserung von 44% gegenüber dem Stand der Technik bei der Optimierung von AQFP-Schaltungen.

Zusammenfassend wird in dieser Arbeit das Wesen der modernen Logiksynthese am Beispiel der AQFP-Schaltungsoptimierung dargestellt. Heutzutage besteht die größte Herausforderung in der Logiksynthese darin, in dem riesigen Entwurfsraum ein lokales Optimum zu finden, das "gut genug" ist und gleichzeitig eine angemessene Effizienz aufweist, sowie neue Methoden zu erfinden oder neu zu entwerfen, um unkonventionelle Einschränkungen durch neue Technologien zu bewältigen.

**Stichwörter:** Elektronische Entwurfsautomatisierung (EDA), Logiksynthese, supraleitende Elektronik, adiabatisches Quantenflussparametron (AQFP)

## Contents

| A  | cknov   | wledge  | ments                                                                 | i    |

|----|---------|---------|-----------------------------------------------------------------------|------|

| Al | bstra   | ct (Eng | lish/Deutsch)                                                         | iii  |

| Li | st of ] | Figure  | S                                                                     | xiii |

| Li | st of ' | Tables  |                                                                       | xv   |

| Li | stof    | Algorit | hms                                                                   | xvii |

| Li | st of . | Acrony  | 7ms                                                                   | xix  |

| 1  | Intr    | oducti  | on                                                                    | 1    |

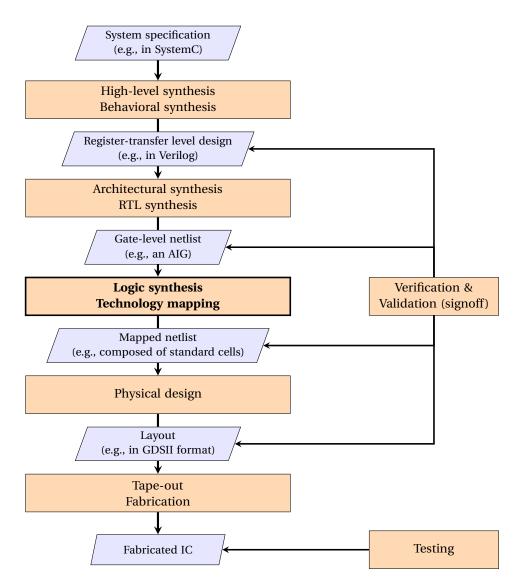

|    | 1.1     | Electr  | onic Design Automation                                                | 2    |

|    | 1.2     | Logic   | Synthesis                                                             | 4    |

|    | 1.3     | Trend   | s in Logic Synthesis Techniques                                       | 5    |

|    | 1.4     | Challe  | enges and Opportunities of Contemporary Logic Synthesis               | 6    |

|    | 1.5     | Thesis  | s Organization                                                        | 6    |

|    |         | 1.5.1   | Chapter 3: Simulation-Guided Paradigm                                 | 7    |

|    |         | 1.5.2   | Chapter 4: Heuristic Resynthesis                                      | 8    |

|    |         | 1.5.3   | Chapter 5: Design Space Exploration                                   | 8    |

|    |         | 1.5.4   | Chapter 6: Testing and Debugging Logic Synthesis Algorithms           | 8    |

|    |         | 1.5.5   | Chapter 8: Impact of Sequential Design on AQFP Technology Constraints | 9    |

|    |         | 1.5.6   | Chapter 9: AQFP Technology Legalization by Buffer/Splitter Insertion  | 9    |

|    |         | 1.5.7   | Chapter 10: AQFP Logic Synthesis Toolbox                              | 10   |

| 2  | Bac     | kgrour  | nd                                                                    | 13   |

|    | 2.1     | Mathe   | ematical Abstractions and Data Structures for Logic Circuits          | 13   |

|    |         | 2.1.1   | Boolean Logic                                                         | 13   |

|    |         | 2.1.2   | Truth Tables                                                          | 14   |

|    |         | 2.1.3   | Logic Networks                                                        | 14   |

|    | 2.2     | Comp    | outational Tools                                                      | 17   |

|    |         | 2.2.1   | Boolean Satisfiability Problem                                        | 17   |

|    |         | 2.2.2   | Integer Linear Programming                                            | 18   |

|    |         | 2.2.3   | Satisfiability Modulo Theory                                          | 18   |

|    |         |         |                                                                       |      |

|   | 2.3 | Components of Logic Synthesis                                | 18 |

|---|-----|--------------------------------------------------------------|----|

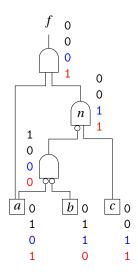

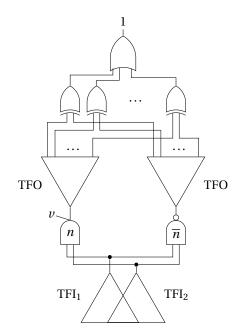

|   |     | 2.3.1 Structural Analysis                                    | 18 |

|   |     | 2.3.2 Don't-Care Conditions                                  | 20 |

|   |     | 2.3.3 Exact Synthesis and Databases                          | 22 |

|   | 2.4 | Modern Logic Synthesis Algorithms                            | 22 |

|   |     | 2.4.1 Algebraic and Boolean Methods                          | 22 |

|   |     | 2.4.2 Cut Rewriting                                          | 23 |

|   |     | 2.4.3 Boolean Resubstitution                                 | 23 |

|   |     | 2.4.4 Technology Mapping                                     | 24 |

|   |     | 2.4.5 Combinational Equivalence Checking                     | 24 |

|   | 2.5 | List of Symbols and Common Variables                         | 25 |

|   | 2.6 | Summary                                                      | 26 |

| I | Cor | ntemporary Logic Synthesis                                   | 27 |

| 3 | Sim | ulation-Guided Paradigm                                      | 29 |

|   | 3.1 | Motivation                                                   | 29 |

|   | 3.2 | Overview                                                     | 30 |

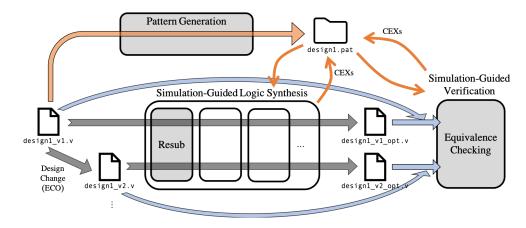

|   | 3.3 | The Simulation-Guided Paradigm                               | 31 |

|   | 3.4 | Simulation Pattern Generation                                | 33 |

|   |     | 3.4.1 Stuck-at Values                                        | 33 |

|   |     | 3.4.2 Observability                                          | 34 |

|   |     | 3.4.3 Bit-Packing                                            | 37 |

|   |     | 3.4.4 Discussion                                             | 38 |

|   | 3.5 | Simulation-Guided Resubstitution                             | 38 |

|   | 3.6 | Simulation-Guided Equivalence Checking                       | 40 |

|   | 3.7 | Experimental Results                                         | 41 |

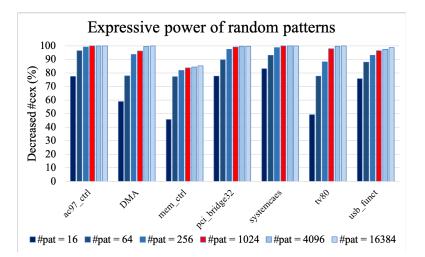

|   |     | 3.7.1 Size of Simulation Pattern Set                         | 41 |

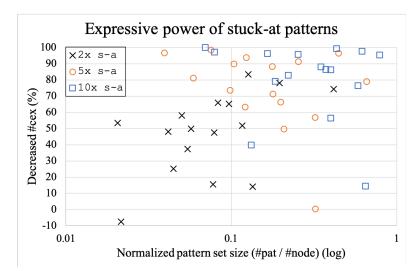

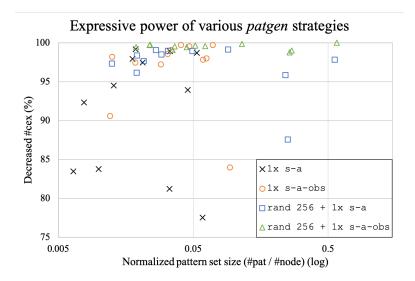

|   |     | 3.7.2 Pattern Generation Strategies                          | 42 |

|   |     | 3.7.3 Pattern Compression with Bit-packing                   | 44 |

|   |     | 3.7.4 Effect of Expressive Patterns in Resubstitution        | 44 |

|   |     | 3.7.5 Reusability of Simulation Patterns                     | 45 |

|   |     | 3.7.6 Quality of Simulation-Guided Resubstitution            | 46 |

|   |     | 3.7.7 Reduction on SAT Calls in CEC with Expressive Patterns | 51 |

|   | 3.8 | Summary                                                      | 52 |

|   | 3.9 | Future Work                                                  | 52 |

| 4 | Heu | ıristic Resynthesis                                          | 55 |

|   | 4.1 | Motivation                                                   | 55 |

|   | 4.2 | Problem Formulation                                          | 56 |

|   |     | 4.2.1 Logic Resynthesis                                      | 56 |

|   |     | 4.2.2 Peephole Optimization Targeting Size Reduction         | 57 |

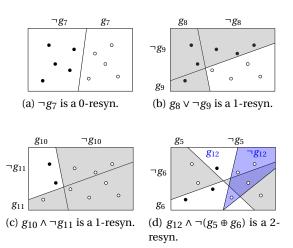

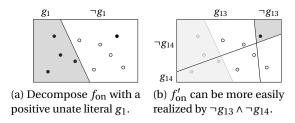

|   |      | 4.2.3 Don't-Care-Based Optimization 58                    |

|---|------|-----------------------------------------------------------|

|   |      | 4.2.4 Simulation-Guided Logic Synthesis                   |

|   | 4.3  | Overview                                                  |

|   | 4.4  | Related Works    60                                       |

|   |      | 4.4.1 Functional Dependency by Interpolation              |

|   |      | 4.4.2 SAT-Based Exact Synthesis                           |

|   |      | 4.4.3 Enumeration-Based Resubstitution                    |

|   |      | 4.4.4 Akers' Majority Synthesis 63                        |

|   | 4.5  | Heuristic AND-Based Resynthesis                           |

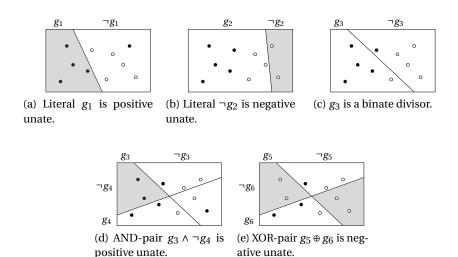

|   |      | 4.5.1 Classification of Divisors                          |

|   |      | 4.5.2 Simple Dependency Circuits                          |

|   |      | 4.5.3 Recursive Decomposition                             |

|   |      | 4.5.4 Summary of AND-Based Resynthesis                    |

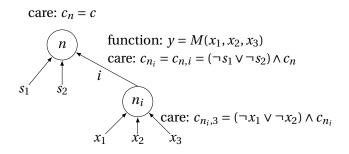

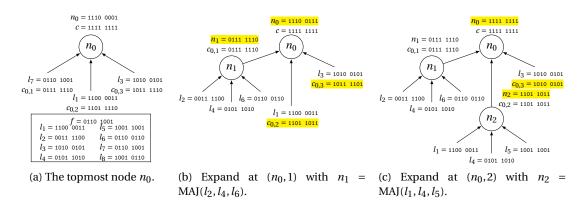

|   | 4.6  | Heuristic MAJ-Based Resynthesis                           |

|   |      | 4.6.1 Normalization                                       |

|   |      | 4.6.2 The Care Function                                   |

|   |      | 4.6.3 Choosing Divisors                                   |

|   |      | 4.6.4 Expansion                                           |

|   |      | 4.6.5 Summary and Example of MAJ-Based Resynthesis        |

|   | 4.7  | Heuristic MUX-Based Resynthesis                           |

|   | 4.8  | Experimental Results                                      |

|   |      | 4.8.1 Extracted Resynthesis Problems                      |

|   |      | 4.8.2 Resynthesis as the Core of High-Effort Optimization |

|   | 4.9  | Summary                                                   |

| 5 | Des  | ign Space Exploration 83                                  |

|   | 5.1  | Motivation                                                |

|   | 5.2  | Related Works    84                                       |

|   | 5.3  | Overview                                                  |

|   | 5.4  | Escaping Local Optimum 85                                 |

|   | 5.5  | Stretching Out in the Design Space                        |

|   | 5.6  | On-the-fly Exploration                                    |

|   | 5.7  | Customization                                             |

|   | 5.8  | Experimental Results                                      |

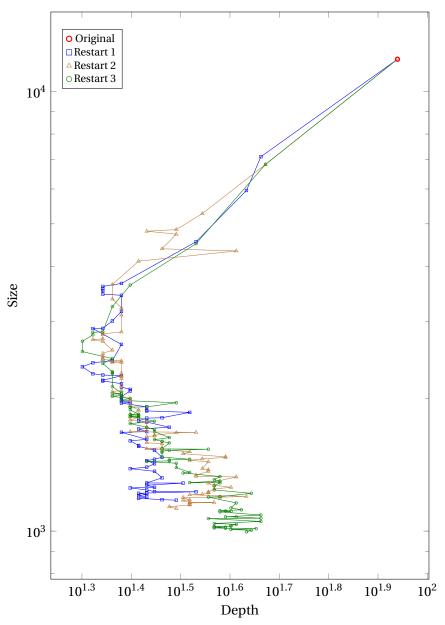

|   |      | 5.8.1 Application to MIG Optimization                     |

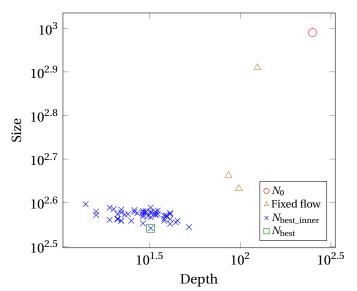

|   |      | 5.8.2 Design Space Exploration                            |

|   |      | 5.8.3 Importance of Random Restarts                       |

|   | 5.9  | Summary                                                   |

| 6 | Test | ing and Debugging Logic Synthesis Algorithms 93           |

|   | 6.1  | Motivation                                                |

|   | 6.2  | Scope                                                     |

|   | 6.3  | Related Works   94                                        |

|   | 0.0  |                                                           |

|    |                                                                                     | 6.3.1 Fuzz Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                                                                 |

|----|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|    |                                                                                     | 6.3.2 Delta Debugging and Testcase Minimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                 |

|    | 6.4                                                                                 | Cesting and Debugging Toolkit for Logic Synthesis Applications    95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                 |

|    |                                                                                     | 6.4.1    Testcase Generation    95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                 |

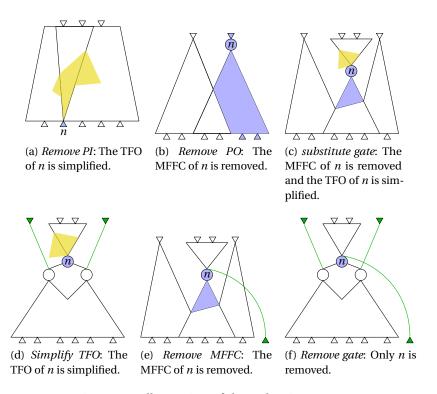

|    |                                                                                     | 6.4.2    Testcase Minimization    97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                                 |

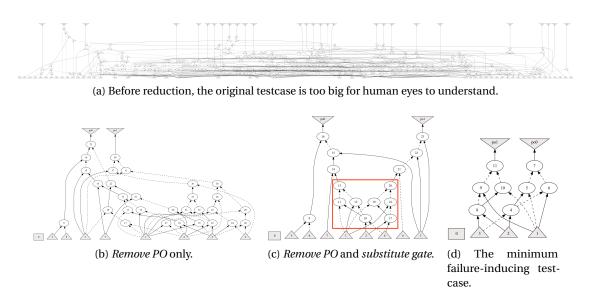

|    |                                                                                     | 6.4.3 Usage Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                 |

|    | 6.5                                                                                 | Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                 |

|    |                                                                                     | 6.5.1 Capturing The Defect with Fuzz Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                 |

|    |                                                                                     | 6.5.2 Effects of The Reduction Stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                                                                                 |

|    | 6.6                                                                                 | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                 |

|    |                                                                                     | 5.6.1 Fuzzing Open-Source Logic Synthesis Tools    103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                                                 |

|    |                                                                                     | 5.6.2 Testcase Minimization    109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                 |

|    | 6.7                                                                                 | Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                 |

|    |                                                                                     | 6.7.1 Non-deterministic Defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                 |

|    |                                                                                     | 6.7.2 Other Applications of The Toolkit 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                 |

|    | 6.8                                                                                 | Future Directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                 |

|    | 6.9                                                                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                 |

|    |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |

| II | AQ                                                                                  | P Circuit Optimization 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                                                                 |

| 7  | Adia                                                                                | patic Quantum-Flux Parametron 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                                 |

|    | 7.1                                                                                 | Supervised duration The structure 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                 |

|    | 1.1                                                                                 | Superconducting Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                 |

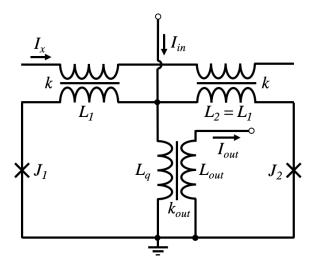

|    | 7.2                                                                                 | Basic Principles of Adiabatic Quantum-Flux Parametron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

|    |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                 |

|    |                                                                                     | Basic Principles of Adiabatic Quantum-Flux Parametron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0                                                                            |

|    |                                                                                     | Basic Principles of Adiabatic Quantum-Flux Parametron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0<br>1                                                                       |

|    |                                                                                     | Basic Principles of Adiabatic Quantum-Flux Parametron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0<br>1<br>1                                                                  |

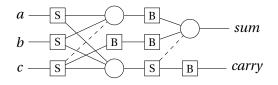

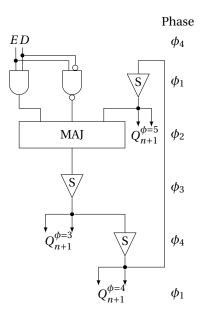

|    |                                                                                     | Basic Principles of Adiabatic Quantum-Flux Parametron1107.2.1 Parametron and Quantum-Flux Parametron1107.2.2 Adiabatic Operation1117.2.3 Logic Computation111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0<br>0<br>1<br>1<br>2                                                             |

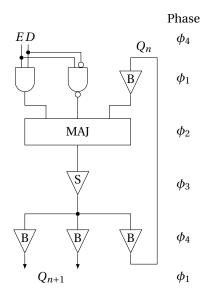

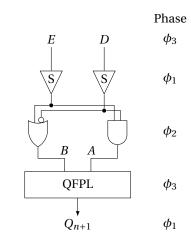

|    | 7.2                                                                                 | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0<br>0<br>1<br>2<br>3                                                             |

|    | 7.2<br>7.3<br>7.4                                                                   | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         AQFP Design Constraints       113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0<br>0<br>1<br>2<br>3<br>3                                                        |

| 8  | <ul><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                           | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         7.2.4 Memory Devices and Architectural Clocking       113         7.2.5 Adiabatic Operation       114         7.2.6 Computation       115         7.2.7 Adiabatic Operation       115         7.2.8 Logic Computation       115         7.2.9 Adiabatic Operation       115         7.2.4 Gate-level Clocking Schemes       116         7.2.4 Gate-level Clocking Schemes       117         7.2.4 Adjustric Clocking Schemes       117         7.2.4 Adjustric Clocking Schemes       117         7.2.5 Adjustric Clocking Schemes       116         7.2.6 Adjustric Clocking Schemes       117         7.2.7 Adjustric Clocking Schemes       117         7.2.8 Adjustric Clocking Schemes       117         7.9 Adjustric Clocking Schemes       118         7.9 Adjustric Clocking Schemes       118         7.9 Adjustric Clocking Schemes       118         7.9 Adjustric Clocking Schemes       118 <th>0<br/>0<br/>1<br/>2<br/>3<br/>3<br/>5</th> | 0<br>0<br>1<br>2<br>3<br>3<br>5                                                   |

| 8  | 7.2<br>7.3<br>7.4<br>7.5<br>Imp                                                     | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       115         ct of Sequential Design on AQFP Technology Constraints       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0<br>0<br>1<br>2<br>3<br>3<br>5<br>7                                              |

| 8  | <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>Imp<br/>8.1</li> </ul> | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         7.2.4 Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         Abstraction and Terminology       115         Act of Sequential Design on AQFP Technology Constraints       117         Motivation       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0<br>0<br>1<br>2<br>3<br>5<br>7<br>7                                              |

| 8  | <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>Imp<br/>8.1</li> </ul> | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         7.2.4 Memory Devices and Architectural Clocking       113         Abstraction and Terminology       113         Act of Sequential Design on AQFP Technology Constraints       117         Motivation       117         AQFP Design Constraints       117         118       117         119       117         110       117         111       118         112       117         113       118         114       117         115       117         116       117         117       117         118       117         119       117         111       117         111       117         112       118         113       117         114       118                                                                                                                                                                                                                                                                                                           | 0<br>0<br>1<br>2<br>3<br>5<br>7<br>7<br>8                                         |

| 8  | <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>Imp<br/>8.1</li> </ul> | Basic Principles of Adiabatic Quantum-Flux Parametron       110         Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       112         7.2.3 Logic Computation       112         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       112         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         AVER Design Constraints       115         ACT of Sequential Design on AQFP Technology Constraints       117         AQFP Design Constraints       118         AQFP Desig                                                                       | 0<br>0<br>1<br>2<br>3<br>5<br>7<br>7<br>8<br>9                                    |

| 8  | <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>Imp<br/>8.1</li> </ul> | Basic Principles of Adiabatic Quantum-Flux Parametron       110         Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         Act of Sequential Design on AQFP Technology Constraints       117         Motivation       117         AQFP Design Constraints       117         All Schemes       117         All Schemes <t< th=""><th>0<br/>1<br/>1<br/>2<br/>3<br/>5<br/>7<br/>7<br/>8<br/>9<br/>1</th></t<>                                                                     | 0<br>1<br>1<br>2<br>3<br>5<br>7<br>7<br>8<br>9<br>1                               |

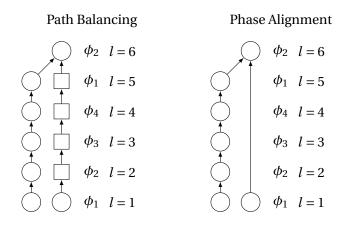

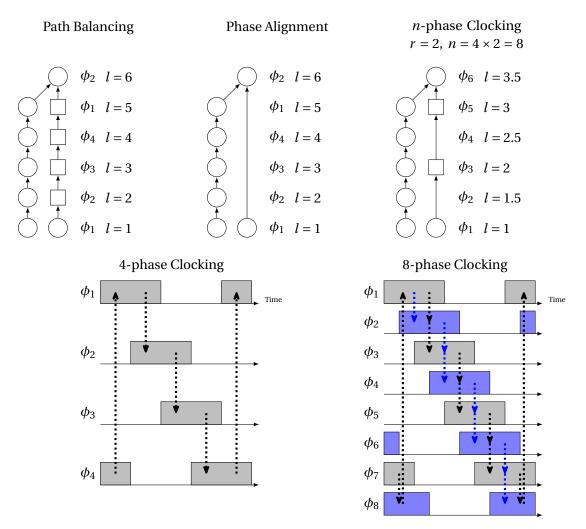

| 8  | <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>Imp<br/>8.1</li> </ul> | Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         7.2.4 Memory Devices and Architectural Clocking       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         AQFP Design Constraints       115         Abstraction and Terminology       115         AGFP Design Constraints       116         Abstraction and Terminology       117         AQFP Design Constraints       117         Ager Design Constraints       117         Ager Design Constraints       117         Ager Design Constraints       117         Ager Design Constraints       116         B.2.1 Phase Alignment Instead of Path Balancing       116         B.2.2 PI Capacity and Phases       122         B.2.3 Consideration of Clock Skews       122                                                                                                                                                                                                              | 0<br>0<br>1<br>2<br>3<br>3<br>5<br>7<br>7<br>8<br>9<br>1<br>2                     |

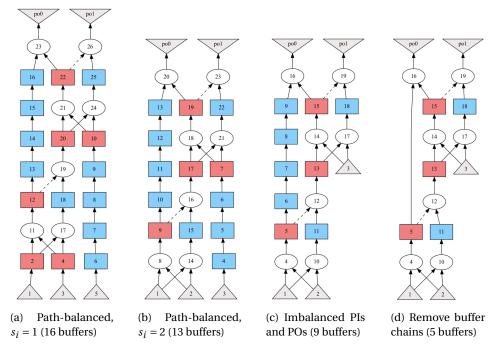

| 8  | 7.2<br>7.3<br>7.4<br>7.5<br><b>Imp</b><br>8.1<br>8.2                                | Basic Principles of Adiabatic Quantum-Flux Parametron       110         Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         AQFP Design Constraints       115         Addiation       115         Act of Sequential Design on AQFP Technology Constraints       117         AQFP Design Constraints       116         AQFP Design Constraints       117         AQFP Design Constraints       117         AQFP Design Constraints       117         AQFP Design Constraints       116         3.2.1 Phase Alignment Instead of Path Balancing       116         3.2.2 PI Capacity and Phases       122         3.2.3 Consideration of Clock Skews       122         3.2.3 Consideration of Clock Skews       122         Amount of Technology Constraints on JJ Count       123         Amount of Technology Constrai                                    | 0<br>0<br>1<br>2<br>3<br>3<br>5<br>7<br>7<br>8<br>9<br>1<br>2<br>3                |

| 8  | 7.2<br>7.3<br>7.4<br>7.5<br><b>Imp</b><br>8.1<br>8.2                                | Basic Principles of Adiabatic Quantum-Flux Parametron       110         Basic Principles of Adiabatic Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         AQFP Design Constraints       115         Addiation       115         Act of Sequential Design on AQFP Technology Constraints       117         AQFP Design Constraints       116         AQFP Design Constraints       116         AQFP Design Constraints       117         AQFP Design Constraints       116         3.2.1 Phase Alignment Instead of Path Balancing       116         3.2.2 PI Capacity and Phases       122         3.2.3 Consideration of Clock Skews       122         3.2.3 Consideration of Clock Skews       122         Amount of Technology Constraints on JJ Count       123                                                                                                                    | 0<br>0<br>1<br>2<br>3<br>5<br>7<br>7<br>8<br>9<br>1<br>2<br>3<br>3                |

| 8  | 7.2<br>7.3<br>7.4<br>7.5<br><b>Imp</b><br>8.1<br>8.2                                | Basic Principles of Adiabatic Quantum-Flux Parametron       110         Parametron and Quantum-Flux Parametron       110         7.2.1 Parametron and Quantum-Flux Parametron       110         7.2.2 Adiabatic Operation       111         7.2.3 Logic Computation       111         7.2.4 Gate-level Clocking Schemes       112         7.2.4 Gate-level Clocking Schemes       113         AQFP Design Constraints       113         Memory Devices and Architectural Clocking       113         Abstraction and Terminology       114         AQFP Design Constraints       115         Motivation       115         AQFP Design Constraints       116         AQFP Design Constraints       117         AQFP Design Constraints       117         AQFP Design Constraints       117         AQFP Design Constraints       117         AQFP Design Constraints       116         3.2.1 Phase Alignment Instead of Path Balancing       117         3.2.2 PI Capacity and Phases       122         3.2.3 Consideration of Clock Skews       122         3.3.1 Buffer/Splitter Insertion Considering Relaxed Constraints       123                                                                                                                                                          | 0<br>0<br>1<br>2<br>3<br>5<br>7<br>7<br>8<br>9<br>1<br>2<br>3<br>3<br>4           |