#### **OPEN ACCESS**

# Characteristics and ultra-high total ionizing dose response of 22 nm fully depleted silicon-on-insulator

To cite this article: Gennaro Termo et al 2024 JINST 19 C03039

View the article online for updates and enhancements.

# You may also like

- Influences of total ionizing dose on single event effect sensitivity in floating gate cells Ya-Nan Yin, , Jie Liu et al.

- Evaluation of total-ionizing-dose effects on reconfigurable field effect transistors and SRAM circuits

- Jingyan Shao, Xianglong Li, Ziyu Liu et al.

- Bias and geometry dependence of totalionizing-dose effects in SOI FinFETs Zhexuan Ren, Xia An, Gensong Li et al.

RECEIVED: November 3, 2023 ACCEPTED: February 3, 2024 Published: March 19, 2024

Topical Workshop on Electronics for Particle Physics Geremeas, Sardinia, Italy 1–6 October 2023

# Characteristics and ultra-high total ionizing dose response of 22 nm fully depleted silicon-on-insulator

Gennaro Termo  $\mathbf{o},^{a,b,*}$  Giulio Borghello, $^a$  Federico Faccio, $^a$  Kostas Kloukinas, $^a$  Michele Caselle, $^c$  Alexander Friedrich Elsenhans, $^c$  Ahmet Cagri Ulusoy, $^c$  Adil Koukab $^b$  and Jean-Michel Sallese $^b$

aCERN.

Geneva, Switzerland

<sup>b</sup>École Polytechnique Fédérale de Lausanne,

Lausanne, Switzerland

<sup>c</sup>Karlsruhe Institute of Technology,

Karlsruhe, Germany

E-mail: gennaro.termo@cern.ch

ABSTRACT. The radiation response of MOS transistors in a 22 nm Fully Depleted Silicon-On-Insulator (FDSOI) technology exposed to ultra-high total ionizing dose (TID) was investigated. Custom structures including n- and p-channel devices with different sizes and threshold voltage flavours were irradiated with X-rays up to a TID of  $100\,\mathrm{Mrad}(\mathrm{SiO}_2)$  with different back-gate bias configurations, from  $-8\,\mathrm{V}$  to  $2\,\mathrm{V}$ . The investigation revealed that the performance is significantly affected by TID, with the radiation response being dominated by the charge trapped in the buried oxide.

Keywords: Inspection with x-rays; Radiation damage to electronic components; Radiation-hard electronics

<sup>\*</sup>Corresponding author.

| Co | ontents                         |   |

|----|---------------------------------|---|

| 1  | Introduction                    | 1 |

| 2  | Test structures                 | 1 |

| 3  | Results                         | 2 |

|    | 3.1 TID response                | 2 |

|    | 3.2 Compensation of TID effects | 4 |

| 4  | Conclusions                     | 5 |

#### 1 Introduction

Single Event Effects (SEEs) are a major cause of failure for Application-Specific Integrated Circuits (ASICs) operating in harsh radiation environments, such as space or particle accelerators [1]. A particle with high Linear Energy Transfer (LET), like an energetic ion, generates an ionization tail of electron-hole pairs as it passes through the substrate of a semiconductor device. In a bulk technology, this charge can be collected relatively deep in the substrate and is responsible for current pulses at active nodes of the circuit, giving origin to SEU (upsets), SET (transient) or SEL (latchup) [2–4].

In Silicon-On-Insulator (SOI) technologies, the thin silicon channel layer overlays a thick Buried OXide (BOX) that isolates the channel from the bulk substrate. The presence of the BOX limits the extension of the charge collection region and makes these technologies intrinsically more tolerant to SEE [5, 6]. Furthermore, the electrical coupling between the front and back channel interfaces in a Fully Depleted SOI (FDSOI) transistor enables the tuning of its electrical characteristics via back-gate biasing [7]. However, the BOX is typically tens of nanometers thick and therefore trapping significant amounts of charge when exposed to ionizing dose [8]. Total Ionizing Dose (TID) susceptibility of FDSOI devices results mainly from the coupling between the back gate and the front gate, meaning that charges trapped in the BOX modify the electrical characteristics of the transistor [9-13]. Thus, although SOI technologies are appealing in reducing SEE, they may exhibit a greater sensitivity to TID compared to bulk technologies. In view of possible application in HEP, where doses can be orders of magnitude higher than those typically reached in space applications [14], it is interesting to study the TID response of commercial SOI technologies and if/how it can be improved by dedicated biasing techniques. In this work, the characteristics of n- and p-channel transistors with different sizes and threshold voltage in a 22 nm FDSOI technology were evaluated before irradiation and after exposure to X-rays up to a TID of 100 Mrad(SiO<sub>2</sub>). High-temperature annealing and compensation of TID-induced effects using back-biasing were also studied.

#### 2 Test structures

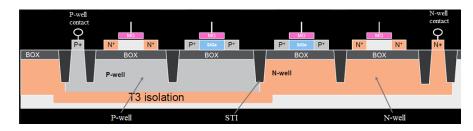

The irradiated samples were custom test structures containing several isolated n- and p-channel transistors as schematically depicted in figure 1. Note that both pMOS and nMOS can be built on top of a p- or n-well doped substrate region, and that p-wells have to be biased at voltages lower than n-wells. The chips were designed at Karlsruhe Institute of Technology (KIT) and fabricated in a commercial-grade 22 nm FDSOI technology. In the technology studied, the thin silicon film

**Figure 1.** Schematic of the irradiated transistors in 22 nm FDSOI. The p-well and n-well contact are used to tune the threshold voltage of the device.

that forms the channel is undoped and the devices are equipped with an external pad to provide back-gate biasing via p-well/n-well contacts in order to tune the threshold voltage ( $V_{th}$ ) of the device. Applying a negative bias to the p-well reduces the  $V_{th}$  of the pMOS (forward body biasing, FBB) and increases it for the nMOS (reverse body biasing, RBB). Similarly, applying a positive bias to the n-well increases the  $V_{th}$  of the pMOS and reduces it for the nMOS.

#### 3 Results

### 3.1 TID response

In this section the radiation response of 22 nm FDSOI technology is discussed referring only to the devices that are in the p-well, i.e., FBB pMOS and RBB NMOS (left structure in figure 1). The same phenomena were observed in the devices in the n-well.

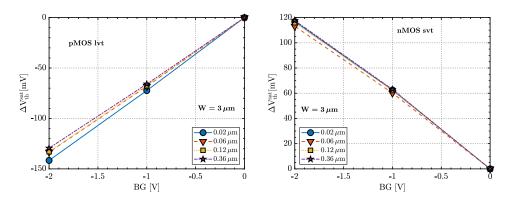

In a fully depleted SOI technology the silicon film of the SOI structure is thin enough that completely depletion can occur, thereby coupling the two gates, hereafter front-gate (FG) and back-gate (BG), and rendering the threshold voltage of each gate dependent on the conditions of the other [9]. Once the two gates are coupled, applying a bias to the BG influences the front channel threshold voltage  $V_{\rm th}$ . Low, high and standard threshold voltage transistors were investigated, hereafter denoted as lvt, hvt and svt respectively. Figure 2 shows the  $\Delta V_{\rm th}^{\rm sat}$  of the FG  $V_{\rm th}$  induced by changing the BG bias from 0 to -2 V in pMOS and nMOS transistors with  $W=3~\mu m$  and L ranging from 20 nm to 360 nm built on p-well. As the bias applied to the BG decreases,  $V_{\rm th}$  linearly decreases for p-type transistors whereas it linearly increases for n-type devices. In this  $V_{\rm BG}$  range, the threshold variation induced by the back-gate voltage is only slightly dependent on device size.

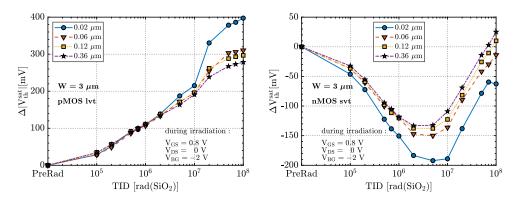

Figure 3 reports the  $\Delta V_{\rm th}^{\rm sat}$  measured at  $V_{\rm BG}=0$  V of p- and n-type transistors with W=3 µm and L ranging from 20 nm to 360 nm irradiated up to 100 Mrad(SiO<sub>2</sub>) with X-ray at T = 25 °C. During exposure, the devices were biased with  $V_{\rm FG}=\pm0.8$  V,  $V_{\rm S}=V_{\rm D}=0$  V,  $V_{\rm BG}=-2$  V. Both types of transistors are severely affected by TID; the relatively small dose of 1 Mrad(SiO<sub>2</sub>) is already sufficient to increase the  $|V_{\rm th}|$  by  $\sim 110$  mV for pMOS and a reduction of about the same amount for nMOS transistors, exception made for the shortest one which exhibit a decrease of about 150 mV. After 2 Mrad(SiO<sub>2</sub>), nMOS transistors show a rebound caused by the different build-up time of positive charge in the oxides and negative charge at the interface [15–18]. In pMOS devices, the charge in the oxide and at the interface has the same sign, causing the monotonic behavior of the radiation response. The radiation response of the  $V_{\rm th}$  is caused by the charge in the buried oxide which being coupled to the front-gate causes a change in the threshold voltage of the front channel [9–13]. The observed response depends on transistor length, with shorter devices exhibiting a greater variation. This is

Figure 2. Front-gate threshold voltage as a function of back-gate bias of pristine  $W = 3 \mu m$  and L ranging from 20 nm to 360 nm pMOS(left) and nMOS(right) built on p-well.

**Figure 3.**  $\Delta V_{\text{th}}^{\text{sat}}(\text{TID})$  of p- and n-type transistors with  $W = 3 \, \mu\text{m}$  and L ranging from 20 nm to 360 nm exposed to  $10 \, \text{Mrad}(\text{SiO}_2)$ .

especially evident in the minimum size device, but it is also visible in the other transistors. The reason for the dependence of this technology on channel length is not yet fully understood. Some authors have observed greater degradation in the short transistors of certain FDSOI technologies [13, 19], but these studies investigate devices with doped channels, thus different from the undoped FDSOI studied in this paper. The TID response of some bulk technologies is dependent on the L due to the presence of the spacer oxides [15, 20] or the presence of the halo implants in the channel [21]. However, because the channel is undoped, in this technology there are no halo implants, low-doped drain, or spacer oxides used in creating the latter.

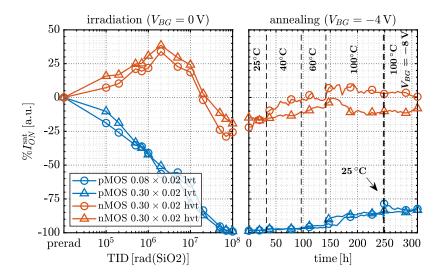

Figure 4 shows the percentage degradation of the on current of  $[80, 300] \times 20$  nm lvt pMOS and  $[80, 300] \times 20$  nm hvt nMOS transistors measured at room temperature with  $V_{BG} = 0$  V after irradiation to  $100 \,\mathrm{Mrad}(\mathrm{SiO}_2)$  and then annealed at different temperature up to  $T = 100\,^{\circ}\mathrm{C}$ . During irradiation, the devices were biased at  $V_{GS} = \pm 0.8$  V and  $V_{DS} = V_{BG} = 0$  V. The same bias was kept during annealing with exception of the back-gate where  $V_{BG}$  was set to = -4 V. In the last  $\sim 50$  h of annealing,  $V_{BG}$  was set to = -8 V to enhance the recovery of the devices. The performance of both types of transistors is severely degraded by TID, with pMOS devices most affected (figure 4, left). In pMOS, a total dose of  $1 \,\mathrm{Mrad}(\mathrm{SiO}_2)$  results in  $\sim 50\%$  degradation of the turn-on current. Unlike what observed in bulk technology [15], the radiation response is independent of the transistor width. The performance of the devices did not recover after several hours of annealing at  $T = 25, 40, 60, 100\,^{\circ}\mathrm{C}$ , indicating that the

**Figure 4.**  $\%I_{\rm ON}^{\rm sat}({\rm TID})$  of  $[80,300] \times 20\,{\rm nm}$  lvt pMOS and  $[80,300] \times 20\,{\rm nm}$  hvt nMOS irradiated to  $100\,{\rm Mrad}({\rm SiO}_2)$  and annealed at different temperatures  $T=25-100\,{\rm ^\circ C}$ . The last measurement after annealing was performed at room temperature.

irradiation produced deep-level defects whose removal process requires more energy than that provided during annealing at this temperature. Switching to  $V_{\rm BG} = -8 \, \rm V$  did not significantly enhance recovery.

## 3.2 Compensation of TID effects

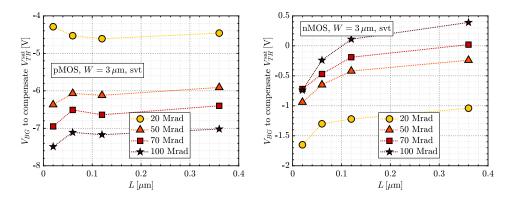

The most significant effect induced by TID in 22 nm FDSOI is the threshold voltage shift (figure 3). Since the back-bias provides designer with an additional degree of freedom for tuning the threshold voltage, it might be possible to compensate for TID induced threshold voltage shift by varying the back-gate bias accordingly. Figure 5 shows the BG voltage that should be applied in order to compensate for the  $V_{th}$  shift induced by different levels of TID as a function of the length of the transistor for both pMOS and nMOS devices. To obtain compensation voltage values, the  $I_D(V_G)$  characteristics of the devices were measured at varying back-gate voltages. The  $V_{BG}$  used ranged from -8 V to 0 V with a step size of 1 V. The compensation value was then obtained by finding the intersection point between the  $\Delta V_{th}(V_{BG})$  curve and 0 V.

**Figure 5.** Compensation of the threshold voltage shift caused by different levels of TID by applying a different back-gate bias in pMOS (left) and nMOS (right) with same width and different lengths.

Although it is possible to compensate the shift caused by a certain level of TID by applying a specific BG bias, the voltage to be applied depends on the size of the transistors. For each level of TID considered there is a difference of about 0.5 V in the bias to be applied between the shortest and the longest transistor for pMOS transistors and about 1 V for nMOS devices.

#### 4 Conclusions

The radiation response of 22 nm FDSOI transistors was evaluated by X-ray irradiation at ultra-high levels of TID. The study revealed that the coupling between the front and back gates allows the charge trapped in the buried oxide to severely shift the front gate threshold voltage, which is the main TID-induced effect observed in this technology. The observed degradation is not recovered when the devices are annealed at high temperature. The possibility to compensate TID-induced effects by varying the back-gate bias has been explored, showing that the  $V_{\rm BG}$  needed to compensate for the TID-induced  $V_{\rm th}$  shift depends on the channel length of the device. From a practical standpoint, this study underscores two noteworthy issues in implementing a compensation method in a real chip where hundreds of thousands of transistors with different sizes are involved. Firstly, it is necessary to actively monitor the degradation of the device to apply the appropriate bias. Secondly, the bias to be applied at each TID level is different for devices of different sizes, posing a significant challenge in the actual application of the compensation method.

#### References

- [1] R. García Alía et al., Single event effects in high-energy accelerators, Semicond. Sci. Tech. 32 (2017) 034003.

- [2] F.W. Sexton, Destructive single-event effects in semiconductor devices and ICs, IEEE Trans. Nucl. Sci. 50 (2003) 603.

- [3] A. Taber and E. Normand, Single event upset in avionics, IEEE Trans. Nucl. Sci. 40 (1993) 120.

- [4] T. Karnik et al., Characterization of soft errors caused by single event upsets in CMOS processes, IEEE Trans. Dependable Secure Comput. 1 (2004) 128.

- [5] O. Musseau, Single-event effects in SOI technologies and devices, IEEE Trans. Nucl. Sci. 43 (1996) 603.

- [6] V. Ferlet-Cavrois et al., Statistical Analysis of the Charge Collected in SOI and Bulk Devices Under Heavy lon and Proton Irradiation Implications for Digital SETs, IEEE Trans. Nucl. Sci. 53 (2006) 3242.

- [7] M. Gaillardin et al., *Total Ionizing Dose Effects Mitigation Strategy for Nanoscaled FDSOI Technologies*, *IEEE Trans. Nucl. Sci.* **61** (2014) 3023.

- [8] J.R. Schwank et al., Advantages and limitations of silicon-on-insulator technology in radiation environments, Microelectron. Eng. 36 (1997) 335.

- [9] H.-K. Lim and J.G. Fossum, *Threshold voltage of thin-film Silicon-on-insulator (SOI) MOSFET's*, *IEEE Trans. Electron Devices* **30** (1983) 1244.

- [10] W.C. Jenkins and S.T. Liu, Radiation response of fully-depleted MOS transistors fabricated in SIMOX, *IEEE Trans. Nucl. Sci.* **41** (1994) 2317.

- [11] O. Flament, A. Torres and V. Ferlet-Cavrois, *Bias dependence of FD transistor response to total dose irradiation*, *IEEE Trans. Nucl. Sci.* **50** (2003) 2316.

- [12] M. Gaillardin et al., Impact of SOI Substrate on the Radiation Response of UltraThin Transistors Down to the 20 nm Node, IEEE Trans. Nucl. Sci. 60 (2013) 2583.

- [13] M. Spear et al., Non-Linear Coupling Effects in Fully Depleted SOI Transistors, IEEE Trans. Nucl. Sci. 70 (2023) 434.

- [14] D. Contardo et al., *Technical Proposal for the Phase-II Upgrade of the CMS Detector*, CERN-LHCC-2015-010 (2015) [DOI:10.17181/CERN.VU8I.D59J].

- [15] F. Faccio et al., Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs, IEEE Trans. Nucl. Sci. 62 (2015) 2933.

- [16] F. Faccio and G. Cervelli, *Radiation-Induced Edge Effects in Deep Submicron CMOS Transistors*, *IEEE Trans. Nucl. Sci.* **52** (2005) 2413.

- [17] S. Bonaldo et al., *Ionizing-Radiation Response and Low-Frequency Noise of 28-nm MOSFETs at Ultrahigh Doses, IEEE Trans. Nucl. Sci.* **67** (2020) 1302.

- [18] G. Borghello et al., *Ionizing radiation damage in 65 nm CMOS technology: Influence of geometry, bias and temperature at ultra-high doses*, *Microelectron. Reliab.* **116** (2021) 114016 1302.

- [19] J. Wang et al., *The total ionizing dose response of leading-edge FDSOI MOSFETs*, *Microelectron. Reliab.* **88-90** (2018) 979.

- [20] F. Faccio et al., Influence of LDD Spacers and H<sup>+</sup> Transport on the Total-Ionizing-Dose Response of 65-nm MOSFETs Irradiated to Ultrahigh Doses, IEEE Trans. Nucl. Sci. 65 (2018) 164.

- [21] S. Bonaldo et al., Influence of Halo Implantations on the Total Ionizing Dose Response of 28-nm pMOSFETs Irradiated to Ultrahigh Doses, IEEE Trans. Nucl. Sci. 66 (2019) 82.