Thèse n°10282

# EPFL

# Silicon CMOS and InGaAs(P)/InP SPADs for NIR/SWIR detection

Présentée le 12 avril 2024

Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Utku KARACA

Acceptée sur proposition du jury

Prof. G. Boero, président du jury Prof. E. Charbon, directeur de thèse Dr A. Rochas, rapporteur Prof. A. Gulinatti, rapporteur Prof. J.-M. Sallese, rapporteur

École polytechnique fédérale de Lausanne

2024

To My Friends, My Family & My Ashley

# Acknowledgements

First of all, I would like to express my sincere gratitude to my supervisor, Prof. Edoardo Charbon, for his extraordinary guidance and help in this work. I also want to thank him for giving me the chance to work in such an amazing laboratory. Although there was a one-year delay, I am very grateful that he still considered me for a PhD position and saw value in me.

I would like to thank Dr. Claudio Bruschini for supervising me with regular meetings and sharing his experience to improve my knowledge and the quality of this work.

I am thankful to Prof. Giovanni Boero for being the president of my thesis committee. It was also a great experience to teach with him during my PhD.

I would like to thank Prof. Angelo Gulinatti, Dr. Alexis Rochas, and Prof. Jean-Michel Sallese for their participation in my jury committee, evaluating my thesis, and providing me invaluable feedback to improve its quality.

I would like to express my sincere gratitude to my Master's thesis supervisor at Middle East Technical University, Prof. Serdar Kocaman, who is one of the most important people in my career. He taught me about semiconductors and photonics and gave me a chance to work with him on exciting projects that greatly helped me finish this thesis work as well.

I also owe a debt of gratitude to Ekin Kızılkan, with whom I have worked since 2015, performed projects together, and did a lot of brainstorming and discussions throughout our academic career, besides for his invaluable friendship in and outside the laboratory.

I would like to thank old and new AQUA lab members Halil Kerim Yildirim, Baris Can Efe, Francesco Gramuglia, Pouyan Keshavarzian, Ming-lo Wu, Paul Mos, Augusto Carimatto, Ivan Michel Antolovic, Andrea Ruffino, Vladimir Pesic, Jad Bensehir, Yasemin Uzun, Tommaso Milanese, Andrada Muntean, Andrei Ardelean, Preethi Padmanabhan, Yang Lin, Chufan Zhou, Arin Can Ulku, Batuhan Keskin, Won Yong Ha, Kodai Kaneyasu, Samuele Bisi, Jiuxuan Zhao, and Yating Zou for their friendship, technical discussions, and enjoyable moments outside the

#### **Chapter 0**

lab. I am also very happy to meet our lab administrative assistants, Brigitte Khan and Begonia Tora, and their help regarding everything in the lab.

I would like to thank my friends Juan Francisco Gonzalez Marin, Cheol-Yeon Cheon, Ulas Dinc, Asli Sahin, Mustafa Kangul, Silan Sahan, Selen Keles, Deniz Yalcin, Andac Yigit, Eray Kacar, Fatih Kalyon, Yigit Ozer, Kubra Circir, Muammer Kozan, and Halit Dolas for their friendship and support.

Last but not least, I would like to express my love to my family and my fiancee Ashley for always being with me, for supporting me, and for their unconditional love that made me a better person and helped me finalize my PhD. They are my most valuable things, and without any of them, I could not finish this work.

Renens, 4 December 2023

U. K.

### Abstract

Applications demanding imaging at low-light conditions at near-infrared (NIR) and shortwave infrared (SWIR) wavelengths, such as quantum information science, biophotonics, space imaging, and light detection and ranging (LiDAR), have accelerated the development of NIR/SWIR single-photon detectors. Up to date, there have been various detector types performing single-photon detection at infrared wavelengths. Among them, single-photon avalanche diodes (SPADs) have gained significant attention thanks to their low noise near room temperature (< 100 cps), high detection efficiencies (> 50%), and low timing jitter (< 100 ps). In addition, the integration of SPADs with standard CMOS technologies has paved the way for the design of low-cost, large pixel arrays with embedded photon-counting and timestamping circuitry.

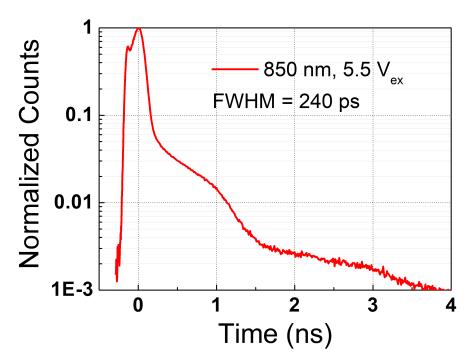

For detection at NIR/SWIR, Si CMOS and InGaAs(P)/InP-based SPADs appear as the most promising material systems. Si CMOS has the advantage of yielding low noise and integrating SPADs with on-chip readout circuits; however, the low absorption coefficient towards NIR is a bottleneck to enhancing detection efficiencies. In this sense, the wide depletion region approach was investigated in this work by designing SPADs in a 110 nm CIS technology with a 10  $\mu$ m active diameter. The implemented techniques of doping compensation and double multiplication region showed that the former can be utilized to extend depletion region widths, whereas the latter increases the total avalanche breakdown probability in a wide depletion SPAD, leading to high NIR efficiencies at a relatively lower breakdown voltage. In the fabricated SPADs with doping compensation, 7.3% PDP and 68 ps timing jitter at 850 nm and 5 V<sub>ex</sub> were achieved under the noise of 962 cps. Thanks to a fully substrate-non-isolated structure with graded substrate doping and enhanced breakdown probabilities, 25.5% PDP at 850 nm and 5.5 V<sub>ex</sub> were obtained in the device with the double multiplication region with a 295 cps noise, all at room temperature. However, the jitter at 850 nm was deteriorated to 236 ps due to many detected diffused carriers creating a diffusion peak in the timing histogram.

InGaAs(P)/InP-based SPADs were also designed, fabricated, and characterized, targeting 1.06  $\mu$ m and 1.55  $\mu$ m wavelengths. Planar device structures based on double zinc diffusions were implemented to define the active and guard ring regions of the SPADs. A comprehensive study was conducted via TCAD simulations to adjust the multiplication region thickness and the depth difference between two diffusions, which allowed for optimization of noise and active area uniformity. The numerical study also enabled the removal of floating guard rings,

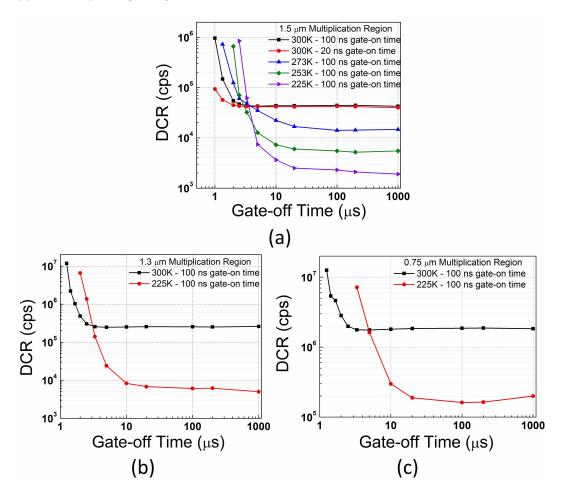

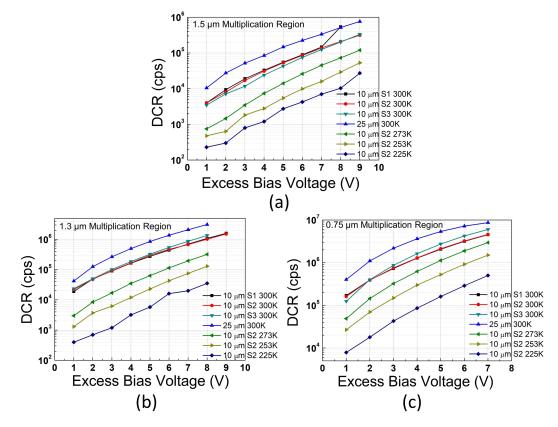

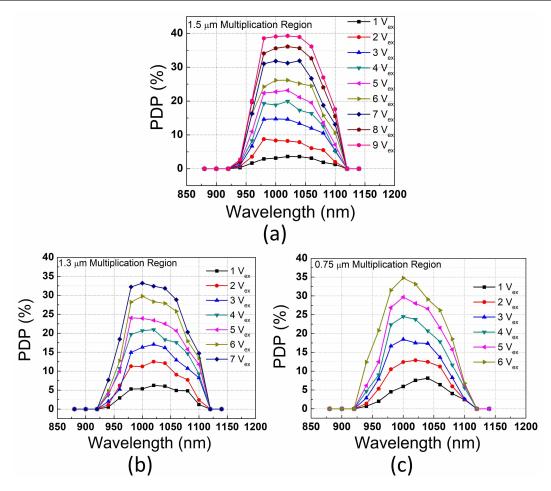

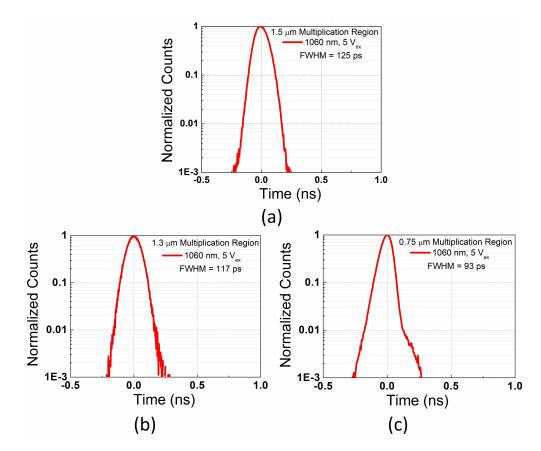

shrinking pixel sizes for future array implementation. The noise of a 10  $\mu$ m device with an InGaAsP absorber and a 1.5  $\mu$ m multiplication region at 5 V<sub>ex</sub> was 14.1 kcps, 5.5 kcps, and 2.75 kcps at 273K, 253K, and 225K, respectively, at 10 kHz frequency and 100 ns gate-on time. It was shown that the maximum operating frequency can be increased up to 200 kHz without suffering from the afterpulsing effect near room temperature. The PDP can be increased up to 36% at 9 V<sub>ex</sub> and 1060 nm wavelength, and the jitter was reduced to 118.4 ps at 5 V<sub>ex</sub> and 1060 nm. A 10  $\mu$ m SPAD with an InGaAs absorber and 1.5  $\mu$ m multiplication region achieved 20% PDP at 1550 nm and 61 kcps noise, both at 6 V<sub>ex</sub>. The jitter of this device was 123 ps at 1550 nm and 5 V<sub>ex</sub>.

Key words: Single-photon avalanche diodes (SPADs), near-infrared (NIR), short-wave infrared (SWIR), light detection and ranging (LiDAR), quantum key distribuiton (QKD), near-infrared optical tomography (NIROT), time-correlated single-photon counting (TCSPC), CMOS image sensor technology, doping compensation, double multiplication region, InGaAs(P)/InP, III-V, 3D integration

## Résumé

Les applications exigeant l'imagerie dans des conditions de faible luminosité dans les longueurs d'onde du proche infrarouge (NIR) et de l'infrarouge à ondes courtes (SWIR), telles que la science de l'information quantique, la biophotonique, l'imagerie spatiale et la détection et la télémétrie de la lumière (LiDAR), ont accéléré le développement de Détecteurs à photon unique NIR/SWIR. Jusqu'à présent, il existe différents types de détecteurs effectuant une détection de photons uniques dans les longueurs d'onde infrarouges. Parmi elles, les diodes à avalanche à photon unique (SPAD) ont retenu l'attention grâce à leur faible bruit proche de la température ambiante (< 100 cps), leur efficacité de détection élevée (> 50%) et leur faible gigue temporelle (< 100 ps). De plus, l'intégration des SPAD avec les technologies CMOS standard a ouvert la voie à la conception de grands réseaux de pixels à faible coût avec des circuits intégrés de comptage de photons et d'horodatage.

Pour la détection en NIR/SWIR, les SPAD à base de Si CMOS et InGaAs(P)/InP apparaissent comme les systèmes de matériaux les plus prometteurs. Le Si CMOS présente l'avantage de produire un faible bruit et d'intégrer des SPAD avec des circuits de lecture sur puce; cependant, le faible coefficient d'absorption vers le NIR constitue un goulot d'étranglement pour améliorer l'efficacité de la détection. En ce sens, l'approche de la région d'appauvrissement large a été étudiée dans ce travail en concevant des SPAD dans une technologie CIS de 110 nm avec un diamètre actif de 10 µm. Les techniques mises en œuvre de compensation de dopage et de région de double multiplication ont montré que la première peut être utilisée pour étendre la largeur de la région d'appauvrissement, tandis que la seconde augmente la probabilité totale de claquage par avalanche dans un SPAD à appauvrissement large, conduisant à des rendements NIR élevés à une tension de claquage relativement inférieure. Dans les SPAD fabriqués avec compensation de dopage, 7.3% PDP et 68 ps gigue à 850 nm et 5 Vex ont été obtenus sous un bruit de 962 cps. Grâce à une structure entièrement non isolée avec un dopage de substrat gradué et des probabilités de rupture améliorées, 25.5% de PDP à 850 nm et 5.5 Vex ont été obtenus dans le dispositif avec la région de double multiplication avec un bruit de 295 cps, le tout à température ambiante. Cependant, la gigue à 850 nm a été réduite à 236 ps en raison de nombreuses porteuses diffuses détectées, créant un pic de diffusion dans l'histogramme temporel.

Des SPAD basés sur InGaAs(P)/InP ont également été conçus, fabriqués et caractérisés, ciblant

des longueurs d'onde de 1.06 µm et 1.55 µm. Des structures de dispositifs planaires basées sur des doubles diffusions de zinc ont été mises en œuvre pour définir les régions actives et d'anneau de garde des SPAD. Une étude complète a été menée via des simulations TCAD pour ajuster l'épaisseur de la région de multiplication et la différence de profondeur entre deux diffusions, ce qui a permis d'optimiser l'uniformité du bruit et de la zone active. L'étude numérique a également permis de supprimer les anneaux de garde flottants, réduisant ainsi la taille des pixels pour la mise en œuvre future du réseau. Le bruit d'un appareil de 10 µm avec un absorbeur InGaAsP et une région de multiplication de  $1.5 \,\mu\text{m}$  à 5 V<sub>ex</sub> était de 14.1k cps, 5.5k cps et 2.75k cps à 273K, 253K et 225K, respectivement, à une fréquence de 10 kHz et à un temps d'activation de 100 ns. Il a été démontré que la fréquence de fonctionnement maximale peut être augmentée jusqu'à 200 kHz sans souffrir de l'effet de rémanence à proximité de la température ambiante. Le PDP peut être augmenté jusqu'à 36% à 9 Vex et 1060 nm de longueur d'onde, et la gigue a été réduite à 118.4 ps à 5  $V_{ex}$  et 1060 nm. Un SPAD de 10  $\mu$ m avec un absorbeur InGaAs et une région de multiplication de 1.5 µm a atteint 20% de PDP à 1550 nm et un bruit de 61k cps, tous deux à 6 Vex. La gigue de cet appareil était de 123 ps à 1550 nm et 5 V<sub>ex</sub>.

Mots clefs : Diodes à avalanche à photon unique (SPAD), proche infrarouge (NIR), infrarouge à ondes courtes (SWIR), détection et télémétrie par la lumière (LiDAR), distribution de clés quantiques (QKD), tomographie optique dans le proche infrarouge (NIROT), comptage de photons uniques corrélés dans le temps (TCSPC), technologie des capteurs d'images CMOS, compensation du dopage, région de double multiplication, InGaAs(P)/InP, III-V, intégration 3D

# Contents

| Ac  | knov                            | wledgements                                                          | i    |

|-----|---------------------------------|----------------------------------------------------------------------|------|

| Ab  | Abstract (English/Français) iii |                                                                      |      |

| Lis | List of figures xi              |                                                                      |      |

| Lis | ist of tables xvi               |                                                                      |      |

| Ac  | rony                            | 7ms                                                                  | xvii |

| 1   | Intr                            | oduction                                                             | 1    |

|     | 1.1                             | NIR/SWIR detection and its advantages                                | 1    |

|     | 1.2                             | Application areas of NIR/SWIR single-photon detectors                | 4    |

|     |                                 | 1.2.1 Light detection and ranging                                    | 4    |

|     |                                 | 1.2.2 Quantum cryptography                                           | 6    |

|     |                                 | 1.2.3 NIR optical tomography                                         | 7    |

|     | 1.3                             | Single-photon detector types                                         | 8    |

|     |                                 | 1.3.1 Photomultiplier tubes                                          | 9    |

|     |                                 | 1.3.2 Single-photon avalanche diodes                                 | 10   |

|     |                                 | 1.3.3 Superconducting nanowire single-photon detectors               | 12   |

|     |                                 | 1.3.4 Superconducting transition-edge sensor single-photon detectors | 13   |

|     |                                 | 1.3.5 Quantum dot based single-photon detectors                      | 14   |

|     |                                 | 1.3.6 Figures of merit comparison of single-photon detectors         | 16   |

|     | 1.4                             | Motivation and the aims of the thesis                                | 17   |

|     | 1.5                             | Contributions                                                        | 17   |

|     | 1.6                             | Thesis organization                                                  | 18   |

| 2   | Figu                            | res of Merit and Metrology of SPADs                                  | 19   |

|     | 2.1                             | SPAD's working principles                                            | 19   |

|     | 2.2                             | Quench and recharge techniques                                       | 20   |

|     |                                 | 2.2.1 Passive technique                                              | 21   |

|     |                                 | 2.2.2 Active technique                                               | 23   |

|     | 2.3                             | Operation modes of the SPADs                                         | 24   |

|     | 2.4                             | Figures of merit of the SPADs                                        | 26   |

|     |                                 | 2.4.1 Breakdown voltage                                              | 26   |

|   |            | 2.4.2 Dark count rate                                            | 27        |

|---|------------|------------------------------------------------------------------|-----------|

|   |            | 2.4.3 Afterpulsing probability                                   | 30        |

|   |            | 2.4.4 Photon detection probability                               | 32        |

|   |            | 2.4.5 Timing jitter                                              | 34        |

| _ |            |                                                                  |           |

| 3 |            | X/SWIR SPAD Case Analysis                                        | 37        |

|   | 3.1        | NIR Enhanced Si CMOS SPADs                                       | 37        |

|   |            | 3.1.1 Wide depletion region SPADs                                | 38        |

|   |            | 3.1.2 Back-side-illumination                                     | 40        |

|   |            | 3.1.3 Electrical micro-lensing or charge-focusing technique      | 41        |

|   |            | 3.1.4 Light-trapping structures                                  | 41        |

|   | 3.2        | NIR/SWIR InGaAs(P)/InP SPADs                                     | 42        |

|   |            | 3.2.1 Planar double Zn diffusion technique                       | 45        |

|   |            | 3.2.2 Mesa technique                                             | 47        |

|   |            | 3.2.3 One-step Zn diffusion with SAG                             | 47        |

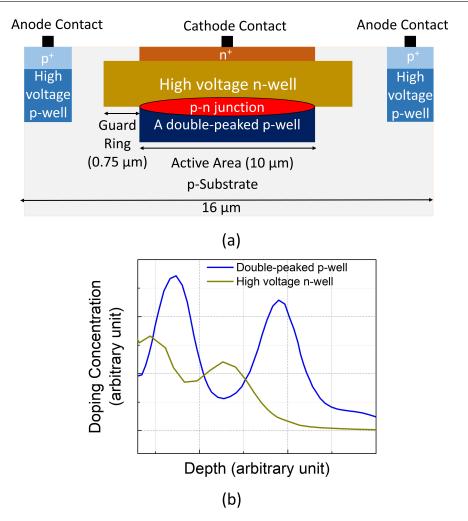

| 4 | Nou        | v Techniques and Optimization for NIR Sensitivity Enhancement in |           |

| 4 |            | MOS SPADs                                                        | 49        |

|   | 4.1        | TCAD simulation methodology of Si SPADs                          | <b>49</b> |

|   | 4.1<br>4.2 | Doping compensation technique                                    | 49<br>52  |

|   | 4.2        |                                                                  |           |

|   |            |                                                                  | 54<br>55  |

|   |            |                                                                  | 55<br>56  |

|   | 4.2        |                                                                  | 50<br>61  |

|   | 4.3        | Double multiplication region technique      1.1                  |           |

|   |            | <ul><li>4.3.1 Device structure</li></ul>                         | 63        |

|   |            |                                                                  | 64        |

|   | 4 4        | 4.3.3 Characterization results                                   | 67<br>72  |

|   | 4.4        | A guard ring study for an isolated wide depletion region SPAD    | 72        |

|   |            | <ul><li>4.4.1 Device structures</li></ul>                        | 72        |

|   |            |                                                                  | 73        |

|   | 4 5        | 4.4.3 Characterization results                                   | 74        |

|   | 4.5        | Comparison with the state-of-the-art                             | 77        |

| 5 | InG        | aAs(P)/InP-based SPAD                                            |           |

|   |            | relopment Targeting 1.06 μm and 1.55 μm Wavelengths              | 81        |

|   | 5.1        | TCAD simulation methodology of InGaAs(P)/InP-based SPADs         | 81        |

|   | 5.2        | Planar InGaAsP/InP SPADs for 1.06 µm wavelength detection        | 83        |

|   |            | 5.2.1 Device structures                                          | 83        |

|   |            | 5.2.2 TCAD simulation results                                    | 85        |

|   |            | 5.2.3 Fabrication procedure                                      | 90        |

|   |            | 5.2.4 Characterization results                                   | 91        |

|   |            |                                                                  | 103       |

|   | 5.3        | -                                                                | 103       |

|   | 0.0        |                                                                  | 101       |

|   |            | 5.3.1  | Device structures                                              | 105 |

|---|------------|--------|----------------------------------------------------------------|-----|

|   |            | 5.3.2  | TCAD simulation results                                        | 106 |

|   |            | 5.3.3  | Fabrication procedure                                          | 109 |

|   |            | 5.3.4  | Characterization results                                       | 109 |

|   |            | 5.3.5  | Comparison with the state-of-the-art                           | 114 |

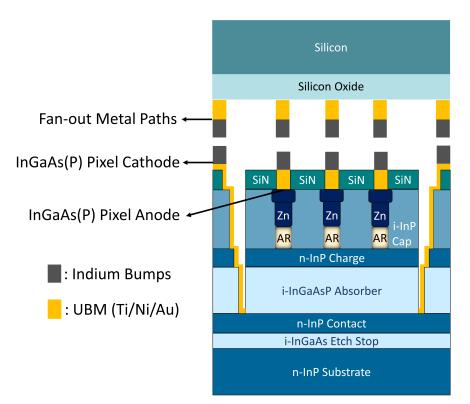

|   | 5.4        | Devel  | opment for the 3D Integration of InGaAs(P)/SPADs with Si ROICs | 115 |

|   |            |        |                                                                |     |

| 6 | Con        | clusio | ns and Future Perspective                                      | 121 |

| 6 |            |        | ns and Future Perspective usions and the summary of the works  |     |

| 6 | 6.1        | Concl  | I I                                                            | 121 |

|   | 6.1<br>6.2 | Concl  | usions and the summary of the works                            | 121 |

# List of Figures

| 1.1 | (a) Illustration of light propagation and data transmission in an optical fiber        |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | (Credits to Cadence). (b) Spectral photon exitance graphs belonging to various         |    |

|     | blackbody temperatures, including the Sun. (c) Maximum permissible exposure            |    |

|     | for eye-safe lasers for 1 ns pulse duration [18]. (d) Illustration of reduced Rayleigh |    |

|     | scattering through images captured by a visible and a SWIR camera [19]                 | 2  |

| 1.2 | Applications and operation principles of LiDAR                                         | 5  |

| 1.3 | A QKD system, which is implemented for high key generation rate at 1550 nm,            |    |

|     | where 8 pixels SNSPD was used as the detector at the receiver side [33]                | 7  |

| 1.4 | (a) Absorption spectrum of the main absorbers in the human body, indicating            |    |

|     | an optical window at NIR for medical imaging. [39]. (b) A NIROT setup to               |    |

|     | reconstruct the features in the tissues [41]                                           | 8  |

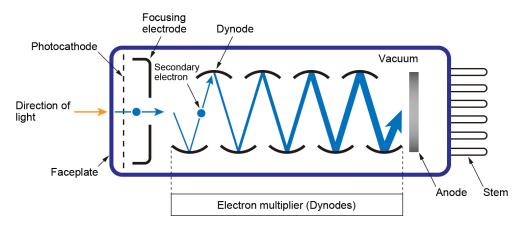

| 1.5 | A schematic of a conventional photomultiplier tube [44].                               | 10 |

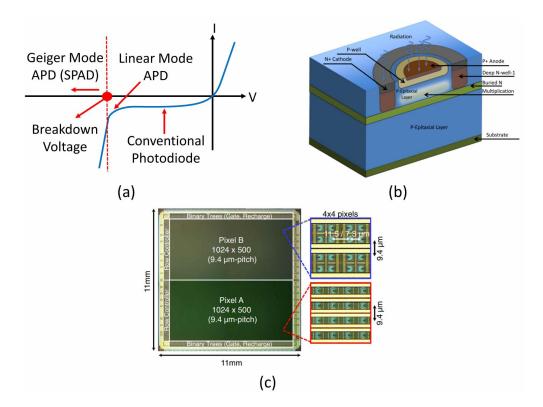

| 1.6 | (a) Operation modes of a p-n junction photodiode. (b) Cross section of a con-          |    |

|     | ventional SPAD pixel in a CMOS technology [47]. (c) First megapixel SPAD array         |    |

|     | fabricated in 180 nm CMOS technology combined with time-gating circuit for             |    |

|     | 2D and 3D imaging applications [48]                                                    | 11 |

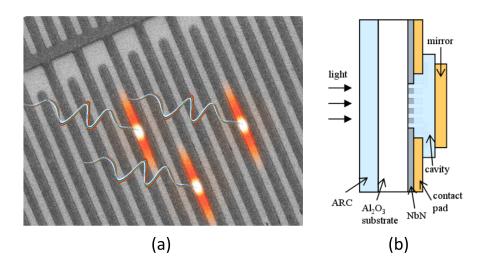

| 1.7 | (a) Nanowire heat-up process via photon absorption (Credits to Duke University).       |    |

|     | (b) An SNSPD cross section integrated with an optical cavity and mirrors to            |    |

|     | enhance absorption efficiency [68].                                                    | 13 |

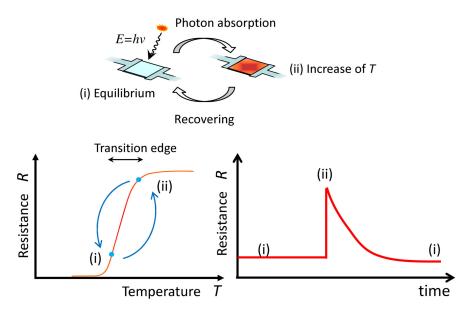

| 1.8 | Operation mechanism and phases of a TES [73]                                           | 14 |

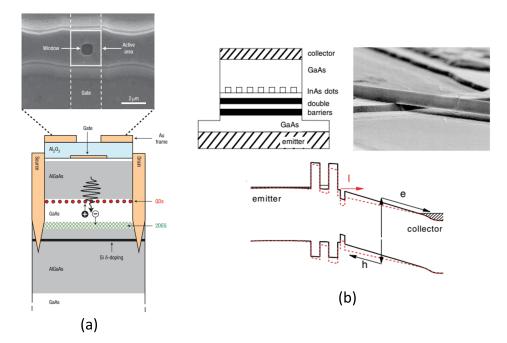

| 1.9 | (a) An illustration of an optically gated QDFET [78]. (b) A QD resonant tunneling      |    |

|     | diode device [79]                                                                      | 15 |

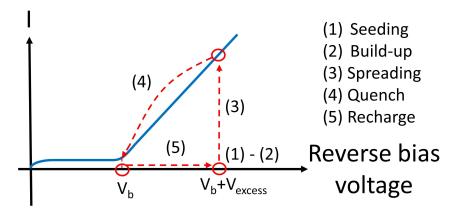

| 2.1 | The phases of an avalanche process                                                     | 20 |

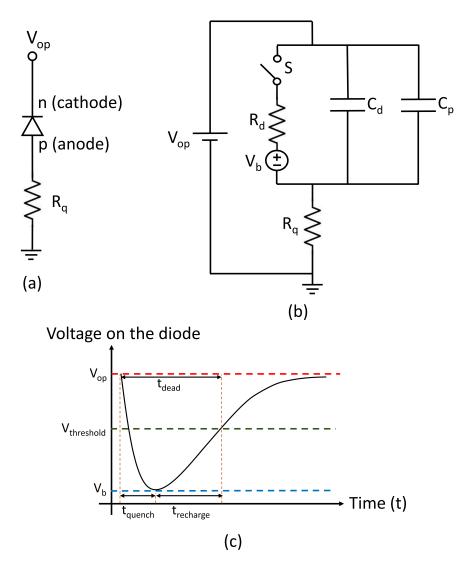

| 2.2 | (a) A schematic of a SPAD quenched and recharged passively. (b) The equivalent         |    |

|     | circuit of a SPAD with passive quench and recharge. (c) The illustration of the        |    |

|     | quench and recharge phases in passive technique through the voltage developed          |    |

|     | on the diode over time                                                                 | 22 |

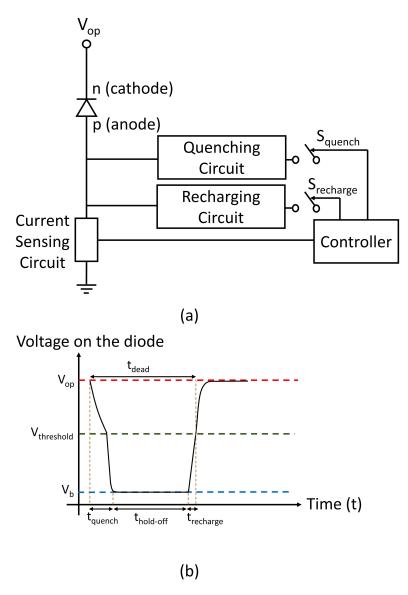

| 2.3 | (a) A schematic of a SPAD quenched and recharged actively. (b) The illustration        |    |

|     | of the quench and recharge phases in active technique through the voltage              |    |

|     | developed on the diode in time.                                                        | 24 |

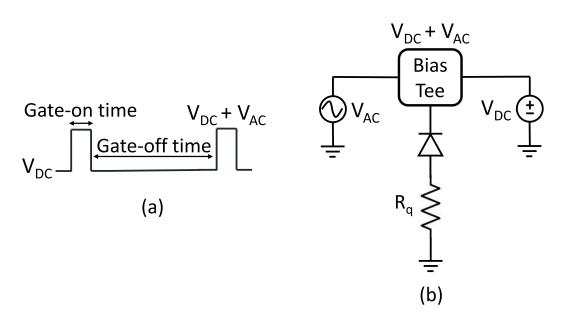

| 2.4 | (a) Timing and voltage diagrams of gated or time-gating mode SPADs. (b) A              |    |

|     | circuit implementation of time-gating mode.                                            | 25 |

#### Chapter 0

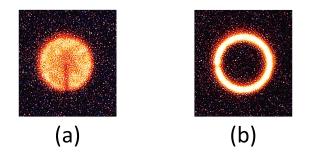

| 2.5 | Light emission test result of a (a) properly functioning SPAD, (b) SPAD with premature edge breakdown.                                                    | 27 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

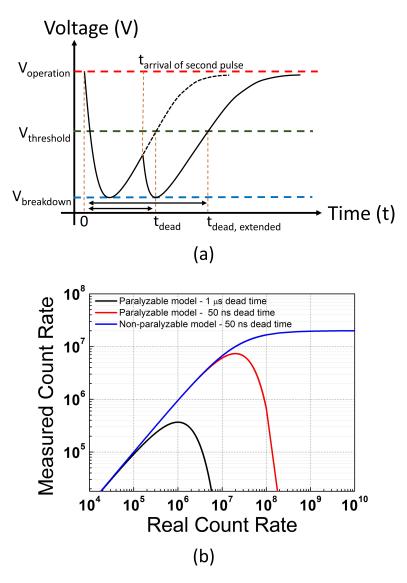

| 2.6 | (a) Representation of the extended dead time effect modeled by the paralyzable dead time model. (b) The relation between the measured and real count rate |    |

|     | according to the paralyzable and non-paralyzable dead time models under                                                                                   |    |

|     | different count rates.                                                                                                                                    | 29 |

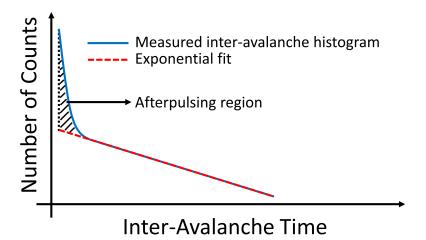

| 2.7 | An example measured afterpulsing histogram with the exponential fit represent-                                                                            | 21 |

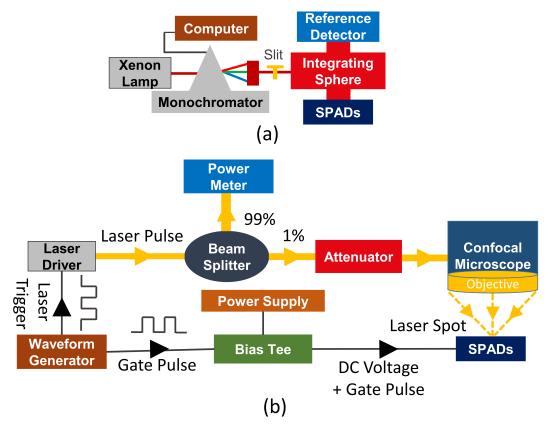

| 2.8 | <ul><li>ing the case when there is no afterpulsing.</li><li>(a) The setup to characterize the PDP of the SPADs with a continuous light source.</li></ul>  | 31 |

|     | (b) The optical setup to measure the PDP of the SPADs with a focused pulsed                                                                               |    |

|     | laser beam.                                                                                                                                               | 34 |

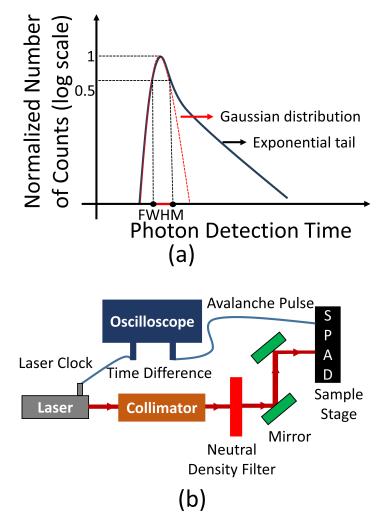

| 2.9 | (a) A representative timing jitter histogram and its components. (b) A timing                                                                             |    |

|     | jitter measurement setup based on TCPSC technique.                                                                                                        | 36 |

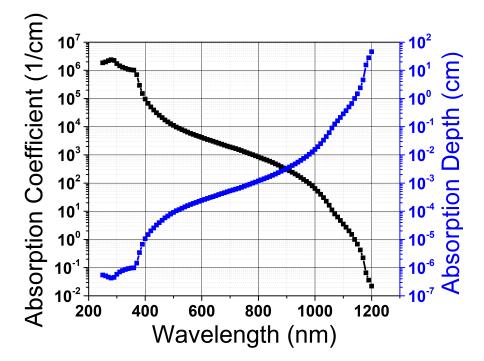

| 3.1 | Absorption coefficients and depths of Si with respect to wavelengths                                                                                      | 38 |

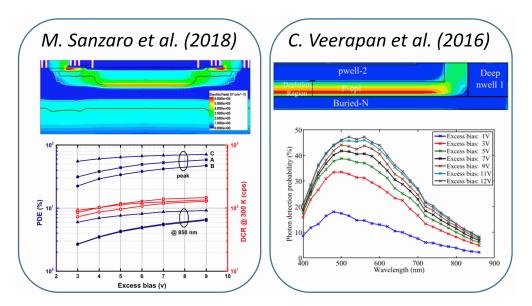

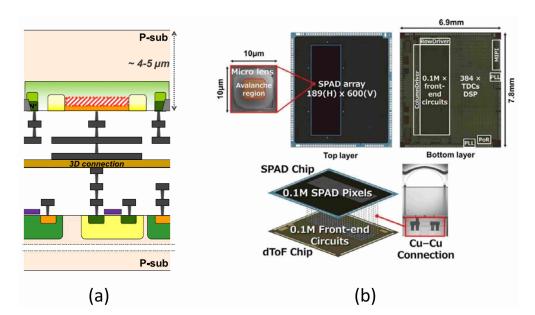

| 3.2 | Wide depletion region SPADs demonstrated in the literature [51], [110]                                                                                    | 39 |

| 3.3 | (a) Overview of the BSI approach in a cross-section [114]. (b) BSI-stacked large-                                                                         |    |

|     | format SPAD sensor with copper-to-copper bonding [26]                                                                                                     | 40 |

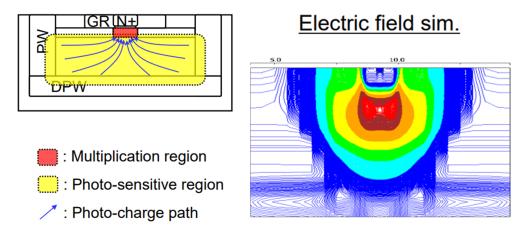

| 3.4 | Electrical micro-lensing technique, also known as charge focusing, explained                                                                              |    |

|     | with a cross-section and electrical field simulations [115], [116].                                                                                       | 41 |

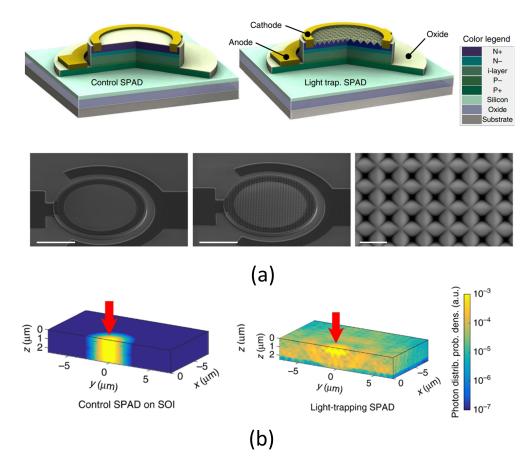

| 3.5 | (a) The cross-section and SEM images of a conventional SPAD and a SPAD with                                                                               |    |

|     | inverse pyramid-shaped light-trapping structures [117]. (b) Photon distribution                                                                           |    |

|     | probability of a conventional SPAD and a SPAD with light-trapping nanostruc-                                                                              |    |

|     | tures [117]                                                                                                                                               | 42 |

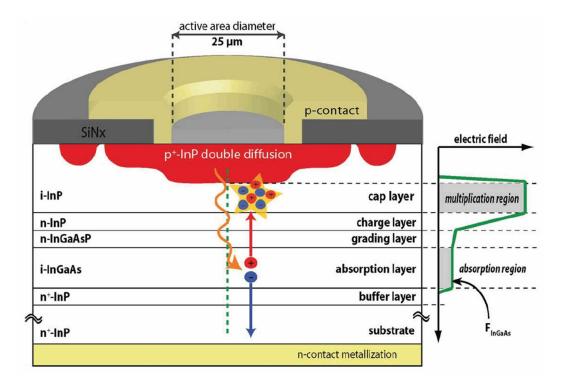

| 3.6 | Cross-section of an InGaAs(P)/InP SPAD fabricated with the double Zn diffusion                                                                            |    |

|     | process [119]                                                                                                                                             | 45 |

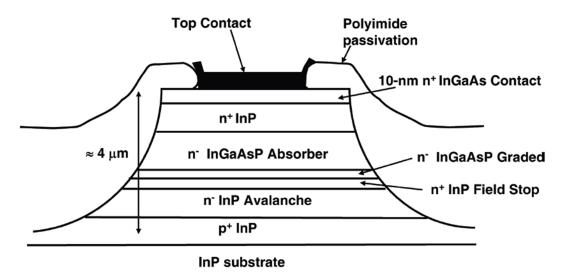

| 3.7 | Cross-section of an InGaAs(P)/InP SPAD fabricated with the mesa process [98].                                                                             | 47 |

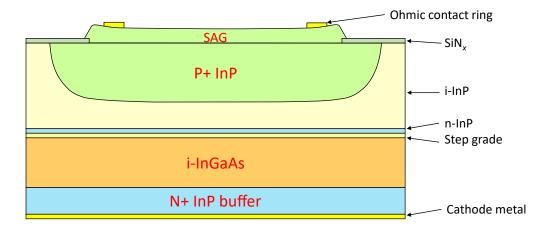

| 3.8 | Cross-section of an InGaAs(P)/InP SPAD fabricated with the SAG followed by                                                                                |    |

|     | one-step Zn diffusion [128], [135]                                                                                                                        | 48 |

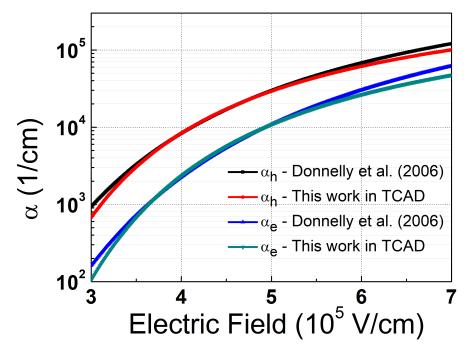

| 4.1 | Electron and hole impact ionization coefficients utilized in TCAD for Si                                                                                  | 52 |

| 4.2 | The energy band diagram of a compensated semiconductor.                                                                                                   | 53 |

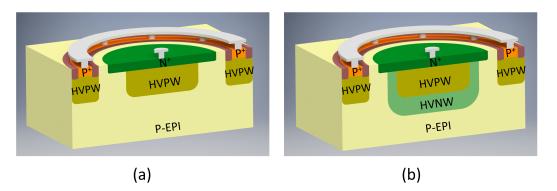

| 4.3 | Cross-sections of (a) $\mathrm{N}^+/\mathrm{HVPW}$ junction with a virtual GR and (b) $\mathrm{N}^+/\mathrm{HVPW}$                                        |    |

|     | junction with the HVNW doping compensation layer and a virtual GR                                                                                         | 54 |

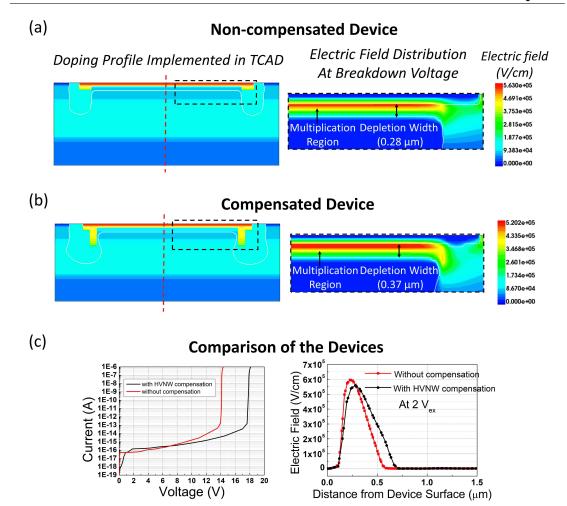

| 4.4 | Doping profile and electric field distribution at breakdown voltage of the (a)                                                                            |    |

|     | non-compensated SPAD and (b) compensated SPAD with HVNW layer. (c) I-V                                                                                    |    |

|     | curves and electric field magnitudes at $2\mathrm{V}_{ex}$ taken along the center of the devices.                                                         | 55 |

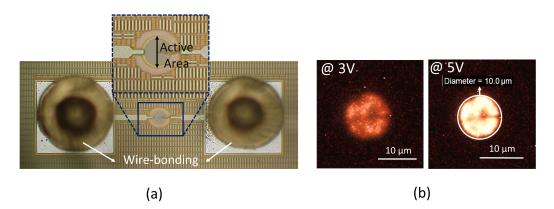

| 4.5 | (a) Micrograph of a fabricated device. (b) Light emission test results of the                                                                             |    |

|     | compensated SPAD sample #3                                                                                                                                | 56 |

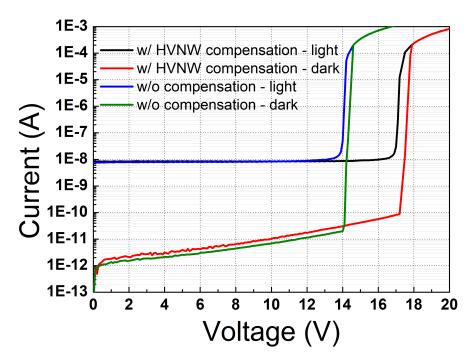

| 4.6 | I-V characteristics of the devices with and without doping compensation under                                                                             |    |

|     | both light and dark conditions.                                                                                                                           | 57 |

| 4.7 | DCR versus excess bias voltage curves of non-compensated and compensated                                                                                  |    |

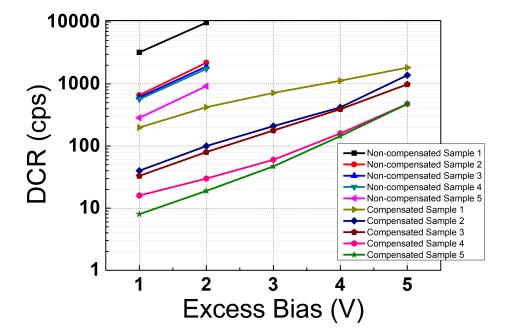

|     | SPADs obtained from 5 different dies at room temperature                                                                                                  | 58 |

|     |                                                                                                                                                           |    |

#### LIST OF FIGURES

| 4.8  | (a) Measured PDP spectrums of the compensated and non-compensated devices at various excess bias voltages. (b) PDP versus DCR comparison of the device at   |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | the peak and NIR wavelengths.                                                                                                                               | 59       |

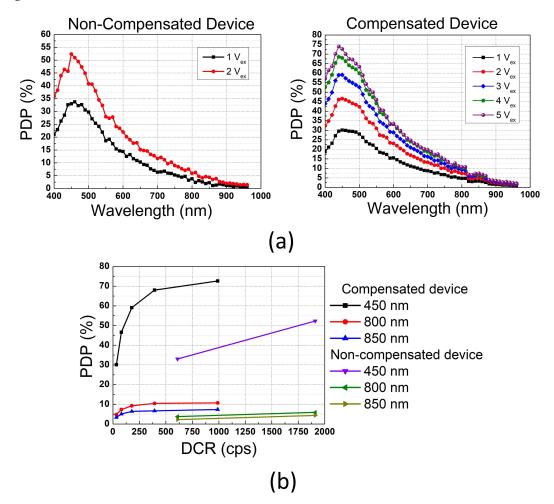

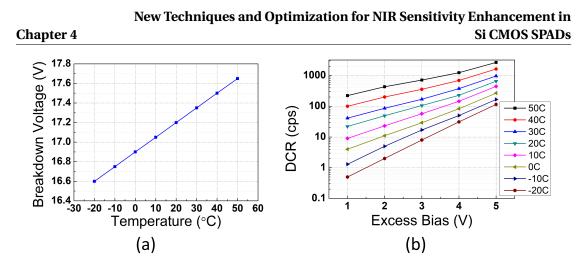

| 4.9  | (a) Breakdown voltage variation with temperature. (b) DCR versus $V_{ex}$ curves for                                                                        | 60       |

| 4 10 | different temperatures                                                                                                                                      | 60<br>60 |

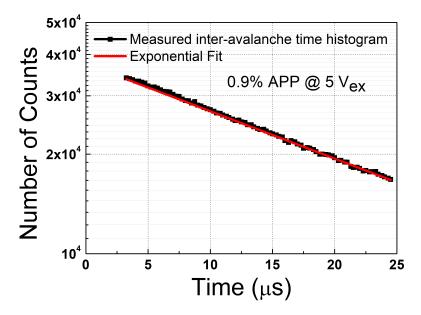

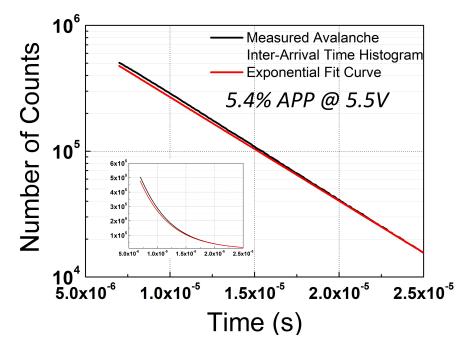

|      | Inter-arrival time histogram of the compensated SPAD at 5 $V_{ex}$                                                                                          | 60       |

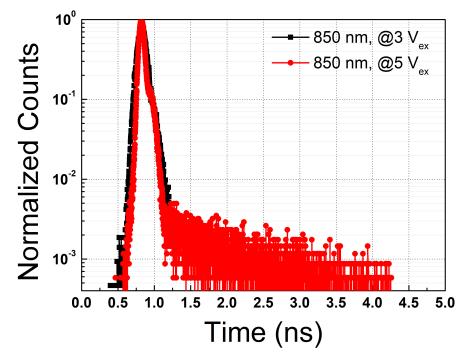

|      | Timing jitter histograms of the compensated SPAD at 850 nm                                                                                                  | 61       |

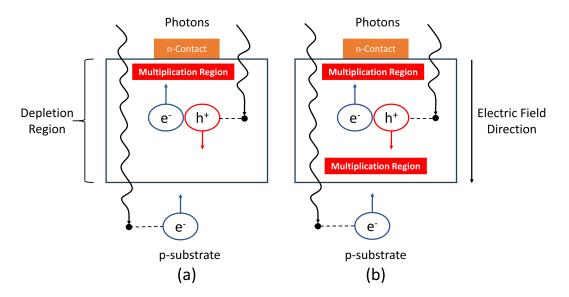

| 4.12 | Photon absorption at longer wavelengths and avalanche multiplication pro-<br>cesses in a wide depletion SPAD with (a) one multiplication region, (b) double |          |

|      | multiplication region.                                                                                                                                      | 62       |

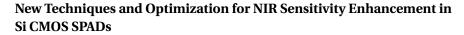

| 4.13 | (a) Cross-section of the proposed device. (b) Doping profiles of the utilized layers                                                                        |          |

|      | in arbitrary units.                                                                                                                                         | 63       |

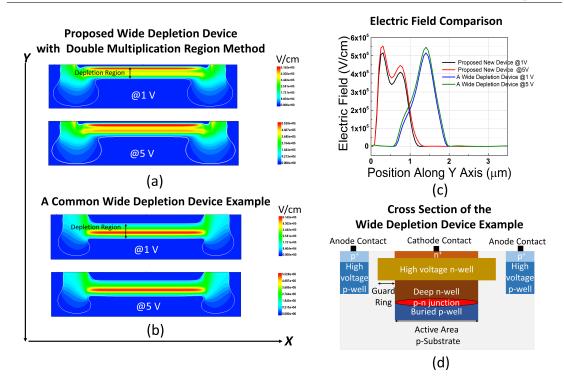

| 4.14 | Electric field profiles of (a) the proposed device with the double multiplication                                                                           |          |

|      | region and (b) a SPAD with a wide depletion region. (c) Magnitude of the electric                                                                           |          |

|      | field at the center of each device along the y axis. (d) The cross-section of the                                                                           |          |

|      | reference SPAD with a wide depletion                                                                                                                        | 65       |

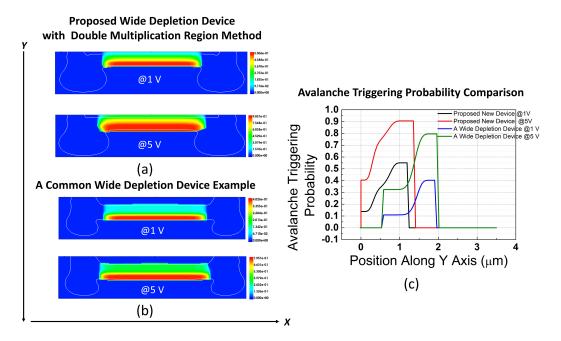

| 4.15 | Electron-hole avalanche breakdown probabilities of (a) the proposed device                                                                                  |          |

|      | with double multiplication region method, and (b) reference wide depletion                                                                                  |          |

|      | region SPAD. (c) Values of the avalanche breakdown probabilities at the center                                                                              |          |

|      | of each device along the y axis.                                                                                                                            | 66       |

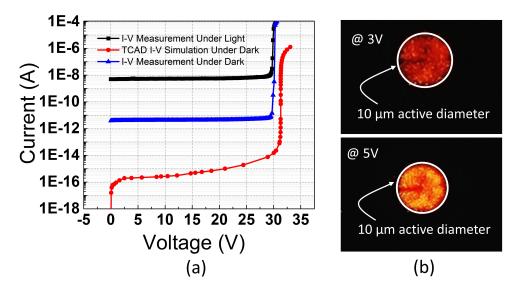

| 4.16 | (a) Measured and simulated I-V characteristics of the proposed device. (b) Light                                                                            |          |

|      | emission tests at 3 $V_{ex}$ and 5 $V_{ex}$                                                                                                                 | 67       |

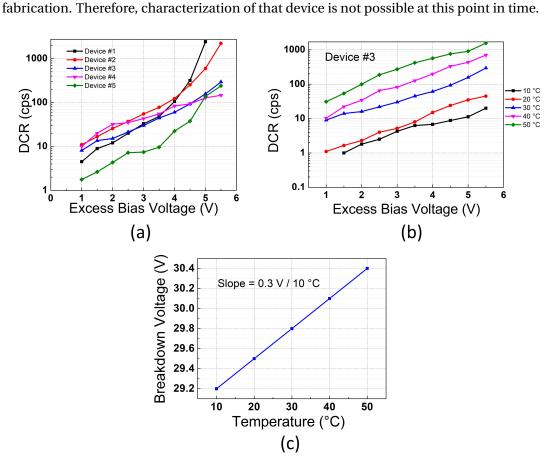

| 4.17 | (a) DCR measurements of the device on 5 different dies for various excess bias                                                                              |          |

|      | voltages at room temperature. (b) DCR versus temperature analysis of the se-                                                                                |          |

|      | lected Device #3. (c) The change in breakdown voltage between 10 and 50 $^{\circ}\mathrm{C.}$                                                               | 68       |

|      | Inter-arrival time histogram of the device at 5.5 $V_{ex}$                                                                                                  | 69       |

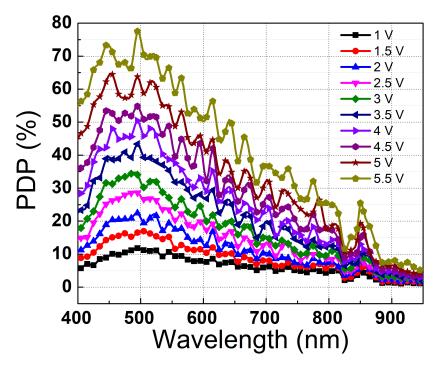

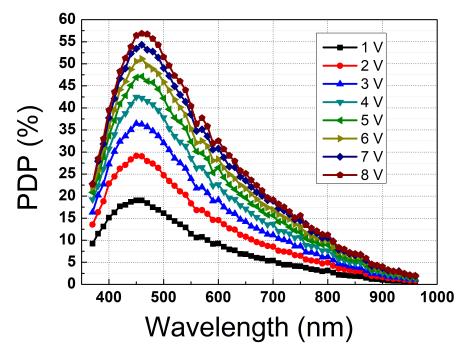

|      | PDP measurements of the device from 1 V <sub>ex</sub> to 5.5 V <sub>ex</sub>                                                                                | 70       |

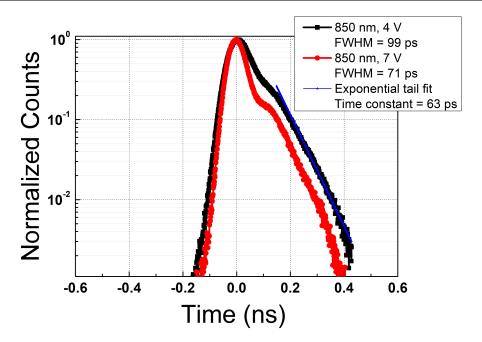

|      | Jitter measurement of the device at 850 nm and at 5.5 $V_{ex}$                                                                                              | 71       |

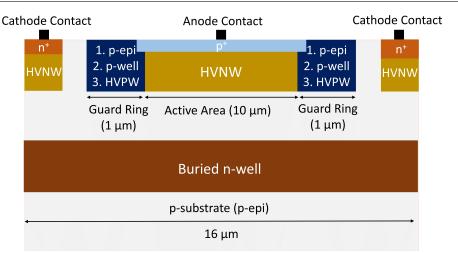

| 4.21 | Cross-sections of the substrate-isolated SPADs.                                                                                                             | 73       |

| 4.22 | Electric field profiles of the device with (a) p-epi GR, (b) p-well GR, and (c) HVPW                                                                        |          |

|      | GR at the breakdown voltage. (d) Electric field magnitude of the devices taken at                                                                           |          |

|      | the center of the active region and GR.                                                                                                                     | 73       |

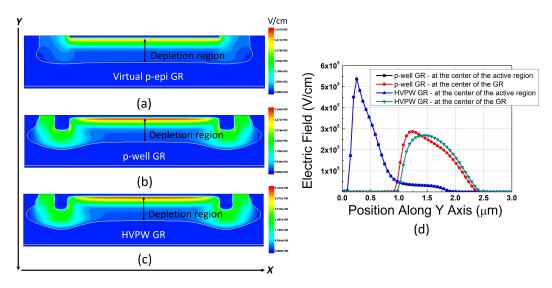

| 4.23 | (a) I-V measurements and simulation of the SPAD with p-well and HVPW GRs                                                                                    |          |

|      | under dark and light conditions. (b) Light emission tests of the device with p-well                                                                         |          |

|      | GR at various excess bias voltages.                                                                                                                         | 74       |

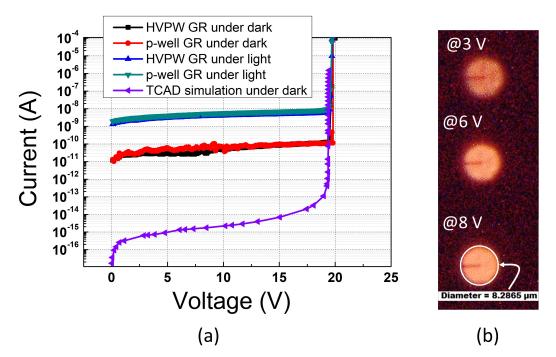

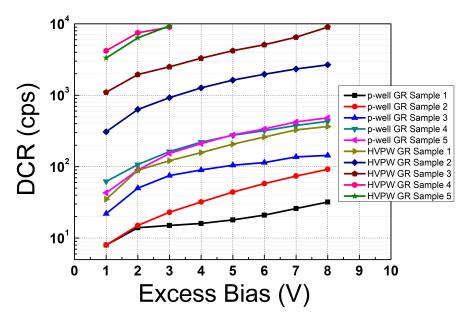

| 4.24 | DCR versus excess bias voltage curves of the $p^+/HVNW$ SPAD with the p-well                                                                                |          |

|      | and HVPW GRs obtained from 5 different dies at room temperature                                                                                             | 75       |

| 4.25 | PDP spectrum of the SPAD with the p-well GR from 1 $V_{ex}$ to 8 $V_{ex}.$ $\ldots$ $\ldots$ $\ldots$                                                       | 76       |

| 4.26 | Jitter measurements of the device with the p-well GR at 850 nm                                                                                              | 77       |

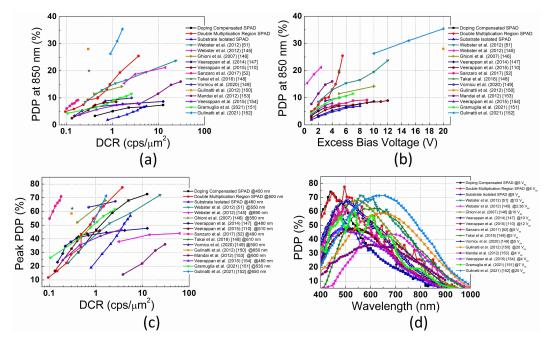

| 4.27 | (a) PDP at 850 nm versus normalized DCR, (b) PDP at 850 nm versus $V_{\text{ex}}$ (c)                                                                       |          |

|      | peak PDP versus normalized DCR, and (d) PDP spectrum comparisons of the                                                                                     |          |

|      | developed SPADs with FSI state-of-the-art wide depletion region SPADs                                                                                       | 78       |

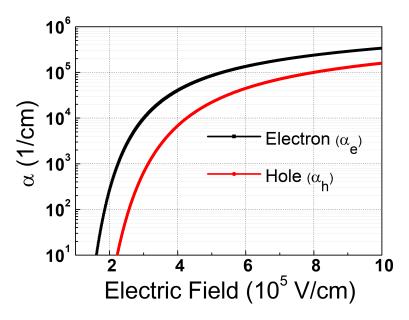

| 5.1  | InP electron and hole impact ionization coefficients that are extracted from Ref.<br>[98] and utilized in TCAD in this work                                                                                                                                                                                                                                           | 82 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

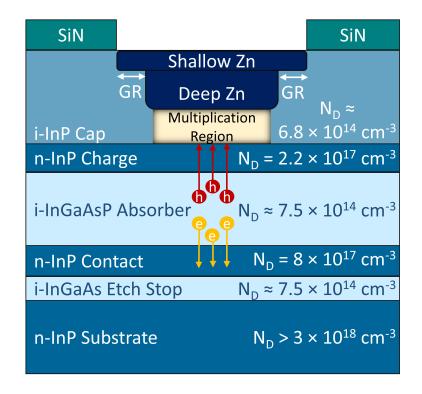

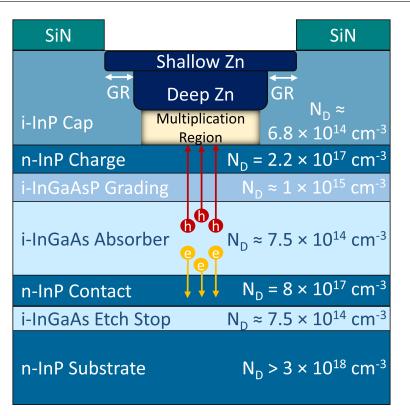

| 5.2  | The cross-section of 1.1 µm cutoff InGaAsP/InP SPADs.                                                                                                                                                                                                                                                                                                                 | 84 |

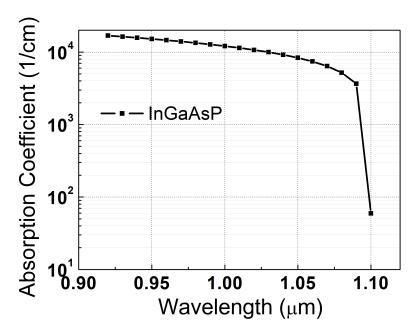

| 5.3  | The absorption coefficient of InGaAsP with respect to wavelength                                                                                                                                                                                                                                                                                                      | 85 |

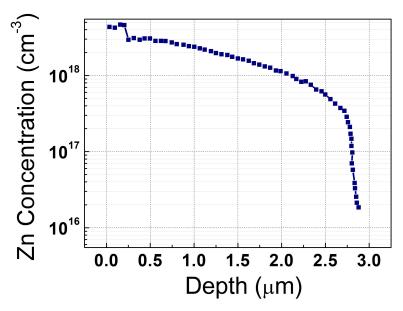

| 5.4  | Zn diffusion profile utilized in TCAD.                                                                                                                                                                                                                                                                                                                                | 86 |

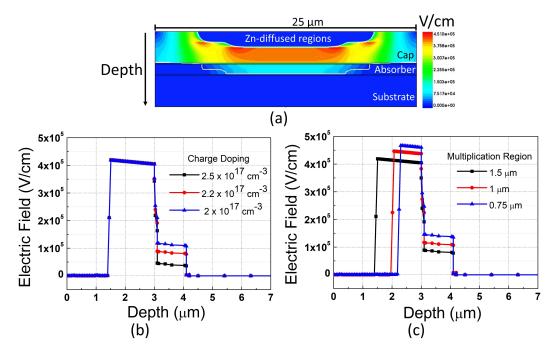

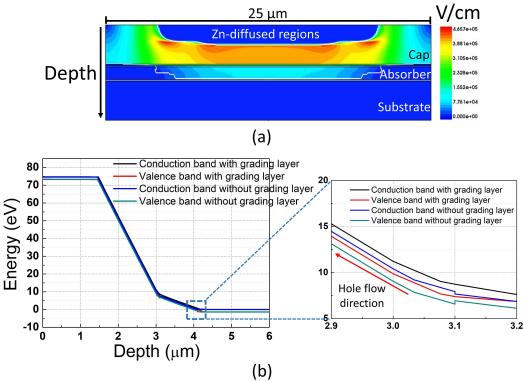

| 5.5  | (a) The electric field distribution of the device with a $1.5 \mu$ m multiplication region<br>at the breakdown voltage. (b) Charge doping sweep for the device with a $1.5 \mu$ m multiplication region at the breakdown voltage. (c) Multiplication region<br>thickness sweep for InGaAsP/InP SPADs.                                                                 | 87 |

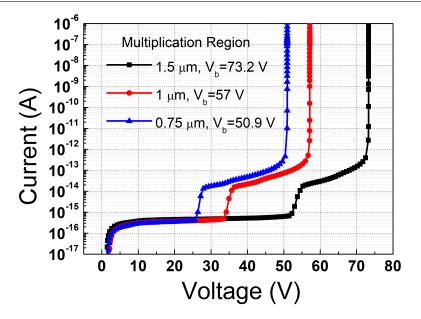

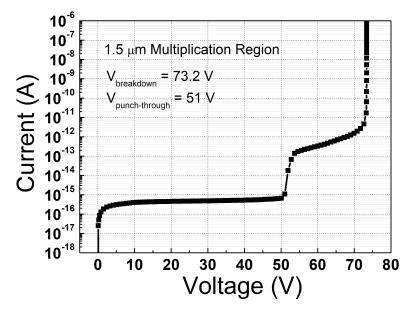

| 5.6  | The dark I-V curves of the devices with the 1.5 µm, 1 µm, and 0.75 µm multiplication region thicknesses at 300K in TCAD.                                                                                                                                                                                                                                              | 88 |

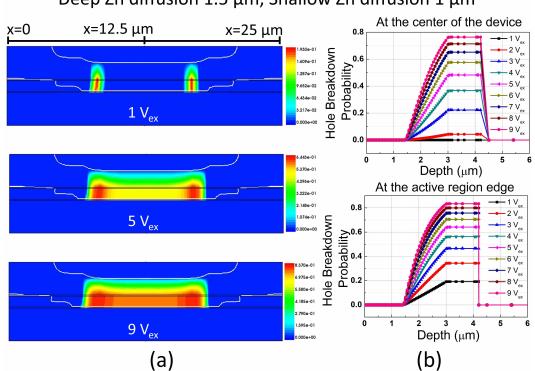

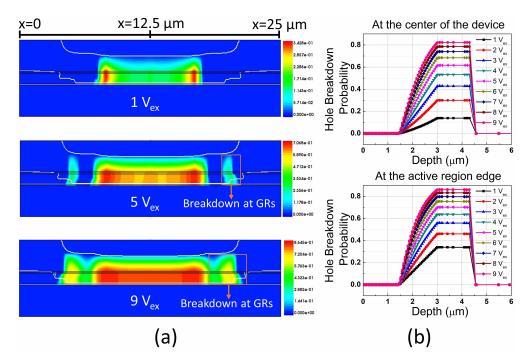

| 5.7  | (a) Hole avalanche breakdown probability distribution of the device with a 1.5 $\mu$ m multiplication region and 0.5 $\mu$ m depth difference between Zn diffusions at 1 V <sub>ex</sub> , 5 V <sub>ex</sub> , and 9 V <sub>ex</sub> . (b) Hole avalanche breakdown probabilities taken at the center and edge of the active region for various excess bias voltages  | 89 |

| 5.8  | (a) Hole avalanche breakdown probability distribution of the device with a 1.5 $\mu$ m multiplication region and 0.25 $\mu$ m depth difference between Zn diffusions at 1 V <sub>ex</sub> , 5 V <sub>ex</sub> , and 7 V <sub>ex</sub> . (b) Hole avalanche breakdown probabilities taken at the center and edge of the active region for various excess bias voltages | 90 |

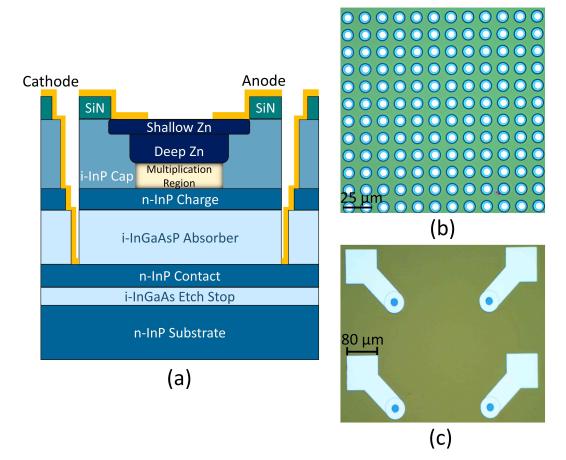

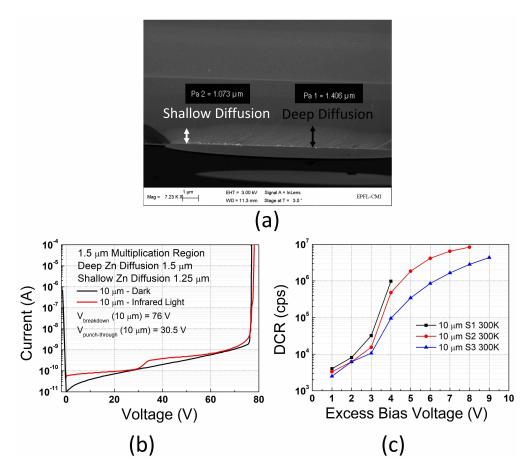

| 5.9  | <ul> <li>(a) The cross-section of the InGaAsP/InP SPADs after finalizing the fabrication.</li> <li>(b) A microscope image of arrays of 10 μm active diameter SPADs with a 2.5 μm</li> <li>GR after performing the deep and shallow Zn diffusion. (c) A microscope image of metallized text pixels.</li> </ul>                                                         | 91 |

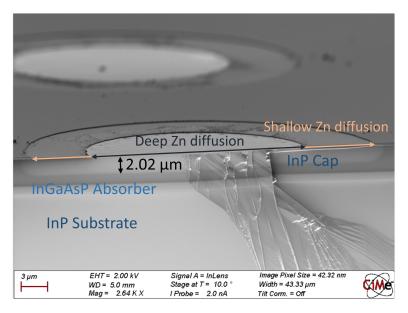

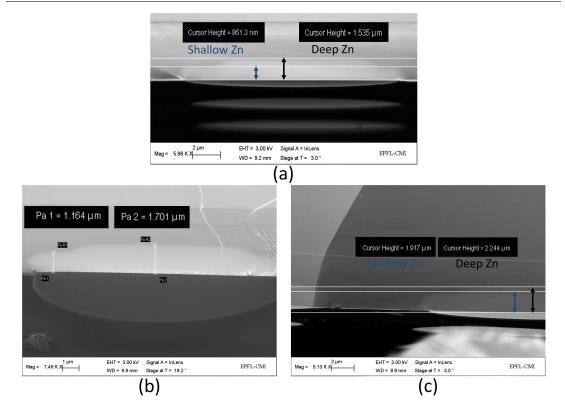

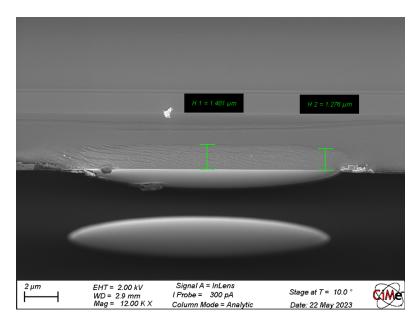

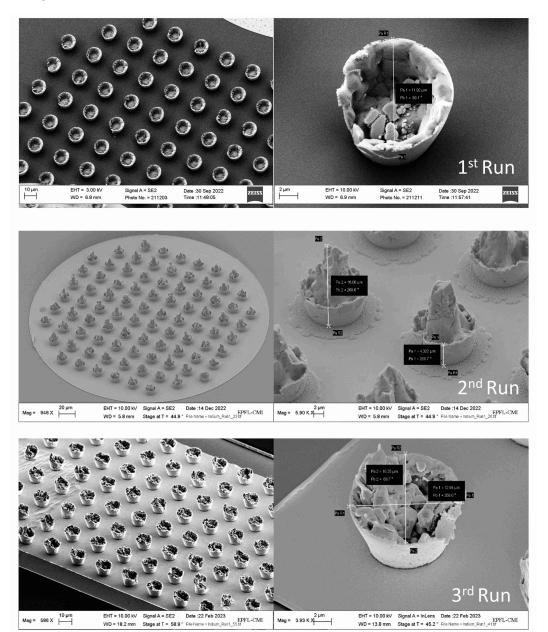

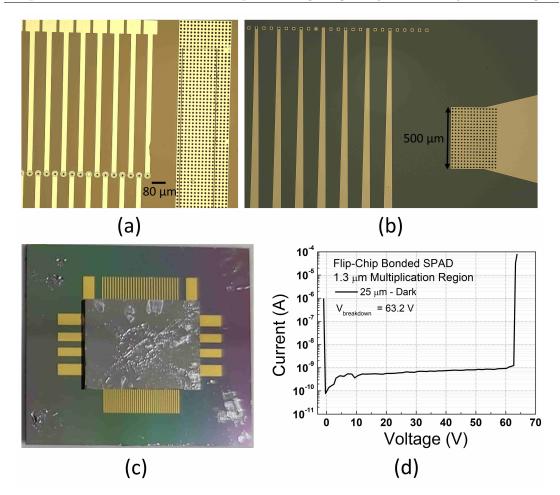

| 5.10 | An SEM image of the cross-section of a SPAD with a 10 $\mu$ m active, 2.5 $\mu$ m GR                                                                                                                                                                                                                                                                                  |    |

|      | diameter, and 1.5 $\mu m$ shallow, 2 $\mu m$ deep Zn diffusions. $\hfill \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                          | 92 |

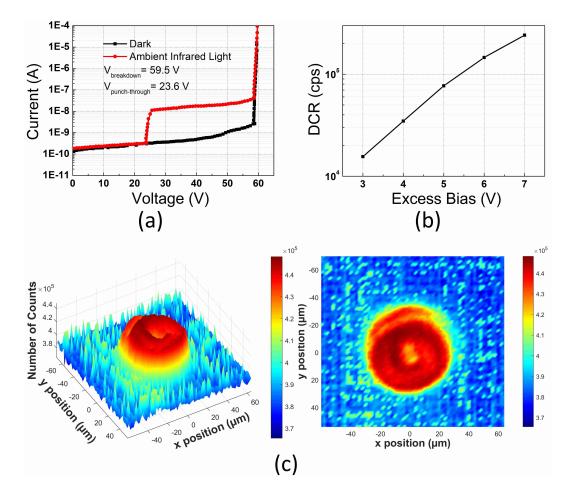

| 5.11 | (a) I-V curves of a SPAD with a 10 $\mu$ m active and 2.5 $\mu$ m GR diameter. (b) DCR measurement of a 10 $\mu$ m device at room temperature with 10 kHz gating frequency and 100 ns gate-on time. (c) Active area scanning of a SPAD with a 25 $\mu$ m active and 40 $\mu$ m GR diameter with a 1060 nm pulsed laser at 5 V <sub>ex</sub> and room                  |    |

|      | temperature                                                                                                                                                                                                                                                                                                                                                           | 93 |

| 5.12 | Double Zn diffusion profiles of devices with (a) $1.5 \mu\text{m}$ deep and $1 \mu\text{m}$ shallow diffusions, (b) $2 \mu\text{m}$ deep and $1.5 \mu\text{m}$ shallow diffusions, and (c) $2.25 \mu\text{m}$ deep and $1.75 \mu\text{m}$ shallow diffusions.                                                                                                         | 95 |

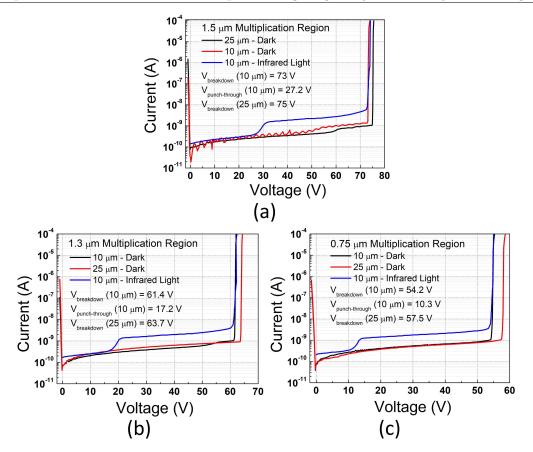

| 5.13 | I-V curves of the devices with (a) $1.5 \mu m$ multiplication region, (b) $1.3 \mu m$ multiplication region, and (c) $0.75 \mu m$ multiplication region.                                                                                                                                                                                                              | 96 |

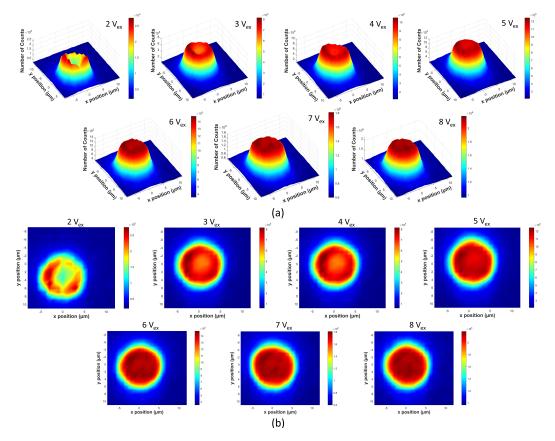

| 5.14 | Active area scanning of a 10 $\mu$ m diameter SPAD with a 1.3 $\mu$ m multiplication region shown from the (a) side view, (b) top view from 2 V <sub>ex</sub> to 8 V <sub>ex</sub> .                                                                                                                                                                                  | 97 |

| 5.15 | Gate-off time sweeps of 10 $\mu$ m diameter devices with 2.5 $\mu$ m GRs and (a) 1.5                                                                                                                                                                                                                                                                                  | -  |

|      | $\mu m$ multiplication region, (b) 1.3 $\mu m$ multiplication region, and (c) 0.75 $\mu m$                                                                                                                                                                                                                                                                            |    |

|      | multiplication region at 5 $V_{ex}$ and various temperatures                                                                                                                                                                                                                                                                                                          | 98 |

| 5.16 | The DCRs of 10 $\mu$ m and 25 $\mu$ m devices with 2.5 $\mu$ m GRs and (a) 1.5 $\mu$ m multiplication region, (b) 1.3 $\mu$ m multiplication region, and (c) 0.75 $\mu$ m multiplication |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      |                                                                                                                                                                                          | 00   |

| - 17 | region at various temperatures.                                                                                                                                                          | 99   |

| 5.17 | The PDP spectrums of 10 $\mu$ m devices with 2.5 $\mu$ m GRs and (a) 1.5 $\mu$ m multipli-                                                                                               |      |

|      | cation region, (b) 1.3 $\mu$ m multiplication region, and (c) 0.75 $\mu$ m multiplication                                                                                                |      |

|      | region at room temperature.                                                                                                                                                              | 100  |

| 5.18 | The timing histograms of 10 $\mu m$ devices with 2.5 $\mu m$ GRs and (a) 1.5 $\mu m$ multipli-                                                                                           |      |

|      | cation region, (b) 1.3 $\mu m$ multiplication region, and (c) 0.75 $\mu m$ multiplication                                                                                                |      |

|      | region at 5 $V_{ex}$ and room temperature                                                                                                                                                | 101  |

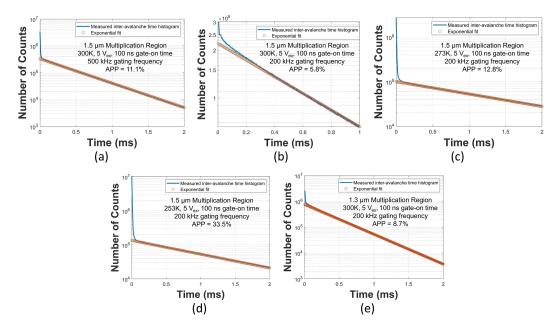

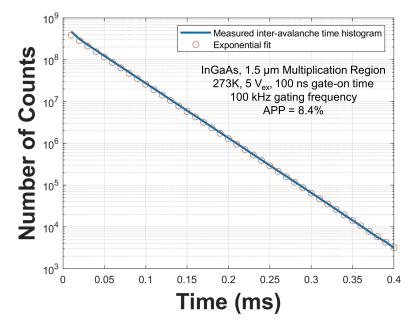

| 5.19 | The avalanche inter-arrival time histograms of a 10 $\mu m$ device with 2.5 $\mu m$ GRs                                                                                                  |      |

|      | and a 1.5 $\mu m$ multiplication region at 5 $V_{ex}$ , 100 ns gate-on time, (a) 300K and                                                                                                |      |

|      | 500 kHz, (b) 300K and 200 kHz, (c) 273K and 200 kHz, and (d) 253K and 200 kHz.                                                                                                           |      |

|      | (e) The same measurement for a 10 $\mu m$ device with 2.5 $\mu m$ GRs and a 1.3 $\mu m$                                                                                                  |      |

|      | multiplication region at 5 $V_{ex}$ , 100 ns gate-on time, 300K, and 200 kHz. $\ .\ .\ .$                                                                                                | 102  |

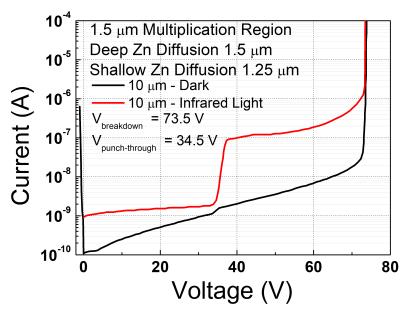

| 5.20 | (a) The SEM analysis, (b) I-V characteristics at 300K, and (c) DCR measurements                                                                                                          |      |

|      | taken at 300K, 10 kHz gating frequency, and with 100 ns gate-on time of the                                                                                                              |      |

|      | SPAD with the 1.5 $\mu m$ deep and 1.25 $\mu m$ shallow Zn diffusions                                                                                                                    | 103  |

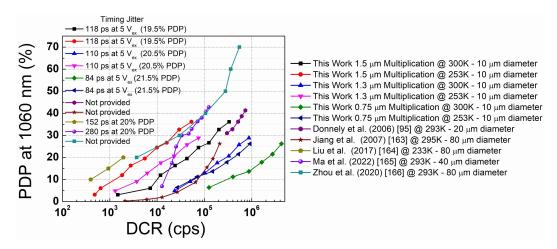

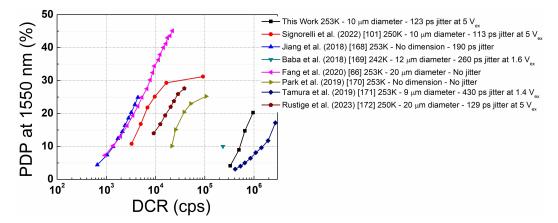

| 5.21 | The DCR, PDP, and timing jitter comparison of the proposed InGaAsP/InP SPADs                                                                                                             |      |

|      | with the state-of-the-art for 1.06 $\mu wavelength$ detection                                                                                                                            | 104  |

| 5.22 | The cross-section of the 1.7 $\mu m$ cutoff InGaAs/InP SPADs. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                        | 106  |

| 5.23 | (a) The electric field distribution and (b) the energy band diagram with and                                                                                                             |      |

|      | without the grading layer of a 10 $\mu m$ InGaAs SPAD with 1.5 $\mu m$ deep, 1.25 $\mu m$                                                                                                |      |

|      | shallow diffusion, and 2.5 $\mu m$ GR width at the breakdown voltage. $\hdots$                                                                                                           | 107  |

| 5.24 | The simulated dark I-V curve of the described 10 $\mu m$ InGaAs SPAD with 2.5 $\mu m$                                                                                                    |      |

|      | GRs at 300K                                                                                                                                                                              | 108  |

| 5.25 | (a) Hole avalanche breakdown probability distribution of the device with a 1.5                                                                                                           |      |

|      | $\mu m$ multiplication region and 0.25 $\mu m$ depth difference between Zn diffusions at                                                                                                 |      |

|      | $1V_{ex}$ , 5 $V_{ex}$ , and 9 $V_{ex}.$ (b) Hole avalanche breakdown probabilities taken at the                                                                                         |      |

|      | center and edge of the active region for various excess bias voltages                                                                                                                    | 108  |

| 5.26 | The SEM analysis of the described InGaAs with a 10 $\mu m$ diameter and 2.5 $\mu m$ GRs                                                                                                  | .109 |

| 5.27 | The I-V characteristics of the InGaAs SPAD with a 10 $\mu m$ diameter and 2.5 $\mu m$                                                                                                    |      |

|      | GRs at 300K                                                                                                                                                                              | 110  |

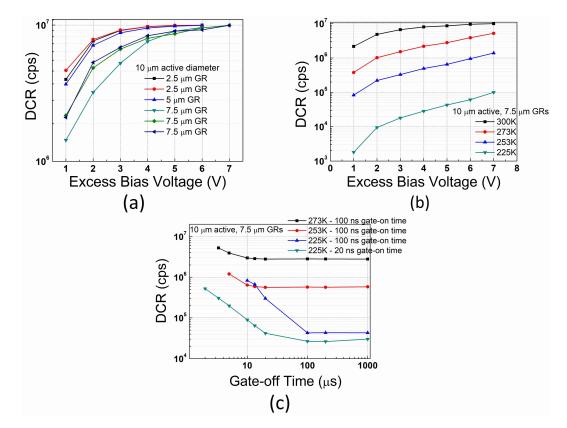

| 5.28 | (a) DCR versus $V_{ex}$ analysis of 10 $\mu m$ SPADs for various GR widths at 10 kHz                                                                                                     |      |

|      | gating with 100 ns gate-on time. (b) The DCR of a 10 $\mu m$ SPAD with 7.5 $\mu m$ GRs                                                                                                   |      |

|      | under various temperatures. (c) Gating frequency sweep of a SPAD with 7.5 $\mu m$                                                                                                        |      |

|      | GRs from 273K to 225K                                                                                                                                                                    | 111  |

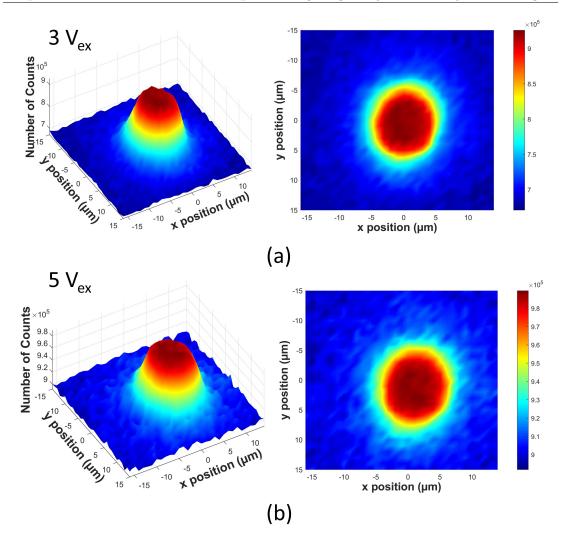

| 5.29 | The active area scanning of a 10 $\mu m$ InGaAs/InP SPAD with 7.5 $\mu m$ GRs with a                                                                                                     |      |

|      | 1550 nm pulsed laser at room temperature and (a) 3 $V_{ex}$ and (b) 5 $V_{ex}.$                                                                                                          | 112  |

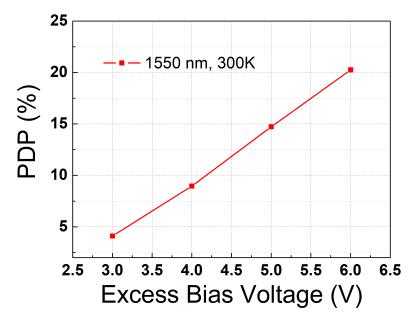

| 5.30 | The PDP measurements of a 10 $\mu m$ InGaAs/InP SPAD with 7.5 $\mu m$ GRs at 1550                                                                                                        |      |

|      | nm and room temperature for various excess bias voltages                                                                                                                                 | 113  |

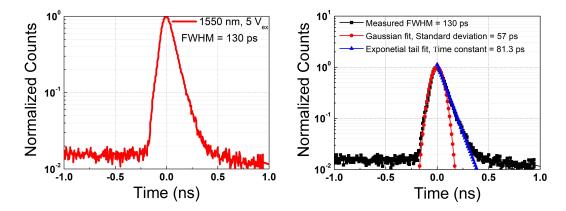

| 5.31 | The timing histogram of a 10 $\mu m$ InGaAs/InP SPAD with 7.5 $\mu m$ GRs at 1550 nm,                                                                                                    |      |

|      | room temperature and 5 <sub>ex</sub> .                                                                                                                                                   | 113  |

| 14 |

|----|

|    |

| 15 |

|    |

| 16 |

| 17 |

|    |

|    |

|    |

| 18 |

| 1  |

# List of Tables

## Acronyms

2DEG two-dimensional electron gas

APDs avalanche photodiodes

Au gold

BSI back-side-illumination

BTB band-to-band

- $C_d\;$  diode junction capacitance

- $C_p$  parasitic capacitance

$C_t$  total capacitance

**CCD** charge-coupled device

CIS CMOS Image Sensor

CMi Center of MicroNanoTechnology

CMOS complementary metal-oxide-semiconductor

cps counts per second

DCR dark count rate

DLTS deep-level transient spectroscopy

DMZn dimethylzinc

dToF direct ToF

E electric field magnitude

$E_g$  bandgap energy

ebCMOS electron-bombarded CMOS

**f** frequency

FET field-effect transistor **FGRs** floating guard rings FOV field of view FSI front-side-illumination FWHM full-width-at-half-maximum **GaAsP** gallium arsenide phosphide Ge germanium GHz gigahertz **GR** guard ring  $H_2O_2$  hydrogen peroxide H<sub>3</sub>PO<sub>4</sub> phosphoric acid HCl hydrochloric acid HHb deoxygenated hemoglobin HVNW high-voltage n-well HVPW high-voltage p-well  $I_q$  characteristic quench current In indium InGaAs indium gallium arsenide **InGaAsP** indium gallium arsenide phosphide **InP** indium phosphide iToF indirect ToF K Kelvin LEDs light emitting diodes LiDAR light detection and ranging M measured count rate **MEMS** micro-electromechanical systems

N real count rate

#### Acronyms

| NbN niobium nitride                                   |

|-------------------------------------------------------|

| NbTiN niobium titanium nitride                        |

| NFAD negative feedback avalanche diode                |

| Ni nickel                                             |

| NIR Near-infrared                                     |

| NIROT Near-infrared optical tomography                |

| nm nanometer                                          |

| O2Hb oxygenated hemoglobin                            |

| P Phosphorus                                          |

| <b>PDP</b> photon detection probability               |

| PMTs photomultiplier tubes                            |

| QDs quantum dots                                      |

| QE quantum efficiency                                 |

| <b>QKD</b> quantum key distribution                   |

| <b>R</b> <sub>d</sub> dynamic resistance              |

| $\mathbf{R}_{\mathbf{q}}$ ballast resistor            |

| <b>ROICs</b> read-out integrated circuits             |

| S switch                                              |

| <b>SACM</b> separate absorption-charge-multiplication |

| <b>SAG</b> selective area growth                      |

| SEM scanning electron microscope                      |

| Si silicon                                            |

| Si <sub>3</sub> N <sub>4</sub> silicon nitride        |

| SIMS secondary ion mass spectrometry                  |

| SiO <sub>2</sub> silicon oxide                        |

| SMU source measure unit                               |

| SNR signal-to-noise ratio                             |

#### **Chapter 0**

**SNSPDs** superconducting nanowire single-photon detectors SPADs single-photon avalanche diodes **SQUID** superconducting quantum interference device SRH Shockley-Read-Hall SWIR short-wave infrared T temperature TAT trap-assisted-tunneling TCAD Technology Computer-Aided Design TCCC time-correlated carrier counting TCSPC time-correlated single-photon counting TDCs time-to-digital converters **TESs** transition-edge sensors Ti titanium ToF time-of-flight **UBM** under bump metallization **UV** ultraviolet V<sub>b</sub> avalanche breakdown voltage  $V_{ex}$  excess bias voltage Vop operating voltage W tungsten WSi tungsten silicide **Zn** Zinc  $Zn_3P_2$  zinc phosphide

## **1** Introduction

Near-infrared (NIR) and short-wave infrared (SWIR) wavelengths offer advantageous features and contrast in imaging, where visible and thermal detection become ineffective. Thanks to their unique properties, NIR/SWIR photodetectors can be utilized in a wide range of applications, such as imaging through haze, dust, and fog [1], imaging of tissues and organs [2], hyperspectral imaging to identify moisture levels and contamination of agricultural products [3], [4], and in night vision through nightglow phenomena [5].

Single-photon detectors are a special category of photodetectors that enable the capture of individual photons and the counting of them accurately. These detectors are characterized by virtually zero readout noise and high timing accuracy, generally in the order of tens of picoseconds. If single-photon detectors only suffer from low dark noise, denoted as dark count rate, they enable Poisson-limited detection, which is why they have gained attention over the last decades in quantum imaging and quantum information science [6]–[9]. Since the last decade, many quantum information applications and quantum cryptography methods, for instance, quantum key distribution (QKD), have preferred utilizing NIR/SWIR single-photons to be able to provide secure communication [10]–[13]. However, quantum information science is not the only field that can benefit from NIR or SWIR single-photon detectors. Applications such as light detection and ranging (LiDAR) [14], [15], biomedical imaging [16], and space imaging [17] could also benefit from single-photon detectors in photon-starved scenarios or in complex time-of-flight (ToF) multi-bounce scenes. Hence, research in the field of NIR/SWIR single-photon detection is currently moving forward at a fast pace.

#### 1.1 NIR/SWIR detection and its advantages

NIR/SWIR detectors and image sensors have become increasingly important in recent years due to the unique advantages they present compared to their visible and longer wavelength infrared counterparts. Essentially, NIR covers the wavelengths between 700 nanometer (nm) and 1000 nm, and the SWIR region corresponds to the 1000 nm to 3000 nm part of the wavelength spectrum. There are many light sources that emit photons at these wavelengths.

Although the photon flux is reduced with respect to visible wavelengths, the Sun is still a photon source at NIR/SWIR. Thus, the reflected sunlight from the objects can be detected to perform 2D imaging. This is also the reason why NIR/SWIR images resemble typical images taken by photographic instruments in use nowadays. Secondly, the primary photon source may be active illumination devices, such as lasers and light emitting diodes (LEDs). In particular, lasers utilized in fiber-optic telecommunication require SWIR sensors for detection as the optical fibers have the lowest loss at these wavelengths. Besides, the overtones of molecular vibrations can be absorbed in the NIR/SWIR band, which offers signature identification of molecules that contain chemical bonds between hydrogen and oxygen, carbon, and nitrogen. Hyperspectral imaging is hereby another significant field, especially in farming. Lastly, the radiance of the night sky, which is also known as nightglow, allows night vision in SWIR. The reflected Moon and the star lights can be employed as photon sources, for instance, to do surveillance at night. In addition to discussing the photon sources, the distinct advantages of building an optical sensor for NIR/SWIR detection are listed in Fig.1.1.

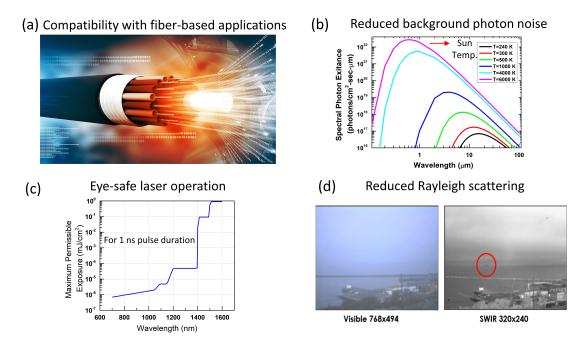

Figure 1.1: (a) Illustration of light propagation and data transmission in an optical fiber (Credits to Cadence). (b) Spectral photon exitance graphs belonging to various blackbody temperatures, including the Sun. (c) Maximum permissible exposure for eye-safe lasers for 1 ns pulse duration [18]. (d) Illustration of reduced Rayleigh scattering through images captured by a visible and a SWIR camera [19].

The first advantage of operating at NIR/SWIR wavelengths is to gain compatibility with fiberbased applications, as pictured in Fig. 1.1 (a). The standard fiber-optic telecommunication wavelengths are known to be 850 nm, 1310 nm, but mostly 1550 nm; all reside in the NIR or SWIR region. These wavelengths are chosen as they coincide with the minimum loss points for light propagation in an optical fiber. In general, a multi-mode 850 nm fiber has an attenuation of 2.5 decibel/kilometer (dB/km), and single-mode 1310 nm and 1550 nm fibers have an optical loss of 0.3 and 0.2 dB/km, respectively [20]. Since dB is a logarithmic unit, even changing the communication wavelength from 1310 to 1550 can be interpreted as an almost 50% increase in transmission distance for the same data rate. Therefore, the most popular wavelength of operation in telecommunication is 1550 nm. Any optical communication system using one of these wavelengths requires a detector at the receiver side to convert this optical information into electrical one. Given that the optical loss is significant in a fiber-optic system and that single photons are utilized in an optical fiber-based quantum communication system to obtain a secure way of transmitting information through quantum states, designing single-photon detectors with high efficiency in NIR/SWIR is vital.

The second advantage of NIR/SWIR is that, in the case of using active illumination sources, the background photon noise exerted by the Sun is reduced. Free-space applications that need to be run under daylight conditions with a photon source have performance limitations due to the noise created by the enormous number of photons coming from the sunlight. The blackbody radiation of the Sun (a 6000 K object) in terms of spectral photon exitance is indicated in Fig.1.1 (b). As can be seen, the peak wavelength of the Sun resides in the visible region, whereas the number of photons from the sunlight decreases towards the infrared wavelengths. Hence, in order to reduce the background noise of the Sun, NIR/SWIR photon sources and detectors are excellent choices.

The third advantage is to acquire eye-safe operation for active illumination sources such as lasers and LEDs. Applications making use of these light sources, especially in free space, will have much less risk of damaging the human eye. As shown in Fig. 1.1 (c), the maximum permissible exposure of an 800 nm laser, which is still safe for the human eye, is  $10^{-6}$  milijoule/centimeter<sup>2</sup> (mJ/cm<sup>2</sup>) for 1 ns pulse duration [18]. However, laser power can be increased safely by  $5 \times$  at 1100 nm,  $50 \times$  at 1300 nm, and  $10^{6} \times$  at 1550 nm as seen from the graph. Using higher laser power levels at NIR/SWIR wavelengths also results in an increase in the maximum attainable depth since the laser photons can penetrate longer distances. This means that the field of view (FOV) of an imaging system can be improved.

The last advantage of moving to the NIR/SWIR bands is the reduced Rayleigh scattering. Rayleigh scattering occurs when light interacts with particles whose size is smaller than its wavelength. Therefore, it is a wavelength-dependent phenomenon that changes inversely with the fourth power of the wavelength  $(1/\lambda^4)$ . In fact, this is the reason why the sky appears blue as the blue scatters more than the other colors. Thus, at longer wavelengths, Rayleigh scattering is less effective, which permits the light to travel more without perturbation and increases the FOV. A comparison of visible camera and SWIR camera images through the same hazy environment is provided in Fig.1.1 (d) [19]. As can be observed in these images, a visible camera cannot identify some of the objects under mist, whereas a clear vision of the shore in detail and even a ship at the farthest point of the FOV can be obtained with a SWIR camera thanks to less Rayleigh scattering. Hence, a NIR/SWIR imager provides better results through haze, which is an important property for applications doing 2D and 3D imaging.

#### 1.2 Application areas of NIR/SWIR single-photon detectors

#### 1.2.1 Light detection and ranging

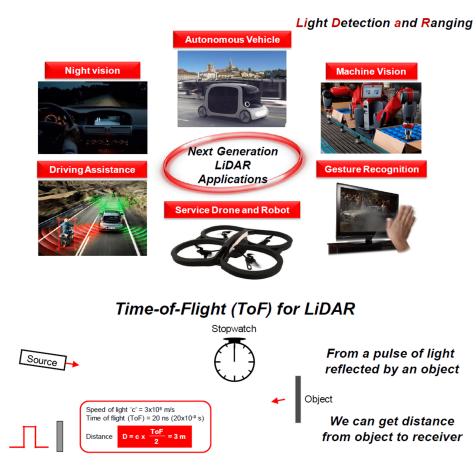

LiDAR, which allows us to obtain 3D representations of environments and to construct highresolution depth maps, has gained significant attention over the last decades. Autonomous vehicles, driving assistance, machine vision, virtual reality, robotics, and drone technologies are just some of the application areas of LiDAR, as illustrated in Fig. 1.2. The principle of depth sensing in a LiDAR system is based on recording the ToF of detected photons measured using direct and indirect methods [21]. In indirect ToF (iToF), the light source amplitude is modulated, and the phase shift between the emitted wave and reflected wave is measured to estimate the distance of an object. In order to increase the measurement range of iToF, one can decrease the frequency of the modulation, or use multiple frequencies to resolve ambiguity. This results in a trade-off between the distance, resolution, and complexity of the system. The main problem with iToF is the energy of the light source that is spread out in the period, thus creating the need for high light power to achieve reliable distance detection in the presence of high background illumination. Thus, highly collimated light can be used, like in the Bosch PLR15 telemeter, which achieves a point measurement at large distences. Or, alternatively, short distances can be used with a larger field of view [22]. Since a linear response is required due to the modulation, conventional photodiodes, or avalanche photodiodes (APDs) are preferred on the receiver side of an iToF system.

In direct ToF (dToF), typically a pulsed laser or LED is used as the illumination source. The laser is synchronized with the read-out integrated circuits (ROICs), and a kind of stopwatch starts to keep track of the time when the laser is fired. Then, the reflected light from the objects present in the surroundings is detected at the receiver side, and high time resolution ROIC translates the signal into time. Since the photons travel at the speed of light (c), the ToF information can be easily converted into distance (D) between the object and the receiver with the following formula:

$$D = c \times \frac{ToF}{2}.$$

(1.1)

As a result, according to the distance of different objects, a 3D depth map of the environment can be built based on timestamping. As shown in Fig.1.2, in a dToF LiDAR system with 20 ns timing resolution, targets that are 3 m apart from each other can be distinguished. If the timing resolution is decreased to 200 ps, the resolution in distance is increased to 3 cm, which would be a sufficient imaging resolution for most of the mentioned applications of LiDAR. Therefore, photomultiplier tubes (PMTs), single-photon avalanche diodes (SPADs) or superconducting nanowire single-photon detectors (SNSPDs) are considered for dToF imaging.

dToF LiDARs can be further divided into two categories: scanning and flash LiDARs. In a scanning LiDAR, the laser source scans the scene horizontally or vertically with the help

of mirrors or solid-state crystals, which are driven by actuators [23]–[25]. Since high laser power can be utilized for each shot and point in the FOV, high signal-to-noise ratio (SNR) can be achieved in scanning mode LiDARs. On the other hand, the dependence on the moving mechanical parts makes them bulky and can cause long-term reliability problems. Recently, micro-electromechanical systems (MEMS) based micromirrors have been integrated to address these issues and to make the system much smaller [26]. In a flash LiDAR, the whole target scene is illuminated in one shot instead of doing point-by-point scanning [27]–[29], which results in low-cost and reliable systems. In order to illuminate the FOV uniformly, an optical diffuser is used, which diverges the laser beam. Due to this light diffusion, laser power detected by the pixel array is weakened, which degrades the SNR and the resolution of the system over long distances. Yet, flash LiDARs are reliable systems for short-range applications.

Since LiDAR applications arise outdoors, the major problem becomes ambient Sun light, which introduces shot noise and false detections. However, at NIR/SWIR wavelengths, this problem becomes less of a concern thanks to the reduced background photon noise, as discussed. Similarly, to be able to use higher power for eye-safe lasers in the NIR/SWIR bands, the range and resolution of the LiDAR system can be improved as well.

Figure 1.2: Applications and operation principles of LiDAR.

#### 1.2.2 Quantum cryptography

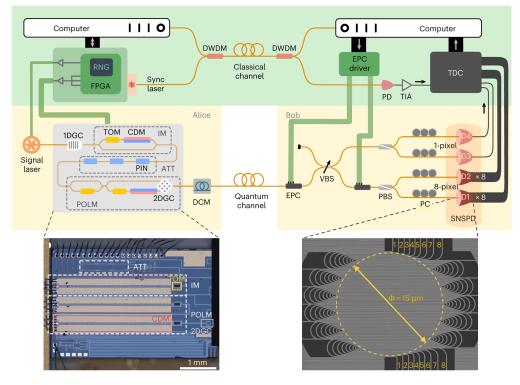

Quantum cryptography is one of the most interesting and popular applications of quantum communication, which focuses on how to protect information in communication channels against eavesdropping. In one embodiment, known as QKD, one uses the quantum states of the photons to transfer information between two sides, possibly far from each other. Thanks to the quantum no-cloning phenomenon, these two individuals can determine if an outsider is trying to access the information in their communication link [30]. OKD systems can be implemented in free space, from the Earth to a satellite, or with optical fibers between two communication centers. Free space systems are beneficial to cover longer distances, such as in building an intercontinental network. However, their performance will be limited due to background noise coming from the sunlight. Conversely, fiber-based QKD offers reliable and stable operation regardless of the environmental conditions and the ability to use alreadyinstalled telecommunication infrastructure, but they cannot cover very long distances because of the fiber losses. Eventually, a hybrid system, which is composed of both free space and fiberbased communication, is inevitable in order to reach many users separated by long distances. With the latest technological advances, a 830 km fiber-based OKD link [31], and a hybrid 4600 km QKD system, which covers 2600 km in free space and 2000 km with fibers on the ground, have been established [32]. These demonstrations prove that secure communication and the internet for everyone is feasible in the near future. Another important parameter for a QKD framework is the key generation rate. To be able to satisfy the need for high data rates in some applications and to reach numerous users in the same network, high key generation rates are demanded. A typical QKD system can achieve a kilobits/second key rate, but recently, a record of 115.8 megabits/second key generation rate has been reported over a 10 km standard optical fiber, where the network also distributes keys over 328 km of low-loss fibers [33].

QKD systems demand robust and bright photon sources to generate a series of single photons since the purity and reliability of photons possess great importance. Hereby, single-photon detectors with high detection efficiencies have become another key element for these systems. Regarding the operation wavelength, 1550 nm has turned out to be more attractive as it gives compatibility to use existing telecommunication networks and to perform the process in daylight with much less background noise, which also leads to facilitating hybrid fiberbased and free space platforms. Most of the demonstrated QKD systems at 1550 nm utilize SNSPDs thanks to their very low noise and above 80% detection efficiency [31], [33]–[35]. A QKD system utilizing SNSPDs for high key generation rate at 1550 nm is presented in Fig.1.3 [33]. However, the necessity to cool these devices down to 4 Kelvin (K) appears to be the bottleneck for scalability, portability, and their integration into real user networks. Hence, indium gallium arsenide (InGaAs)/indium phosphide (InP) based SPADs, which can provide 40%-50% detection efficiency and can be operated with a thermoelectric cooler to achieve low dark counts, have been experimented with for their integration with QKD systems as well [32], [36]–[38]. As a result, developing single-photon detectors that can function near room temperature with high detection rates is critical for the achievability of secure communication in the form of QKD, whereas timestamping and timing resolution are not crucial parameters for this application.

Figure 1.3: A QKD system, which is implemented for high key generation rate at 1550 nm, where 8 pixels SNSPD was used as the detector at the receiver side [33].

#### 1.2.3 NIR optical tomography

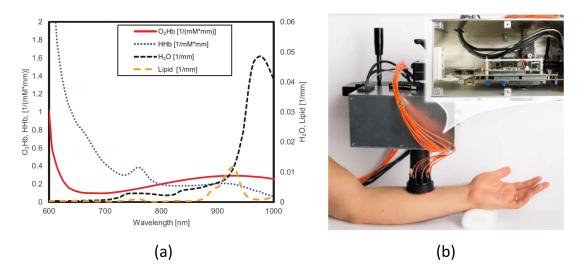

Near-infrared optical tomography (NIROT), also called diffuse optical tomography, is an important subdomain of biomedical imaging that focuses on monitoring soft tissues like the brain or the breasts. In the human body, water and lipids are known to be the most common absorbers of light. In fact, these substances are reasonably transparent between 200 nm and 900 nm wavelengths. Conversely, for these wavelengths, hemoglobin, which is the blood cell that carries oxygen to the organs and tissues, becomes the main absorber in the forms of oxygenated hemoglobin ( $O_2Hb$ ) and deoxygenated hemoglobin (HHb). However, the absorption of hemoglobin drops significantly between 650 nm and 900 nm, as depicted in Fig.1.4 (a) [39]. For this reason, 650 nm to 900 nm wavelengths are often defined as the biological optical window, where the light can penetrate deep inside the tissue (a few centimeters) and enable imaging.

In the case of less light absorption, scattering mechanisms play a role in determining light's journey. A high number of scattering events result in diffusive light in mediums like human tissues. Diffusive light can be modeled by the diffusion equation, which explains the angular dependency of the light intensity [40]. Hence, in practice, when a tissue is illuminated with a light source, the backscattered photons from the surface can be collected to construct

tomographic images and calculate the concentration of hemoglobin and the other absorbers. Eventually, measuring the oxygenation would be very beneficial in cancer treatments or preventing brain injuries in prematurely born infants.

In a typical NIROT setup, as can be seen in Fig.1.4 (b), optical probes are attached to the surface of a tissue for illumination [41]. The backscattered photons are then directed to a detector array via a lens. However, due to the limited surface area, the number of sources and detectors become limited, which is not desirable to increase and acquire more information from such a diffusive medium. Therefore, time-domain measurements have been integrated into NIROT systems to enhance the amount of information that can be obtained [16], [41], [42]. With the ToF information, the tissue scattering coefficient can be calculated, which also facilitates predicting precisely the concentrations of hemoglobin and other substances. Given that PMTs and SPADs can provide timing information based on the time-correlated single-photon counting (TCSPC) method and can operate at room temperature, they are mostly the preferred photodetector types, except that SPADs can be fabricated in large pixel arrays, which improves the spatial resolution of NIROT systems.