# X-HEEP: An Open-Source, Configurable and **Extendible RISC-V Microcontroller for the Exploration of Ultra-Low-Power Edge Accelerators**

Simone Machetti, Pasquale Davide Schiavone, Thomas Christoph Müller, Miguel Peón-Quirós, David Atienza

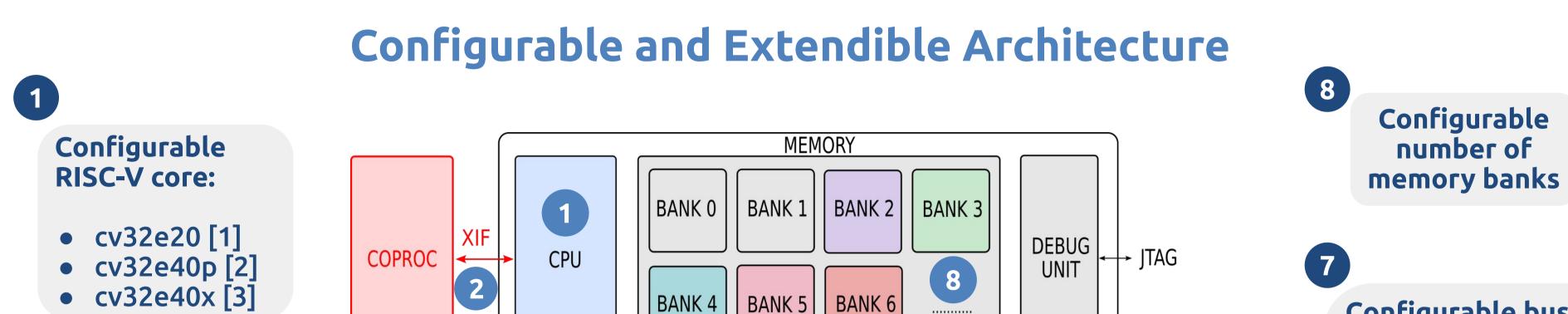

## <u>X-HEEP: eXtendible Heterogeneous Energy Efficient Platform</u>

[1] Low-power, 32-bit, in-order RISC-V core with a 2-stage pipeline that implements RV32[E|I][M]C instruction set architecture. [2] High-performance, 32bit, in-order RISC-V core with a 4-stage pipeline that implements RV32IMFC[Xpulp] instruction set architecture. [3] High-performance, 32-bit, in-order RISC-V core with a 4-stage pipeline that implements the

RV32[I,E][M|Zmmul][A]Zca\_Zcb\_Zcmp\_Zcmt[Zba\_Zbb\_Zbb\_Zbb\_Zbc\_Zbs]ZicntrZihpmZicsrZifencei[X] instruction set architecture and offers extensions through the CORE-V-XIF interface.

# **<u>FPGA</u>: Fully-virtualized Platform for Healthcare Applications**

## **XILINX**<sub>®</sub>

### Implementation and Features

# Configurable bus • One-at-a-time • Fully-connected Configurable bus • Contiguous Interleaved

#### **SW IMPLEMENTATION** $\rightarrow$ HAL and FreeRTOS

<u>CONFIGURATION</u>  $\rightarrow$  SystemVerilog templates

thanks to customizable parameters

Automatic tools to configure the RTL code of X-HEEP

• Includes an hardware abstraction layer (HAL) for easy access to peripherals' functionalities

**Design Flow Support**

• Supports FreeRTOS to enable concurrent execution and enhance resource management

#### **SIMULATION AND HW IMPLEMENTATION** → FuseSoC

Automatic tool to generate the required script to simulate and implement the design

#### Supported tools:

- Simulation: Verilator, Questasim, etc.

- ASIC: Design Compiler, Innovus, etc.

- FPGA: Vivado, etc.

### <u>Useful Links</u>

#### **Open-source Repositories**

**FPGA-HW**

X-HEEP

**FPGA-SW**

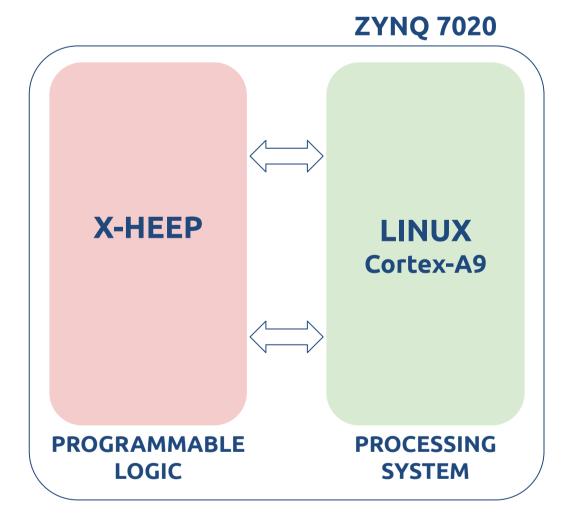

#### **IMPLEMENTATION** $\rightarrow$ Zynq 7020 on Pynq-Z2 board

X-HEEP implemented on the programmable logic side communicates with the Linux system on the processing system side

**FULL VIRTUALIZATION**  $\rightarrow$  No off-board I/O connectivity required

All peripherals virtualized under Linux

**Examples: JTAG** virtualized towards Linux GPIOs, **UART** virtualized towards a Linux serial port, FLASH virtualized on the board DRAM, etc.

#### **ESTIMATIONS** $\rightarrow$ **Performance and energy**

• **Performance estimation** through dedicated performance counters • Energy estimation based on TSMC 65nm CMOS technology

#### <u>USER INTERACTION</u> → Jupyter notebook

Dedicated Python class to support interaction through Jupyter notebook

<u>X-HEEP</u>  $\rightarrow$  Main repository of X-HEEP https://github.com/esl-epfl/x-heep

<u>FPGA</u>  $\rightarrow$  Repositories of the FPGA emulation platform https://github.com/esl-epfl/x-heep-femu https://github.com/esl-epfl/x-heep-femu-sdk

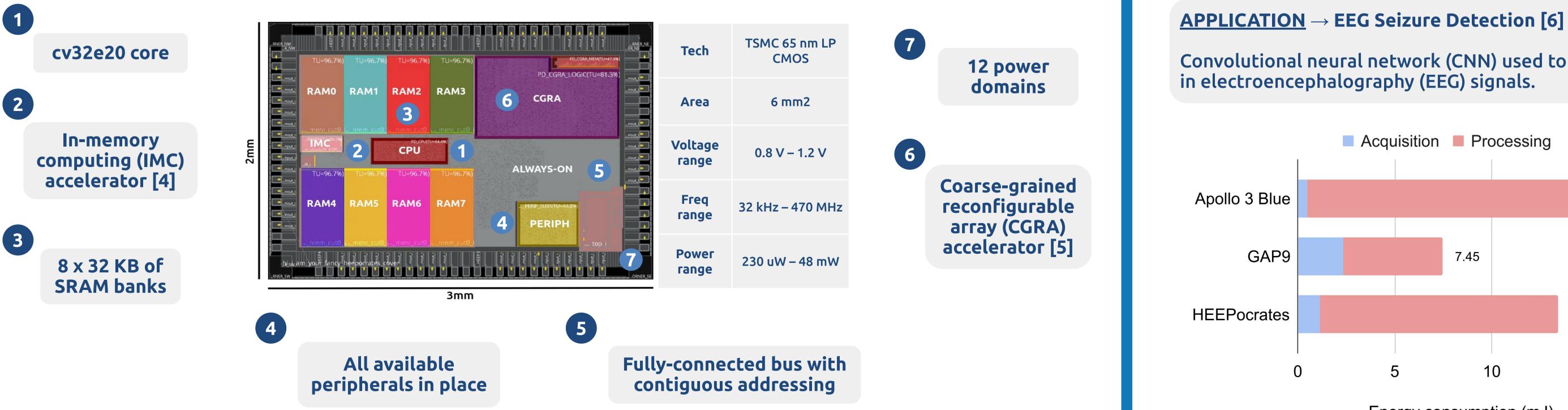

### **<u>HEEPOCRATES</u>: X-HEEP-based Chip for Healthcare Applications**

### Post-PnR Layout and Silicon Characterization

[4] William Andrew Simon, Yasir Mahmood Qureshi, Marco Rios, Alexandre Levisse, Marina Zapater, and David Atienza. 2020. Blade: an in-cache computing architecture for edge devices. IEEE Transactions on Computers, 69, 9, 1349–1363.

[5] Loris Duch, Soumya Basu, Rubén Braojos, David Atienza, Giovanni Ansaloni, and Laura Pozzi. 2016. A multi-core reconfigurable architecture for ultra-low power bio-signal analysis, 416–419.

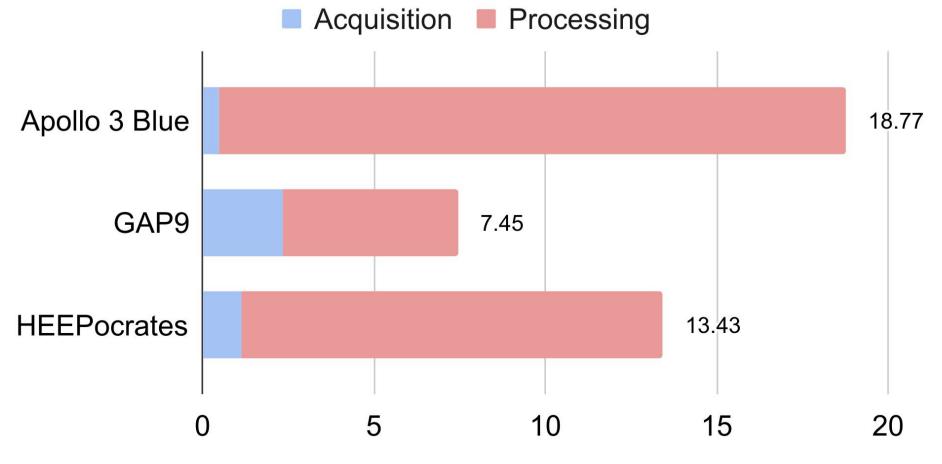

Convolutional neural network (CNN) used to detect seizures in electroencephalography (EEG) signals.

**Energy Consumption**

#### Energy consumption (mJ)

[6] Catalina Gómez, Pablo Arbeláez, Miguel Navarrete, Catalina Alvarado-Rojas, Michel Le Van Quyen, and Mario Valderrama. 2020. Automatic seizure detection based on imaged-eeg signals through fully convolutional networks. Scientific reports, 10, 1, 1–13.