Thèse n°10693

# EPFL

### Front-End Circuits for Radiation-Hard Monolithic CMOS Sensors targeting High-Energy Physics Applications

Présentée le 13 octobre 2023

Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Francesco PIRO

Acceptée sur proposition du jury

Prof. I.-C. Benea-Chelmus, présidente du jury Prof. E. Charbon, Dr W. J. Snoeys, directeurs de thèse Dr R. Dinapoli, rapporteur Dr F. Hartmann, rapporteur Prof. K. Choo, rapporteur

École polytechnique fédérale de Lausanne

2023

Non chi comincia ma quel che persevera. – Leonardo Da Vinci

## Acknowledgements

As I approach the end of my PhD, there are countless people to whom I feel grateful, even though a few lines are not enough to express all my gratitude.

First and foremost, I owe a great deal of gratitude to Dr. Walter Snoeys who, after already working together for almost two years, put trust in me and allowed me to continue working with him as a doctoral student. I particularly admire his creativity and positive attitude. I also feel grateful to Prof. Edoardo Charbon, who gave me the privilege to be part of his laboratory, for the fruitful discussions and his exceptional availability over these years.

Special thanks go also to Thanushan Kugathasan for his continuous technical guidance and, in particular, moral support.

Throughout these years, I had the fortune of sharing the office with a lot of amazing people: Ivan Berdalovic, Roberto Cardella, Leyre Flores, Wenjing Deng, Geun Hee Hong, Leonardo Cecconi, Dominik Dobrievic. Thank you all for creating the best work environment imaginable and for all the laughs that made the loooong workdays more enjoyable.

Thanks also to my current office mates who kept me sane during the final stretch of my PhD: João for his "constructive criticism", the "French ministry of Baguettes" Corentin Lemoine for brightening our breaks with his cakes, and Simone Emiliani who actually kindly read this manuscript and helped me to ensure good quality risking severe neurological damages... I really appreciated.

I would also like to thank my former colleagues from UNIGE: Lorenzo Paolozzi, Pierpaolo Valerio, Emanuele Ripiccini, and Fulvio Martinelli, with whom this amazing experience in Geneva started and who continue to provide valuable advice.

Un ringraziamento speciale va ai miei amici di sempre: Emiliano, Dario, Toni, Gianluigi e Marilena su cui posso sempre contare, e ogni qualvolta ci incontriamo, riescono sempre a farmi sentire a casa, come se il tempo non fosse mai trascorso, nonostante le enormi distanze che ci separano.

Grazie a Mamma, Papà e alle mie sorelle, per essermi stato accanto ad ogni passo e farmi sentire amato ogni giorno.

Geneva, 5 September 2023

Francesco Piro

### Abstract

Monolithic pixel sensors integrate the sensor matrix and readout in the same silicon die, and therefore present several advantages over the more largely used hybrid detectors in highenergy physics. They offer an easier detector assembly, lower cost, lower material budget and lower power consumption. This work has been carried out in the EP-R&D program at CERN and its main goal is the development of analog readout solutions for monolithic sensors able to cope with the requirements of future high-energy physics experiments.

The optimization of an analog front-end amplifier integrated in a large-scale monolithic sensor targeting the requirements of the outer layer of the ATLAS Inner Tracker upgrade is shown. The chip is manufactured in the TowerJazz 180 nm imaging process. The sensor is designed with a small collection electrode offering therefore a small capacitance (< 5 fF), key feature to achieve high analog performance. Furthermore, it implements a process modification which enhances the charge collection properties of the sensor and its radiation tolerance. The chip has been extensively tested and the characterization results relevant to the front-end circuit are also presented.

To cope with the demand of higher granularity and lower material budget of future highenergy physics experiments, the possibility of moving future monolithic developments in a smaller node technology has been explored in the framework of the EP-R&D program. One of the main targeted applications is the ALICE Inner Tracking System upgrade. The 65 nm imaging technology from the Tower Partners Semiconductor Co. was considered as a possible candidate. Several test structures have been therefore developed to validate this technology for HEP applications. Amongst these, an analog test structure allows to monitor the analog behavior of the sensor and its charge collection properties. Another prototype, instead, allows to characterize the sensor with a fully-featured readout, composed of an analog front-end amplifier and discriminator followed by a digital logic. This work presents the design of these structures and discusses their main characterization results.

Another important target of the R&D effort is to prove the possibility of realizing wafer-scale monolithic sensors with the stitching technique offered by the aforementioned 65 nm process. Large-scale sensors facilitate the coverage of large sensitive areas and, if able to cover the entire sensitive area of a detector, eliminate the need of tiling multiple chips achieving a significant reduction of the material budget. The upgrade of the ALICE Inner Tracking System is based on

this idea. Two wafer-scale sensors have been developed to gain fundamental knowledge and experience on the stitching technique for particle detection. A primary concern in designing such large systems is to obtain a high yield. The two prototypes feature different readout architectures and cope differently with this issue. An overview on the main design aspects of these two structures is given in this manuscript.

Key words: High-energy physics, vertex detectors, Monolithic Active Pixel Sensors, radiationhardness, front-end electronics.

## Résumé

Les capteurs monolithiques à pixels intègrent la matrice sensible et l'électronique de lecture dans la même puce en silicium. De ce fait, ils possèdent plusieurs caractéristiques avantageuses pour leur utilisation en physique des hautes énergies en comparaison aux plus répandus capteurs hybrides. Ils sont plus faciles à assembler, moins couteux, ont un plus faible budget matière et une consommation plus faible. Ce travail, réalisé dans le cadre du programme EP-R&D du CERN, a pour objectif principal le développement d'une électronique de lecture analogique pour les capteurs monolithiques capable de répondre aux besoins des futures expériences en physique des hautes énergies.

L'optimisation du front-end analogique intégré dans un capteur monolithique de grande taille, répondant aux exigences de la couche externe de la mise à niveau du tracker interne d'ATLAS est présentée. Cette puce est fabriquée dans le processus d'imagerie TowerJazz 180 nm. Le capteur est conçu avec une petite électrode de collection présentant donc une faible capacité (< 5 fF), une caractéristique clé pour atteindre des performances analogiques élevées. En outre, elle inclut une modification du processus de fabrication qui améliore à la fois les propriétés de collection de charge du capteur mais aussi sa radio-tolérance. La puce a fait l'objet de mesures approfondies et les résultats de la caractérisation du front-end sont également présentés.

Pour répondre aux besoins des futures expériences de physique des hautes énergies tels que la réduction de la taille des pixels ou la diminution du budget matière, la possibilité d'utiliser un nœud technologique plus fin a été explorée dans le cadre du programme EP-R&D. L'une des principales applications visées est la mise à niveau du tracker interne d'ALICE. La technologie d'imagerie 65 nm de Tower Partners Semiconductor Co. a été étudié en tant que candidat. Plusieurs structures de test ont donc été développées et fabriquées pour valider cette technologie pour les applications en physique des hautes énergies. Parmi celles-ci, une structure de test analogique permet de caractériser le comportement analogique du capteur et ses propriétés de collecte de charges. Un autre prototype permet quant à lui de caractériser le capteur via une chaine de lecture complète, composée de l'amplificateur et du discriminateur analogiques, mais également de la logique numérique. Ce travail présente la conception de ces structures de test et les résultats de leur caractérisation.

Un autre objectif important de la R&D est de prouver la possibilité de réaliser des capteurs monolithiques de très grande taille avec la technique du stitching offerte par la technologie 65nm susmentionné. Ces capteurs de très grande taille facilitent la couverture de larges zones et, si leur taille permet de couvrir la totalité de la zone sensible d'un détecteur, il n'est plus nécessaire d'assembler plusieurs puces, ce qui permet une réduction significative du budget matière. La mise à niveau du tracker interne d'ALICE est basée sur cette idée. Deux prototypes de capteur très grande taille ont été mis au point pour acquérir des connaissances et de l'expérience sur la technique de stitching et sur son utilisation pour la détection des particules. L'une des principales préoccupations lors de la conception de systèmes de cette taille est d'obtenir un taux de succès élevé lors de la fabrication. Les deux prototypes sont dotés d'architectures de lecture différentes et répondent différemment à ce problème. Une vue d'ensemble des principaux aspects de la conception de ces deux structures est présentée dans ce manuscrit.

Mots clefs : Physique des hautes énergies, détecteur de vertex, détecteur monolithique à pixels actifs, radio-tolérance, électronique front-end.

## Contents

| Ac | knov  | wledge  | ments                                                        | i    |

|----|-------|---------|--------------------------------------------------------------|------|

| Ał | ostra | ct (Eng | lish/Français)                                               | iii  |

| Li | st of | figures | 3                                                            | xi   |

| Li | st of | tables  |                                                              | xvii |

| 1  | Intr  | oducti  | ion                                                          | 1    |

|    | 1.1   | Motiv   | vation and background                                        | . 2  |

|    | 1.2   | Requi   | irements of pixel sensors for particle tracking              | . 3  |

|    |       | 1.2.1   | Position resolution                                          | . 3  |

|    |       | 1.2.2   | Multiple scattering                                          | . 4  |

|    |       | 1.2.3   | Impact parameter resolution                                  | . 4  |

|    |       | 1.2.4   | Momentum resolution                                          | 6    |

|    |       | 1.2.5   | Readout electronics requirements                             | 6    |

|    | 1.3   | Challe  | enges for future HEP experiments at the LHC                  | . 7  |

|    |       | 1.3.1   | ATLAS Inner Tracker upgrade                                  | . 9  |

|    |       | 1.3.2   | ALICE Inner Tracking System upgrade                          | . 11 |

|    |       | 1.3.3   | Other applications                                           | . 13 |

|    | 1.4   | Thesi   | s contributions                                              | . 13 |

|    | 1.5   | Manu    | script organization                                          | . 14 |

| 2  | Fun   | damer   | ntals of pixel sensors                                       | 17   |

|    | 2.1   | Detec   | ction of particles in silicon                                | . 17 |

|    |       | 2.1.1   | Energy loss of charged particles                             | . 17 |

|    |       | 2.1.2   | Interaction with electromagnetic radiation                   | . 19 |

|    |       | 2.1.3   | Charge generation                                            | 20   |

|    |       | 2.1.4   | Charge transport                                             | 21   |

|    |       | 2.1.5   | P-n junction                                                 | 21   |

|    |       | 2.1.6   | Signal formation                                             | . 24 |

|    |       | 2.1.7   | Radiation effects in the sensor - Non ionizing energy losses | . 25 |

|    | 2.2   | Hybri   | d pixel sensors                                              | . 26 |

|    | 2.3   | Mono    | olithic active pixel sensors                                 | . 27 |

#### Contents

|    | 2.4    | Readout electronics                                                       | 28  |

|----|--------|---------------------------------------------------------------------------|-----|

|    |        | 2.4.1 Noise sources                                                       | 30  |

|    |        | 2.4.2 Charge sensitive amplifier                                          | 31  |

|    |        | 2.4.3 Importance of high Q/C                                              | 33  |

|    |        | 2.4.4 Radiation effects on the electronics - Ionizing radiation           | 34  |

| 3  | Dev    | velopments in the TowerJazz 180 nm imaging technology                     | 37  |

|    | 3.1    | Sensor technology                                                         | 38  |

|    |        | 3.1.1 The standard TowerJazz 180 nm process                               | 38  |

|    |        | 3.1.2 The modified TowerJazz 180 nm process                               | 39  |

|    | 3.2    | Analog front-end                                                          | 40  |

|    | 3.3    | The MALTA2 chip                                                           | 49  |

|    | 3.4    | Front-end characterization                                                | 50  |

|    | 3.5    | Conclusions                                                               | 57  |

| 4  | Dev    | elopments in the TPSCo 65 nm imaging technology                           | 59  |

|    | 4.1    | Sensor technology                                                         | 60  |

|    | 4.2    | 0                                                                         | 61  |

|    |        | 4.2.1 Characterization                                                    | 65  |

|    | 4.3    | Digital pixel test structure                                              | 71  |

|    |        | 4.3.1 Front-end                                                           | 72  |

|    |        | 4.3.2 Digital readout                                                     | 80  |

|    |        | 4.3.3 Chip overview                                                       | 82  |

|    |        | 4.3.4 Characterization                                                    | 83  |

|    | 4.4    | Conclusions                                                               | 90  |

| 5  | Des    | sign of monolithic stitched sensors in the TPSCo 65 nm imaging technology | 93  |

|    | 5.1    | Stitching                                                                 | 94  |

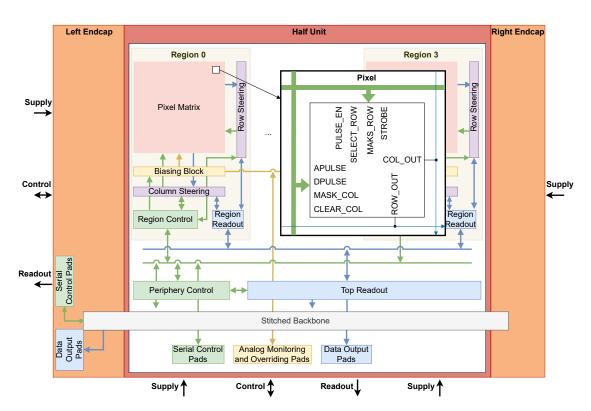

|    | 5.2    | MOSS - MOnolithic Stitching Sensor                                        | 95  |

|    |        | 5.2.1 Front-end implementation                                            | 95  |

|    |        | 5.2.2 In-pixel digital logic                                              | 97  |

|    |        | 5.2.3 Architecture                                                        | 98  |

|    | 5.3    | MOST - MOnolithic Stitching sensor with Timing                            | 103 |

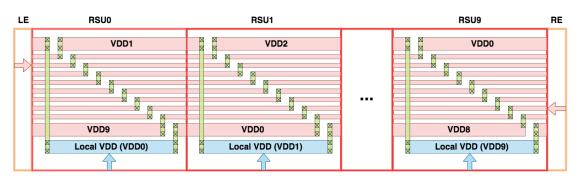

|    |        | 5.3.1 Front-end implementation                                            | 104 |

|    |        | 5.3.2 Digital readout                                                     | 105 |

|    |        | 5.3.3 Power gating                                                        | 107 |

|    |        | 5.3.4 Architecture                                                        | 109 |

|    | 5.4    | Summary                                                                   | 112 |

| 6  | Con    | nclusions and outlook                                                     | 115 |

| Cł | nip ga | allery                                                                    | 119 |

| Bi | bliog  | graphy                                                                    | 123 |

|    | - C    |                                                                           | -   |

|    |        |                                                                           |     |

viii

Contents

**Curriculum Vitae**

## List of Figures

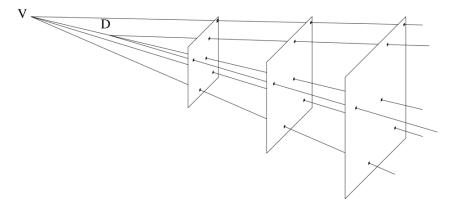

| 1.1 | Topology of a short-lived particle decay. V indicates the primary vertex whereas D the decay or secondary vertex. Three detector planes are used for track recon-               |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | struction [9]                                                                                                                                                                   | 2  |

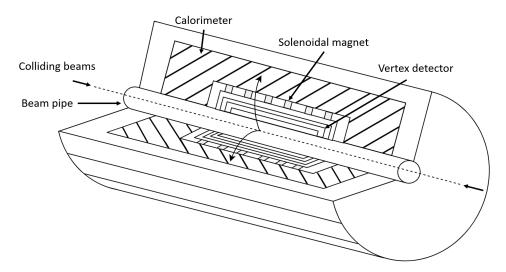

| 1.2 | Schematic structure of a high-energy physics detector.                                                                                                                          | 3  |

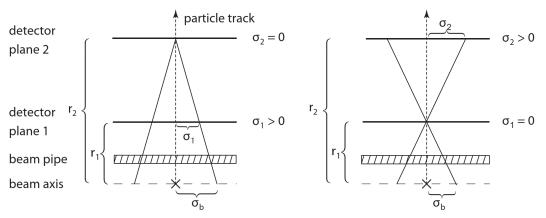

| 1.3 | Simplified two-layer vertex detector. The layers are cylindrically arranged at distances r1 and r2 and have position resolutions $\sigma_1$ and $\sigma_2$ in the plane perpen- | _  |

| 1.4 | dicular to the beam [12]                                                                                                                                                        | 5  |

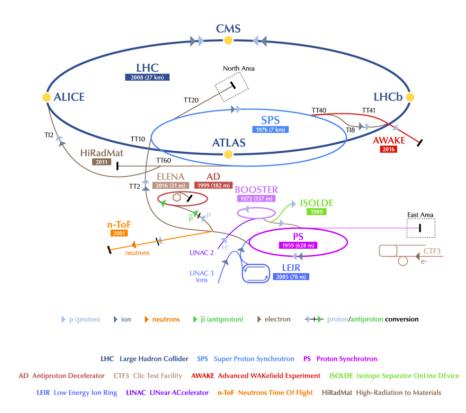

|     | [19]                                                                                                                                                                            | 7  |

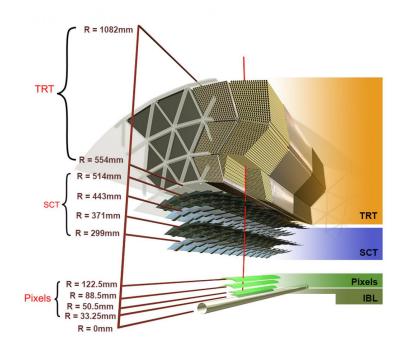

| 1.5 | Structure of the ATLAS Inner Detector [28]                                                                                                                                      | 9  |

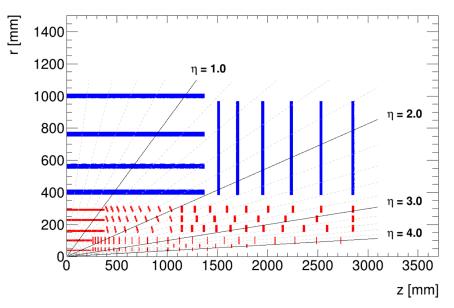

| 1.6 | Schematic view of an ATLAS ITk quadrant with pixel sensors shown in red and                                                                                                     |    |

|     | microstrip sensors shown in blue.                                                                                                                                               | 10 |

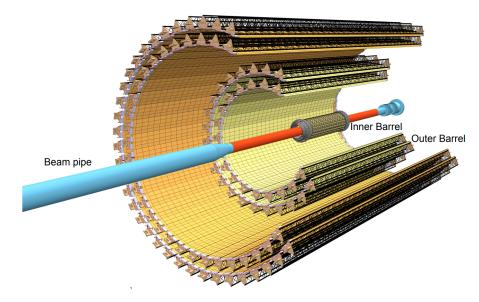

| 1.7 | Schematic view of an ALICE ITS layout [31].                                                                                                                                     | 11 |

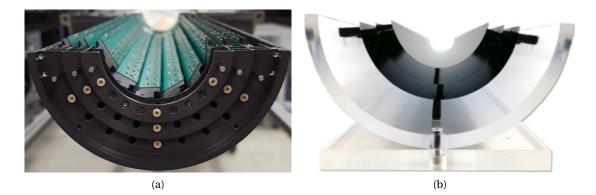

| 1.8 | Picture of a) the Inner Barrel of the current ALICE ITS b) the dummy silicon                                                                                                    |    |

|     | model for the upgrade of the Inner Barrel of the ALICE ITS.                                                                                                                     | 12 |

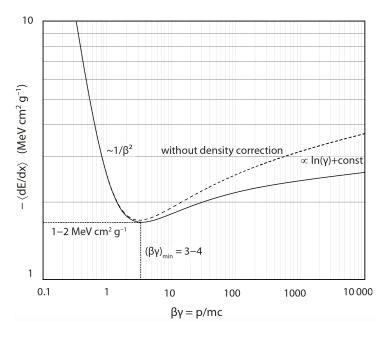

| 2.1 | Stopping power of pions in silicon as a function of the normalized momentum                                                                                                     |    |

|     | [12]                                                                                                                                                                            | 18 |

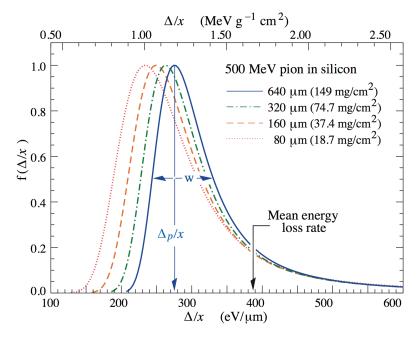

| 2.2 | Probability density functions $f(\Delta/x)$ of energy loss ( $\Delta$ ) for 500 MeV pions in silicon of different thicknesses (x), normalized to unity at the most probable     |    |

|     | value [47].                                                                                                                                                                     | 19 |

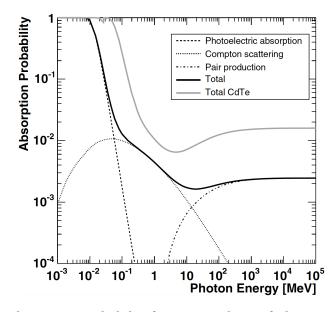

| 2.3 | Photon absorption probability for a $300 \mu m$ layer of silicon or cadmium telluride (CdTe) as function of the photon energy. The contributions from the different             |    |

|     | processes are indicated for the case of silicon [9].                                                                                                                            | 20 |

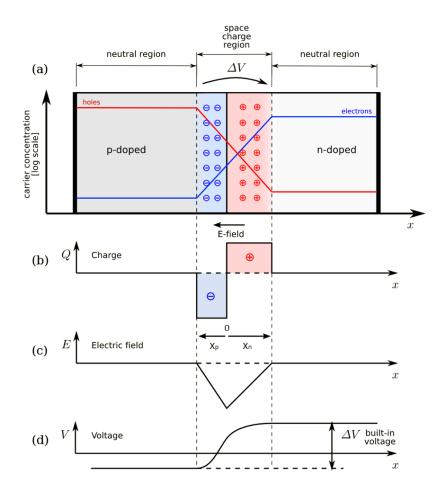

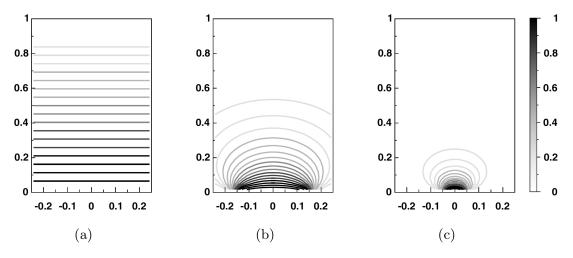

| 2.4 | The p-n junction: a) structure b) space charge density c) electric field distribution                                                                                           | 22 |

| 2.5 | and d) potential distribution [54]                                                                                                                                              | 22 |

| 2.5 | trode width of b) 1/3 and c) 1/10 of the sensor thickness, arbitrarily set to 1                                                                                                 |    |

|     | [9]                                                                                                                                                                             | 24 |

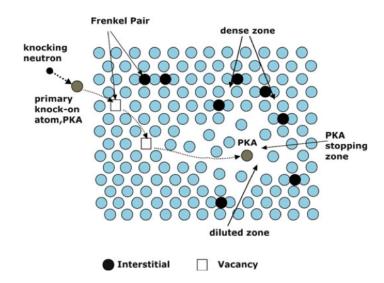

| 2.6 | Example of defects in silicon generated by impinging high-energy neutrons [56].                                                                                                 | 25 |

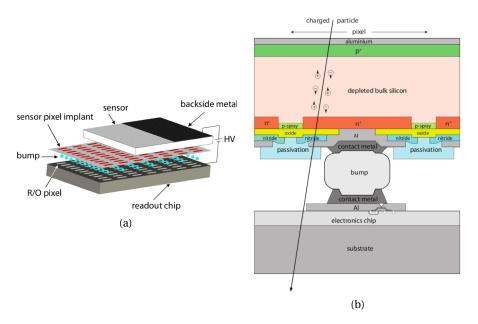

| 2.7 | Hybrid pixel sensor: a) cut-away view and b) single pixel cell [58].                                                                                                            | 26 |

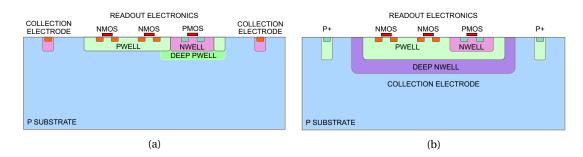

| 2.8 | Cross section of a MAPS: a) small and b) large collection electrode design                                                                                                      | 27 |

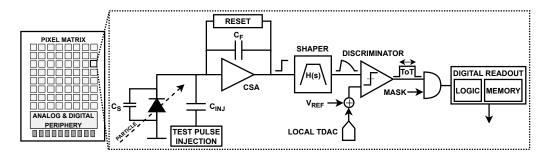

| 2.9 | Typical readout scheme used in pixel sensors.                                                                                                                                   | 28 |

|     |                                                                                                                                                                                 |    |

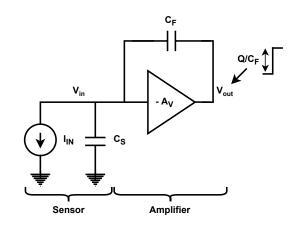

| 2.10 | Basic principle of a CSA                                                                                                                                                                                                        | 31 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

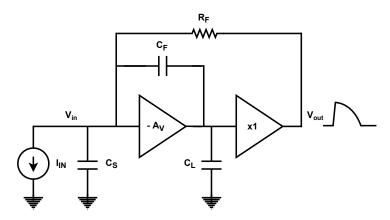

| 2.11 | CSA with reset resistor and output buffer                                                                                                                                                                                       | 32 |

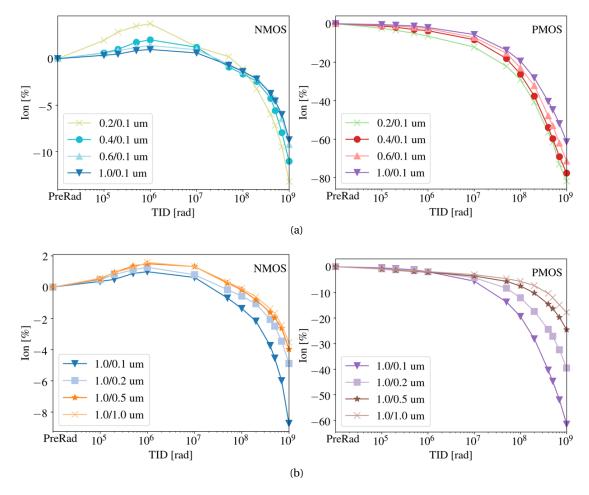

| 2.12 | Variation of $I_{ON}$ ( $V_{GS,DS} = 1.2V$ ) with TID for NMOS and PMOS transistors with<br>(a) a length of 0.1µm and different widths (b) a width of 1µm and different                                                         |    |

|      | lengths [76]                                                                                                                                                                                                                    | 35 |

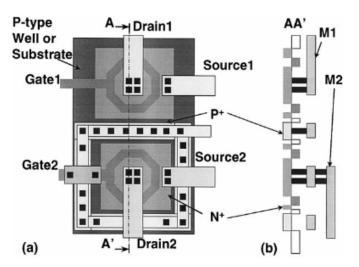

| 2.13 | (a) Layout and (b) cross-section of two enclosed layout NMOS transistors with a p+ contact guard ring which prevents inter-device leakage [77]                                                                                  | 36 |

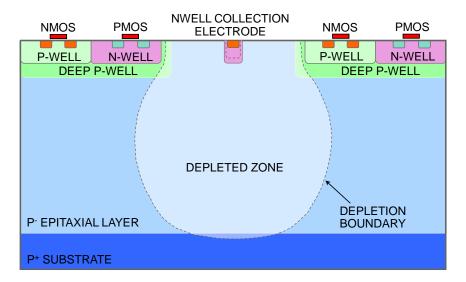

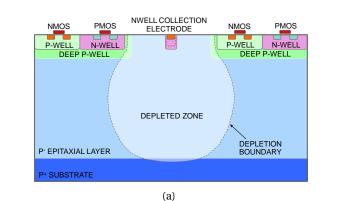

| 3.1  | Cross-section of the standard sensor in the TowerJazz 180 nm process [85]                                                                                                                                                       | 38 |

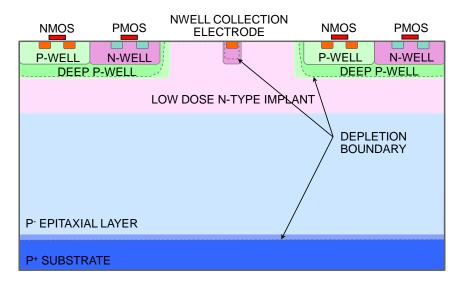

| 3.2  | Cross-section of the sensor in the TowerJazz 180 nm modified process [85]                                                                                                                                                       | 39 |

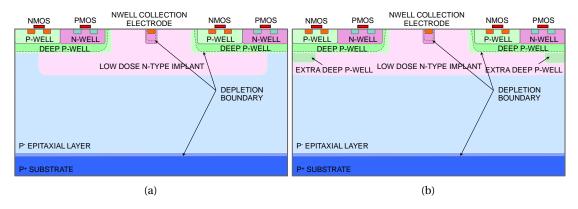

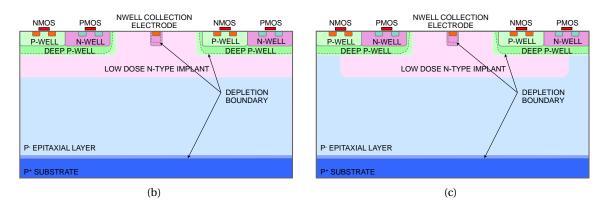

| 3.3  | Cross-section of the sensor in the TowerJazz 180 nm modified process with: (a)                                                                                                                                                  |    |

|      | gap in the low-dose n- implant (b) extra deep p-well [83].                                                                                                                                                                      | 40 |

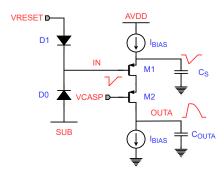

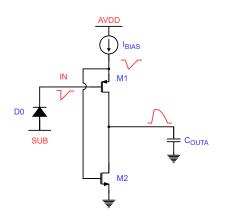

| 3.4  | Principle of the front-end amplifier.                                                                                                                                                                                           | 41 |

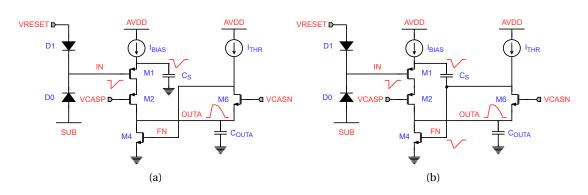

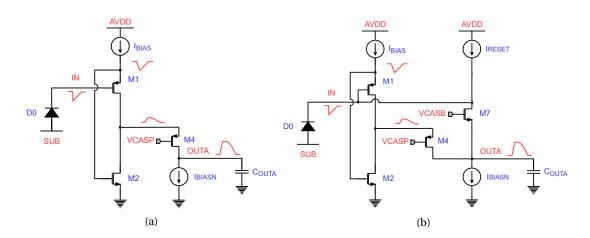

| 3.5  | Principle of the front-end amplifier: (a) with feedback to adjust the operating                                                                                                                                                 | 42 |

| 2.0  | point (b) with additional gain mechanism.                                                                                                                                                                                       |    |

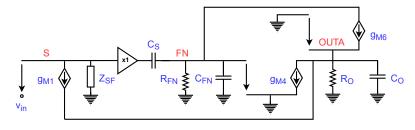

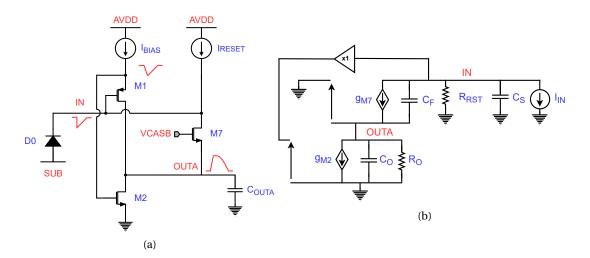

| 3.6  | Small signal model of the front-end amplifier.                                                                                                                                                                                  | 42 |

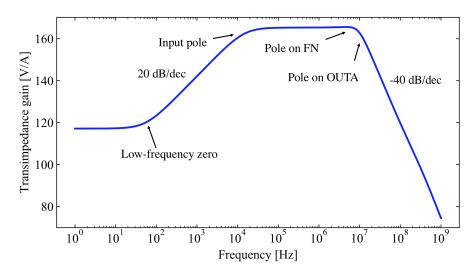

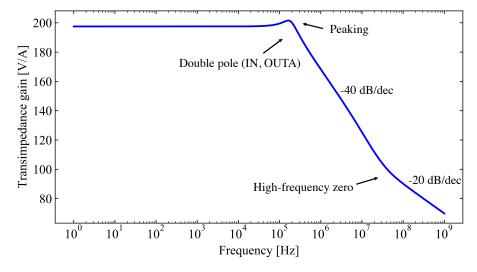

| 3.7  | AC simulation of the transimpedance gain of the amplifier.                                                                                                                                                                      | 43 |

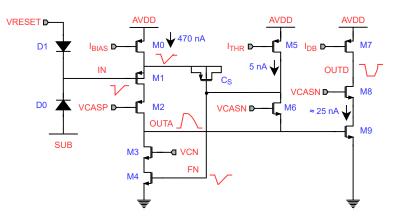

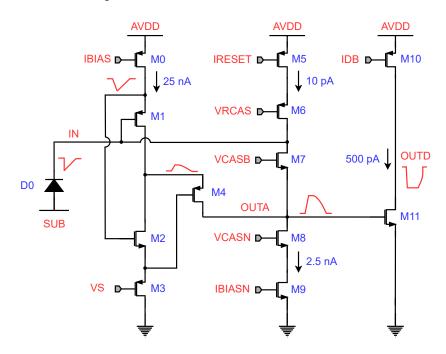

| 3.8  | Complete schematic of the front-end with discriminator.                                                                                                                                                                         | 44 |

| 3.9  | Front-end simulated transient response with a $100e^-$ threshold: signals at the                                                                                                                                                | 40 |

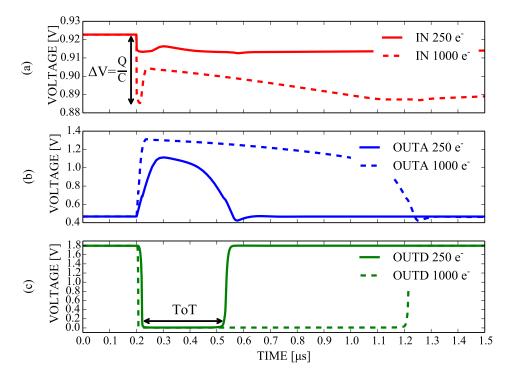

| 0.10 | (a) sensing node (b) output of the amplifier (c) output of the discriminator                                                                                                                                                    | 46 |

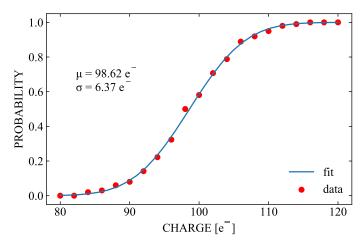

|      | Hit probability as a function of the input charge with simulated transient noise.                                                                                                                                               | 47 |

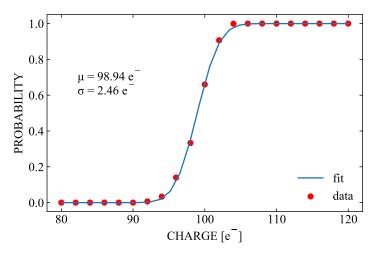

| 3.11 | Hit probability as a function of the input charge with simulated transistors'                                                                                                                                                   | 40 |

| 0.10 | mismatch.                                                                                                                                                                                                                       | 48 |

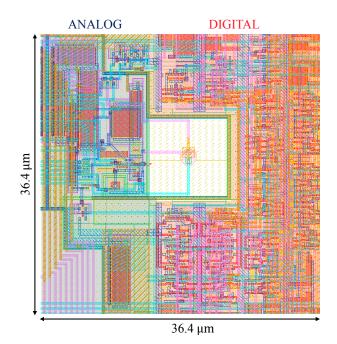

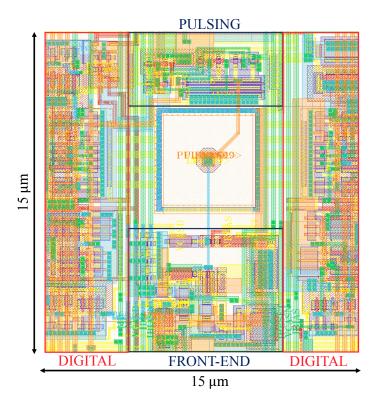

|      | Layout of the MALTA2 pixel.                                                                                                                                                                                                     | 49 |

|      | Picture of the MALTA2 chip                                                                                                                                                                                                      | 50 |

|      | Time walk curve obtained with a ${}^{90}Sr$ source.                                                                                                                                                                             | 51 |

|      | Dependence of front-end time jitter on the input charge                                                                                                                                                                         | 52 |

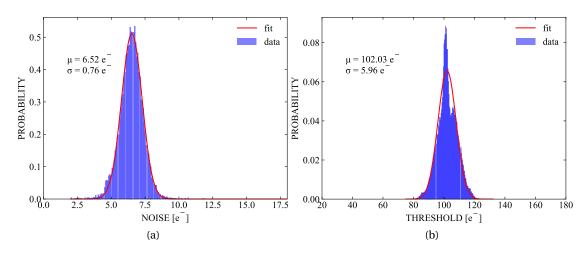

|      | Distribution of (a) ENC (b) threshold.                                                                                                                                                                                          | 53 |

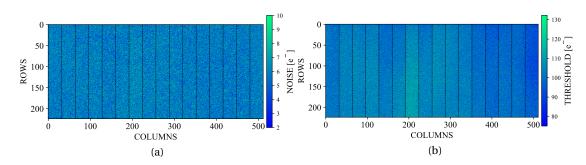

|      | 2D map for (a) ENC (b) threshold.                                                                                                                                                                                               | 53 |

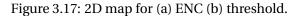

| 3.18 | Distribution of the threshold vs the (a) columns and (b) rows                                                                                                                                                                   | 53 |

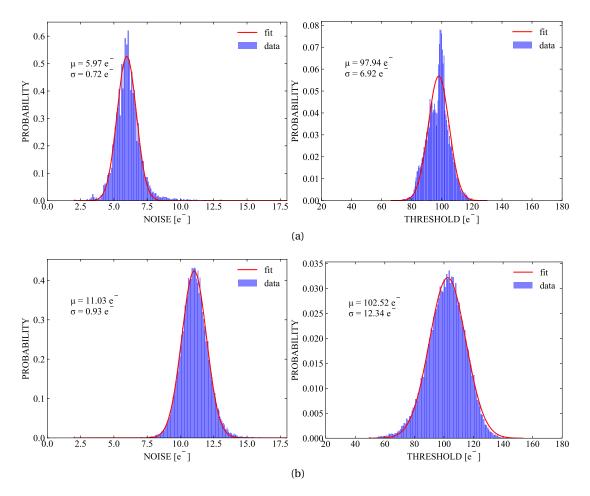

| 3.19 | Distribution of ENC and threshold with a threshold of $\approx 100  e^{-1}$ for (a) an unirra-                                                                                                                                  |    |

|      | diated sample and (b) a sample irradiated at $3 \cdot 10^{15} 1  \text{MeVn}_{eq}  \text{cm}^{-2}$ and $3  \text{Mrad}$ .                                                                                                       | 54 |

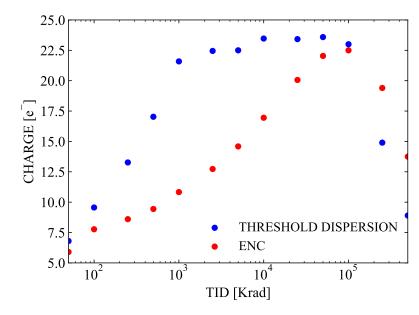

| 3.20 | Dependence of ENC and threshold dispersion on TID with a threshold of $\approx 100  e^-$ .                                                                                                                                      |    |

|      | The points at 50 krad represent measurements before irradiation. The points at                                                                                                                                                  |    |

|      | 250 Mrad and 500 Mrad correspond to measurements after 24 hours annealing                                                                                                                                                       |    |

| 0.01 | at room temperature and additional 24 hours of annealing at 80 °C, respectively.                                                                                                                                                | 55 |

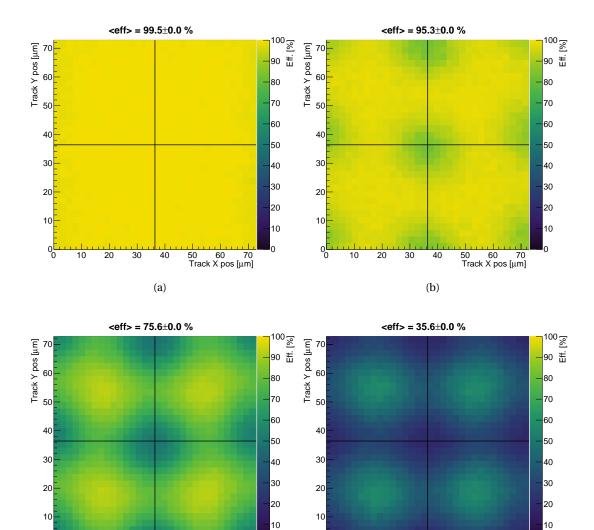

| 3.21 | In-pixel efficiency over an area of $2 \times 2$ pixels with a charge threshold of $\approx 100 \text{ e}^-$ for (a) an unirradiated sample and samples irradiated up to $3 \cdot 10^{15} 1 \text{ MeV} n_{eq} \text{ cm}^{-2}$ |    |

|      | and 3Mrad with a step of $10^{15}$ 1 MeV $n_{eq}$ cm <sup>-2</sup> and 1 Mrad in (b), (c) and (d)                                                                                                                               |    |

|      | respectively.                                                                                                                                                                                                                   | 56 |

|      |                                                                                                                                                                                                                                 | 50 |

| 4.1   | Cross section of the sensor in the TPSCo 65 nm imaging technology (a) standard process (b) modified process with low-dose n- implant (c) with gap in the low- |          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | dose n- implant                                                                                                                                               | 60       |

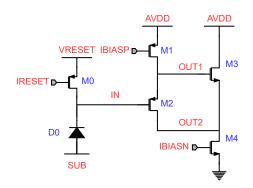

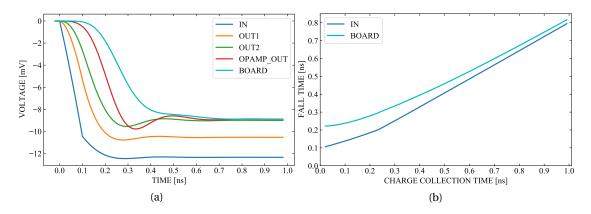

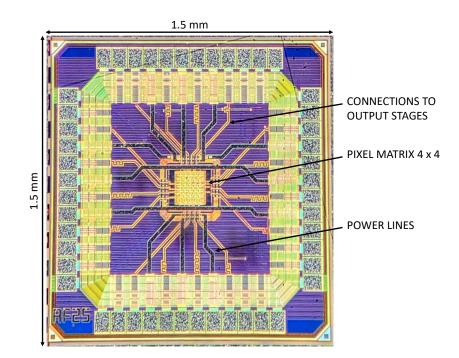

| 4.2   | Buffer circuit in the APTS pixel.                                                                                                                             | 61       |

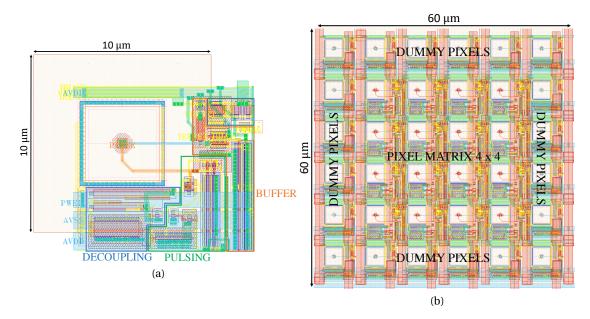

| 4.3   | Layout of the APTS (a) pixel and (b) matrix.                                                                                                                  | 62       |

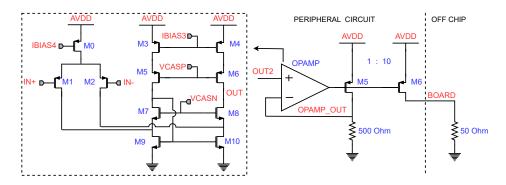

| 4.4   | Buffer circuit in the APTS periphery.                                                                                                                         | 63       |

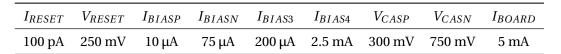

| 4.5   | Simulated response of the buffer chain in the APTS with an input charge of                                                                                    |          |

|       | 150e <sup>-</sup> : (a) transient waveforms for a charge collection time of 100 ps (b) fall time                                                              |          |

|       | of the signal on the electrode and on the off-chip 50 $\Omega$ resistance as a function of                                                                    |          |

|       | the charge collection time.                                                                                                                                   | 63       |

| 4.6   | Buffer chain in the APTS version with readout entirely based on source followers.                                                                             | 64       |

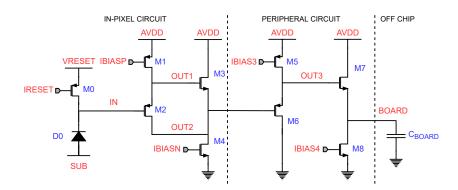

| 4.7   | Picture of the APTS chip                                                                                                                                      | 65       |

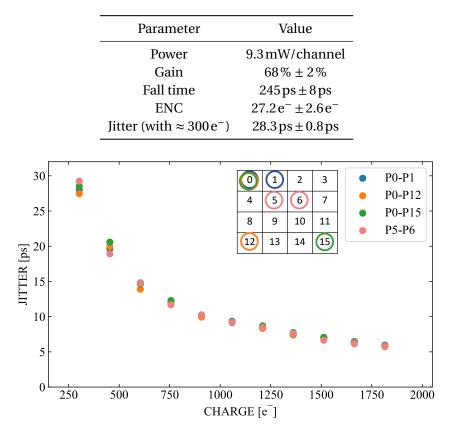

| 4.8   | Jitter of the buffer chain in the APTS as a function of the input charge                                                                                      | 66       |

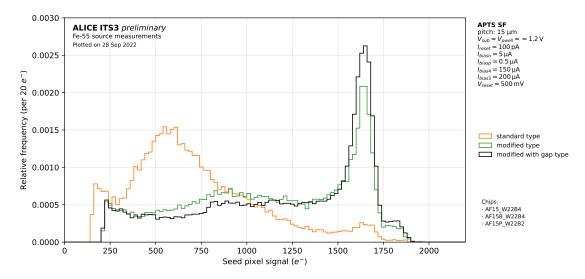

| 4.9   | Spectrum of the charge collected by the seed pixel under exposure to a ${}^{55}Fe$                                                                            |          |

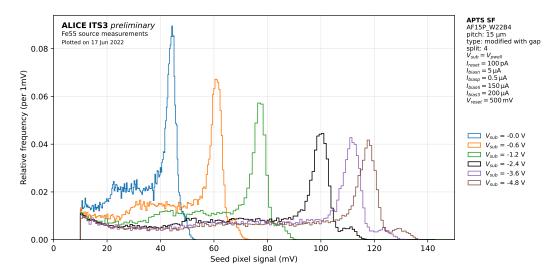

|       | source for the different sensor flavours [100]                                                                                                                | 67       |

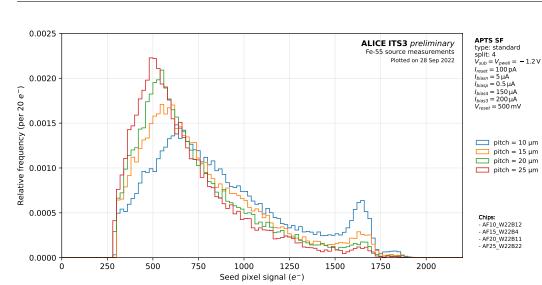

| 4.10  | Spectrum of the charge collected by the seed pixel under exposure to a ${}^{55}Fe$                                                                            |          |

|       | source for the standard sensor and different pixel pitches [100]                                                                                              | 68       |

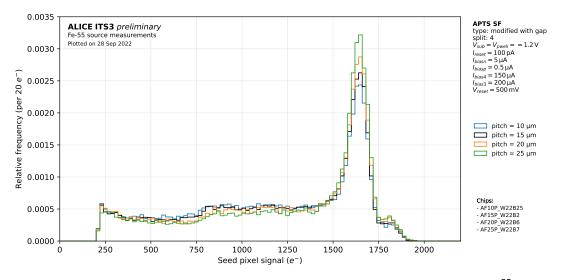

| 4.11  | Spectrum of the charge collected by the seed pixel under exposure to a ${}^{55}Fe$                                                                            |          |

|       | source for the modified sensor with cut in the low-dose n- implant and different                                                                              |          |

|       | pixel pitches [100].                                                                                                                                          | 68       |

| 4.12  | Spectrum of the signal on the seed pixel under exposure to a ${}^{55}Fe$ source as a                                                                          |          |

|       | function of the substrate voltage for the modified sensor with cut in the low-dose                                                                            |          |

|       | n- implant                                                                                                                                                    | 69       |

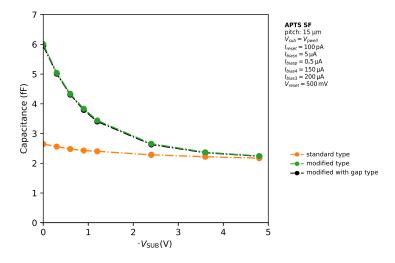

| 4.13  | Sensor capacitance as a function of the substrate voltage for the different sensor                                                                            |          |

|       | flavors.                                                                                                                                                      | 69       |

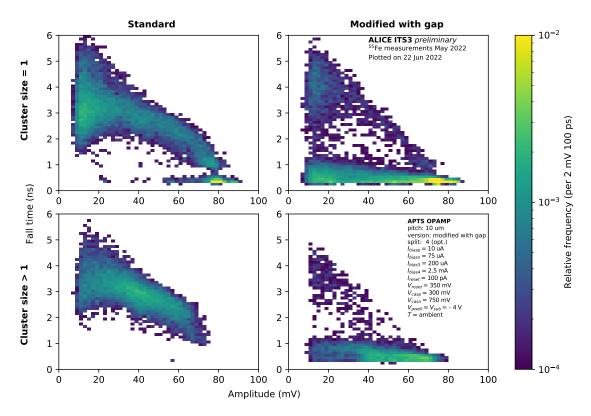

| 4.14  | 2D distributions of the output signals from the seed pixel in an amplitude-fall                                                                               |          |

|       | time plane obtained by exposing the chip to a ${}^{55}Fe$ source comparing different                                                                          | 70       |

| 4 1 5 | sensor flavors and cluster sizes [101].                                                                                                                       | 70       |

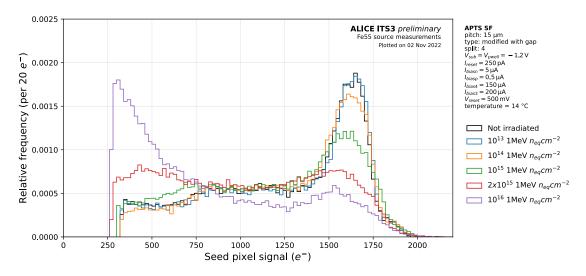

| 4.15  | Spectrum of the charge collected by the seed pixel under exposure to a ${}^{55}Fe$                                                                            |          |

|       | source for the modified sensor with cut in the low-dose n- implant at different                                                                               | 71       |

| 4.10  | levels of irradiation [100].    .      Principle of the front-end amplifier.    .                                                                             | 71<br>72 |

|       | Principle of the front-end amplifier: (a) with cascode and (b) with feedback and                                                                              | 12       |

| 4.17  | reset mechanism.                                                                                                                                              | 73       |

| 1 18  | Schematic of the (a) front-end amplifier without cascode and (b) small-signal                                                                                 | 15       |

| 4.10  | model.                                                                                                                                                        | 74       |

| 4 19  | AC simulation of the transimpedance gain of the amplifier.                                                                                                    | 75       |

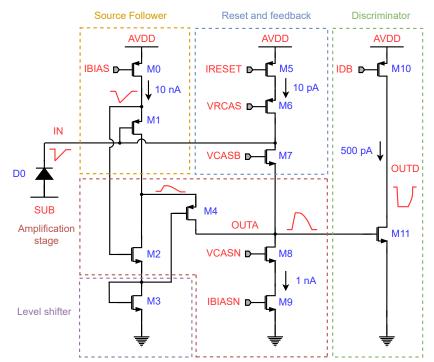

|       | Complete schematic of the front-end with discriminator.                                                                                                       | 76       |

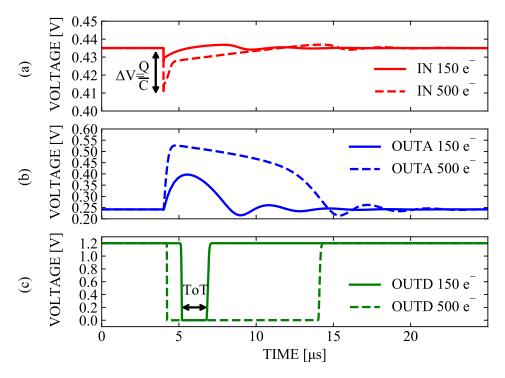

|       | Front-end simulated transient response with a threshold of $\approx 140  \text{e}^-$ : (a) signals                                                            |          |

|       | on the collection electrode, (b) signals at the output of the amplifier, (c) signals                                                                          |          |

|       | at the output of the discriminator.                                                                                                                           | 77       |

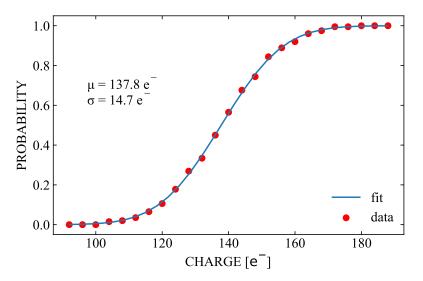

| 4.22  | Hit probability as a function of the input charge with simulated transient noise.                                                                             | 78       |

|       |                                                                                                                                                               |          |

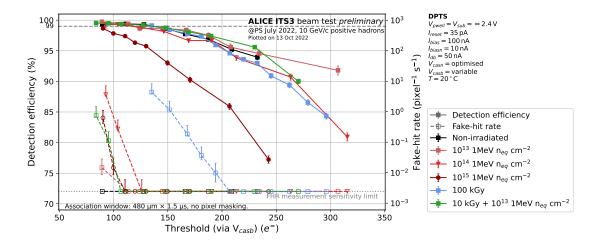

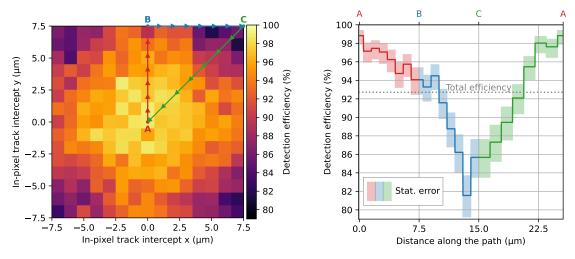

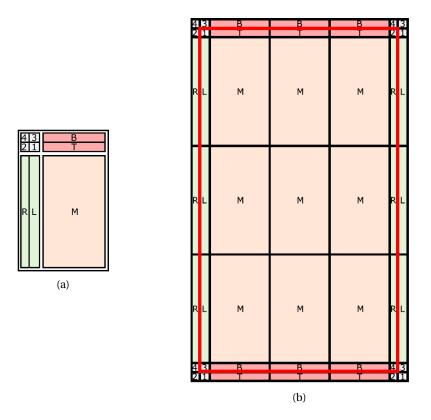

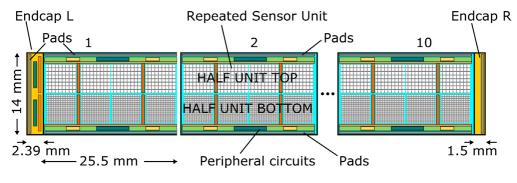

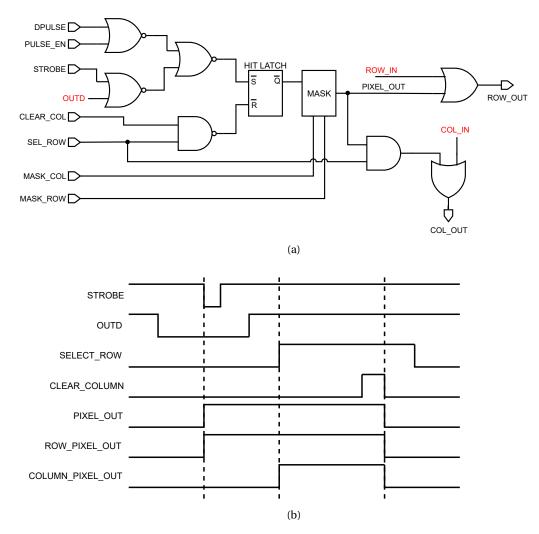

| <ul> <li>4.24 Layout of the DPTS pixel</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.23 Hit probability as a function of the input charge with simulated transis                      | tors'  |

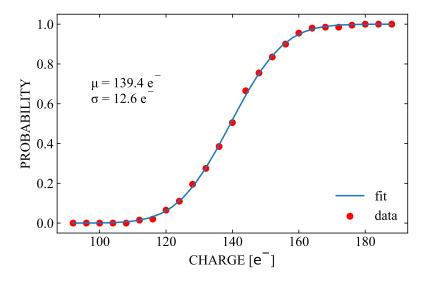

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|

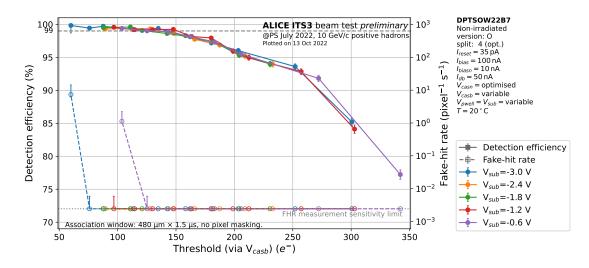

| 4.25 Readout components for the time encoding of the pixel coordinates and ToT: (a)<br>row pulse generator (b) processing logic (c) column delay chain.814.26 Picture of the DPTS chip.824.27 Map of time intervals encoding the row and column information of a hit measured by pulsing each pixel a thousand times.834.28 Front-end time walk curve.844.30 Distribution of (a) ENC (b) threshold.854.31 2D map for (a) ENC (b) threshold.864.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the<br>power consumption.864.33 Distributions of ENC and threshold with a nominal threshold of ≈ 140e <sup>-</sup> for (a)<br>an unirradiated sample and (b) a sample irradiated at 10 <sup>15</sup> 1 MeVneq cm <sup>-2</sup> and<br>1 Mrad.874.34 Distribution of (a) ENC and thy breshold for a sample irradiated at 50 Mrad after<br>an annealing of ≈ 30 days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.895.1 Principle of the stitching technique: (a) design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mismatch                                                                                           | 79     |

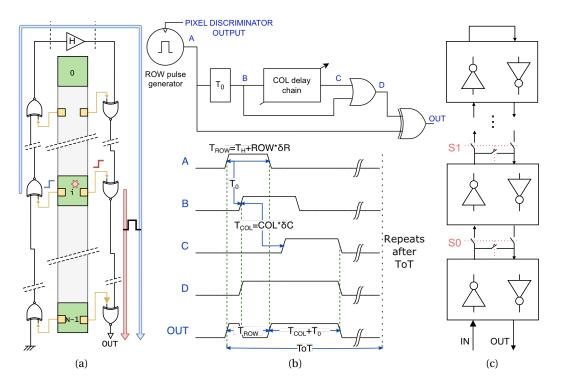

| row pulse generator (b) processing logic (c) column delay chain.814.26 Picture of the DPTS chip.824.27 Map of time intervals encoding the row and column information of a hit measured by pulsing each pixel a thousand times.834.28 Front-end time walk curve.844.30 Distribution of (a) ENC (b) threshold.854.31 2D map for (a) ENC (b) threshold.864.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the power consumption.864.33 Distributions of ENC and threshold with a nominal threshold of ≈ 140e <sup>-</sup> for (a) an unirradiated sample and (b) a sample irradiated at 10 <sup>15</sup> 1 MeV n <sub>eq</sub> cm <sup>-2</sup> and 1 Mrad.874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after an annealing of ≈ 30 days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.894.37 In-pixel detection efficiency of a chip irradiated to 10 <sup>15</sup> 1 MeV n <sub>eq</sub> cm <sup>-2</sup> with a nominal charge threshold of ≈ 150e <sup>-</sup> [103].905.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) subframes on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.945.2 Concept diagram of the MOSS chip.965.3 Schematic of the front-end in the MOSS chip.975.4 Architecture of a half unit of the MOSS chip.985.5 Architecture of a half unit of the MOSS chip.985.6 Schematic diagram of the MoSS chip.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.24 Layout of the DPTS pixel.                                                                     | 80     |

| <ul> <li>4.26 Picture of the DPTS chip.</li> <li>82</li> <li>4.27 Map of time intervals encoding the row and column information of a hit measured by pulsing each pixel a thousand times.</li> <li>83</li> <li>4.28 Front-end time walk curve.</li> <li>84</li> <li>4.29 Front-end time jitter.</li> <li>84</li> <li>4.30 Distribution of (a) ENC (b) threshold.</li> <li>86</li> <li>4.31 D map for (a) ENC (b) threshold.</li> <li>86</li> <li>4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the power consumption.</li> <li>86</li> <li>4.33 Distributions of ENC and threshold with a nominal threshold of ≈ 140e<sup>-</sup> for (a) an unirradiated sample and (b) a sample irradiated at 10<sup>15</sup>1 MeV n<sub>eq</sub> cm<sup>-2</sup> and 1 Mrad.</li> <li>87</li> <li>4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after an annealing of ≈ 30 days at room temperature.</li> <li>88</li> <li>4.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.</li> <li>89</li> <li>4.36 Detection efficiency of a chip irradiated to 10<sup>15</sup>1 MeV n<sub>eq</sub> cm<sup>-2</sup> with a nominal charge threshold of ≈ 150e<sup>-</sup> [103].</li> <li>90</li> <li>5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) subframes on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.</li> <li>94</li> <li>52 Concept diagram of the MOSS chip.</li> <li>53 Schematic of the front-end in the MOSS chip.</li> <li>96</li> <li>54 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.</li> <li>98</li> <li>55 Architecture of a half unit of the MOSS chip.</li> <li>99</li> <li>56 Schematic diagram of the MOSS chip.</li> <li>99</li> <li>57 High-level diagram of the MOSS chip.</li> <li>99</li> <li>58 Chematic diagram of the MOSS chip.</li> <li>99</li> <li>59</li> <li>50 Schematic of the front-end in the MOSS chip.</li> <li>91</li> <li>510 Schematic of the front-end in the MOSS chip.</li> <li>92</li> <li>510 Schematic of the front-en</li></ul> | 4.25 Readout components for the time encoding of the pixel coordinates and ToT                     | Г: (а) |

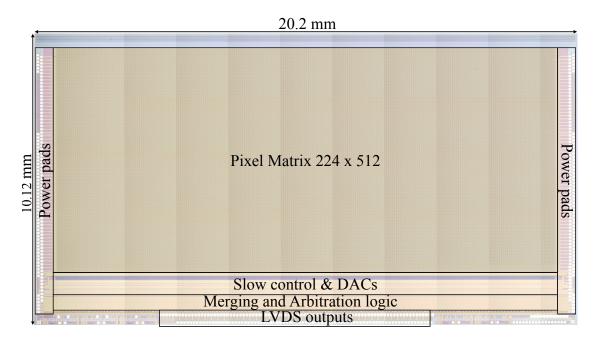

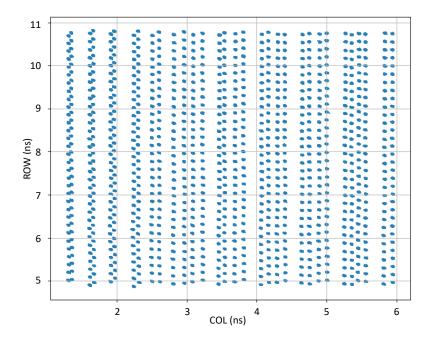

| 4.27 Map of time intervals encoding the row and column information of a hit measured by pulsing each pixel a thousand times.834.28 Front-end time walk curve.844.29 Front-end time jitter.844.30 Distribution of (a) ENC (b) threshold.854.31 2D map for (a) ENC (b) threshold.864.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the<br>power consumption.864.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for (a)<br>an unirradiated sample and (b) a sample irradiated at $10^{15}1  MeV_{neq}  cm^{-2}$ and<br>$1  Mrad$ .874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx 30$ days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.35 Detection efficiency of a chip irradiated to $10^{15}1  MeV_{neq}  cm^{-2}$ with a<br>nominal charge threshold of $\approx 150e^-$ [103].905.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2 Concept diagram of the MOSS chip.965.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.965.5 Architecture of a half unit of the MOSS chip.905.6 Schematic diagram of the line hopping method used in the MOSS chip.1005.7 Layout of the MOSS chip.1025.8 Layout of the MOSS chip.1025.9 High-level diagram of the line hopST chip.1035.10 Sche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | row pulse generator (b) processing logic (c) column delay chain. $\ldots$ .                        | 81     |

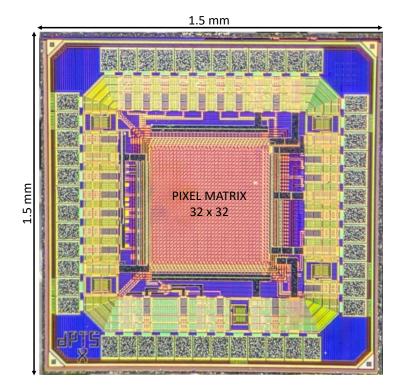

| sured by pulsing each pixel a thousand times.834.28Front-end time walk curve.844.29Front-end time jitter.844.30Distribution of (a) ENC (b) threshold.854.312D map for (a) ENC (b) threshold.864.32Trend of (a) nominal threshold, (b) threshold dispersion and noise with the<br>power consumption.864.33Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for (a)<br>an unirradiated sample and (b) a sample irradiated at $10^{15}1  \text{MeVn}_{eq}  \text{cm}^{-2}$ and<br>$1  \text{Mrad}$ .874.34Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx 30$ days at room temperature.884.35Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36Detection efficiency of a chip irradiated to $10^{15}1  \text{MeVn}_{eq}  \text{cm}^{-2}$ with a<br>nominal charge threshold of $\approx 150e^-$ [103].905.1Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2Concept diagram of the MOSS chip.965.4MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5Architecture of a half unit of the MOSS chip.905.7Layout of the MOSS chip.1005.8Layout of the MOSS chip.1005.9High-level diagram of the line hopping method used in the MOSS chip.1005.7Layout o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.26 Picture of the DPTS chip                                                                      | 82     |

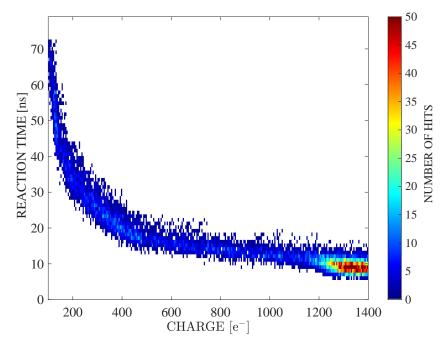

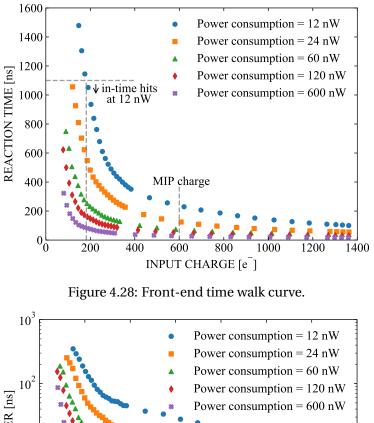

| 4.28 Front-end time walk curve.       84         4.29 Front-end time jitter.       84         4.30 Distribution of (a) ENC (b) threshold.       85         4.31 2D map for (a) ENC (b) threshold.       86         4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the power consumption.       86         4.33 Distributions of ENC and threshold with a nominal threshold of ≈ 140e <sup>-</sup> for (a) an unirradiated sample and (b) a sample irradiated at 10 <sup>15</sup> 1 MeV n <sub>eq</sub> cm <sup>-2</sup> and 1 Mrad.       87         4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after an annealing of ≈ 30 days at room temperature.       88         4.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.       89         4.36 Detection efficiency and FHR as a function of the nominal charge threshold for different levels of irradiation [103].       89         4.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1$ MeV n <sub>eq</sub> cm <sup>-2</sup> with a nominal charge threshold of ≈ 150e <sup>-</sup> [103].       90         5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-frames on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.       94         5.2 Concept diagram of the MOSS chip.       96         5.3 Schematic of the front-end in the MOSS chip.       96         5.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.       98 <td< td=""><td>4.27 Map of time intervals encoding the row and column information of a hit r</td><td>mea-</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.27 Map of time intervals encoding the row and column information of a hit r                      | mea-   |

| 4.29 Front-end time jitter.844.30 Distribution of (a) ENC (b) threshold.854.31 2D map for (a) ENC (b) threshold.864.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the<br>power consumption.864.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140 e^-$ for (a)<br>an unirradiated sample and (b) a sample irradiated at $10^{15} 1 \text{MeV}n_{eq} \text{ cm}^{-2}$ and<br>$1 \text{ Mrad.}$ 874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx 30$ days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different levels of irradiation [103].894.37 In-pixel detection efficiency of a chip irradiated to $10^{15} 1 \text{ MeV} n_{eq} \text{ cm}^{-2}$ with a<br>nominal charge threshold of $\approx 150 e^-$ [103].905.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2 Concept diagram of the MOSS chip.965.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5 Architecture of a half unit of the MOSS chip.905.6 Schematic diagram of the line hopping method used in the MOSS chip.1005.7 Layout of the MOSS chip.1025.8 Layout of the MOSS chip.1025.9 High-level diagram of the MOST chip.1035.10 Schematic of the front-end in the MOST chip.<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | sured by pulsing each pixel a thousand times.                                                      | 83     |

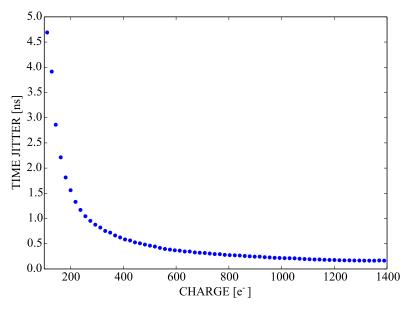

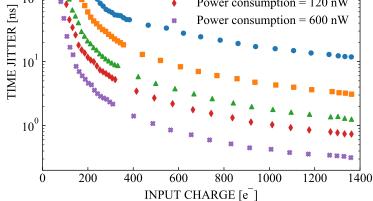

| 4.30 Distribution of (a) ENC (b) threshold.       85         4.31 2D map for (a) ENC (b) threshold.       86         4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the power consumption.       86         4.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for (a) an unirradiated sample and (b) a sample irradiated at $10^{15}1 \text{MeVn}_{eq} \text{cm}^{-2}$ and 1 Mrad.       87         4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after an annealing of $\approx 30$ days at room temperature.       88         4.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.       89         4.36 Detection efficiency and FHR as a function of the nominal charge threshold for different levels of irradiation [103].       89         4.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1 \text{MeVn}_{eq} \text{cm}^{-2}$ with a nominal charge threshold of $\approx 150e^-$ [103].       90         5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) subframes on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.       94         5.2 Concept diagram of the MOSS chip.       95         5.3 Schematic of the front-end in the MOSS chip.       96         5.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.       98         5.5 Architecture of a half unit of the MOSS chip.       90         5.6 Schematic diagram of the line hop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.28 Front-end time walk curve.                                                                    | 84     |

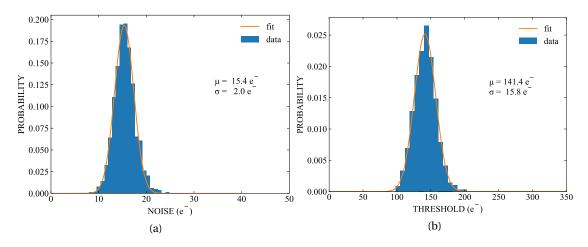

| 4.31 2D map for (a) ENC (b) threshold.       86         4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the power consumption.       86         4.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for (a) an unirradiated sample and (b) a sample irradiated at $10^{15}1 \text{MeVn}_{eq} \text{cm}^{-2}$ and 1 Mrad.       87         4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at $50 \text{Mrad}$ after an annealing of $\approx 30 \text{days}$ at room temperature.       88         4.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.       89         4.36 Detection efficiency and FHR as a function of the nominal charge threshold for different levels of irradiation [103].       89         4.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1 \text{MeVn}_{eq} \text{cm}^{-2}$ with a nominal charge threshold of $\approx 150e^-$ [103].       90         5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) subframes on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.       94         5.2 Concept diagram of the MOSS chip.       96         5.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.       98         5.5 Architecture of a half unit of the MOSS chip.       99         5.6 Schematic diagram of the line hopping method used in the MOSS chip.       90         5.7 Layout of the MOSS chip.       102         5.8 Layout of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.29 Front-end time jitter                                                                         | 84     |

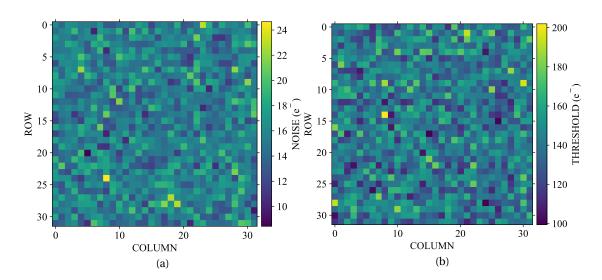

| 4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with the       86         4.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for (a)       an unirradiated sample and (b) a sample irradiated at $10^{15}1$ MeV $n_{eq}$ cm <sup>-2</sup> and         1.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after       an annealing of $\approx 30$ days at room temperature.       88         4.35 Detection efficiency and FHR as a function of the nominal charge threshold for       different substrate voltages.       89         4.36 Detection efficiency and FHR as a function of the nominal charge threshold for       different levels of irradiation [103].       89         4.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1$ MeV $n_{eq}$ cm <sup>-2</sup> with a       90         5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-frames on the wafer for the realization of the stitched device whose dicing lane       94         5.2 Concept diagram of the MOSS chip.       95         5.3 Schematic of the front-end in the MOSS chip.       96         5.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.       98         5.5 Architecture of a half unit of the MOSS chip.       99         5.6 Schematic diagram of the line hopping method used in the MOSS chip.       100         5.7 Layout of the MOSS chip.       102         5.8 Layout of the MOSS chip.       103         5.9 High-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.30 Distribution of (a) ENC (b) threshold.                                                        | 85     |

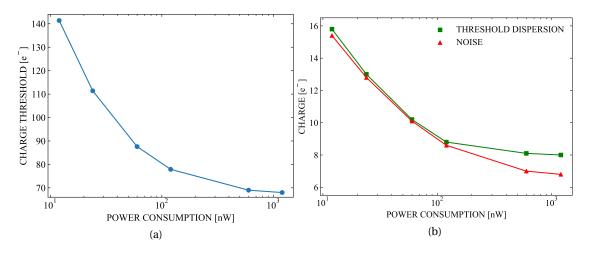

| power consumption.864.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140  e^-$ for (a)<br>an unirradiated sample and (b) a sample irradiated at $10^{15} 1  MeV n_{eq}  cm^{-2}$ and<br>$1  Mrad.$ 874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx 30$ days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different levels of irradiation [103].894.37 In-pixel detection efficiency of a chip irradiated to $10^{15} 1  MeV n_{eq}  cm^{-2}$ with a<br>nominal charge threshold of $\approx 150  e^-$ [103].905.1Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2Concept diagram of the MOSS chip.955.3Schematic of the front-end in the MOSS chip.985.4MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5Architecture of a half unit of the MOSS chip.905.7Layout of the MOSS chip.1025.8Layout of the MOSS chip.1025.9High-level diagram of the line hopping method used in the MOSS chip.1025.8Layout of the MOSS chip.1035.10Schematic diagram of the MOST chip.1035.10Schematic of the front-end in the MOST chip.1035.10Schematic of the f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.31 2D map for (a) ENC (b) threshold.                                                             | 86     |

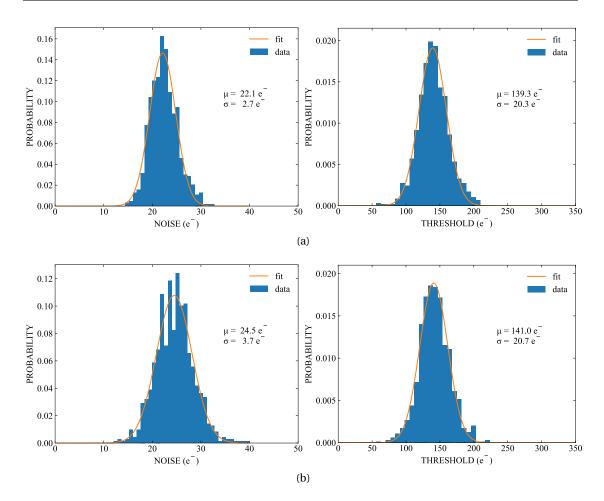

| 4.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140 e^-$ for (a) an unirradiated sample and (b) a sample irradiated at $10^{15}1 \text{ MeV}n_{eq} \text{ cm}^{-2}$ and $1 \text{ Mrad.}$ 87         4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after an annealing of $\approx 30$ days at room temperature.       88         4.35 Detection efficiency and FHR as a function of the nominal charge threshold for different substrate voltages.       89         4.36 Detection efficiency and FHR as a function of the nominal charge threshold for different levels of irradiation [103].       89         4.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1 \text{ MeV}n_{eq} \text{ cm}^{-2}$ with a nominal charge threshold of $\approx 150 e^-$ [103].       90         5.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) subframes on the wafer for the realization of the stitched device whose dicing lane is indicated with the red line.       94         5.2 Concept diagram of the MOSS chip.       95         5.3 Schematic of the front-end in the MOSS chip.       99         5.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.       98         5.5 Architecture of a half unit of the MOSS chip.       90         5.7 Layout of the MOSS chip.       102         5.8 Layout of the MOSS chip.       102         5.9 High-level diagram of the MOST chip.       102         5.9 High-level diagram of the MOST chip.       103         5.10 Schematic o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.32 Trend of (a) nominal threshold, (b) threshold dispersion and noise with                       | ı the  |

| an unirradiated sample and (b) a sample irradiated at $10^{15}1 \text{ MeV}n_{eq} \text{ cm}^{-2}$ and<br>$1 \text{ Mrad.}$ 874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx$ 30 days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different levels of irradiation [103].894.37 In-pixel detection efficiency of a chip irradiated to $10^{15}1 \text{ MeV}n_{eq} \text{ cm}^{-2}$ with a<br>nominal charge threshold of $\approx 150 \text{ e}^{-}$ [103].905.1Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2Concept diagram of the MOSS chip.955.3Schematic of the front-end in the MOSS chip.995.4MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5Architecture of a half unit of the MOSS chip.905.7Layout of the MOSS chip.905.8Layout of the MOSS chip.905.4MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5Architecture of a half unit of the MOSS chip.905.6Schematic diagram of the line hopping method used in the MOSS chip.905.7Layout of the MOSS chip.1025.8Layout of the MOSS chip.1025.9High-level diagram of the MOST chip.103 <t< td=""><td>power consumption.</td><td> 86</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | power consumption.                                                                                 | 86     |

| 1 Mrad.874.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50 Mrad after<br>an annealing of $\approx$ 30 days at room temperature.884.35 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different substrate voltages.894.36 Detection efficiency and FHR as a function of the nominal charge threshold for<br>different levels of irradiation [103].894.37 In-pixel detection efficiency of a chip irradiated to $10^{15} 1 \text{MeV} n_{eq} \text{ cm}^{-2}$ with a<br>nominal charge threshold of $\approx 150 \text{ e}^{-}$ [103].905.1 Principle of the stitching technique: (a) design reticle with sub-frames (b) sub-<br>frames on the wafer for the realization of the stitched device whose dicing lane<br>is indicated with the red line.945.2 Concept diagram of the MOSS chip.955.3 Schematic of the front-end in the MOSS chip.965.4 MOSS in-pixel digital logic: (a) block diagram (b) timing diagram.985.5 Architecture of a half unit of the MOSS chip.995.6 Schematic diagram of the line hopping method used in the MOSS chip.1005.7 Layout of the MOSS chip.1025.8 Layout of the MOSS chip.1035.9 High-level diagram of the MOST chip.1035.10 Schematic of the front-end in the MOST chip.103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.33 Distributions of ENC and threshold with a nominal threshold of $\approx 140e^-$ for           | or (a) |

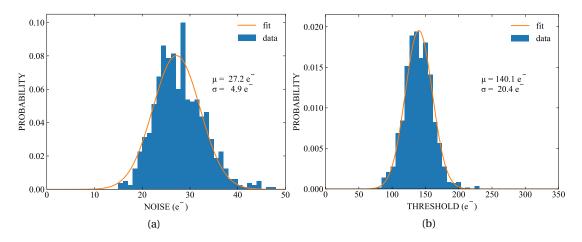

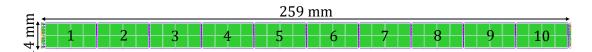

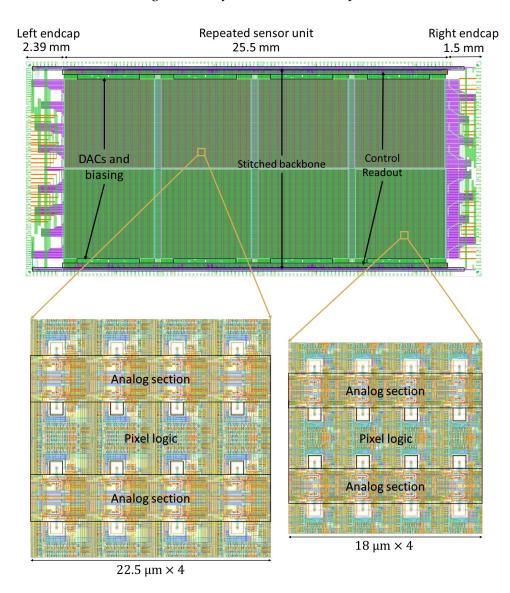

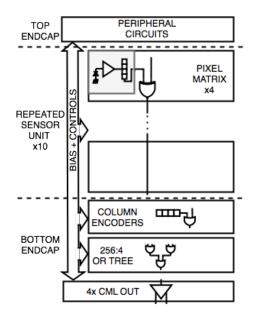

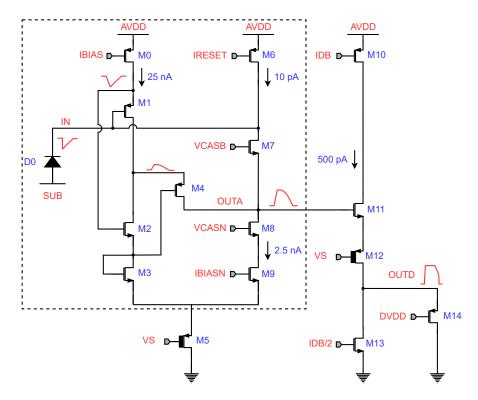

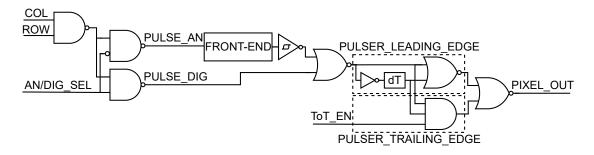

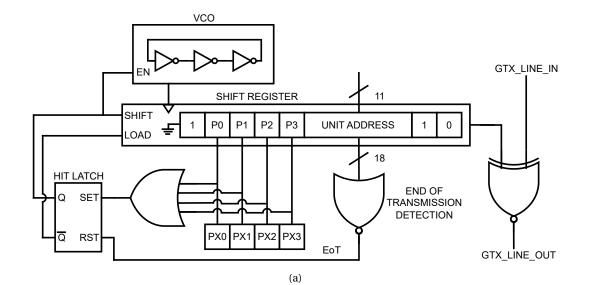

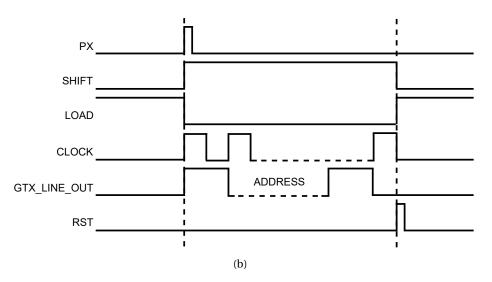

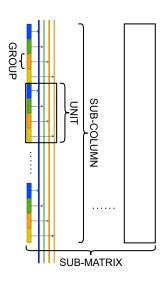

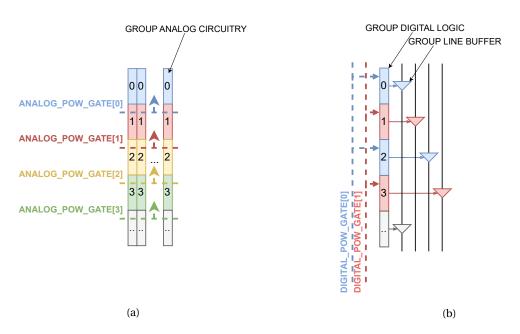

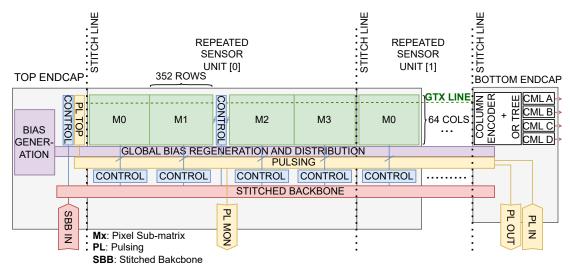

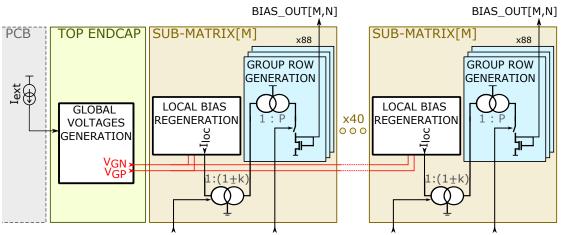

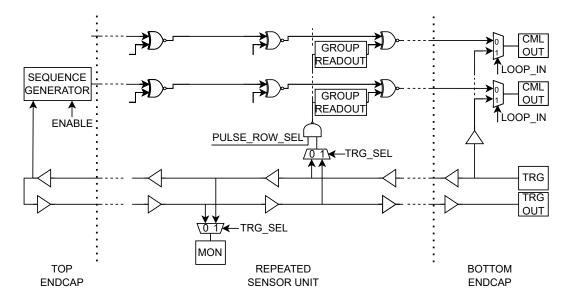

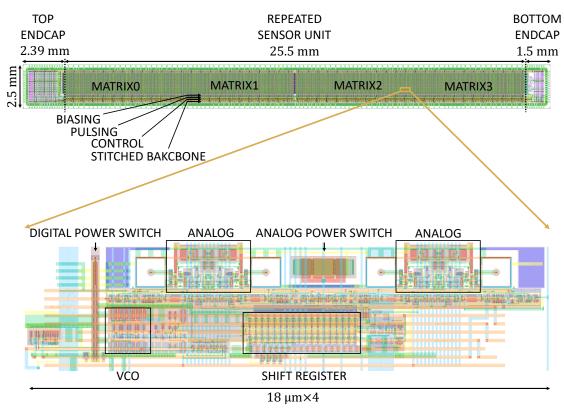

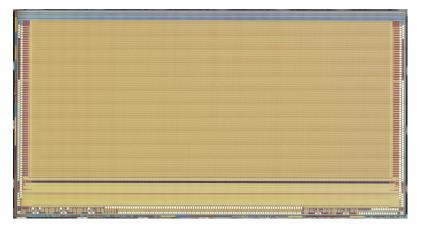

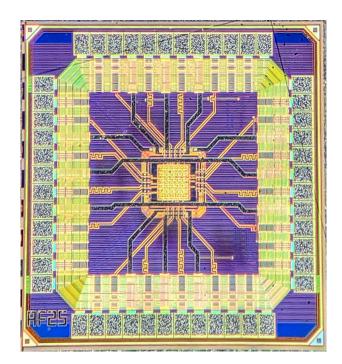

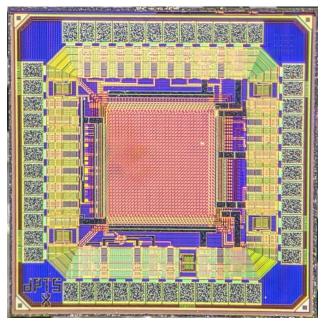

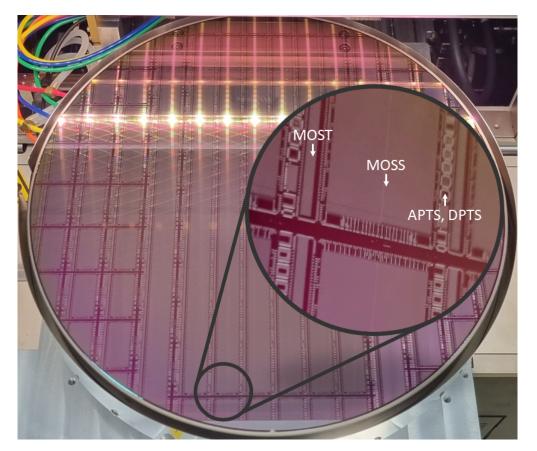

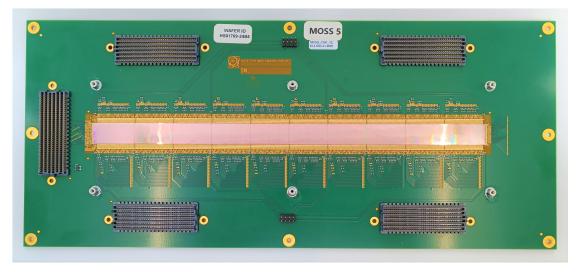

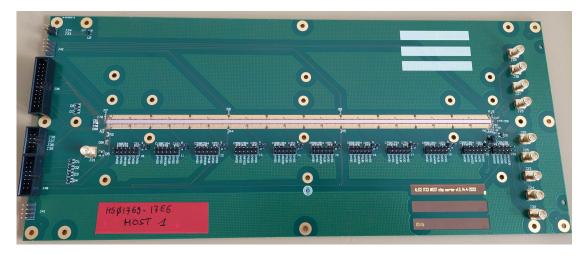

| <ul> <li>4.34 Distribution of (a) ENC and (b) threshold for a sample irradiated at 50Mrad after<br/>an annealing of ≈ 30 days at room temperature</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | an unirradiated sample and (b) a sample irradiated at $10^{15} 1  {\rm MeV} n_{eq}  {\rm cm}^{-2}$ | and    |