# Hardware-Software co-design Methodologies for Edge AI Optimization

Présentée le 25 septembre 2023

Faculté des sciences et techniques de l'ingénieur Laboratoire des systèmes embarqués Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### Flavio PONZINA

Acceptée sur proposition du jury

Prof. A. M. Alahi, président du jury

Prof. D. Atienza Alonso, directeur de thèse

Prof. T. Simunic Rosing, rapporteuse

Prof. L. Pozzi, rapporteuse

Prof. A. Burg, rapporteur

# Acknowledgements

EXTREMELY hard is to include in this section all the people who had an impact on my life and allowed me to reach this achievement. Starting from the beginning, the first mention goes to my *family*, who intensively supervised my studies during the very first years of school, always stressing the importance of school, respect, and commitment.

I am really grateful I had Prof. *Massimo Castagno* for three years at high school. In addition to his technical classes on computer science, he teaches his students responsibility and method. I believe his words significantly contribute to my growth, as a professional and, even more, as a person. During the same years, I met a real friend, *Davide Saggese*, who motivated me to improve continuously and with whom I spent some of my best days.

At Politecnico di Torino, I had the chance to be in contact with so many good professors and researchers. I want to recognize Prof. *Andrea Calimera* and Dr. *Valentino Peluso* for the opportunity they gave me to work on cutting-edge research on Artificial Intelligence for my master's thesis. Valentino spent so much time teaching me and supervising my work, and I am really thankful for what he has done. Let me also recognize his patience in making me understand topics that took me time to (hopefully) master.

The Embedded Systems Laboratory (ESL) of EPFL welcomed me in 2019 and allowed me to broaden my horizons in these last years. I had the honor to join the lab to pursue a Ph.D., which is something I had never considered at an early age, and that I usually thought of as something much bigger than me

(even recently when seeing the great work of other students in the lab). Here, I met people from all over the world, who definitely changed the way I look at my future. We are one of the largest labs in EPFL, so citing all of them would result in an incredibly long list. I want to thank *Denisa, Davide, Giovanni, Miguel, José, and Tomás*, post-docs of the lab who taught me a lot. I also met really astonishing colleagues like *Elisabetta, Darong, and Lara*, who I really admire for their commitment and passion for what they do.

I also want to thank the commission who reviewed my thesis and helped me improve the clarity of its content. Namely, I thank Professors *Pozzi, Rosing, Alahi*, and *Burg* for their time spent reading and evaluating this document. Moreover, I must also thank them for accepting to be part of my Ph.D. commission and especially for being available to attend my private defense on a late Friday afternoon!

Finally, I must conclude these acknowledgments by mentioning the person who really had the most considerable impact on my work in these years: Professor *David Atienza*, my thesis supervisor. Always available and supportive when I needed help. Most importantly, he believed in me and, by accepting me as a Ph.D. student in his laboratory, he gave me the most valuable opportunity I had in my life. Not only that, but he is still assisting me in my future career, supporting among other things, my application for a postdoctoral position abroad.

Thanks, David.

Lausanne, September 9, 2023

Flavio Ponzina

# **Abstract**

RTIFICIAL Intelligence (AI) is revolutionizing a vast range of industrial and scientific applications due to its several advantages, which include self-learning capabilities, extraction of intrigued hidden patterns from input data, and flexibility. While the cloud-based computing paradigm has been a baseline approach for AI inferences in the past years, recent technology advancements and AI optimization methods advocate and support a shift toward an edge-computing alternative. Nevertheless, Edge AI poses storage, computational, and efficiency challenges that must be addressed to support the deployment of compute-intense algorithms in embedded devices. To continuously increase the quality of their outputs, AI models are evolving into more complex algorithms, with extremely high memory and computing requirements that strain the resource capacity of edge low-power nodes. Aware of this challenge, the research community is studying the problem from different perspectives, mainly focusing on algorithmic optimizations or hardware accelerators. On one hand, the optimization of AI algorithms can reduce their memory need and computing complexity. On the other hand, the implementation of domain-specific hardware accelerators enables efficient executions of AI workloads by providing specialized resources designed to accelerate common kernels in AI inferences (e.g., matrix-vector multiplications).

Although optimization approaches tackling this problem from either an algorithmic or a hardware perspective exist, *hardware-software co-design method-ologies* are key. Indeed, by employing a co-design strategy, hardware-aware

algorithmic transformations can be effectively harnessed in workload-aware hardware resources to retrieve real energy efficiency gains. In this context, I endorse the implementation of accuracy-driven co-design methodologies, as they can guarantee that the optimized design abides by user-defined output quality levels. Such a co-design optimization vision is the research focus of this thesis. First, I introduce the E<sup>2</sup>CNNs methodology, an algorithmic-level transformation that builds ensembles of Convolutional Neural Networks (CNNs) to improve accuracy and robustness without increasing the initial memory and computing requirements. Then, I apply this methodology to different co-design strategies including codebook-based representations, approximate computing, and in-memory computing accelerators. The achieved results show that synergic combinations of hardware-aware application-level optimizations allow significant efficiency improvements in the evaluated AI benchmarks.

**Keywords:** Artificial intelligence, machine learning, deep learning, convolutional neural networks, embedded systems, internet-of-things, edge AI, energy efficiency, co-design, heterogeneous optimization.

# Résumé

INTELLIGENCE artificielle (IA) est en train de révolutionner une vaste gamme d'applications industrielles et scientifiques en raison de ses nombreux avantages, notamment ses capacités d'auto-apprentissage, l'extraction de caractéristiques cachés à partir de données d'entrée, et sa flexibilité. Alors que le paradigme de l'informatique en nuage a été une référence pour les inférences d'IA au cours des dernières années, les progrès technologiques récents et les méthodes d'optimisation de l'IA préconisent et soutiennent un changement vers une alternative d'informatique en périphérie. Néanmoins, l'IA périphérique pose des problèmes de stockage de données, de calcul, et d'efficacité qui doivent être résolus pour soutenir le déploiement d'algorithmes à forte intensité de calcul dans les appareils embarqués. Pour améliorer en permanence la qualité de leurs résultats, les modèles d'IA évoluent vers des algorithmes plus complexes, avec des exigences extrêmement élevées en matière de mémoire et de calculs qui mettent à rude épreuve les ressources des nœuds périphériques à faible consommation d'énergie. Consciente de ce défi, la communauté des chercheurs étudie le problème sous différents angles, en se concentrant principalement sur les optimisations algorithmiques ou les accélérateurs matériels. D'une part, l'optimisation des algorithmes d'IA peut réduire leur besoin en espace mémoire ainsi que la complexité de calcul. D'autre part, la mise en œuvre d'accélérateurs matériels spécifiques à un domaine permet des exécutions efficaces des charges de travail de l'IA en fournissant des ressources spécialisées conçues pour accélérer les noyaux communs dans les inférences de l'IA (par exemple, les multiplications matrice-vecteur).

Bien qu'il existe des approches d'optimisation abordant ce problème d'un point de vue algorithmique ou matériel, les méthodologies de co-conception *matériel-logiciel* sont essentielles. En effet, en employant une stratégie de co-conception, les transformations algorithmiques conscientes des enjeux matériels peuvent s'adapter pleinement aux ressources matérielles sensibles à la charge de travail afin de récupérer de réels gains d'efficacité énergétique. Dans ce contexte, j'approuve la mise en œuvre de méthodologies de co-conception axées sur la précision, car elles peuvent garantir que la conception optimisée respecte les niveaux de qualité de sortie définis par l'utilisateur. Cette vision de l'optimisation de la co-conception est l'objet de recherche de cette thèse. Tout d'abord, je présente la méthodologie E<sup>2</sup>CNNs, une transformation au niveau algorithmique qui construit des ensembles de réseau de neurones convolutifs pour améliorer la précision et la robustesse sans augmenter les exigences initiales en matière de mémoire et de calcul. Ensuite, j'applique cette méthodologie à différentes stratégies de co-conception, y compris les représentations basées sur le codebook, le calcul approximatif, et les accélérateurs de calcul en mémoire. Les résultats obtenus montrent que les combinaisons synergiques d'optimisations au niveau de l'application en fonction du matériel permettent des améliorations significatives de l'efficacité dans les repères d'IA évalués.

**Mots-clés:** Intelligence artificielle, apprentissage automatique, apprentissage profond, convolutional neural networks, systèmes embarqués, internet des objets, edge AI, efficacité énergétique, co-conception, optimisation hétérogène.

# **Contents**

| A  | cknov | vledgements                                                | 1   |

|----|-------|------------------------------------------------------------|-----|

| Ał | ostra | ct (Résumé)                                                | iii |

| 1  | Intr  | oduction                                                   | 1   |

|    | 1.1   | Artificial Intelligence                                    | 1   |

|    | 1.2   | Convolutional Neural Networks                              | 3   |

|    | 1.3   | Edge AI                                                    | 7   |

|    | 1.4   | Optimizations for Edge AI                                  | 9   |

|    |       | 1.4.1 Application-level optimizations                      | 9   |

|    |       | 1.4.2 Hardware-level optimizations                         | 10  |

|    | 1.5   | Trading-off accuracy for efficiency                        | 12  |

| 2  | Eml   | bedded Ensembles of                                        |     |

|    | Con   | volutional Neural Networks                                 | 17  |

|    | 2.1   | Introduction                                               | 17  |

|    |       | 2.1.1 Robustness of CNN models                             | 17  |

|    |       | 2.1.2 Ensembling                                           | 20  |

|    | 2.2   | $E^2$ CNNs methodology                                     | 23  |

|    |       | 2.2.1 Building the ensemble                                | 23  |

|    |       | 2.2.2 Example: LeNet5 vs. LeNet5-based E <sup>2</sup> CNNs | 25  |

|    |       | 2.2.3 Selecting the $E^2$ CNNs cardinality                 | 26  |

|    | 2.3   | $E^2$ CNNs achievements                                    | 28  |

|    |       | 2.3.1 Experimental set-up                                  | 28  |

|    |       |                                                            |     |

#### **Contents**

|   |     | 2.3.2  | Accuracy improvements                                     | 31 |

|---|-----|--------|-----------------------------------------------------------|----|

|   |     | 2.3.3  | Robustness improvements                                   | 32 |

|   |     | 2.3.4  | Reducing energy and memory requirements                   | 34 |

| 3 | Cod | lebook | x-based compression                                       | 37 |

|   | 3.1 | Intro  | duction                                                   | 37 |

|   |     | 3.1.1  | Codebooks-based representations                           | 38 |

|   |     | 3.1.2  | Using codebooks to represent CNN models                   | 40 |

|   | 3.2 | Codel  | book-based compression methodology                        | 42 |

|   |     | 3.2.1  | Target: general purpose systems                           | 43 |

|   |     | 3.2.2  | $Heterogeneous\ codebook-based\ compression\ strategy\ .$ | 44 |

|   |     |        | 3.2.2.1 Use of $E^2$ CNNs in contrast to single-instance  |    |

|   |     |        | model                                                     | 45 |

|   |     |        | 3.2.2.2 Per-layer iterative compression method            | 45 |

|   |     |        | 3.2.2.3 Sensitivity-based logarithmic batch optimization  |    |

|   |     |        | 3.2.2.4 Complexity analysis                               | 47 |

|   | 3.3 | Exper  | rimental results                                          | 48 |

|   |     | 3.3.1  | Experimental Set-up                                       | 48 |

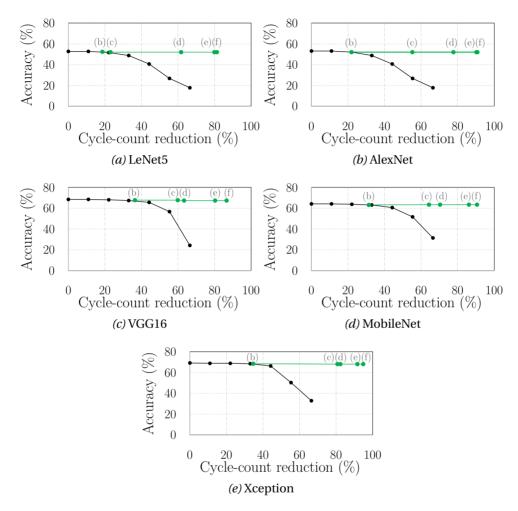

|   |     | 3.3.2  | Compression/Accuracy trade-off                            | 49 |

|   |     | 3.3.3  | Performance gains                                         | 52 |

| 4 | App | roxim  | ate Computing                                             | 55 |

|   | 4.1 | Intro  | duction                                                   | 55 |

|   |     | 4.1.1  | 11 0                                                      | 56 |

|   |     | 4.1.2  | Approximations in machine learning                        | 57 |

|   |     | 4.1.3  | Approximate multipliers                                   | 58 |

|   | 4.2 | Unlea  | ash inexact arithmetic in CNNs                            | 59 |

|   |     | 4.2.1  | Methodology overview: a co-design vision                  | 60 |

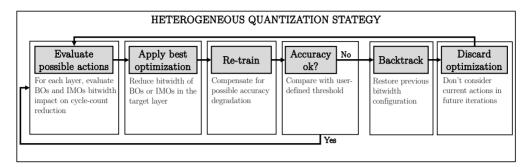

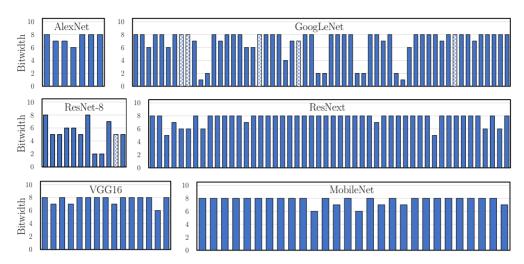

|   |     | 4.2.2  | Heterogeneous per-layer quantization                      | 60 |

|   |     |        | 4.2.2.1 Stage A: Robustness-Aware CNN Optimization        | 61 |

|   |     |        | 4.2.2.2 Stage B: Mapping on Inexact HW Resources          | 62 |

|   | 4.3 | Resul  | ts                                                        | 64 |

|   |     | 4.3.1  | Experimental Setup                                        | 64 |

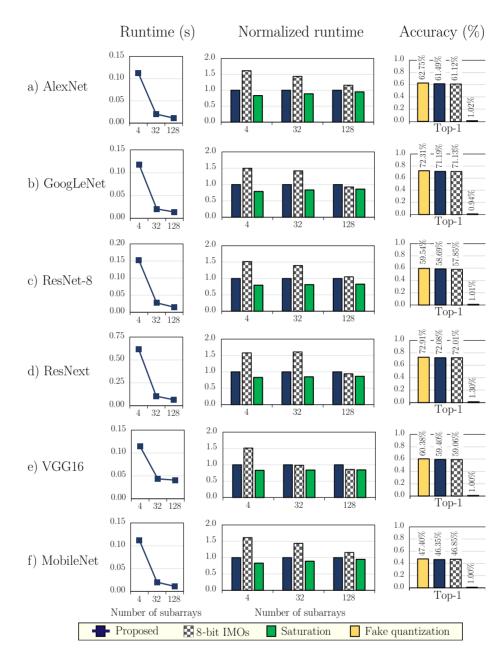

|   |     | 4.3.2  | Sensitivity analysis                                      | 67 |

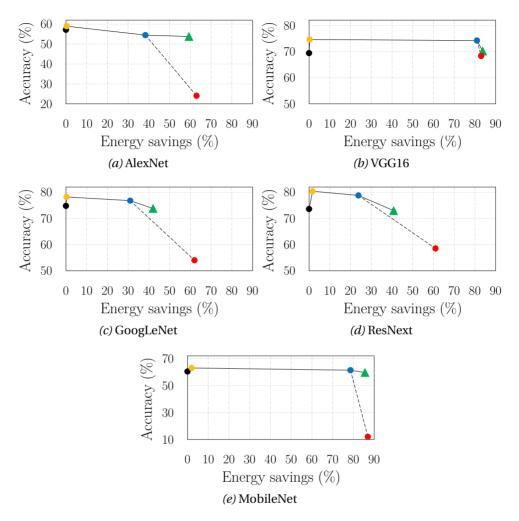

|   |     | 4.3.3  | Analysis of the QoS/Energy trade-off                      | 69 |

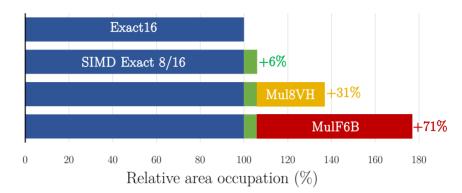

|   |     | 4.3.4  | Area overhead                                             | 73 |

|   | 4.4  | Concl  | usions .   |                                              | 74  |

|---|------|--------|------------|----------------------------------------------|-----|

| 5 | In-N | Memor  | y Compi    | ıting                                        | 77  |

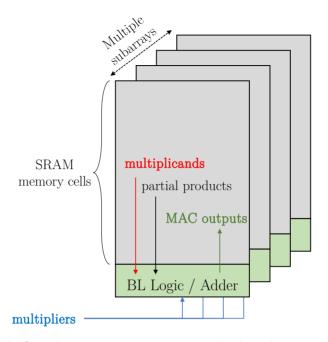

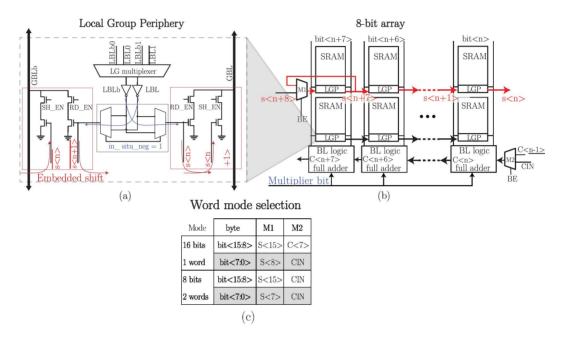

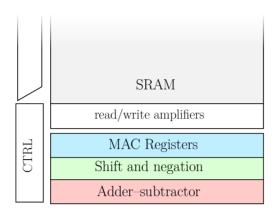

|   | 5.1  | IMC a  | ırchitectı | ıral design                                  | 78  |

|   |      | 5.1.1  |            | l implementations                            | 78  |

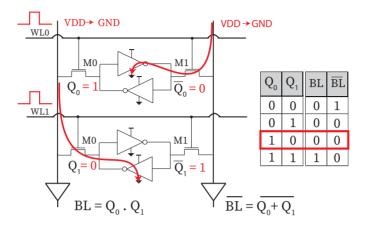

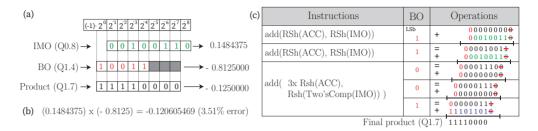

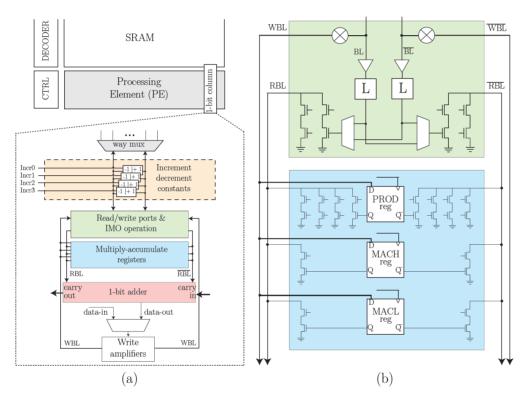

|   |      | 5.1.2  | •          | nenting multiply-accumulate operations       | 81  |

|   |      | 5.1.3  | -          | ications as a series of shift-adds           | 83  |

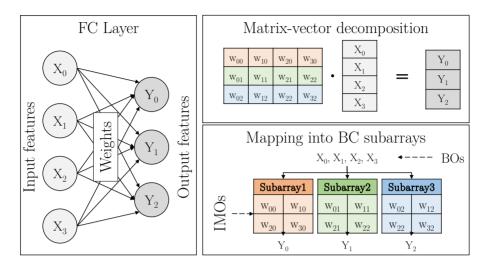

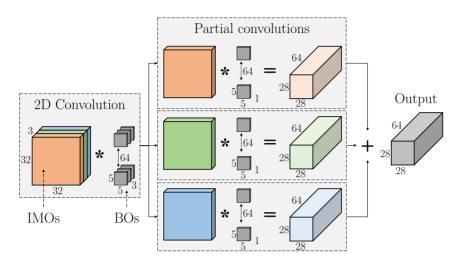

|   |      | 5.1.4  | -          | ating CNN layers                             | 86  |

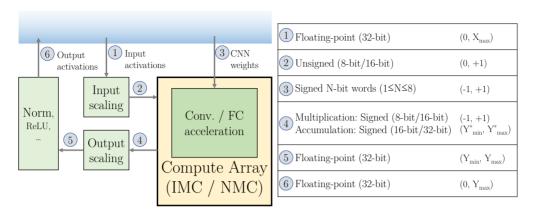

|   | 5.2  | An IM  | C-aware    | CNN quantization methodology                 | 90  |

|   |      | 5.2.1  |            | lology evaluation                            | 93  |

|   |      |        | 5.2.1.1    | Experimental Setup                           | 93  |

|   |      |        | 5.2.1.2    | Experimental Results                         | 94  |

|   | 5.3  | Mana   | ging ove   | rflows in IMC                                | 97  |

|   |      | 5.3.1  | Numeri     | ical overflows                               | 98  |

|   |      | 5.3.2  | Overflo    | w-free arithmetic for in-memory computing    | 99  |

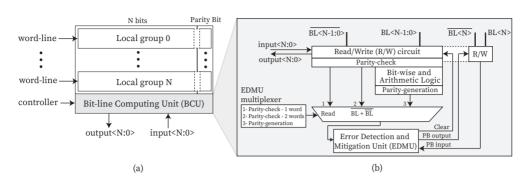

|   |      |        | 5.3.2.1    | Architectural design                         | 100 |

|   |      |        | 5.3.2.2    | Workflow for CNN acceleration                | 101 |

|   |      |        | 5.3.2.3    | Improved heterogeneous quantization strategy | 103 |

|   |      | 5.3.3  | Experin    | nental setup                                 | 105 |

|   |      |        | 5.3.3.1    | Baselines                                    | 105 |

|   |      |        | 5.3.3.2    | Benchmarks                                   | 106 |

|   |      |        | 5.3.3.3    | Pytorch-based environment for CNN training . | 107 |

|   |      |        | 5.3.3.4    | Accuracy and runtime evaluations             | 108 |

|   |      |        | 5.3.3.5    | IMC implementation                           | 108 |

|   |      | 5.3.4  | Experin    | nental results                               | 108 |

|   |      |        | 5.3.4.1    | Area and energy evaluation                   | 108 |

|   |      |        | 5.3.4.2    | Improved heterogeneous quantization method-  |     |

|   |      |        |            | ology                                        | 109 |

|   |      |        | 5.3.4.3    | Comparison with baselines                    | 110 |

|   | 5.4  | Scalin | ig SRAM    | voltage to improve efficiency                | 113 |

|   |      | 5.4.1  | Operati    | ng SRAMs at sub-nominal voltages             | 113 |

|   |      | 5.4.2  | SRAM p     | protection codes                             | 114 |

|   |      | 5.4.3  | IMC im     | plementation of memory parity check          | 115 |

|   |      |        | 5.4.3.1    | Detection and mitigation strategy            | 116 |

|   |      |        | 5.4.3.2    | Detection and mitigation circuit             | 118 |

#### **Contents**

|    |        | 5.4.4  | Experin   | nental Setup                                    | 119 |

|----|--------|--------|-----------|-------------------------------------------------|-----|

|    |        |        | 5.4.4.1   | Single-instance and $E^2\text{CNNs}$ benchmarks | 119 |

|    |        |        | 5.4.4.2   | Stuck-at fault error model                      | 120 |

|    |        |        | 5.4.4.3   | Energy and area evaluation                      | 122 |

|    |        | 5.4.5  | Experie   | mental results                                  | 123 |

|    |        |        | 5.4.5.1   | Area, energy and performance breakdown          | 123 |

|    |        |        | 5.4.5.2   | Accuracy/energy trade-off                       | 123 |

| 6  | Con    | cludin | g remarl  | <b>cs</b>                                       | 127 |

|    | 6.1    | Possib | le extens | sions of proposed approaches                    | 129 |

|    |        | 6.1.1  | Short-te  | erm                                             | 129 |

|    |        | 6.1.2  | Long-te   | rm                                              | 130 |

| Bi | bliog  | raphy  |           |                                                 | 133 |

| Cu | ırricı | ılum V | itae      |                                                 | 149 |

# Introduction

## 1.1 Artificial Intelligence

Artificial intelligence (AI) has been a research topic investigated by the computer science community for more than 60 years now. The term was first used in 1956 at the Dartmouth Conference, held at Dartmouth College, in the USA. Indeed, that conference is considered a milestone in the development of AI, although the roots of this approach can be traced even further. For example, the early foundations of AI can be found in the work of Alan Turing, who introduced the concept of universal machine [1] in 1936, paving the groundwork for the theoretical possibility of intelligent machines. Other key pioneers in the field of AI include Warren McCulloch and Walter Pitts, who introduced the concept of neural networks in 1943 [2]. In the years following the Dartmouth Conference, AI research gained momentum, and various algorithms and methods were developed. These include symbolic reasoning, expert systems, machine learning, and natural language processing. Since then, AI has received continuously growing attention, which led to significant progress and breakthroughs. An emblematic example of the incredible potential of AI in those years was represented by Deep Blue [3], an AI-based check player developed by IBM and able to defeat the world chess champion Garry Kasparov in 1997.

Over the years, numerous AI algorithms have been proposed. The *Logic Theorist* [4], developed by Allen Newell and Herbert A. Simon in 1956, was

one of the earliest AI programs, designed to prove mathematical theorems using symbolic logic and heuristic search. Two years later, Frank Rosenblatt presented the perceptron [5], a type of neural network algorithm aimed at mimicking the functioning of a biological neuron and able to recognize and classify patterns. The list of artificial intelligence algorithms grew faster and faster since then, with the introduction of more sophisticated and diverse AI algorithms encompassing areas such as machine learning, and, more recently, deep learning.

The high interest in AI is due to its capability to address a wide range of problems and challenges across a large pool of domains. A few examples of tasks and applications AI can efficiently handle include pattern recognition [6], predictive analytics [7], personalized recommendations [8], and fraud detection [9]. This ability makes these algorithms particularly appealing to solve tasks such as image recognition [10], speech recognition [11], and natural language processing [12]. In this context, AI finds application in fields like computer vision, voice assistants, and automated language translation, where Convolutional Neural Networks (CNNs) [13] represent widely investigated models. A more recent application of AI consists in providing personalized recommendations in various domains, such as e-commerce, streaming services, and content platforms, with AI-powered systems able to analyze user behavior and preferences. In all the presented applications, AI algorithms can also help in detecting anomalies in input data, identifying patterns of fraudulent behavior, and thus enhancing cybersecurity measures [14].

As a consequence of the vast range of opportunities offered by AI algorithms, several industries and scientific research areas are investing in this research topic. In healthcare, AI is currently used in medical imaging analysis, disease diagnosis, drug discovery, and personalized health monitoring using wearable systems [15–17]. Other sectors highly interested in employing AI as part of their software infrastructure include finance, manufacturing, education, and agriculture, as well as astronomy, genomics, drug discovery, climate modeling, and particle physics in scientific domains [18–20].

The reason why AI is so widely spread in almost every industrial and scientific application is due to the several advantages it provides when compared

to non-AI alternatives. First, AI can effectively handle complex and largescale input data. In particular, deep learning models efficiently deal with high-dimensional and unstructured data (e.g., images, audio, or text), being able to extract relevant features to ultimately produce accurate predictions. Second, the learning ability of AI algorithms allows them to improve their accuracy over time. An embodiment of this approach, known as reinforcement learning [21], enables these models to handle evolving situations, making their predictions and decisions better and better over a certain number of simulations. Finally, AI algorithms scale well to different degrees of task complexity and can discover intricate patterns that traditional approaches may not easily discern. Nonetheless, despite the aforementioned advantages, it must be noticed that AI algorithms are not always superior to non-AI alternatives. Usually, the choice between AI and non-AI approaches may depend on several factors, such as the specific problem, the type and the amount of available data, the available hardware resources, and the need for results interpretability [22].

#### 1.2 Convolutional Neural Networks

Among the plethora of AI, machine learning, and deep learning models proposed in the past years, this thesis focuses on Convolutional Neural Networks (CNNs) as target benchmarks, presenting different HW-SW co-design methodologies to optimize their execution from a resource, performance, energy, and accuracy perspectives. As detailed in the next paragraph, CNNs show different degrees of complexity, which make them good candidates to demonstrate the effectiveness of the proposed methodologies on a wide range of AI applications.

CNNs are indeed deep learning models that find applications in multiple fields, from computer vision [23,24] to personalized healthcare [25,26]. CNNs exhibit a layer-based structure, comprising convolutional, fully-connected, and pooling layers among the most common ones. These are combined in linear or more complex structures and enable the automatic extraction of features from input data (usually having spatial relationships, such as images), eventually producing abstract interpretations as output (e.g., recognizing objects, or classifying input samples). The parameters of CNN models, mainly

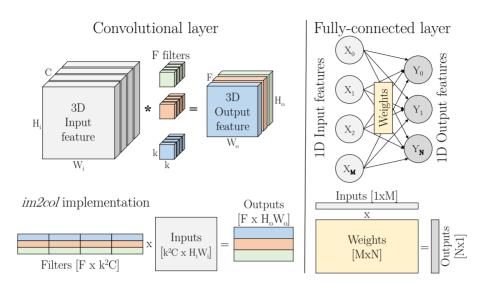

Figure 1.1: Computation of convolutional (left) and fully-connected (right) layers of neural network models. While fully-connected layers are naturally represented as matrix-vector operations, convolutions can be implemented in a similar way using an algorithmic transformation based on the im2col method (bottom).

used to perform convolutional and fully-connected layers, are referred to as weights. Conversely, the input and output features of each layer are known as activations.

Convolutional and fully-connected layers are the most compute-intense layers of CNNs, requiring the execution of millions of multiply-accumulate (MAC) instructions in recent models [27]. The former group together sets of learnable weights into multiple convolutional filters, which are then convolved over a region of the input data. Filters slide over the input features, producing a scalar output activation for each position covered. As a consequence, each filter produces as output a two-dimensional plane, and by employing multiple filters, convolutional layers can produce three-dimensional outputs. An example is illustrated in Figure 1.1(top-left), where three four-channel convolutional filters are applied to the four-channel input feature map to generate a three-channel output. Instead, in fully-connected layers, input and output elements, usually referred to as neurons, are connected

in a full-mesh topology by a matrix of weights, with output elements being computed using matrix-vector operations (Figure 1.1(top-right)).

Recent algorithms implement both convolutional and fully-connected layers as a series of matrix-vector multiplications. On one side, fully-connected layers are naturally represented as matrix-vector operations, with  $w_{i,j}$  being the element of the weight matrix connecting the i-th input to the j-th output, as shown in Figure 1.1(bottom-right). On the other side, convolutions can be transformed to matrix-vector multiplications as well by properly reshaping input weights and activations. This offers computing advantages, especially when implementing them in HW accelerators, and it can be obtained using the im2col algorithm [28]. This approach indexes weights of entire convolutional layers as a matrix, including in each row the unrolled values of a filter. A schematic overview of this approach is depicted in Figure 1.1(bottom-left).

To perform their task (e.g., classification, detection, or segmentation), CNNs must undergo a process, called training, that allows them to properly tune their weights to achieve good performance. Training can be implemented in different ways, but the most common is supervised training [29]. First, a dataset comprising input samples enriched with corresponding labels (e.g., the class the sample belongs to, in the case of classification problems) must be collected. Usually, samples are pre-processed, by resizing them according to specific input constraints of the target CNN model, and by normalizing their values (e.g., fitting them to a specific data range). The dataset is then divided into training, validation, and testing sets. The first one is used to actually train the model, with the validation set being used to evaluate its performance during the process. The testing set is instead used only after the training is completed, to measure accuracy on new data, unseen during the training stage.

The weights of the CNN are first initialized, usually randomly and following Gaussian distributions. Then, the CNN model is fed with the samples in the training set and its output predictions are compared with the correct labels (forward pass). This comparison is used to measure, using a loss function, the discrepancy between the predicted outputs and the true labels. Gradients with respect to the computed loss are then evaluated using a process called

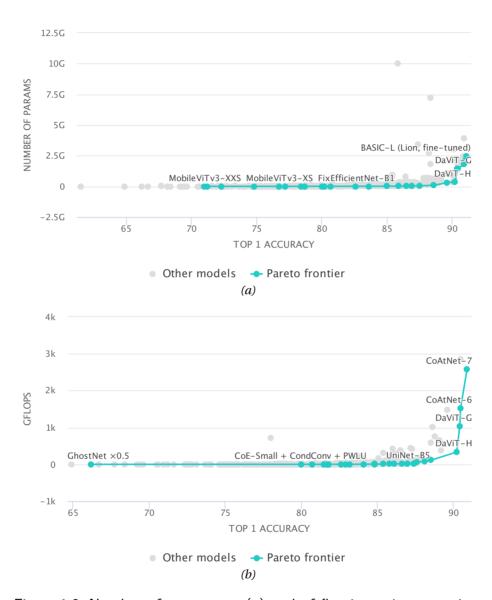

Figure 1.2: Number of parameters (a) and of floating-point operations (GFLOPS) (b) in state-of-the-art models designed for ImageNet classification. The highest accuracies are obtained with large and compute-intense models. Plots are extracted from <a href="https://paperswithcode.com">https://paperswithcode.com</a>

backpropagation, which propagates the gradients from the last layers of the CNN model to the first ones. Gradients are then used to update the weight values in each layer, in order to minimize the loss. Different algorithms have been proposed to implement the weights update, including Stochastic Gradient Descent (SGD), Adam, and RMSprop, among the most common. The validation set is then used to evaluate the new accuracy of the model, after the update of its parameters. The forward pass, the backpropagation, and the validation accuracy evaluation are repeated multiple times in an iterative procedure until the model accuracy converges or achieves acceptable performance. Once training is complete, the obtained model is tested on the so far unused testing set, to evaluate its performance on unseen data.

Figure 1.2 illustrates a summary of AI models proposed in the literature in the past years to solve image classification tasks. It compares them in terms of accuracy, as well as from memory and computing requirements perspectives. The best-performing architectures rapidly evolved to highly accurate implementations with extremely high memory and computing requirements. Indeed, the plots show that to achieve high accuracy, models tend to be larger and, in particular, increase their computing requirements, with billions of floating-point operations required in most models. This poses some challenges for the deployment of these models, especially when the execution is shifted from the cloud to the edge, as discussed in the following section.

## 1.3 Edge AI

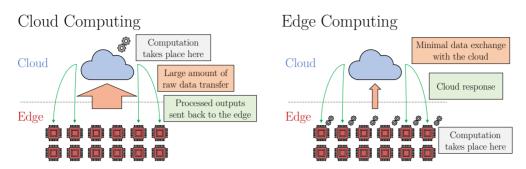

In the era of rapidly evolving technologies and increasing data generation, edge computing has emerged as an alternative to cloud computing as a promising paradigm for distributed data processing [30]. On one side, both the cloud and the edge computing approaches aim to provide computing capabilities and solutions to the end nodes deployed for different applications in the field of the Internet of Things (IoT). On the other side, they differ in terms of architectural design, processing capabilities, latency, scalability, degree of privacy, and resource utilization. An overview of the two computing paradigms is illustrated in Figure 1.3.

#### **Chapter 1. Introduction**

Figure 1.3: Comparison between the cloud computing and the edge computing approaches. By advocating data processing in the edge nodes, the amount of data collected at the edge and transmitted to the cloud is significantly reduced.

Cloud computing is a traditional approach that sees the end nodes mainly (or only) as data-collecting systems, leaving data processing to take place in large-scale data centers with high computing power and storage capacity (i.e., the cloud). Due to its centralized and high-performance architecture, cloud computing has the main advantage of providing high scalability and resource availability, being able to handle massive workloads and accommodating spikes in computing demand by provisioning additional resources [31].

Conversely, the edge computing paradigm is a decentralized approach that processes data at the network edge, where it is collected by the end nodes (or very close to it). Executing data processing workloads locally in the edge nodes offers several advantages. First, edge computing excels in low-latency and real-time scenarios because it minimizes the delay caused by transmitting data to remote servers. This makes it suitable for applications such as autonomous vehicles, industrial control systems, and, more in general, any real-time application. Second, for a similar reason, edge computing optimizes network bandwidth, since only the computed outputs, in contrast to the whole amount of collected inputs, are transmitted to the central cloud. Finally, it also addresses data security and privacy concerns by keeping sensitive data within the local network or device. The described advantages, as well as hardware technology and optimization methods advancements, are the core reasons for the rapid development of new edge computing solutions

in a wide range of applications. This also applies to artificial intelligence and goes under the name of *Edge AI*.

Nevertheless, new challenges arise in this context: one of the main limitations of edge computing resides in the hardware constraints of embedded devices, whose limited memory and computing resources can prevent the execution of large AI workloads. This problem is currently being investigated in the research community, which tackles it from different perspectives. It is also the main focus of this thesis, where I present different co-design methodologies combining application-level transformations with ad-hoc hardware optimizations to reduce memory, computing, and energy requirements in Edge AI inference.

## 1.4 Optimizations for Edge AI

Optimizations supporting Edge AI can be broadly divided into three main categories. First, continuous technology improvements and, in particular, CMOS technology scaling, allow new generations of embedded devices to be equipped with higher-capacity memories and faster computing units. However, these advancements are currently slowing down, while the requirements of AI workloads are increasing at a fast pace [32]. Therefore, Edge AI optimizations tackle the computing and efficiency challenges of edge computing from two other perspectives, widely investigated in the research community. This thesis shows how these two optimization paths can be merged to retrieve larger efficiency gains.

## 1.4.1 Application-level optimizations

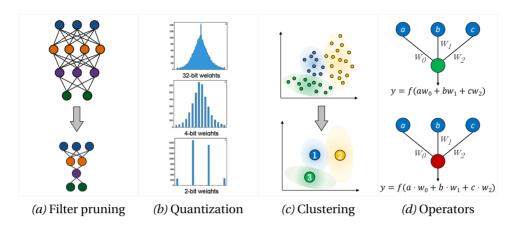

On one hand, algorithmic-level optimizations aim at reducing the complexity of AI workloads. Several techniques have been proposed so far. *Quantization* is a popular method that reduces the precision of input and output operands from the traditional 32-bit floating-point format to more compact integer representations [33,34]. Common quantization levels include 8-bit and 16-bit schemes. Thus, quantization effectively reduces memory requirements, but can also improve efficiency as integer arithmetic requires simpler circuits than the ones required to manage floating-point formats. Targeting the same

objectives, *pruning* is another approach to reduce complexity, especially in machine learning and deep learning models [35,36]. It removes specific computing elements from the original model and it is often applied to CNN models. Such an approach can be effectively applied due to the intrinsic redundancy of AI models, so that pruned architectures can still achieve acceptable accuracy levels. In the case of CNNs, pruning is usually applied to convolutional layers, either removing specific weights (fine-grain pruning) or removing entire convolutional filters (coarse-grain pruning). In addition to quantization and pruning methods, *weights encoding* [37,38] and *weights clustering* [39] are other examples of strategies sometimes used to further shrink the memory needs of AI workloads. Most of these methods are orthogonal or complementary to each other and are hence often applied in synergy.

#### 1.4.2 Hardware-level optimizations

On the other hand, hardware-level optimizations play a crucial role in achieving high-performance and energy-efficient Edge AI solutions and focus on providing AI applications with specific physical resources to efficiently execute the typical computing patterns of these workloads. To this end, ultralow power processors have been designed for embedded systems to limit energy consumption. An example is the PULP platform [40], specifically designed to address the requirements of energy-efficient and high-performance computing in resource-constrained environments. It consists of a family of open-source processor cores optimized for ultra-low power consumption, that enable the implementation of parallel processing systems. The cores within the PULP platform are based on the RISC-V instruction set architecture [41], which enables customization and optimization. Targeting AI workloads, PULP also includes features and extensions that support AI algorithms, such as specialized instructions and hardware accelerators for efficient matrix operations, which are fundamental to many AI computations such as neural network inference.

In addition to low-power processors, dedicated hardware accelerators are largely employed in the field of Edge AI. Typical specialized units include Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGAs),

or Application-Specific Integrated Circuits (ASICs), which trade off computing flexibility for efficiency. Focusing on deep learning accelerators, two very popular classes of dedicated processing elements include systolic arrays [42] and neuromorphic accelerators [43]. The former consist of a grid of processing elements (PEs) interconnected in regular patterns to synchronously share data. These grids are often programmable, enable high levels of parallelism and data reuse, and, thanks to their structure, are particularly well-suited for energy-efficient executions of matrix-vector operations, which are indeed the core computing patterns of the majority of deep learning algorithms. Neuromorphic accelerators are instead inspired by the functionality of the human brain and excel in the execution of neural networks. By leveraging the inherent sparsity and irregularity of neural networks, and by simulating the sparse nature of neural activity, these accelerators reduce computational requirements and memory bandwidth, leading to significant efficiency gains. Sparsity-driven techniques, such as spike-based coding and event-driven processing, enable the selective and efficient processing of relevant information. Additionally, they also support on-chip learning and adaptability, allowing them to continuously learn and evolve with the data they process. A recent and revolutionary class of accelerators for Edge AI is represented by In-Memory Computing (IMC) devices [44,45]. The IMC paradigm overcomes the traditional Von Neumann architecture by moving computation where data resides (or very close to it). By performing arithmetic and logic operations inside (or at the proximity of) the storage elements, IMC minimizes data movements and latency, enabling efficient and high-performance Edge AI solutions.

Another venue to reduce the energy cost of Edge AI workloads is the approximate computing paradigm [46–48]. The key idea is that inexact, yet simpler, arithmetic circuits can produce approximate outputs that can still lead to acceptable output quality levels. Thus, they trade off precision for faster and less energy-expensive executions. Common approximate operators include adders and multipliers, as highly stressed computing units in AI inferences [49, 50].

Finally, dynamic voltage and frequency scaling (DVFS) is a method that optimizes power consumption by adjusting the supply voltage and the operating frequency at which the system operates. Although not deeply investigated in the literature on AI optimization methodologies, few previous works have studied the impact of this technique from an energy-saving perspective [51,52]. Since the voltage level is quadratically proportional to power consumption, its reduction can lead to significant energy savings, but it should be carefully tailored to avoid impacting performance and Quality of Service (QoS). In fact, errors can appear in the memory sub-system as a result of DVFS techniques: when reducing the voltage in SRAMs, stuck-at faults emerge as weaker bit-cells cannot be correctly written. Alternatively, when reducing the operating frequency in DRAMs, the resulting lower refresh rates can make bit-cells lose their content.

# 1.5 Trading-off accuracy for efficiency

Most of the optimization methods presented in the previous sections introduce data approximations or computation errors. For example, quantization and clustering adjust the weights of AI models, forcing them to assume specific values, hence being equivalent to a form of data approximation. Similarly, inexact operators introduce approximations in the performed computation, while pruning approximates the input-output relation by reducing the complexity of the involved functions. Aggressive voltage scaling can introduce stuck-at faults when applied to memory elements, as weaker bit-cells do not receive enough energy to flip their content during write operations.

As a result, different degrees of inexactness usually affect inferences in Edge AI when the presented optimization methods are applied. Nevertheless, the research community has demonstrated that, up to a certain degree, these techniques do not significantly affect output quality [53–55]. In fact, the redundant structure and sparse nature of most ML models (e.g., random forests and neural networks) make them intrinsically tolerant toward a certain level of inexactness. This is why it is possible to retrieve essential efficiency improvements by introducing specific magnitudes of approximation so that the desired QoS can still be achieved. Importantly, the algorithmic characteristics of ML models cannot provide a designer with a priori knowledge of the accuracy impact of a specific error density or noise level. In other words, it is not possible to determine, at design time, the accuracy degradation that

a certain model experiences when one of the aforementioned optimization approaches is employed. For example, voltage reductions may cause memory errors, which randomly affect memory bit-cells. As a consequence, the impact of these faults will be different based on the affected cells: for example, errors affecting the most significant bits (MSb) of a word usually introduce larger variations than errors affecting the least significant bits (LSb).

The methodologies for optimizing Edge AI applications that I present in this thesis take into account and address this challenge: I will show different strategies to optimize AI workloads, combining algorithmic-level and hardware-level methods to increase achievable gains. In all proposed design methodologies, I will include accuracy constraints to drive the optimization procedures. This approach, sometimes overlooked in state-of-the-art studies, enables the optimizations of AI applications from memory, performance, and energy perspectives, while also abiding by user-defined accuracy levels. As previously discussed, I consider CNN models as target benchmarks for evaluating the proposed Edge AI methodologies. Nonetheless, the majority of the presented solutions and techniques can be naturally extended to different models in the field of AI.

Effective integration between hardware and software is crucial for optimizing Edge AI systems from energy and performance points of view. On one hand, hardware-aware software optimization, such as algorithmic transformations and quantization can adjust AI models in order to maximize the utilization of hardware resources and effectively leverage them. On the other hand, software-aware accelerators can be designed to efficiently implement specific computing patterns of the target workload or application domain. Without such a co-design vision, the risk of not being able to fully exploit the potential of the applied optimization is high. For example, very fine-grained quantization levels cannot reach the desired shrink of memory requirements if the target platform only supports 32-bit data. Dually, reducing the voltage to save energy cannot be a practical solution if the application is not robust enough to cope with the potential memory errors deriving from this technique. Starting from these considerations, the next chapters describe codesign methodologies targeting domains where different classes of hardware resources are available.

First, I introduce the concept of *Embedded Ensembles of Convolutional Neural Networks* ( $E^2CNNs$ ), an algorithmic-level transformation I propose to improve robustness against errors in neural network models.  $E^2CNNs$  combines pruning and replication to construct ensemble-based models that benefit the higher accuracy and resiliency of state-of-the-art ensembles, but without increasing the requirements of the baseline single-instance model. Then, I take advantage of the characteristics of  $E^2CNNs$  to retrieve high-efficiency gains in a wide spectrum of AI co-designs.

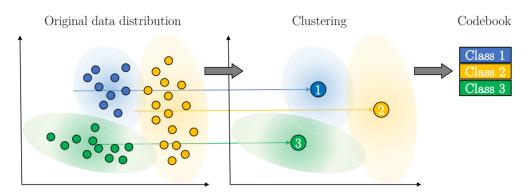

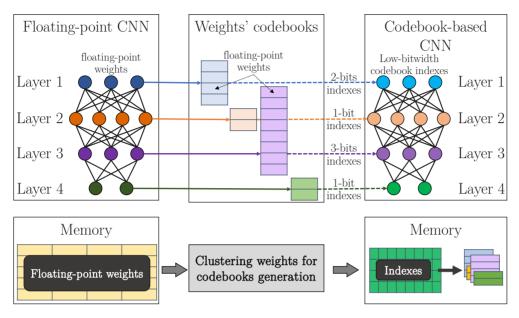

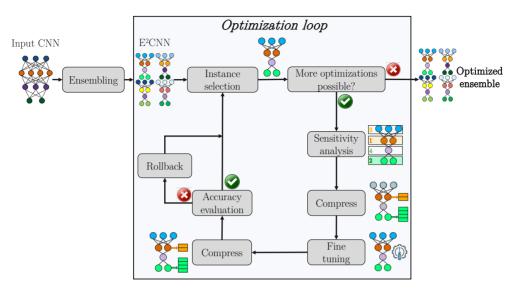

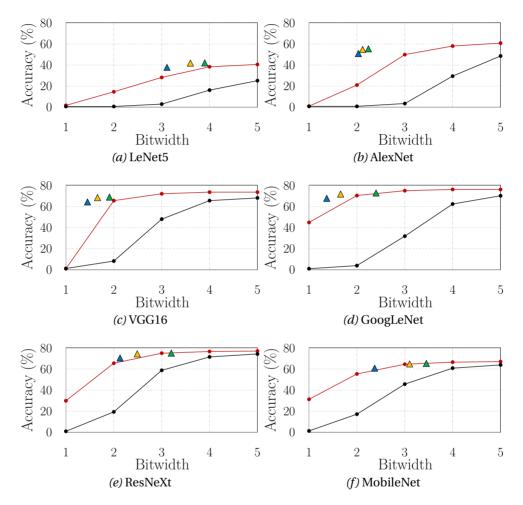

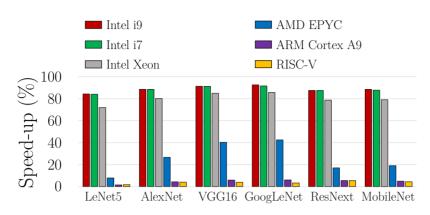

I initially focus on general-purpose processing units as target hardware resources. In this case, ad-hoc hardware accelerators may not be available, thus posing a limit to the pool of algorithmic-level optimizations that can be effectively exploited in hardware. I propose a methodology based on codebook-based optimizations, a class of algorithmic-level transformations that effectively reduce the computing and memory requirements of AI models. By tightly limiting the number of unique weight values, they allow the storage of representative parameters in small look-up tables (i.e., codebooks) containing a limited number of floating-point entries. AI models are then represented as low-bitwidth indexes of such codebooks, enabling model compression while preserving floating-point inference. I introduce a novel methodology that employs an E<sup>2</sup>CNNs design and finds highly beneficial codebook schemes, trading off accuracy for model compression in codebook-based models.

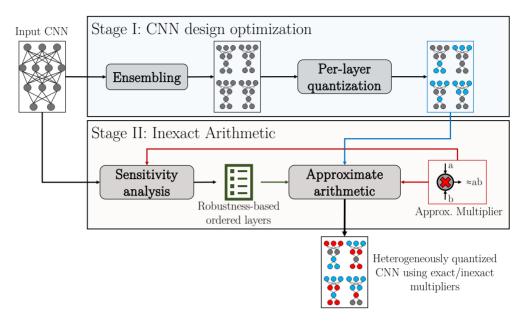

Then, I consider the availability of approximate hardware as a design choice to reduce energy in Edge AI. Indeed, previous studies have demonstrated that, up to a certain degree, AI models can tolerate noisy input data and inaccurate intermediate results, ultimately being still able to produce acceptable output qualities. Nonetheless, when dealing with arithmetic inexact operators, a judicious use of approximation is crucial to limit accuracy degradation. Determining the magnitude of inexactness that can be introduced is a challenging task because the implementation of inexact operators is often decided at design time when the application and its robustness profile are unknown. The result is a risk of over-constraining or over-provisioning the hardware. To bridge this gap, I propose a two-stage optimization that initially optimizes the target model, applying E<sup>2</sup>CNNs in conjunction with a heterogeneous

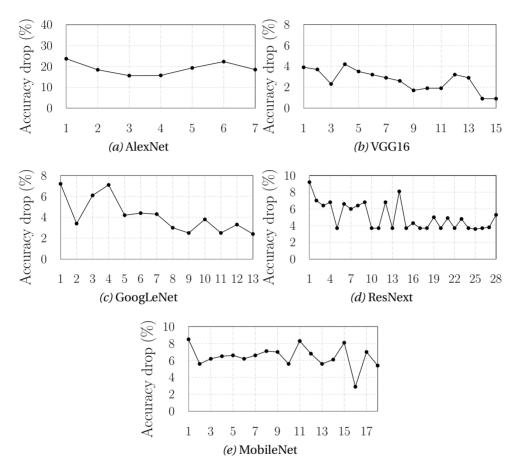

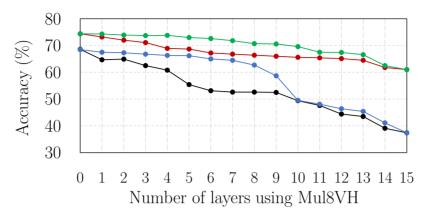

quantization strategy. This phase reduces the bitwidth of input and output operands enhancing at the same time error resiliency, so that inexact operations can be performed as frequently as possible. Then, a sensitivity analysis is performed and used to drive the mapping of computing kernels into either exact or inexact hardware.

Finally, I target In-Memory Computing (IMC) accelerators, proposing different implementation and algorithmic optimization approaches to maximize energy savings when running AI inferences. In fact, IMC supports the efficient execution of data-centric workloads, such as those characterizing AI algorithms. These accelerators provide computing capabilities as part of the memory array structures, bringing the processing elements inside storage. By doing so, IMC minimizes the cost of data access and enables highly parallel computations by exploiting the regular structure of memory arrays. However, the regular layout of memory elements also constrains the data range of inputs and outputs, since the bitwidths of operands and results stored at each address cannot be freely varied. To tackle this challenge, I introduce a novel optimization heuristic, which tailors the quantization levels according to both memory design characteristics and workloads considerations. I also show how lightweight hardware support is required in the proximity of storage elements to increase computing parallelism and to ensure overflow-free arithmetic under strict bitwidth constraints. Finally, I combine most of the presented techniques and methodologies in a more complete co-design approach. On the one hand, I show that highly effective error detection and mitigation strategies can be implemented in IMC devices with little extra hardware. On the other hand, I use algorithmic transformations including E<sup>2</sup>CNNs and quantization to increase the robustness of AI models against errors. In doing so, more aggressive voltage scaling techniques can be applied to run the accelerator relying on ultra-low supply voltage levels. While this approach inevitably introduces errors in the memory arrays, the higher degree of resiliency exposed by algorithmic optimization minimizes the impact of such errors on the output quality of the model.

# **Embedded Ensembles of Convolutional Neural Networks**

Herein, I present *Embedded Ensembles of Convolutional Neural Networks* ( $E^2CNNs$ ), a methodology to build memory- and compute-constrained ensemble-based models. First, in Section 2.1, I include a brief analysis of CNN and ensemble-based models, discussing the two alternative implementations in terms of timing and resource requirements and from an error resiliency perspective. Then, I detail the  $E^2CNNs$  methodology in Section 2.2, describing how to construct and train constrained ensembles, analyzing their benefits with respect to state-of-the-art ensembles of CNNs. Finally, in Section 2.3, I evaluate the  $E^2CNNs$  design by comparing different  $E^2CNNs$  configurations to the corresponding baseline single-instance CNNs. This methodology has been presented in [56].

## 2.1 Introduction

#### 2.1.1 Robustness of CNN models

In many real-world scenarios, input data is often corrupted by noise or errors. Measurement imprecision, interference, memory faults, or incorrect data transmission are just a few examples of data corruption sources [57–59]. In such situations, it is crucial to have robust algorithms that can tolerate such inaccuracies and still provide accurate and reliable outputs. In this regard, machine learning models happen to be highly resilient to input noise and data approximations [48, 53]. In particular, CNN models well tolerate errors

# Chapter 2. Embedded Ensembles of Convolutional Neural Networks

Table 2.1: Yield analysis showing the percentage of simulated chips with accuracy degradation limited to 5% for an industrial CNN model used for capsule recognition at different sub-nominal voltage levels. Error rates at different voltage supplies are derived from [51].

| Voltage          | 850 mV | $750 \mathrm{mV}$    | 700  mV              | 650  mV              | $600 \mathrm{mV}$    |

|------------------|--------|----------------------|----------------------|----------------------|----------------------|

| Error rate       | 0      | $1.3 \times 10^{-5}$ | $1.0 \times 10^{-4}$ | $7.0 \times 10^{-4}$ | $2.2 \times 10^{-3}$ |

| Floating-point   | 100.0% | 11.2%                | 0.0%                 | 0.0%                 | 0.0%                 |

| Fixed-point 8/16 | 100.0% | 100.0%               | 99.5%                | 66.3%                | 0.2%                 |

in the processed data, thus being able to offer acceptable output quality, even in non-ideal conditions [54]. Nevertheless, these models are nowadays employed in a vast range of applications, that typically require different degrees of robustness and must abide by specific Quality of Service (QoS) metrics. For example, computer vision, speech recognition, or natural language processing applications can tolerate a certain degree of QoS degradation without significantly affecting their overall performance and user experience. On the contrary, the quality of the output is a must in sensitive or safety-critical applications, such as medical diagnosis, autonomous driving vehicles, financial forecasting, and industrial automation.

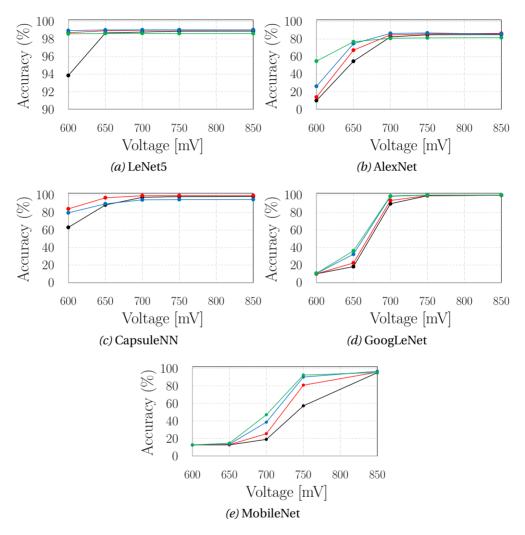

To investigate the robustness of CNN models against errors, my colleagues and I have evaluated the impact of data representation in a proprietary CNN model used for coffee capsule recognition [60]. In particular, our analysis considered memory errors due to sub-nominal voltage supplies in the memory sub-system, producing stuck-at faults in the input data, also impacting the whole inference execution. We have conducted experiments varying the voltage level to evaluate the accuracy degradation at different error rates. For each of them, we have considered 1000 random error maps which emulate different fabricated memory chips. Finally, we have performed a yield analysis to measure the percentage of chips that were able to achieve accuracies within 5% of the baseline. A simplified, yet not reductive, overview of the results obtained in [60] is presented in Table 2.1, comparing the yield achieved by a floating-point model with the one obtained quantizing weights

and activations using 8 and 16 bits, respectively (i.e., a scheme I refer to as 8/16 quantization level). These results provide multiple insights: first, the yield obtained at a nominal voltage (i.e., 850 mV) confirms that, if properly designed, quantization has a negligible impact on accuracy. More precisely, accuracy evaluations showed that the accuracy degradation with respect to the floating-point baseline is negligible when employing an 8/16 quantization scheme. Second, results indicate that a fixed-point format is significantly more robust than floating-point representations, achieving a yield of 99.5% at 700 mV, where instead none of the chips employing a floating-point representation can reach the target accuracy level. The higher sensitivity toward memory errors of the floating-point implementation can be explained by considering the peculiar memory representation of floating-point values. In fact, the distinction between sign, exponent, and mantissa bits may be critical if errors affect certain bit positions: for example, errors affecting the sign bit produce dramatic deviations in high-magnitude floating-point numbers. In a similar way, errors affecting the exponent bits can transform relatively small values into high-magnitude ones, and vice-versa. In addition, specific floating point codes are used to represent  $\pm \infty$  and not-a-number (NaN) values. As a consequence, if errors make them appear, these values propagate through the CNN layers, preventing arithmetic computation and thus producing unreliable outputs. In contrast, fixed-point formats do not suffer similar effects, as, in the worst case, errors affecting the sign or the most significant bits can have a significant, but not so critical, impact.

As a result, this analysis shows that fixed-point representations are key for the resiliency of CNN models and, if properly dimensioned, these formats do not even affect the baseline floating-point accuracy. In line with the results presented in related works [54, 55], this analysis demonstrates the intrinsic resiliency of (quantized) CNN models. Nevertheless, above a certain threshold, the error density results in high-magnitude data perturbations that dramatically degrade output quality. Error protection mechanisms and algorithmic strategies to improve the robustness against errors have a double target. On one hand, mitigating the impact of errors by limiting noise or introducing error detection mechanisms (e.g., parity check or memory error correction codes) is crucial in safety-critical applications. On the other hand,

# Chapter 2. Embedded Ensembles of Convolutional Neural Networks

an increased robustness against errors can be leveraged to enable more aggressive optimization strategies, ultimately achieving improved energy efficiency levels for a minimal accuracy cost, as discussed in Chapter 1.

While several approaches to improve the accuracy and robustness of CNN models exist [61–63], I am now going to focus on ensembling methods [64–66], proposing a novel way to construct ensemble-based models for Edge AI inference.

#### 2.1.2 Ensembling

In machine learning, ensembling is a technique that combines together multiple algorithmic instances to create a more robust and accurate model [67]. The core idea is that by combining the predictions of several *weak* models, the errors and biases of individual models can be offset, leading to a more precise and reliable overall prediction.

As deeply detailed in [67], there are several ways to perform ensembling in machine learning applications, including:

- Bagging. It consists in training multiple models on random subsets of the training data and then combining their predictions to produce the output result. Bagging is often used with decision tree models, creating a random forest ensemble.

- Boosting. In this technique, multiple weak models are trained sequentially, with each new one trained on the residuals of the previous model.

The final prediction is then a weighted average of the predictions of all the trained instances.

- *Stacking*. It involves training multiple instances and using their predictions as input features for a higher-level model, making the final prediction. This approach can be particularly effective when the individual instances are trained on different aspects of the data, allowing the higher-level model to learn from a wider range of features.

Ensembling is a powerful technique that has been used with great success in many areas of machine learning, including image recognition, natural language processing, and speech recognition [64,65].

While bagging mainly operates on dataset splits and, like boosting, is commonly used to build random forests, stacking is instead a more general ensembling method that has been also applied to CNN models [66], and hence considered in this chapter. In this regard, it employs multiple CNN instances, possibly sharing different structures, and combines together their individual predictions to compute the ensemble output. Depending on the objective task, aggregation can be implemented either as a simple average of individual predictions of each CNN instance in the ensemble or using those predictions to feed (and tune) an additional meta-model. The meta-model, typically a very simple machine learning model, eventually uses these predictions as input features to produce the final output.

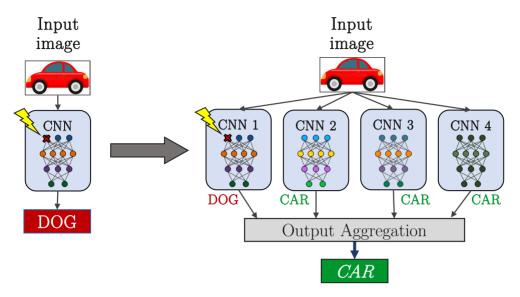

One of the key advantages of stacking is that it can handle complex relationships between features and target variables. By combining the predictions of multiple models, stacking enables the capture of a wider range of patterns and features from the input data, leading to improved accuracy and generalization performance. Even more, ensemble-based architectures also increase resiliency against errors. Figure 2.1 illustrates this concept by comparing the effect of an error in a single-instance CNN model (left) and in an ensemble of four CNNs (right). This simple example shows that an error affecting the first layer of the single-instance CNN model results in a wrong classification of the input image. On the other hand, the same error affecting the first instance of the ensemble still produces a misclassification in the first CNN instance. Nonetheless, the wrong prediction can be mitigated by the correct predictions of the other three instances, ultimately allowing the ensemble to correctly classify the input sample.

Stacking but, more in general, any ensembling method, is computationally expensive, requiring careful tuning of the base models and, if included, of the meta-model. Let's consider the example depicted in Figure 2.1, assuming the four models in the ensemble-based design share the same structure. The higher accuracy and resiliency of the ensemble-based architecture are

Figure 2.1: Single-instance CNN model (left) and a state-of-the-art ensemble-based alternative comprising four CNN instances (right). While leading to misclassification in the single-instance model, the same error can be mitigated in an ensemble-based implementation.

achieved at the cost of memory and computing overheads. In particular, memory requirements increase by  $4\times$  because four CNN models have to be stored in memory. Similarly, inference runtime also increases by a similar factor, as four CNN models must be evaluated. In general, overhead may be even larger, since in some cases tens or hundreds of CNN models are combined together [68, 69].

Therefore, while the accuracy and robustness gains of state-of-the-art ensembles are key for most applications, their actual deployment in edge devices is often prohibitive, due to the memory, timing, and energy constraints of embedded systems. To address this limitation, I propose Embedded Ensembles of Convolutional Neural Networks (E<sup>2</sup>CNNs) [56], a methodology to build and deploy ensembles in edge AI applications. As the name suggests, it targets CNN models, although the key concept of this methodology could be applied to different machine learning models.

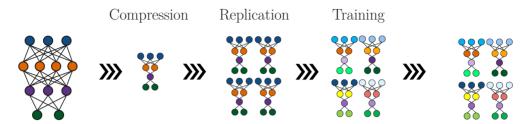

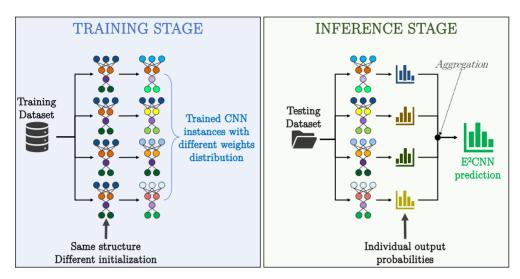

Figure 2.2: E<sup>2</sup>CNNs methodology. The baseline CNN model is first compressed to reduce its complexity. Then, the obtained (pruned) structure is replicated multiple times to build an ensemble that has the same properties as the baseline model. Each instance is trained from initial random weight initialization, resulting in different trained weights distribution, key to improving accuracy and robustness.

# 2.2 E<sup>2</sup>CNNs methodology

E<sup>2</sup>CNNs transforms a target CNN model into an equivalent ensemble-based architecture. Targeting edge devices, the objective is to construct ensembles of CNN models that do not increase the memory and computing requirements of the initial single-instance network. To achieve this goal, E<sup>2</sup>CNNs combines pruning and replication to construct ensembles that benefit from the higher accuracy and robustness of state-of-the-art ensembles, but without increasing baseline requirements.

# 2.2.1 Building the ensemble

The proposed methodology to build  $E^2$ CNNs is summarized in Figure 2.2. The first step is to compress the baseline single-instance structure to reduce its complexity. In particular, the input can be an *untrained* CNN architecture, and the compression stage reduces the number of parameters (i.e., weights and biases of convolutional and fully-connected layers), as well as the number of multiply-accumulate (MAC) operations required to execute the network. In general, both metrics are reduced by a factor N. Compression is performed via filter pruning [35]. Since the input single-instance structure is an untrained architecture, random filter pruning is used. This approach removes random filters from the convolutional layers of the input

Figure 2.3: E<sup>2</sup>CNNs training (left) and inference (right) stages. Training is performed offline, before deploying the ensemble in the target application. At inference time, the same sample is processed by all trained instances, with a final aggregation step producing the E<sup>2</sup>CNNs prediction.

CNN. While more advanced filter pruning methods have been proposed [36], the pseudo-randomness selection of filters to remove makes this approach one of the few approaches suitable for untrained CNN structures. To avoid over-compressing certain layers and under-compressing others, filter pruning homogeneously compresses the whole architecture.

The resulting pruned structure exhibits  $N \times$  fewer parameters and  $N \times$  less MAC operations than the initial model. As a consequence, the obtained pruned CNN can be replicated N times to build an ensemble of CNNs with N instances, without incurring any memory or computing overheads with respect to the initial single-instance baseline.

Before their deployment in the field for inference executions, the N models must first be trained. Training is performed offline, before deploying  $E^2CNNs$  in the target device. A high-level scheme showing the two distinct phases is presented in Figure 2.3. Each pruned CNN is independently trained on the entire training dataset, starting from a random initialization of the model

| LeNet5                                                      | In/Out Feature Size                                                                                                                                                                                                                                                          | MACs                                  | Params                           |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|

| Convolutional                                               | $32 \times 32 \times 1 \longrightarrow 28 \times 28 \times 6$                                                                                                                                                                                                                | 117,600                               | 156                              |

| Max Pool                                                    | $28 \times 28 \times 6 \longrightarrow 14 \times 14 \times 6$                                                                                                                                                                                                                | -                                     | -                                |

| Convolutional                                               | $14 \times 14 \times 6 \longrightarrow 10 \times 10 \times 16$                                                                                                                                                                                                               | 240,000                               | 2,416                            |

| Max Pool                                                    | $10 \times 10 \times 16 \longrightarrow 5 \times 5 \times 16$                                                                                                                                                                                                                | -                                     | -                                |

| Convolutional                                               | $5 \times 5 \times 16 \longrightarrow 1 \times 1 \times 120$                                                                                                                                                                                                                 | 48,000                                | 48,120                           |

| Fully-Connected                                             | $120 \longrightarrow 84$                                                                                                                                                                                                                                                     | 10,080                                | 10,164                           |

| Fully-Connected                                             | $84 \longrightarrow 10$                                                                                                                                                                                                                                                      | 840                                   | 850                              |

|                                                             | Totals                                                                                                                                                                                                                                                                       | 416,520                               | 61,706                           |

|                                                             |                                                                                                                                                                                                                                                                              |                                       |                                  |

| 2-E <sup>2</sup> CNNs instance                              | In/Out channels                                                                                                                                                                                                                                                              | MACs                                  | Params                           |

| <b>2-E<sup>2</sup>CNNs instance</b> Convolutional           | In/Out channels $32 \times 32 \times 1 \longrightarrow 28 \times 28 \times 4$                                                                                                                                                                                                | MACs 78,400                           | Params<br>104                    |

|                                                             |                                                                                                                                                                                                                                                                              |                                       |                                  |

| Convolutional                                               | $32 \times 32 \times 1 \longrightarrow 28 \times 28 \times 4$                                                                                                                                                                                                                |                                       |                                  |

| Convolutional<br>Max Pool                                   | $32 \times 32 \times 1 \longrightarrow 28 \times 28 \times 4$ $28 \times 28 \times 4 \longrightarrow 14 \times 14 \times 4$                                                                                                                                                  | 78,400<br>-                           | 104                              |

| Convolutional Max Pool Convolutional                        | $32\times32\times1\longrightarrow28\times28\times4$ $28\times28\times4\longrightarrow14\times14\times4$ $14\times14\times4\longrightarrow10\times10\times10$                                                                                                                 | 78,400<br>-                           | 104                              |

| Convolutional<br>Max Pool<br>Convolutional<br>Max Pool      | $32\times32\times1\longrightarrow28\times28\times4$ $28\times28\times4\longrightarrow14\times14\times4$ $14\times14\times4\longrightarrow10\times10\times10$ $10\times10\times10\longrightarrow5\times5\times10$                                                             | 78,400<br>-<br>100,000<br>-           | 104<br>-<br>1,010<br>-           |

| Convolutional Max Pool Convolutional Max Pool Convolutional | $32\times32\times1 \longrightarrow 28\times28\times4$ $28\times28\times4 \longrightarrow 14\times14\times4$ $14\times14\times4 \longrightarrow 10\times10\times10$ $10\times10\times10 \longrightarrow 5\times5\times10$ $5\times5\times10 \longrightarrow 1\times1\times80$ | 78,400<br>-<br>100,000<br>-<br>20,000 | 104<br>-<br>1,010<br>-<br>20,000 |

Table 2.2: LeNet5 vs. LeNet5-based 2-E<sup>2</sup>CNNs structure

weights. In this way, the resulting trained CNN instances will show different weights distributions, which ultimately allow E<sup>2</sup>CNNs to improve its generalization capabilities and robustness. Notice that an ensemble where all the CNN instances have the same weight values will perform exactly like each individual instance would perform alone. Finally, the trained models are deployed in the field. To act as an ensemble, the individual predictions of each CNN instance are combined together using a simple output average.

# 2.2.2 Example: LeNet5 vs. LeNet5-based E<sup>2</sup>CNNs

This section presents an example showing a very simple CNN model being transformed into an  $E^2$ CNNs equivalent. For simplicity, this example considers LeNet5 [70] as the baseline single-instance CNN, and an  $E^2$ CNNs

# Chapter 2. Embedded Ensembles of Convolutional Neural Networks

implementation composed of two instances (in the rest of this thesis, I use the N-E<sup>2</sup>CNNs notation to refer to ensembles of N instances).

The structure of LeNet5 is reported in Table 2.2(top). It consists of three convolutional layers and two fully-connected (FC) layers, with two additional pooling layers to reduce input dimensionality. The second column of the table reports the size of input and output features for each layer, in the form  $W \times H \times C$ , with W, H, and C being the width, height, and depth of the corresponding feature maps, respectively. Next, the last two columns show the number of MAC operations executed in each layer and the number of weights required for their execution. Pooling layers have no parameters and their complexity is negligible compared to convolutional and FC layers. In total, LeNet5 executes more than 400K MAC operations per inference and needs more than 60K parameters.

Building 2-E<sup>2</sup>CNNs requires halving both the memory and the computing requirements of LeNet5. The result of the pruning stage is shown in Table 2.2 (bottom). Filter pruning reduces the number of filters in the three convolutional layers, from the baseline 6, 16, and 120 filters, to the 4, 10, and 80 filters applied by the pruned model. The reduction of the number of filters has a positive effect on both memory size (since fewer filters must be stored) and performance (since a lower number of filters must be applied to the input features). Reducing the number of convolutional filters in layer i positively impacts both layer i and layer i+1. In fact, fewer filters in layer i produce smaller output feature maps (i.e., outputs have a lower number of channels). As a consequence, this has an effect on layer i+1, because each filter can be smaller, as it must be applied to a reduced number of input channels.

In conclusion, the table shows that the pruned instance used to build 2-E<sup>2</sup>CNNs has approximately halved the number of MAC operations *and* the number of weights. Therefore, when employing two instances, there will be no overhead when compared to the baseline LeNet5 implementation.

# 2.2.3 Selecting the E<sup>2</sup>CNNs cardinality

This section concludes the description of the  $E^2$ CNNs methodology discussing how to determine the *cardinality* of the generated ensemble. The

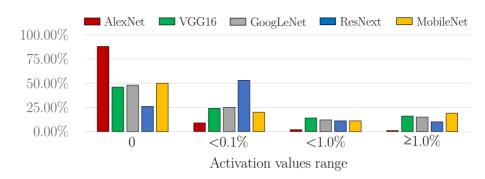

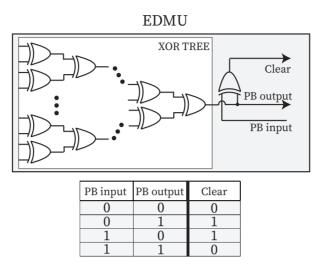

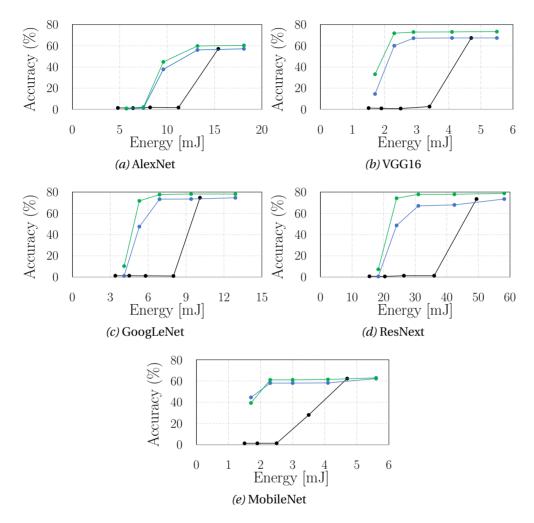

term cardinality is used to indicate the number N of instances included in E<sup>2</sup>CNNs. I will show in Section 2.3 that E<sup>2</sup>CNNs of different cardinality achieve different accuracy levels and exhibit different robustness degrees, thus making the selection of the E<sup>2</sup>CNNs cardinality N an important design choice.