# Evaluating, Exploiting, and Hiding Power Side-Channel Leakage of Remote FPGAs

Présentée le 29 août 2023

Faculté informatique et communications Laboratoire d'architecture de systèmes parallèles Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

## Ognjen GLAMOČANIN

Acceptée sur proposition du jury

Prof. P. Thiran, président du jury

Prof. B. Falsafi, Dr M. Stojilović, directeurs de thèse

Prof. R. Kastner, rapporteur

Dr M. Macchetti, rapporteur

Prof. D. Atienza, rapporteur

The moment you doubt whether you can fly, you cease for ever to be able to do it.  $-- J.\ M.\ Barrie,\ Peter\ Pan$

To Teodora, the love of my life.

## Acknowledgements

I came to EPFL in September 2018 to start my PhD journey, expecting it to be challenging. After all, both my bachelor's and master's studies were extremely difficult, but with dedication and hard work, I managed to finish them successfully. What I did not foresee at the time was just how challenging that journey would be, and if it were not for the support of all the wonderful people around me, I would not have made it to the finish line. I owe my deepest gratitude to all these people. Thus, it is fitting to start this thesis by extending my heartfelt thanks to them.

First, I am grateful to my advisors, Dr. Mirjana Stojilović and Prof. Babak Falsafi. It goes without saying that my supervisor, Mirjana, was the most influential presence throughout this journey. Since the beginning, she pushed me to be better and more efficient in everything I do. She taught me how to articulate and present my ideas clearly and confidently, both in writing and when presenting. She made me question everything, making me the researcher I am today. With her constant dedication and drive, there were moments when I felt like she cared more about my PhD than myself, and I thank her for that. Babak was my mentor throughout the PhD journey. He was always there when I needed advice and provided support whenever I needed it. He taught me the importance of clarity: clarity of thought, clarity in writing, and clarity in presentations. Besides work, Babak taught me about the other vital things in life: food and drinks. Most notably, he sparked my love for espresso and later entrusted me to be the coffee tsar at PARSA, which I will forever be grateful for.

Next, I would like to thank the members of my thesis committee, Prof. Patrik Thiran, Prof. David Atienza, Prof. Ryan Kastner, and Dr. Marco Macchetti, for their guidance and feedback during and after my thesis exam. Ryan is one of the kindest people I ever met, and his feedback

during the end stages of my PhD was instrumental in shaping my research and thesis. I also wanted to thank Prof. Mathias Payer, my EDIC mentor. I would not be here without his kind support. He was always happy to take time and listen to me, and his advice reshaped how I look at research.

I am very grateful to have had an extraordinary set of close collaborators. Prof. Francesco Regazzoni was my go-to hardware security expert, whose cool composure toward research always calmed me down during incredibly stressful paper deadlines. Prof. Mathias Payer always provided very insightful comments that made me rethink my approach for the better, leading to a significantly better paper. The other closest collaborators I am incredibly thankful to are Dina G. Mahmoud, Shashwat Shrivastava, David Spielmann, Louis Coulon, Hajira Bazaz, Anđela and Staša Kostić, Nour Ardo, Jinwei Yao, Kostas Papagiannopoulos, Dorian Ros, Melissa Azouaoui, Andrea Caforio, Daniel Collins, and Subhadeep Banik. I immensely appreciate their contribution to enriching my doctoral journey. I also want to thank all the students I have worked with throughout my PhD, who motivated me to be a better teacher and supervisor. Thank you to Alexandre Abbey, Dorian Ros, Léa Micheloud, David Spielmann, Hajira Bazaz, Arthur Passuello, Jinwei Yao, Nour Ardo, David Dervishi, and Anđela and Staša Kostić.

Next, I want to thank the people who did not directly participate in my PhD journey but nevertheless left a significant impact on me and my overall academic path. First, Prof. Laslo Nad, whose enthusiasm to understand *why and how* an idea came to be, shaped how I look at science and engineering during my Bachelor's studies. Then, Prof. Staniša Dautović, whose passion for science and research motivated me to pursue a PhD and do research. And finally, Prof. Rastislav Struharik, who gave me a strong technical background in FPGAs I heavily relied on during my PhD journey. Finally, I would like to thank my middle school teachers, Senja Stavrić, who taught me what it means to have and meet high expectations, and Danica Gavrilović, who sparked my interest in technical sciences and engineering.

Next, I would like to acknowledge all the PARSA members, who added much-needed joy and color to my PhD journey. First and foremost, I want to thank Siddharth Gupta. Sid and I shared most of our PhD journeys and bonded very closely in my second year, probably because we were the only ones coming to the office at the time. I want to thank him for being a good

listener and giving me some of the best advice I have gotten during my PhD. He always listened to my angry rants about random and most minor stuff. Above all, I want to thank him for listening to all my, as he would call it hyperventilating, when my anxiety took over, and I would spiral on negative things. I think Sid has singlehandedly prevented an early end of my PhD more times than I can count. Thank you, Sid, for being the best friend I needed throughout this journey. Next, I want to thank Mario Drumond. Even though Mario and I overlapped for only one year at PARSA, he is still a very important person in my path. He may not realize it, but he saved me from "financial ruin" during my PhD by helping me and my then-unemployed wife get subsidies for health insurance in my first year. I started hanging out with Mario more after he graduated, and he significantly helped me handle the stress of the PhD and job search with concise and constructive advice. Also, he was my right-hand man in making fun of poor Sid. Next, I want to thank Arash Pourhabibi. He was my first office mate and one of the warmest and most supportive people I ever had the chance to meet. He was always ready to take time, listen, and give sage advice that would completely change how I look at my problems, suddenly making them manageable. When he graduated, he also became my gaming buddy, and we shared many discussions about our favorite games. When I came to Switzerland, I was a big softy and could not tolerate spicy food. I am incredibly grateful to Arash and Sid, who taught (forced?) me to eat spicy food, and opened my eyes to a whole new world of fantastic tastes. While not in the lab, I always felt Negar Foroutan was part of the PARSA gang, at least spiritually. I am very grateful to have met her, as she always helped with the most selfless intentions. I always enjoyed having amazing history/linguistics conversations with her, through which I learned much about Iran.

I am also grateful to have spent much time with my two Turkish friends, Ahmet Caner Yüzügüler and Simla Burcu Harma. Simla and Ahmet are complete and total opposites, but both are amazing people. One comes from the *cool* part of Turkey, and the other from the *lame* part. They both agree on this, though I am not sure they mean the same thing. Simla's optimism always helped me focus on the *amazing* things in life, and I thank her for that. Ahmet's relaxed attitude helped me realize that life is not all about work and stress; that we should relax from time to time, be it by chilling at the lake, or eating some spicy crackers

and watching Pineapple Express. I am also really grateful for having the SOL team, Shashwat Shrivastava and Louis Coulon. Shashu and Lulu have been very supportive throughout the last stages of my PhD, and were always ready to listen to my rants. They are both very grounded and positive people who helped me in my research, but also pushed me to stand up for myself. I also want to thank Dina for all her help and support. We were working in the same area of research, and discussions with her helped me clarify and understand many things. She was always happy to help with both technical, but also personal issues. Even though for a short time, I am incredibly grateful to have met Hussein Kassir in my first year. We both quickly realized we shared the same weird sense of humor and later became Reddit buddies. Hussein and I stayed in regular contact, and he was extremely helpful with my job search, advising me and providing me with resources to prepare for hardware interviews. I also want to thank Atri Bhattacharyya. We started our PhDs at the same time, and connected on a lot of topics, both technical and non-technical. Atri always amazed and motivated me with his ability to ask really good questions at every talk I attended with him. He organized great board game nights, where I would usually miserably lose to either him or his friend. I am also grateful to have spent time with Mark Sutherland, maybe the biggest overthinker I know. I want to thank him for all the long discussions, both philosophical and technical. But also, for sending me all those amazing Key and Peele videos; these guys are really cool. I would also like to thank all the other PARSA members whom I enjoyed interacting with and that made PARSA the amazing and lively place it is: Rafael Pizarro Solar, Yuanlong Li, Shanqing Lin, Ali Ansari, Ayan Chakraborty, and Buğra Eryılmaz. Finally, I would like to thank Stéphanie Baillargues, for helping me in anything and everything related to EPFL administration. She was always ready to go above and beyond to do the crazy things that came to our minds, from renovating the lab, to organizing trips and reimbursing receipts, and doing it all faster than the speed of light. Next, I also want to thank my EPFL PhD colleagues from other labs that I was very close to throughout my PhD journey. First, I want to thank the Kashmiri gang: Mahyar Emami, Sahand Kashani, Xinrui Jia, and Rishabh Iyer. Mahyar and Sahand were my FPGA buddies, and we shared a lot of the sweat and blood needed to use FPGAs. Mahyar and I started the PhD at the same time and immediately bonded on gaming, movies, and TV shows. Mahyar lent me

his PS4 one day, and doomed me for the rest of my life, for which I am unironically incredibly thankful, as he revived my long-lost love for gaming. Whenever somebody asks me about Sahand, I say he is the greatest FPGA wizard I ever knew. He is one of the most disciplined and driven people I have ever known. If you give Sahand enough time, he will make miracles possible. He and I share an intense need for cleanness which we have first bonded on, but we later realized we have much more in common, and I really enjoyed spending time with him and discussing various technical and non-technical topics. I also wish to thank Sahand and Mahyar for graciously letting me use their Alveo U200 FPGA board. Their scripts and guidance helped significantly reduce my workload, and I used their infrastructure for most of the papers in my senior years. I am also very grateful to have met Xinrui Jia. We started our PhD at the same time, and she has been an incredibly good friend throughout the five years of our PhD journeys. She was always ready to listen and help whenever needed. Xinrui is one of the most reliable people I have met. If she agrees to do something, it will be done perfectly. She was always happy to water my plants whenever I went out of town, and was one of the very few people I trusted enough to do this surprisingly complicated procedure (maybe because we share a love for our beautiful orchids). Finally, I want to thank Rishabh. He is probably one of the most competitive people I have ever seen. I will never forget the look on his face when I won an unbelievable poker hand. However, I incredibly admire that he uses his competitiveness to push himself and improve, instead of pushing others down. Like Mario, he was an amazing accomplice for pranking Sid.

Next, I want to thank the LAP gang, including Stefan Nikolić, Grace Zgheib, Sahand Kashani, Lana Josipović, Mikhail Asiatici, Louis Coulon, and Andrea Guerrieri. While PARSA was my home, my research community was not in computer architecture. My research centers on FPGAs, in which the people from the LAP gang are the experts. Whenever I went to FPGA conferences, they made me (and my wife) feel like a part of their group, invited me to dinners and trips, and introduced me to various experts in the community. Thank you all for adopting me into your FPGA family and providing me with the fondest memories during my conference trips.

I am also incredibly indebted to the amazing people I have known for years in Serbia, who

supported my path towards a PhD from 1,000 km away. First, I would like to thank Vojin Jovičić, whom I met when I was three, and who has been a constant support throughout my life. We went through a lot together, from kindergarten to my marriage, at which he was the best man. We went everywhere on roller skates together, and played Yu-Gi-Oh cards and video games. We shared our love for music, and even played in a band together. We played pretty bad, but we had a blast, like we always do. He was the one that drove me to Lausanne by car the day I started my PhD. Throughout my PhD, the stories about his (mis)adventures have made me smile on many a dark day. He was always there when I returned to visit Serbia, and bent over backwards to spend as much time with me as possible. He is the best friend anyone could ask for, and I am proud to have shared most of my life with him. I am also very grateful for my middle school group of friends, including Vojin Jovičić (again), Dragan Gobla Špančić, Bojan Jagetić, Nikola Kričković, and the latecomer, Miloš Vlaškalić. I spent so much time with these people throughout middle and high school, just chilling on the bench, drinking coke or beer, and talking about the most random stuff ever. Thank you for filling my teenage years with amazing memories.

I am also incredibly grateful to my two great friends at EPFL from my high school choir days, Stefan Nikolić and Viktor Šanca. Stefan and I met in a mosh pit at a punk metal concert at high school. Ever since then, we have been great friends. We quickly discovered we share many similar interests, from music to our love of engineering, steam trains, sailships, and hiking. After high school, we attended the same university and followed all the classes together. He always had an encyclopedic knowledge, and discussions with him really helped me gain a deeper understanding of the material we were working on. Stefan is the one who convinced me to apply to EPFL, and I am incredibly grateful for that. Like Stefan, Viktor and I sang in the same high school choir. We were both tenors and classical music geeks, so we quickly bonded. In Switzerland, Viktor was my go-to guy for anything law- or regulation-related. Somehow, he always knew exactly where the answer to my question was, and pointed me to the precise line of the exact law that had the answer. I should add that he is not Swiss, at least not officially. He was always a great listener, and we enjoyed ranting to each other about various things throughout our PhD journeys.

I am also very grateful to my two high school friends, Ognjen Stanojev and Aleksa Nikolić. Ogi has always been a cool and composed presence in my life, always there to listen and try to help. He has lodged me more times than I can count, both in Zurich and the US. Whenever I hang out with Aleksa (usually with Ogi, too), we always end up having unexpected fun. We end up in crazy places doing crazy things, and I will always remember our trips together. I would also like to thank my Jules Verne family, with which I learned French and had amazing adventures since I was a kid: Vojin Jovičić, Lena Pucarević, Anja Jurić, Jelisaveta Džigurski, Nemanja Jevtović, Jelena Begić, Marija Drapšin, Miloš Ubović, Marko Jurić, and Natalija Čomić. I made sure to see them whenever I returned to Serbia, and every time, even though years and months passed, it was as if not a single day had passed. I am very grateful for their support throughout my PhD journey. I am also very grateful to my amazing group of friends from my university days in Novi Sad, including Stefan Nikolić, Dajana Milićević, Jovana Zoranović, Stefan (Stena) Stanić, Kosta Ivančević, and Predrag Kovačević. Our many discussions and study sessions helped me better master the material, and hanging out with them made my university days incredibly fun. I am also incredibly grateful to all the choir friends that I met and sang with throughout the years, from both the "Jovan Jovanović Zmaj" high school, led by Jovan Travica and Jasmina Nešković, but also the "Klapa Capa" a capella group, including Viktor Šanca, Nikola Jovanović, Miloš Stojanović, Staša Stajić, Branislav Glogovac, Zoran Otrupčak, Stefan Nikolić, Goran Stanić, and Uroš Dobrić. Singing in these two choirs not only allowed me to meet my wife and fall in love, but also allowed me to express my love for singing with many like-minded friends.

Next, I want to thank all my friends from Sorbonne Université, including Yohan Fargeix, José-Paul Dominguez, David Bananier, and Arthur Hennequin, who helped me catch up when I joined the second year of the two-year master's program. I learned a lot from them, and working and hanging out was a pleasure. I am also grateful to Aleksandar Miladinović, whom I met when I first came to our dorm in Paris. He is an amazing person I enjoyed cooking with and visiting Paris, making my time in Paris super fun.

I am also incredibly grateful for the people from ARM I used to hang out with during my internship. Abdelhadi Moustafa is an amazing guy who taught me much about Lebanese food

and culture. I also enjoyed discussing TV shows with him, and I think he is the only person that *truly* understands what binge-watching a whole TV show means. Yohan Fargeix has unknowingly helped me deal with a lot of problems during the internship with his unbelievably positive attitude. I think he is one of the rare people I know who almost never worries about anything, and his attitude rubbed on me and made my time at ARM much more fun. Even though I have not talked to Maria Teresa Bevivino much during my internship, I greatly enjoyed spending time with her later on, during many of our trips around Europe with Yohan and Abdelhadi. JP is one of the kindest and tamest people I have ever met, and I also greatly enjoyed spending time with him during my internship. He drove us to so many beaches that summer that his poor car just decided to give up at the end of August. We are still waiting for the gas bill from JP.

Finally, I would like to extend my immeasurable gratitude to my family. They are the main reason I am where I am right now, and without their unconditional love and everlasting support throughout my entire life, I would not have reached the end of my PhD journey. I want to thank my parents, Jelena and Zoran, for believing in me since day one and investing so much time, energy, and resources in me, my education, and my well-being. I am incredibly thankful for all the sacrifices that they made. I am grateful for all the little (and big) details: the hugs, the walks in nature, the travel to imaginary worlds and real places all over Europe, the support in my education, English, French, and piano lessons, the encouragement to study abroad, and the countless other selfless things they did for me that I am maybe not even aware of. I also want to thank my two brothers, Dušan and Nikola, for always being there for me and sharing their childhood with me. I always fondly remember our time together, building LEGOs, watching movies, playing video games, and laughing. I am proud of what you are now, and I am looking forward to spending more time with you in the future. I am also very grateful to my grandma Cecilija, grandpa Dušan, and aunt Jelena, who have always been there for me since I was a child, and took me on wild adventures all over Serbia. Some of my fondest memories are from spending time with them, at their home or our country-side house, and I will always be thankful for their support. I would like to acknowledge another very important person in my life, my grandmother Katica, who passed away shortly before I started my PhD. I am

very grateful to have had her in my life. She used to spend so much time with me when I was little, taking me on adventures all around Novi Sad. When I was having trouble in elementary school, she sat me down and taught me how to study, and to this day, I use her advice, for which I am forever grateful. I also want to extend my gratitude to my in-laws, Valerija, Relja, and Fedor Popović, who have always considered and treated me as their own. I would like to thank them for their love and support throughout my PhD journey.

Last but not least, I would like to thank my wife Teodora, the love of my life, and my *giving tree*. She is the main reason I am where I am right now, and I would not have had the strength to finish this journey without her. Doing a PhD was the hardest thing I have ever done in my entire life, by far. I think my PhD journey was also one of the hardest things she did, too. She left everyone she knew and loved to move across the Alps to be with me, for which she will forever have my gratitude. And during the difficult periods of my PhD—and there were *a lot* of them—she put her problems aside and always unconditionally supported and encouraged me. She has been my rock, my safe place, the first person I want to see in the morning, and the last person I want to see before I go to sleep. I am forever grateful to have a person in my life that unconditionally believes in me, and constantly reminds me to stop doubting that I can fly. I love her more than anything else in the world, and I look forward to spending the rest of my life with her.

I would also like to thank the people and organizations that financially supported my PhD journey. I am thankful to EPFL, the Swiss National Science Foundation, and finally, the Swiss people for supporting me through their taxes.

Lausanne, July 17, 2023

Ognjen Glamočanin

### **Abstract**

The pervasive adoption of field-programmable gate arrays (FPGAs) in both cyber-physical systems and the cloud has raised many security issues. Being integrated circuits, FPGAs are susceptible to fault and power side-channel attacks, which require physical access to the victim device. However, recent work demonstrated that physical proximity is no longer required for these attacks, as FPGA logic can be misused to create on-chip voltage sensors or power-wasting circuits. The work in this thesis explores the impact of FPGA-based voltage sensors on FPGA security and shows that sensors create new opportunities to evaluate, exploit, and hide power side-channel leakage in remote FPGAs.

In the first part of this thesis, we demonstrate that voltage sensors can increase power side-channel security. In the case of deployed and no longer accessible cyber-physical devices, we show that FPGA-based voltage sensors allow designers to evaluate the power side-channel leakage after deployment, ensuring constant power side-channel security monitoring. Our results, comparable to state-of-the-art measuring equipment, move the leakage evaluation boundary from controlled lab environments to the field, allowing future work to combine leakage evaluation with other security measures such as tamper detection.

In the second part of the thesis, we focus on evaluating the security impact of FPGA-based voltage sensors on multitenant FPGAs, and show that voltage sensors can evaluate, exploit, and hide power side-channel leakage. We demonstrate that a remote attacker can mount both statistical (correlation power analysis) and machine learning based attacks with the voltage sensors, emphasizing the need to deploy countermeasures in multitenant FPGAs. The work in this thesis was the first to show a successful remote power analysis attack on cloud FPGA instances and the first to provide an instruction-level leakage analysis of soft-core CPUs in a

shared FPGA scenario. Motivated by the exploits, this thesis proposes a novel hiding technique against remote power side-channel analysis attacks: active wire fences. Our results show that active wire fences outperform the state-of-the-art hiding techniques in shared FPGAs. In the last part of the thesis, we explore more efficient and stealthy techniques for sensing on-chip voltage. We present the first stealthy routing-based FPGA sensor that outperforms the state of the art in remote power analysis attacks. With our stealthy sensor architecture, we show that detecting sensor circuits is not a scalable solution for guaranteeing security. Finally, this thesis evaluates the impact of external factors, specifically temperature, on FPGA-based voltage sensors and the success of remote power side-channel attacks in multitenant FPGAs. Our work shows that, if ignored, temperature effects on voltage sensors can lead to misleading attack results.

**Keywords:** reconfigurable logic and FPGAs, multitenancy, power analysis attacks, on-chip sensors, cloud, CPU instruction identification, hiding, temperature impact

### Résumé

L'adoption généralisée de systèmes FPGA dans les systèmes cyber-physiques et dans le cloud a soulevé de nombreux problèmes de sécurité. En tant que circuits intégrés, les FPGAs sont sensibles aux attaques d'analyse de consommation, qui nécessitent un accès physique au dispositif victime. Cependant, des travaux récents ont démontré que la proximité physique n'est plus nécessaire pour l'éxécution de ces attaques, car les ressources internes des FPGAs peuvent être utilisées à mauvais escient pour créer des capteurs de tension directement sur la puce, ou des circuits qui gaspillent de l'énergie. Cette thèse explore l'impact que peut avoir, sur la sécurité des FPGAs, de capteurs de tension basés ces derniers. Nous montrons que ces capteurs créent de nouvelles opportunités pour évaluer, exploiter et dissimuler des fuites issus de canaux latéraux d'alimentation dans les FPGA distants.

Dans la première partie de cette thèse, nous démontrons que les capteurs de tension peuvent augmenter la sécurité. Dans le cas de dispositifs cyber-physiques déployés et devenus inaccessibles, nous montrons que les capteurs de tension basés sur les FPGA permettent aux concepteurs d'évaluer la présence de fuites d'information à travers un canal latéral de puissance après que le système FPGA ait été déploié, assurant ainsi une surveillance constante de la sécurité. Nos résultats, comparables à ceux obtenus avec de l'équipement de mesure de pointe, déplacent la limite d'évaluation des fuites depuis un environnement de laboratoire contrôlé vers le terrain, ce qui permettra à l'avenir de combiner l'évaluation des fuites avec d'autres mesures de sécurité telles que la détection de sabotage.

Dans la deuxième partie de la thèse, nous nous concentrons sur l'évaluation de l'impact sécuritaire des capteurs de tension on-chip sur les FPGAs multi-utilisateur, et nous montrons que les capteurs de tension peuvent évaluer, exploiter et dissimuler des fuites de canaux latéraux de puissance. Nous démontrons qu'un assaillant distant peut déployer des attaques statistiques (analyse de puissance par corrélation) et des attaques basées sur l'apprentissage automatique avec les capteurs de tension, soulignant la nécessité de déployer des contremesures dans les FPGAs multi-utilisateur. Les travaux de cette thèse ont été les premiers à montrer une attaque réussie d'analyse de puissance à distance sur des instances FPGA dans le cloud, et les premiers à fournir une analyse de fuite au niveau des instructions des CPU soft-core dans un scénario FPGA partagé. Motivée par ces exploits, cette thèse propose une nouvelle technique de dissimulation contre les attaques d'analyse de canal latéral de puissance à distance : les clôtures de fils actives. Nos résultats montrent que les clôtures de fils actives sont plus performantes que les techniques de dissimulation de pointe dans les FPGAs partagés.

Dans la dernière partie de la thèse, nous explorons des techniques plus efficaces et plus furtives pour détecter la tension sur une puce. Nous présentons le premier capteur FPGA furtif basé sur le routage qui surpasse l'état de l'art dans les attaques d'analyse de puissance à distance. Avec notre architecture de capteur furtif, nous montrons que la détection des circuits de capteurs n'est pas une solution qui peut être mise à l'échelle pour garantir la sécurité. Enfin, cette thèse évalue l'impact des facteurs externes, en particulier de la température, sur les capteurs de tension basés sur les FPGAs et le succès des attaques par canal latéral de puissance à distance dans les FPGAs multi-utilisateur. Notre travail montre que, s'ils sont ignorés, les effets de la température sur les capteurs de tension peuvent conduire à résultats trompeurs en ce qui concerne la réussite ou l'échec d'une attaque.

**Mots clés :** logique reconfigurable et FPGAs, multi-utilisateur, attaques d'analyse de puissance, capteurs on-chip, cloud, identification des instructions CPU, dissimulation, impact de la température

## **Contents**

| Ac | knov  | wledge   | ments                                                      | j    |

|----|-------|----------|------------------------------------------------------------|------|

| Ał | ostra | ct       |                                                            | xi   |

| Li | st of | Figure   | S                                                          | xxi  |

| Li | st of | Tables   |                                                            | xxix |

| Li | st of | Abbrev   | riations                                                   | xxx  |

| 1  | Intr  | oducti   | on                                                         | 1    |

|    | 1.1   | Thesis   | s Goals                                                    | 2    |

|    | 1.2   | Thesis   | s Contributions                                            | 4    |

|    |       | 1.2.1    | Evaluating the Security of Deployed Cyber-Physical Devices | 4    |

|    |       | 1.2.2    | Multitenant FPGAs: Attacks and Mitigations                 | 6    |

|    |       | 1.2.3    | Advanced Voltage Sensing and Temperature Effects           | 8    |

|    | 1.3   | Thesis   | s Organization                                             | g    |

|    |       | 1.3.1    | Bibliographic Notes                                        | 10   |

| 2  | Sec   | urity Ir | mplications of FPGAs in Modern Heterogeneous Systems       | 11   |

|    | 2.1   | Towar    | rds Heterogeneous Systems                                  | 11   |

|    | 2.2   | FPGA     | s in Heterogeneous Systems                                 | 13   |

|    |       | 2.2.1    | FPGAs in the Cloud                                         | 14   |

|    |       | 2.2.2    | Security Concerns                                          | 14   |

|    | 2.3   | Electr   | ical-Level Attacks on FPGA Systems                         | 16   |

#### **Contents**

|    |     | 2.3.1   | Physical Attacks                                  | 17  |

|----|-----|---------|---------------------------------------------------|-----|

|    |     | 2.3.2   | Remote Attacks                                    | 18  |

| •  | ъ.  |         |                                                   | 0.1 |

| 3  |     | kgrour  |                                                   | 21  |

|    | 3.1 | FPGA    | Architecture                                      | 21  |

|    | 3.2 | FPGA    | -Based On-Chip Voltage Sensors                    | 22  |

|    | 3.3 | Power   | Analysis Attacks                                  | 27  |

|    |     | 3.3.1   | Correlation Power Analysis Attack                 | 29  |

|    |     | 3.3.2   | Attack Success Metrics                            | 30  |

|    | 3.4 | First-0 | Order Side-Channel Leakage Evaluation             | 32  |

|    |     |         |                                                   |     |

| Ι  | Eva | luatin  | g the Security of Deployed Cyber-Physical Devices | 33  |

| 4  | Pow | er Side | e-Channel Leakage Evaluation on Remote FPGAs      | 35  |

|    | 4.1 | Threa   | t Model                                           | 37  |

|    | 4.2 | Tamp    | ering with the PDN                                | 38  |

|    | 4.3 | Onlin   | e Computation of the <i>t</i> -test Statistic     | 38  |

|    | 4.4 | Built-  | in Leakage Evaluation System                      | 44  |

|    |     | 4.4.1   | System Architecture and Integration               | 46  |

|    |     | 4.4.2   | Power-Supply Voltage Sensor                       | 48  |

|    |     | 4.4.3   | Hardware Implementation of the <i>t</i> -test     | 48  |

|    |     | 4.4.4   | Encryption Core                                   | 50  |

|    |     | 4.4.5   | System Calibration and Robustness                 | 50  |

|    | 4.5 | Exper   | imental Results                                   | 51  |

|    | 4.6 | Chapt   | ter Summary                                       | 55  |

|    |     |         |                                                   |     |

| II | Μι  | ıltiten | ant FPGAs: Attacks and Defenses                   | 57  |

| 5  | Ren | note St | atistical Power Analysis Attacks on Cloud FPGAs   | 59  |

|    | 5.1 | Threa   | t Model                                           | 60  |

|   | 5.2  | Porting the TDC Sensor on Ultrascale+ FPGAs                           | 61  |

|---|------|-----------------------------------------------------------------------|-----|

|   | 5.3  | System Architecture and Experimental Setup                            | 63  |

|   | 5.4  | Experimental Results                                                  | 65  |

|   | 5.5  | Chapter Summary                                                       | 69  |

| 6 | Inst | ruction-Level Power Side-Channel Leakage Evaluation of Soft-Core CPUs | 71  |

|   | 6.1  | Threat Model                                                          | 74  |

|   | 6.2  | Experimental Setup                                                    | 76  |

|   |      | 6.2.1 FPGA Voltage-Drop Sensors                                       | 78  |

|   |      | 6.2.2 Controller                                                      | 79  |

|   | 6.3  | Instruction Classification                                            | 80  |

|   |      | 6.3.1 Instruction Template Generation                                 | 81  |

|   |      | 6.3.2 Instruction Classification Models                               | 83  |

|   | 6.4  | Evaluation on Sakura-X                                                | 84  |

|   |      | 6.4.1 Visual Analysis of Sensor Traces                                | 87  |

|   |      | 6.4.2 Deep Learning-Based Instruction Leakage Evaluation              | 90  |

|   |      | 6.4.3 Impact of Preprocessing On Instruction Leakage                  | 95  |

|   |      | 6.4.4 Comparison with Classical ML Approaches                         | 96  |

|   |      | 6.4.5 Impact of the Number of Sensors on Instruction Leakage          | 97  |

|   |      | 6.4.6 Impact of Averaging on Instruction Leakage                      | 99  |

|   |      | 6.4.7 Impact of the Dataset Size on Instruction Leakage               | .00 |

|   | 6.5  | Evaluation on Alveo U200                                              | .01 |

|   |      | 6.5.1 Instruction-Level Leakage on Cloud-Scale FPGAs                  | .02 |

|   |      | 6.5.2 Code Sequence Classification                                    | .03 |

|   | 6.6  | Discussion                                                            | .04 |

|   | 6.7  | Countermeasures                                                       | .07 |

|   | 6.8  | Limitations                                                           |     |

|   | 6.9  | Chapter Summary                                                       | .10 |

| 7 | Acti | ve Wire Fences Against Remote Power Analysis Attacks 1                | 13  |

#### **Contents**

|    | 7.1  | Threa   | t Model                                                        | 114 |

|----|------|---------|----------------------------------------------------------------|-----|

|    | 7.2  | Active  | Wire Fence                                                     | 115 |

|    |      | 7.2.1   | Wire-Based Power Waster                                        | 115 |

|    |      | 7.2.2   | Building a Wire Fence                                          | 116 |

|    | 7.3  | Experi  | imental Setup                                                  | 118 |

|    | 7.4  | Result  | s and Discussion                                               | 120 |

|    |      | 7.4.1   | Voltage Drop Comparison                                        | 121 |

|    |      | 7.4.2   | Varying Distance $D$                                           | 121 |

|    |      | 7.4.3   | Power Side-Channel Attack Success                              | 123 |

|    | 7.5  | Chapt   | er Summary                                                     | 126 |

|    |      |         |                                                                |     |

| II | I Ac | dvance  | ed Voltage Sensing and Temperature Analysis                    | 129 |

| В  | FPG  | SA Rout | ting Delay Sensors for Effective Remote Power Analysis Attacks | 131 |

| •  | 8.1  |         | t Model                                                        |     |

|    | 8.2  |         | ivity of TDC Voltage Sensors                                   |     |

|    | 8.3  |         | ng Delay Sensors                                               |     |

|    | 0.5  |         | VRDS and HRDS                                                  |     |

|    |      |         | RDS                                                            |     |

|    |      |         |                                                                |     |

|    |      |         | Calibration                                                    |     |

|    | 0.4  |         | Portability and Detectability                                  |     |

|    | 8.4  |         | imental Evaluation                                             |     |

|    |      | 8.4.1   | System Architecture and Floorplan                              |     |

|    |      | 8.4.2   | Experimental Setup                                             |     |

|    | 8.5  |         | s and Discussion                                               |     |

|    |      | 8.5.1   | RDS Sensors Versus TDC and VITI                                |     |

|    |      | 8.5.2   | Impact of The RDS Size on The Attack Success                   |     |

|    |      | 8.5.3   | RDS Versus TDC on The Alveo U200 Datacenter Card               |     |

|    |      | 8.5.4   | Varying the Placement                                          | 155 |

|    |        | Con                                              | tents      |

|----|--------|--------------------------------------------------|------------|

|    | 8.6    | Chapter Summary                                  | 157        |

| 9  | Tem    | perature Impact on Remote Power Analysis Attacks | 159        |

|    | 9.1    | Temperature Impact on TDC Sensors                | 160        |

|    | 9.2    | Evaluating The Impact of Temperature             | 162        |

|    |        | 9.2.1 Leakage Analysis                           | 162        |

|    |        | 9.2.2 ML Accuracy Evaluation                     | 163        |

|    | 9.3    | Results and Discussion                           | 166        |

|    |        | 9.3.1 Leakage Analysis                           | 166        |

|    |        | 9.3.2 ML Accuracy Evaluation                     | 170        |

|    | 9.4    | Chapter Summary                                  | 173        |

| 10 | Rels   | ated Work                                        | 175<br>177 |

| 10 |        | Monitoring of Security Primitives                |            |

|    |        | Power Analysis Attacks on Shared FPGAs           |            |

|    |        | Power Side-Channel Disassembly Attacks           |            |

|    |        | Power Wasters                                    |            |

|    | 10.4   | 10.4.1 Active Fences                             |            |

|    | 10.5   | 5 Voltage-Drop FPGA Sensors                      |            |

|    |        | 5 Temperature Effects                            |            |

| 11 |        | aclusions and Future Work                        |            |

| 11 | Con    | iciusions and Future work                        | 187        |

| Bi | bliog  | graphy                                           | 191        |

| Cı | ırricı | ulum Vitae                                       | 211        |

# **List of Figures**

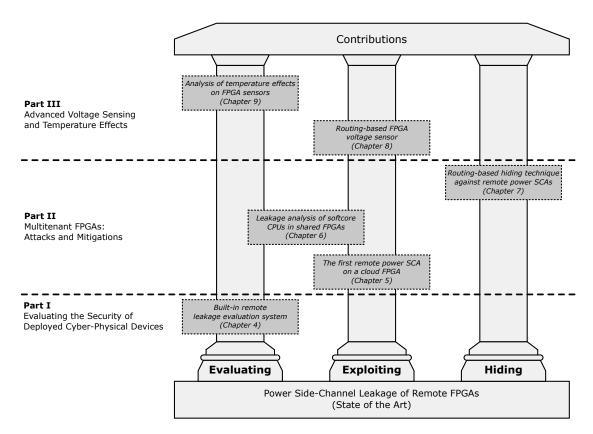

| 1.1 | Thesis contributions supported by three main pillars: evaluating, exploiting, and |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | hiding power side-channel leakage of remote FPGAs. Our work in Chapters 4, 6,     |    |

|     | and 9 presents the contributions along the evaluating pillar, extending the state |    |

|     | of the art with new techniques for measuring leakage of deployed devices, mea-    |    |

|     | suring leakage of softcore CPUs, and analyzing the temperature impact on FPGA     |    |

|     | sensors. Our work in Chapters 5, 6, and 8 builds the contributions of the ex-     |    |

|     | ploiting pillar, demonstrating statistical and ML-based attacks on cloud FPGAs    |    |

|     | and a new FPGA sensor architecture. Finally, the work in Chapter 7 contributes    |    |

|     | to the hiding pillar, improving the state of the art hiding techniques with new   |    |

|     | routing-based power-wasting circuits                                              | 5  |

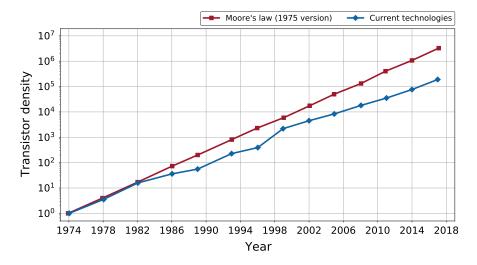

| 2.1 | Difference between the transistor density predicted by Moore's law and the        |    |

|     | current state of the art [1]                                                      | 12 |

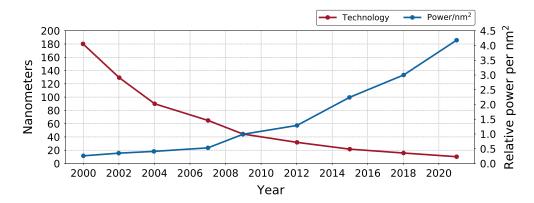

| 2.2 | Breakdown of Dennard scaling. Power consumption in the function of the            |    |

|     | technology node [1]                                                               | 12 |

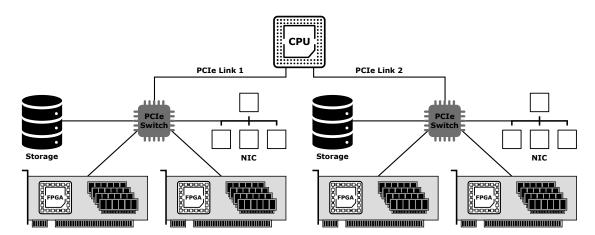

| 2.3 | Architecture of cloud FPGA servers                                                | 15 |

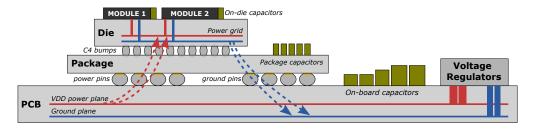

| 2.4 | Power delivery network coupling across the board, package, and the FPGA die.      | 16 |

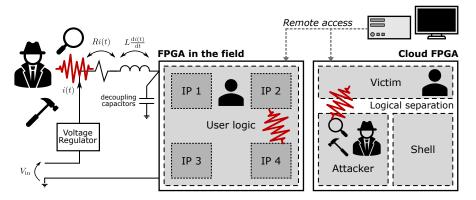

| 2.5 | Threat model for remote FPGAs. For FPGAs deployed in the field, an attacker has   |    |

|     | physical access to the device and can perform physical attacks such as power      |    |

|     | analysis, fault injection, or tampering. For multitenant FPGAs in the cloud, an   |    |

|     | attacker has remote access and can misuse the FPGA logic to perform remote        |    |

|     | power analysis and fault-injection attacks                                        | 17 |

|     |                                                                                   |    |

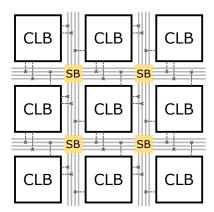

| 3.1 | FPGA architecture consisting of a matrix of configurable logic blocks (CLBs) and           |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | routing resources. The vertical and horizontal routing resources are connected             |    |

|     | with cross-bars called switch boxes (SB)                                                   | 22 |

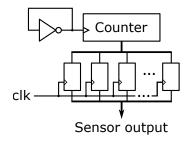

| 3.2 | RO-based voltage sensor.                                                                   | 23 |

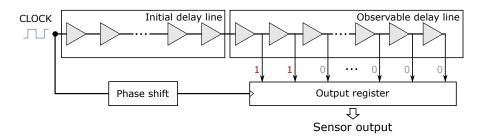

| 3.3 | Time-to-digital converter (TDC) sensor architecture                                        | 24 |

| 3.4 | TDC sensor architecture with a tunable phase shift between the clock that enters           |    |

|     | the observable delay line and the clock that samples the output (i.e., takes               |    |

|     | a snapshot of the observable delay line). The exact number of slices in our                |    |

|     | implementation is in Table 6.2                                                             | 24 |

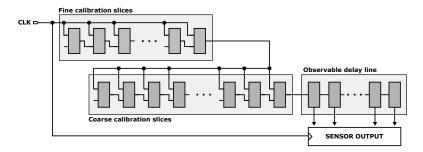

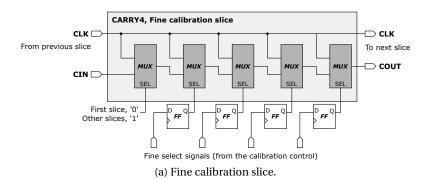

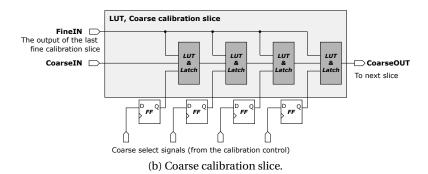

| 3.5 | The implementation of each slice in the TDC sensor in Fig. 3.4, including the              |    |

|     | calibration and sensor output registers. For space reasons, CARRY4 chain is                |    |

|     | shown horizontally; in the FPGA design layout, it spans vertically                         | 26 |

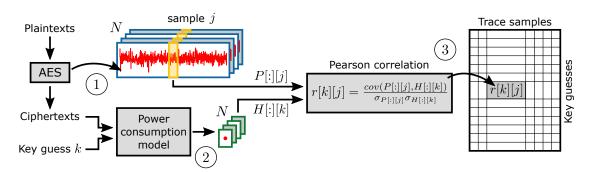

| 3.6 | Correlation power analysis attack                                                          | 30 |

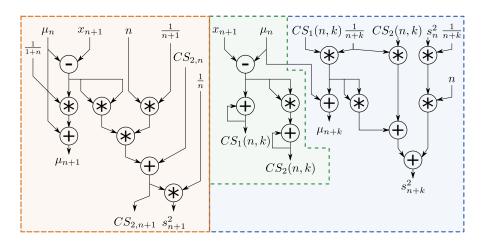

| 4.1 | Dataflow graph for operations when calculating the mean and variance incre-                |    |

|     | mentally with step 1                                                                       | 43 |

| 4.2 | Architecture of the built-in leakage evaluation system. The leakage evaluation             |    |

|     | system is co-located with the cyber-physical system, allowing for fast leakage             |    |

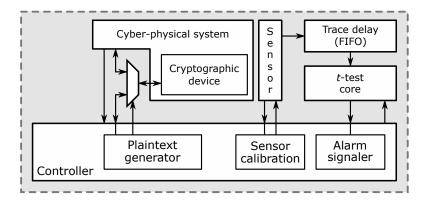

|     | evaluation with minimal service interruption                                               | 47 |

| 4.3 | Architecture of the $t$ -test block. The blocks in the green part are updated with         |    |

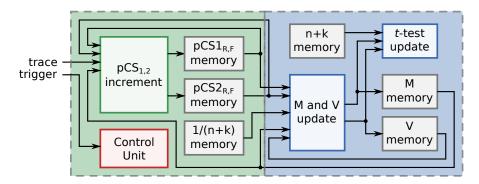

|     | every trace, while blocks in the blue part are updated after $k$ traces                    | 49 |

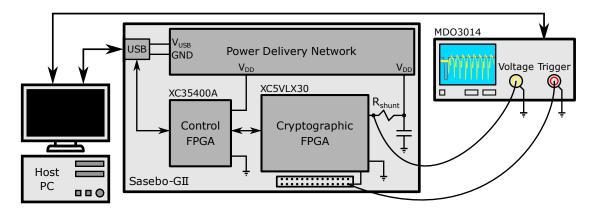

| 4.4 | Measurement setup used for acquiring the power side-channel traces on the                  |    |

|     | Sasebo-GII board, and evaluating the correctness of the $t$ -test system                   | 51 |

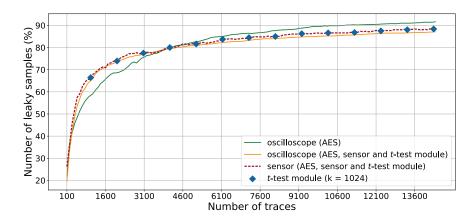

| 4.5 | The percentage of power trace samples for which the <i>t</i> -test fails for the non-      |    |

|     | pipelined AES, in the function of the number of traces. Solid lines are obtained           |    |

|     | using the oscilloscope traces and a <i>t</i> -test software routine in floating-point pre- |    |

|     | cision. Dashed lines are obtained using the FPGA sensor traces and the same                |    |

|     | software routine, while the diamond markers—which almost perfectly overlap                 |    |

|     | the dashed line—are the result of the FPGA <i>t</i> -test module                           | 52 |

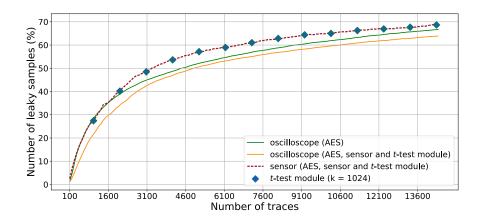

| 4.6 | The percentage of power trace samples for which the $t$ -test falls for the pipelined     |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | AES, in the function of the number of traces. Solid lines are obtained using              |    |

|     | the oscilloscope traces and a $t$ -test software routine in floating-point precision.     |    |

|     | Dashed lines are obtained using the FPGA sensor traces and the same software              |    |

|     | routine, while the diamond markers—which almost perfectly overlap the dashed              |    |

|     | line—are the result of the FPGA <i>t</i> -test module                                     | 53 |

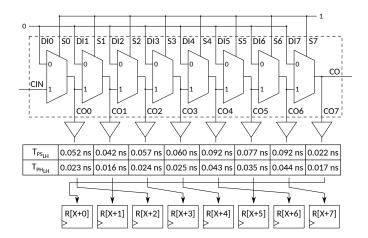

| 5.1 | CARRY8 internal architecture and nonmonotonic delays from input <i>CIN</i> to the         |    |

|     | outputs $CO_i$ , $0 \le i \le 7$ . To increase the likelihood of monotonically increasing |    |

|     | delays with the increase in the CARRY8 output index, it suffices to permute               |    |

|     | the CARRY8 outputs before they reach the sensor register. The permutation is              |    |

|     | devised from a detailed timing analysis of all paths within one CARRY8 element.           | 62 |

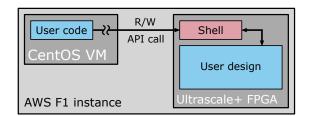

| 5.2 | Amazon EC2 F1 Instance architecture                                                       | 63 |

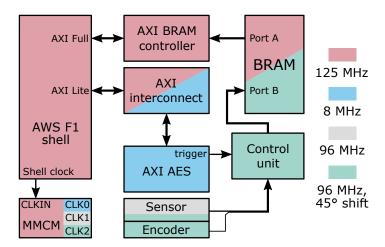

| 5.3 | System architecture                                                                       | 64 |

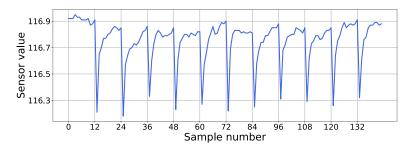

| 5.4 | Waveform obtained by averaging a hundred power-consumption traces. Plain-                 |    |

|     | text loading and all ten AES encryption rounds can be clearly identified                  | 65 |

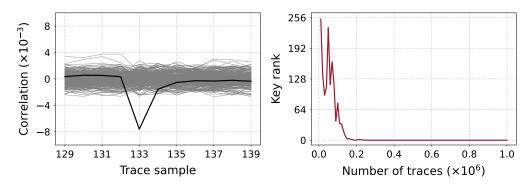

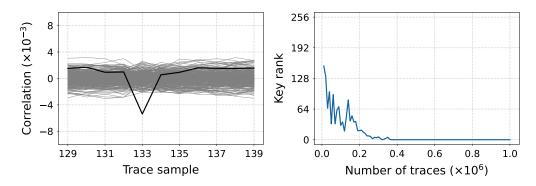

| 5.5 | CPA attack on the seventh byte of the AES encryption, using $10^6$ permuted traces.       |    |

|     | On the left, the correlation for all key guesses, with the correct key candidate in       |    |

|     | black. On the right, key rank evolution of the correct key candidate                      | 66 |

| 5.6 | CPA attack on the seventh byte of the AES encryption, using $10^6$ nonpermuted            |    |

|     | traces. On the left, the correlation for all key guesses, with the correct key            |    |

|     | candidate in black. On the right, key rank evolution of the correct key candidate.        | 66 |

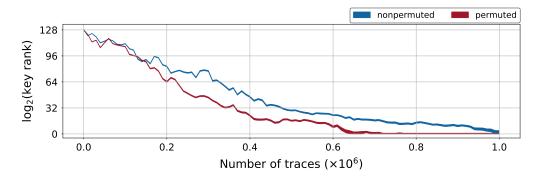

| 5.7 | Key rank estimation when attacking the full 128-bit key of the AES encryption             |    |

|     | for the nonpermuted and permuted traces                                                   | 67 |

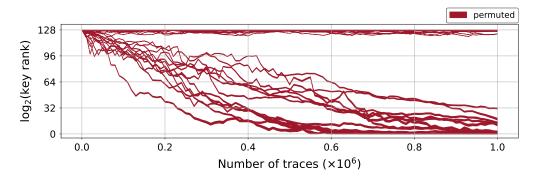

| 5.8 | Key rank estimation for all 30 different experiment runs on the Amazon EC2 F1             |    |

|     | instances, using permuted traces                                                          | 68 |

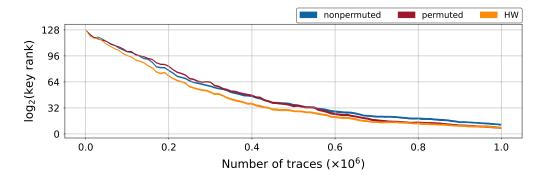

| 5.9 | Key rank estimation for three different sensor output encodings on the Amazon             |    |

|     | EC2 F1 instances, averaged over 30 experiments                                            | 69 |

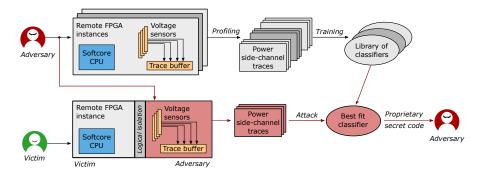

| 6.1  | Threat model. The top half illustrates the profiling phase, which results in a                   |     |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | library of side-channel instruction classifiers, for a number of FPGA instances                  |     |

|      | and CPU and sensor placements. The bottom half shows the attack                                  | 75  |

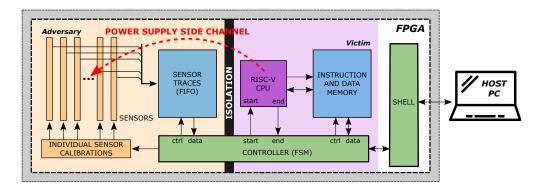

| 6.2  | Overview of the experimental setup                                                               | 78  |

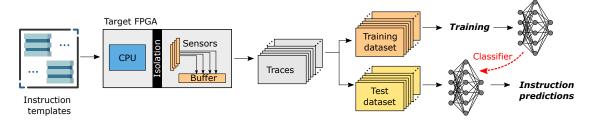

| 6.3  | Side-channel instruction leakage evaluation                                                      | 80  |

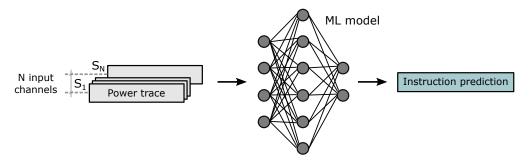

| 6.4  | Classification process. The power trace of each sensor $(S_1 \text{ to } S_N)$ is used as one of |     |

|      | N input channels. The input is then forwarded to the model, and the instruction                  |     |

|      | prediction is collected for accuracy evaluation                                                  | 84  |

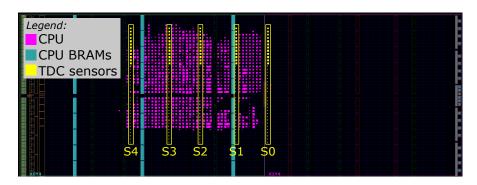

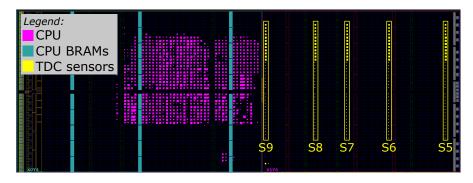

| 6.5  | Sensor delay lines (in yellow) and CPU (in purple) in Exp-IN                                     | 85  |

| 6.6  | Sensor delay lines (in yellow) and CPU (in purple) in Exp-OUT1                                   | 85  |

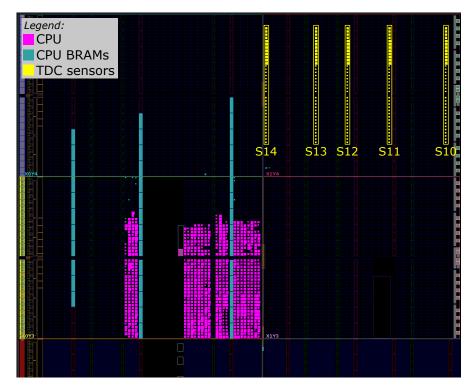

| 6.7  | Sensor delay lines (in yellow) and CPU (in purple) in Exp-OUT2                                   | 86  |

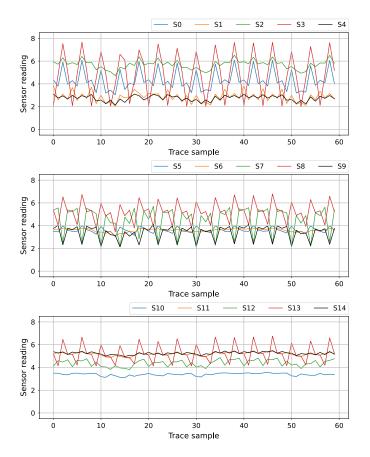

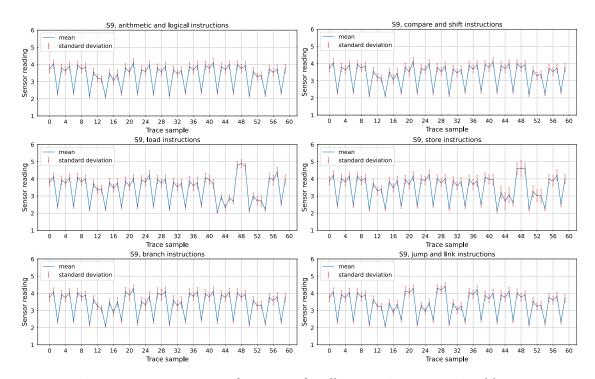

| 6.8  | Average sensor traces for the arithmetic and logical instructions in Table 6.3                   | 88  |

| 6.9  | Average traces of sensor S9 for all instruction groups in Table 6.3                              | 89  |

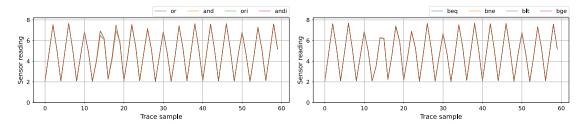

| 6.10 | O Average S3 traces for OR, AND, ORI, and ANDI (left) compared to S3 traces for                  |     |

|      | BEQ, BNE, BLT, and BGE (right)                                                                   | 89  |

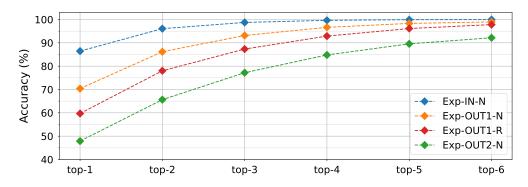

| 6.11 | Top-K accuracy (K = 1, 2, 3, 4, 5, and 6) using ResNet, for all four datasets                    | 92  |

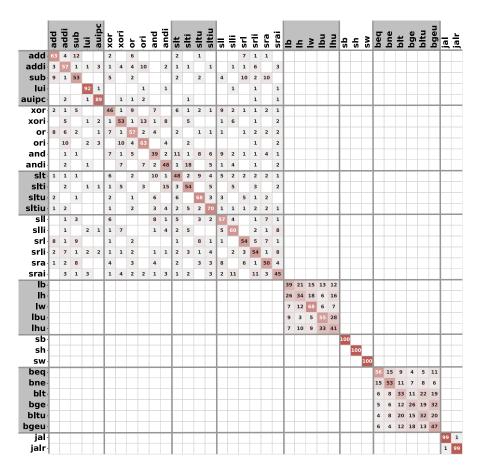

| 6.12 | 2 Normalized confusion matrix (in %, rounded) of the ResNet model (100 epochs),                  |     |

|      | for Exp-OUT1-R                                                                                   | 93  |

| 6.13 | 3 Confusion matrix in case of instruction type classification                                    | 94  |

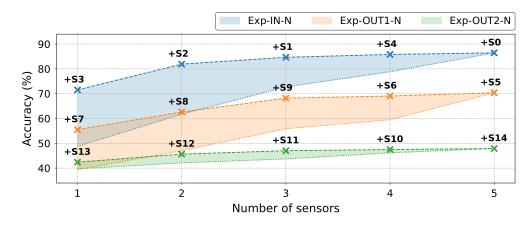

| 6.14 | Average instruction classification accuracy in the function of the number of                     |     |

|      | sensors contributing to the dataset, for all datasets, with the ResNet model.                    |     |

|      | Upper, dashed lines correspond to including the next best sensor in the dataset.                 |     |

|      | Lower, dotted lines correspond to including the next worst sensor in the dataset.                | 98  |

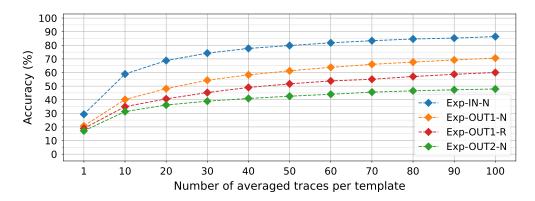

| 6.15 | 5 Accuracy in the function of the number of averaged traces per template. The                    |     |

|      | dataset size is 10,000 templates per instruction, while the model used for training              |     |

|      | is ResNet                                                                                        | 99  |

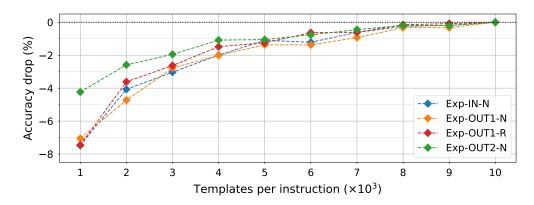

| 6.16 | 6 Accuracy drop in the function of the dataset size (number of templates) used for               |     |

|      | training and testing compared to the full dataset with 10,000 templates. Results                 |     |

|      | are shown on the ResNet model for all four datasets                                              | 100 |

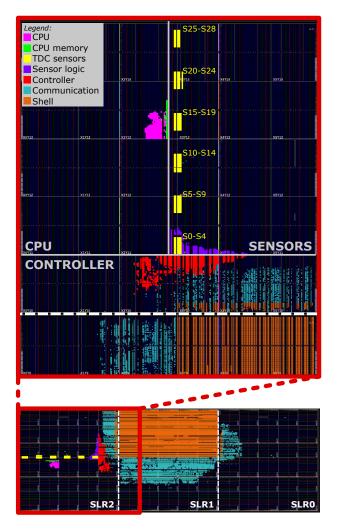

| 6.17 | Floorplan on the Alveo U200 board. Sensor delay lines (in yellow) and CPU (in                 |     |

|------|-----------------------------------------------------------------------------------------------|-----|

|      | purple)                                                                                       | 102 |

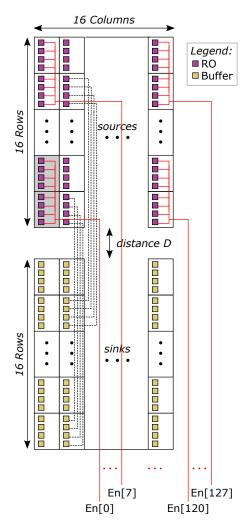

| 7.1  | RO fence occupying 32×16 FPGA slices; four LUTs are used per slice. Four                      |     |

|      | vertically neighboring slices form a bank. In gray, bank with index zero. Each                |     |

|      | bank is controlled by a dedicated enable signal                                               | 116 |

| 7.2  | Wire fence of 32×16 FPGA slices; four LUTs are used per slice. The top region                 |     |

|      | is occupied by sources (ROs). The bottom region is reserved for sinks (buffers).              |     |

|      | The distance between the two regions is adjustable. Two vertically-neighboring                |     |

|      | slices form a bank. Each bank is controlled by a dedicated enable signal                      | 117 |

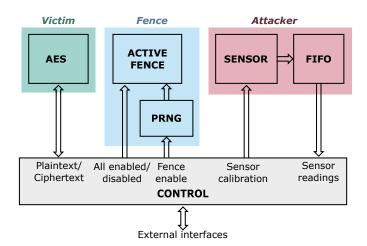

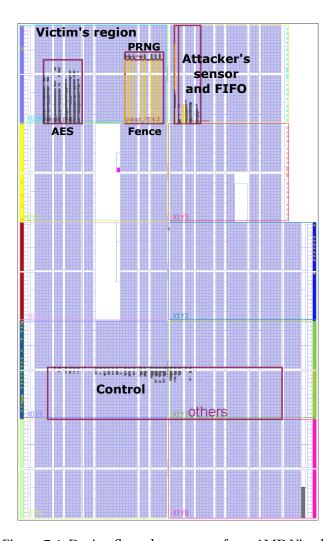

| 7.3  | System block diagram                                                                          | 119 |

| 7.4  | Design floorplan, as seen from AMD Vivado                                                     | 120 |

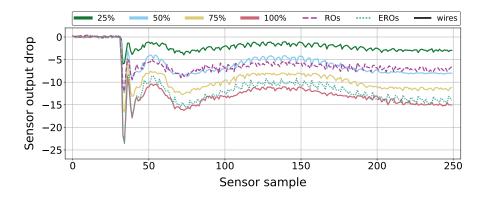

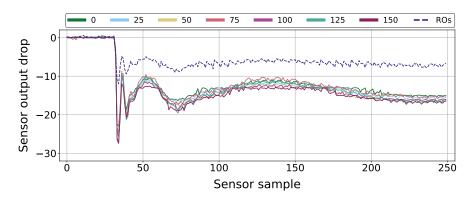

| 7.5  | Sensor readings drop (i.e., voltage drop) caused by the activation of RO/ERO                  |     |

|      | wasters (dashed lines) compared to wire-based wasters (solid lines)                           | 121 |

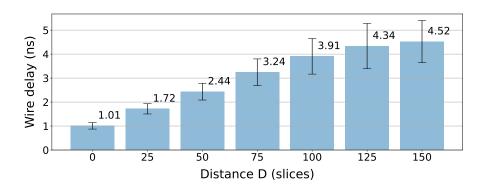

| 7.6  | Voltage drop for different distances $\mathcal{D}$ (in slices) with wire-based wasters (solid |     |

|      | lines), compared to ROs (dashed line)                                                         | 122 |

| 7.7  | Wire delay from source to sink of a wire-based waster extracted using Vivado                  |     |

|      | 2018.3 static timing analysis, in the function of distance parameter $D.\dots$                | 122 |

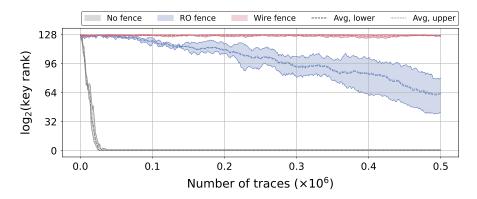

| 7.8  | Key rank estimation with 0.5M traces                                                          | 124 |

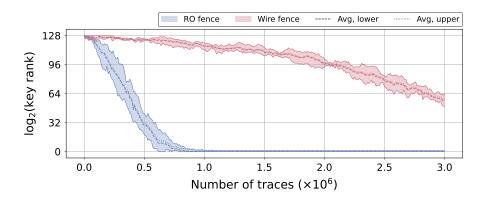

| 7.9  | Key rank estimation with 3M traces                                                            | 125 |

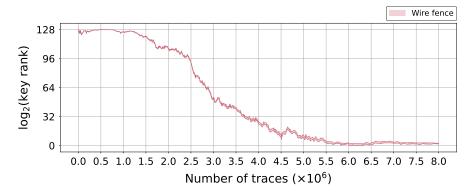

| 7.10 | Key rank estimation for the wire fence with 8M traces                                         | 126 |

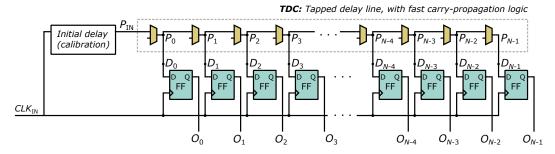

| 8.1  | TDC sensor                                                                                    | 134 |

| 8.2  | Routing delay sensor with a tapped delay line                                                 | 138 |

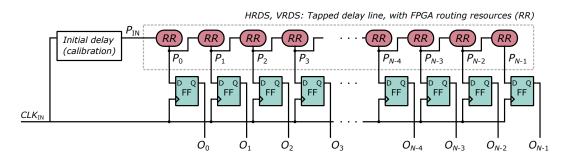

| 8.3  | Placement and routing of a segment of VRDS and HRDS sensors                                   | 138 |

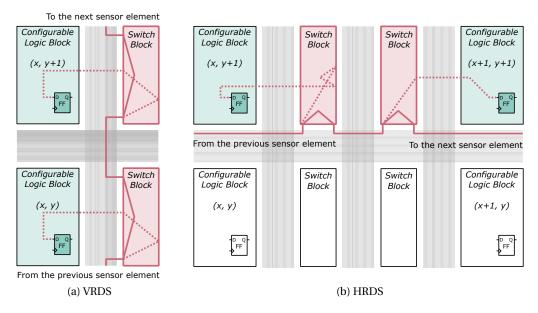

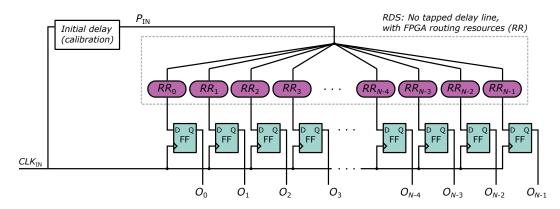

| 8.4  | RDS sensor.                                                                                   | 140 |

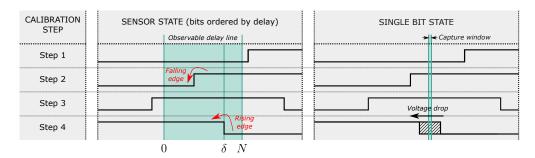

| 8.5  | Calibration steps for the RDS sensor.                                                         | 143 |

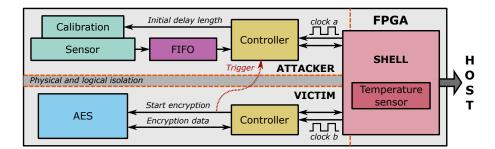

| 8.6  | System architecture                                                                           | 146 |

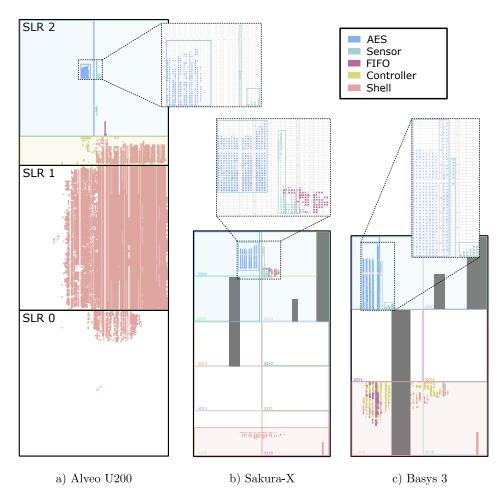

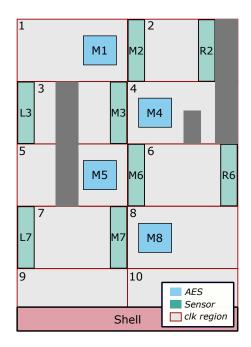

| 8.7  | Floorplan of all three boards used in the experimental evaluation                             | 147 |

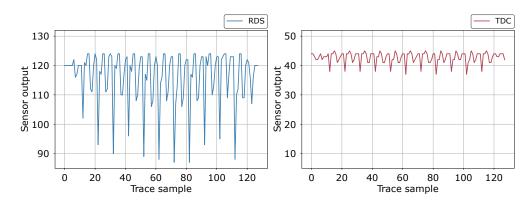

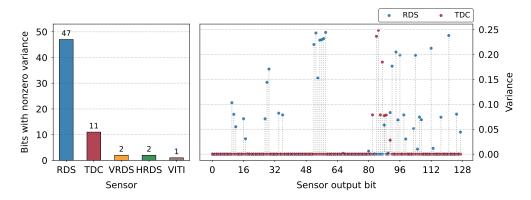

| 8.8  | One side-channel trace recorded with the RDS (left) and the TDC (right) sensor.               | 150 |

| 8.9                                                                   | Number of bits toggling during trace acquisition for every sensor (left), and the                                                      |                   |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                       | variance of the bits for RDS and TDC sensors (right)                                                                                   | 151               |

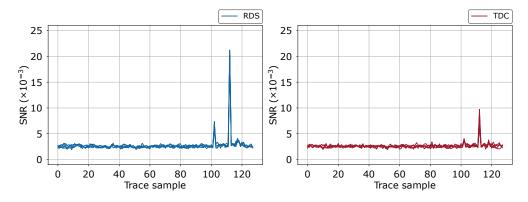

| 8.10                                                                  | Signal-to-noise ratio for the RDS (left) and TDC (right), computed on the least-                                                       |                   |

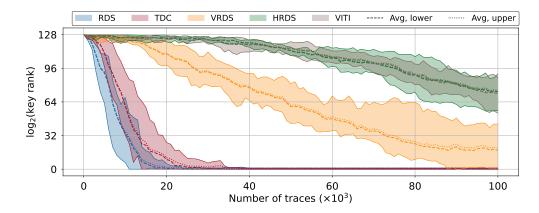

|                                                                       | significant byte of the output of the ninth AES round                                                                                  | 152               |

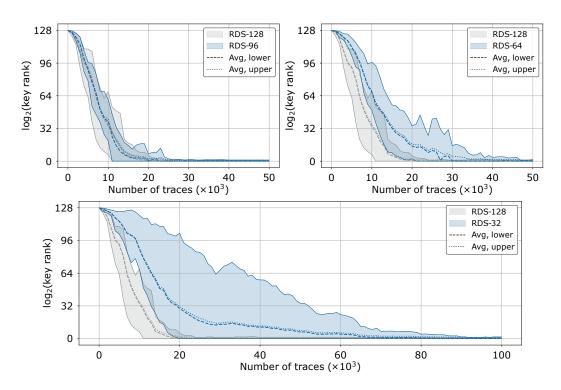

| 8.11                                                                  | Key rank estimation for TDC, VITI, and our three RDS variants                                                                          | 152               |

| 8.12                                                                  | Comparison of RDS sensors with the number of bits used                                                                                 | 153               |

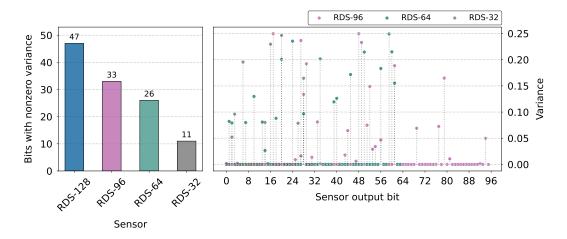

| 8.13                                                                  | Left, the number of bits toggling during 100k trace acquisitions for the RDS with                                                      |                   |

|                                                                       | 128, 96, 63, and 32 bits in the output register. Right, the variance per bit                                                           | 154               |

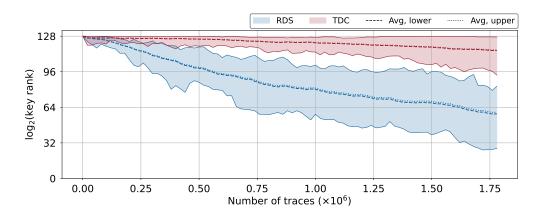

| 8.14                                                                  | Key rank estimation for the TDC and RDS sensors on the Alveo U200 board. $$ . $$ .                                                     | 154               |

| 8.15                                                                  | Floorplans for the chosen sensor and AES placements                                                                                    | 155               |

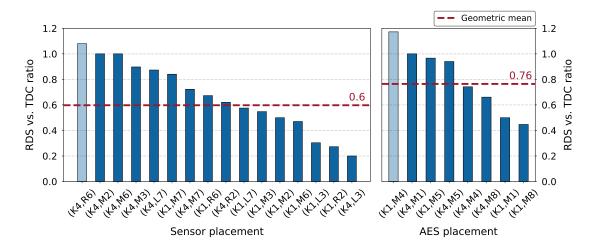

| 8.16                                                                  | Ratio between the number of traces needed to break the key with the RDS and                                                            |                   |

|                                                                       | the TDC sensor when varying the placement of the sensor (left) or the AES (right).                                                     |                   |

|                                                                       | In dark blue are the results where an attack with RDS is at least as efficient as                                                      |                   |

|                                                                       | with TDC. The dashed red line corresponds to the geometric mean                                                                        | 157               |

|                                                                       |                                                                                                                                        |                   |

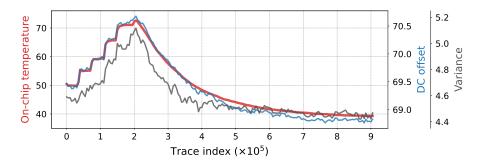

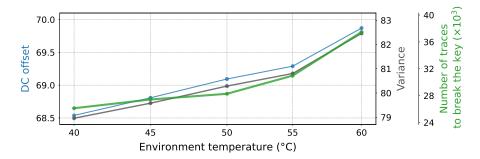

| 9.1                                                                   | The trace DC offset and variance at different on-chip temperatures, in the func-                                                       |                   |

| 9.1                                                                   | The trace DC offset and variance at different on-chip temperatures, in the function of elapsed time, i.e., the trace acquisition index | 167               |

| 9.1                                                                   |                                                                                                                                        |                   |

|                                                                       | tion of elapsed time, i.e., the trace acquisition index.                                                                               | 167               |

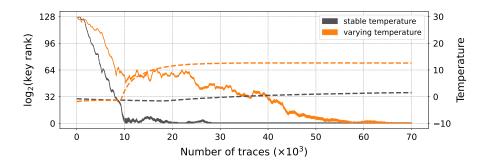

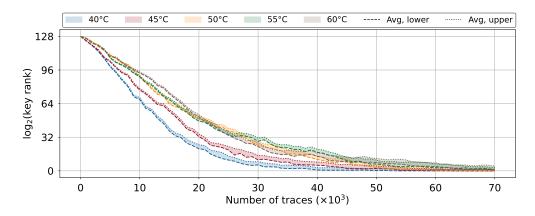

| 9.2                                                                   | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167               |

| 9.2<br>9.3                                                            | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168        |

| 9.2<br>9.3                                                            | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168        |

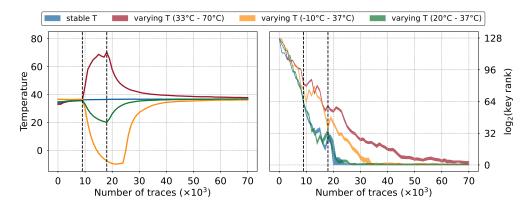

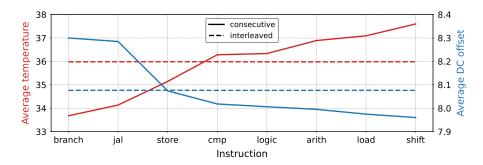

| 9.2<br>9.3<br>9.4                                                     | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168<br>168 |

| 9.2<br>9.3<br>9.4                                                     | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168<br>168 |

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li></ul>             | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168<br>168 |

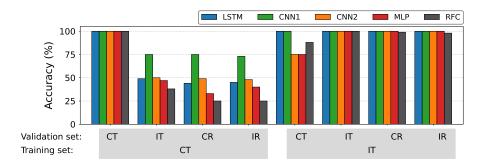

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li></ul>             | tion of elapsed time, i.e., the trace acquisition index                                                                                | 167<br>168<br>168 |

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li><li>9.6</li></ul> | tion of elapsed time, i.e., the trace acquisition index                                                                                | 168<br>168<br>169 |

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li><li>9.6</li></ul> | tion of elapsed time, i.e., the trace acquisition index                                                                                | 168<br>168<br>169 |

| 9.9 | 9 Impact of trace acquisition on the evolution of the training accuracy, in the case |     |  |  |

|-----|--------------------------------------------------------------------------------------|-----|--|--|

|     | of soft-core CPU instruction classification                                          | 173 |  |  |

## **List of Tables**

| 4.1  | FPGA resource utilization breakdown. The number of available resources shown        |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | first. In the left columns of the two AES groups, the resources occupied by the     |     |

|      | encryption core and related modules. In the right columns, the resources used       |     |

|      | by the leakage-estimation parts of the system                                       | 54  |

| 6.1  | Resource utilization of the soft-core CPUs                                          | 78  |

| 6.2  | Coarse calibration, fine calibration, and observable delay line slices per sensor.  | 79  |

| 6.3  | RV32I base integer instructions for template generation                             | 82  |

| 6.4  | Architecture details of the deep learning models                                    | 91  |

| 6.5  | Instruction classification accuracies (in %) for the deep learning methods. The     |     |

|      | highest accuracies, in bold, are obtained using the 1D-CNN2 and ResNet models.      | 92  |

| 6.6  | Classification accuracy of the ResNet model trained for hierarchical classification |     |

|      | on the Exp-OUT1-R dataset                                                           | 94  |

| 6.7  | Difference in the instruction classification accuracies when using classical ML     |     |

|      | approaches, compared to the deep learning methods                                   | 96  |

| 6.8  | Instruction classification accuracies for the classical machine-learning methods.   |     |

|      | The highest accuracies, in bold, are obtained when combining SVM with PCA           |     |

|      | and QDA with LDA                                                                    | 97  |

| 6.9  | Average instruction classification accuracies (in %) of ResNet, when trained on     |     |

|      | the traces of a single sensor only. In bold, the highest accuracies for each of the |     |

|      | four datasets                                                                       | 98  |

| 6.10 | Instruction classification accuracies on Alveo U200 (in %) for the ResNet model.    | 103 |

|      |                                                                                     |     |

#### List of Tables

| 6.11 | Code sequence classification accuracies (in $\%$ ) for the deep learning methods. |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | The highest accuracies, in bold, are obtained using the 1D-CNN1, 1D-CNN2,         |     |

|      | LSTM & 1D-CNN, and ResNet models                                                  | 104 |

| 7.1  | CPA attack results with 0.5M traces                                               | 123 |

| 7.2  | CPA attack results with 3M traces                                                 | 125 |

| 8.1  | Characteristics of the TDC, VITI, and our three variants of the RDS sensor        | 140 |

| 8.2  | Key and plaintext values used in the experimental evaluation                      | 148 |

| 8.3  | Resource utilization of TDC, VITI, and RDS                                        | 149 |

| 8.4  | Number of traces required to break the full AES 128-bit key, for different sensor |     |

|      | placements (AES placed at M1) and different AES placements (sensor placed at      |     |

|      | M2). The last row shows the average number of traces to break the key per FPGA    |     |

|      | region, both RDS and TDC sensors considered                                       | 157 |

| 9.1  | Architecture details of the ML models                                             | 165 |

| 9.2  | Accuracy of ML models with and without preprocessing                              | 173 |

## **List of Abbreviations**

AES advanced encryption standard

ASIC application-specific integrated circuit

**BRAM** block RAM

**CLB** configurable logic block

**CNN** convolutional neural network

**CPA** correlation power analysis

**CPU** central processing unit

CSP cloud service provider

**CWT** continuous wavelet transform

**DCM** digital clock manager

DL deep learning

DoS denial-of-service

**DPA** differential power analysis

**DSP** digital signal processing

EM electromagnetic

FF flip-flop

#### **List of Tables**

FIFO first-in-first-out FPGA field-programmable gate array FSM finite state machine **GDM** Gaussian diffusion model **GPU** graphics processing unit **HD** Hamming distance **ISA** instruction set architecture **ITD** inverse temperature dependence **k-NN** k-nearest neighbors KL Kullback-Leibler LDA linear discriminant analysis LFSR linear-feedback shift register **LSTM** long short-term memory LUT look-up table ML machine learning MLP multi-layer perceptron MMCM mixed-mode clock manager **PCA** principal component analysis PCB printed circuit board **PDN** power delivery network PID proportional-integral-derivative xxxii

PLL phase-locked loop

PRNG pseudo-random number generator

QDA quadratic discriminant analysis

**RDS** routing-delay sensor

**ResNet** residual network

**RFC** random forest classifier

**RNN** recurrent neural network

RO ring oscillator

**RR** routing resources

**RSA** Rivest-Shamir-Adleman

SB switch box

**SCA** side-channel analysis

**SLR** super-logic region

**SNR** signal-to-noise ratio

**SPA** simple power analysis

**SVM** support vector machine

**TDC** time-to-digital converter

**TPU** tensor processing unit

**TRNG** true random number generator

TVLA test vector leakage assessment

VM virtual machine

**VTA** versatile tensor accelerator

## 1 Introduction

Due to the end of Moore's law and the breakdown of Dennard's scaling, compute-intensive systems are transitioning from homogeneous and processor-dominated systems toward more heterogeneous architectures which rely on specialized hardware to improve performance and energy efficiency. As a result, today's computing systems feature not only central processing units (CPUs) but also graphics processing units (GPUs) and special-purpose integrated circuits such as application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs). Compared to ASICs, using FPGAs significantly reduces design time, development, and deployment costs. The flexibility of FPGAs, coupled with their highly-parallel architecture and energy efficiency, has led to their integration into various heterogeneous systems—from small embedded and cyber-physical systems to datacenters and, recently, the public cloud of major cloud service providers (Microsoft Azure [2], Amazon AWS [3], and Alibaba Cloud [4]).

The growing awareness of the importance of security and privacy and the increased regulatory and legal attention to data makes security not only desired but, in many cases, required in modern systems. Industry and research trends have seen an increase in attention to cybersecurity, trusted execution environments, and confidential and trusted computing [5, 6]. Therefore, apart from satisfying the short design time and ever-growing complexity of the systems, designers of FPGA-based systems face a new challenge: ensuring security and privacy for the system end users. Consequently, previous work has explored FPGA security in heterogeneous systems,

covering vulnerabilities such as fault injection or side-channel analysis (SCA) attacks [7]. In particular, power SCA attacks—targeting information inadvertently leaked through the power consumption or supply voltage fluctuations—can be easily mounted by attackers with physical access to the device [8, 9]. In power SCA attacks, an adversary collects a number of power measurements, typically with an oscilloscope, and applies statistical or machine learning techniques to infer algorithmically secure information. These attacks represent a critical class of side-channel attacks, as even a limited number of power measurements can contain leakage sufficient to extract confidential data, such as encryption keys, from unprotected devices [10].

Recent research demonstrated that physical proximity is no longer required for SCA power measurements on FPGA, as voltage fluctuations occurring during the computation of a hardware module, for example, a cryptographic accelerator, can also be captured by dedicated circuits realized in the FPGA logic itself, such as time-to-digital converter (TDC) converter sensors or ring oscillators [11–14]. Data collected with these voltage-drop sensors could then be used instead of the classical power measurements collected by an oscilloscope to successfully recover confidential information. Successful examples of these attacks directly exploited the relation between circuit activity and the voltage fluctuations on the power delivery network (PDN) to extract encryption keys of a cryptographic core [12,13] or data from machine learning (ML) accelerators [15,16].

In this thesis, motivated by the possibility of performing remote voltage measurements, we investigate the implication of voltage-drop sensors on the security of remotely accessible FPGAs. We identify two prominent use cases of remote FPGAs—cyber-physical devices deployed in the field and cloud FPGAs—and we show that on-chip voltage sensors can be used to both evaluate and compromise the security of FPGA-based systems.

#### 1.1 Thesis Goals

Often accessible to attackers, deployed cyber-physical devices remain susceptible to physical attacks. In the case of both protected and unprotected devices in the field, adversaries can

resort to more invasive methods to increase the power side-channel leakage and reduce the attack effort, such as tampering with the PDN [12, 17]. Moreover, effects such as aging, malfunctioning, or even maintenance can also impact the leakage. However, the device leakage is only verified before deployment, in a controlled scenario, and is almost never reevaluated after deployment. As its **first objective**, this thesis explores the possibility of leveraging on-chip sensors to provide continuous monitoring and evaluate the device's vulnerability to first-order power SCA attacks [18].

In the cloud, a multitenant ecosystem is already in place, and the available computational resources—namely CPUs—are shared between system users. To enable better management and use of available datacenter resources, increased efforts are being made to support secure virtualization and sharing of FPGA hardware acceleration fabric [19–31]. However, spatial sharing, i.e., co-locating multiple users on the same FPGA, implies many security issues, primarily due to the access to low-level hardware primitives and electrical-level coupling via the shared PDN or long wires [32, 33]. As a **second objective**, this thesis tackles power side-channel security in shared, i.e., multitenant FPGAs. It uncovers and analyzes new security vulnerabilities introduced by attackers with access to low-level FPGA logic—power SCA attacks on encryption and soft processor cores using on-chip voltage sensors [14]—and explores new, more efficient ways of mitigating these vulnerabilities specialized for shared FPGAs.

As a **third objective**, this thesis aims to explore new, more efficient, and stealthy techniques of sensing on-chip voltage in shared FPGAs [34]. Finally, this thesis aims to evaluate the impact of external factors, specifically temperature, on on-chip voltage sensors and the success of remote power side-channel attacks in multitenant FPGAs [35].

#### **Thesis statement:**

Access to fine-grained FPGA hardware in modern heterogeneous systems allows constructing efficient on-chip voltage sensors, which create new opportunities to evaluate, exploit, and hide power side-channel leakage in remote FPGAs.

#### 1.2 Thesis Contributions

As indicated in the thesis title and statement, this work extends the state of the art alongside three main pillars of power side-channel leakage in remote FPGAs: evaluating, exploiting, and hiding. Fig. 1.1 illustrates the main contributions of this work. Alongside the evaluating axis, this thesis leverages FPGA-based voltage sensors to enhance security by providing continuous leakage monitoring and methodologies to evaluate the power side-channel security of deployed devices. Our work uses FPGA-based voltage sensors to demonstrate new vulnerabilities in FPGA-based systems, enhancing the state of the art alongside the exploiting axis. Finally, our work contributes to the hiding axis by leveraging low-level FPGA logic to reduce the power side-channel leakage, while using the FPGA-based sensor to record voltage traces.

We organize the thesis contributions into three main parts to align with the thesis goals outlined in Chapter 1.1. Part I centers around evaluating the security of deployed cyber-physical devices, contributing to the evaluating axis. Part II, contributing to all three axes of power side-channel security, centers around multitenant FPGA security. Lastly, Part III, contributing to the evaluating and exploiting axis, centers around advanced sensor architectures and temperature impact on sensors. In the following subsections, we describe the contributions of each of the three main parts of the thesis.

#### 1.2.1 Evaluating the Security of Deployed Cyber-Physical Devices

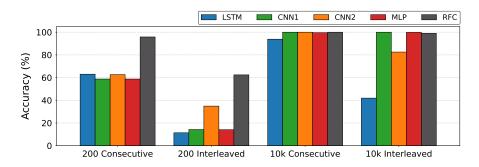

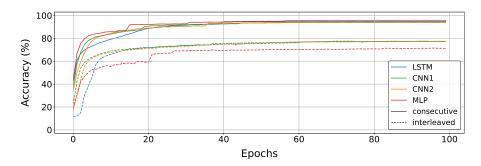

The leakage of cyber-physical devices can change during their service life for various reasons (tampering, aging, or malfunctioning). However, until our thesis, the device leakage was typically evaluated in laboratory environments before deployment and not reevaluated. Previous work demonstrated that FPGA-based voltage sensors require an order of magnitude more traces than an oscilloscope for a successful power analysis attack [12]. Our work shows that, despite lower-quality power measurements, FPGA-based voltage sensors can be successfully leveraged to evaluate power side-channel leakage in deployed devices. The work in this thesis was the first to present and validate a built-in test for self-evaluation of power side-channel