## Rebooting Virtual Memory with Midgard

Présentée le 22 août 2023

Faculté informatique et communications Laboratoire d'architecture de systèmes parallèles Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

## Siddharth GUPTA

Acceptée sur proposition du jury

Prof. C. Koch, président du jury

Prof. B. Falsafi, A. Bhattacharjee, directeurs de thèse

Dr G. Loh, rapporteur

Dr J. Gandhi, rapporteur

Prof. S. Kashyap, rapporteur

अति का भला ना बोलना, अति की भली ना चुप ।

अति का भला ना बरसना, अति की भली ना धूप ।

— कबीरदास

Excess of speaking is bad, and excess of silence is also bad.

Just like excess of rain is bad, and excess of sun is also bad.

Excess of anything is bad, balance is key.

— KabirDas

To my mentors...

# Acknowledgements

My PhD journey has been the most intensive task I have ever undertaken. Striving for a PhD has significantly altered various aspects of my personality and underlined the value of perseverance, teamwork, balance, and patience. Throughout my PhD journey, I have immensely enjoyed working on various research projects and met extremely talented colleagues from diverse academic and cultural backgrounds, which has motivated and taught me much about collaboration. And just like every other PhD student, I have also had various dips in my motivation during the challenging parts, which left me questioning various tradeoffs I had made. I would not have been able to reach the finish line without the support of the wonderful people around me, to whom I owe my sincere gratitude.

First, I am grateful to my advisors, Babak Falsafi and Abhishek Bhattacharjee. Babak is famous for being a tough taskmaster, which is fueled by his deep commitment to the success of his students. There have been multiple instances where my motivation faltered, but he tenaciously and unceremoniously pushed me past the finish line. While I have undoubtedly questioned his methods during the process, I can now understand the great value he provides to his students. Babak is extremely smart and has an excellent knack for spotting technology trends, which results in fruitful research directions for his students. He seeks perfection in everything and has always shone a spotlight on my shortcomings and the "wing-it" attitude, forcing me to improve as a well-rounded researcher and individual. He inculcates a strong lab culture which leads to long-lasting ties and friendships among students in and across generations. Being his student has connected me to a large family of super talented and successful individuals who drive the future of technology, which is a great perk on its own. Finally, Babak and his lab's culture are solely responsible for me finding a great love of my life — skiing — which I hope

#### Acknowledgements

will continue till my knees give out. Thank you, Babak!

Abhishek is one of the kindest persons I have ever met, and cares deeply about the well being of his students. For all the deadlines we have endured together, he has never failed to check up on me and offer words of encouragement. He has always offered me a different perspective on things compared to the Babak school of thought, which has helped me in exploring new ideas in research and presentation. Being one of the leading experts on Virtual Memory with concrete industry-scale contributions, he has been instrumental in shaping my understanding of the area and the output of research projects. Being Abhishek's student gave me access to another academic family of great colleagues, even though we only met at conferences. I am very glad that Abhishek agreed to advise me.

I am also grateful to my silent advisor, Boris Grot, who has been helping me even before I started my PhD journey. Boris is a great blend of interpersonal skills and technical knowledge, and has been a great source of inspiration for me. He is single-handedly responsible for me diving into a 6-year-long PhD program with Babak at the naive age of 22. I had worked with him for only four months when he convinced me to go for a PhD instead of a shorter Masters program as was done by many of my colleagues, and my current research standing is a direct result of his intuition. I am forever indebted to Boris for giving me my big break as an intern to work in a high-profile research lab during my Bachelors, and for teaching me my first lesson in research and presentation. I am very excited that I will have the opportunity to work with Boris again at my next venture.

Next, I would like to thank Gabriel Loh, Jayneel Gandhi, Sanidhya Kashyap, and Christoph Koch for serving on my PhD thesis committee, and for invaluable advice that has shaped the final thesis. Yuanlong Li, Yunho Oh, Atri Bhattacharyya, Qingxuan Kang, and Mathias Payer have been close collaborators in the work done as part of my thesis. Thank you for all your help and support!

The strong group culture at PARSA (my home away from home) has been a highlight of my PhD journey. I would like to start by thanking Mario Drumond, Rishabh Iyer, and Ognjen Glamočanin (in the order of increasing hair on their head) who have been my closest friends

and brothers. Mario is an extremist — but not the kind you see on TV — with an out-of-the-world perspective on almost every topic. The best thing about Mario is his direct unfiltered opinions, but they might take some time to get used to. While he was still in the lab and was forced to listen to my random research ideas, he only gave reactions falling in "this is the greatest thing ever" or "everyone in the room is now dumber" bucket. Fortunately or unfortunately, I have adopted Mario's way of dealing with bad and nervous situations, which typically involves saying "it could be worse, you could be missing a leg", or "you can cry throughout the presentation and just change the slides, and your paper will still get published". It helped a lot!

While Rishabh is not in PARSA, he is considered an honorary member because of historical reasons. Rishabh is extremely competitive, which shows up in his work, games, fitness, and asks of a tougher final exam. He also has a strictly hate relationship with bureaucracy, keys, cards, etc. which often ends up in rescue requests or stones being thrown at windows. We have spent countless hours walking along the lake and discussing research ideas, which has been greatly helpful. Having Rishabh around has definitely motivated me to perform better as a researcher and at many other activities. Now that he is changing continents, it will be much harder to come up with crazy activities on my own.

Ogi has been my office mate for the past few years, and has endured various outbursts followed by calm-down conversations. His love for cleanliness has resulted in a display of sanitizers in our office, and hate for bed bugs has been a constant source of amusement. He has this amazing ability where he can take the simplest event, and start spiralling and imagining the worst outcome possible. While I have enjoyed the days where I only had his company, we have always needed to open a window from time to time. All in all, Ogi has been a great friend and office mate, and it is certain that without him, my PhD experience would be much worse. In various permutations, we have all shared a lot of laughs together, which has made my time at EPFL considerably easier. Thank you guys!

Moving on to the rest of the lab, I will first thank the alumni — Alex Daglis, Yunho Oh, Arash Pourhabibi, Mark Sutherland, and Javier Picorel — who have already tasted the sweet nectar

of graduation. Alex was the senior-most student in the lab when I started my PhD and we overlapped for only one year, which shocks him each time we meet. I was extremely fortunate to submit my first paper with Alex because he gladly took that opportunity to show me the ropes of how things were done in the lab, in particular how to match the fonts in the figures with the ones in the text, something that I have never done because "the fonts are too pointy". I can honestly say that meeting Alex and discussing random research topics for hours is one of the main reasons I go to conferences in the first place.

Yunho has been one of the most positive people I have met, where the positivity is typically succeeded by a comment about how I am doomed. We have the weirdest conversations as none ends without death threats, references to the Godfather, talks about adopting and smuggling me to Korea, or weird GIFs being sent around. I cannot go to KFC anymore without remembering the great times we have had. He also strangely keeps visiting Switzerland just to hang out in Lausanne, and skips all other interesting parts of the country. God help him! Arash is one of the most diligent people I have met, and the phrase "slow and steady" applies very well to him, while I am more of a "move fast and break things" person. He is an Apple fanatic, and I do not know anyone else with the same degree of obsession. Finally, the image of him saying "you have got to listen" while pulling his ear has been burned into my brain, and I don't think that I can ever erase it, even though I might not end up listening anyways. Mark is one of the most detail-oriented people I have met, and his motivation to chase down technical nitty-gritties or conduct a super-thorough evaluation of an idea has been inspiring. He is also very disciplined, and his ability to regularly come to the office early in the morning and leave at a good hour to maintain a work-life balance is something to be adopted. Javier is the biggest party-person I know, and is really fun to be around. I am really thankful to him for hiring me for a five-month cool-down period in Munich, which was punctuated with long beer-drinking sessions, and barbecue sessions along the Isar river. I really needed it! I hope we get to work together again in the future.

I am also very grateful to Atri Bhattacharyya, Simla Harma, Yuanlong Li, Shanqing Lin, Shashwat Shrivastava, and Ayan Chakraborty for their support. Atri's attitude to handle life as it comes is inspiring, or in his words "carefree wanderings". Simla is a very warm and cheerful

person and I have always seen her smiling, which is a very rare quality today. Yuanlong is super smart and hardworking, and I am sure that he will be successful with taking Midgard forward. Shanqing is super fun to be around, and is never afraid to ask the "why" questions, especially when they result in hilarious responses. Shashwat and Ayan have suffered through many skiing days with me. Shashwat has a great ability to fall randomly, but then get up immediately and start skiing again without losing confidence. Ayan seems to be the only person who has matched my craziness for skiing in the lab, and I really hope that he can pass it to other lab members, and keep the skiing culture going strong. I would also like to thank Dmitrii Ustiugov, Dina Gamaleldin, Ali Ansari, and Buğra Eryılmaz for their constant feedback and support. Finally, I would like to sincerely thank Stéphanie Baillargues, without whom the list of PARSA members is incomplete. Stéphanie is a wizard when it comes to administrative affairs, and does not let the bureaucracy get to the PhD students in the lab. While I have loved spending the lab's money, I have always needed to battle Stéphanie who is responsible for spending the Swiss taxpayer's money reasonably. Needless to say, the Swiss taxpayers chose a great champion to represent them.

Beyond PARSA, I would like to thank a few more people for their help and support. Effi Georgala has been very supportive and motivating whenever she is around. Teca Glamočanin has been a great help when selecting gifts (which is typically beyond my scope of expertise), and has sometimes succumbed to the skiing pressure applied by me. Negar Foroutan and Kyveli Short have always been great fun to hang out with. Sahand Kashani, Mahyar Emami, Ahmet Yüzügüler, and Xinrui Jia have been frequent lunch buddies, and have provided a safe space to vent about the typical PhD blues. Sahand shares my aversion to heat and love for the cold, and accompanied Ahmet and I for the amazing trip to Swedish laplands during Christmas in 2022. Ahmet has been a master of not giving a damn for things he does not care about. Pakshal Bohra has been a great friend, and has helped a lot in balancing Rishabh out, especially during WWE gaming marathons or eating out in restaurants. Poulami Das and Diya Joseph have been great conference friends, and we have had incredible trips to Heidelberg and Portugal together. Phil and Paola have been my flatmates for the last couple of years,

#### Acknowledgements

and we have had great fun in cooking together, watching movies, having intense spicy noodle eating contests, and even a few skiing lessons which were never repeated. Finally, the YUVA organization at EPFL has been a great source of keeping in touch with the Indian folks around, and enjoying Indian festivals far away from home.

I would like to sincerely thank my close group of friends from BITS - Pratyush Patel, Rohith (Madara) Ramakrishnan, Pratik Singhal, and Mukul Kothari. Patel, Madara, Singhal, and I (the OG OSFS) worked on various unsupervised projects during BITS (such as building an OS from scratch), which I believe was a key in developing my interest towards computer architecture and systems. Patel, Madara, Singhal, Mukul, and I starting hanging out daily in my second year at BITS, which immediately led to a plunge in my GPA, something they will not let me forget easily (especially LCS and Philosophy). We have done a lot of crazy stuff together, in and after BITS, and hopefully will continue to do the same. I am glad to say that we all are still in regular contact, something that typically does not happen when everyone is in a different physical location. Srishti Sahani, Priyanshi Nanda, Aishwarya Anand, Furquan Uddin, Shray Agarwal, Srishti Chaudhary, Rachit Jawrani, and Peshal Agarwal have been my (school) friends for about 15 years now. The best part about our friendship is that we might not talk for months, but when we do talk or meet, then things are exactly the way they were last time. Thank you for being in my life all this time.

Last but not the least, I would like to thank my family from the bottom of my heart for their unconditional love and support. It is the environment and upbringing that I received from my mom, dad, uncle, and aunt, that has moulded my character to its current form and is directly responsible for any success I have in this life. My younger brothers — Harsh, Shantanu, and Yash — have been a great company to grow up with, and I am very proud of you. I don't have enough words to describe the sacrifices made by my family to build a better future for me and my siblings. I am extremely fortunate and grateful to have them. Finally, even though it is recent, I would like to thank Anvita and my in-laws for wholeheartedly welcoming me into their lives. No backsies! I am excitedly looking forward to a future together.

I thank the various funding sources that have enabled this thesis. My PhD research has been partially supported by EPFL, a Qualcomm Innovation Fellowship on *Rebooting Virtual Memory with Midgard* (CMS Contract No. ECO-461760), and the *Hardware/Software Co-Design for In-Memory Services* project (200020B\_188696) of the Swiss National Science Foundation.

Lausanne, August 15, 2023

Siddharth Gupta

## **Abstract**

Virtual Memory (VM) is a critical programming abstraction that is widely used in various modern computing platforms. With the rise of datacenter computing and the birth of planet-scale online services, the semantic and capacity requirements from memory have evolved dramatically and pose various challenges for VM. The traditional VM implementations cannot scale with the increasing memory capacity present in modern datacenter servers, and the adoption of heterogeneous memory hierarchies stresses the synchronization mechanisms in VM implementations. The increasing degree of multi-tenancy in datacenter servers requires lean virtualization mechanisms built using VM as a foundation, while the adoption of new paradigms such as microservices and serverless computing lead to increased contention and performance loss in VM implementations. Finally, the increasing requirement of confidentiality in various computing domains also requires improvements in VM implementation as it forms the basis of modern security mechanisms.

This thesis aims to holistically reinvent the VM implementation using OS, architecture, and microarchitecture co-design, which can help solve the above challenges. Our redesign of VM is based on the following key insights: (i) we can use the existing abstraction of Virtual Memory Areas (VMAs) to optimize address translation while ensuring that the application programming model is still POSIX-compliant so no changes are required, and reuse of existing abstractions provides an easy adoption path for the OS developers; (ii) we can divide the traditional address translation into a fast and slow step where the fast step is required on the critical path of all memory accesses and thus mandates specialized microarchitectural support, while the slow step is invoked infrequently and can be supported using the existing resources present in the cache hierarchy without requiring significant additional silicon; and (iii) instead

of encapsulating complicated functionalities completely in the microarchitecture, we can partly offload it to the OS using a simple OS and microarchitecture co-design while helping the OS developers ensure correctness by providing formal specifications of the required behavior. We realize the above insights by introducing an intermediate address space called Midgard between the virtual and physical address spaces. The Midgard address space is used to index the cache hierarchy and coherence domain while ensuring that the physical address space is only required when accessing the physical memory device. The introduction of the Midgard address space enables lean VMA-based virtual-to-Midgard address translation, providing fast access control and access to cache hierarchy while requiring little microarchitectural support. The page-based Midgard-to-physical address translation is only required for capacity management when accessing physical memory and can be performed using the resources already present in the cache hierarchy instead of requiring specialized microarchitectural support. To handle the exceptions generated by the delayed Midgard-to-physical address translation without requiring significant silicon resources, we introduce a novel OS + microarchitecture co-design to partly offload complicated microarchitectural functionality to be easily performed in the OS and provide formalism to help the OS developers ensure correct behavior. We evaluate the address translation in Midgard using full-system trace simulation and show that Midgard can eliminate address translation overhead by using incoming large-capacity cache hierarchies. We also build a full-system RISC-V prototype with Linux to model exception handling behavior for Midgard and show that the resulting design is both performant and correct. Overall, Midgard reinvents the traditional VM implementation and allows it to scale with the increasing memory capacity requirements in modern datacenter servers.

## Résumé

La mémoire virtuelle (VM) est une abstraction critique pour la programmation et est largement utilisée dans diverses platesformes informatiques modernes. Avec l'essor de l'informatique des centres de données et la naissance de services en ligne à l'échelle planétaire, les exigences sémantiques et de capacité de la mémoire ont considérablement évolué et posent divers défis à la VM. Les implémentations de VM traditionnelles ne peuvent pas évoluer avec la capacité de mémoire croissante présente dans les serveurs de centres de données modernes, et l'adoption de hiérarchies de mémoire hétérogènes met de la pression sur les mécanismes de synchronisation dans les implémentations de VM. Le degré croissant de multi-location dans les serveurs de centres de données nécessite des mécanismes de virtualisation allégés construits à l'aide de VM comme base, et l'adoption de nouveaux paradigmes tels que les microservices et l'informatique "serverless" entraînent une augmentation des conflits et une perte de performances dans les implémentations de VM. Enfin, l'exigence croissante de confidentialité dans divers domaines informatiques nécessite également des améliorations dans l'implémentation des machines virtuelles car elles constituent la base des mécanismes de sécurité modernes.

Cette thèse vise à réinventer de manière holistique l'implémentation des VM en co-concevant le système d'exploitation, l'architecture, et la microarchitecture, ce qui peut aider à résoudre les défis ci-dessus. Notre refonte de VM est basée sur les idées clés suivantes : (i) nous pouvons utiliser l'abstraction existante des zones de mémoire virtuelle (VMA) pour optimiser la traduction d'adresses tout en garantissant que le modèle de programmation pour les applications est toujours conforme à POSIX de sorte qu'aucune modification logicielle ne soit nécessaire, et la réutilisation des abstractions existantes fournit un chemin d'adoption facile pour le

développeurs de système d'exploitation; (ii) nous pouvons diviser la traduction d'adresse traditionnelle en une étape rapide et une étape lente où l'étape rapide est requise sur le chemin critique de tous les accès à la mémoire et nécessite donc un support microarchitectural spécialisé, tandis que l'étape lente est invoquée rarement et peut être prise en charge en utilisant le ressources existantes présentes dans la hiérarchie de cache sans consommer beaucoup plus d'espace; et (iii) au lieu d'encapsuler complètement des fonctionnalités compliquées dans la microarchitecture, nous pouvons les décharger en partie sur le système d'exploitation en utilisant une simple co-conception du système d'exploitation et de la microarchitecture tout en aidant les développeurs du système d'exploitation à garantir une execution correcte en fournissant des spécifications formelles du comportement requis.

Nous réalisons les idées ci-dessus en introduisant un espace d'adressage intermédiaire appelé Midgard entre les espaces d'adressage virtuel et physique. L'espace d'adressage Midgard est utilisé pour indexer la hiérarchie de cache et le domaine de cohérence tout en garantissant que l'espace d'adressage physique n'est requis que lors de l'accès au dispositif de mémoire physique. L'introduction de l'espace d'adressage Midgard permet une traduction allégée des adresses virtuelles vers Midgard basée sur VMA, offrant un contrôle d'accès rapide et un accès à la hiérarchie de cache tout en nécessitant peu de support microarchitectural. La traduction d'adresse Midgard en adresse physique basée sur des pages n'est requise que pour la gestion de la capacité lors de l'accès à la mémoire physique et peut être effectuée à l'aide des ressources déjà présentes dans la hiérarchie de cache au lieu de nécessiter un support microarchitectural spécialisé. Pour gérer les exceptions générées par la traduction retardée de l'adresse Midgard vers l'adresse physique sans nécessiter beaucoup plus d'espace, nous introduisons une nouvelle co-conception OS + microarchitecture pour décharger en partie les fonctionnalités microarchitecturales complexes à exécuter facilement dans le système d'exploitation et fournir un formalisme pour aider les développeurs de systèmes d'exploitation à garantir un comportement correct. Nous évaluons la traduction d'adresses dans Midgard à l'aide d'une simulation de trace complète du système et montrons que Midgard peut éliminer les frais généraux de traduction d'adresses en utilisant des hiérarchies de cache de grande capacité prochainement disponibles. Nous construisons également un prototype RISC-V complet avec Linux pour modéliser le comportement de gestion des exceptions pour Midgard et montrer que la conception résultante est à la fois performante et correcte. Dans l'ensemble, Midgard réinvente l'implémentation traditionnelle des machines virtuelles et lui permet d'évoluer avec les besoins croissants en capacité de mémoire dans les serveurs de centres de données modernes.

# **Contents**

| Ac | cknov | vledgements                                   |    | j             |

|----|-------|-----------------------------------------------|----|---------------|

| Al | ostra | zt                                            |    | ix            |

| Li | st of | Figures                                       | xv | / <b>ii</b> i |

| Li | st of | <b>Tables</b>                                 | x  | xii           |

| 1  | Intr  | oduction                                      |    | 1             |

|    | 1.1   | Virtual Memory in Datacenters                 |    | 2             |

|    | 1.2   | Thesis Goals                                  |    | 5             |

|    | 1.3   | Thesis Contributions                          |    | 7             |

|    | 1.4   | Thesis Organization                           |    | 11            |

|    |       | 1.4.1 Bibliographic Notes                     |    | 12            |

| 2  | Virt  | ual Memory                                    |    | 13            |

|    | 2.1   | A Fundamental Programming Abstraction         |    | 13            |

|    |       | 2.1.1 Programmability and Portability         |    | 14            |

|    |       | 2.1.2 Isolation and Protection                |    | 14            |

|    |       | 2.1.3 Memory Management and Over-Subscription |    | 16            |

|    |       | 2.1.4 Performance Optimizations               |    | 16            |

|    | 2.2   | Virtual Memory Implementation Today           |    | 17            |

|    |       | 2.2.1 Virtual Address Space                   |    | 18            |

|    |       | 2.2.2 Physical Address Space                  |    | 19            |

|    |       |                                               |    |               |

## **Contents**

|   |     | 2.2.3 Address Translation    |                                | 21 |

|---|-----|------------------------------|--------------------------------|----|

|   | 2.3 | Scaling Problems             |                                | 23 |

|   | 2.4 | Previous Proposals           |                                | 26 |

|   |     | 2.4.1 Contiguity in the Phy  | ysical Address Space           | 26 |

|   |     | 2.4.2 Virtual Cache Hierar   | chies                          | 29 |

|   |     | 2.4.3 Intermediate Addres    | s Spaces                       | 31 |

| 3 | Mid | dgard: An Overview           |                                | 35 |

|   | 3.1 | A VMA-Based Intermediate     | Address Space                  | 35 |

|   | 3.2 | Two-Step Address Translation | on: Logic-side and Memory-side | 38 |

|   | 3.3 | Challenges and Opportunit    | ies                            | 39 |

|   | 3.4 | Interface for Address Transl | ation                          | 40 |

| 4 | Mer | mory-side Exception Handli   | ng                             | 43 |

|   | 4.1 | Exception Handling Backgr    | ound                           | 45 |

|   |     | 4.1.1 Precise exceptions     |                                | 45 |

|   |     | 4.1.2 Long-Latency Excep     | tions can be Imprecise         | 47 |

|   |     | 4.1.3 Forced Precise Excep   | otions Kill Performance        | 48 |

|   | 4.2 | Precise Exceptions with Spe  | eculation                      | 49 |

|   |     | 4.2.1 Post-Retirement Spe    | culation                       | 49 |

|   |     | 4.2.2 Case Study: ASO        |                                | 51 |

|   |     | 4.2.3 Quantifying the Spec   | culation State                 | 52 |

|   | 4.3 | Imprecise Store Exceptions   |                                | 54 |

|   |     | 4.3.1 Brief Description      |                                | 54 |

|   |     | 4.3.2 Formal Definition of   | Memory Models                  | 55 |

|   |     | 4.3.3 Observing the Memo     | ory Order                      | 57 |

|   |     | 4.3.4 Contract Among the     | Cores, Interface, and OS       | 58 |

|   |     | 4.3.5 Formalism with Split   | t Stream                       | 60 |

|   |     | 4.3.6 Formalism without S    | Split Stream                   | 63 |

|   | 1 1 | Dacign                       |                                | 64 |

|   |     | 4.4.1   | Exception Detection                                | 64 |

|---|-----|---------|----------------------------------------------------|----|

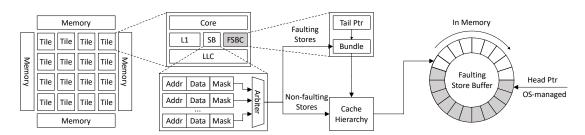

|   |     | 4.4.2   | Faulting Store Buffer and Controller               | 65 |

|   |     | 4.4.3   | Exception Handling                                 | 66 |

|   |     | 4.4.4   | OS Requirements                                    | 68 |

|   | 4.5 | Proto   | type and Evaluation                                | 69 |

|   |     | 4.5.1   | Prototype Overview                                 | 69 |

|   |     | 4.5.2   | Error Injection and Handling                       | 70 |

|   |     | 4.5.3   | Functionality Correctness                          | 70 |

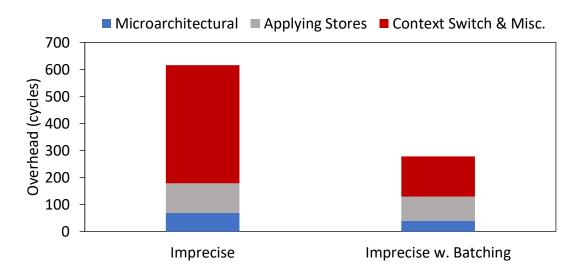

|   |     | 4.5.4   | Performance: Microbenchmark                        | 72 |

|   |     | 4.5.5   | Performance: Real Workloads                        | 73 |

| 5 | Log | ia sida | Address Translation                                | 75 |

| 3 | J   |         |                                                    |    |

|   | 5.1 |         | pport                                              | 75 |

|   |     | 5.1.1   | Virtual Address Space Organization                 | 76 |

|   |     | 5.1.2   | Midgard Address Space Organization                 | 77 |

|   |     | 5.1.3   | Tracking Virtual-to-Midgard Mappings in VMA Tables | 79 |

|   | 5.2 | Micro   | architectural Support                              | 81 |

|   |     | 5.2.1   | Cores and Integrated Accelerators                  | 81 |

|   |     | 5.2.2   | IO Devices and Discrete Accelerators               | 84 |

|   |     | 5.2.3   | Accessing the Cache Hierarchy                      | 85 |

| 6 | Mer | norv-s  | ide Address Translation                            | 89 |

|   | 6.1 | •       | pport                                              | 90 |

|   | 0.1 | 6.1.1   | Physical Address Space Organization                | 90 |

|   |     | 6.1.2   | OS Permissions for Memory Management               | 91 |

|   |     |         |                                                    |    |

|   |     | 6.1.3   | Tracking Midgard-to-Physical Mappings              | 94 |

|   | 6.2 |         | architectural Support                              | 95 |

|   |     | 6.2.1   | Bottom-Up Page-Table Walk                          | 95 |

|   |     | 6.2.2   | Explicit Caching for Page-Table Entries with MLBs  | 98 |

|   |     | 6.2.3   | NUMA Systems and Huge Pages                        | 99 |

## **Contents**

|    |        | 6.2.4   | Memory-side Translation Coherence    | 101 |

|----|--------|---------|--------------------------------------|-----|

|    |        | 6.2.5   | Access Bits                          | 102 |

|    |        | 6.2.6   | Dirty Bits                           | 106 |

|    |        | 6.2.7   | Memory-side Permissions              | 108 |

| 7  | Eva    | luatior | 1                                    | 111 |

|    | 7.1    | Metho   | odology                              | 111 |

|    | 7.2    | Logic   | -side Translation                    | 113 |

|    | 7.3    | Memo    | ory-side Translation                 | 115 |

|    |        | 7.3.1   | Memory-side Translation without MLBs | 115 |

|    |        | 7.3.2   | Memory-side Translation with MLBs    | 119 |

| 8  | Fut    | ure Wo  | rk and Conclusion                    | 123 |

|    | 8.1    | Path t  | o Practical Adoption                 | 123 |

|    | 8.2    | Virtua  | lization                             | 125 |

|    | 8.3    | Memo    | ory Pooling                          | 127 |

|    | 8.4    | Concl   | usion                                | 128 |

|    |        |         |                                      |     |

| Bi | bliog  | graphy  |                                      | 131 |

| Cı | ırricı | ulum V  | litae litae                          | 149 |

# **List of Figures**

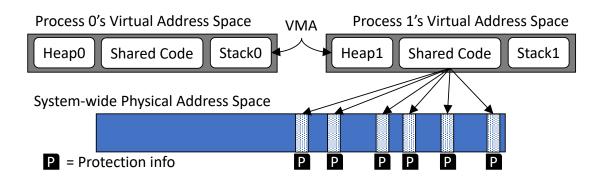

| 2.1 | VMAs in the virtual address space consist of fixed-size pages, which may or may   |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | not be mapped to frames in the physical address space by the OS                   | 17 |

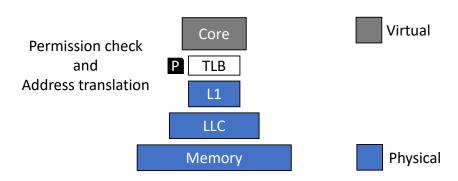

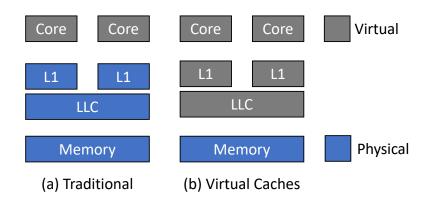

| 2.2 | Existing systems use physical addresses to index the cache and memory hierarchy.  | 22 |

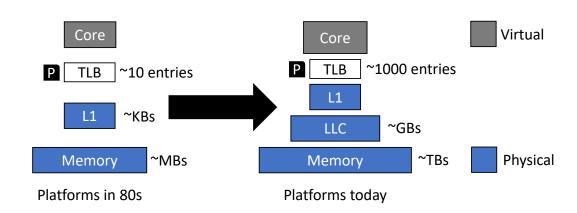

| 2.3 | While 10s of TLB entries were enough to cover KBs and MBs of cache and memory     |    |

|     | in the 80s, TLBs today contain 1000s of entries but cannot provide enough         |    |

|     | coverage for the GBs and TBs of cache and memory available today                  | 23 |

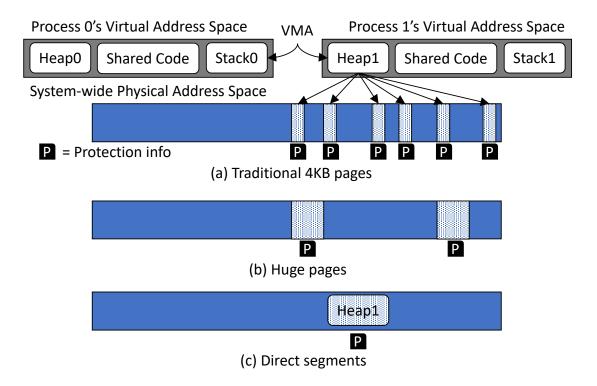

| 2.4 | Proposals relying on contiguity in the physical address space either require      |    |

|     | maintaining (b) huge pages or (c) direct segments / VMAs in the physical address  |    |

|     | space itself                                                                      | 27 |

| 2.5 | Existing systems (a) use physical addresses to index the cache, while virtual     |    |

|     | cache hierarchy proposals (b) use virtual addresses to index the cache hierarchy. | 29 |

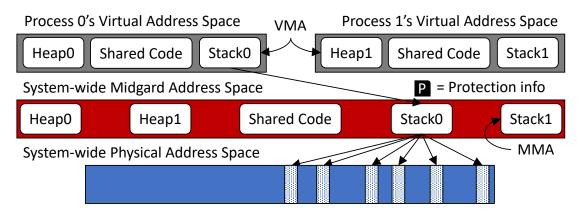

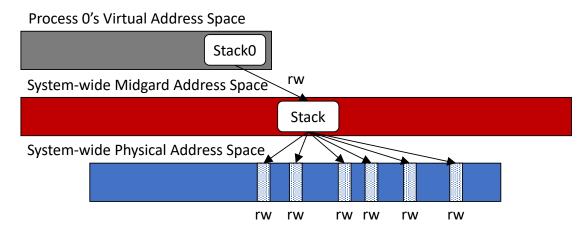

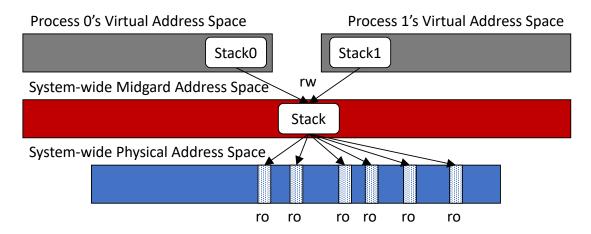

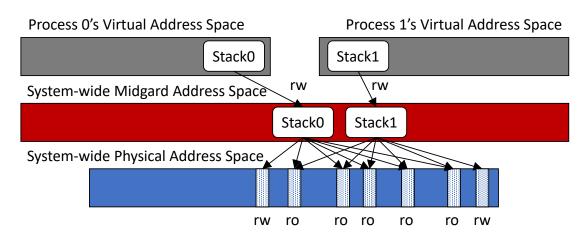

| 3.1 | VMAs in the virtual address space are mapped to Midgard Memory Areas (MMAs)       |    |

|     | in the Midgard address space. The protection information is also specified at     |    |

|     | the VMA granularity. Finally, the MMAs are divided in pages which might be        |    |

|     | mapped to physical frames in the physical address space                           | 36 |

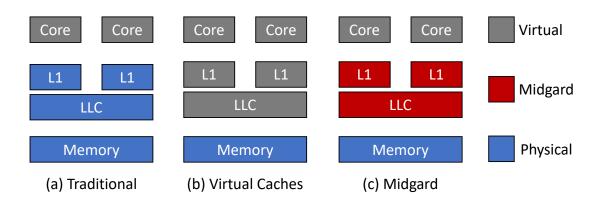

| 3.2 | Existing systems (a) use physical addresses to index the cache, virtual cache     |    |

|     | proposals (b) use virtual addresses to index the cache hierarchy, while Midgard   |    |

|     | (c) uses the Midgard addresses to index the cache hierarchy.                      | 37 |

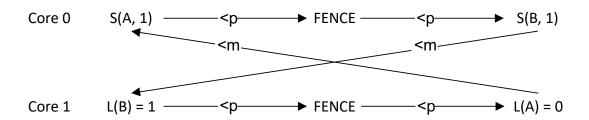

| 4.1 | Violation in the message-passing litmus test                                      | 58 |

| 4.2 | Race condition between the GET operation on Core 1 and the PUT(S(A)) opera-       |    |

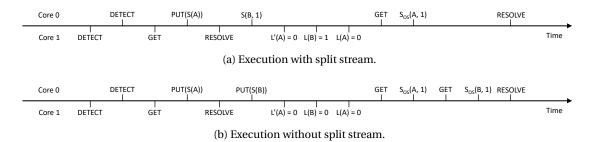

|     | tion on Core 0                                                                    | 60 |

|     |                                                                                   |    |

## **List of Figures**

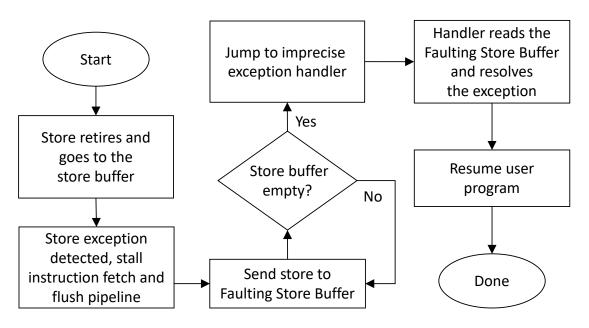

| 4.3 | Imprecise store exception handling flow.                                                               | 64 |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 4.4 | $Modifications \ to \ handle \ imprecise \ exceptions \ in \ a \ generic \ multicore \ system.\ . \ .$ | 65 |

| 4.5 | Overhead breakdown of imprecise exceptions with and without batching. $\ \ldots$                       | 73 |

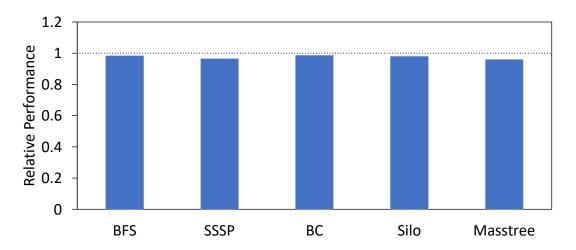

| 4.6 | Relative performance of GAP and Tailbench workloads with imprecise store                               |    |

|     | exceptions                                                                                             | 74 |

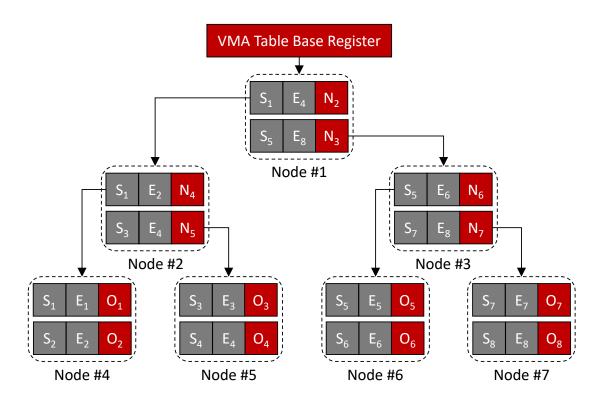

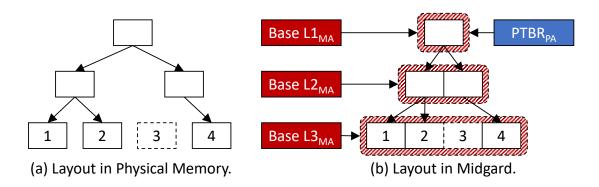

| 5.1 | A diagram of a hypothetical VMA table where each node has two child nodes.                             |    |

| 0.1 | The VMA Table Base Register is a per-core register that contains the base Midgard                      |    |

|     | address of the VMA table of the currently scheduled process. Each dotted box                           |    |

|     | represents a node in the VMA table, while the contained horizontal rectangles                          |    |

|     | ·                                                                                                      |    |

|     | represent two entries per node. The grey boxes signify the stored virtual address,                     |    |

|     | while the red boxes signify the stored Midgard address. Finally, $S_i$ indicates the                   |    |

|     | starting virtual address of the region $i$ , $E_i$ indicates the ending virtual address                |    |

|     | of the region $i$ , and $N_i$ or $O_i$ indicates the Midgard address of the child node                 |    |

|     | $\it i$ , or the offset of the region $\it i$ in the Midgard address space respectively. The           |    |

|     | diagram shows that leaf nodes directly track the regions corresponding to the                          |    |

|     | VMAs, while the non-leaf nodes track the regions corresponding to their child                          |    |

|     | nodes                                                                                                  | 79 |

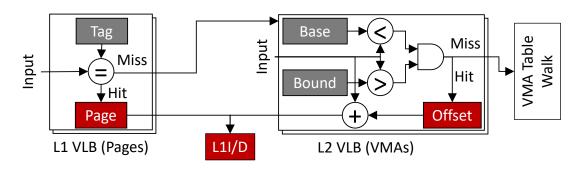

| 5.2 | A two-level VLB design to accommodate the long latency of range lookups. The                           |    |

|     | L1 VLB is similar to an existing page-based TLB where each entry represents a                          |    |

|     | fixed-size page mapping, allowing fast checks with equality comparisons. The                           |    |

|     | L2 VLB contains VMA granularity mappings, and therefore each entry check re-                           |    |

|     | quires two inequality comparisons, thus incurring relatively high latency. There-                      |    |

|     | fore, we suggest a two-level design where the L1 VLB acts as a sectored cache for                      |    |

|     | the L2 VLB while offering fast latency lookups                                                         | 83 |

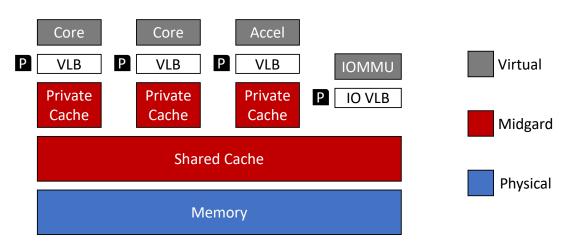

| 5.3 | Logic-side translation is applicable for logic entities such as cores and integrated                   |    |

|     | accelerators, along with any PCIe-attached devices that might communicate                              |    |

|     | with the cache hierarchy and memory. All such entities require using a VLB so                          |    |

|     | that they can translate virtual addresses to Midgard addresses which are required                      |    |

|     | to index the cache hierarchy                                                                           | 84 |

| 6.1 | Copy-on-write example using Midgard and memory-side translation permissions.         | 92  |

|-----|--------------------------------------------------------------------------------------|-----|

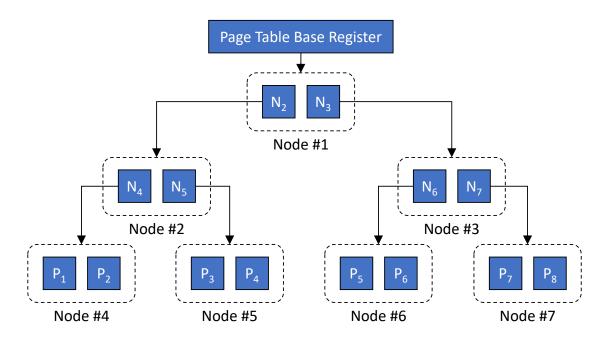

| 6.2 | A diagram of a hypothetical page table where each node has two child nodes.          |     |

|     | The Page Table Base Register is a system-wide register that contains the physical    |     |

|     | address of the root of the system-wide Midgard page table. Each dotted box           |     |

|     | represents a node in the page table, while the contained boxes represent two         |     |

|     | entries per node. Every contained box represents an entry that stores the physical   |     |

|     | address of the child node, or the page in case of the leaf nodes. Finally, $N_i$     |     |

|     | indicates the physical address of the child node $i$ , while the $P_i$ indicates the |     |

|     | physical address of the page $\it i$ tracked by the corresponding entry. The diagram |     |

|     | shows that leaf nodes directly track the pages, while the non-leaf nodes track the   |     |

|     | pages corresponding to their child nodes                                             | 94  |

| 6.3 | A hypothetical layout of a two-level radix page table with a radix degree of two.    |     |

|     | In the diagram, (a) shows the page-table layout in the physical memory, where        |     |

|     | every page-table node can be in different parts of the physical address space,       |     |

|     | while (b) shows the page-table layout in the Midgard address sapce where all         |     |

|     | the page-table nodes are placed contiguously, thus allowing direct offset-based      |     |

|     | lookups of the page-table entries.                                                   | 96  |

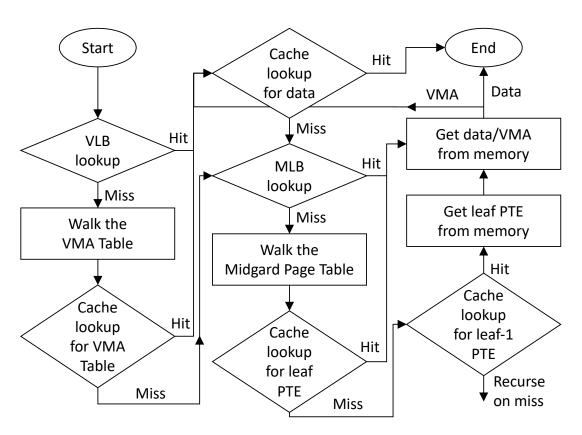

| 6.4 | The flowchart depicts all the steps required for the completion of a memory          |     |

|     | access while considering hits and misses in the various caches provisioned for       |     |

|     | address translation and data                                                         | 98  |

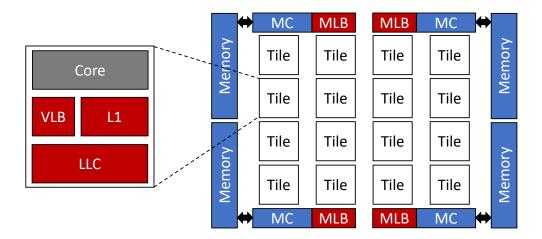

| 6.5 | The diagram shows the application of the Midgard address in a NUMA system.           |     |

|     | Each tile consists of a core, VLB, a private L1 cache, and a shared LLC tile. The    |     |

|     | MLBs are co-located with the memory controllers (MC) which are connected to          |     |

|     | the memory devices                                                                   | 100 |

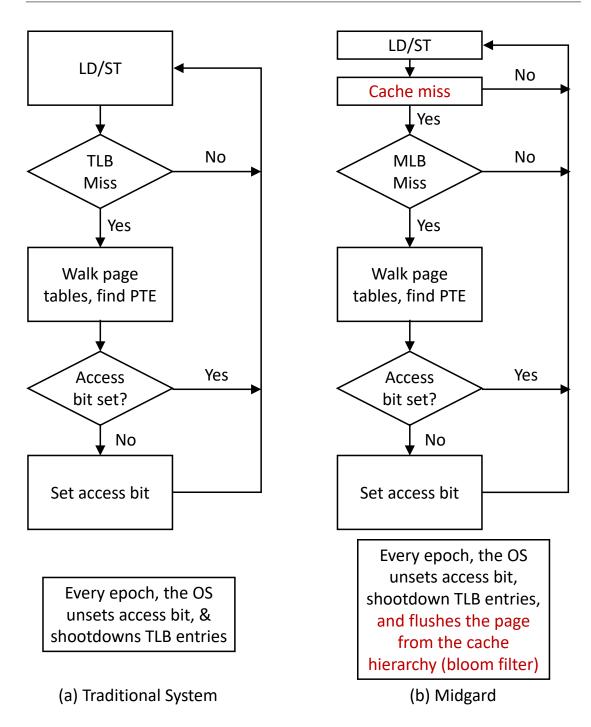

| 6.6 | Flowcharts describing the setting of access bits by an MMU in (a) Traditional        |     |

|     | System, and (b) Midgard.                                                             | 103 |

| 6.7 | Flowcharts describing the setting of bits bits by an MMU in (a) Traditional          |     |

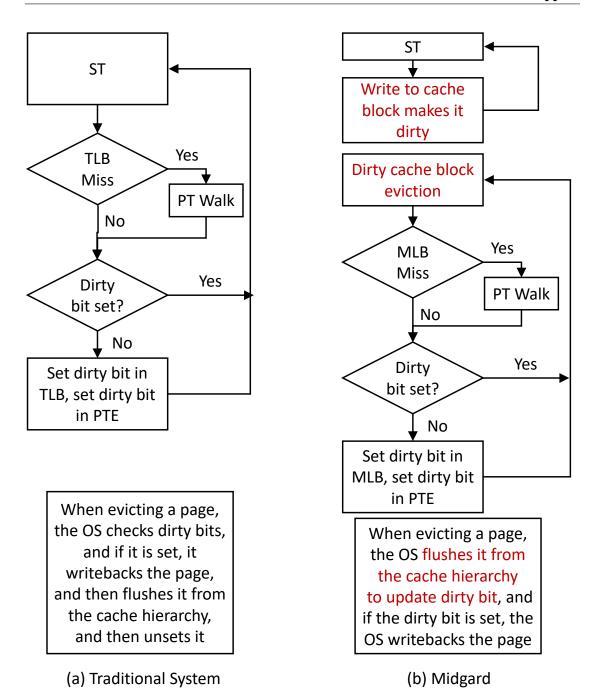

|     | System, and (b) Midgard                                                              | 107 |

## **List of Figures**

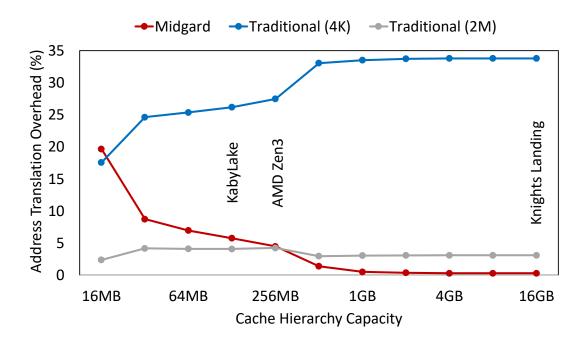

| 7.1 | The graph shows the address translation overhead (%) as part of the overall    |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | Average Memory Access Time (AMAT) for varying cache hierarchy capacity. The    |     |

|     | X-axis shows the overall cache hierarchy capacity along with various products  |     |

|     | such as Intel Kabylake [130], AMD Zen3 [128], and Intel Knights Landing [113]. | 116 |

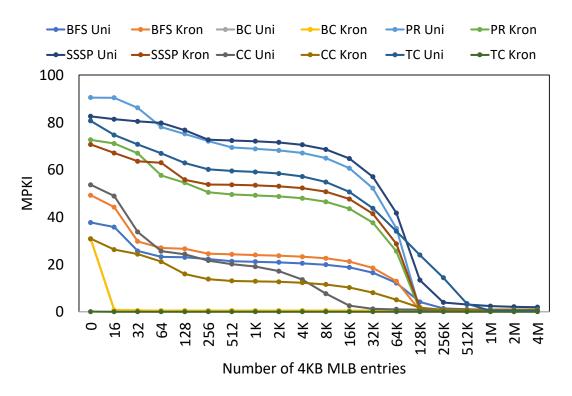

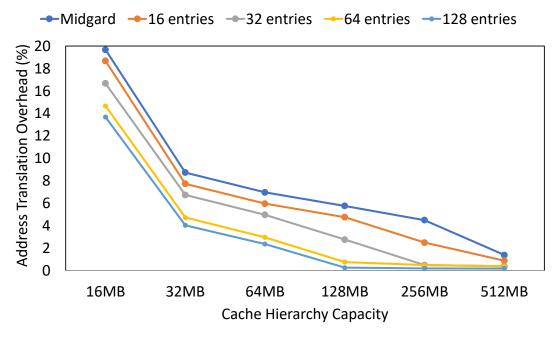

| 7.2 | Graph (a) shows the overall MPKI distribution for varying MLB capacity, while  |     |

|     | graph (b) shows the address translation overhead as part of the Average Memory |     |

|     | Access Time (AMAT) while varying the cache hierarchy capacity                  | 120 |

# **List of Tables**

| 2.1 | Comparison of cache hierarchy and TLB capacity in various generation of com-      |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | mercial CPU products. $^*$ Apple M1 uses 16KB pages that increases its coverage,  |     |

|     | while all other products use 4KB pages                                            | 25  |

| 2.2 | Comparison of core-side and memory-side translation attributes among various      |     |

|     | previous proposals and Midgard. (*) indicates that Single Address Space Oper-     |     |

|     | ating Systems have restricted programmability because they do not provide a       |     |

|     | private virtual address space to each application, therefore, the applications do |     |

|     | not have the flexibility to map data at any required address                      | 31  |

| 4.1 | Classification of x86 exceptions [58]                                             | 46  |

| 4.2 | System parameters for simulation on QFlex [89]                                    | 50  |

| 4.3 | We list the evaluated benchmarks, their instruction mix (%), and the WC speedup   |     |

|     | over SC                                                                           | 50  |

| 4.4 | We list the evaluated benchmarks, their speculation state requirements (in KB)    |     |

|     | to achieve the full WC performance benefits in the baseline SC system, a system   |     |

|     | with 2× memory latency, and a system with 4× store-to-load latency skew           | 51  |

| 4.5 | Memory consistency formalism notations [84]                                       | 56  |

| 4.6 | The contract among the cores, interface, and OS                                   | 60  |

| 4.7 | Ordering rules [5] covered in litmus tests                                        | 71  |

| 7.1 | System parameters for simulation on QFlex [89]                                    | 112 |

| 7.2 | VMA count against dataset size and thread count                                   | 113 |

|     |                                                                                   |     |

## List of Tables

| 7.3 | Analysis of the logic-side translation: for each workload, the table depicts the |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | TLB MPKI in existing systems, the hit rate for different L2 VLB capacities, and  |     |

|     | the overall required VLB capacity.                                               | 114 |

| 7.4 | Analysis of the memory-side translation: for each workload, the table depicts    |     |

|     | the % of memory operations filtered by the cache hierarchy and the average       |     |

|     | page-table walk cycles in memory-side translation                                | 118 |

# 1 Introduction

Our society is undergoing a paradigm-shifting digital transformation where online services have become an integral part of our daily life, e.g., social media, video streaming, online shopping, web search, etc. Data is the ultimate currency which is fueling this transformation, especially in areas such as Artificial Intelligence and Machine Learning, and allows customizing and automating various services and increasing their usefulness for the end users. The requirement of storing and processing large amounts of data has given birth to datacenters, which are large deployments of thousands of servers that work together to host modern online services. Popular online services today have billions of users spread throughout the planet, which in turn generate increasing amounts of data that needs to be processed and stored in datacenters. At the time of writing, Microsoft claims about 100 million while Google claims more than 1 billion daily active users in the search domain [123]. In the social media domain, Facebook is the leader with about 3 billion monthly active users, while Youtube closely follows with about 2.5 billion monthly active users [104]. Similarly, in the online shopping domain, Amazon claims to have over 300 million active user accounts [31].

Such planet-scale online services also have the requirement of answering the requests received from their users under a given threshold of time. Such tight latency constraints are important for providing a high-quality experience to the users, in absence of which the users might turn to a competitor service, thus resulting in customer loss. For example, for every 100ms increase

in latency, Amazon has claimed to have lost 1% in sales. Similarly, Google has claimed that a 500ms latency increase in the search results leads to a 20% traffic loss [81]. Therefore, to meet these latency requirements, the datacenter operators typically host a significant fraction of the overall data in memory devices such as DRAM to benefit from its low latency. The same can be illustrated by modern cloud platforms which provide TBs of DRAM per server [59, 112]. As DRAM is expensive [47], it is important to use the available DRAM capacity efficiently. Virtual Memory has been used in computing systems for decades to provide ease of development to the programmers while allowing the OS to efficiently manage the underlying memory capacity.

## 1.1 Virtual Memory in Datacenters

Virtual Memory (VM) is a classic programming abstraction that provides an abstract representation of memory for easier programming without exposing the underlying physical constraints of memory capacity and technology, and simplifies the programming model by obviating the need for programmer-orchestrated data movement among memory devices and persistent storage [19], offers "a pointer is a pointer everywhere" semantics across multiple CPU cores [95] and accelerators (e.g., GPUs [94], FPGAs [71], NICs [86], and ASICs [69, 96]). VM also forms the foundation of access control and memory protection mechanisms ubiquitous to modern computer systems security and are the building blocks of other advanced mechanisms like trusted execution environments.

With the rise of datacenter computing, the services provided by large-scale datacenters are becoming increasingly popular and are serving up to billions of users across the planet. With the increasing number of users, the memory requirements of such datacenter services are increasing as well. Therefore, systems designers are building cache and memory hierarchies with increasing capacity to capture the ever-increasing working sets of datacenter workloads and improve the performance of datacenter services [15, 63, 64, 95], as evidenced by recent work on die-stacking, chiplets, DRAM caches [60, 61, 125], and non-volatile byte-addressable memories [28, 50]. However, these high-capacity cache and memory hierarchies also shift the performance bottleneck to virtual-to-physical address translation, which can pose an

overhead of about 10-30% on the overall system performance [15,64,95,96]. Therefore, VM today is plagued with crippling performance and complexity challenges that undermine its programmability benefits.

Hosting the data from online services in memory comes with five key challenges for VM in the post-Moore era.

- 1. Increasing memory capacity: as the online services become popular and the number of users increases, the online services require increasing memory capacity in the datacenter servers hosting the service. Increasing the overall memory capacity in a server increases both the material and energy cost associated with the server, and also puts additional performance pressure on the hardware and software subsystems (especially VM) as they need to manage a larger memory capacity. Finally, with the end of Moore's law, increasing the memory capacity using DRAM directly is prohibitive and requires innovative solutions.

- 2. Heterogeneous memory hierarchies: with the increasing difficulty in increasing the memory capacity using DRAM, datacenter operators have started exploring Heterogeneous memory technologies to supplement the memory capacity. For example, the introduction of commercial Storage Class Memory [45,56] has made it possible to increase the memory capacity for a fraction of the overall memory cost. Similarly, the introduction of memory pooling technologies such as RDMA and CXL [33, 86, 99] allow using the memory of neighboring servers as an extension of the local memory. However, such heterogeneity in the memory hierarchy introduces challenges regarding data movement and coherence among the memory devices and servers, as now multiple servers are required to have a coherent view of shared memory using a collection of memory devices. In particular, VM requires introducing new synchronization primitives that can ensure coherence among the various copies of VM-associated metadata, which might be present in multiple places in the same server, or even across servers.

- 3. Virtualization in the cloud: with the increasing demand for resources by third-party

online service providers, datacenter operators have resorted to hosting multiple users/services per server (multi-tenancy) in order to increase the overall utilization of the datacenter servers and reduce the total cost per user. However, co-locating multiple users on the same physical machine results in both performance problems and security concerns among the users. Therefore, datacenter operators have tried to build primitives to provide the illusion of isolation to users. VM is the basis of modern virtualization techniques as it provides isolation among various processes running in the same physical server, and has been extended to provide isolation among virtual machines co-located on the same physical server as well. However, such VM-based techniques have their own performance overheads [15, 39, 64] which scale poorly with the overall users and resources (such as memory capacity) in the system.

- 4. Emerging workloads: with the growth in the number of users of online services, and the increasing cost of datacenter servers, online service providers along with datacenter operators have started exploring new ways of deploying online services in order to decrease the cost of hosting the online services and increase the ease of deployment. This search has led to paradigms such as microservices [137] and serverless computing [124]. However, these paradigms have their own performance challenges as they allow co-locating multiple microservices together, or running short-lived serverless jobs which leads to contention because of tracking increased address translation entries in the current VM implementations, compared to traditional long-running monolithic workloads.

- 5. *Confidential computing*: the increase in the number of users of online services and the services/users co-located on a physical datacenter server has accelerated the development of confidential computing platforms such as SGX [57] which have already become key in hosting various sensitive services in the domains of healthcare, finance, streaming services, etc. All modern confidential computing techniques are built on top of VM, as VM provides the basic memory isolation primitives among processes running in the same system. However, as the data processed by such platforms increases, it places

a significant performance burden due to increased memory capacity when providing such confidential services using VM.

As the above challenges explicitly rely on VM for functionality, we need to ensure that VM performance can scale with the increasing demands in modern datacenters. In this thesis, we focus on the increased memory capacity requirement which is the underlying issue in all the above challenges. To improve VM performance, computer and system architects continuously design complex address translation hardware and Operating System (OS) support that requires significant silicon resources and sophisticated implementation. Such complex support poses verification burdens despite which design bugs are still common [78]. Individual CPU cores (and recent accelerators) integrate large two-level TLB hierarchies with thousands of entries, separate TLBs at the first level for multiple page sizes, and skew/hash-rehash TLBs at the second level to cache multiple page sizes concurrently [30, 88, 108]. Such large TLB hierarchies and multiple page sizes necessitate a staggering amount of OS logic to defragment memory and create huge pages [92, 93, 134, 135] and heuristics to determine when to create, break, and migrate them [73, 85, 117, 118]. As huge pages can lead to performance pathologies and hence are not a panacea, processor vendors also integrate specialized MMU cache per core to accelerate the page-table walk [13, 18]. Specialized per-core TLBs and MMU caches, in turn, necessitate sophisticated coherence protocols in the OS (i.e., shootdowns) that are slow and buggy, especially with the adoption of asynchronous approaches to hide shootdown overheads at a higher core and socket counts in modern servers [10, 72, 79].

## 1.2 Thesis Goals

The primary goal of this thesis is to remove the performance bottleneck caused by address translation in case of large memory capacity in datacenter servers. We aim to improve the performance VM subsystem while ensuring POSIX compatibility, thus making sure that the developers do not need to rewrite their application code. Moreover, as memory capacity is both limited and expensive, we do not want to rely exclusively on techniques such as huge pages which might lead to internal memory fragmentation compared to a fine-grained

#### **Chapter 1. Introduction**

management of memory using fixed-size pages. If we can improve the performance of address translation for large memory capacities, then it will in turn benefit the overall VM performance for all the five key challenges explained before.

We intend to introduce a holistic redesign of the VM subsystem while prioritizing software compatibility and efficient memory capacity utilization. We start by focusing on the management of both the virtual and physical address spaces as is done in the traditional systems. We observe that the virtual address space inherently contains data in the form of flexible and logical data sections called Virtual Memory Areas (VMAs), which are a modern incarnation of age-old segments [132]. In contrast, the physical address space is managed in terms of fixed-size pages which allow utilizing the overall memory capacity efficiently. The mapping of each VMA into multiple fixed-size pages results in the creation of a large amount of address translation metadata which has to be consulted every time the virtual-to-physical address translation is required, thus creating a performance bottleneck. To avoid this bottleneck, we propose dividing the traditional virtual-to-physical address translation logic into a fast and slow component. The fast component represents only the memory management done in the logical address spaces (such as virtual address space) and can be used to perform common case permission checks and cache hierarchy accesses, while the slow component represents the capacity management performed in the physical address space representing the backing memory devices. Such a division in the address translation can be caused by introducing an intermediate address space in the system.

#### **Thesis Statement:**

A VMA-based intermediate address space can be used for common case access control and cache hierarchy accesses while requiring the page-based physical address space for only capacity management.

### 1.3 Thesis Contributions

In this thesis, we aim to circumvent the performance problems of the existing VM implementations by using the following key insights:

- Redesign microarchitecture for address translation using existing programming abstractions such as VMAs that already exist in the traditional OS and application toolchains in order to maintain POSIX compliance, thus ensuring no effort for the application developers and quick adoption from the OS developers.

- 2. Decouple address translation into two steps where the first step is invoked for all memory accesses, and therefore mandates (lean) specialized microarchitecture for high performance, while the second step is invoked infrequently and can rely on the existing cache hierarchy resources instead of requiring specialized structures.

- 3. Instead of completely delegating complicated functionalities to the microarchitecture (in particular exception handling), we can offload some of the functionality to the OS using an OS + microarchitecture co-design. We can also provide formal specifications to the OS developers to help ensure correctness in order to prevent hard-to-find bugs such as the ones that have plagued TLB shootdown mechanisms [9] for years.

We propose the Midgard — the original name for the middle realm between Asgard and Helheim in Norse mythology — as an intermediate address space between the virtual and physical address spaces, which relies on fusing the existing OS abstraction of VMAs into hardware for the first time. As applications view memory as a collection of a few flexibly-sized VMAs with specific permissions, it is possible to create a unique Midgard address space where VMAs of various processes can be mapped after deduplication. The unique Midgard address space serves as a namespace for all data in the coherence domain and cache hierarchies, and thus all cache hierarchy accesses must require a translation from the program's virtual address to the unique Midgard address. Translation from Midgard to physical addresses is only required when the required cache block is not found in the cache hierarchy and has to be

fetched from physical memory.

The Midgard idea is inspired in part by prior work on virtual cache hierarchies [23, 24, 43], which reduce address translation pressure by deferring the need for physical addresses until physical memory access. Unfortunately, they also create implementation complexity by exposing synonyms/homonyms or compromising programmability due to reliance on inflexible fixed-size segments. While approaches like single address space OSes [70] tackle some of these problems (i.e., removal of synonyms/homonyms), they require the recompilation of binaries to map all data shared among processes into a unified virtual address space. Instead, to achieve our goal, we provide a programmer-transparent but OS-managed intermediate address space, where the OS ensures the resolution of any synonym or homonym using the existing abstraction of VMAs. Thus, the intermediate address space can be used to index the cache hierarchy without the shortcomings of homonyms/synonyms or segments [132], and also enables a fast translation from virtual addresses to the intermediate addresses using VMAs and requires a slow translation from intermediate addresses to physical addresses using pages only when accessing the physical memory.

With the introduction of Midgard as an intermediate address space, the translation from virtual to Midgard addresses can be accomplished using translation caching structures much smaller than TLBs because there are far fewer frequently-used VMAs (~10) than pages in real-world workloads. In contrast, the translation from Midgard to physical addresses still remains slow, but is required infrequently and allows utilizing the trends of increasing cache hierarchy capacity. Larger cache hierarchies traditionally amplify VM overheads, but instead, they can mitigate VM overheads by absorbing most of the page-based translation activity and obviate the requirement of specialized translation hardware. While large 1000-entry (~16KB SRAM) per-core TLBs fail to meet the performance requirements for address translation in traditional systems and require impractically larger structures, Midgard allows the page-based translation to be performed using zero or very few TLB entries, thus reclaiming the 100KB-to-MB of SRAM dedicated towards TLBs in modern manycore systems [128] which anyways fails to meet the performance requirements of address translation today. Therefore, instead of

amplifying the address translation overheads, larger cache hierarchies can now be leveraged to *reduce* them. Our trace-based evaluation shows that for large-capacity cache hierarchies, Midgard's address translation overhead drops to near zero as the working sets fit in the cache hierarchy, while traditional TLBs suffer even higher degrees of address translation overhead. Overall, the introduction of the Midgard address space can provide the benefits of virtual cache hierarchies without homonym/synonym problems.

The introduction of the Midgard address space delays the page-based address translation near memory, which can give rise to complicated exception handling scenarios in infrequent cases. In particular, the traditional microarchitecture design relies on detecting any VMrelated exceptions in the pipeline itself in a precise manner as the address translation and permission check is tightly integrated with the pipeline. The same assumption allows the microarchitecture implementation to retire stores before completion which leads to a significant performance boost in the pipeline and forms the basis for modern relaxed memory consistency models. However, when address translation is performed away from the cores, then the above assumption breaks and the same optimizations cannot be naively applied. While there are well-understood post-retirement speculation techniques that can handle such exceptions without losing performance, they also impose an overhead of 10-20KB SRAM per core to maintain the state for optimistically retired stores. Unfortunately, such silicon requirements will undermine the benefits received from removing the traditional TLBs. Therefore, to maintain the original system performance using early store retirement without spending significant silicon resources, we propose handling the exceptions *imprecisely* while offloading part of the microarchitectural functionality to the OS which can be carried out easily in the infrequent cases when exceptions are generated by the page-based translation. As such a OS + microarchitecture co-design will interact with complicated microarchitectural concepts such as memory consistency models, ensuring correctness is of primary importance here to prevent hard-to-find bugs such as the ones that have plagued TLB shootdown mechanisms [9] for years. Therefore, to help the OS developers ensure correct behavior, we develop a complete formalism and proofs to show that the design for imprecise exceptions is compatible with popular memory consistency models such as Processor Consistency (PC) and Weak Consis-

#### **Chapter 1. Introduction**

tency (WC). We then describe the detailed hardware-software co-design required to bring the imprecise exception idea to fruition. However, the formalism allows other system designers to come up with their own design while ensuring correctness.

Overall, this thesis explains the various modifications required to support Midgard in the OS, requirements for the virtual-to-Midgard address (logic-side) translation, and requirements for the Midgard-to-physical address (memory-side) translation, along with the OS + microarchitecture co-design for imprecise exception handling. The OS requires tracking the VMAs for each process, mapping all the unique VMAs as MMAs in the Midgard address space, maintaining architectural VMA tables that track VMA-to-MMA mappings along with the application permissions, and maintaining system-wide page tables that track the page-granularity mappings from the Midgard to physical address space along with the OS-specified permissions. The logic-side translation requires hardware caching support to store the mappings for recently-used VMAs, fast access time for both the address translation mappings and the cache hierarchy, and supporting precise exceptions in case of faults in the logic-side and memory-side translations. The memory-side translation instead relies on the cache filtering for infrequent invocations and requires techniques for performing the memory-side page-table walk with or without specialized address translation caches, along with coherence among the memory-side page-table entries.

We evaluate Midgard by quantifying its performance characteristics over cache hierarchies ranging in size from tens of MBs to tens of GBs and show that even modest MB-scale SRAM cache hierarchies filter the majority of memory accesses, leaving only a small fraction of memory references for translation from Midgard to physical addresses. We characterize VMA counts as a function of dataset size and thread count and confirm that low VMA counts mean a seamless translation from virtual to Midgard addresses. Using average memory access time (AMAT) analysis, we show that LLC capacities in the tens of MBs comfortably outperform traditional address translation and that at hundreds of MBs, they even outperform huge pages. In our evaluation, Midgard reaches within 5% of address translation overhead of traditional 4KB-page TLB hierarchies for a 16MB LLC and breaks even with 2MB-page TLB

hierarchies for a 256MB LLC. Unlike TLB hierarchies exhibiting higher overhead with larger cache hierarchies, Midgard's overhead drops to near zero as secondary and tertiary data working sets fit in the cache hierarchies. Finally, we show that even for pessimistic scenarios with small LLCs, Midgard can be augmented with modest hardware assistance to achieve competitive performance with traditional address translation. To showcase the imprecise exception handling idea, we further develop a full-system RISC-V prototype of an out-of-order core that supports generic imprecise exceptions and runs Linux. We run litmus tests for memory consistency models to show that our implementation is compatible with the RISC-V memory consistency model. Then we provide an end-to-end evaluation of various benchmarks to show that the imprecise exceptions can work successfully, and are able to maintain similar overall performance as in the traditional system.

## 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 explains the importance of the VM abstraction, the traditional implementation of the VM subsystem, scaling problems with large memory capacities, and various classes of previous proposals that have aimed to improve VM performance. Chapter 3 to chapter 7 present the contributions of this thesis.

- Chapter 3 provides a brief overview of Midgard along with the high-level design and the interface required to support Midgard.

- Chapter 4 explains the exception handling logic required in Midgard.

- Chapter 5 explains the VMA-granularity logic-side address translation in Midgard that provides application-level access control and access to the cache hierarchy.

- Chapter 6 explains the page-granularity memory-side address translation in Midgard that provides capacity management in the physical address space and provides access to the memory device.

- Chapter 7 describes our evaluation that quantifies the benefits of Midgard compared to

#### **Chapter 1. Introduction**

traditional systems.

Finally, chapter 8 describes future research directions with Midgard and concludes the thesis.

### 1.4.1 Bibliographic Notes

This thesis was conducted under the supervision of my advisors, Babak Falsafi and Abhishek Bhattacharjee. Portions of it are a product of collaboration with Yuanlong Li, Qingxuan Kang, Atri Bhattacharyya, Yunho Oh, and Mathias Payer. The design, implementation, and evaluation of Midgard is based on a conference paper published in *Proceedings of the 48th International Symposium on Computer Architecture (ISCA)* in 2021 [44]. The chapter 4 on the exception handling in Midgard is based on a conference paper published in *Proceedings of the 50th International Symposium on Computer Architecture (ISCA)* in 2023 [46].

## 2 Virtual Memory

As computing has evolved over the last six decades, Virtual Memory (VM) [19] has played an essential role as a programming abstraction for computing systems. VM allows programmers to write programs without being concerned about the underlying memory subsystem, forms the basis of modern security and virtualization technologies, and is responsible for the efficient utilization of memory capacity present in a system. VM has been so successful as a programming abstraction that today it is ubiquitous in computing systems of all scales such as datacenter servers, desktops, mobile devices, and even various forms of embedded computing. With the rise of datacenter computing [14] and continued scaling of memory capacity [59, 112] coupled with the end of Moore's law [32, 122], the existing implementation of VM is expected to result in a high performance overhead [15, 39, 64] which will dwarf the programming benefits it provides, therefore requiring a careful redesign to reduce the implementation overhead. This chapter explains the benefits of VM, its current design and implementation, the overheads associated with scaling VM implementations along with the growing memory capacity, and various classes of proposals that have tried to mitigate the overheads associated with VM.

## 2.1 A Fundamental Programming Abstraction

VM is the de-facto programming abstraction in almost all computing systems today because of the benefits it provides. We now explain the various features of VM that make it so successful as a programming abstraction.

#### 2.1.1 Programmability and Portability

VM allows the programmers to write programs while ignoring the specifics of the underlying memory subsystem. VM provides the abstraction of a *virtual address space* to the programmers which is logical and not tied to the physical memory capacity of the system. The virtual address space is designed to have a large capacity (e.g., modern CPUs support 57-bit address spaces [55] that can store up to 2<sup>57</sup> bytes of data) which is considerably more than the typical memory usage of programs today. Therefore, the programmer (in co-operation with the linker and compiler) is able to use the whole virtual address space freely without accounting for the capacity restrictions of the underlying physical address space dictated by the amount of physical memory in the system. The availability of more than explicitly-required memory capacity allows the programmer to easily construct a variety of logical data sections (e.g., heap, stack, code, files, libraries) which can be placed in different parts of the virtual address space. Such a placement also allows special programming properties such as the stack starts at a high address and grows down while the heap starts at a lower address and grows up, while being practically ensured to never collide with each other. Finally, as the programs are written using the virtual addresses, they can be easily ported to other machines without any memory-addressing-related modifications because every machine can provide the abstraction of a virtual address space irrespective of the varying physical capacity of memory.

#### 2.1.2 Isolation and Protection

VM forms the basis of modern security mechanisms in computing systems as it provides memory security inside and among various processes running on the same system. In modern systems, each process has a private virtual address space and can only generate addresses belonging to its own virtual address space. Therefore, while multiple processes might be concurrently running in a system, no process can generate virtual addresses to access data belonging to another process in the system unless the data is explicitly shared using files or

shared memory regions, providing every process an isolated environment as if it is the only process running in the system. However, the bugs present in the code running in a process can still cause it to malfunction and destroy critical data. Morever, while memory isolation directly provides security and ease of programming, there are various other interfaces that allow the processes to interact with other processes in the system, or even those running on other machines. Such interactions can turn malicious if the external processes try to abuse the provided interface to exploit bugs and security vulnerabilities present inside a particular process. To counter such security issues, VM further provides protection mechanisms that can limit the type of memory operations that can be performed on a particular virtual address. VM does so by enforcing permission checks with each virtual address, where the permissions can be provided by the programmer in cooperation with the toolchain. For example, to protect against attacks that attempt to inject malicious code in the process, the code section of the process is given only executable and read permissions, thus ensuring that the code can never be re-written while the process is running. Similarly, the data-containing sections such as heap and stack are typically not given the executable permissions so that malicious code disguised as data cannot be executed from such sections. Overall, VM provides security mechanisms both inside and among virtual address spaces.

The isolation and protection mechanisms provided by VM also form the basis of virtualization [22], which is a foundational technology required for cloud computing today. Using further extensions in OS and hardware, VM provides the foundation of memory virtualization where the guest virtual machine is given the abstraction of a physical memory device, while the underlying physical memory is managed only by the host OS. The guest OS runs its own VM implementation inside the guest virtual machine, maintains its own guest virtual address spaces and maps them to a guest physical address space which is provided by the host OS. The host OS treats the guest physical address space similar to its other virtual address spaces and maps data from it to the actual physical address space. Therefore, while the guest OS sees an abstract physical address space, only the host OS can control and manipulate the actual physical address space that represents the physical memory present in the machine. In this way, VM ensures complete memory isolation even when running multiple virtual machines

on the same physical machine while sharing the underlying physical memory.

#### 2.1.3 Memory Management and Over-Subscription