# Integrated Electronics for Deep Implants to Remotely Monitor Hemodynamics

Présentée le 26 juin 2023

Faculté des sciences et techniques de l'ingénieur Groupe SCI STI MM Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Mustafa BESIRLI

Acceptée sur proposition du jury

Dr J.-M. Sallese, président du jury Dr M. Mattavelli, Prof. C. Dehollain, directeurs de thèse

Prof. P. Malcovati, rapporteur

Prof. Y. Leblebici, rapporteur

Prof. A. P. Burg, rapporteur

To my parents, my brother, my sister, and To my wife, Sevdenur . . .

## Acknowledgements

First of all, I would like to express my sincere gratitude to my thesis advisors, Prof. Catherine Dehollain and Dr. Marco Mattavelli, for giving me the opportunity to pursue this very interesting PhD research at EPFL. Their guidance, support, and patience throughout this research project have been invaluable, and I am truly grateful for their kind and encouraging supervision.

I would like to extend my thanks to the distinguished members of my thesis committee, Dr. Jean-Michel Sallese, Prof. Piero Malcovati, Prof. Yusuf Leblebici, and Prof. Andreas Burg, for their expert evaluation and valuable feedback on my thesis. I am also grateful to Prof. Franco Maloberti for his insightful comments and valuable feedback on my publications.

I am deeply thankful to my colleagues in the CardioCMOS project, whose contributions were vital to the completion of this thesis. I owe a special debt of gratitude to Prof. Diego Barrettino, who served as a *de facto* co-advisor and provided me with continuous guidance and unwavering support throughout the project. Working with Dr. Kerim Türe in the same office for the first years of my PhD was a great pleasure, and I deeply appreciate his support and contribution to my thesis, which significantly improved its quality, as well as his close friendship. Additionally, I would like to thank our medical collaborator at HUG, Prof. Maurice Beghetti, for his expert guidance and extensive medical knowledge, which greatly enhanced the impact of this work. I acknowledge the financial support of the Swiss National Science Foundation (SNSF) through Sinergia program under grant CRSII5 180272/1.

I would like to thank all my friends and colleagues at EPFL for the good times we shared over the years. Special thanks to my group mates Aurélien Bloch and Ünsal Öztürk for their warm friendship and amazing coffee breaks. I would also like to express my appreciation to Daniela Vallat and Isabelle Buzzi for their support in administrative work, and to Dr. Alain Vachoux, Cédric Meinen, Adrien Toros, and Nicolas Fumeaux for their technical support. I would like to thank Dr. Adil Koukab, Dr. Francesco Mazzilli, Fırat Çelik, and Ayça Akkaya for the valuable technical discussions. I am thankful to all my current and former colleagues and friends at EPFL: Mohammad Karimi, Bakul Vinchhi, Rosane Moura, Çağrı Erbağcı, Marwan Chehade, Yuteng Wang, Simone Casale Brunet, Can Baltacı, Duygu Kostak, Arda Uran, Bilal Demir, Cem Tekin, and Utku Ertürk.

#### Acknowledgements

I have had the chance to meet some great people during my PhD journey, and I am extremely grateful for the enjoyable and memorable moments we shared in Switzerland. I would like to express my heartfelt gratitude to Selman & Şerife Ergünay, Mustafa & Züleyha Kılıç, Nuh & Kübra Bahar, Mehmet & Esma Ertaş, Kerim & Edibe Türe, Fatih & Filiz Karakoyun, and Murat & Hatice Ünlü for their warm friendship in Lausanne.

Although I have been physically far away for a considerably long time, I have always felt the unwavering support and warm friendship of my friends from Istanbul. I am deeply grateful to Selami Çiçek, Ahmet Aksoy, Murat Birinci, Alper Sezer, Anıl Alkal, and Mehmet Fatih Haberdar for their great friendship and for always being there for me.

Most importantly, I cannot thank enough my mother Mine and my father Aydın for their unwavering support, patience, and endless love throughout my life. This journey would not have been possible without them. I am greatly thankful to my brother Mehmet Umut and to my sister Işıl for bringing joy and love to my life. I am hugely indepted to my grandmother Feride, my grandfather Mehmet (may his soul rest in peace), and my aunts Minire, Şule, and Emine for their endless support and love throughout my life. I am also thankful to my family-in-law, Hatice, Selçuk, and Aydın, for their support.

And finally, I appreciate every moment I spent with my beloved wife, Sevdenur, for her unconditional encouragement, endless support, and boundless love. Without her, none of this would be possible.

Lausanne, March 31, 2023

Mustafa Beşirli

### **Abstract**

The integration of technology in the medical field has greatly improved accuracy in diagnoses, thus leading to more effective treatments. Wearable and implantable medical devices offer great potential for remote patient monitoring, particularly for heart failure (HF) patients. Continuous and accurate monitoring of the patient's hemodynamics, especially pulmonary artery pressure (PAP) and cardiac output (CO), is essential for adapting treatments and reducing repeated hospital admissions. This thesis presents an implantable wireless system for remote hemodynamic monitoring, which enables direct, continuous (24/7), and simultaneous measurement of the PAP and cross-sectional area (CSA) of the artery, that is necessary to accurately calculate the CO.

The implantable system is designed to minimize clinical issues by reducing its dimensions and power consumption. Techniques for designing low-power, miniature circuits and systems to measure pressure and artery diameter are presented. An energy-efficient bridge-to-digital converter (BDC) for pressure measurements is introduced and exploits duty cycling to reduce the power consumption of the piezoresistive sensor and the instrumentation amplifier (IA) in the sensor readout, while inherently cancelling the IA's offset and 1/f noise thanks to a novel spinning method. Thus, it avoids the need for complex IAs that foresee offset-reduction techniques or calibration. This novel architecture enables high resolution and ultra-low energy consumption in bridge sensor systems, representing state-of-the-art performance in energy efficiency.

An innovative method is developed to directly measure the diameter and CSA of an artery. The method exploits the inductive characteristic of an implant's anchoring loops and provides a direct and accurate measurement of the artery's CSA. The anchoring loop is used for both the fixation of the implantable system in the artery and the measurement of the artery's CSA. The deformation of the loop changes its inductance, which is correlated to the artery's diameter and CSA. An oscillator-based inductive readout circuit that measures the inductance change of a nitinol anchoring loop is presented. It enables remote monitoring of the artery's CSA and improves by a factor of four the lateral resolution of echocardiography.

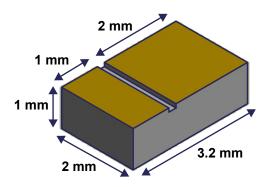

Ultrasound (US) is the most efficient method for powering miniature implants at great depths. To meet the requirements for a small form factor, a single implantable piezoelectric transducer is used for simultaneous power and uplink data transfer. The US powering through an 8.5 cm

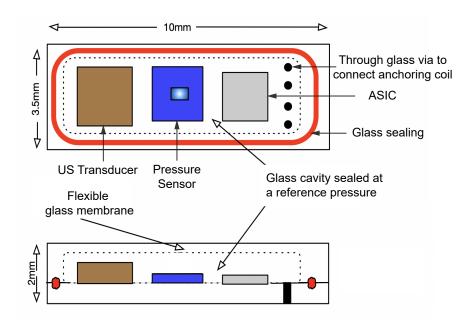

tissue phantom provides sufficient link efficiency, enabling wireless powering with an acoustic intensity much lower than the Food and Drug Administration (FDA) safety limit. The parallel uplink data transfer, using amplitude-shift keying (ASK) modulation, achieves a high modulation index, thus providing a robust communication link. Prototype integrated circuits (ICs) are designed and implemented in a standard 180-nm CMOS technology. A biocompatible, hermetic glass packaging approach is developed to enable long-lasting and low-cost implants. The size of the glass-packaged implantable system is 3.2 mm  $\times$  2 mm  $\times$  10 mm. The challenges of powering the glass-packaged implant are discussed, and the system's performance is verified in an *in vitro* experimental setup that emulates the arterial blood flow.

**Keywords:** Implantable medical device (IMD), remote patient monitoring (RPM), hemodynamic monitoring of heart failure (HF) patients, pressure sensor, energy-efficient, CMOS, instrumentation amplifier (IA), analog-to-digital converter (ADC), bridge-to-digital converter (BDC), wireless ultrasonic power and data transfer.

### Résumé

L'intégration de la technologie dans le domaine médical a considérablement amélioré la précision des diagnostics et a permis des traitements plus efficaces. Les dispositifs médicaux portables et implantables offrent un grand potentiel pour la surveillance à distance des patients, en particulier pour les patients souffrant d'insuffisance cardiaque (IC). La surveillance continue et précise de l'hémodynamique du patient, en particulier de la pression artérielle pulmonaire (PAP) et du débit cardiaque (DC), est essentielle pour adapter les traitements et réduire les admissions répétées à l'hôpital. Cette thèse présente un système sans fil implantable pour la surveillance hémodynamique à distance, permettant une mesure directe, continue (24/7) et simultanée de la PAP et de la surface de section transversale (SST) des artères, ce qui est nécessaire afin de calculer précisément le DC.

Le système implantable est conçu pour minimiser les problèmes cliniques en réduisant ses dimensions et sa consommation d'énergie. Des techniques pour concevoir des circuits et des systèmes miniaturisés à faible consommation d'énergie servant à mesurer la pression et le diamètre des artères sont présentées. Un convertisseur pont numérique (CPN) à faible consommation d'énergie pour les mesures de pression est présenté. Le CPN met à profit le cycle de fonctionnement pour réduire la consommation d'énergie du capteur piézorésistif et de l'amplificateur d'instrumentation (AI) dans la lecture du capteur, tout en annulant implicitement le décalage et le bruit 1/f de l'AI grâce à une méthode innovante de rotation. Cela évite les AIs complexes qui prévoient des techniques de réduction de décalage ou nécessitent un calibrage. Cette architecture innovante permet une résolution élevée et une très faible consommation d'énergie dans les systèmes de capteur en pont, représentant une performance de pointe en terme d'efficacité énergétique.

Une méthode innovante est développée pour mesurer directement le diamètre et la SST d'une artère. La méthode exploite la caractéristique inductive des boucles d'ancrage de l'implant et fournit une mesure plus précise et directe de la SST de l'artère. La boucle d'ancrage est utilisée à la fois pour le placement du système implantable dans l'artère et pour la mesure de la SST de l'artère. La déformation de la boucle change son inductance, qui est corrélée au diamètre et à la SST de l'artère. Un circuit de lecture inductif à base d'oscillateur qui mesure le changement d'inductance d'une boucle d'ancrage en nitinol est présenté. Il permet la surveillance à distance de la SST de l'artère et améliore d'un facteur quatre la résolution latérale de l'échocardiographie.

#### Résumé

L'ultrason est la méthode la plus efficace pour alimenter les implants miniaturisés à grande profondeur. Pour répondre aux exigences d'un petit facteur de forme, un seul transducteur piézoélectrique implantable est utilisé pour le transfert simultané de puissance et de données de liaison ascendante. L'alimentation en ultrasons à travers un fantôme de tissu de 8,5 cm offre une efficacité de liaison suffisante, permettant une alimentation sans fil avec une intensité acoustique beaucoup plus faible que la limite de sécurité de la FDA (Food and Drug Administration). Le transfert de données de liaison ascendante parallèle utilisant la modulation d'amplitude (ASK) atteint un indice de modulation élevé, offrant ainsi une liaison robuste. Des circuits intégrés prototypes (CI) sont conçus et mis en œuvre dans une technologie CMOS standard de 180 nm. Une encapsulation en verre biocompatible hermétique est développée pour permettre des implants à longue durée de vie et à faible coût. La taille du système implantable encapsulé en verre est de 3,2 mm x 2 mm x 10 mm. Les challenges liés à l'alimentation de l'implant encapsulé en verre sont discutés et les performances du système sont vérifiées grâce à une plateforme expérimental in vitro qui émule le flux sanguin artériel.

**Mots clés :** Dispositif médicaux implantables (DMI), surveillance à distance des patients (SDP), surveillance hémodynamique des patients atteints d'insuffisance cardiaque (IC), capteur de pression, économie d'énergie, CMOS, amplificateur d'instrumentation (AI), convertisseur analogique-numérique (CAN), convertisseur pont-numérique (CPN), transfert par ultrason sans fil d'énergie et de données.

# **Contents**

| Ac | knov  | wledgements                                                        | j   |

|----|-------|--------------------------------------------------------------------|-----|

| Ał | ostra | ct (English/Français)                                              | iii |

| Li | st of | Figures                                                            | X   |

| Li | st of | Tables                                                             | χι  |

| 1  | Intı  | roduction                                                          | 1   |

|    | 1.1   | Heart Failure (HF)                                                 | 2   |

|    |       | 1.1.1 Societal and Economic Impact                                 | 2   |

|    |       | 1.1.2 Diagnosis and Monitoring                                     | 3   |

|    | 1.2   | State-of-the-Art Hemodynamic Monitoring                            | 4   |

|    |       | 1.2.1 Pulmonary Artery Catheter (PAC)                              | 4   |

|    |       | 1.2.2 CardioMEMS <sup>TM</sup> HF System                           | 4   |

|    |       | 1.2.3 Cordella <sup>TM</sup> PAP Sensor                            | 5   |

|    |       | 1.2.4 Ultrasound Cardiac Output Monitor (USCOM)                    | 6   |

|    | 1.3   | Thesis Goal                                                        | 7   |

|    |       | 1.3.1 System Overview                                              | 7   |

|    |       | 1.3.2 System Specifications                                        | 10  |

|    | 1.4   | Thesis Contributions                                               | 10  |

|    | 1.5   | Thesis Outline                                                     | 11  |

| 2  | Ene   | ergy and Area-Efficient Capacitively-Coupled Chopper IA            | 13  |

|    | 2.1   | Overview of Instrumentation Amplifiers                             | 13  |

|    | 2.2   | Design of an Energy and Area-Efficient CCCIA                       | 15  |

|    |       | 2.2.1 Topology and Design Considerations                           | 15  |

|    |       | 2.2.2 Implementation                                               | 17  |

|    | 2.3   | Ripple Reduction Loop (RRL)                                        | 19  |

|    |       | 2.3.1 Topology and Design Considerations                           | 19  |

|    |       | 2.3.2 Implementation                                               | 20  |

|    | 2.4   | Measurement Results                                                | 22  |

|    | 2.5   | Conclusion                                                         | 25  |

| 3  | Ene   | ergy-Efficient Bridge-to-Digital Converter for Pressure Monitoring | 27  |

#### Contents

|   | 3.1 | Overview of Implantable Pressure Sensing Systems                     | 28 |  |

|---|-----|----------------------------------------------------------------------|----|--|

|   | 3.2 | Duty-Cycled and Spinning Excitation BDC                              |    |  |

|   | 3.3 | System Design                                                        | 32 |  |

|   | 3.4 | Capacivitely-Coupled Instrumentation Amplifier (CCIA)                | 33 |  |

|   |     | 3.4.1 First Stage: Low-Noise Amplifier (LNA)                         | 34 |  |

|   |     | 3.4.2 Second Stage: Variable Gain Amplifier (VGA)                    | 36 |  |

|   | 3.5 | SAR ADC                                                              | 37 |  |

|   |     | 3.5.1 Capacitor Array DAC (CDAC)                                     | 37 |  |

|   |     | 3.5.2 Sample-and-Hold Switches                                       | 40 |  |

|   |     | 3.5.3 Dynamic Latch Comparator                                       | 41 |  |

|   |     | 3.5.4 SAR Control Logic                                              | 42 |  |

|   | 3.6 | Measurement Results                                                  | 44 |  |

|   |     | 3.6.1 Electrical Measurements                                        | 44 |  |

|   |     | 3.6.2 System Measurements                                            | 48 |  |

|   | 3.7 | Conclusion                                                           | 50 |  |

| 4 | Imr | olantable Inductive Sensor for Measuring Artery Cross-Sectional Area | 53 |  |

|   | 4.1 |                                                                      | 53 |  |

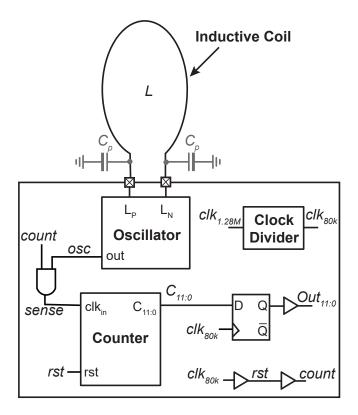

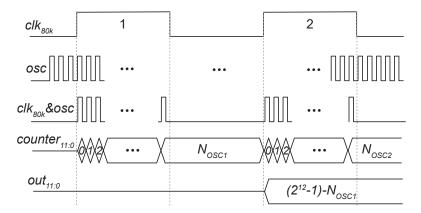

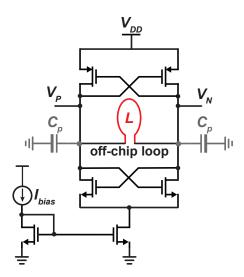

|   | 4.2 | Oscillator-Based Inductive Readout System                            | 54 |  |

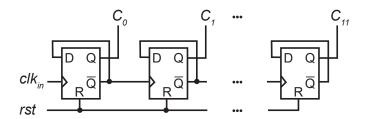

|   | 4.3 | Implementation Details                                               | 57 |  |

|   | 4.4 | Experimental Results                                                 | 58 |  |

|   | 4.5 | Conclusion                                                           | 60 |  |

| _ |     |                                                                      |    |  |

| 5 |     | eless Ultrasonic Power and Data Transfer                             | 63 |  |

|   | 5.1 | Wireless Power Transfer (WPT) Techniques for Implants                | 64 |  |

|   | 5.2 | WPT and Communication Using Ultrasound                               | 65 |  |

|   | 5.3 | Piezoelectric Transducers                                            | 66 |  |

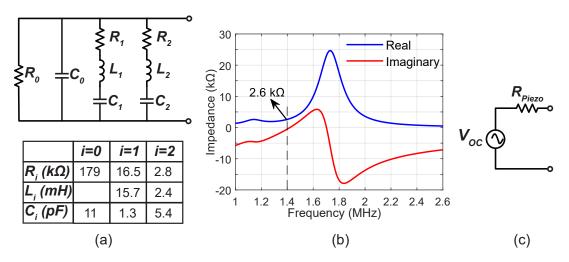

|   |     | 5.3.1 Implantable Transducer (Piezo)                                 | 66 |  |

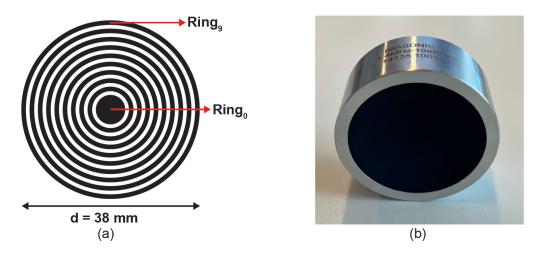

|   |     | 5.3.2 External Transducer                                            | 68 |  |

|   | 5.4 | Ultrasonic Power Transfer                                            | 69 |  |

|   |     | 5.4.1 Rectifier                                                      | 70 |  |

|   |     | 5.4.2 Voltage Regulator                                              | 72 |  |

|   |     | 5.4.3 Voltage Regulator to Generate Common-Mode Voltage              | 75 |  |

|   |     | 5.4.4 System Level Measurements of the Power Recovery Circuits       | 76 |  |

|   | 5.5 | Wireless Communication                                               | 78 |  |

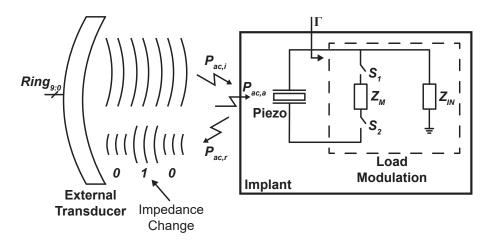

|   |     | 5.5.1 Ultrasonic Backscatter Communication                           | 79 |  |

|   |     | 5.5.2 Clock Recovery                                                 | 81 |  |

|   | 5.6 | Ultrasound Characterization                                          | 81 |  |

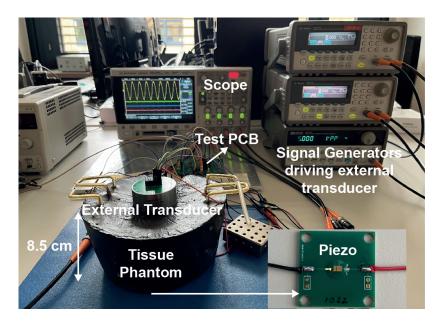

|   |     | 5.6.1 Modular Test Setup                                             | 81 |  |

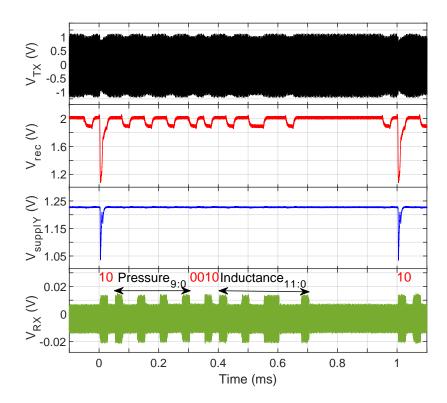

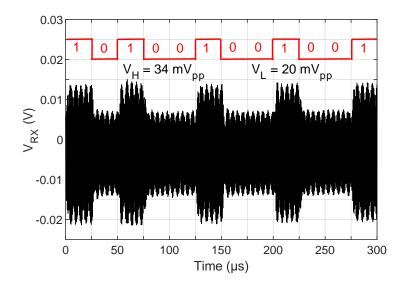

|   |     | 5.6.2 Experimental Results                                           | 82 |  |

|   | 5.7 | Conclusion                                                           | 85 |  |

| 6 | Bio | compatible Glass Packaging and Experimental Validations              | 87 |  |

|    |        | Cont                             | tents |

|----|--------|----------------------------------|-------|

|    |        |                                  |       |

|    | 6.1    | Biocompatible Glass Packaging    | 87    |

|    | 6.2    | Glass Package Characterization   | 89    |

|    | 6.3    | <i>In Vitro</i> Characterization | 91    |

|    | 6.4    | Conclusion                       | 93    |

| 7  | Con    | nclusion                         | 95    |

|    | 7.1    | Summary                          | 95    |

|    | 7.2    | Future Work                      |       |

| Bi | bliog  | graphy                           | 99    |

| Li | st of  | Acronyms                         | 115   |

| Pι | ıblica | ations & Patents                 | 117   |

| Cı | urric  | ulum Vitae                       | 119   |

# **List of Figures**

| 1.1  | Process of pulmonary artery catheter                                                                                                                           | 5  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Existing remote hemodynamic monitoring devices: (a) CardioMEMS <sup>TM</sup> HF System of Abbott, the state-of-the-art PAP-guided implantable hemodynamic mon- |    |

|      | itoring device in the market. (b) Cordella <sup>TM</sup> PAP Sensor of Endotronix, an in-                                                                      |    |

|      | vestigational device similar to CardioMEMS <sup>TM</sup> . (c) Ultrasound Cardiac Output                                                                       |    |

|      | Monitor (USCOM) device for non-invasive CO monitor based on Doppler ultra-                                                                                     |    |

|      | sound technology.                                                                                                                                              | 6  |

| 1.3  | (a) Conceptual view of the remotely powered deep implant placed in the PA.                                                                                     |    |

|      | (b) An example of placement for the external base station for wireless power and                                                                               |    |

|      | data transfer. (c) The implantable system consisting of (A) a piezoelectric trans-                                                                             |    |

|      | ducer, (B) a piezoresistive pressure sensor, (C) an ASIC, and (D) two conductive                                                                               |    |

|      | anchoring loops.                                                                                                                                               | 8  |

| 1.4  | Block diagram of the complete system with the US link                                                                                                          | 9  |

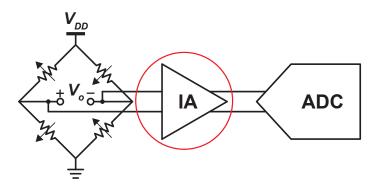

| 2.1  | Conventional readout circuit for Wheatstone bridge sensors                                                                                                     | 14 |

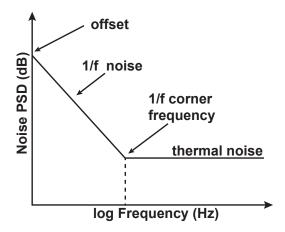

| 2.2  | Low-frequency noise spectrum for CMOS amplifiers                                                                                                               | 15 |

| 2.3  | Schematic of the CCCIA with a bridge sensor                                                                                                                    | 16 |

| 2.4  | Schematic of a chopper switch based on four NMOS transistors                                                                                                   | 17 |

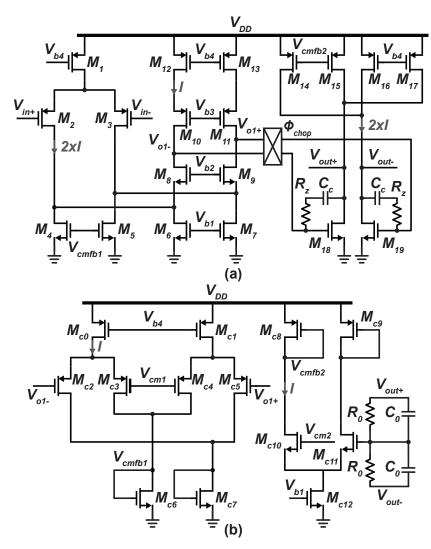

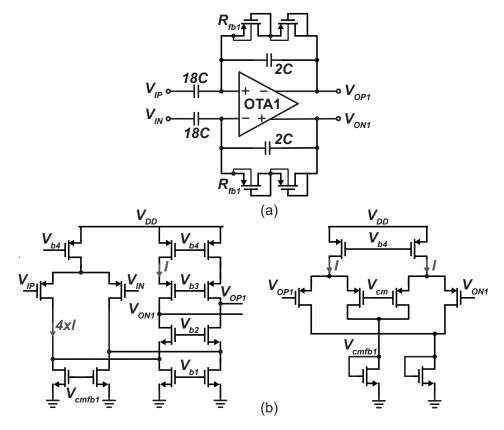

| 2.5  | Schematic of (a) the two-stage Miller OTA ( $G_{m1}$ and $G_{m2}$ ) with (b) two seperate                                                                      |    |

|      | CMFB circuits                                                                                                                                                  | 18 |

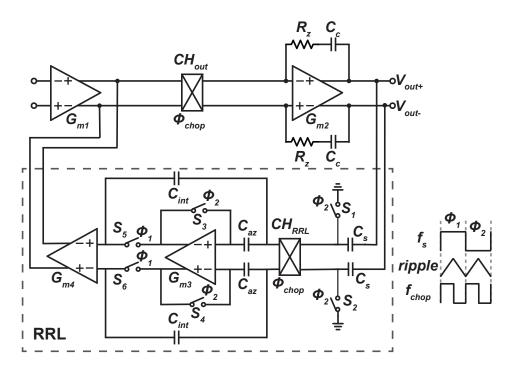

| 2.6  | Schematic and timing diagram of the SC RRL                                                                                                                     | 20 |

| 2.7  | Schematic of the (a) SC RRL integrator OTA ( $G_{m3}$ ) with its CMFB circuit, and (b)                                                                         |    |

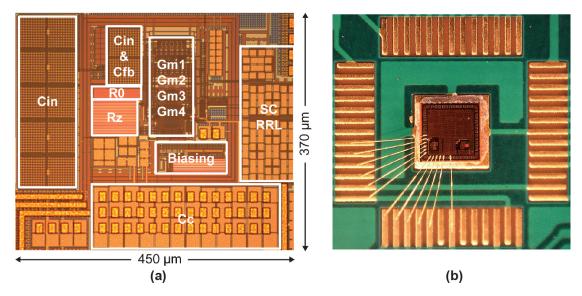

|      | the compensation transconductor ( $G_{m4}$ )                                                                                                                   | 21 |

| 2.8  | (a) Die micrograph of the CCCIA and (b) photo of the test PCB with the wire-                                                                                   |    |

|      | bonded IC                                                                                                                                                      | 22 |

| 2.9  | (a) Measured frequency response for different gain configurations and (b) output                                                                               |    |

|      | noise spectrum at the highest gain configuration                                                                                                               | 23 |

| 2.10 | Measured (a) input-referred offset and (b) transient step response                                                                                             | 23 |

| 2.11 | Measured output ripple with and without the RRL                                                                                                                | 24 |

| 3.1  | Schematic view of a piezoresistive pressure sensor                                                                                                             | 28 |

| 3.2  | Conventional bridge-to-digital converter (BDC)                                                                                                                 | 29 |

|      |                                                                                                                                                                |    |

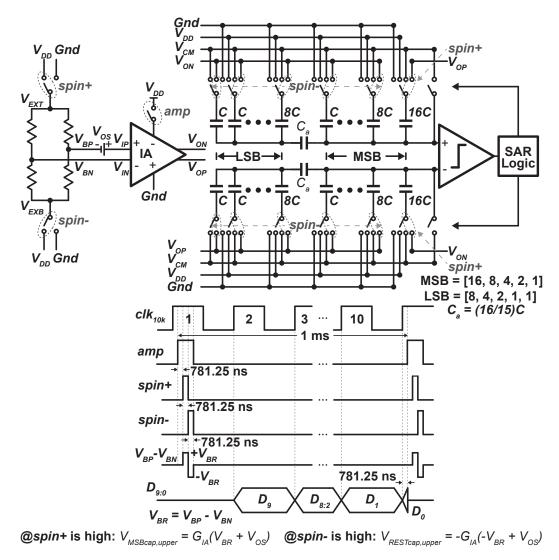

| 3.3  | Circuit diagram of the highly duty-cycled and spinning excitation BDC, and its              | 31  |

|------|---------------------------------------------------------------------------------------------|-----|

| 2.4  | timing diagram.                                                                             |     |

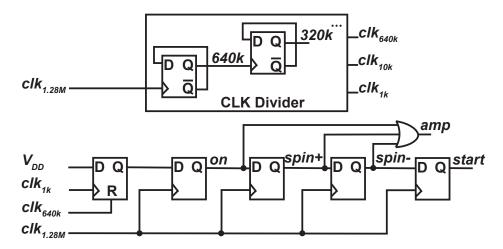

| 3.4  | Simplified circuit diagram of the spinning control logic.                                   | 33  |

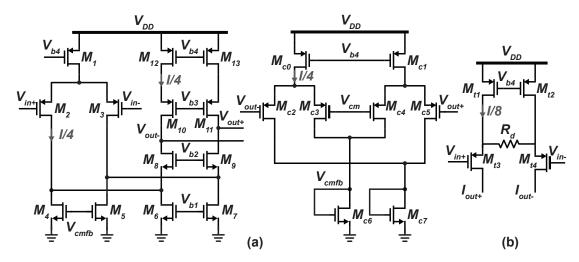

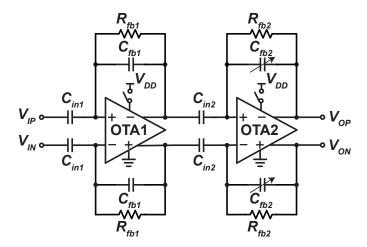

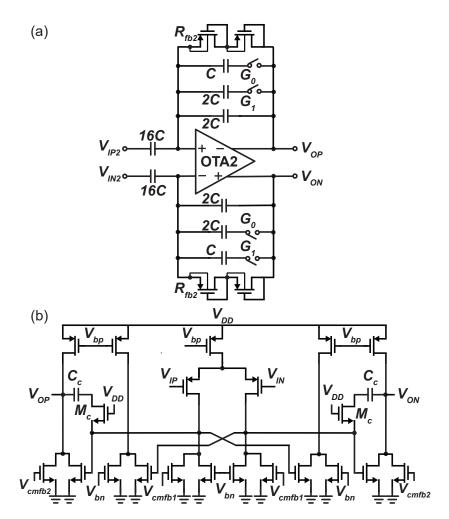

| 3.5  | Circuit diagram of the capacitively-coupled IA consisting of two gain stages                | 34  |

| 3.6  | Schematics of the (a) low-noise amplifier (LNA) and (b) the folded-cascode (FC)             | 0.5 |

|      | amplifier (OTA1) with its CMFB circuit.                                                     | 35  |

| 3.7  | Schematics of the (a) variable gain amplifier (VGA) and (b) two-stage Miller                |     |

|      | amplifier with a class AB output stage (OTA2)                                               | 36  |

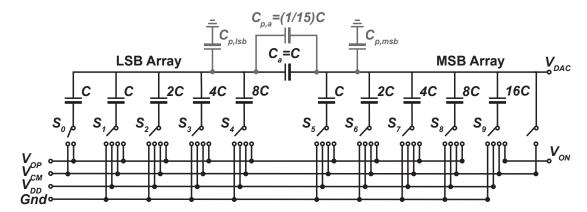

| 3.8  | Schematic of the split CDAC employing $V_{cm}$ -based switching technique                   | 39  |

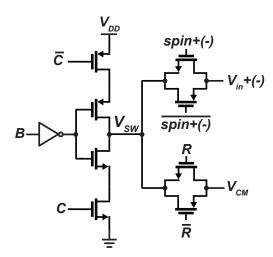

| 3.9  | Schematic of the sample-and-hold switches                                                   | 40  |

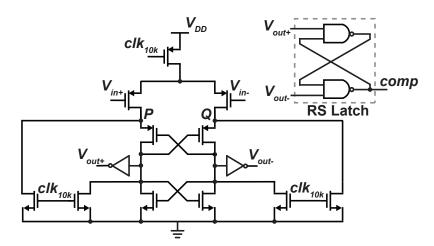

|      | Schematic of the StrongARM latch dynamic comparator                                         | 42  |

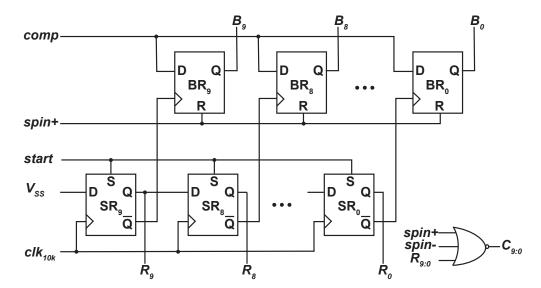

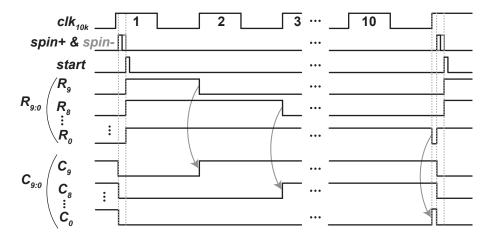

| 3.11 | Block diagram of the SAR control logic                                                      | 43  |

|      | Timing diagram of the SAR control logic                                                     | 43  |

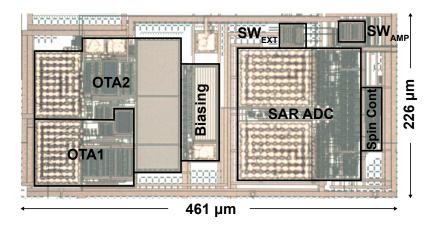

|      | Die micrograph of the BDC ASIC fabricated in a 180-nm CMOS process                          | 44  |

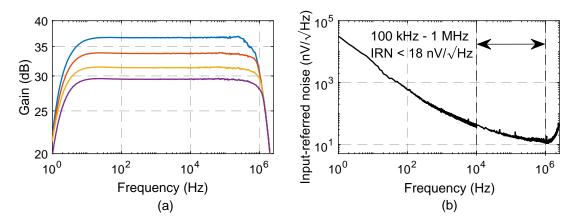

| 3.14 | CCIA's measured (a) frequency response for different gain configurations and (b)            |     |

|      | input-referred noise (IRN) spectrum.                                                        | 45  |

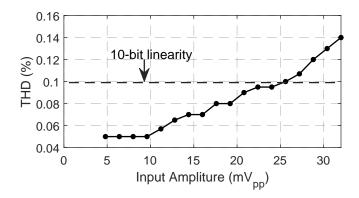

| 3.15 | THD as a function of the input amplitude                                                    | 45  |

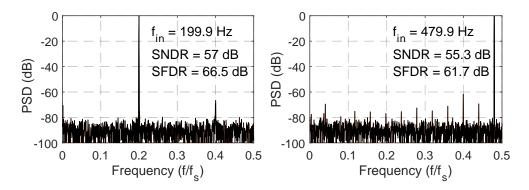

| 3.16 | Measured FFT spectrum at 1 kS/s                                                             | 46  |

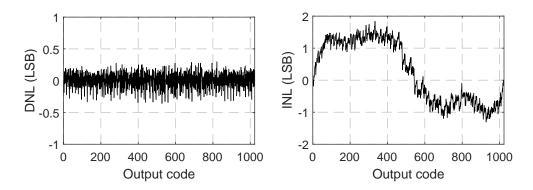

| 3.17 | Measured DNL and INL                                                                        | 46  |

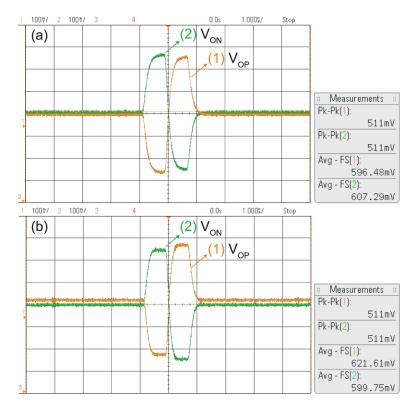

| 3.18 | Output voltages of the (a) first and (b) second commercial amplifier                        | 47  |

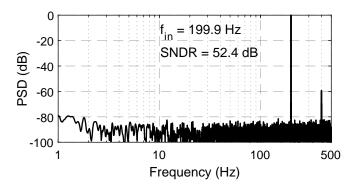

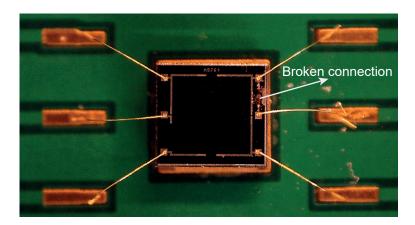

| 3.19 | Measured output spectrum of the BDC                                                         | 47  |

| 3.20 | SNDR vs. input amplitude of the BDC at $f_{in}$ = 199.9 Hz                                  | 47  |

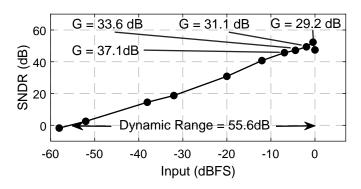

| 3.21 | Photo of the wire-bonded MS761 sensor with a broken connection eliminating                  |     |

|      | reverse biasing and current leakage issues                                                  | 48  |

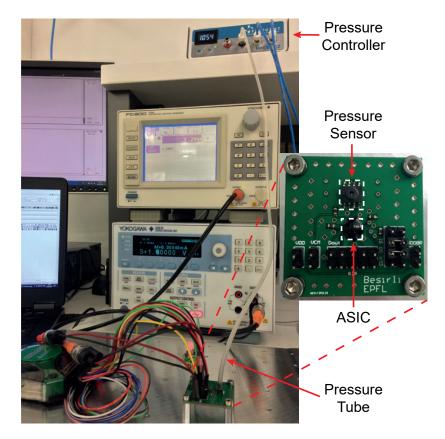

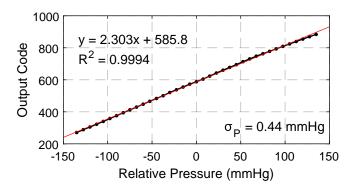

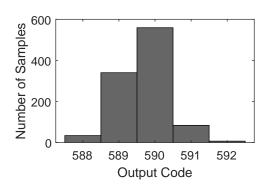

| 3.22 | Experimental setup for pressure measurements of the BDC                                     | 49  |

| 3.23 | Measured decimated output of the BDC with swept pressure from –135 mmHg                     |     |

|      | to +135 mmHg with respect to the ambient pressure                                           | 50  |

| 3.24 | Histogram of the decimated output at zero pressure input for 1024 samples                   | 51  |

|      |                                                                                             |     |

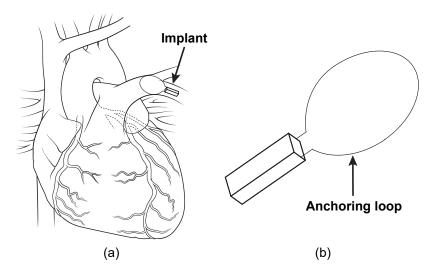

| 4.1  | (a) Conceptual view of a hemodynamic monitoring implant mounted in a pul-                   |     |

|      | monary artery branch of a patient's heart. (b) Conceptual view of the implant               |     |

|      | with an anchoring loop for the placement and CSA measurement in the artery.                 | 55  |

| 4.2  | Block diagram of the inductive readout IC with its connections to the inductive             |     |

|      | anchoring coil                                                                              | 56  |

| 4.3  | Timing diagram of the inductive readout circuit                                             | 57  |

| 4.4  | Schematic of the cross-coupled voltage controlled oscillator                                | 58  |

| 4.5  | Schematic of the 12-bit asynchronous up counter                                             | 58  |

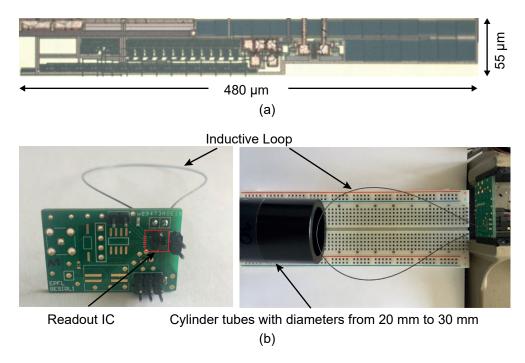

| 4.6  | (a) Die micrograph of the inductive readout IC. (b) Test PCB with a nitinol                 |     |

|      | anchoring loop and the readout IC, and the experimental setup. $\ \ldots \ \ldots \ \ldots$ | 59  |

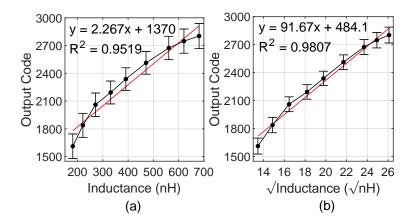

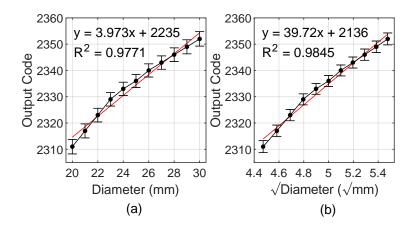

| 4.7  | Measured decimated output of the inductive readout with respect to (a) the                  |     |

|      | inductance (L), and (b) $\sqrt{L}$                                                          | 60  |

| 4.8         | Measured decimated output of the inductive readout with the nitinol anchoring loop with respect to the cylindrical tube's (a) diameter $D$ , and (b) $\sqrt{D}$ | 60  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

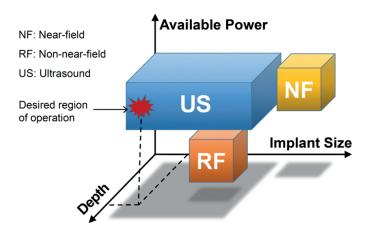

| 5.1         | Conceptual diagram showing applicable regimes of different WPT methods                                                                                          | 64  |

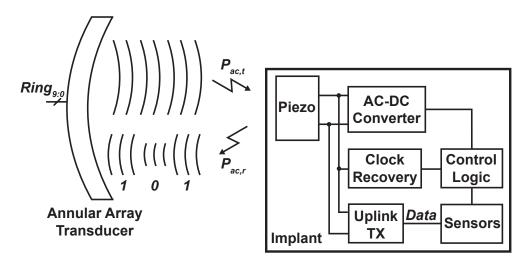

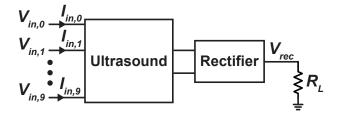

| 5.2         | Block diagram of the US link for simultaneous power and data transfer                                                                                           | 65  |

| 5.3         | Implantable piezoelectric transducer with dimensions of 3.2 mm $\times$ 2 mm $\times$ 1                                                                         |     |

|             | mm                                                                                                                                                              | 66  |

| 5.4         | (a) Equivalent circuit model and (b) the simulated impedance of the piezo in-                                                                                   |     |

|             | cluding the effect of acoustic loadings from 150- $\mu$ m thick glass. (c) Equivalent                                                                           |     |

|             | circuit model of the piezo at short-circuit resonance frequency                                                                                                 | 67  |

| 5.5         | (a) Schematic and (b) photo of the external transducer which is an annular array                                                                                |     |

|             | transducer consisting of 10 rings                                                                                                                               | 68  |

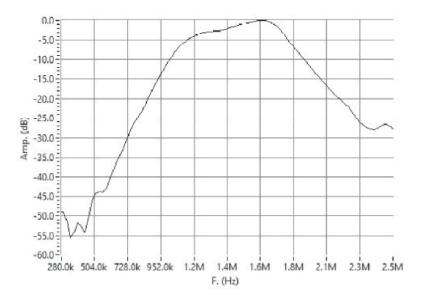

| 5.6         | Measured frequency spectrum of the external transducer, provided by IMASONIC.                                                                                   | 69  |

| 5.7         | Building blocks of the implantable device                                                                                                                       | 70  |

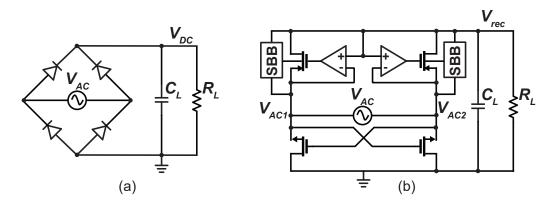

| 5.8         | Schematics of a (a) full-wave diode-bridge rectifier and (b) full-wave comparator-                                                                              |     |

|             | based active rectifier                                                                                                                                          | 71  |

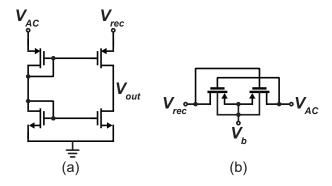

| 5.9         | Schematics of a (a) conventional common-gate-type comparator and (b) dy-                                                                                        |     |

|             | namic body bias circuit.                                                                                                                                        | 71  |

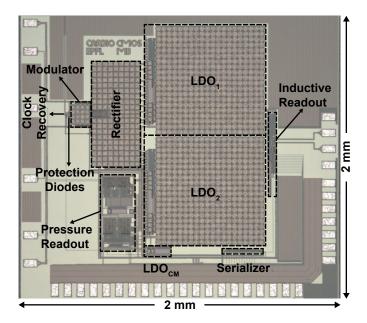

|             | Die micrograph of the ASIC in 180-nm CMOS                                                                                                                       | 72  |

| 5.11        | (a) Rectifier output voltage ( $V_{rec}$ ) versus input voltage ( $V_{in}$ ) for different output                                                               |     |

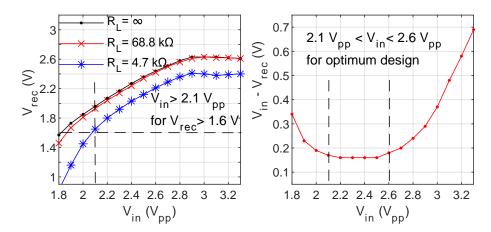

|             | loads, and (b) $V_{in}$ - $V_{rec}$ versus $V_{in}$ for 68 k $\Omega$ load resistance                                                                           | 73  |

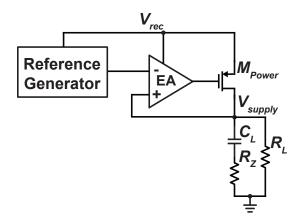

|             | Schematic of the LDO regulator                                                                                                                                  | 73  |

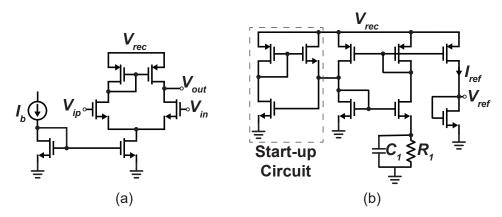

| 5.13        | Schematic of (a) the single-stage differential amplifier used in the EA, and (b)                                                                                |     |

|             | the Beta-multiplier current reference used as the reference generator                                                                                           | 74  |

| 5.14        | Measured output voltage of the LDO regulator versus its input voltage for differ-                                                                               |     |

|             | ent output loads.                                                                                                                                               | 75  |

|             | Schematic of the LDO regulator generating CM voltage                                                                                                            | 76  |

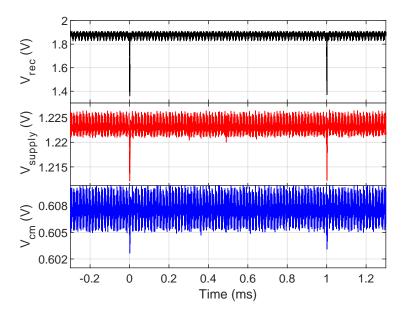

|             | Measured powering signals supplying the BDC when $V_{in} = 2.1 V_{pp}$                                                                                          | 77  |

|             | Measured powering signals supplying the BDC when $V_{in}$ = 2.6 $V_{pp}$                                                                                        | 77  |

|             | Measured powering signals supplying the BDC and the inductive readout when                                                                                      |     |

|             | $V_{in} = 2.1 V_{pp}$                                                                                                                                           | 78  |

|             | Uplink communication through ultrasonic backscattering                                                                                                          | 79  |

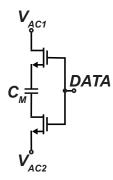

|             | Schematic of the modulator circuit.                                                                                                                             | 80  |

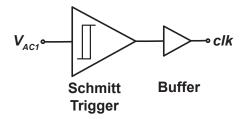

|             | Schematic of the clock recovery circuit                                                                                                                         | 81  |

|             | Modular test setup for ultrasonic measurements using an 8.5 cm tissue phantom.                                                                                  | 82  |

|             | Energy harvesting chain for link efficiency characterization                                                                                                    | 83  |

| 5.24        | Wireless ultrasonic measurement showing powering and communication signals                                                                                      | 0.4 |

| <b>5.05</b> | in a measurement cycle                                                                                                                                          | 84  |

| 5.25        | US uplink signal received by the external transducer                                                                                                            | 85  |

| 6.1         | Innovative, biocompatible, hermetic, and highly-reliable glass packaging approach                                                                               | 00  |

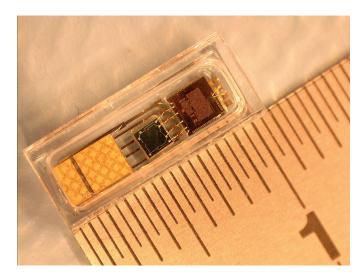

| 6.2         | proach                                                                                                                                                          | 88  |

| 6.2         | Glass-packaged miniature implant without anchoring loops                                                                                                        | 89  |

#### **List of Figures**

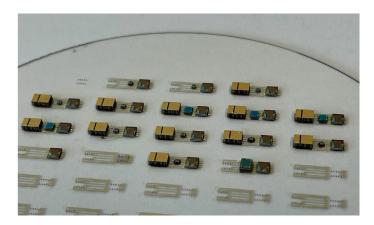

| 6.3 | Different assembled samples on a carrier glass wafer                           | 90 |

|-----|--------------------------------------------------------------------------------|----|

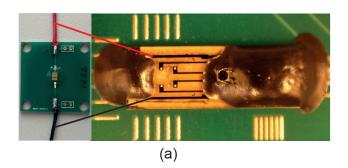

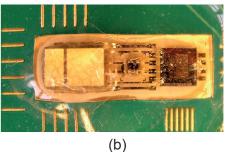

| 6.4 | Glass assembly samples without the top glass cover. (a) The glass board con-   |    |

|     | taining the ASIC and pressure sensor, and the piezo are on different PCBs and  |    |

|     | connected by two wires. (b) All three components are on the glass board, and a |    |

|     | wired connection is made to the piezo's output to monitor the harvested power. | 91 |

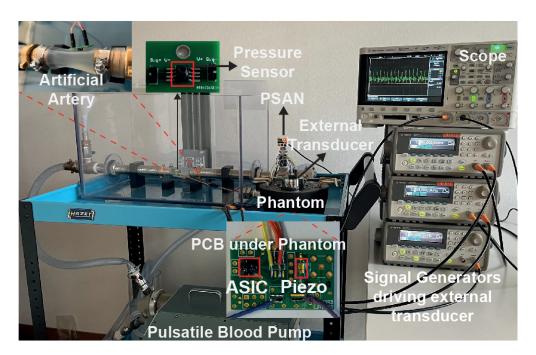

| 6.5 | <i>In vitro</i> experimental setup emulating the arterial blood flow           | 92 |

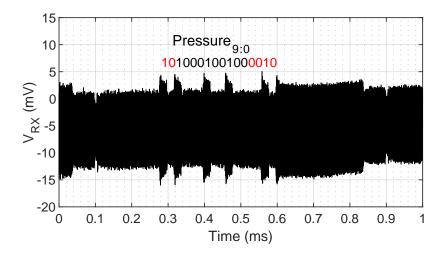

| 6.6 | US uplink signal showing the pressure value                                    | 93 |

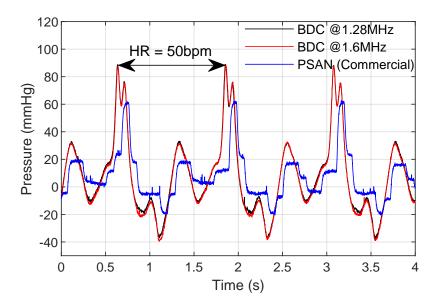

| 6.7 | Comparison of pressure waveforms measured by the implantable system re-        |    |

|     | motely powered by ultrasound at 1.28 MHz and 1.6 MHz, and the commercial       |    |

|     | PSAN pressure sensor                                                           | 94 |

## **List of Tables**

| 1.1 | System specifications for the remote hemodynamic monitoring implant      | 11 |

|-----|--------------------------------------------------------------------------|----|

| 2.1 | CCCIA's performance summary and comparison with the state of the art     | 24 |

|     | Performance summary of the BDC's sub-blocks                              |    |

| 4.1 | Performance summary of the inductive readout for artery CSA measurement. | 61 |

## 1 Introduction

Technology advancements have a significant impact on the diagnosis and treatment of diseases. The incorporation of technology in the medical field has greatly improved the accuracy of diagnoses, leading to more successful treatments. Today, mobile health technologies have enormous potential for enhancing patient care and reducing healthcare costs. Wearable and implantable devices are driving a transformation in the mobile health era and are receiving increasing attention in various biomedical applications such as medical diagnostics, clinical therapy, and personal healthcare [1].

Wearable devices that can continuously monitor patients' vital signs are widely available in the form of smart watches, glasses, and arm bands. These devices are capable of monitoring a range of physiological parameters, including heart rate, blood pressure, respiration rate, blood oxygen saturation level, and body temperature [1]. Additionally, there is a growing demand for implantable medical devices and electronics among both patients and clinicians. Since the first pacemaker implant in 1958, a variety of implantable devices such as pacemakers, cardioverter defibrillators, cochlear implants, and deep brain stimulators have been developed and are used to treat millions of patients [2, 3]. According to a report by Allied Market Research [4], the implantable medical devices market was valued at \$91.9 billion in 2020 and is expected to reach \$179 billion by 2030.

Recent advancements in fabrication and packaging techniques have made it possible to embed multiple microelectronic and micromechanical sensors very sensitively into a small and cost-effective area, allowing for the efficient integration of various sensing capabilities into wearable and implantable devices. In addition, improvements in wireless communication technology have enabled high data rates and expanded broadband wireless networks to reach rural and low-income areas [1]. According to a report by the International Telecommunication Union [5], in 2021, 95% of the world's population had access to mobile broadband networks and 4G network coverage reached 88% of the global population. The widespread availability of broadband wireless networks worldwide offers great promise for the use of wearable and implantable sensors in remote and continuous monitoring of patients, which has the potential to greatly improve patient care while significantly reducing healthcare costs.

Remote patient monitoring (RPM), also known as telemonitoring, refers to the monitoring and evaluation of a patient's health parameters remotely. RPM systems wirelessly transfer the patient's physiological data to healthcare providers, allowing for more frequent and sensitive assessment of the patient's clinical status. Utilizing advances in digital technology, RPM offers many benefits to the healthcare system, such as saving time for both healthcare providers and patients, the ability to continuously monitor patients, the prevention of worsening illnesses and untimely deaths, reduced hospitalizations and costs, and more accurate readings while allowing patients to continue with their usual daily activities [6]. It is also useful in situations where patients have mobility issues or when physical interactions are risky, such as during a pandemic. During the Covid-19 pandemic, the popularity of RPM increased and several applications were developed to help reduce hospitalization rates [7]. One of the main areas where wearable and implantable devices can be effectively used for RPM is remote hemodynamic monitoring of heart failure (HF) patients, allowing healthcare providers to continuously track key indicators of their condition and intervene proactively to prevent deterioration, reducing the risk of repeated hospitalizations. This thesis presents the design and development of an implantable system for remote and long-term hemodynamic monitoring of HF patients.

#### 1.1 Heart Failure (HF)

Heart Failure is a severe and progressive clinical condition in which the heart is unable to pump enough blood to meet the needs of the body. It is one of the leading causes of death, disability, and healthcare costs in the 21<sup>st</sup> century [8, 9, 10]. One of the defining characteristics of HF is a high incidence of hospital admission and readmission, with HF causing the highest rate of rehospitalization compared to all other medical conditions [9]. High rate of HF hospitalization (HFH) results in a significant economic burden to the health care system and decreases the quality of life of millions of patients. HF patients suffer from progressively declining functional status and impaired quality of life, leading to death within 5 years of diagnosis for approximately 42% of them [11]. HF is diagnosed by monitoring a patient's heart function. Monitoring of hemodynamics, which is the dynamics of the blood flow, plays a crucial role in the management of HF [12, 13]. The continuous (24/7) and accurate monitoring of the patient's hemodynamics, particularly pulmonary artery (PA) pressure and cardiac output (CO), is essential for adapting treatments based on the patient's reactions to the prescribed medications and reducing repeated hospital admissions.

#### 1.1.1 Societal and Economic Impact

The global impact of cardiovascular diseases (CVDs) is burdensome as reported by the World Health Organization (WHO) [14]: they are the leading cause of death globally, accounting for 32% of all deaths, killing about 17.9 million people every year worldwide. Focusing on HF, it is a global epidemic, affecting more than 64 million people worldwide, with rates increasing due to population growth and aging [15].

In the United States, the prevalence of HF is projected to increase by 46% from 2012 to 2030, and it is estimated that more than 8 million adults older than 18 years will suffer from HF in 2030 [16, 17]. The total percentage of the population with HF is expected to rise from 2.4% in 2012 to 3% in 2030. Hospitalization is inevitable to treat acute complications of HF. This places a growing burden on national healthcare systems and is becoming increasingly unsustainable. In 2018, HF hospitalizations in the United States exceeded 1.2 million, and the number of deaths due to HF in 2019 was more than 86,000 [17]. In Switzerland, the overall HF prevalence is estimated at 2.5%, representing more than 200,000 people [18, 19]. According to the Swiss Federal Office of Statistics, among all causes of death, cardiovascular mortality in 2020 was 26.9%, and more than 62,000 men and 44,000 women were hospitalized for CVDs [20].

As the population is aging, the prevalence of HF continues to rise and its economic burden on healthcare systems significantly increases, with the cost of care becoming unsustainable. The global economic burden of HF in 2012 was estimated to be \$108 billion per year, and this value is expected to continue to rise further with the aging and increasing global population [21]. In the United States, the estimated total cost of HF in 2020 is \$43.6 billion, and the annual total cost of care is projected to increase by 60% to \$69.7 billion by 2030 [16]. HFH is a major contributor to the high cost of HF care. The annual median total cost for HF care per patient was estimated at \$24,383, with HFH driving costs at \$15,879 per patient [22].

#### 1.1.2 Diagnosis and Monitoring

The journey of HF patients is complex and difficult, beginning with the onset of initial symptoms and progressing to a decline in physical status, which can vary in its severity, and may lead to death. Medical management aims to stabilize the disease and treat acute decompensation leading to hospitalization. When the HF process of congestion [23] and decompensation begins, the earliest change in a physiologic parameter is an increase in cardiac filling and PA pressure (PAP), which could be detected weeks before hospitalization [13]. A recent study [24] showed that even small changes in PAP can predict mortality in patients with chronic HF. In a 6 months period, a 3 mmHg reduction in estimated PA diastolic pressure was associated with a 19.2% reduction in mortality risk whereas 5 mmHg reduction was associated with a 30% reduction. Contrarily, a rise of 3 mmHg in the estimated PA diastolic pressure was associated with 23.8% increase in mortality risk while an increase of 5 mmHg after 6 months was associated with a 42.8% increase in mortality risk.

Cardiac output is the volume of blood that the heart pumps in a time interval of one minute [25]. The changes in cardiac function associated with HF result in a decrease in CO [13]. According to the definition of European Society of Cardiology, HF is due to a structural and/or functional abnormality of the heart that results in elevated intracardiac pressures and/or inadequate cardiac output at rest and/or during exercise [13]. Therefore, two essential physiological parameters to assess the early development of HF are PAP and CO.

#### 1.2 State-of-the-Art Hemodynamic Monitoring

Hemodynamic monitoring plays a crucial role in the management of HF patients. The pulmonary artery catheter (PAC) [26] is the current "gold standard" for measuring the PAP and CO directly and simultaneously [27]. However, this invasive technique is limited to intensive care settings and operating rooms and is not suitable for RPM. There are also other hemodynamic monitoring systems such as pulse wave analysis, echocardiography, Doppler ultrasonography, carbon dioxide rebreathing, and bioimpedance [12, 27]. However, these methods are limited in accuracy as they do not directly measure the CO and are also not suitable for RPM, outside of the critical care or in-hospital environment. The demand for remote hemodynamic monitoring has led to the development of devices such as the CardioMEMS<sup>TM</sup> HF System, Cordella<sup>TM</sup> HF System, and the USCOM device. These devices will be explained and compared in the following sections. The current state-of-the-art implantable remote hemodynamic monitoring device in the market is CardioMEMS<sup>TM</sup> HF System. By providing accurate PAP measurements during the CHAMPION trial [9], it showed a 37% reduction in the relative risk of HF hospitalizations and a significant improvement in the quality of life of HF patients.

#### 1.2.1 Pulmonary Artery Catheter (PAC)

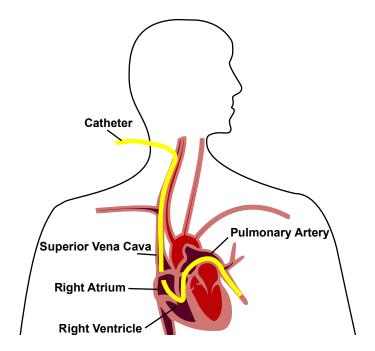

The pulmonary artery catheter (PAC) is a thin, flexible tube with a small balloon at the tip that is inserted into a PA during a procedure called pulmonary artery catheterization or right heart catheterization. Fig. 1.1 illustrates the process of PAC. The technique was introduced by Drs. Swan and Ganz in 1970 [26] and is the current "gold standard" in hemodynamic monitoring [12, 27]. It has a key advantage over many other systems in that it provides simultaneous measurements of other hemodynamic parameters in addition to CO, including PAP, right-sided and left-sided filling pressures, and mixed venous oxygen saturation [12].

The thermodilution technique computes CO by timing the temperature change of a set volume of cold injectate as it travels a set distance to the PAC temperature sensor [12]. This technique offers a direct and accurate CO measurement, combined with other useful indicators. The drawbacks include invasive equipment carrying potential severe complications and requiring complex calibrations, making it unsuitable outside of highly monitored environments, technical factors affecting measurements, and intermittent measurements [27]. Most importantly, it is not suitable for telemonitoring.

#### 1.2.2 CardioMEMS<sup>TM</sup> HF System

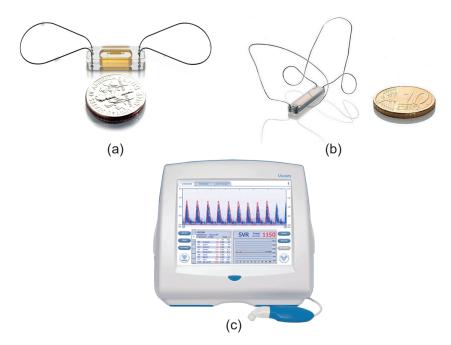

CardioMEMS<sup>TM</sup> HF System [29] from Abbott is the state-of-the-art PAP-guided remote hemodynamic monitoring device in the market. The system is passive and consists of a capacitive pressure sensor and an inductor [30]. Pressure applied to the capacitive sensor leads to a characteristic shift in the resonant frequency, and by applying electromagnetic signals from an external station, this data is transmitted to the external base station. Fig. 1.2(a) shows the

Figure 1.1: Process of pulmonary artery catheter. Adapted from [28].

implantable sensor unit hermetically sealed by glass and having two nitinol loops to permanently anchor the implant in a branch of the PA. It is small in size, measuring  $3.5 \, \text{mm} \times 2 \, \text{mm} \times 15 \, \text{mm}$ , suitable for endovascular delivery and permanent implantation [31].

Several clinical trials demonstrated its long-term safety and clinical efficacy [32, 33], and Food and Drug Administration (FDA) approved it in 2014 for PAP monitoring in HF patients. The system has a small size, a good safety profile, a simple implantation procedure, and provides an accurate PAP measurement comparable to the Swan-Ganz method [31, 34]. In the CHAMPION trial, CardioMEMS<sup>TM</sup> guided therapy led to a 37% reduction in HFHs at 1 year [32]. The extended efficacy of pressure-directed HF therapy was demonstrated using CHAMPION trial data, with HFHs reduced by 33% over the randomized access process and 48% over the open access process over 31 months follow-up [34]. Despite its undeniable advantage for remote hemodynamic monitoring, CardioMEMS<sup>TM</sup> relies only on PAP to assess cardiovascular status, giving a limited understanding of the HF mechanism. Recently, it was used to estimate the CO using a software algorithm calculating CO based on the analysis of pressure waveforms [35]. However, it does not measure the CO directly, only estimates it based on pressure waveforms.

#### 1.2.3 Cordella<sup>TM</sup> PAP Sensor

The Cordella<sup>TM</sup> PAP Sensor from Endotronix is a prototype device and is not currently approved for clinical use in any region. Similar to CardioMEMS<sup>TM</sup>, it is a PAP-guided HF management system [36, 37]. Cordella<sup>TM</sup> is a passive system consisting of a capacitive pressure sensor and an inductor [38]. The pressure data from the capacitive sensor is transmitted to an

Figure 1.2: Existing remote hemodynamic monitoring devices: (a) CardioMEMS<sup>TM</sup> HF System of Abbott, the state-of-the-art PAP-guided implantable hemodynamic monitoring device in the market. (b) Cordella<sup>TM</sup> PAP Sensor of Endotronix, an investigational device similar to CardioMEMS<sup>TM</sup>. (c) Ultrasound Cardiac Output Monitor (USCOM) device for non-invasive CO monitor based on Doppler ultrasound technology. Photos from [29],[39],[40]

external base station using electromagnetic signals via inductive coupling. Fig. 1.2(b) shows the hermetically sealed implantable sensor having two nitinol anchoring loops.

The results of the first-in-human clinical study (SIRONA) [36] showed that the implantation of the Cordella<sup>TM</sup> sensor was safe, feasible, and provided accurate PAP measurements that were comparable to those obtained with the Swan-Ganz catheter. However, the rates of HF hospitalization were found to be higher than those seen with the CardioMEMS<sup>TM</sup>. The PROACTIVE-HF clinical studies [37] are currently underway to evaluate the effectiveness of the system. In December 2021, the FDA approved changing the trial to a single-arm study with pre-specified safety and effectiveness endpoints, in order to provide objective evidence of a similar risk-benefit profile to the CardioMEMS<sup>TM</sup>. Like the CardioMEMS<sup>TM</sup>, Cordella<sup>TM</sup> sensor relies on PAP to assess the cardiovascular status and does not measure the CO, giving a limited understanding of the HF mechanism.

#### 1.2.4 Ultrasound Cardiac Output Monitor (USCOM)

The Ultrasound Cardiac Output Monitor (USCOM) device is a non-invasive CO monitor based on continuous wave Doppler ultrasound (US) technology [41]. The device can measure CO from the pulmonary or aortic valve by measuring blood flow velocity through the valve using the Doppler effect. When measured by echocardiography, CO is defined as the product of

stroke volume (SV) and heart rate (HR), where SV is velocity time integral (VTI) multiplied by the cross-sectional area (CSA) of the artery or valve [25]:

$$CO_{\left[\frac{ml}{min}\right]} = VTI_{\left[\frac{cm}{beat}\right]} \times CSA_{\left[cm^{2}\right]} \times HR_{\left[\frac{beats}{min}\right]}. \tag{1.1}$$

For cardiac output measurement at the pulmonary valve, the ultrasound probe is placed on the patient's chest and directed at the pulmonary valve [42]. Blood flow velocity is measured by the Doppler effect, but the CSA of the valve is only estimated based on the patient's age and weight [42, 43]. Fig. 1.2(c) shows the USCOM device with its ultrasound probe.

This non-invasive device was approved by FDA in 2005, but has been found to have poor agreement with the CO measurements obtained using the pulmonary artery catheter method [42]. This is likely due to the fact that the USCOM device does not directly measure the cross-sectional area of the valve, which is a significant source of error in CO measurements [25, 42]. To measure the CO accurately, the CSA should be directly measured.

#### 1.3 Thesis Goal

The goal of this thesis is to develop an advanced, implantable wireless system for remote hemodynamic monitoring of HF patients. This system aims to enable direct, continuous (24/7), and simultaneous measurement of the PA pressure and artery cross-sectional area, using ultrasound technology for wireless power transfer and data communication. The main advancements of this thesis include:

- 1. Development of a miniaturized and energy-efficient bridge-to-digital converter enabling duty-cycling of the piezoresistive pressure sensors to achieve an ultra-low power pressure sensing system for direct and continuous (24/7) PAP measurement.

- 2. Development of a novel method for direct and continuous (24/7) measurement of the CSA of an artery, based on the inductance change of the anchoring loops mounted on a miniaturized system implanted in a section of the artery.

- 3. Development of a wireless ultrasonic power and data platform for efficient powering and robust communication of deeply implanted medical devices.

- 4. Integration of the system in a miniaturized biocompatible package enabling permanent implantation in the pulmonary artery.

#### 1.3.1 System Overview

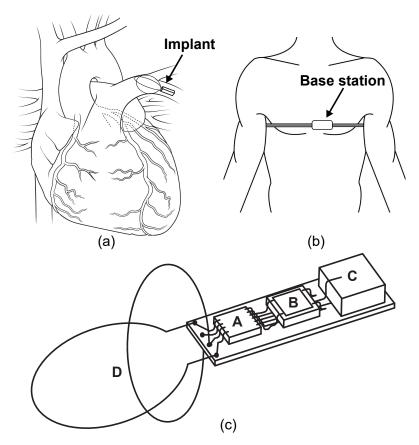

In this thesis, an implantable active system for direct and remote hemodynamic monitoring, specifically for PAP and artery CSA measurements, is developed. Fig. 1.3(a) illustrates the concept of the deep implantable system placed in a branch of the pulmonary artery. A wireless

Figure 1.3: (a) Conceptual view of the remotely powered deep implant placed in the PA. (b) An example of placement for the external base station for wireless power and data transfer. (c) The implantable system consisting of (A) a piezoelectric transducer, (B) a piezoresistive pressure sensor, (C) an ASIC, and (D) two conductive anchoring loops.

ultrasonic power transfer solution is used with the deep implant, with an external piezoelectric transducer placed over the implanted unit. Fig. 1.3(b) shows an example of a placement for the external unit.

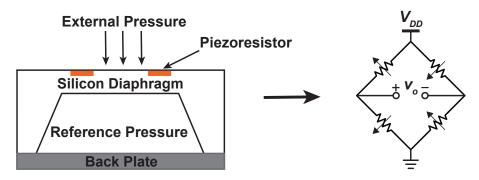

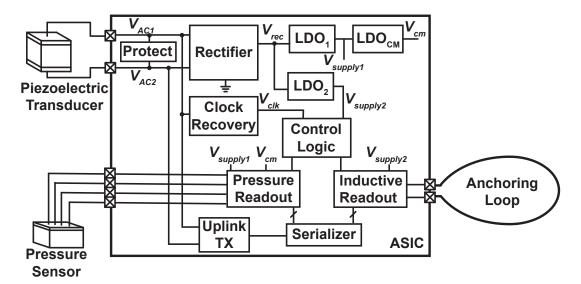

The proposed system requires low power consumption for remote powering and a small volume for implantation in the PA. As demonstrated in Fig. 1.3(c), the implantable system comprises a piezoelectric transducer, a piezoresistive pressure sensor, an application-specific integrated circuit (ASIC), and two conductive anchoring loops. Ultrasound is the most efficient method to power small-volume implants at great depths and achieves state-of-the-art performance in depth/volume ratio [44, 45]. In this thesis, a single piezoelectric transducer is used in the implant as a transceiver for both power harvesting and data communication. Piezoresistive pressure sensors, implemented as microelectromechanical systems (MEMS) and configured in a Wheatstone bridge, are widely used to measure pressure thanks to their small size and high accuracy [46, 47, 48, 49, 50, 51]. A miniature piezoresistive pressure sensor is employed to accurately measure the pressure. The ASIC consists of sensor readout circuits,

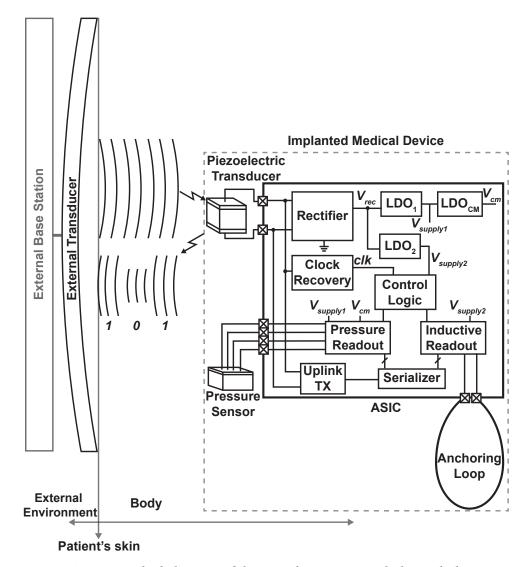

Figure 1.4: Block diagram of the complete system with the US link.

power management, and communication blocks. Implantable hemodynamic monitoring devices such as CardioMEMS<sup>TM</sup> and Cordella<sup>TM</sup> use nitinol-based anchoring loops for implant placement in the PA. This work employs conductive anchoring loops for both fixing the implant in the PA and measuring its cross-sectional area, by exploiting the inductive characteristic of the conductive anchoring loops.

Fig. 1.4 shows the complete system with the US link. An external transducer, which is an annular array transducer consisting of 10 rings, converts electrical power into acoustic power and transmits the acoustic power toward the implant. Hence, a second transducer, which is in the implant, converts the acoustic power into electrical power to energize the implanted device. Then, the implanted device sends the data relative to the sensor activity back to the external transducer by backscattering. The external base station is not in the scope of this thesis and waveform generators are used to drive the external transducer.

#### 1.3.2 System Specifications

Deep implantation of the proposed system in the PA presents certain physical limitations. To minimize blockage of blood flow in the PA, it is essential that the implant occupies a small volume. The dimensions of the implant are designed to be  $3.2~\text{mm} \times 2~\text{mm} \times 10~\text{mm}$ , which is comparable to FDA-approved implantable devices. Additionally, the system should consume low power for remote powering at great depths.

The system will be powered by ultrasound and must comply with FDA safety regulations, that is, the maximum acoustic intensity must not exceed 7.2 mW/mm $^2$  [52]. Since US signals experience low tissue attenuation [53], milliwatt power levels can be safely transferred. To stay safe within FDA regulations, the system's total power budget is aimed to be less than 100  $\mu$ W. The system requires significant implantation depths, which can range from 5 cm to 12 cm depending on the patient. For this study, the powering distance is set to be around 8.5 cm.

Patients are considered at risk for HFH if their pressures are higher than 35 mmHg for systolic, 15-20 mmHg for diastolic, and 20-25 mmHg for mean PAP [9]. To cover high-pressure limits and allow calibration for atmospheric pressure, the pressure range is selected to be from -135 mmHg to +135 mmHg. To achieve accurate PAP monitoring by detecting fast peaks of systolic and diastolic pressure changes, the pressure resolution is set to be higher than 0.5 mmHg, and the system's bandwidth ranges from 0 to 450 Hz. Therefore, the pressure readout circuit requires a 10-bit analog-to-digital converter (ADC) with a sampling rate of 1 kilosamples-per-second (kS/s). In a study involving 3171 volunteers [54], the mean PA diameter was measured to be  $25.1 \pm 2.8$  mm and can be as high as 30 mm. In addition, the lateral resolution of echocardiography, which is the clinical standard for artery CSA measurement, is typically around 1 mm [55]. As an improvement, the resolution of the diameter measurement is set to 0.25 mm in a diameter range from 20 mm to 30 mm. An oscillator-based inductive readout circuit is designed and uses a 12-bit counter to achieve sufficient resolution. The pressure readout creates a 10-bit output code per conversion while the inductive readout generates 12-bit output code. To cover the 22-bit sensor output and some additional bits for preambles, the data rate is set to 40 kilo-bits-per-second (kbps). Overall system specifications are summarized in Table 1.1. In order to meet these specifications, the ASIC was designed and fabricated using a 180-nm standard CMOS technology. This technology node is chosen thanks to its low cost and sufficiently high core and IO voltages to supply the piezoresistive sensors and power management circuits. Since the input voltage of the rectifier is always lower than 3.3 V peak-to-peak, there is no need to use a high-voltage (HV) CMOS technology.

#### 1.4 Thesis Contributions

The building blocks of the proposed system shown in Fig. 1.4 are presented in the following chapters. The main contributions of this thesis consist of proposing a novel energy-efficient bridge-to-digital converter enabling ultra-low conversion energy in piezoresistive sensor systems, an innovative system to directly measure the CSA of an artery based on the inductance

| Implant Volume (mm <sup>3</sup> ) | $3.2 \times 2 \times 10$ |

|-----------------------------------|--------------------------|

| Power Budget (μW)                 | 100                      |

| Powering Distance (cm)            | ~ 8.5                    |

| Pressure Range (mmHg)             | -135 to +135             |

| Pressure Resolution (mmHg)        | 0.5                      |

| Artery Diameter Range (mm)        | 20 to 30                 |

| Diameter Resolution (mm)          | 0.25                     |

| Data Rate (kbps)                  | 40                       |

Table 1.1: System specifications for the remote hemodynamic monitoring implant.

change of the implant's anchoring loops, a wireless ultrasonic power and data platform for powering and communication of deeply implanted medical devices, and a biocompatible and hermetic glass packaging approach for low-cost and long-lasting implants. In this collaborative work, Dr. Kerim Türe from the EPFL Radio Frequency Integrated Circuits Group designed the wireless powering and communication circuits, and some blocks of the inductive readout. The implantable and external piezoelectric transducers were designed and fabricated by IMASONIC, whereas Yalosys developed the glass package for the implant.

#### 1.5 Thesis Outline

This thesis is organized as follows:

- In Chapter 2, an energy and area-efficient capacitively-coupled chopper instrumentation amplifier (CCCIA) for implantable bridge sensor systems is proposed.

- In Chapter 3, an innovative energy-efficient bridge-to-digital converter for pressuresensing implants is presented. This chapter introduces a novel spinning method exploiting duty cycling to reduce the power consumption of the bridge sensor and the instrumentation amplifier (IA) while inherently cancelling the IA's offset and 1/f noise.

- In Chapter 4, a novel system for direct measurement of the artery CSA is proposed. This system exploits the inductive characteristic of an anchoring loop that mounts the implant in a branch of the artery.

- In Chapter 5, a wireless ultrasonic power and data platform is introduced for efficient powering and robust data communication of deeply implanted medical devices.

- In Chapter 6, a biocompatible and hermetic glass packaging approach is discussed and *in vitro* experimental results are presented.

- In Chapter 7, the thesis conclusion and potential future research are discussed.

## 2 Energy and Area-Efficient Capacitively-Coupled Chopper IA

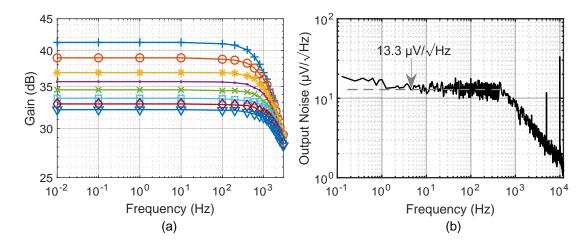

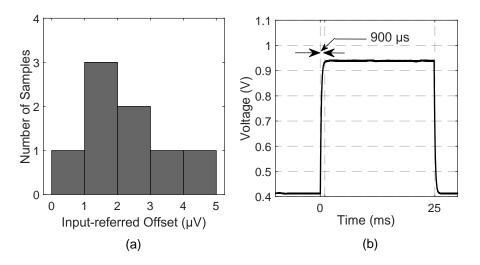

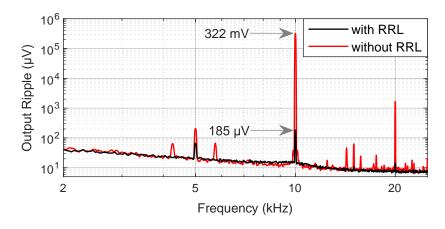

This chapter presents an energy and area-efficient capacitively-coupled chopper instrumentation amplifier (CCCIA) dedicated to implantable bridge sensor systems. Its target application is an implantable pressure sensing system used to measure the pulmonary artery pressure (PAP), which is particularly relevant for monitoring heart failure (HF) and pulmonary hypertension (PH) patients. The CCCIA employs chopper stabilization to decrease its offset and 1/f noise. The resulting ripple due to the up-modulated offset and 1/f noise is suppressed by a switched-capacitor (SC) ripple reduction loop (RRL). The gain of the instrumentation amplifier (IA) is defined by a programmable capacitive feedback network with a gain range from 40 V/V to 116 V/V, making it suitable for use with bridge sensors having different output voltages. The proposed CCCIA was designed and fabricated in a standard 180-nm CMOS technology. It achieves an input-referred noise density of 88.2 nV/ $\sqrt{\text{Hz}}$ , a worst-case input offset of 5 µV, and a noise efficiency factor (NEF) of 6.2 while drawing 3.3 µA current from a 1.2 V supply. The SC RRL suppresses the output ripple to less than 185 µV at all harmonics. The CCCIA achieves state-of-the-art performance in terms of small area, occupying only 0.17 mm<sup>2</sup>. The results make the system suitable for implantable bridge sensor systems. Some parts of this chapter were published in [56, 57].

This chapter is organized as follows: Section 2.1 provides an overview of instrumentation amplifiers. Section 2.2 describes the design and implementation of the proposed CCCIA, whereas the details of the implemented ripple reduction loop are presented in Section 2.3. Section 2.4 summarizes the measurement results and Section 2.5 concludes the chapter.

#### 2.1 Overview of Instrumentation Amplifiers

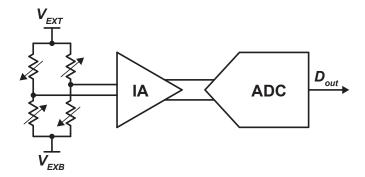

Instrumentation amplifiers are commonly used to detect low-amplitude signals from sensors. A typical implantable sensing system is composed of a bridge sensor and its readout circuit, which consists of an IA followed by an analog-to-digital converter (ADC). Fig. 2.1 shows the conventional readout circuit for piezoresistive sensors configured in a Wheatstone bridge. To accurately amplify low-amplitude output signals of sensors in an energy-efficient way, the IA

Figure 2.1: Conventional readout circuit for Wheatstone bridge sensors.

should have low offset, low noise, and low power consumption [58, 51, 59, 60, 61, 62, 63]. Since most sensor applications operate near DC with a bandwidth of a few hundred Hz, the IA's offset and 1/f noise significantly degrade the amplifier performance. Fig. 2.2 shows the low-frequency noise spectrum of CMOS amplifiers. The worst-case offset of a CMOS differential amplifier can be as large as 10 mV. Additionally, the 1/f noise dominates the low-frequency spectrum and is inversely proportional to the frequency, with a typical 1/f noise corner of a few kHz to tens of kHz [64]. To achieve accurate and energy-efficient measurements, several techniques such as auto-zeroing, correlated double sampling, and chopping have been used for low-frequency noise and offset cancellation [64]. The chopping technique is superior to other techniques since it provides a continuous-time output and does not cause noise folding. Moreover, it is more energy-efficient than other dynamic offset cancellation techniques.

The IA determines the system's energy efficiency since the main noise contribution comes from its input stage. The classic 3-Opamp IA and the current-feedback IA have two noise-critical input stages, while the capacitively-coupled IA (CCIA) has only one [65]. Therefore, the CCIA delivers the best performance in terms of both accuracy and energy efficiency [62]. It achieves a high gain accuracy without any extra cost since on-chip capacitors have excellent matching characteristics. In addition, the input capacitors of the CCIA block the common-mode (CM) input voltages of the Wheatstone bridge and allow using different supply voltages for the resistive bridge and the readout circuit [50].

Although the capacitively-coupled chopper instrumentation amplifier provides highly accurate and energy-efficient measurements, it has two main drawbacks. Firstly, the up-modulated offset and 1/f noise of the amplifier generates a large ripple at the output of the IA. Several ripple-reduction techniques have been proposed to suppress the output ripple [62, 66, 67, 68]. Secondly, the chopping technique reduces the input impedance of the IA to less than 10 M $\Omega$  at typical chopping frequencies. This input impedance is high enough for most of the resistive bridges since their equivalent resistances are usually lower than 10 k $\Omega$ . For the applications requiring very-high input impedance, a positive feedback loop has been proposed to boost the CCCIA's input impedance [62].

Figure 2.2: Low-frequency noise spectrum for CMOS amplifiers.

#### 2.2 Design of an Energy and Area-Efficient CCCIA

An energy and area-efficient CCCIA was designed and implemented to be used in implantable bridge sensor systems. It amplifies the output of a bridge sensor accurately and energy-efficiently to profit from the full input range of the succeeding ADC.

#### 2.2.1 Topology and Design Considerations

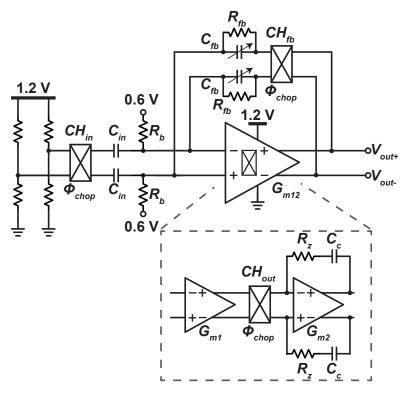

Fig. 2.3 shows the schematic of the CCCIA consisting of a two-stage Miller-compensated operational transconductance amplifier (OTA) ( $G_{m1}$  and  $G_{m2}$ ), a programmable capacitive feedback network to set the gain ( $C_{in}$  and  $C_{fb}$ ), three chopper switches ( $CH_{in}$ ,  $CH_{out}$  and  $CH_{fb}$ ), and high-value pseudo-resistors ( $R_b$  and  $R_{fb}$ ) to set input common-mode (CM) level. The IA's gain is accurately defined by  $C_{in}/C_{fb}$ , where  $C_{fb}$  are 3-bit programmable capacitor arrays. It is a 3-bit controlled variable gain amplifier (VGA) that enables tuning the input range of the IA for different bridge sensors and avoids the saturation of the IA output arising from the bridge offset.

Chopper modulation enables the cancellation of the amplifier's 1/f noise and input offset. The DC and low-frequency signals at the output of the bridge are converted to higher-frequency AC signals by input chopper switches  $(CH_{in})$  and then capacitively coupled to the input of  $G_{m1}$ . The up-modulated input signals are amplified by  $G_{m1}$  and then demodulated back to the baseband by output chopper switches  $(CH_{out})$ , while the 1/f noise and offset of  $G_{m1}$  is up-modulated away from the signal band. As a result, the IA can achieve very low input noise and input offset, thus enabling a high accuracy at low frequencies [64]. Thanks to  $G_{m1}$ 's high gain, the noise and offset contributions of the following stages are negligible. The DC gain  $(A_0)$  of the OTA is designed to be larger than 100 dB to achieve a high gain accuracy. In order to obtain such a high gain, a two-stage Miller compensated amplifier is employed  $(G_{m1})$  and  $G_{m2}$ .

Figure 2.3: Schematic of the CCCIA with a bridge sensor.

Chopper stabilization provides continuous-time operation and can achieve microvolt offset and very low 1/f noise. However, this technique has two main drawbacks. Firstly, the upmodulated offset and 1/f noise of  $G_{m1}$  inevitably appear as an output ripple. The amplitude of the ripple can be estimated [62] by

$$V_{ripple} = \frac{V_{os} \times G_{m1}}{2 \times f_{chop} \times C_c},\tag{2.1}$$

where  $V_{os}$  is  $G_{m1}$ 's offset. The output ripple voltage can consume too much headroom at low supply voltages and has to be removed. Thus, this ripple is suppressed by an additional ripple reduction loop (RRL). Secondly, the input impedance of the CCCIA at DC is defined [62] by a switched-capacitor (SC) resistor formed by  $CH_{in}$  and input capacitors ( $C_{in}$ ):

$$Z_{in,DC} = \frac{1}{2 \times f_{chop} \times C_{in}}. (2.2)$$

Since  $C_{in}$  is usually in the order of a few pF, the input impedance of a chopped amplifier is limited to ~10 M $\Omega$ , which is lower than the DC input impedance of non-chopped amplifiers.

The chopper frequency,  $f_{chop}$ , is one of the most important design parameters. It must be higher than the 1/f noise corner of  $G_{m1}$  to eliminate the 1/f noise completely. On the

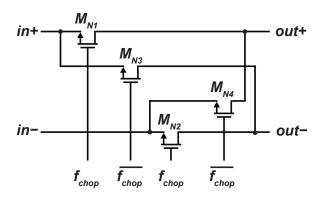

Figure 2.4: Schematic of a chopper switch based on four NMOS transistors.

other hand, the charge injection and clock feedthrough at the  $CH_{in}$  lead to a residual offset proportional to  $f_{chop}$  [64]. Therefore,  $f_{chop}$  must be carefully chosen since increasing  $f_{chop}$  reduces the input noise but also increases the residual offset. In addition, increasing  $f_{chop}$  reduces the amplitude of the output ripple whereas it decreases the DC input impedance of the CCCIA. Therefore, the chopper frequency has to be carefully selected in a precise frequency range.

## 2.2.2 Implementation

The chopper frequency is selected to be 10 kHz in order to be higher than the 1/f noise corner frequency of  $G_{m1}$  and to be low enough to achieve a low residual offset and high input impedance. To apply chopper modulation and demodulation, polarity-reversing chopper switches are implemented. As shown in Fig. 2.4, the chopper switches are made of four NMOS switches driven by clock signals with two complementary phases at  $f_{chop}$ . The size of the NMOS switches should be minimized to suppress the charge injection and clock feedthrough errors [64]. However, the noise of the on-resistor of the input chopper switches has to be low enough for low-noise operation. As a compromise, NMOS switches with a width (W) of 880 nm and length (L) of 180 nm are employed. In order to achieve effective offset cancellation, the two complementary chopping clocks must have a 50% duty cycle and have transitions at the same time. A D-flip-flop-based divider-by-two circuit is placed very close to each chopper switch to ensure a 50% duty cycle[69]. Two buffers are used at the outputs of clock dividers to drive the nearby chopper switches with complementary clock signals having very low rise and fall times.

The gain of the CCCIA is defined by the capacitive ratio  $C_{in}/C_{fb}$ . The feedback capacitors are programmed by 3 configuration bits and the gain settings are 40, 44, 48, 54, 69, 80, 96, and 116 V/V, thus making the IA flexible for different bridge sensors. Apart from  $f_{chop}$ , the value of input capacitors,  $C_{in}$ , is also an important design parameter. It has to be minimized to save the chip area and to keep the input impedance of the CCCIA as high as possible. In addition, the transient settling of the CCCIA is limited by the time constant determined by the pseudo

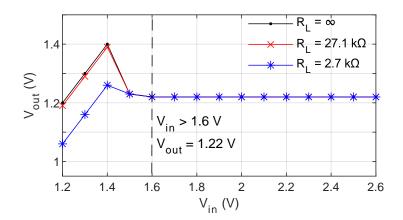

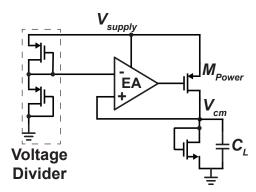

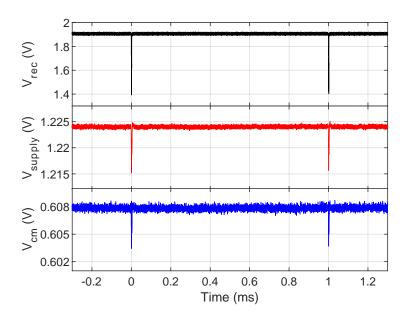

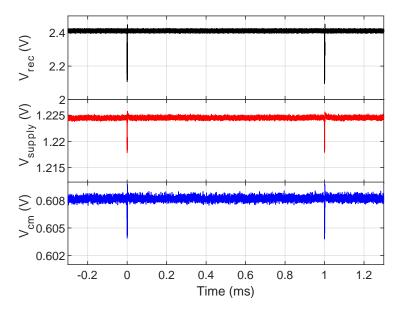

Figure 2.5: Schematic of (a) the two-stage Miller OTA ( $G_{m1}$  and  $G_{m2}$ ) with (b) two seperate CMFB circuits.