# Compilation and Design Space Exploration of Dataflow Programs for Heterogeneous CPU-GPU Platforms

Présentée le 9 juin 2023

Faculté des sciences et techniques de l'ingénieur Groupe SCI STI MM Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

# Aurélien François Gilbert BLOCH

Acceptée sur proposition du jury

Dr J.-M. Sallese, président du jury Dr M. Mattavelli, directeur de thèse Prof. J.-F. Nezan, rapporteur Dr M. Raulet, rapporteur Prof. A. Burg, rapporteur

# Acknowledgements

I would like to start by expressing my gratitude to my thesis advisor, Dr. Marco Mattavelli, for the opportunity to pursue my own research topic and for his support throughout this thesis.

Additionally, I extend my thanks to the members of my thesis committee, Dr. Jean-Michel Sallese, Prof. Andreas Burg, Prof. Jean-François Nezan, and Dr. Mickaël Raulet for their feedback, constructive criticism, and expert evaluation of my work.

I would also like to extend my appreciation to both Dr. Endri Bezati and Dr. Simone Casale Brunet for their valuable technical guidance at various stages of my thesis.

I would like to thank all past and current members of the SCI-STI-MM group, especially my colleagues Ana Hernandez-Lopez, Ünsal Öztürk, and Mustafa Beşirli for these long debate and discussion fueled with coffee that made this long journey more interesting. A warm thank you goes to our lab secretary, Daniela Vallat, for bringing the lab together.

I am very lucky to have great circles of friends both in France and in Switzerland and I would like to thank them all for their affection along this difficult endeavor. A truly special recognition goes to my closest friends Léa Prost and Chiara Ercolani for their tremendous and unwavering moral support without which this thesis would not have been completed.

I would like to express loving thanks to my partner Lucy Fitzgerald for her support during the final stretch of this thesis, which allowed me to gain perspective.

Last but not least, I have to sincerely express my love to all members of "La famille proche" but of course more specifically to my parents Florence and Jean-Sébastien Bloch without whom I wouldn't be there today both literally and figuratively for their love, and infinite support all along my studies.

Lausanne, April 28, 2023

Aurelien Bloch

# **Abstract**

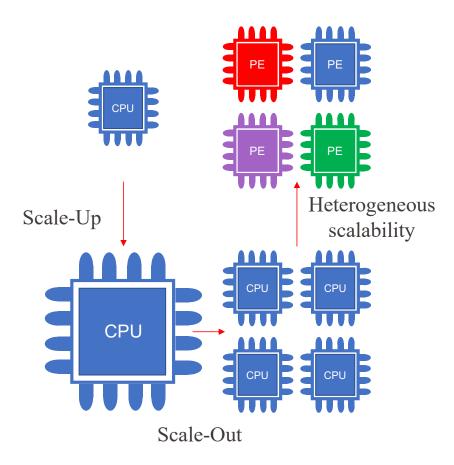

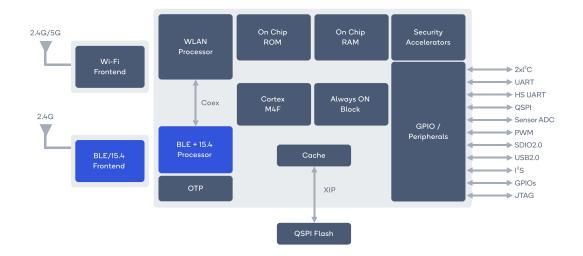

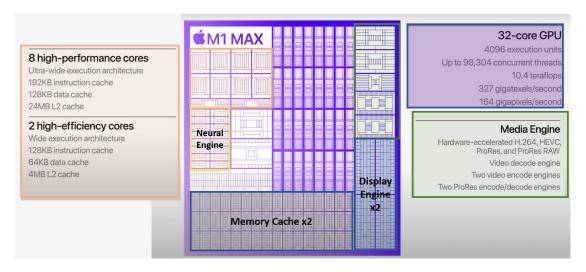

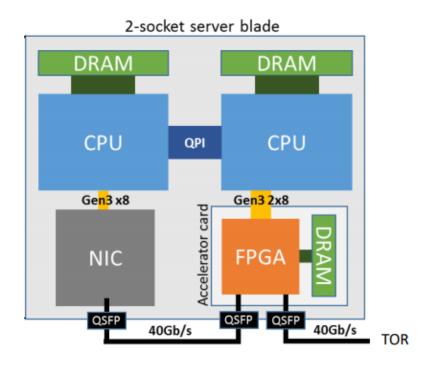

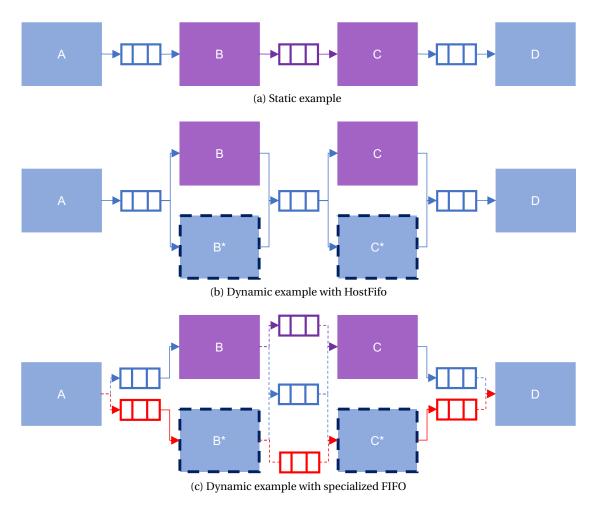

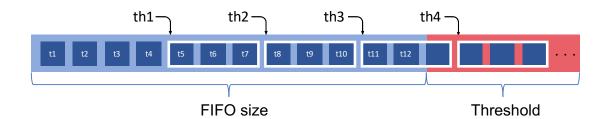

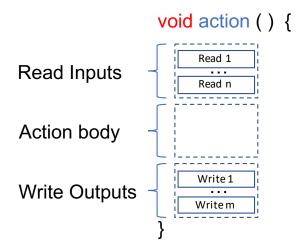

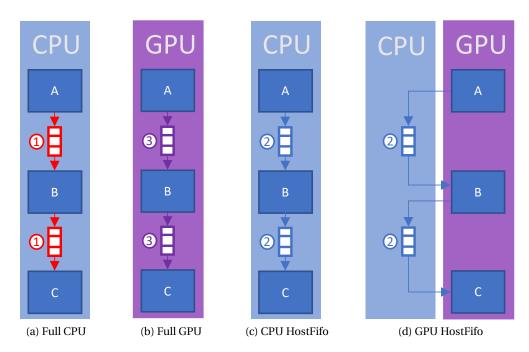

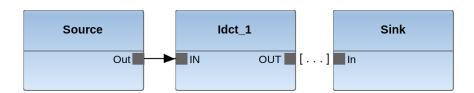

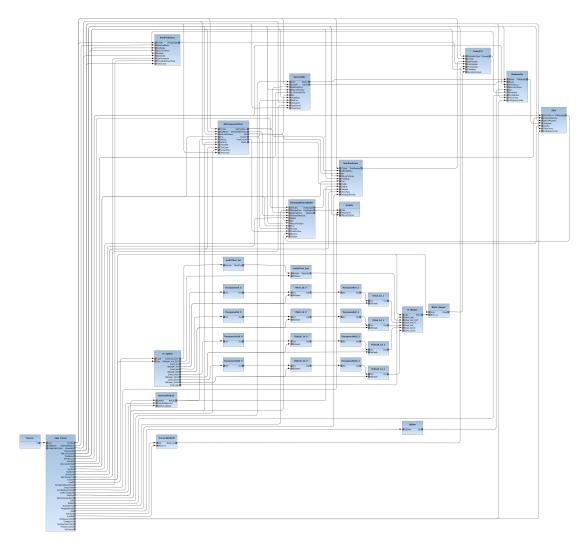

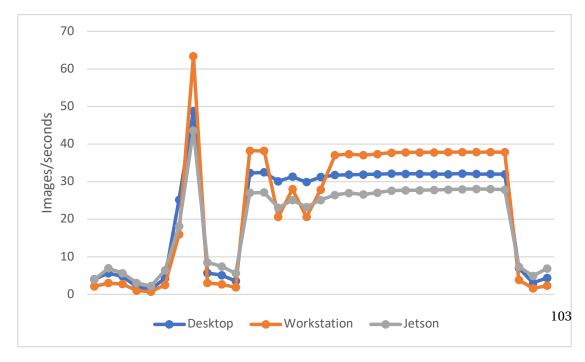

Today's continued increase in demand for processing power, despite the slowdown of Moore's law, has led to an increase in processor count, which has resulted in energy consumption and distribution problems. To address this, there is a growing trend toward creating more complex heterogeneous systems where multicore, many-core, GPU, FPGA, and DSPs are combined in a single system. This poses challenges in terms of how to take advantage of such systems and how to efficiently program, evaluate, and profile applications where sub-components run on different hardware. Dataflow programming languages like RVC-CAL have proven to be an appropriate methodology for achieving such a complex goal due to their intrinsic portability and the ability to easily decompose a network of actors on different processing units, matching the heterogeneous hardware. Previous research has shown the efficacy of this methodology for systems combining multicore, many-core, CPU, FPGAs, and others. It has also been shown that the performance of programs executed on heterogeneous parallel platforms largely depends on the design choices regarding how to partition the computation on the various processing units. In other words, it depends on the parameters that define the partitioning, mapping, scheduling, and allocation of data exchanges among the various processing elements of the platform executing the program. The advantage of programs written in languages using the dataflow model of computation is that executing the program with different configurations and parameter settings does not require rewriting the application software for each configuration but only requires launching a new generation of the execution code corresponding to the parameters, using automatic generation tools. Another competitive advantage of dataflow software methodologies is that they are well-suited to support designs on heterogeneous parallel systems as they are inherently free of memory access contention issues and naturally expose the available intrinsic parallelism. However, it is still an open research question whether dataflow programming languages such as RVC-CAL can fit with massively parallel SIMD architecture such as GPUs. Recent GPU architectures make available numbers of parallel processing units that exceed by orders of magnitude the ones offered by CPU architectures. While programs written using dataflow programming languages are well-suited for programming parallel heterogeneous systems, they may not offer sufficient parallel degrees to efficiently exploit the resources available on today's GPUs. Furthermore, the dynamic nature of the RVC-CAL model may conflict with the very rigid SIMD pipeline. The objective of this thesis is to develop a full suite of tools using the dataflow programming language RVC-CAL to provide an automated design flow for programming, analyzing, and optimizing application programs running on CPU/GPU heterogeneous systems. The main contribu-

#### **Abstract**

tions of this thesis are the development of a high-level compiler infrastructure that targets CPU/GPU heterogeneous processing platforms and supports the full specification of the RVC-CAL dataflow programming language, facilities for generating instrumented applications for profiling purposes, and a set of design space exploration pipelines to automatically optimize the resulting application by suggesting performant partition and mapping configurations.

**Key words**: dynamic dataflow, source-to-source compiler, RVC-CAL, heterogeneous CPU-GPU systems, SIMD, parallel computing, profiling, performance estimation, design space exploration.

# Résumé

L'augmentation continue de la demande en puissance de calcul, et ce malgré le ralentissement de la loi de Moore, a conduit à une augmentation du nombre de processeurs, ce qui a entraîné des problèmes de consommation et de distribution d'énergie. Pour remédier à cela, il y a une tendance croissante à la création de systèmes hétérogènes plus complexes où les processeurs multicore, many-core, GPU, FPGA et DSP sont combinés dans un seul système. Cela pose des défis en termes d'utilisation de ces systèmes, de programmation efficace, d'évaluation et de profilage des applications dans lesquelles les sous-composants s'exécutent sur différents matériels. Les langages de programmation de flux de données tels que RVC-CAL se sont avérés être une méthodologie appropriée pour atteindre un tel objectif en raison de leur portabilité intrinsèque et de leur capacité à décomposer facilement un réseau d'acteurs sur différentes unités de traitement, correspondant aux systemes hétérogènes. Des recherches antérieures ont montré l'efficacité de cette méthodologie pour des systèmes combinant des processeurs multicore, many-core, FPGA et autres. Il a également été démontré que les performances des programmes exécutés sur des plates-formes parallèles hétérogènes dépendent largement des choix de conception concernant la manière de partitionner le traitement sur les différentes unités de calculs. En d'autres termes, cela dépend des paramètres qui définissent le partitionnement, l'assignement, l'ordonnancement et l'allocation des échanges de données entre les différents éléments de traitement de la plate-forme exécutant le programme. L'avantage des programmes écrits dans des langages utilisant le modèle de calcul en flux de données est que l'exécution du programme avec différentes configurations et paramètres ne nécessite pas de réécrire le logiciel pour chaque configuration, mais nécessite simplement de lancer une nouvelle génération du code d'exécution correspondant aux paramètres, en utilisant des outils de génération automatique. Un autre avantage concurrentiel des méthodologies de logiciels de flux de données est qu'elles conviennent bien à la prise en charge de conceptions sur des systèmes parallèles hétérogènes car elles sont exemptes de problèmes de contention d'accès mémoire et exposent naturellement le parallélisme intrinsèque disponible. Cependant, il s'agit encore d'une question de recherche ouverte de savoir si les langages de programmation de flux de données tels que RVC-CAL peuvent s'adapter aux architectures SIMD massivement parallèles constituent les GPU. En effet, les architectures GPU récentes mettent à disposition des nombres d'unités de traitement parallèles qui dépassent de plusieurs ordres de grandeur ceux offertes par les architectures CPU. Bien que les programmes écrits à l'aide de langages de programmation de flux de données soient bien adaptés à la programmation de systèmes hétérogènes parallèles, ils peuvent ne pas offrir suffisamment de degrés de parallélisme pour

exploiter efficacement les ressources disponibles sur les GPU actuels. De plus, la nature dynamique du modèle RVC-CAL peut entrer en conflit avec la rigidité du pipeline SIMD. L'objectif de cette thèse est de développer une suite complète d'outils utilisant le langage de programmation de flux de données RVC-CAL pour fournir un processus de développement automatisé pour la programmation, l'analyse et l'optimisation de programmes s'exécutant sur des systèmes hétérogènes CPU/GPU. Les principales contributions de cette thèse sont le développement d'une infrastructure de compilateur de haut niveau qui cible les plates-formes de traitement hétérogènes CPU/GPU et prend en charge la spécification complète du langage de programmation de flux de données RVC-CAL, des fonctionnalités pour générer des applications instrumentées à des fins de profilage, et un ensemble d'options pour l'exploration de l'espace de design pour optimiser automatiquement l'application résultante en suggérant des configurations de partitionnement et de d'assignement performantes.

**Mots clefs** : flux de données dynamique, compilateur de source à source, RVC-CAL, systèmes hétérogènes CPU-GPU, SIMD, calcul parallèle, profilage, estimation de performance, exploration de l'espace de conception.

# **Contents**

| Ac | knov  | vledgements                                                  | j            |

|----|-------|--------------------------------------------------------------|--------------|

| Li | st of | Figures                                                      | xi           |

| Li | st of | Tables                                                       | XV           |

| Li | st of | Listings                                                     | <b>xvi</b> i |

| 1  | Intr  | oduction                                                     | 1            |

|    | 1.1   | Programming Heterogeneous Systems                            | 1            |

|    | 1.2   | Problem Statement and Motivation                             | 2            |

|    | 1.3   | Challenges of Dataflow Synthesis on GPUs                     | 4            |

|    | 1.4   | Research Contributions                                       | 5            |

|    | 1.5   | Thesis Organization                                          | 6            |

| 2  | Stat  | e of the Art and Background                                  | 9            |

|    | 2.1   | Introduction                                                 | 9            |

|    | 2.2   | Heterogeneous Platforms                                      | 11           |

|    |       | 2.2.1 Systems Overview                                       | 11           |

|    |       | 2.2.1.1 Embedded System                                      | 11           |

|    |       | 2.2.1.2 General Computing System                             | 12           |

|    |       | 2.2.1.3 Data Center                                          | 13           |

|    |       | 2.2.2 GPU Systems                                            | 13           |

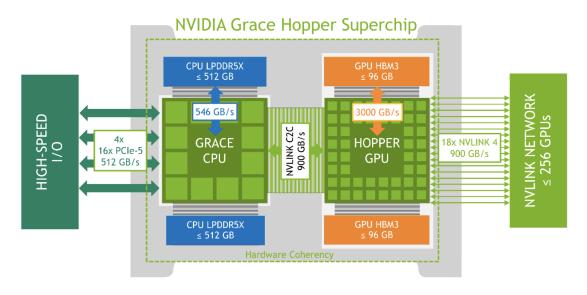

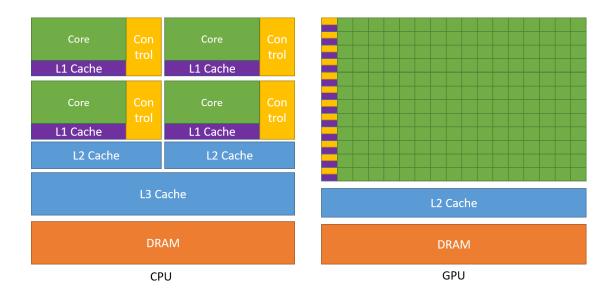

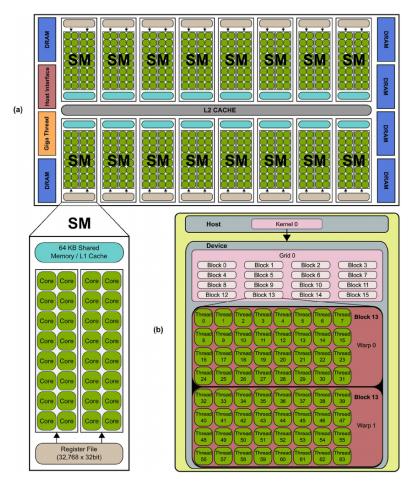

|    |       | 2.2.3 NVIDIA Architecture                                    | 15           |

|    | 2.3   | Software Development Framework                               | 16           |

|    |       | 2.3.1 Development Framework for CPU/GPU Programming          | 16           |

|    |       | 2.3.2 Dataflow Development Framework for CPU/GPU Programming | 17           |

|    | 2.4   | Design Space Exploration                                     | 20           |

|    | 2.5   | Conclusion                                                   | 20           |

| 3  | Dat   | aflow Programming                                            | 23           |

|    | 3.1   | Introduction                                                 | 23           |

|    | 3.2   | Dataflow Model of Computation                                | 24           |

|    |       | 3.2.1 Kahn Process Networks                                  | 24           |

|    |       | 3 2 1 1 Kahn Process                                         | 25           |

## **Contents**

|   |      |       | 3.2.1.2 Monotonicity and Continuity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25         |

|---|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |      | 3.2.2 | Dataflow Process Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26         |

|   |      |       | 3.2.2.1 Actor with Firings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26         |

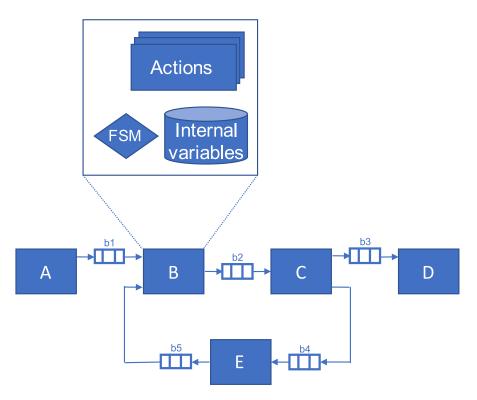

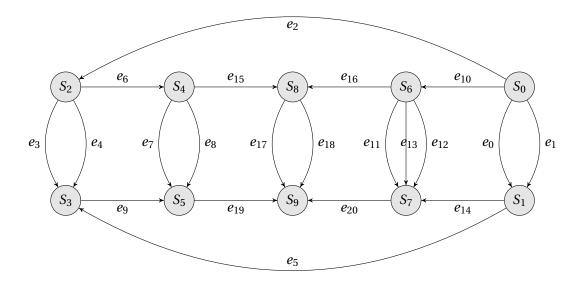

|   |      | 3.2.3 | Actor Transition System and Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27         |

|   |      |       | 3.2.3.1 Enabled Transition and Step of an Actor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27         |

|   |      |       | 3.2.3.2 Actors Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82         |

|   | 3.3  | CAL A | ctor Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82         |

|   |      | 3.3.1 | Formal Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30         |

|   |      | 3.3.2 | Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30         |

|   |      | 3.3.3 | Syntax and Semantic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32         |

|   |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32         |

|   |      |       | 3.3.3.2 Actors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32         |

|   |      |       | 3.3.3.3 Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33         |

|   |      |       | 3.3.3.4 Guards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33         |

|   |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34         |

|   |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34         |

|   |      | 3.3.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35         |

|   | 3.4  | Open  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88         |

|   | 3.5  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1          |

|   |      | 3.5.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12         |

|   |      | 3.5.2 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13         |

|   |      | 3.5.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>!</b> 5 |

|   |      | 3.5.4 | Design Space Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ŀ7         |

|   | 3.6  | Concl |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50         |

|   |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

| 4 | Higl |       | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1          |

|   | 4.1  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51         |

|   | 4.2  | CUDA  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51         |

|   |      | 4.2.1 | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51         |

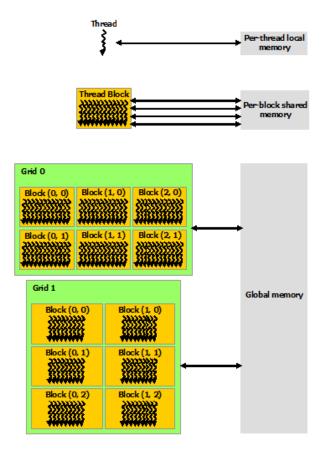

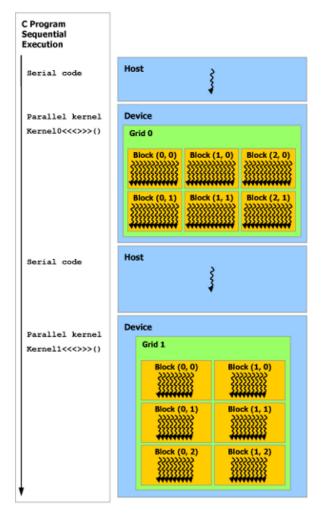

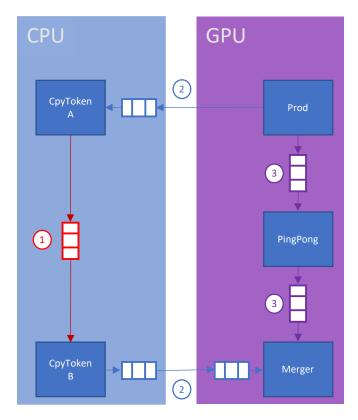

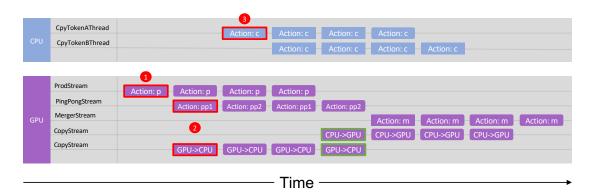

|   |      | 4.2.2 | CUDA Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52         |

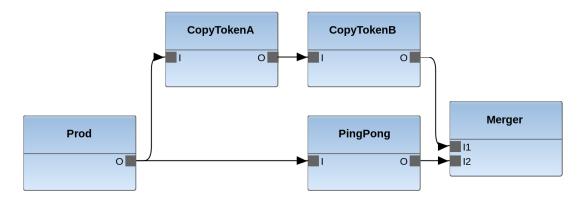

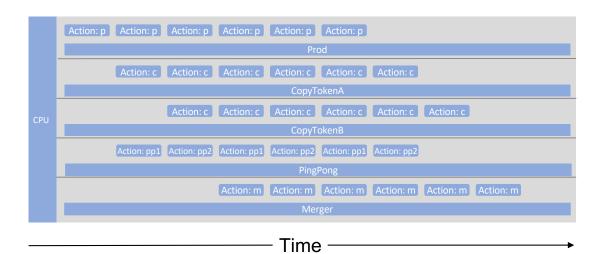

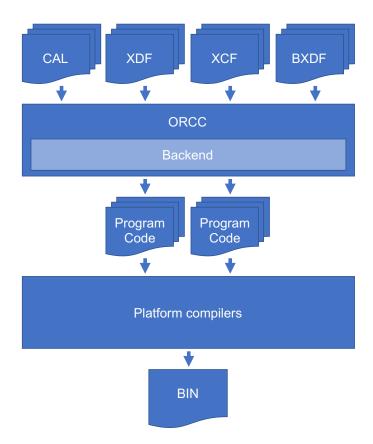

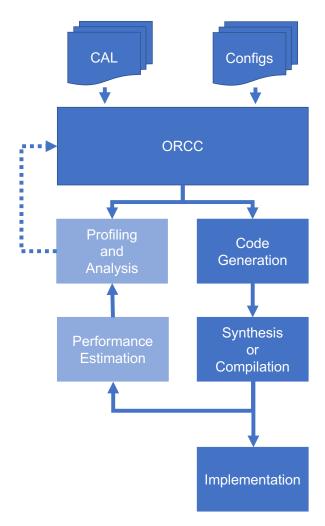

|   | 4.3  | Mode  | o contract of the contract of | 6          |