# Modelling and design of CMOS SPAD sensors for quantum random number generation

Présentée le 1er juin 2023

Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Pouyan KESHAVARZIAN

Acceptée sur proposition du jury

Prof. D. Atienza Alonso, président du jury

Prof. E. Charbon, Dr M. Stipcevic, directeurs de thèse

Prof. F. Regazzoni, rapporteur

Dr L. Gasparini, rapporteur

Prof. K. Choo, rapporteur

Attention is a state of openness that assumes there is something new to be seen, it is also true that this state must resist our tendency to declare our observations finished—to be done with it.

— Jenny Odell

Anyone who considers arithmetical methods of producing random digits is, of course, in a state of sin.

— John von Neumann

زن زندگی آزادی

To Mali.

## Acknowledgements

Over the course of my graduate studies, I have had the great privilege of meeting, working, exploring, and celebrating with a number of extraordinary professionals. This story that has passed with many highs and lows, it is now time to express my gratitude for all who have been a part of the journey. First, to my thesis director, Prof. Edoardo Charbon and my thesis co-director Dr. Mario Stipčević. Edoardo, you pushed me to seize opportunities but also gave me the freedom to explore, which I am grateful for. Mario, I was quite 'green' in terms of QRNGs at the start, so without your breadth of knowledge, this work would not have been possible. Also, to my M.Sc. supervisors, Prof. Michal Okoniewski and Prof. John Nielsen back home in Calgary, thank you for inspiring me to pursue research in the first place.

I arrived at AQUA lab in February 2019, on the heels of what was, by all accounts, the greatest Christmas party of all time. I slowly met the organizers of that party (my colleagues), many of whom have become close friends and confidants. In the early days, the old alumni of Delft set the standard for quality and culture. A special thank you to Ivan Michel Antolovic and Augusto Carimatto for helping me find my bearings in the beginning and for your kind friendship as time went on. Another special thank you to Francesco Gramuglia and Ekin Kizilkan for the rock-solid collaboration we had together on the 55 nm project. On Fridays au Galop, a newer generation of colleagues, Ming-Lo Wu, Paul Mos, Baris Can Efe, Halil Kerim Yildirim, Yang Lin, Vladimir Pesic, Tommaso Milanese, Utku Karaca, Emanuele Ripiccini, Jad Benserhir, Feng Liu, Won-yong Ha and others, came together for beers, burgers and chess, which was always good fun. Thank you Arin Ulku, Ermanno Bernasconi, Preethi Padmanabhan, Carlo Alberto Fenoglio, Andrei Ardelean, Andrada Muntean, Michael Wayne, Scott Lindner, Jiuxuan Zhao, Simone Frasca, Kodai Kaneyasu, Chufan Zhou, Kazuhiro Morimoto, and Yasemin Uzun, Yating Zou. It has been a pleasure getting to know you all. To my friends Bedirhan Ilik and Andrea Ruffino, I've cherished our many discussions, laughs and adventures around Switzerland. Thank you also to Claudio Bruschini, Samuel Burri and the team at Qrypt for the collaborations that led to the development of the QRNG sensors. In this same vein, I would like to thank GlobalFoundries and the team in Singapore for the excellent opportunity to develop SPADs in the 55 nm BCD process, along with Myung-Jae Lee and the group at KIST for collaborating on this project. I owe a huge debt of gratitude to the two lab administrators at AQUA, Brigitte Khan, and her successor, Begonia Tora, for all the help. kindness and professionalism, over the years.

It's certainly not an exaggeration to say that, in early 2020, the world changed in a way that our generation has not yet experienced. Covid-19 turned the *train-train-quotidien* into *restez-chez-vous*. The process of professional and personal adaptation was frustrating, anxiety-ridden,

long and uncertain. What's more, it also just happened to coincide with a period of great personal difficulty. Not to mention that, as PhD students in the field of microelectronics, we had to adapt to the resulting 'chip shortage' and 'semiconductor crisis' (still waiting on those level shifters ordered in 2021...). Getting through this stretch would not have been possible without the support of my friends and family (those weekend calls/Zooms were fundamental). Maman, Baba, Naz, Bryce, Leila, Mina, thank you for your love, encouragement and support. To my dear friends back home and across the globe, Brett, Rebecca, Stephen, Ally, Cassie, Megan, Jules, Mike, Michael, Marie, and Amar, you know I can't express how grateful I am for you all. And of course to Auntie Sanja, Uncle Anuj and Nimaya, I'm so blessed to have your consistent, loving presence.

Switzerland is a country that is unique and wonderful in many ways. One of those is the existence of four national languages. Although not initially concerned with the challenge (hubris) of not speaking a word of any of those languages, I quickly learned the daunting struggle (humbled) of such an endeavor. I'm grateful for my french teacher, Abigail, who put up with my constant, « J'ai pas eu le temps de faire mes devoirs cette semaine...» and patiently helped me rectify (at least to some extent) my language deficiency.

Finally, and most importantly, to my partner-in-crime, Malithi. You have been part of this journey since Day 1 (in fact, since Day 1 of undergrad). Whether it was weekend trips from GVA to LBA, or the TGV between Lausanne and Gare de Lyon, we hustled relentlessly to prioritize each other along the way. Your love and care during the lowest of the lows, your ability to drive many of our joint projects (including the wedding), your patience with the years-long journey, your reminders to stay persistent in the face of adversity, and of course, your passion for the adventure, has made it all possible.

Neuchâtel, 09 March 2023

P. K.

### Abstract

Modern digital connectivity has necessitated the creation of robust methods for securely storing and transferring data. At the heart of all security infrastructure is the random number generator (RNG). While random numbers find use in a variety of applications, from scientific simulation to gambling, it is in the hardware security domain, where their performance is most critical. As a fundamental security primitive, the requirements for an RNG are exhaustive. Any practical RNG realization, which extracts entropy from a physical source of randomness, requires intensive modelling, characterization and robustness against environmental changes and adversarial attacks. Existing implementations often rely on heavy levels of post-processing of the digital bits produced to meet performance requirements. Furthermore, with the advent of Quantum Computing, which promises to shatter the security of many existing encryption protocols, the demands placed on RNG designs is fortifying considerably. Quantum random number generators (RNGs) hope to meet those demands. A variety of techniques, that exploit various quantum mechanical phenomena, can be used to generate random numbers. However, many require complex, bulky setups that are not amenable to small form factor implementations or scalability. Single-photon avalanche diodes (SPADs) are a CMOS-compatible modern detector technology enabling versatile sensing of optical photons. SPAD-based sensors, which have the ability to co-integrate a myriad of digital timing and processing functions, are a promising potential solution for QRNG implementations.

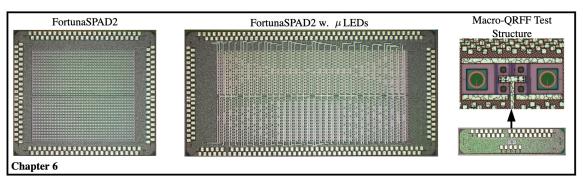

This thesis focuses on modelling and design of quantum random bit generators in a 55 nm Bipolor-CMOS-DMOS (BCD) process. First, several new detectors are developed in a 55 nm BCD process. Effective optimization of the designs, without changes to the standard process, are proposed and tested, resulting in excellent noise and sensitivity performance. These detectors are then combined with pixel circuits that exploit photon-timing statistics for generation of random bits. Intensive modelling on bias and system modelling are performed. In particular, an analytical method for determining serial correlation of bits, when considering detector dead time and afterpulsing, is proposed and validated by way of simulation and experiments. Based on the analysis of bias, a dynamic comparator based sampling flip-flop approach, for reduction of bit bias, is introduced as a component in a quantum random flip-flop (QRFF), configuration. This method is compared and contrasted to a first photon-arrival comparison bit generation method. The designs are scaled to SPAD sensor arrays that, when combined with external illumination, function as gigabit-per-second QRNGs. The FortunaSPAD QRNG is a dual-interface design, capable of a combined output data rate of

$3.3~\mathrm{Gbps}$ . The FortunaSPAD2 QRNG sensor implements a macro-pixel design to improve robustness against pixel failure.

Key words: Random number generation, quantum random number generation, single-photon avalanche diodes, hardware security, BCD technology, pixel-electronics, dead time modelling, afterpulsing effects, quantum random flip-flop.

### Résumé

La connectivité numérique moderne a nécessité la création de méthodes robustes pour stocker et transférer des données en toute sécurité. Au cœur de toute infrastructure de sécurité se trouve le générateur de nombre aléatoires (GNA). Alors que les chiffres aléatoires trouvent une utilisation dans une variété d'applications, comme de la simulation scientifique au jeu de hasard, c'est dans le domaine de la cryptographie que leurs performances sont les plus critiques. En tant que primitive de sécurité fondamentale, les exigences pour un GNA sont exhaustives. Toute réalisation GNA pratique, qui extrait l'entropie d'une source physique aléatoire, nécessite une modélisation, une caractérisation et une robustesse intensives contre les changements environnementaux et les attaques adverses. Les implémentations existantes reposent souvent sur des niveaux élevés de post-traitement des chiffres numériques produits pour répondre aux exigences de performances. De plus, avec l'avènement de l'informatique quantique, qui promet de briser la sécurité de nombreux protocoles de cryptage existants, les exigences imposées aux conceptions GNA se renforcent considérablement. Les générateurs de nombres aléatoires quantiques (GNAQ) espèrent répondre à ces demandes. Une variété de techniques, qui exploitent divers phénomènes de mécanique quantique, peuvent être utilisées pour générer des nombres aléatoires. Cependant, beaucoup nécessitent des configurations complexes et volumineuses qui ne se prêtent pas à des implémentations ou à une évolutivité à petit facteur de forme. Les diodes diode à avalanche monophotonique sont une technologie de détection moderne compatible avec CMOS, qui permet une détection polyvalente des photons optiques. Les capteurs basés sur SPAD, qui ont la capacité de co-intégrer une myriade de fonctions de synchronisation et de traitement numériques, constituent une solution potentielle prometteuse pour les implémentations GNAQ.

Cette thèse porte sur la modélisation et la conception de générateurs de nombres aléatoires quantiques dans un processus Bipolaire-CMOS-DMOS (BCD) 55 nm. Tout d'abord, plusieurs nouveaux détecteurs sont développés dans un procédé BCD à 55 nm. Une optimisation efficace des conceptions, sans modification du processus standard, est proposée et testée, ce qui se produits de performances de bruit et de efficacité. Ces détecteurs sont ensuite combinés avec des circuits de pixels qui exploitent les statistiques de synchronisation des photons pour la génération de chiffres aléatoires. Une modélisation intensive sur les biais et la corrélation est effectuée. En particulier, une méthode analytique pour déterminer la corrélation en série des chiffres, compte tenu du temps mort du détecteur et de la post-impulsion, est proposée et validée par simulation et expérience. Sur la base de l'analyse du biais, une approche de flip-flop

d'échantillonnage basée sur un comparateur dynamique, pour la réduction du biais de bit, est introduite en tant que composant dans une configuration de bascule aléatoire quantique. Cette méthode est comparée et mise en contraste avec une première méthode de génération de bits de comparaison d'arrivée de photons. Les conceptions sont mises à l'échelle des réseaux de capteurs SPAD, qui, lorsqu'ils sont combinés avec un éclairage externe, fonctionnent comme des conceptions QRNG gigabit par seconde. Le FortunaSPAD GNAQ est une conception à double interface, capable d'un débit de données de sortie combiné de 3,3 Gbps. Le détecteur FortunaSPAD2 GNAQ implémente une conception macro-pixel pour améliorer la robustesse contre la défaillance des pixels.

Mots clefs: Génération de nombres aléatoires, génération de nombres aléatoires quantiques, diode avalanche monophotonique, sécurité matérielle, technologie BCD, électronique des pixels, modélisation des temps morts, effets post-impulsion, flip-flop aléatoire quantique

# Contents

| A            | ckno   | edgements                                               |     |

|--------------|--------|---------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra  | $({ m English/Français})$                               | ii  |

| Ta           | able « | Contents                                                | ix  |

| Li           | st of  | igures                                                  | X   |

| Li           | st of  | ables                                                   | ťΧ  |

| Li           | ist of | cronyms                                                 | cii |

| Li           | ist of | ymbols                                                  | χı  |

| 1            | Ran    | om number generation: fundamentals, methods and systems | 1   |

|              | 1.1    | Preliminaries                                           |     |

|              |        | .1.1 Entropy                                            | 2   |

|              |        | .1.2 Keys in a cryptographic system                     | ŗ   |

|              | 1.2    | Caxonomy of generator designs                           | ŗ   |

|              |        | .2.1 Pseudo-random number generators                    | (   |

|              |        | .2.2 Classical TRNGs and chaotic maps                   | 7   |

|              |        | .2.3 Quantum random number generators                   | Ć   |

|              | 1.3    | Extraction methods, and post-processing algorithms      | 12  |

|              | 1.4    | RNGs in contemporary and future security systems        | 14  |

|              | 1.5    | Thesis goals and contributions                          | 16  |

|              | 1.6    | Thesis organization                                     | 17  |

| <b>2</b>     | Silio  | n SPADs: background and QRNG considerations             | 18  |

|              | 2.1    | PAD Device Physics, Operation, and Characterization     | 18  |

|              |        | .1.1 Basic operation and circuit abstraction            | 18  |

|              |        | .1.2 Detection efficiency and fill factor               | 22  |

|              |        | .1.3 Noise Performance                                  | 24  |

|              |        | .1.4 Timing Performance                                 | 27  |

|              |        | .1.5 SPADs in CMOS                                      | 28  |

|              | 2.2    | PAD sensors                                             | 29  |

|              |        | .2.1 Additional FoMs for arrays                         | 29  |

|    | 2.3    | Recent advances and trends                                 | 31  |

|----|--------|------------------------------------------------------------|-----|

| 3  | Silio  | con SPADs in 55 nm BCD                                     | 34  |

|    | 3.1    | Passive-quench active-recharge pixel circuit               | 36  |

|    | 3.2    | Deep junction SPADs                                        | 36  |

|    | J      | 3.2.1 Device description                                   |     |

|    |        | 3.2.2 TCAD simulation                                      | 37  |

|    |        | 3.2.3 Measurements                                         |     |

|    | 3.3    | Shallow Junction SPADs                                     |     |

|    | 5.5    | 3.3.1 SJ1                                                  | 44  |

|    |        |                                                            |     |

|    | 9.4    |                                                            |     |

|    | 3.4    | Comparison                                                 | 47  |

| 4  | Mo     | delling and design of random bit generators in 55 nm       | 51  |

|    | 4.1    | Counting statistics of SPAD detectors                      | 51  |

|    | 4.2    | Overview of methods                                        | 53  |

|    | 4.3    | Comprehensive modelling of SC QRFF                         | 55  |

|    | 4.4    | Quantum random bit generators in 55 nm BCD                 | 67  |

|    |        | 4.4.1 SC QRFF                                              | 67  |

|    |        | 4.4.2 FA QRFF                                              | 72  |

| 5  | Fort   | tunaSPAD: A dual-interface QRNG with 3.3 Gbps output rate  | 79  |

| _  | 5.1    | System architecture                                        | 79  |

|    | 5.2    | Measurements and characterization                          |     |

|    | 5.3    | NIST SP 800-22 and SP 800-90B randomness testing           |     |

|    | 0.0    | 5.3.1 Theory                                               |     |

|    |        | 5.3.2 Results                                              |     |

|    | 5.4    | Discussion and state-of-the-art comparison                 | 92  |

|    | 3.4    | Discussion and state-of-the-art comparison                 | 92  |

| 6  | Fort   | tunaSPAD2: A SPAD-based QRNG with robust macro-QRFF pixels | 95  |

|    | 6.1    | Design of an improved macro-pixel QRFF                     |     |

|    | 6.2    | FortunaSPAD2 architecture and design                       | 98  |

|    |        | 6.2.1 Readout circuitry                                    | 98  |

|    |        | 6.2.2 System design                                        | 98  |

|    | 6.3    | Measurements                                               | 101 |

|    |        | 6.3.1 Single macro-pixel                                   | 101 |

|    | 6.4    | FortunaSPAD2 with integrated micro-LEDs                    | 104 |

| 7  | Con    | nclusions                                                  | 107 |

| •  | 7.1    | Summary of thesis outcomes                                 | 107 |

|    | 7.2    | Future work                                                | 108 |

|    | 1.4    | Tutule work                                                | 100 |

| C  | hip C  | Gallery                                                    | 111 |

| Ρι | ublica | ations                                                     | 112 |

#### CONTENTS

| Bibliography     | 114 |

|------------------|-----|

| Curriculum Vitae | 133 |

# List of Figures

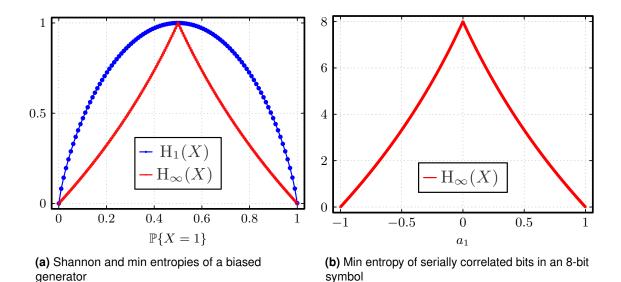

| 1.1 | Shannon and min entropy plots for a binary system in the biased and serially correlated cases. Clearly, to ensure that a certain entropy requirement is met, min entropy places more stringent bounds. The y-axis shows denotes the entropy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

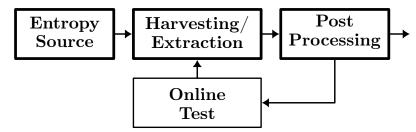

| 1.2 | Anatomy of a random number generator and the slight differences between the general structures of typical RNGs and QRNGs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6  |

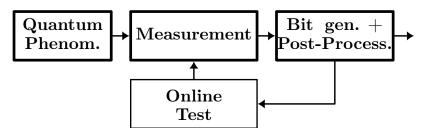

| 1.3 | Classification chart of random number generators. This thesis focuses on techniques based on photon-timing statistics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7  |

| 1.4 | Examples showing each of the four fundamental classes of TRNG designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8  |

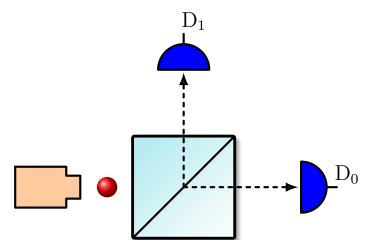

| 1.5 | Archetype QRNG implementation consisting of a photon source, a beam splitter and two detectors. When a detection arrives at $D_0$ , the output bit is 0, and a 1 when detected by D1. The uncertainty of the photon path produces the random behavior. In [38], it was shown that only afterpulsing, twilight events and dead time of detectors cause correlations in the beam splitter-based QRNG.                                                                                                                                                                                                                                                                                                         | 10 |

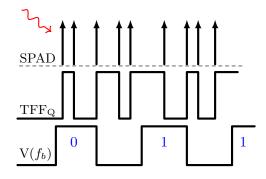

| 1.6 | Timing diagrams demonstrating random bit generation techniques based on photon-timing statistics. SPADs are assumed to be ideal detectors in this simple illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 |

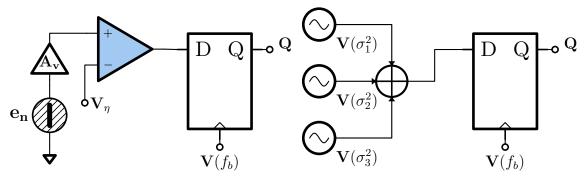

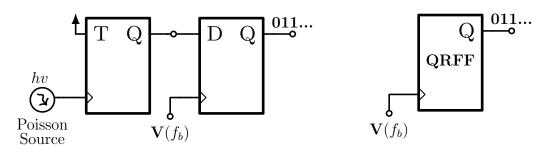

| 1.7 | The quantum random flip-flop (QRFF) concept along with a practical realization, consisting of an ideal source with Poisson-distributed arrival statistics, and two conventional flip-flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 |

| 1.8 | Demonstration of the one-time pad encryption method. When a modulo addition (XOR) is performed with a perfectly random key, the result is a provably secure cipher-text, assuming an adversary does not possess the key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

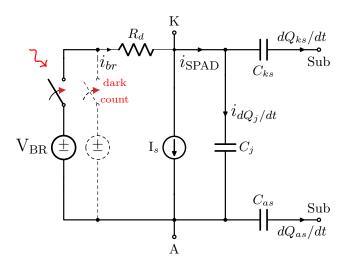

| 2.1 | Circuit representations of a standalone SPAD along with the simplest SPAD detector, which consists of a SPAD and a passive quench resistor. The internal capacitance is dominated by the junction and is in the order of $\simeq 50$ fF for modern silicon SPADs. The static diode current, $I_s$ , is in the range of picoamperes, although photo generated current can increase to nanoamperes. The breakdown voltage can vary greatly between devices ( $\simeq 12-40$ V). Diode resistance, $R_d$ , can vary in the range of a few hundred ohms to low k $\Omega$ depending on the thickness of the SPAD [64]. An avalanche causes the output voltage to rise to $V_{\rm EX} = V_{\rm OP} - V_{\rm BR}$ | 19 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

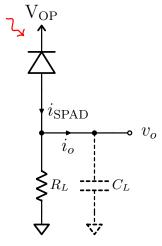

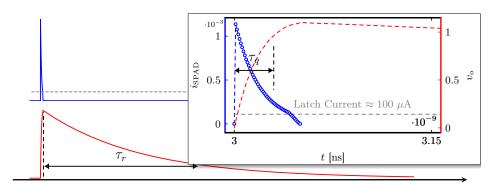

| 2.2 | Results from a SPICE compatible Verilog-A simulation of a passively quenched SPAD. The graph highlights current that flows through the diode, $i_{\rm spad}$ , and the corresponding output voltage, $v_o$ , across the quench resistor, as a function of time. Since the diode resistance is low, typically $\simeq 100~\rm k\Omega$ , the peak current flowing through the SPAD can be in the mA range, although this is for a short period of time (10 – 100ps). Quench, $\tau_q$ , and recharge, $\tau_r$ , times are denoted on the plot. The simulation is performed with a quench resistor of 100 k $\Omega$ and a junction capacitance value of 50 fF                                                | 20 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

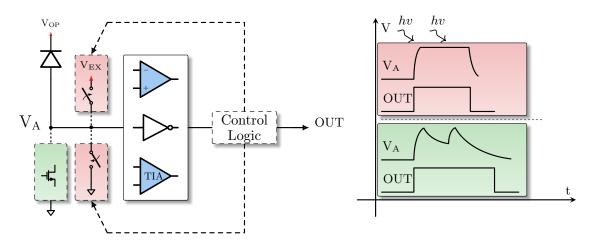

| 2.3 | Diagram of a SPAD circuit interface outlining the various pixel circuit elements. Passive quenching/recharge can be performed with a resistive element i.e. biased transistor (green). However, feedback electronics can also be implemented in order to actively quench and recharge (red). Different discriminator circuits such as transimpedance amplifiers (TIAs) or comparators can be implemented. The timing diagram demonstrates a consequence in terms of dead time when choosing passive techniques. If a photon arrival happens during the recharge stage, this can extend the dead time (paralysable). More on this in Chapter 4. A thorough summary of pixel topologies is presented in [75].  | 21 |

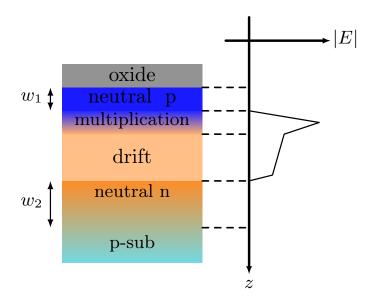

| 2.4 | A PN junction SPAD, under reverse bias, outlining the relevant regions when considering charge collection ( $P_{\rm diff}$ ). Equation (2.7) can be used to analyze the charge collection probability, i.e. the probability that a photo generated charge carrier will enter the depleted region before recombining                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

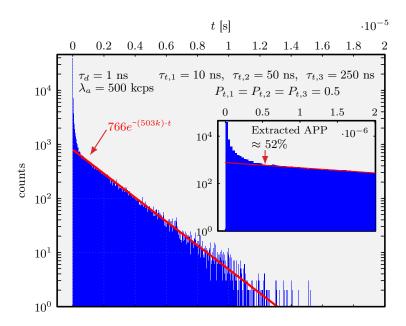

| 2.5 | A Verilog-A simulation used to generate photon arrivals at $\lambda=500$ kcps. The inter-arrival histogram of detections is plotted. Here, 3 traps with varying lifetimes are used to mimic afterpulsing behavior. The pre-exponential factors $P_{t,1}, P_{t,2}, P_{t,3}$ are exaggerated to clearly show the hyper exponential behavior for temporally bunched arrivals, resulting in a high APP (52%). A fitted exponential (red) is used to determine the afterpulsing probability, $\alpha$ . The simulation was performed with a negligible dead time, $\tau_d=1$ ns. The resulting plot mimics closely a measurement taken with a time tagging device                                                 | 26 |

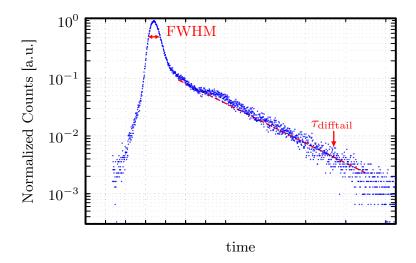

| 2.6 | An example timing jitter histogram of a SPAD detector. The FWHM of the Gaussian component is highlighted. A sample fit showing the time constant of the diffusion tail, $\tau_{\text{difftail}}$ , is also shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 |

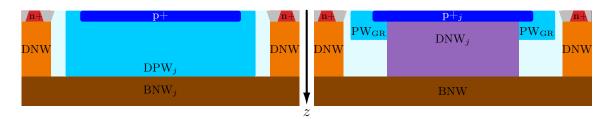

| 2.7 | Sample cross-sections of popular SPAD designs in CMOS. The SPAD on the left can be broadly classified as a deep junction, with the multiplication region formed by the $\mathrm{DPW}_j/\mathrm{BNW}_j$ interface. In this design, a virtual guard ring is used, signifying that no dedicated implant is used on the periphery of the device. On the right, a shallow junction is formed between the $\mathrm{p}+_j/\mathrm{DNW}_j$ interface. An example of an explicit guard ring is drawn as $\mathrm{PW}_{\mathrm{GR}}$ . Many variations of these structures have been demonstrated. $z$ denotes the relative depth within the silicon wafer. These structures are explored in more detail in Chapter 3. | 28 |

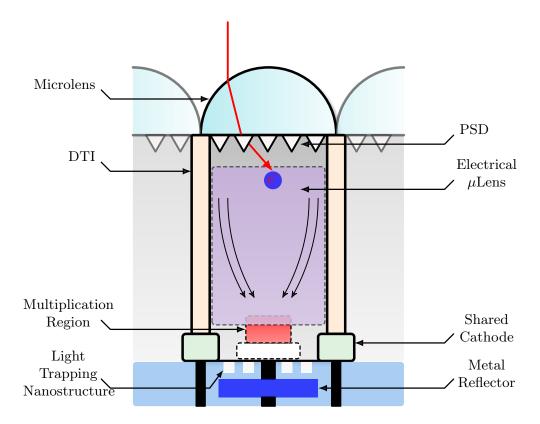

| 2.8 | Anatomy of a modern SPAD in 3D BSI. An optical microlens is shown to help recover fill factor by focusing light into the photocollector region. Moreover, PSDs can be implemented for diffracting NIR photons, which increases sensitivity but reduces timing performance. Electrical microlensing extends the photo collector region. Deep trench isolation enables small pixel pitch while reducing cross talk. Light trapping structures, such as a simple metal layer or more advanced nanostructures, reflects back photons that have passed through the silicon | 32 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

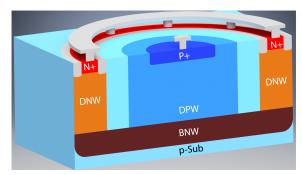

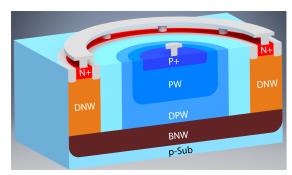

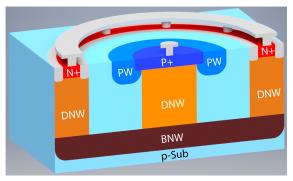

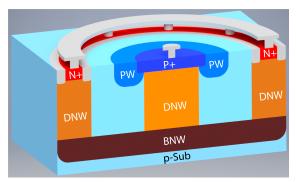

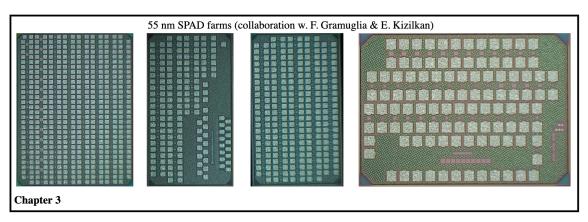

| 3.1 | Cross-sections of SPADs fabricated and characterized in a 55 nm process. Two devices (a,b) with junctions formed deep within the silicon using a buried n-well (BNW), deep p-well (DPW) interface are shown. Two shallow junctions (c,d) are also presented                                                                                                                                                                                                                                                                                                           | 35 |

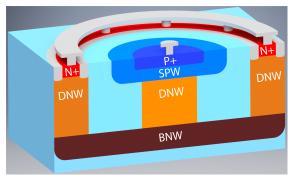

| 3.2 | PQAR circuit integrated with SPADs for accurate characterization of afterpulsing and timing jitter. A cascode transistor is used to enable testing at $V_{\rm EX} \leq 5$ V and a tunable delay element is added in the feedback loop for controllable dead time. The waveform displays the general operation upon detection of a photon                                                                                                                                                                                                                              | 35 |

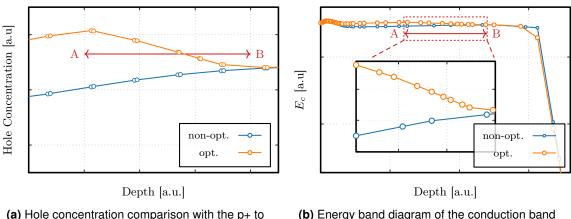

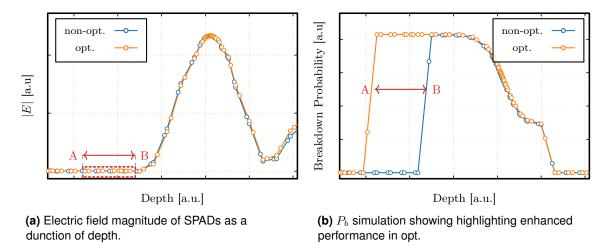

| 3.3 | Diagrams showing the TCAD simulation results for both the optimized (orange) and non-optimized (blue) deep junction SPADs at $V_{\rm EX}=5$ V. The simulation is performed after all implants are combined, i.e. with the net relative doping. The monotonic decrease in hole concentration with the addition of the PW enables electron diffusion towards the multiplication region                                                                                                                                                                                  | 38 |

| 3.4 | Electric field of two deep junction SPADs simulated at $V_{\rm EX}=5$ V and the corresponding breakdown probability as a function of depth. The region AB is clearly shown to be outside the high field multiplication region. Nevertheless, the probability of avalanche from carriers generated in this region remains high.                                                                                                                                                                                                                                        | 38 |

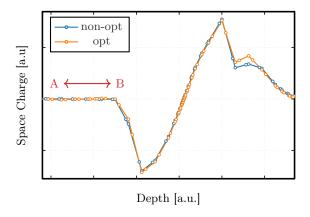

| 3.5 | Space charge plot of both deep junction SPADs, at $V_{\rm EX}=5$ V. This confirms that the depleted regions for both detectors under excess bias are similar                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

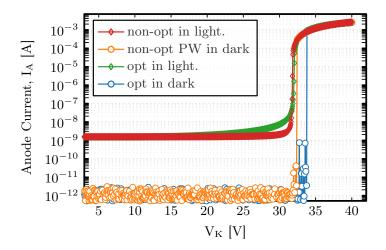

| 3.6 | IV curve of opt and non-opt deep Junction SPADs under dark and illuminated conditions. The opt design demonstrates higher photo-current near the breakdown voltage                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

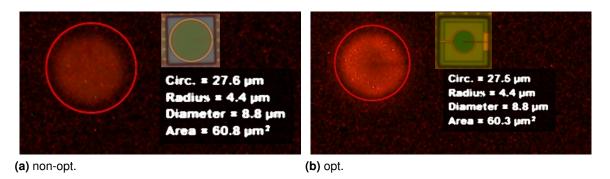

| 3.7 | LET results for deep junction SPADs. Good light emission uniformity around an active radius of 4 $\mu$ m is observed, with no evidence of premature edge breakdown. Testing is performed at $V_{\rm EX}=3$ V. Micrographs of the devices are included                                                                                                                                                                                                                                                                                                                 | 40 |

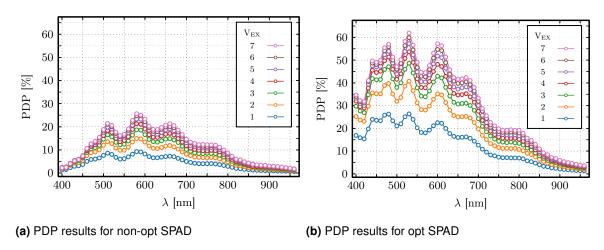

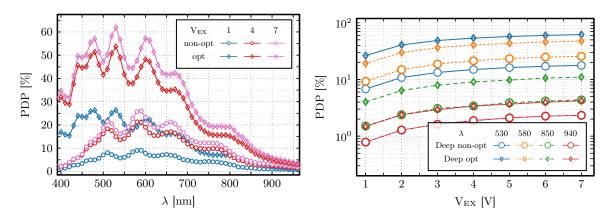

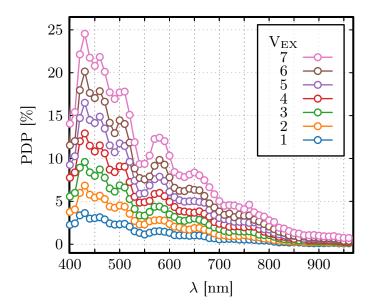

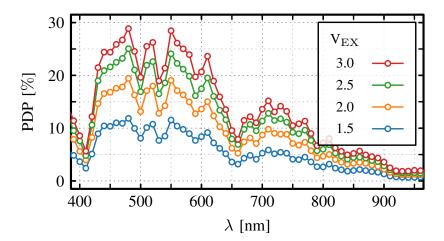

| 3.8 | PDP measurements of deep opt and non-opt SPADs measured at room temperature with $V_{\rm EX}=1-7$ V and a 220 k $\Omega$ passive quench resistor. Measurements are taken at 10 nm intervals. The resulting standing wave pattern is due to a non-optimized optical stack (dielectrics) placed above the SPADs                                                                                                                                                                                                                                                         | 41 |

| 3.9  | PDP comparison of deep junction SPADs. Improved sensitivity is achieved at every wavelength. The non-opt SPAD notably has very low sensitivity at NUV and blue wavelengths, owing to the barrier for carrier transit outlined in simulation.                                                                                                                                                                                                                                                                                                                                                                               | 41 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

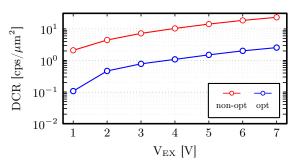

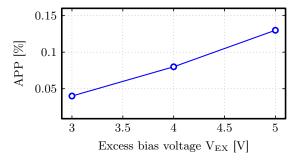

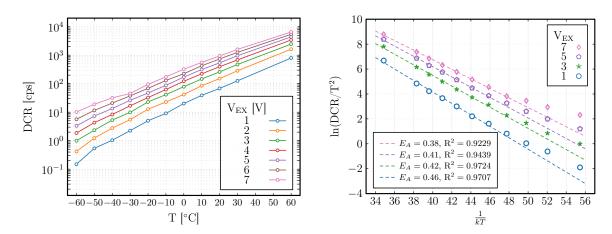

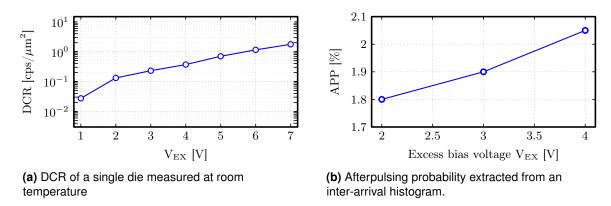

| 3.10 | Noise performance of deep junction SPADs in 55 nm. Ten separate devices for each SPAD were measured for DCR, with the median value plotted. Due to its superior performance, APP was measured only for the opt design                                                                                                                                                                                                                                                                                                                                                                                                      | 42 |

| 3.11 | Temperature dependence of deep opt SPAD in 55 nm BCD process. Measurements are performed across an excess bias range of $V_{\rm EX}=1-7$ and a temperature range of $-60^{\circ}{\rm C}$ to $60^{\circ}{\rm C}$ . The Arrhenius plot is shown, highlighting that trap assisted thermal generation is the dominant contributor to DCR until low temperatures, where tunneling becomes more significant                                                                                                                                                                                                                      | 43 |

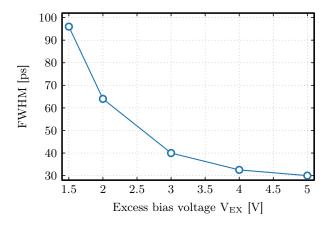

| 3.12 | Single-photon timing jitter (FWHM) of deep opt SPAD, measured at $\lambda=780$ nm across an excess bias range of $V_{\rm EX}=1-5$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |

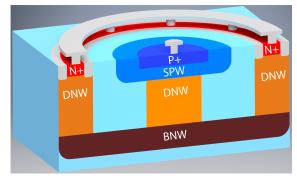

| 3.13 | 55 nm BCD shallow junction cross-sections. SJ1 has an abrupt junction formed using the $p+/DNW$ interface. A PW implant is used as an explicit guard ring. SJ2 improves the detection efficiency of this junction with the addition of a shallow p-well (SPW) implant                                                                                                                                                                                                                                                                                                                                                      | 44 |

| 3.14 | Noise performance of an SJ1 SPAD with an active radius of 4.5 $\mu$ m, measured across excess bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45 |

| 3.15 | PDP measurements of the SJ1 SPAD with an active radius of 4.5 $\mu$ m, at room temperature, with an excess bias range of $V_{EX}=1-7$ V at 10 nm wavelength intervals. Quenching performed with a 220 k $\Omega$ resistor                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

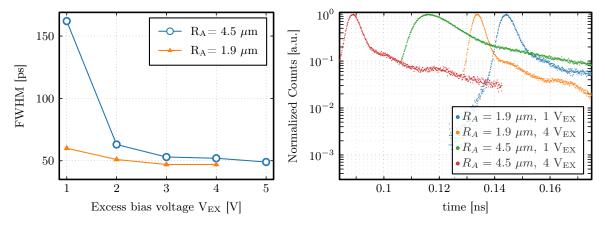

| 3.16 | Timing performance of two separate SJ1 SPADs with active radius $R_A=1.9~\mu m$ and $R_A=4.5~\mu m$ . At low excess bias, the timing performance of the larger SPAD is significantly larger.                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

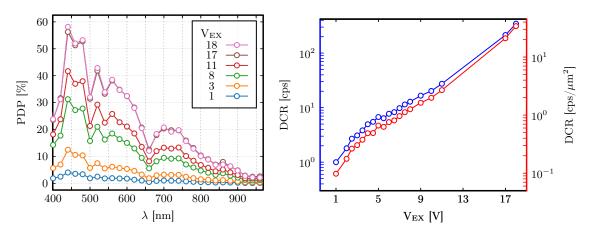

| 3.17 | DCR and PDP measurements for the fully depleted SJ2 shallow junction SPAD in 55 nm BCD. The results show an increase in PDP until an excess bias voltage $V_{EX}=18~V$ , achieving $\simeq~59~\%$ at 440 nm                                                                                                                                                                                                                                                                                                                                                                                                                | 47 |

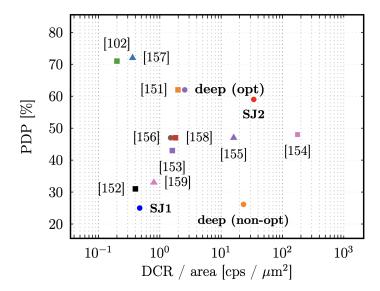

| 3.18 | Comparison of recently published silicon SPAD performance in terms of DCR and PDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48 |

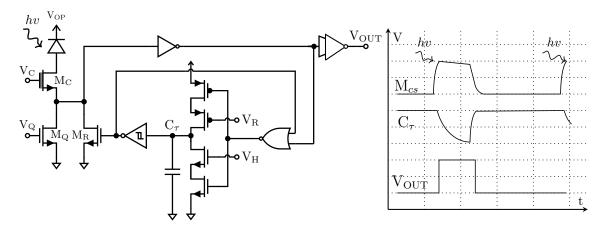

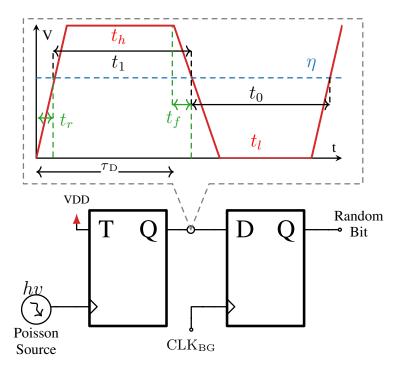

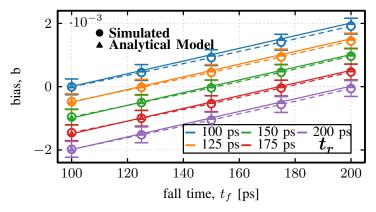

| 4.1  | A realization of the slow-clock QRFF circuit with a source that has ideal Poisson arrival times. A realistic waveform of the output of the TFF is shown, given electronics with finite rise/fall times. These times are denoted as $t_r$ and $t_f$ , respectively. Edge transitions happen, on average, at intervals decided by the detection rate, i.e. $\lambda_{\rm D}=1/\tau_{\rm D}$ . The normalized sampling threshold, i.e. the point at which the sampling DFF determines the signal to be a zero or one, is highlighted by $\eta$ . A bit is generated upon the arrival of the clock signal (CLK <sub>BG</sub> ) | 55 |

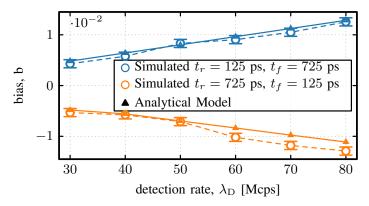

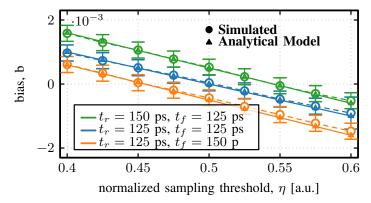

| 4.2  | Verilog-AMS simulation of bias model of the slow-clock QRFF circuit using the bias model presented in [171]. An ideal source, which generates exponentially distributed inter-arrival times, are used for the simulation. The results demonstrate that $\eta$ can be used to eliminate bias caused by mismatched rise and fall times                                                                                        | 56 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

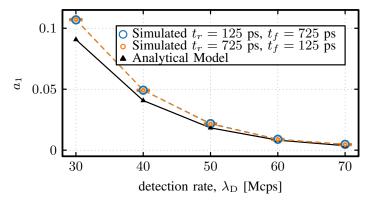

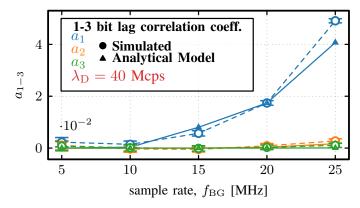

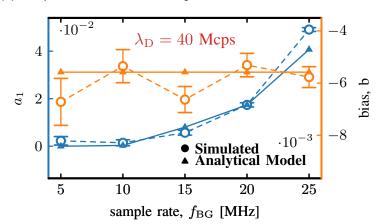

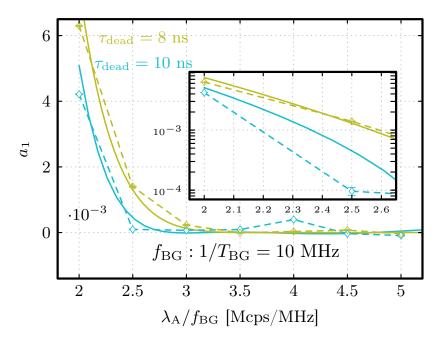

| 4.3  | Comparison of ideal correlation model with results from Verilog-A circuit simulations. The exponential relationship of correlation with the count rate bit generation rate $\lambda_{\rm A}/f_{\rm BG}$ ratio is clearly highlighted. Moreover, it can be see that even as correlation increases due to higher sampling rate at a constant flux, bias remains constant, as expected.                                        | 58 |

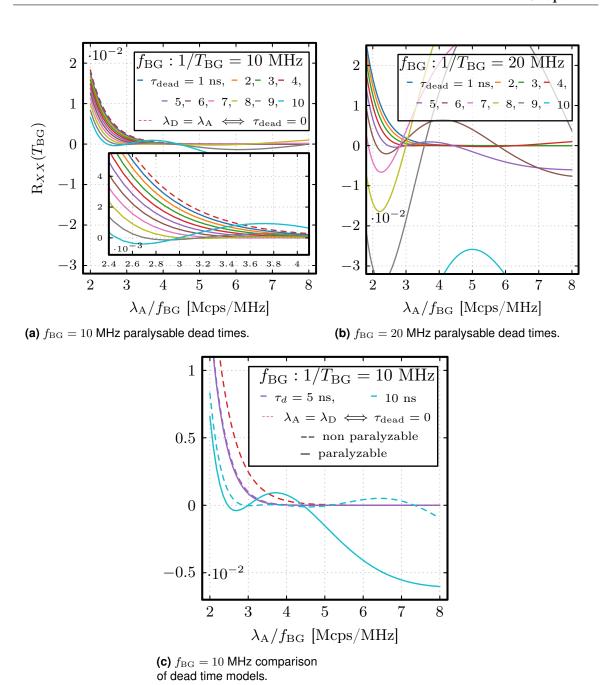

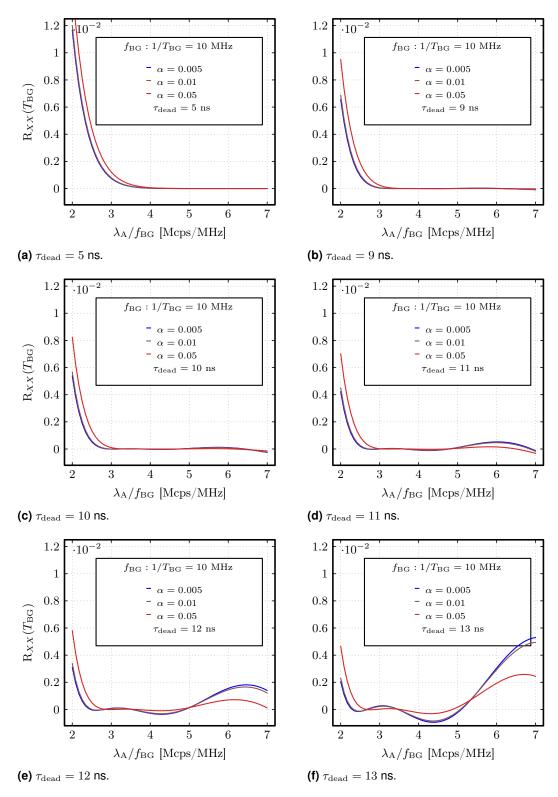

| 4.4  | Autocorrelation function of the QRFF circuit, at varying dead times, calculated using Equation (4.10). The counting models presented in [76], which model passive and active quenching scenarios, are used to calculate the probability of $k$ detections                                                                                                                                                                   | 60 |

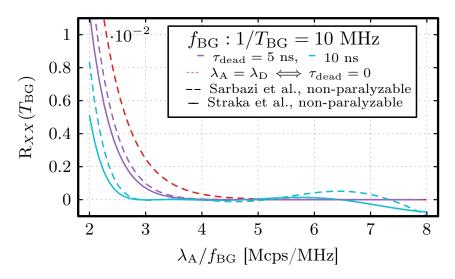

| 4.5  | Comparison of autocorrelation function with non-paralysable detector using the counting models presented in [76] (dashed line) and [170] (solid line) for calculation of Equation (4.10)                                                                                                                                                                                                                                    | 61 |

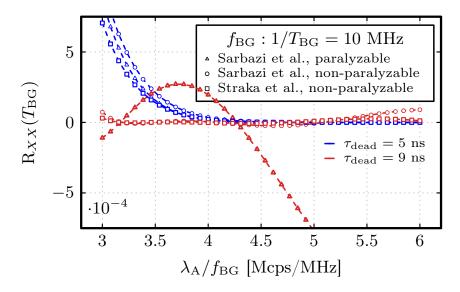

| 4.6  | Comparison of autocorrelation function for a paralysable and non-paralysable detector using both counting models presented in [76] and [170] used to calculate Equation (4.10).                                                                                                                                                                                                                                             | 61 |

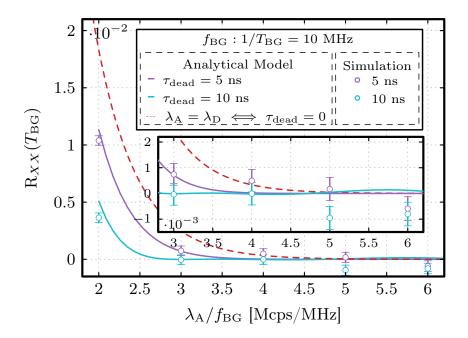

| 4.7  | Verilog-A simulation results of autocorrelation values compared to analytical calculation ([170] counting). The analysis is performed using the non-paralyzable counting model at $\tau_{\rm dead}$ values of 5, and 10 ns. The ideal autocorrelation function, described by Equation (4.9), based on a pure Poisson counting process, is shown by the dashed trace                                                         | 62 |

| 4.8  | Autocorrelation combining dead time and afterpulsing probabilities ( $\alpha$ ) using $f_{\rm BG}=10$ MHz. Counting equations from [170] i.e. no consideration of afterpulsing PDF                                                                                                                                                                                                                                          | 63 |

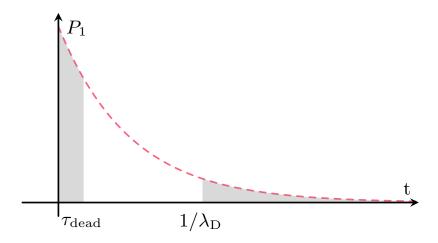

| 4.9  | Diagram illustrating the probability measure of afterpulsing implemented in the model. A carrier which has a decaying probability $P_1$ and lifetime $\tau_1$ can only ignite an avalanche if it is released at time, $t_r$ , $t_r > \tau_q$ but before the next photon arrival. The non-shaded section corresponds to probability values that can ignite an avalanche                                                      | 65 |

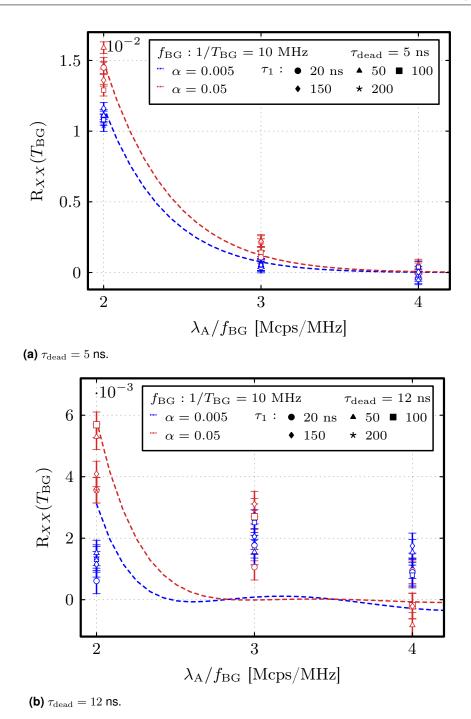

| 4.10 | Comparison between analytical calculation of autocorrelation and simulation. Analysis is performed with $\tau_{\rm dead}=5$ ns and 12 ns and with 0.5 % and 5 % afterpulsing probabilities. Lifetime values of $\tau_1$ of 20, 50, 150, and 200 ns are used for each arrival rate. The dashed line indicates the analytical calculation while the markers are simulated values at $\lambda_a$ values of 20, 30 and 40 Mcps. | 66 |

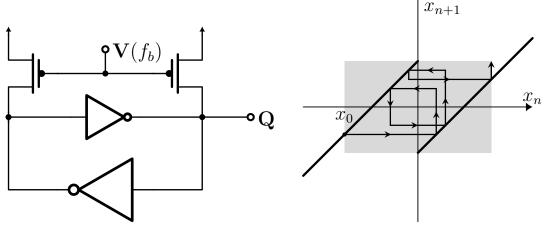

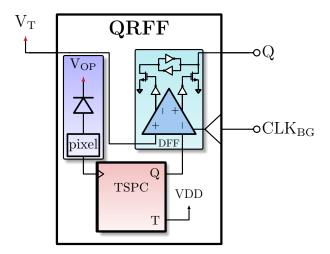

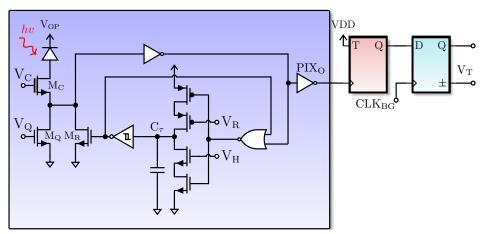

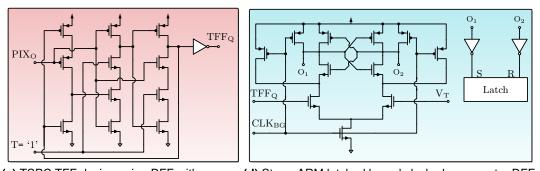

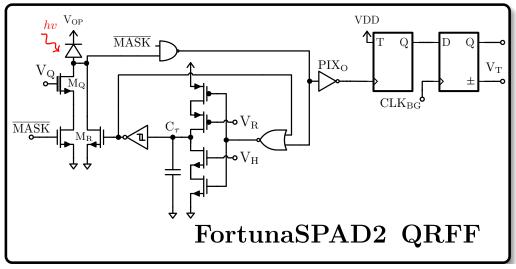

| 4.11 | Slow clock QRFF design presented in this work to generate random bits. A block diagram highlights the major components: a SPAD+pixel, a TSPC TFF and a clocked comparator based DFF. $V_T$ is the threshold control voltage $(\eta=V_T/1.2)$ . A bit is generated at Q upon the arrival of an edge from the bit generation clock, $CLK_{BG}$                                                                                                                                                                                                                                                          | 68 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

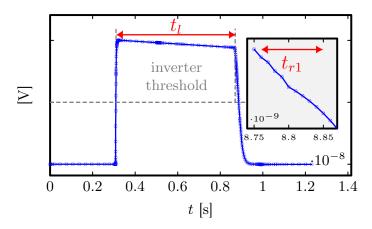

| 4.12 | Plot showing simulated pulse width of the SPAD anode when coupled with the PQAR pixel. While technically paralysable in the time interval $t_l + t_{r1}$ . However, in the hold-off interval, $t_l$ , the excess bias across the SPAD is very low (< 100 mV). Therefore, absorbed photons have a low probability of initiating an avalanche. The recharge time is denoted by $t_{r1}$ , until the inverter threshold is crossed (order of 100 ps). Therefore, the assumption is made that modelling this detector as non-paralysable is acceptable so long as flux is tuned to reduce pile-up effects | 69 |

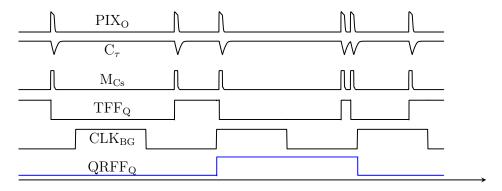

| 4.13 | Timing diagram highlighting the general function of the SC QRFF design. $\;\;$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69 |

| 4.14 | Measured PDP of a single QRFF with excess bias in the range $V_{\rm EX}=1-3~{\rm V}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70 |

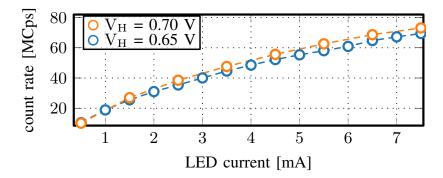

| 4.15 | Counting performance of a single QRFF with hold voltage settings ( $V_H=0.65$ V and $V_H=0.7$ V) vs LED current ( $I_{LED}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70 |

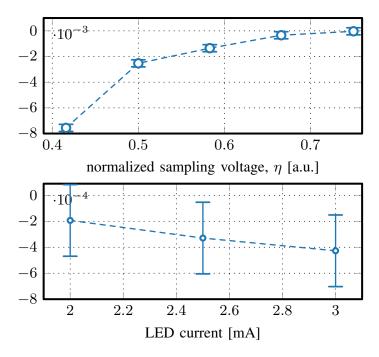

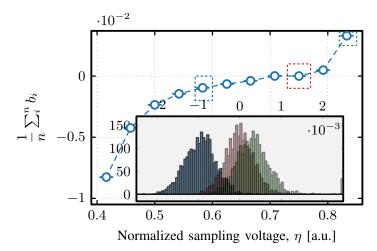

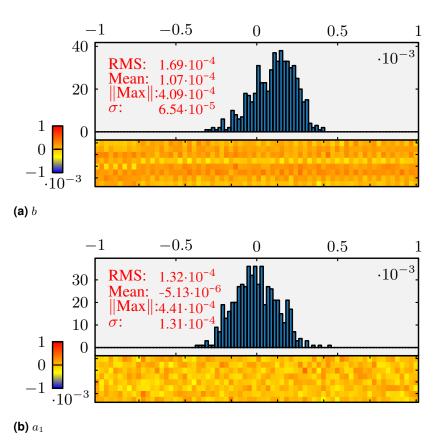

| 4.16 | Bias measurements from $P(X=1)=0.5$ at $f_{\rm BG}=5$ MHz vs normalized sampling threshold and LED current. Upper plot performed with $I_{\rm LED}=2$ mA and lower plot with $V_{\rm T}=0.9$ V $(\eta=0.75)$                                                                                                                                                                                                                                                                                                                                                                                          | 71 |

| 4.17 | Serial correlation measurement results for a single QRFF compared to expected results based on proposed correlation model with dead time                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72 |

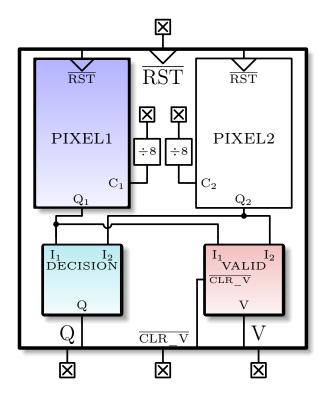

| 4.18 | First arrival (FA) based QRFF block diagram. It consists of two identical SPAD pixels, a decision cell to decide which was the first to fire, along with a valid cell that checks that a photon arrival occurred. Count dividers are added to the pixel outputs so that small pulses $\tau_{\rm dead}$ can be consistently counted by an                                                                                                                                                                                                                                                              |    |

|      | FPGA. Circuit schematics for each block are illustrated by Figure 4.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73 |

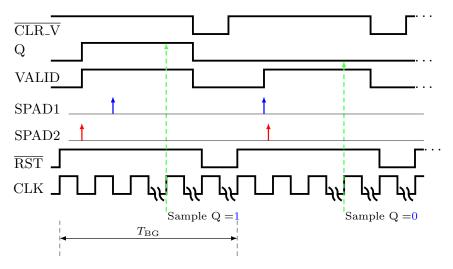

| 4.19 | Timing diagram of the FA QRFF design. The comparison is made within the evaluation window set by $\overline{\text{RST}}$ . A valid signal is generated when a photon is detected                                                                                                                                                                                                                                                                                                                                                                                                                      | 73 |

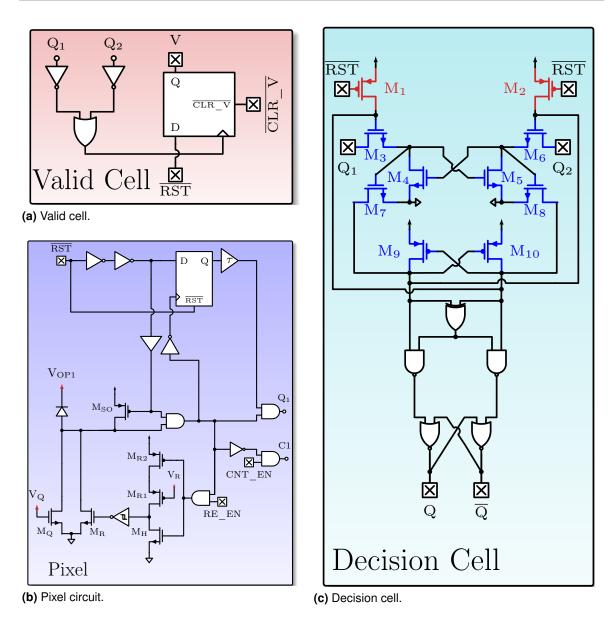

| 4.20 | The FA QRFF circuit schematic. The evaluation period is set by $\overline{RST}$ . An automatic recharge loop is used to quickly activate the SPADs after $M_{SO}$ is turned off. The valid cell check for a photon detection from either of the SPADs. A two stage regenerative amplification process in the decision cell is used to discriminate between closely spaced events                                                                                                                                                                                                                      | 74 |

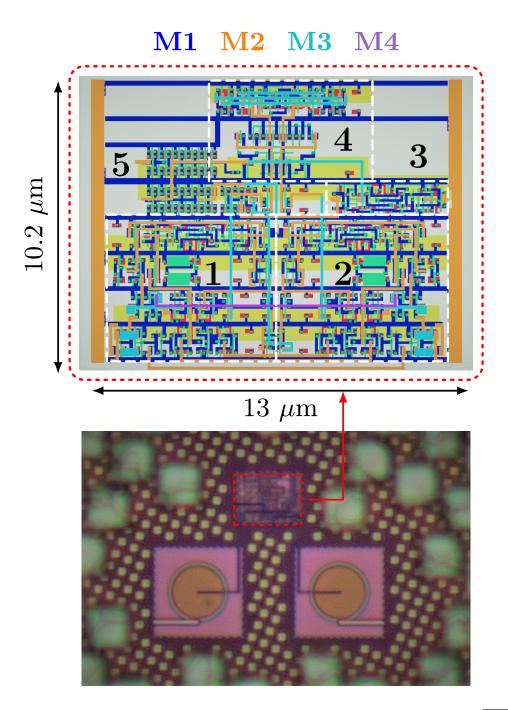

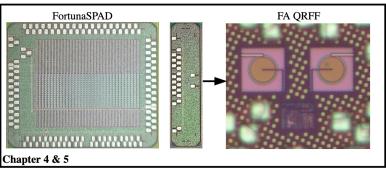

| 4.21 | Layout of FA QRFF cell. 1: Pixel 1, 2: Pixel 2, 3: Valid cell, 4: Decision cell,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | 5: $\overline{\text{RST}}$ clock buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75 |

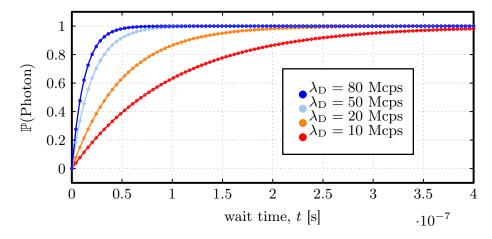

| 4.22 | CDF of the exponential distribution with detection rates $\lambda_D = 10$ , $\lambda_D = 20$ , $\lambda_D = 50$ , and $\lambda_D = 80$ Mcps                                                                                                                                                                                                                                | 76 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

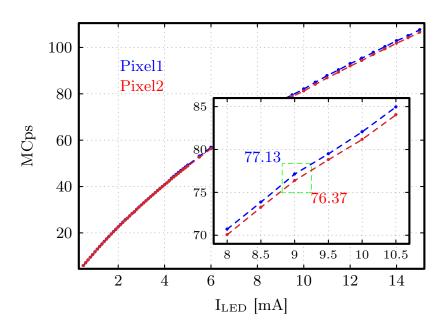

| 4.23 | Counting performance of both detectors in the FA QRFF design, as a function of LED current. Both SPADs are connected to $V_{\rm OP}=33.3~{\rm V.}$                                                                                                                                                                                                                         | 77 |

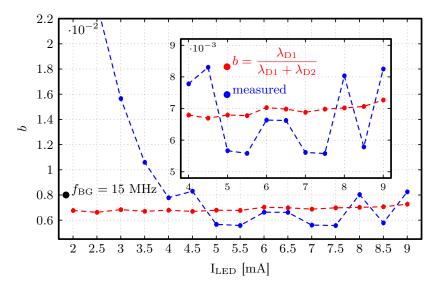

| 4.24 | FA QRFF bias measurement at a constant bit generation rate of $f_{\rm BG}=15$ MHz, compared to the theoretical value based on count rates                                                                                                                                                                                                                                  | 77 |

| 4.25 | FA QRFF bit bias and serial correlation with swept frequency $f_{\rm BG}=5-22.5$ MHz at a constant illumination of $I_{\rm LED}=10$ mA                                                                                                                                                                                                                                     | 78 |

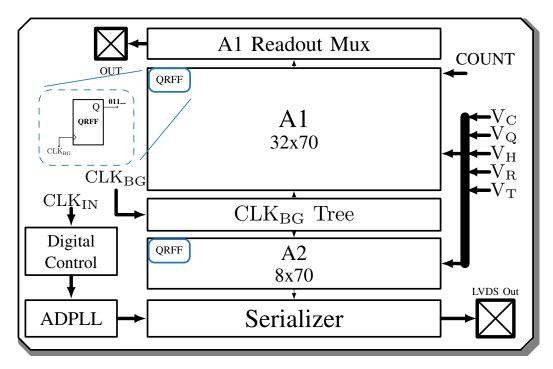

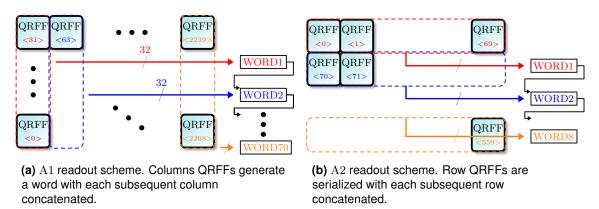

| 5.1  | FortunaSPAD chip architecture. Two independent arrays (A1) and (A2) capable of generating bits concurrently are included. A1 implements a simple readout structure where all pixels are connected to an output readout multiplexer. The readout scheme for A2 uses a high-speed serialization clock generated by the ADPLL to serialize 70 QRFFs onto a single channel     | 80 |

| 5.2  | A diagram that illustrates how random bits generated from individual QRFF pixels are read-out i.e. how serial data is turned into spatial data.                                                                                                                                                                                                                            | 80 |

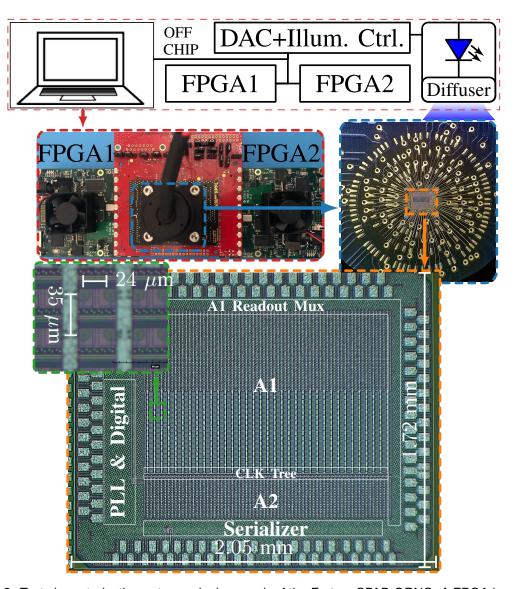

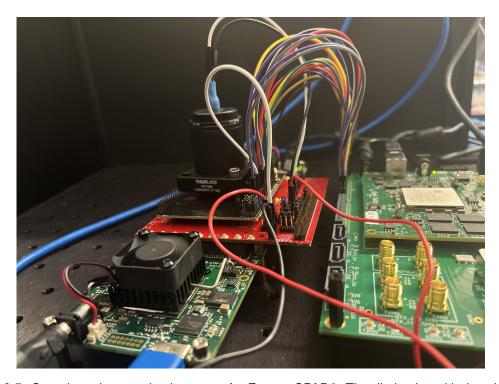

| 5.3  | Test characterization setup and micrograph of the FortunaSPAD QRNG. A FPGA is used for read-out of each array. The LED is housed inside an optical tube. A diffuser is used for more uniform illumination. Red motherboard contains all voltage generation and illumination control required for testing. The total die area is $2.05~\mathrm{mm} \times 1.72~\mathrm{mm}$ | 81 |

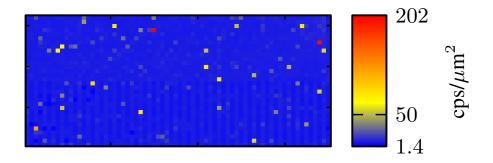

| 5.4  | DCR spatial distribution of A1 array when tested with $V_{\rm OP}=33.3~V$ and at room temperature                                                                                                                                                                                                                                                                          | 82 |

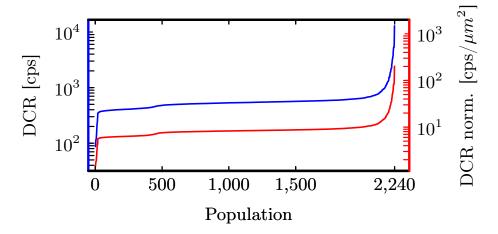

| 5.5  | DCR showing A1 results for both normalized and non-normalized case at room temperature. This plot provides a simple visualization of hot pixel population.                                                                                                                                                                                                                 | 82 |

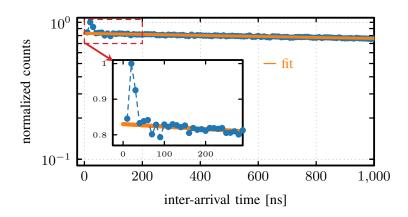

| 5.6  | Inter-arrival time histogram of Fortuna test pixel measured at $\tau_{\rm dead}=8$ ns and room temperature                                                                                                                                                                                                                                                                 | 83 |

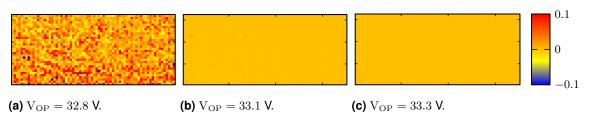

| 5.7  | Spatial bias analysis of bias at $V_{OP}=32.8,\ V_{OP}=33.1,\ and\ V_{OP}=33.3\ V$ for analysis of the breakdown voltage spread. Parameter settings: $I_{LED}=2,\ \eta=0.71,\ f_{BG}=5\ MHz.$                                                                                                                                                                              | 83 |

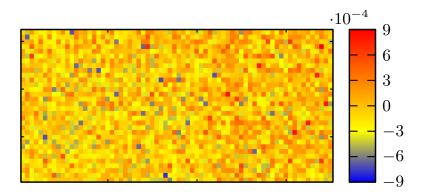

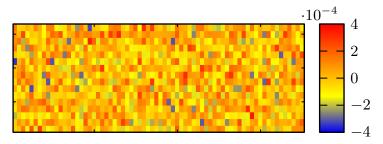

| 5.8  | A1 array spatial bias map from $P(X=1)=0.5$ (Figure 5.7c re-plot with appropriate scale) at $I_{LED}=2$ and a normalized voltage setting $\eta=0.71$ and a bit generation rate of $f_{BG}=5$ MHz                                                                                                                                                                           | 84 |

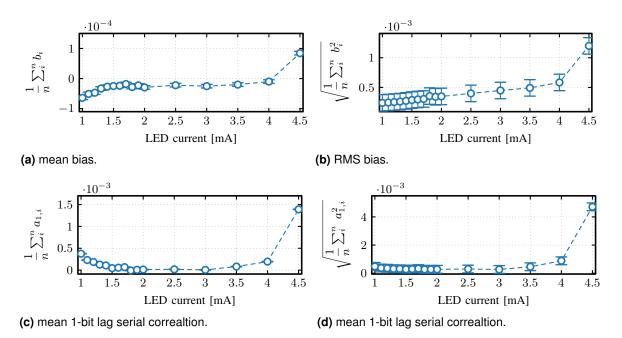

| 5.9  | Bias and correlation analysis using serial data sorted pixel wise of all QRFFs in A1 as a function of LED current. Data is generated at $f_{\rm BG}=5$ MHz. Threshold setting is held constant at $\eta=0.71$ i.e. $V_{\rm T}=0.85$ V                                                                                                                                      | 85 |

| 5.10 | Bias and serial correlation of QRFFs in the A1 array as a function of threshold voltage setting $V_T$ . Measurements performed with $I_{LED}=2.5$ mA and $f_{BG}=5$ MHz                                                                                                                                                                                                    | 86 |

| 5.11 | Spatial bias maps showing the calculated cross-correlation of bits generated by adjacent pixels. Two full columns of data are generated in a single cycle at $f_{\rm BG}=5~{\rm MHz}.$                                                                                                                                                                                                                                                                                                                      | 87 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

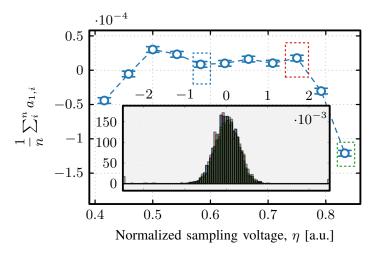

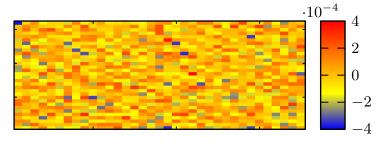

| 5.12 | Spatial bias and correlation analysis of the A2 array. Each channel generates 140 Mbps of data i.e. $f_{\rm BG}=2$ MHz, $I_{\rm LED}=2$ mA and $\eta\simeq 0.71$ . Sorting of data is performed using the STROBE signal output from the ASIC that aligns with the first serialized bit in the word (QRFF[0])                                                                                                                                                                                                | 88 |

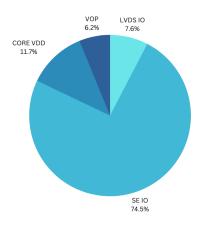

| 5.13 | FortunaSPAD power consumption measurement. Measurement performed at $I_{LED}=2$ mA, $\eta=0.71,$ and $V_{OP}=33.3$ V. Overall the power consumption is 243 mW                                                                                                                                                                                                                                                                                                                                               | 89 |

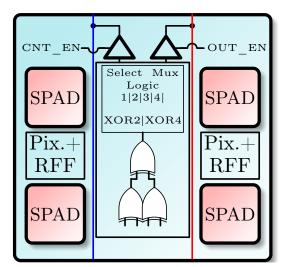

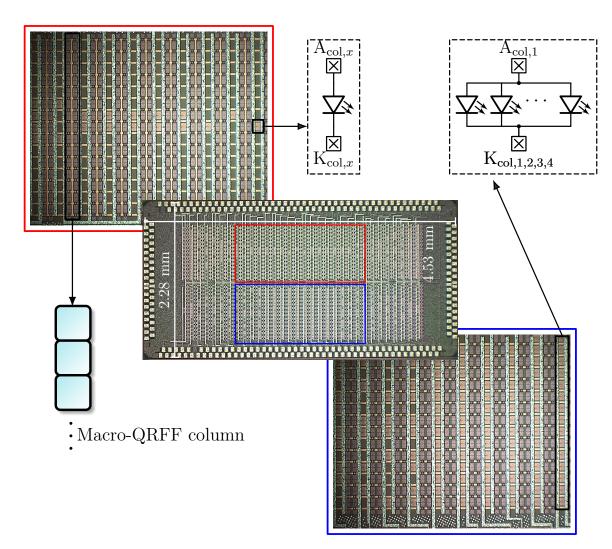

| 6.1  | Macro-pixel based QRFF design for the FortunaSPAD2. Four QRFF designs are combined. Count rates and random data are output on the column blue/red buses, respectively. Count rates and generated random bits from any individual QRFF can be selected. The two QRFFs in a column can also have their random bits XOR'd, or all 4 can be selected for XOR $(Q = 1 \oplus 2, 3 \oplus 4, (1 \oplus 2) \oplus (3 \oplus 4))$ . Pixel-wise masking is also implemented using a 1-bit memory cell in each pixel. | 96 |

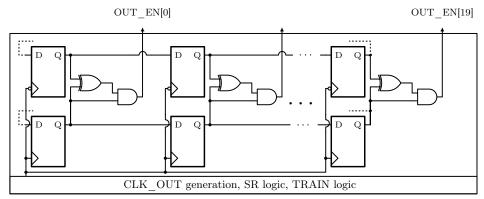

| 6.2  | Column readout circuit and timing diagram for the FortunaSPAD2. Readout is performed by enabling the tri-state buffer of each individual macro-QRFF output onto the column bus. A custom shift-register is designed to perform this with the general circuit architecture shown here. Tri-state buffers are only enabled for a clock-cycle for fast operation while avoiding bus contention. A train option is additionally available to allow for 4-bits of known output                                   | 97 |

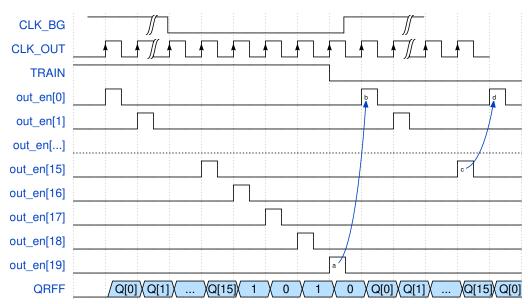

| 6.3  | Block diagram of the FortunaSPAD2. The $64 \times 64$ pixel (SPADs) sensor is symmetrical across the x-axis and consists of a total of $2 \times 32 \times 16$ macro-QRFFs.                                                                                                                                                                                                                                                                                                                                 | 99 |

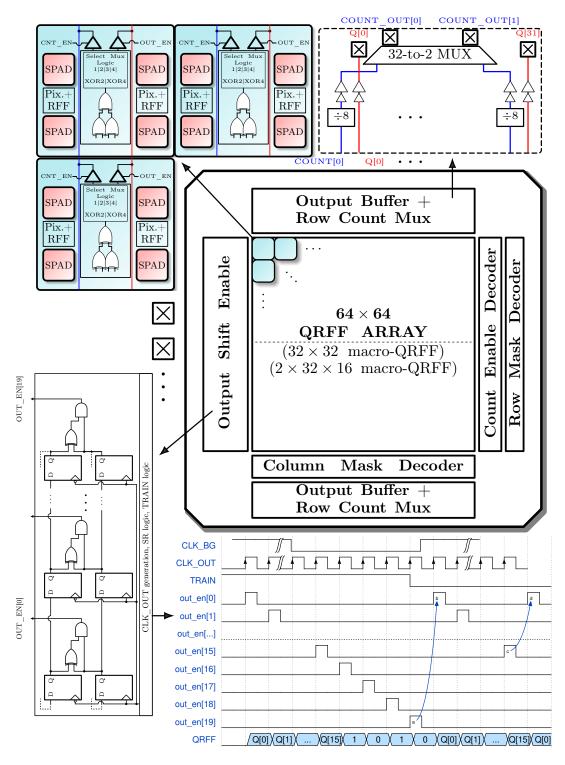

| 6.4  | Micrograph and bonding PCB of the FortunaSPAD2. Layout of the macro-QRFF and its corresponding pixel circuit blocks are also shown                                                                                                                                                                                                                                                                                                                                                                          | 00 |

| 6.5  | Complete characterization setup for FortunaSPAD2. The die is placed below the black optical tube which houses the LED                                                                                                                                                                                                                                                                                                                                                                                       | 00 |

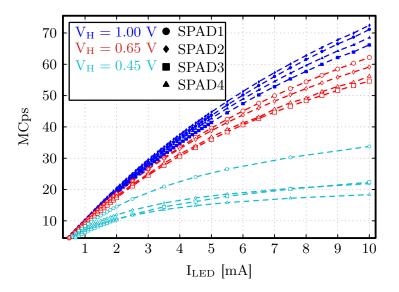

| 6.6  | Measured counts of all four pixels in a single macro-QRFF as a function of illumination current with three separate settings for the hold voltage control $V_{\rm H}.1$                                                                                                                                                                                                                                                                                                                                     | 01 |

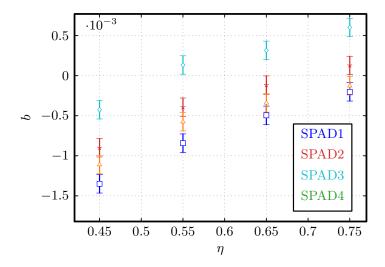

| 6.7  | Measured bias as a function of threshold voltage, at a constant illumination of $I_{LED}=2$ mA, $V_{H}=0.65$ V, $V_{R}=0.35$ V, and $f_{BG}=5$ MHz                                                                                                                                                                                                                                                                                                                                                          | 02 |

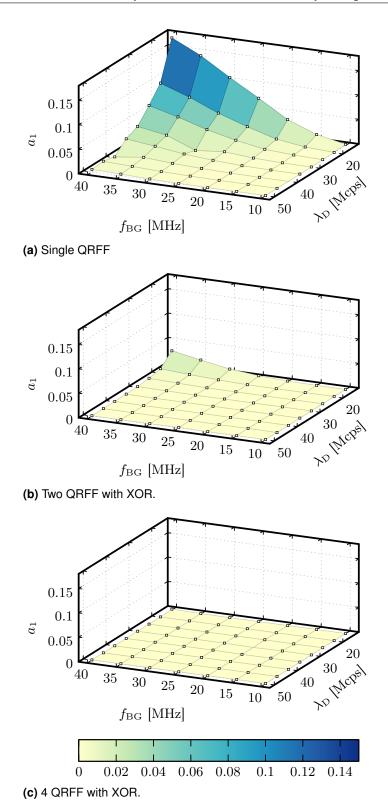

| 6.8  | Autocorrelation result for a single macro-QRFF in the FortunaSPAD2. A 3D visualization of the $\lambda_{\rm D}/f_{\rm BG}$ relationship is shown with a variety of plotted ratios. The results demonstrate that two round of XOR reduces serial correlation to acceptable levels even at $\lambda_{\rm D}/f_{\rm BG} \simeq 0.5.$                                                                                                                                                                           | 03 |

| 6.9  | Micrograph of the FortunaSPAD2 version, which includes silicon $\mu$ -LEDs 1                                                                                                                                                                                                                                                                                                                                                                                                                                | 05 |

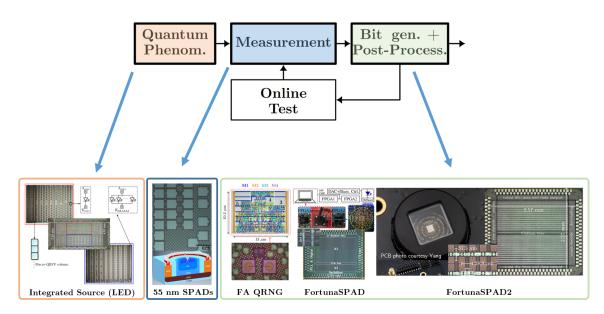

| 7.1 | 7.1 QRNG block diagram with integrated solutions proposed in this thesis. 55 nm |     |  |  |

|-----|---------------------------------------------------------------------------------|-----|--|--|

|     | SPADs, various QRFF circuits, FortunaSPAD and FortunaSPAD2 for random           |     |  |  |

|     | number generation, along with a research platform for studying integrated       |     |  |  |

|     | illumination                                                                    | 107 |  |  |

# List of Tables

| 3.1 | Comparison table of Silicon SPADs in literature                                                                                                                                         | 49 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | A comparison table of SPAD-based random bit generation techniques that are considered for array implemenation                                                                           | 54 |

| 4.2 | Single-QRFF Entropy Characterization at $f_{\rm BG}=10$ MHz and ${\rm V_{OP}}=33.3$ V                                                                                                   | 7  |

| 4.3 | Detailed results of FA QRFF circuit in terms of bias, correlation and entropy. The SPAD bias $(V_{\mathrm{OP}})$ of the first pixel is adjusted to compensate for count rate difference | 78 |

| 5.1 | Sample summary of FortunaSPAD NIST SP 800-22 results. Data generated at 3.3 Gbps overall rate with parameters: $\eta \simeq 0.71$ , $I_{\rm LED}=2$ mA                                  | 9  |

| 5.2 | Published Integrated SPAD-Based QRNGs with bit-generation/extraction on chip.                                                                                                           | 94 |

## List of Acronyms

ADPLL All-Digital Phase-Locked LoopAES Advanced Encryption System

AMS Analog Mixed-SignalAPP Afterpulsing Probability

ASIC Application-Specific Integrated Circuit

**BCD** Bipolar CMOS DMOS

BIW Barak/Impagliazzo/Wigderson

**BNW** Buried N-Well

**BSI** Backside Illumination

**DAC** Digital-to-Analog Converter

DCR Dark Count RateDI Device-Independent

DNW Deep N-WellDPW Deep P-Well

EaaS Entropy-as-a-Service

FA First ArrivalFF Fill FactorFoM Figure of Merit

**FPGA** Field-Programmable Gate Array

FSI Frontside Illumination

**FWHM** Full Width at Half Maximum

IC Integrated Circuit

iid Independent and Identically Distributed

IoT Internet of ThingsLED Light-Emitting DiodeLET Light Emission Testing

LVDS Low-Voltage Differential Signalling

NIR Near-Infrared

**NIST** National Institute of Standards and Technology

**NUV** Near Ultra-violet

PDE Photon Detection Efficiency

PDF Probability Density Function

PDP Photon Detection Probability

PEB Premature Edge Breakdown

**PET** Positron Emissions Tomography

PLL Phase-Locked Loop

PQAR Passive-Quench Active Recharge

PRNG Pseudo-Random Number Generator

PSD Pyramid Surface for Diffraction

PVT Process Voltage Temperature

**QE** Quantum Efficiency

QKD Quantum Key DistributionQRFF Quantum Random Flip-Flop

QRNG Quantum Random Number Generator

RBG Random Bit GeneratorRFF Random Flip-Flop

RNG Random Number Generator

RSA Rivest–Shamir–Adleman

RTS Random Telegraph Signal

SC Slow Clock

SoC System-on-Chip

SOI Silicon-on-Insulator

SP Special Publication

SPAD Single-Photon Avalanche DiodeSPTR Single-Photon Timing Resolution

SPW Shallow P-WellSTS Statistical Test Suite

TCAD Technology Computer Aided DesignTCSPC Time-correlated single-photon counting

**TDC** Time-to-Digital Converter

TRNG True Random Number Generator

TSV Through-Silicon Vias

## List of Symbols

Afterpulsing probability  $\alpha$  $A_a$ SPAD active area  $a_j$ Serial correlation coefficient with j-lag Bias of bit string  $C_{as}$ Anode parasitic capacitance  $C_j$ Diode junction capacitance  $C_{ks}$ Cathode parasitic capacitance  $C_L$ Load capacitance  $DR_s$ SPAD dynamic range  $|\overline{\mathrm{E}_d}|$ Depletion region average electric field magnitude  $E_g$ Bandgap energy  $E_s$ SPAD energy consumed per detection fFrequency  $f_{\rm BG}$ Bit generation frequency  $F_c$ Dynamic range correction factor  $G_{\mathrm{btb}}$ Band-to-band generation  $G_{\text{therm}}$ Thermal carrier generation rate hPlanck constant  $H_1$ Shannon entropy Min-entropy  $H_{\infty}$  $I_s$ Diode static current kNumber of detections per period Boltzmann constant  $k_{\rm B}$ Maximum number of detections in an integration period  $k_{\text{max}}$  $\lambda$ Wavelength of light Photon arrival rate  $\lambda_{\mathsf{A}}$  $\lambda_{\mathrm{D}}$ Photon detection rate  $L_e$ Electron diffusion length Hole diffusion length  $L_h$ m $\mu_d(\lambda)$ Photon penetration depth in silicon of light Intrinsic doping level  $n_i$ *i*<sup>th</sup>-trap  $n_{t,i}$

Recombination center density

$N_t$

Normalized threshold voltage level  $\eta$ Breakdown probability empirical correction factor  $\eta_c$  $\pi$ Ρi  $P_{av}$ Junction avalanche probability  $P_{ab}$ Photon absorption probability Junction breakdown probability  $P_{b}$  $P_{\text{diff}}$ Probability carrier reaches depleted region  $P_e$ Probability of electron-initiated avalanche  $P_h$ Probability of hole-initiated avalanche  $P_r$ Optical power  $P_s$ SPAD power consumed per detection  $P_{t,i}$ i<sup>th</sup>-trap exponential pre-factor probability Normalized charge q $Q_t$ Total charge  $\mathbb{R}$ Real numbers  $R_d$ Diode resistance  $R_L$ Load resistance  $R_{XX}$ Autocorrelation function of random variable, XStandard deviation  $\sigma$ Carrier capture cross-section  $\sigma_0$ Time tTTemperature  $T_{\rm BG}$ Bit generation period Fall time  $t_f$ Rise time  $t_r$ Avalanche build-up time constant  $\tau_b$ Detector dead time  $\tau_{\rm dead}$ Overall detection time constant  $\tau_{det}$ Discriminator pulse time constant  $\tau_p$ Paralysable dead time  $\tau_{par}$ Saturation dead time  $\tau_{sat}$ Carrier transit time constant  $au_t$ i<sup>th</sup>-trap exponential decay time constant  $\tau_{t,i}$ Quenching time constant  $au_q$ Recharge time constant Angle of incidence  $\theta_0$  $T(\lambda, \theta_0)$ Transmittance function  $V_{\rm BR}$ SPAD breakdown voltage SPAD excess bias voltage  $V_{\rm EX}$  $V_{OP}$ SPAD operating voltage Thermal velocity  $v_{th}$  $W_d$ Depletion region width XGeneral random variable

$\mathbb{Z}_0^+$

Positive integers

## 1 Random number generation: fundamentals, methods and systems

#### 1.1 Preliminaries

The concept of randomness extends back several millennia, when dice-throwing and games of chance were used as methods for determining fate. Indeed, throughout human history, the many aspects of day-to-day life, which remain unpredictable, have greatly influenced our spirituality, medical practices, relationships, political systems and more. With the dedicated analysis of randomness starting in the early twentieth century, which led to the eventual formulation of mathematical axioms, randomness has now become a fundamental aspect of our scientific pursuits. In the computer sciences, randomness first stimulated the creation of developments in how data is quantified, stored, and transmitted, which is now classified as information theory.

More unexpected developments followed with the discovery of algorithmic randomness. Here, researchers showed that the introduction of a random sequence could improve an algorithm's ability to perform certain computations. For physicists, probability and stochastic theory are a fundamental part of the lexicon used to develop quantum mechanics. The advent of quantum science has not only shaped our perception of reality, but has also shifted our views on what we deem to be a scientifically conceivable system versus those that remain, for the time being, in the realm of science fiction.