Thèse n° 9884

# EPFL

### Hardware-Software Co-design for Improved Resource Utilization in DNN Accelerators

Présentée le 30 janvier 2023

Faculté des sciences et techniques de l'ingénieur Laboratoire de traitement des signaux 4 Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Ahmet Caner YÜZÜGÜLER

Acceptée sur proposition du jury

Prof. A. Roshan Zamir, président du jury Prof. P. Frossard, directeur de thèse Prof. L. Benini, rapporteur Dr C. Malossi, rapporteur Prof. D. Atienza, rapporteur

École polytechnique fédérale de Lausanne

2023

"Science is the poetry of reality." — Richard Dawkins

To my beloved family...

## Acknowledgements

This thesis is the culmination of a journey that was long and arduous, but ultimately, incredibly rewarding. It would not have been possible without the support and guidance of my colleagues and friends, and for that, I am eternally grateful.

My most sincere thanks go to my advisor, Professor Pascal Frossard, for his ceaseless support and guidance. Besides his vast technical contributions, Pascal's remarkable leadership style has made this thesis possible. Even during the most difficult moments of my Ph.D., he managed to find a way to motivate me to move forward. Every piece of feedback that I received from him was on point, considerate, and carefully crafted in a way that reassured me that I was in the right path. Therefore, I consider myself extremely fortunate to have been Pascal's student, and I will definitely miss working under his supervision and in the superb working environment that he has created in LTS4.

Next, I would like to thank the members of my thesis committee, Professor Amir Zamir, Professor David Atienza Alonso, Professor Luca Benini, and Dr. Cristiano Malossi for their time to review this thesis and for the valuable feedback that they provided. I would also like to thank Professor Babak Falsafi for supervising my research that constitutes the backbone of the third chapter in this thesis. I would like to send a special thanks to Professor Elif Vural, who supervised my first research project in LTS4, and inspired me to pursue a career in research. My deepest gratitude goes to my mentor, Professor Giovanni De Micheli, for his support throughout my Ph.D. I would also like to acknowledge the help of the Hasler Foundation in this thesis, for funding my research and creating an opportunity for me to achieve my goals.

The greatest sources of support throughout my Ph.D. have been my wonderful flatmates and closest friends, Chiara and Nick. Not only did we share a cozy and welcoming home, but we also shared similar goals and faced similar challenges. Together, we navigated the difficulties of the COVID-19 lockdowns and it would have been awfully harder without their presence. The time we spent together will always hold a special place in my memories and I look forward to continuing our friendship long after the completion of our studies.

I am thankful to all of my past and current colleagues at LTS4, including Mireille, Tolis, Beril, Isabela, Ádám, Clément, Guille, Ortal, Yamin, Harshitha, Javier, William, Jelena, and Caroline. With them, I had many fruitful discussions, delightful lunch breaks, and wonderful winter retreats. I would like to extend my special thanks to Nikos, who greatly contributed to the fourth and fifth chapters of this thesis. A special thanks also goes to Abdellah, who kindly helped me to translate the abstract of this thesis to French.

I am deeply grateful to my former colleagues from PARSA, Yunho, Mario, Arash, Sid, Ognjen, Simla, and Canberk. They have been an integral part of my Ph.D. and their help and support have been invaluable. I will always treasure the memories we shared together. My special thanks go to Yunho, Mario, and Canberk, who have made huge contributions to the third chapter of this thesis. Their expertise and contributions have been critical to the success of my research.

I feel lucky to have a fantastic circle of Turkish friends in Lausanne, Kağan, Arman, Didem, Doruk, and Sinem, with whom I shared countless memories and experiences while enjoying the comfort of speaking in my mother tongue.

Last but not least, I must express my deepest gratitude to my beloved family. My brother, Can, and my sister-in-law, Ayça, have been constant sources of support for me over the last years. My beloved newborn nephew, Ege, brought immeasurable joy and excitement to my days spent writing this thesis. I wish him a long and fulfilling life, full of success and happiness. Finally, my deepest appreciation goes to my parents, Mutlu and Kudret, who have dedicated their entire lives to ensuring our happiness and well-being. Their unwavering support has been the driving force behind my Ph.D. journey, and my heart is filled with an overwhelming sense of gratitude for everything they have done for me.

Lausanne, 13 January 2023

A.C. Yüzügüler

## Abstract

Deep neural networks (DNN) have become an essential tool to tackle challenging tasks in many fields of computer science. However, their high computational complexity limits their applicability. Specialized DNN accelerators have been developed to accommodate the high computational complexity of DNN inference, but the mismatch between the accelerators and DNN models prevents unlocking their full potential.

In this thesis, we address the mismatch between accelerators and DNN models from both hardware and software perspectives. First, we investigate one of the most widely used architectures in DNN accelerators, i.e., systolic arrays, and identify the leading cause of underperformance in DNN inference, namely dimension mismatches between arrays and DNN layers. We analyze the characteristics of today's popular DNN models, perform an extensive design-space exploration and propose a novel scale-out systolic array architecture that maximizes the effective throughput (i.e., FLOPS per second) for a given set of target DNN workloads.

Then, we go beyond the limits of what can be achieved with hardware optimization and focus on optimizing DNN architectures to improve the resource utilization at the target accelerators. To that end, we study differentiable neural architecture search frameworks, which automate the creation of DNN architectures using efficient gradient-descent optimizers. We introduce a novel computational model for the utilization of systolic arrays and propose a novel utilization-aware neural architecture search framework. The proposed framework is capable of creating DNN models with improved resource utilization on target accelerators, which permits to perform DNN inference more efficiently and faster.

The existing neural architecture search framework searches for channel dimensions of a DNN model in a fixed search space, which requires to manually design complex search spaces. However, designing a search space is a nontrivial task that requires heuristics and domain expertise, which undermines the effectiveness and practicality of neural architecture search. To eliminate the necessity to predefine search space, we propose a flexible channel masking method, which dynamically adjusts the search space based on the progress of architecture search. We introduce the differentiable neural architecture search framework that uses the

flexible channel masking method, which obviates the need for manually designing a search space. We demonstrate through extensive experiments that the proposed framework significantly reduces the search time and memory requirements compared to the existing neural architecture search framework with fixed search spaces.

Overall, this thesis proposes hardware and software co-design techniques to improve the performance of DNN inference. We demonstrate that the proposed scale-out systolic array architecture combined with DNNs optimized using the proposed neural architecture search frameworks exhibits significantly higher resource utilization. Consequently, the proposed methods enable faster and more efficient DNN inference, improving the effectiveness of DNN applications on resource-constraint platforms.

Keywords: deep neural networks, systolic arrays, neural architecture search

## Résumé

Les réseaux de neurones profonds (DNN) sont devenus des outils essentiels pour aborder les problèmes exigeants et complexes dans plusieurs domaines de la science de l'information. Cependant, la complexité computationnelle de ces modèles profonds limite leur champs d'application. Des accélérateurs spécialisés pour les DNN ont été développés pour répondre à ce problème de complexité de calcul des DNN, mais l'inadéquation entre les accélérateurs et les DNN nous empêche de tirer profit de l'entier du potentiel des accélérateurs.

Dans cette thèse, nous étudions deux perspectives de cette inadéquation, entre les accélérateurs et les modèles du DNN, qui peuvent se manifester sous forme de problèmes hardware ou software. Premièrement, nous investiguons une des architectures les plus utilisées parmi les accélérateurs de DNN, i.e, systolic arrays, et nous identifions la cause fondamentale de la sous-performance durant l'inférence des DNN, qui est l'inadéquation entre les dimensions des arrays et celles des couches des DNN. Nous analysons les caractéristiques des modèles DNN les plus populaires, effectuons une exploration extensive du design-space et proposons une méthode appelée "scale-out systolic array" qui maximise le débit effectif (i.e., FLOPS per second) pour un certain ensemble de charge de travail d'un DNN.

Deuxièmement, nous dépassons les limites de ce que nous pouvons obtenir par une optimisation des hardwares, en focalisant sur l'optimisation des architectures des DNN qui améliorent l'utilisation des ressources d'un accélérateur hardware. A cet effet, nous étudions des méthodes de recherche qui automatisent la création des architectures de DNNs en utilisant une optimisation efficace par descente de gradient. Nous introduisons un nouveau modèle de calcul pour l'utilisation des "systolic arrays" et proposons un nouveau cadre intitulé "utilization-aware neural architecture search". Le cadre proposé est capable de créer des modèles de DNNs avec des utilisations de ressources améliorées pour des accélérateurs cibles, ce qui permet d'effectuer une inférence plus efficace et rapide.

Le cadre existant des "neural architecture search" cherche à trouver les dimensions des channels d'un modèles DNNs dans un espace de recherche fixé, ce qui nécessite un choix manuel d'un espace de recherche complexe. Néanmoins, le choix d'un espace de recherche

représente une tâche non triviale qui exige des heuristiques et une expertise, ce qui affaiblit l'efficacité et la praticité du neural architecture search. Pour éliminer la nécessité de prédéfinir des espaces de recherche, nous proposons une méthode flexible de masquage de channel, qui ajuste dynamiquement l'espace de recherche en se basant sur l'evaluation de la function de recherche. Nous introduisons le cadre nommé; "differentiable neural architecture search", qui utilise la méthode flexible du masquage, qui évite le besoin d'un choix manuel d'espaces de recherche. Nous démontrons à travers différentes expériences et en comparant avec différents modèles que le cadre proposé diminue le temps de recherche et aussi les exigences en termes de mémoire de calcul.

En guise de conclusion, cette thèse propose des techniques de conception conjointe de hardware et software qui améliorent les performances de l'inférence des DNNs. Nous démontrons qu'optimiser les DNN en utilisant le cadre proposé "differentiable neural architecture search" et en le combinant avec la méthode scale-out systolic array, permet une utilisation très élevée des ressources. Par conséquent, la méthode suggérée permet une inférence efficace et rapide des DNN, ce qui améliore l'efficacité de l'application des DNNs sur les plateformes à ressources limitées.

Mots clefs : Réseaux de neurones profonds (DNN), systolic arrays, neural architecture search

## Contents

| Acknowledgements |                           |         |                                        | i    |

|------------------|---------------------------|---------|----------------------------------------|------|

| Ał               | ostra                     | ct (Eng | (lish/Français)                        | iii  |

| Li               | List of figures           |         |                                        |      |

| Li               | st of                     | tables  |                                        | xiii |

| 1                | Intr                      | oducti  | ion                                    | 1    |

|                  | 1.1                       | Multi   | -pod Systolic Architectures            | 1    |

|                  | 1.2                       | Hardy   | ware-aware Neural Architecture Search  | 3    |

|                  | 1.3                       | Thesis  | s Outline                              | 5    |

| 2                | Rela                      | ted W   | ork                                    | 7    |

|                  | 2.1                       | DNN     | Accelerators                           | 7    |

|                  | 2.2                       | Neura   | al Architecture Search                 | 10   |

|                  |                           | 2.2.1   | DNN optimization                       | 10   |

|                  |                           | 2.2.2   | Optimization strategy                  | 11   |

|                  |                           | 2.2.3   | Architecture evaluation                | 12   |

|                  |                           | 2.2.4   | Search space                           | 13   |

| 3                | Scale-out Systolic Arrays |         |                                        |      |

|                  | 3.1                       | Key P   | illars of Multi-pod Accelerator Design | 18   |

|                  |                           | 3.1.1   | Optimal Systolic Array Size            | 18   |

|                  |                           | 3.1.2   | Interconnection Network                | 24   |

|                  |                           | 3.1.3   | Tiling & Scheduling                    | 26   |

|                  | 3.2                       | Scale   | -out Systolic Arrays                   | 27   |

|                  |                           | 3.2.1   | Systolic Pod Microarchitecture         | 27   |

|                  |                           | 3.2.2   | Offline Scheduling Algorithm           | 29   |

|                  | 3.3                       | Exper   | iments                                 | 31   |

|                  |                           | 3.3.1   | Methodology                            | 31   |

|                  |                           | 3.3.2   | Results                                | 31   |

|                  |                           | 3.3.3   | Array Granularity                      | 32   |

|                  |                           | 3.3.4   | Interconnect                           | 35   |

|                  |                           | 3.3.5   | Tiling                                 | 37   |

|   |                         | 3.3.6 Memory                                                    | 37        |

|---|-------------------------|-----------------------------------------------------------------|-----------|

|   |                         | 3.3.7 RTL Synthesis                                             | 38        |

|   |                         | 3.3.8 Comparison to Prior Inference Accelerators                | 38        |

|   | 3.4                     | Conclusion                                                      | 39        |

|   |                         |                                                                 |           |

| 4 |                         | ization-Aware Neural Architecture Search                        | 41        |

|   | 4.1                     |                                                                 | 42        |

|   | 4.2                     | I I I I I I I I I I I I I I I I I I I                           | 46        |

|   |                         | 4.2.1 Approximation of the utilization function                 | 46        |

|   |                         | 4.2.2 Multi-objective loss function                             | 47        |

|   |                         | 4.2.3 NAS algorithm                                             | 47        |

|   | 4.3                     | Experiments                                                     | 47        |

|   |                         | 4.3.1 CIFAR10 experiments                                       | 50        |

|   |                         | 4.3.2 ImageNet100 experiments                                   | 51        |

|   |                         | 4.3.3 Sensitivity to array size                                 | 52        |

|   | 4.4                     | Conclusion                                                      | 53        |

| 5 | Fley                    | kible Channel Dimensions for Differentiable Architecture Search | 55        |

| U | 5.1                     |                                                                 | 55        |

|   | 5.2                     | Differentiable Channel Masking                                  | 57        |

|   | 5.3                     | FlexCHarts                                                      | 59        |

|   | 0.0                     | 5.3.1 Flexible channel masking                                  | 59        |

|   |                         | 5.3.2 Dynamic channel allocation                                | 61        |

|   | 5.4                     | -                                                               | 63        |

|   | 5.1                     | 5.4.1 Experimental setup                                        | 63        |

|   |                         | 5.4.2 Performance of the differentiable channel search          | 64        |

|   |                         | 5.4.3 Comparison with other dimension adaptation methods        | 65        |

|   |                         | 5.4.4 Channel search for improved resource utilization          | 66        |

|   | 5.5                     | Conclusion                                                      | 67        |

|   | 5.5                     |                                                                 | 07        |

| 6 | Con                     | clusions                                                        | 69        |

|   | 6.1                     | Summary                                                         | 69        |

|   | 6.2                     | Future Directions                                               | 70        |

|   | A                       | en die of Chanton (                                             | 70        |

| A |                         | endix of Chapter 4 Micro-architecture search                    | <b>73</b> |

|   |                         |                                                                 |           |

|   |                         | Utilization and Runtime details                                 | 73        |

|   | A.3                     | Additional experimental results                                 | 75        |

|   |                         | A.3.1 CIFAR10 dataset                                           | 75        |

|   | A.4                     | Hyperparameters                                                 | 78        |

| B | Appendix of Chapter 5 7 |                                                                 |           |

| _ |                         | Channel ranges of DMask baselines                               | . e       |

|   |                         |                                                                 |           |

| CONTENTS |  |  |

|----------|--|--|

|          |  |  |

| Bibliography     | 91 |

|------------------|----|

| Curriculum Vitae | 93 |

# List of Figures

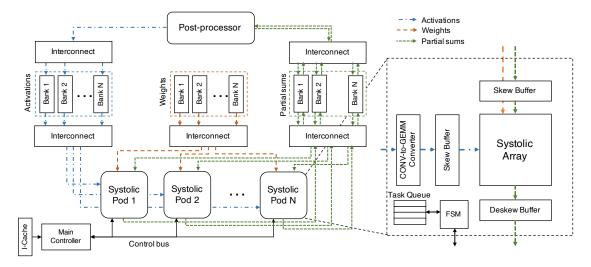

| 1.1   | General overview of a multi-pod systolic architecture.                                                                                                            | 2  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2   | General overview of a hardware-aware differentiable neural architecture search.                                                                                   | 4  |

| 2.1   | Three categories of spatial architectures used in DNN accelerators                                                                                                | 8  |

| 3.1   | A weight-stationary systolic array with $r$ rows and $c$ columns. Activations are assumed to traverse along the rows from left to right, weights and partial sums |    |

|       | traverse along the columns from top to bottom.                                                                                                                    | 16 |

| 3.2   | Three main factors of underutilization in systolic arrays.                                                                                                        | 17 |

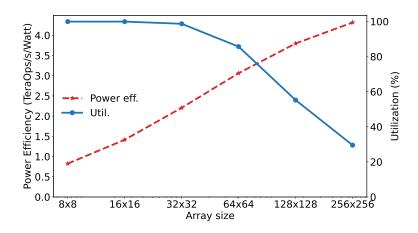

| 3.3   | Trade-off between power efficiency and utilization in systolic arrays with respect                                                                                |    |

|       | to the array dimensions.                                                                                                                                          | 19 |

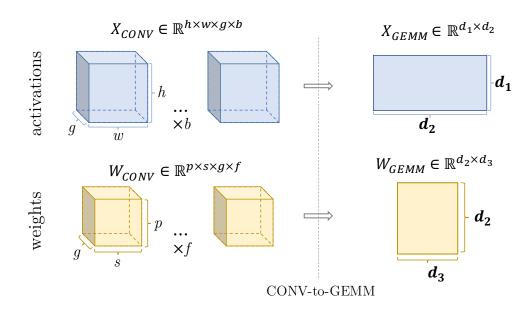

| 3.4   | Illustration of CONV-to-GEMM conversion. Four-dimensional activation and                                                                                          |    |

|       | weight tensors of a convolution operation are reshaped into two-dimensional                                                                                       |    |

|       | matrices.                                                                                                                                                         | 20 |

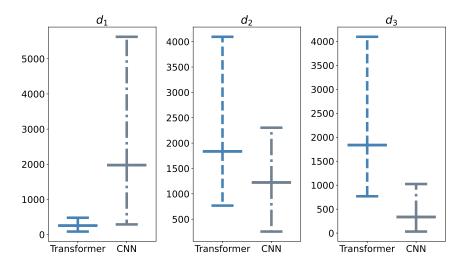

| 3.5   | Range of the matrix dimensions for the GEMM operations in BERT and CNN                                                                                            |    |

|       | models. $d_1$ denotes the first dimension of activation matrix ( $X_{GEMM}$ ) and $d_2$ and                                                                       |    |

|       | $d_3$ denote the first and second dimension of weight matrix ( $W_{GEMM}$ ). Horizontal                                                                           |    |

|       | lines show 10th percentile, average, and 90th percentiles                                                                                                         | 21 |

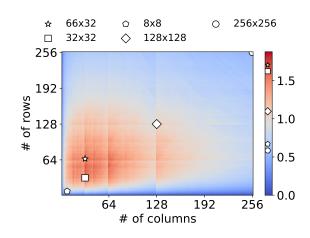

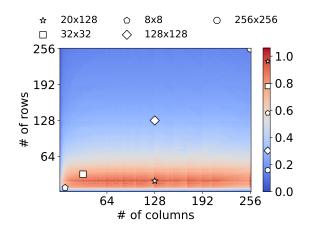

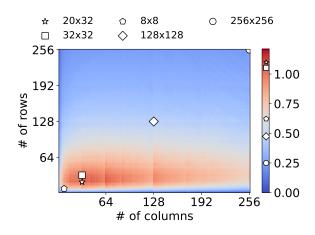

| 3.6   | Design space exploration for systolic arrays. Colormap represents the effective                                                                                   |    |

| 0.7   | throughput (TeraOps/s) per Watt.                                                                                                                                  | 23 |

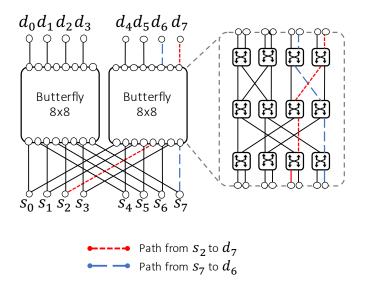

| 3.7   | An 8 × 8 Butterfly network with an expansion factor of 2. Routings from $s_2$ to $d_7$                                                                            | 25 |

| 2.0   | and from $s_7$ to $d_6$ are shown with blue and red lines, respectively                                                                                           | 25 |

| 3.8   | Overview of the proposed architecture, with the internals of the Systolic Pod shown on the right-hand side.                                                       | 28 |

| 2.0   | shown on the right-hand side                                                                                                                                      | 20 |

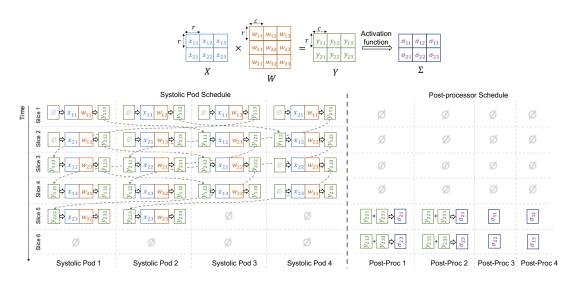

| 3.9   | by an activation function $Y \to \Sigma$ . The example shows the scheduling for four                                                                              |    |

|       | systolic pods with array sizes of $r \times c$ , and four post-processors                                                                                         | 29 |

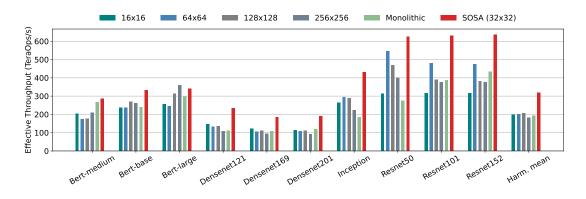

| 3 10  | Effective throughput of SOSA with various array sizes and Monolithic baseline                                                                                     | 23 |

| 5.10  | for various DNN benchmarks. All values are normalized to 400 Watts                                                                                                | 33 |

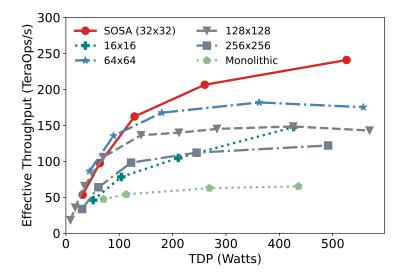

| 3 1 1 | Effective throughput of SOSA and Monolithic baseline for various TDP values.                                                                                      | 00 |

| 0.11  | For Monolithic baseline, we assume a single systolic array and vary its dimen-                                                                                    |    |

|       | sions between $400 \times 400$ and $1024 \times 1024$ ; whereas for SOSA designs, we use keep                                                                     |    |

|       | the array size constant and vary the number of parallel pods                                                                                                      | 34 |

|       | J J J F F F F F F F F F F F F F F F F F                                                                                                                           |    |

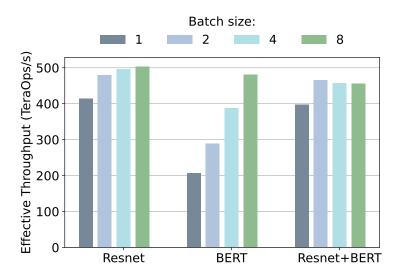

| 3.12 | Effective throughput of SOSA for varying batch sizes for Resnet only, BERT only,    | 05 |

|------|-------------------------------------------------------------------------------------|----|

|      | and both Resnet and BERT in parallel.                                               | 35 |

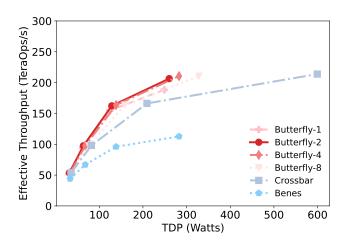

| 3.13 | Effective throughput versus TDP for various interconnect types. Points represent    |    |

|      | the number of pods, which are equal to 32, 64, 128, and 256                         | 36 |

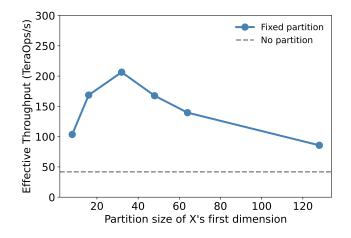

|      | Effective throughput versus data partition size for activation matrices.            | 36 |

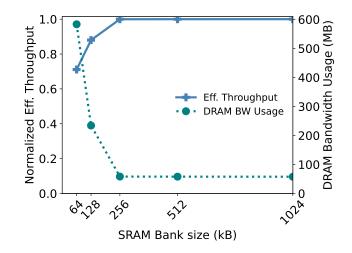

| 3.15 | Effective throughput (normalized to maximum value) and off-chip DRAM usage          |    |

|      | for varying on-chip SRAM bank sizes.                                                | 37 |

| 4.1  | Tiling of a GEMM operation onto a systolic array.                                   | 43 |

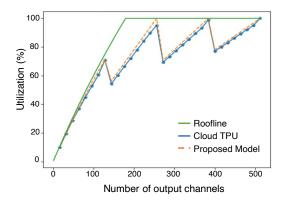

| 4.2  | Measured utilization on Cloud TPUv2 versus predicted utilization with roofline      |    |

|      | and the proposed model.                                                             | 46 |

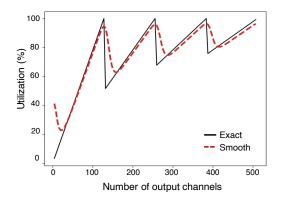

| 4.3  | Proposed utilization model with exact ceil function and its smooth approxima-       |    |

|      | tion using the generalised logistic function.                                       | 46 |

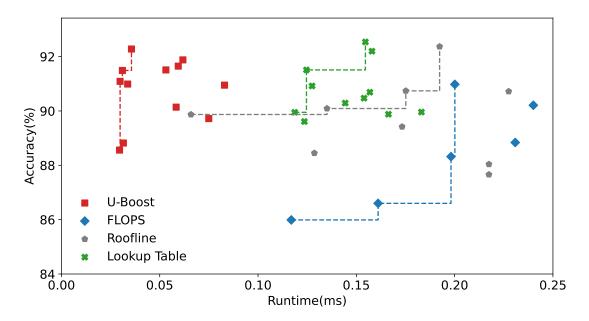

| 4.4  | Experiments on CIFAR10 dataset. Upper left corner is optimal. The dashed lines      |    |

|      | connect the points in the Pareto Front of each method.                              | 49 |

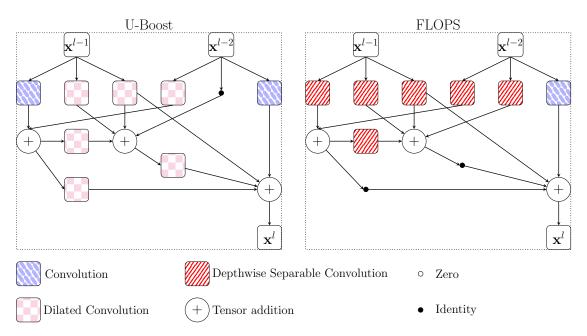

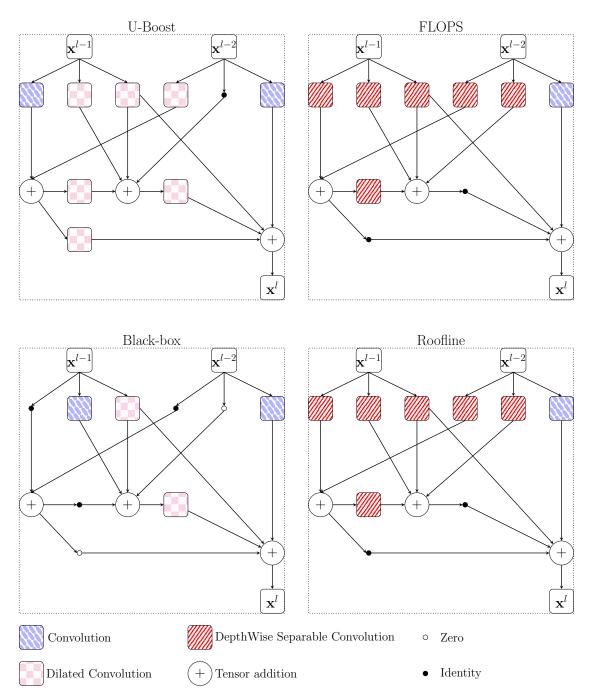

| 4.5  | Visualization of the CIFAR10 cells obtained from U-Boost and FLOPS models           |    |

|      | during the microarchitecture search stage                                           | 50 |

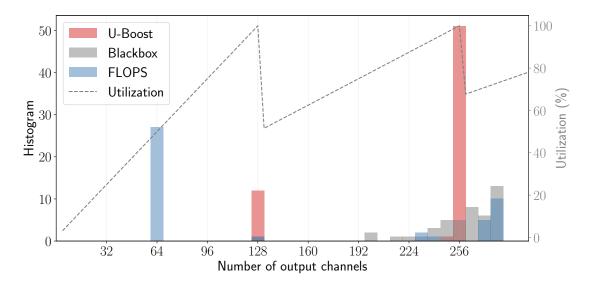

| 4.6  | Histogram of channel dimensions found by U-Boost as well as FLOPS and Black-        |    |

|      | box baselines on CIFAR10 dataset.                                                   | 51 |

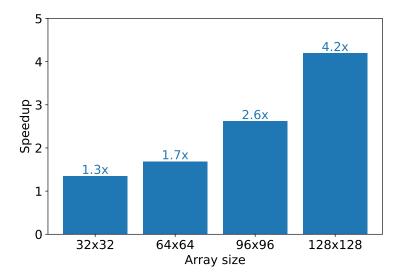

| 4.7  | Speedups obtained using U-Boost over the FLOPS baseline for various array sizes.    | 53 |

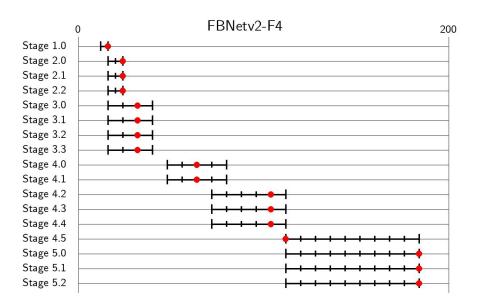

| 5.1  | Prior work's search space for channel dimensions [Wan et al., 2020]. Rows cor-      |    |

|      | respond to the channel range (between 0 and 200) of the layers in FBNetv2-F4.       |    |

|      | Ticks denote the options for channel dimensions and red circles represent the       |    |

|      | channel dimensions found.                                                           | 56 |

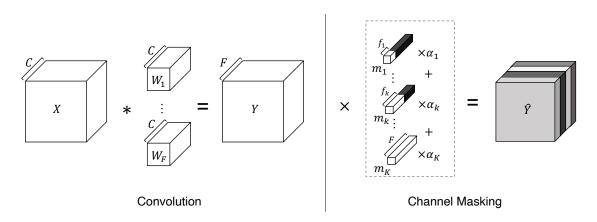

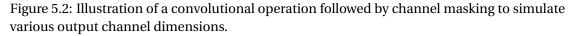

| 5.2  | Illustration of a convolutional operation followed by channel masking to simu-      |    |

|      | late various output channel dimensions.                                             | 58 |

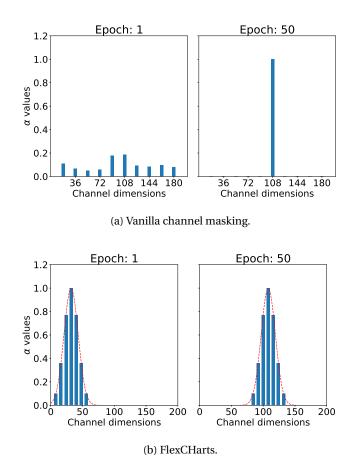

| 5.3  | An example of $\alpha$ values in vanilla channel masking method versus the proposed |    |

|      | FlexCHarts methods between the first and last epoch of a search.                    | 60 |

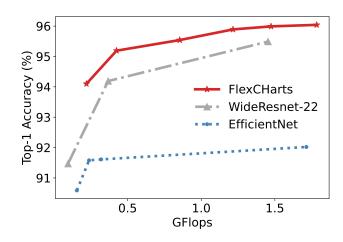

| 5.4  | Accuracy on CIFAR10 versus computational complexity in terms of FLOPS for           |    |

|      | DNN architectures found by FlexCHarts as well as the baseline WideResnet and        |    |

|      | EfficientNet models.                                                                | 65 |

| A.1  | Cell architectures found for $\lambda = 0.1$ on the CIFAR10 dataset.                | 77 |

## List of Tables

| 3.1 | Interconnect performance metrics generated by our cycle-accurate simulator averaged across all the workloads.                                                                                                                                                                 | 25 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Performance of SOSA with various array sizes. The effective throughput is the                                                                                                                                                                                                 | _0 |

| 0.2 | harmonic mean of CNN and Transformer models.                                                                                                                                                                                                                                  | 32 |

| 3.3 | Optimal array size for varying batch size and number of parallel workloads                                                                                                                                                                                                    | 35 |

| 3.4 | Power and area breakdown of the proposed architecture for 256 systolic pods.<br>The design is synthesized in Synopsys Design Compiler using the TSMC 28nm<br>library for up to 16 systolic pods and the results are extrapolated for 256 systolic                             |    |

|     | pods.                                                                                                                                                                                                                                                                         | 38 |

| 3.5 | Summary of the prior inference accelerators and SOSA. <sup>†</sup> Results of Resnet50 with a batch size of one. <sup>*</sup> Implemented on an Intel Arria 10 GX 1150 FPGA. <sup>‡</sup> For a fair comparison, we scaled SOSA down to 64 systolic pods to have equal number |    |

|     | of PEs with TPUv4.                                                                                                                                                                                                                                                            | 39 |

| 4.1 | Utilizations and runtimes for various types of DNN layers                                                                                                                                                                                                                     | 45 |

| 4.2 | Experimental results for ImageNet100 experiments. Underlined measurements show best per column ( $\lambda$ ), bold show best per metric. Number of parameters                                                                                                                 |    |

|     | reported in millions.                                                                                                                                                                                                                                                         | 52 |

| 5.1 | Results of the DMaskingNAS and FlexCHarts methods targeting low and high-<br>resource scenarios. Check and cross marks indicate whether the requirement is                                                                                                                    |    |

|     | satisfied or not.                                                                                                                                                                                                                                                             | 64 |

| 5.2 | Comparison of DMaskingNAS and FlexCHarts for utilization-aware search                                                                                                                                                                                                         | 66 |

| A.1 | Microarchitecture search space. DWS: Depthwise Separable                                                                                                                                                                                                                      | 73 |

| A.2 | Utilizations and runtimes for all building blocks. Symbols explained in text. †                                                                                                                                                                                               |    |

|     | includes all other layer types: identity, zero, maxpooling, ReLUs                                                                                                                                                                                                             | 74 |

| A.3 | Experimental results for CIFAR10 over 3 random seeds.                                                                                                                                                                                                                         | 76 |

| A.4 | Experiment Hyperparameters. – indicates that the ImageNet100 experiment<br>uses the same settings as the CIFAR10 experiment. †: the architecture for                                                                                                                          |    |

|     | ImageNet100 is produced by search on CIFAR10. MS: micro-architecture search, CS: channel search, FT: final training.                                                                                                                                                          | 78 |

|     | -                                                                                                                                                                                                                                                                             |    |

B.1 Channel ranges of DMask-small and Dmask-large baselines for the experiments in Section 5.4.2 and DMask-systolic for the experiments in Section 5.4.4. . . . . 79

## **1** Introduction

Deep neural networks (DNN) have unlocked an unprecedented potential in solving a wide range of challenging problems in various fields of science and engineering. The success of DNNs is mostly attained due to their capability to automatically extract meaningful features from large amounts of data whereas classical algorithms rather rely on human heuristics and engineering efforts to come up with useful features. With the ever-growing amounts of data collected every day, DNNs will undoubtedly remain for the foreseeable future as an indispensable tool for scientists and engineers to learn effective representations of information in various application domains.

While the principles of deep learning date back to mid-20th century, the recent increase in the popularity of DNNs and their widespread adoption in numerous domains coincide with the advents in parallel computing in the modern era. With their high computational complexity, DNN applications have initially resorted to hardware platforms such as field programmable gate arrays (FPGA) [Farabet et al., 2011] and graphic processing units (GPU) [Krizhevsky et al., 2012]. However, the immense volume of DNN workloads in datacenters and mobile devices has encouraged researchers to develop specialized hardware architectures for DNNs, which has led to the emergence of highly efficient and powerful DNN accelerators [Jouppi et al., 2017; Hock, 2019; Liao et al., 2019].

#### 1.1 Multi-pod Systolic Architectures

One of the most widely used specialized hardware architectures in DNN accelerators is *systolic arrays*. In systolic arrays, processing elements are typically organized in a two-dimensional grid, where the adjacent processing elements can efficiently share data with each other through direct links. In each cycle, processing elements retrieve data from a set of adjacent neighbors, perform a multiply-and-accumulate operation, and pass the data and intermediate results to another set of adjacent neighbors <sup>I</sup>. While systolic arrays can achieve exceptional power

<sup>&</sup>lt;sup>I</sup>The name "systolic" comes from the rhythmical pattern of data movement due to its resemblance to a heartbeat.

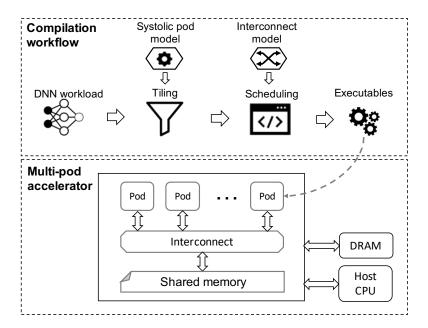

Figure 1.1: General overview of a multi-pod systolic architecture.

efficiency thank to this unique pattern of data movement, they heavily suffer from underutilization due to mismatches between the arrays and DNNs, which prevents the effective usage of available computational resources. For instance, the average resource utilization while processing a DNN in the latest version of a TPU, which is a systolic-array based accelerator, is only 33% [Jouppi et al., 2021], underlining the severity of underutilization in DNN accelerators.

The leading source of underutilization in systolic arrays originates from mismatches between arrays and DNN models [Jouppi et al., 2017; Kung et al., 2019]. When model dimensions (e.g., number of channels and filters) is smaller than the array dimensions, the excess rows and/or columns in the systolic array become idle, resulting in underutilization. A trivial solution to this problem would be to reduce the array dimensions of systolic arrays. However, data reuse in systolic arrays is tightly correlated with the array size. Thus, while small systolic arrays may offer a remedy to the underutilization problem, they would suffer from low data reuse and consequently from poor power efficiency. This intricate relation between power efficiency and utilization in systolic arrays poses a challenging optimization problem that must be carefully addressed while designing accelerators with systolic arrays.

Because the underutilization problem places an upper bound on the size of systolic arrays, architectures with multiple systolic arrays have emerged [Kung et al., 2019], which we simply refer to as *multi-pod* architectures throughout this thesis. These architectures either partition a single DNN workload and run different partitions in parallel pods, or they rely on task-level parallelism and run multiple DNN workloads in parallel pods [Jouppi et al., 2021; Baek et al., 2020].

Figure 1.1 depicts the overall diagram of a multi-pod inference accelerator, where each pod

#### Introduction

includes a systolic array and necessary buffers and peripherals. The pods are connected to an on-chip shared memory through an interconnect network. DNN models and intermediate data are typically stored in on-chip memory for temporal reuse. The accelerators typically have interfaces to off-chip DRAM to store data when the on-chip memory size is not sufficient and a host CPU to receive instructions. In order to map workloads to multiple systolic arrays, DNN layers are first partitioned into tile operations of sizes that match a pod's array dimensions. Then, a scheduler optimizes the mapping of tile operations to pods to maximize parallelism and throughput.

Achieving scalability and high utilization in multi-pod accelerators requires design optimizations in various aspects. First of all, systolic array dimensions should be carefully selected to find a sweet-spot between power efficiency and utilization for the target DNN workloads. Second, the pods should be connected to each other through an interconnect topology that allows sufficient bandwidth with high efficiency. Third, the compiler should be capable of tiling, mapping and scheduling DNN workloads in a way to make use of maximum number of pods in parallel. These design requirements and constraints pose a significant challenge while designing multi-pod accelerators. In this thesis, we address these challenges and propose techniques to improve the resource utilization of multi-pod systolic architectures.

#### 1.2 Hardware-aware Neural Architecture Search

Despite the improvements in hardware architectures, the performance of DNN accelerators varies based on the computational characteristics of the DNN workloads. Therefore, DNNs must also be designed or optimized to improve their compatibility with the target compute platforms. Many aspects of DNNs such as layer types and dimensions have considerable impact on their computational characteristics. However, designing DNNs while taking their computational characteristics into account is a challenging task for developers.

To automate the task of designing DNNs, researchers have proposed *neural architecture search*, which aims to replace design heuristics with optimization algorithms. Such neural architecture search frameworks are often *hardware-aware* and optimizes the DNNs not only for the accuracy at the given task but also for their computational cost at target platforms. The early versions of neural architecture search frameworks have resorted to evolutionary algorithms or reinforcement learning, which require a substantial computational cost to solve this multi-objective optimization problem. However, recent improvements such as *differentiable* neural architecture search frameworks have significantly reduced the cost of design optimization, which becomes practical for a wide range of applications.

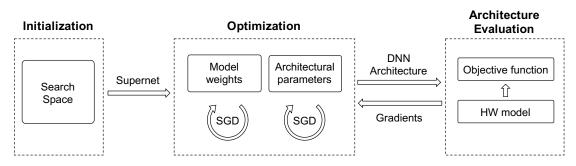

Figure 1.2 depicts the main components of a hardware-aware differentiable neural architecture search framework. We can divide a neural architecture search framework into three phases, namely initialization, optimization, architecture evaluation. The initialization phase includes designing a search space, which contains the set of variables that defines possible candidate architectures. Based on these variables, one obtains an overparameterized DNN model, which

Figure 1.2: General overview of a hardware-aware differentiable neural architecture search.

is also known as *supernet*. The supernet contains both trainable *model weights* that define its functionality as well as a set of *architecture parameters* that simulate different architectural choices. During the optimization stage, the supernet's model weights and architectural parameters are jointly optimized using gradient descent. The gradients for these optimization steps are obtained by calculating a loss value using a batch of training data. Finally, in case of a hardware-aware neural architecture search, hardware-related terms are included in the objective function (e.g., latency), which are typically estimated using a hardware model.

Estimating the hardware-related metrics accurately and efficiently is, however, critical to obtain DNNs that perform well on target platforms. While simplistic hardware models such as FLOPS per second or roofline [Williams et al., 2009] might give rough estimates about the latency or throughput of selected DNNs, they do not capture the nonlinear runtime characteristics of systolic architectures. This leads to discrepancies between estimated and ground-truth values, resulting in DNNs that do not perform well on the target platforms. To overcome the discrepancy between estimated and ground-truth values, researchers have proposed to use *black-box* models, in which measurements from physical devices are stored in lookup tables and retrieved during the architecture search. However, such black-box models are not differentiable; thus, they can not be effectively used in differentiable neural architecture search frameworks that require gradient calculations. Overall, the existing methods to estimate hardware-related metrics are unfortunately either inaccurate for systolic architectures or incompatible with the efficient neural architecture search frameworks.

Besides the challenges in estimating hardware-related metrics, another obstacle to develop an effective and efficient hardware-aware neural architecture search relates to the quality of their search space. Because the search space defines all possible DNN configurations, having a poor search space design may lead to finding suboptimal DNNs. A trivial solution to this problem might be to use an excessively large search space to ensure that it covers the optimal DNN configurations, but this would introduce large amounts of redundant computation, increasing the computational cost of the search. As a result, the existing frameworks rely on domain experts to carefully design an effective search space, which defeats the purpose of automating the design of DNNs. Due to these limitations inherent to their search space, existing frameworks are not capable of finding optimal DNNs that perform well at target platforms. In this thesis, we address the challenges in estimating hardware-related metrics for systolic architectures and limitations inherent to the search space of neural architecture search frameworks.

#### 1.3 Thesis Outline

This thesis addresses the underutilization problem in DNN inference accelerators and proposes solutions from both hardware and software perspectives. We first study the fundamental design trade-offs in systolic arrays and perform a design space exploration for server-grade accelerators targeting convolutional and moderately-sized Transformer models. Then, we study three key design aspects in multi-pod systolic architectures and identify the optimal array granularity, interconnect topology, and tiling strategies. Based on our findings from our design space exploration and analysis on these three key design pillars, we propose a novel scale-out systolic array architecture. We demonstrate that the proposed architecture achieves higher resource utilization and effective throughput in DNN inference workloads compared to the baseline designs.

Then, we turn our focus towards the optimization of DNN models to improve their resource utilization on target inference platforms. Using our insights from the scale-out systolic array architecture, we develop an analytical model for resource utilization on systolic architectures and propose a smooth approximation that makes it suitable for effective optimization methods such as differentiable architecture search. We then develop the novel utilization-aware differentiable neural architecture search framework, which allows finding DNNs that exhibit high resource utilization on target inference platforms. Our experiments on popular vision tasks such image classification show that the DNNs found by the proposed framework achieve higher accuracy and/or shorter inference latency thanks to more effective usage of computational resources at target platforms.

To improve the efficiency and practicality of the proposed utilization-aware neural architecture search framework, we finally address the limitations inherent to the search space of the neural architecture search. We propose a flexible search space, which allows finding the optimal channel dimensions for DNNs without the need for manually designing a search space, and a novel dynamic channel allocation mechanism that enables modifying the dimensions of a supernet efficiently in neural architecture search. We show that the proposed flexible search space and the dynamic channel allocation mechanism obviate the need for manually designing search spaces for channel dimensions and improves the efficiency of neural architecture search compared to the existing frameworks with fixed search spaces.

In short, this thesis makes the following contributions:

• We analyze the workload characteristics of widely used CNN and Transformer models and perform a design space exploration to find the optimal array dimensions in systolic

architectures.

- We study various interconnect topologies and identify the ideal topology to connect large numbers of systolic pods in DNN accelerators.

- We study tiling and scheduling methods for DNN workloads and propose a novel tiling strategy for multi-pod systolic architectures.

- We propose the novel scale-out systolic array architecture and show that it outperforms the existing architectures in DNN inference workloads.

- We develop an analytical model for resource utilization in systolic arrays and propose a smooth approximation to make this model differentiable and amenable to effective optimization.

- We propose a novel utilization-aware differentiable neural architecture search framework that improves the resource utilization of DNNs on target accelerators.

- We introduce a flexible search space for channel dimensions in differentiable neural architecture search and we propose a novel dynamic channel allocation mechanism to improve the efficiency of differentiable neural architecture search.

The rest of this thesis is organized as follows: We first introduce the prior work on DNN accelerators and neural architecture search in Chapter 2. Then, we explain the key design considerations for multi-pod systolic architectures and propose the scale-out systolic array architecture in Chapter 3. e introduce our analytical model for resource utilization and propose the utilization-aware differentiable neural architecture search framework in Chapter 4. Then, we elaborate on the flexible search space for channel dimensions and the dynamic channel allocation mechanism in Chapter 5. Finally, we provide a summary of the contributions that we make in this thesis and discuss potential future directions in Chapter 6.

## 2 Related Work

To accommodate the high computational complexity of DNN inference, a myriad of hardware and software techniques have been proposed. In this chapter, we first give background information and elaborate on the prior work on the specialized hardware for DNN inference, and then we discuss the prior work on software optimizations and co-design techniques with a focus on hardware-aware neural architecture search.

#### 2.1 DNN Accelerators

DNN workloads have been deployed in a wide range of compute platforms from generalpurpose CPUs to specialized accelerators. We can categorize these platforms based on their processing units into four groups: CPU, GPU, FPGA, and ASIC. General-purpose CPUs require low development cost thanks to their programmability; thus, they are in use of DNN inference for certain datacenter applications such as Facebook [Hazelwood et al., 2018]. However, CPUs exhibit high latency and limited throughput and power efficiency due to their long execution pipeline, deep memory hierarchy and complex control flow, which encourages the development and deployment of more specialized platforms for DNN workloads.

Thanks to their massive parallel execution capabilities, GPUs today are widely used in processing DNN workloads. Recent GPUs are equipped with specialized tensor cores [Choquette et al., 2021] and support custom data encoding formats such as BFloat16 [Kalamkar et al., 2019] to further improve their performance and power efficiency on DNN workloads. While their exceptional throughput with such customizations have made GPUs indispensable for DNN training, their long execution pipeline still incurs long latencies as in CPUs, which undermines their applicability in DNN inference for latency-critical online services.

To further improve the efficiency and performance of DNN inference, some services use the FPGA nodes in cloud services [Fowers et al., 2018]. Thanks to their reconfigurability capability, FPGAs enable building execution pipelines that are highly specialized to efficiently process DNN inference [Xuechao Wei et al., 2017; Alwani et al., 2016; Farabet et al., 2011]. Moreover,

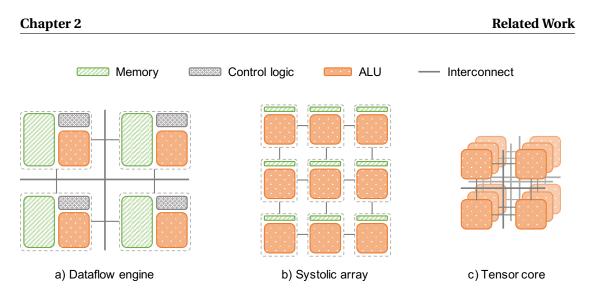

Figure 2.1: Three categories of spatial architectures used in DNN accelerators.

the customized execution pipelines in FPGAs can benefit from more aggressive quantization schemes [Zhang et al., 2018] and efficiently exploit the sparsity [Nurvitadhi et al., 2017] of DNN models. However, the additional logic for reconfigurability incurs significant overhead in FPGAs, placing an upper bound on their maximum clock frequency, arithmetic density and overall performance. Therefore, FGPAs do not offer an effective solution to accommodate the high computational cost of DNN inference.

To maximize throughput and efficiency in DNN workloads, many applications have invested in ASIC solutions. Despite their high cost of development and lack of reconfigurability, ASICs provide 1-2 orders of magnitude higher throughput compared to CPU, GPU, and FPGAs [Jouppi et al., 2017]. These accelerators typically use spatial architectures to simplify data movement between processing elements. Based on the type of spatial architecture that they use, we can group these ASIC solutions into three categories: **Dataflow engines** (e.g., Eyeriss [Chen et al., 2016], Wave DPU [Nicol, 2017]), **Tensor cores** (e.g., NVIDIA A100 [Raihan et al., 2019], Huawei DaVinci [Liao et al., 2019]), and **Systolic arrays** (e.g., Google TPU [Jouppi et al., 2017], Baidu Kunlun [Ouyang et al., 2020]). More details are given below about these spatial architectures, which are illustrated in Figure 2.1.

Dataflow engines typically consist of a grid of processing elements that are connected through a two-dimensional mesh topology, as shown in Figure 2.1a. These architectures aim to maximize both spatial and temporal data reuse by implementing certain mapping and scheduling patterns that are called *dataflow* [Chen et al., 2017]. Thanks to their ability to support various mapping and scheduling patterns, dataflow engines can adapt varying workload characteristics to improve utilization [Lu et al., 2017]. To implement such dataflow schemes, however, dataflow engines typically require a scratchpad memory and control logic in each processing element. Unfortunately, prior work reports that the scratchpad memory and control logic in processing elements incur significant overhead in power consumption and silicon area (up to 90% [Chen et al., 2016]), which places an upper bound on their efficiency and throughput. In contrast to dataflow engines, tensor cores employ simplistic processing elements without any scratchpad memory or control logic [Raihan et al., 2019], as shown in Figure 2.1c. Instead of implementing configurable dataflow schemes, they typically act as matrix multiplication engines with a fixed dataflow. To benefit from the three-dimensional spatial data reuse inherent to the matrix multiplication operations, the processing elements in tensor cores are often organized in a cube topology [NVIDIA, 2020]. While their simplistic design of the processing elements and their cube topology aim to maximize the throughput in matrix multiplication operations, they require large numbers of memory operations and high bandwidth between processing elements and on-chip memory due to the lack of temporal data reuse, which results in high power consumption and reduced efficiency.

Systolic arrays, which are depicted in Figure 2.1b, achieve superior power efficiency compared to tensor cores as they exploit both spatial and temporal data reuse in DNNs [Kung, 1982]. While performing a matrix multiplication operation, they store the elements of one of the operands in the registers of processing elements and reuse them throughout the operation, reducing the memory access and bandwidth requirements between processing elements and on-chip memory. Thanks to these advantages, systolic arrays have been used in various commercial accelerators [Jouppi et al., 2017; Ouyang et al., 2020].

Because systolic arrays reuse one of the operands temporally while performing a matrix multiplication, their spatial data reuse is limited to two-dimensional data. As a result, unlike the tensor cores that are often designed as a three-dimensional cube, the systolic arrays are typically organized in two-dimensional grid topologies. This fundamental limitation in the topology of systolic arrays has significant implications on their resource utilization. For the same number of processing elements, a systolic array organized in a two-dimensional grid has much larger dimensions than a three-dimensional tensor core. As a result of their large grid dimensions, underutilization due to dimension mismatches becomes a significant problem in systolic arrays.

The severity of the underutilization problem in systolic arrays has attracted considerable research efforts and led to various modifications in commercial accelerators. While the first generation TPUs consist of large and monolithic systolic arrays with an array size of  $256 \times 256$  [Jouppi et al., 2017], its successors adopted a multi-pod design with smaller systolic arrays of  $128 \times 128$  [Jouppi et al., 2021]. Likewise, researchers have proposed architectures that consist of many fine-grained systolic arrays with array sizes as small as  $8 \times 8$ [Kung et al., 2019], which greatly sacrifices the power efficiency. However, the question of how to find the optimal array dimensions for systolic arrays for a given set of target DNNs remains unknown. Therefore, in this thesis, we first focus on finding the optimal array granularity in multi-pod systolic array architectures.

The interconnection between the cores of a DNN accelerator pods also plays a critical role in its performance. While prior work has extensively studied the interconnection topologies in the context of dataflow engines, the findings of these studies do not apply to multi-pod systolic

architectures due to former's unique computational characteristics and data movement patterns. Many of the prior work used Mesh [Chen et al., 2017, 2014b; Gao et al., 2019; Shao et al., 2019] or H-tree [Kung et al., 2019; Stevens et al., 2019] topologies to connect the processing elements in DNN accelerators. However, these topologies lack sufficient bisection bandwidth to support a large number of pods in multi-pod systolic architectures. Qin et al. proposed to use a Benes topology due to its high bisection bandwidth [Qin et al., 2020] but this topology suffers from a long round-trip latency, which leads to reduced utilization. Trivial solutions such as Crossbar or Bus are unfortunately not suitable for multi-pod architectures due to their poor scalability. As a result, finding the optimal interconnect topology in multi-pod systolic architectures is also an open research question.

Besides the research efforts in array granularity and interconnect topology, prior work has also explored concurrency as a possible solution to the underutilization problem in systolic architectures. AI-MultiTasking [Baek et al., 2020] has proposed a scheduling strategy to mitigate the memory stalls in multi-pod systolic arrays. PREMA [Choi & Rhu, 2020] has resorted to multi-tenancy to improve the array utilization. Likewise, Equinox [Drumond et al., 2021] has proposed to piggyback DNN training tasks on inference accelerators to claim idle cycles. However, these proposals offer improvements in architectures only with a few pods and do not address the challenges in tiling and scheduling inherent to the architectures with large numbers of pods. Therefore, in this thesis, we also focus on tiling and scheduling DNN inference on multi-pod accelerators that scale up to hundreds of pods, which is critical to unlock the full potential of these accelerators.

To get the best of both systolic arrays and tensor cores, prior work has proposed to integrate these two types of architectures on a single-chip [Guo et al., 2020a]. To enable such integration, Guo et al. proposes micro-architectural modifications in the systolic arrays to make their memory access coalesced. However, these micro-architectural modifications require longer links between processing elements, hindering the arrays' scalability. In this thesis, we adopt a much simpler approach to make the systolic arrays' memory access coalesced without any modifications required in the arrays. We simply devise *skew buffers* in the systolic pods between on-chip memory banks and systolic arrays to transform coalesced memory accesses into the unique data pattern required by the systolic arrays. Therefore, this thesis proposes a simpler and more efficient solution to the limitations inherent to the uncoalesced memory access patterns of systolic arrays than Guo et al.

#### 2.2 Neural Architecture Search

#### 2.2.1 DNN optimization

The development of methods to build DNN architectures that achieve higher accuracies in the given tasks while maintaining low hardware footprint (such as model size and latency [Tan et al., 2019; Wu et al., 2019]) has received considerable attention from researchers. While early

work has introduced design heuristics such as residual connections [He et al., 2016], batch normalization [Ioffe & Szegedy, 2015] and bottleneck layers [Sandler et al., 2018], building DNNs with these techniques requires human expertise and domain knowledge.

To minimize the need for human supervision while building DNNs, researchers have first resorted to model compression and network pruning techniques [Luo et al., 2017; He et al., 2017; Yu & Huang, 2019; Dong & Yang, 2019b]. Likewise, Jha et al. proposed to optimize DNN architectures for the data reuse to improve resource utilization by eliminating the memory bottlenecks [Jha et al., 2020]. Unfortunately, these methods still rely on human supervision for the design of the initial DNN architectures as starting points, which hinders their effectiveness and prevents them from realizing the purpose of automating DNN design. Moreover, addressing only the memory bottlenecks is not sufficient to achieve high resource utilization in systolic array accelerators, which requires a more complex modelling of the computational characteristics of these accelerators.

To that end, researchers have focused on neural architecture search, which aims to fully automate the design process of DNNs without any need for human supervision. There are three components of neural architecture search frameworks that are critical for their effectiveness and efficiency: optimization strategy, architecture evaluation, and search space. In this section, we discuss the prior work on these three critical components of neural architecture search.

#### 2.2.2 Optimization strategy

Early work on neural architecture search adopted reinforcement learning [Pham et al., 2018; Tan et al., 2019; Zoph & Le, 2017; Zoph et al., 2018], evolutionary algorithms [Marchisio et al., 2020; Real et al., 2019], and Bayesian optimization [Bergstra et al., 2011]. Because these methods operate on a discrete search space and need to perform many trials while searching for an optimal architecture in an exponentially-increasing hyperparameter space, they require thousands of GPU-hours to find optimal DNN architectures, which greatly limits their applicability and even raises concerns about their impact on environment [Patterson et al., 2021]. To mitigate the prohibitive cost of architecture search, techniques such as weight-sharing [Pham et al., 2018] and one-shot search [Bender et al., 2018] have been proposed. Likewise, prior work has also used sparse optimization techniques such as compressed sensing to efficiently search discrete search spaces [Hazan et al., 2018; Cho et al., 2019]. While these techniques reduce the cost of each trial by allowing to reuse trained parameters, they still require many trials to find the optimal DNN architectures.

To further reduce the computational cost, recent work has proposed differentiable neural architecture search [Cai et al., 2019; Chang et al., 2019; Liu et al., 2018; Nayman et al., 2019; Xie et al., 2019; Xu et al., 2020], which is a weight-sharing method with a gradient-descent optimizer. In these methods, a continuous relaxation is applied to the categorical decisions using a set of trainable weights (i.e., architectural parameters). Because differentiable NAS methods use the information from gradients with respect to the architectural parameters

during training, they achieve faster convergence than their non-differentiable counterparts. Thanks to reusing trained parameters and faster convergence, differentiable methods achieve a reduction of 2-3 orders of magnitude in the computational cost of neural architecture search [Dong & Yang, 2019a; Stamoulis et al., 2019].

This remarkable reduction in computational cost has encouraged researchers to use differentiable neural architecture search in various ways: Liu et al. proposed to use this technique to search microarchitecture cells (i.e., basic building blocks) [Liu et al., 2019]. Wu et al. proposed a differentiable hardware-aware neural architecture search [Wu et al., 2019], and Wan et al. used a differentiable neural architecture search to find optimal spatial and channel dimensions for DNNs [Wan et al., 2020]. Because of their superior efficiency and widespread adoption in various application domains, in this thesis, we also focus on differentiable neural architecture search.

#### 2.2.3 Architecture evaluation

The objective functions of hardware-aware neural architecture search frameworks typically contain multiple terms such as accuracy on a given task, inference latency [Wu et al., 2019] and energy consumption [Dai et al., 2019]. While the accuracy metrics can be straightforwardly obtained by calculating the cross-entropy loss on a training dataset, the existing hardware-aware neural architecture search frameworks differ in the way that they estimate the hardware-related metrics. Some of the prior work evaluates the DNN directly on physical devices during the search and use real-time measurements on the loss function [Tan et al., 2019; Yang et al., 2018]. While this approach may allow obtaining hardware metrics accurately, it requires access to physical devices during the search, which hinders its practicality and reproducability.

To eliminate the need for accessing physical devices, more recent work proposed to store the measurements from physical devices on lookup tables and read these values during the search to calculate the loss function [Dai et al., 2019; Stamoulis et al., 2019; Wan et al., 2020; Wu et al., 2019]. However, this approach is also not practical due to two reasons. First, the number of required measurements to represent a search space grows combinatorially with the number of architectural parameters and hardware configurations. Second, these lookup tables correspond to *black-box* models, which are non-differentiable and therefore do not allow gradient calculations. As a result, these models can not effectively be used in gradient descent optimizers.

To obtain a differentiable latency model, some of prior work exploits the fact that a DNN's total latency is equal to the sum of individual layers' latency [Wu et al., 2019]. While this approach allows using gradient descent optimizers to make layer-wise decisions such as which layers to keep or discard, it still assumes black-box models to characterize the latency of each layer, prohibiting the usage of gradient descent to optimize layer parameters such as operator type and channel dimensions. Therefore, the proposed differentiable models are effective to optimize only certain aspects of DNNs and do not offer a complete solution.

To be fully compatible with differentiable frameworks, prior work proposed to estimate the hardware-related metrics using surrogate models such as linear regression [Xiong et al., 2021] or neural networks [Choi et al., 2021]. Unfortunately, these models require large numbers of samples for training and do not generalize well to the out-of-distribution samples; therefore, this approach does not offer an effective solution. Other prior works proposed to use analytical hardware models, which estimates the hardware performance metrics using a cycle-accurate model [Marchisio et al., 2020] or a roofline model [Gupta & Akin, 2020; Li et al., 2021a]. Unfortunately, these models do not represent the runtime characteristics of systolic architectures accurately, leading to significant discrepancies between the estimated and actual values of runtime measurements.

In short, the prior approaches to estimate hardware-related metrics in neural architecture search are either not practical, differentiable, or accurate for systolic architectures. Therefore, this thesis also focuses on developing efficient and effective hardware models for systolic architectures that are compatible with differentiable neural architecture search frameworks.

#### 2.2.4 Search space

The design of the search space plays a critical role in the outcome of the neural architecture search; thus, researchers have put considerable effort into developing strategies to design more efficient and extensive search spaces. To simplify the search complexity, Zoph et al. [Zoph et al., 2018] proposed to search for basic building blocks (*cell*), which can be stacked up to form a DNN architecture. Although this approach can construct intricate cell structures with relatively low search space complexity and is widely adopted by others [Liu et al., 2018; Pham et al., 2018; Liu et al., 2019; Real et al., 2019], using identical cells in all stages of DNN architectures has a negative impact on its accuracy and efficiency [Wu et al., 2019]. Therefore, Tan et al. proposed the hierarchical search space, which allows searching unique cells on different stages of a DNN architecture with varying macro-architectural properties such as the number of layers, spatial and channel dimensions.

Among the macro-architectural properties, channel dimensions are especially of interest due to their significant impact on the computational characteristics of DNN architectures. To that end, prior work has proposed numerous methods to search for optimal channel dimensions [He et al., 2018; Ashok et al., 2018; Cai et al., 2018; Tan et al., 2019]. Among these methods, DMaskingNAS [Wan et al., 2020] have become widely popular thanks to its efficiency. However, this method relies on a fixed search space for the channel dimensions that must be carefully tuned for target resource budget, which undermines its practicality.

A few prior work have addressed the issues inherent to such fixed search spaces. Liu et al. [Liu et al., 2018] proposed the *progressive* neural architecture search, which gradually increases the complexity of the search space during search. Similarly, Ci et al. [Ci et al., 2021] proposed the *neural search space evolution* technique, which enables adding new operations to the search space as the architecture search progresses. However, both of these techniques address

only the search space for cell structures, ignoring other critical properties of DNNs such as channel dimensions. As a result, channel dimension search without the restrictions of a fixed search space remains as an open research question. Therefore, in this thesis, we also focus on developing an efficient neural architecture search for channel dimensions with a flexible search space.

## **3** Scale-out Systolic Arrays

Systolic arrays have become the architecture of choice for DNN accelerators as they offer superior power efficiency, high arithmeric density, and scalable design. While many variants of systolic arrays have been used in various data processing applications [Kung, 1982], two-dimensional systolic arrays are adopted for DNN accelerators because of their efficiency in performing matrix multiplication (GEMM) operations, which constitute the backbone of DNN workloads. The GEMM operations compiled from DNN layers are typically in the form of  $XW + P_{in} = P_{out}$ , where X is the input of the layer, W is the trainable parameters of the layer,  $P_{out}$  is the output of the layer, and  $P_{in}$  is the initial value of  $P_{out}$ . Throughout this thesis, we refer to X, W,  $P_{in}$ , and  $P_{out}$  as the *activations, weights, input sums*, and *output sums*, respectively.

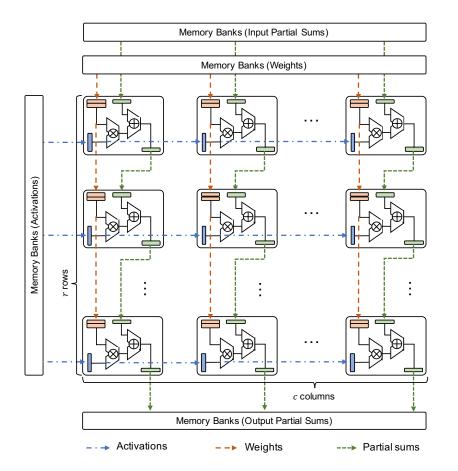

Figure 3.1 depicts a two-dimensional systolic array, in which the processing elements are placed in a grid of *r* rows and *c* columns. Each processing element includes a multiply-and-accumulate (MAC) arithmetic logic unit and a small number of registers to temporarily store the input and output data. The processing elements are connected to their neighbors along rows and columns through uni-directional point-to-point links. While multiple equivalent dataflows exist for two-dimensional systolic arrays, in this thesis, we focus on a weight stationary dataflow due to its widespread adoption in the literature and commerically available accelerators [Jouppi et al., 2017; Kung et al., 2019].

To perform a GEMM operation, a systolic array first fetches the weight matrix row by row and stores them in processing elements. Then, in every cycle, the processing elements in the left-most column fetch activations from the memory banks. Likewise, the processing elements at the top row fetch the input partial sums from the memory banks, perform a multiply-and-accumulate operation, and pass the resulting partial sum to the row below. The operation continues with activations flowing from left to right, partial sums flowing from

Part of this chapter has been accepted to be published in

<sup>&</sup>quot;Scale-out Systolic Arrays", ACM Transactions on Architecture and Code Optimization, 2022.

Figure 3.1: A weight-stationary systolic array with r rows and c columns. Activations are assumed to traverse along the rows from left to right, weights and partial sums traverse along the columns from top to bottom.

top to bottom, and weights staying stationary. The processing elements at the bottom row produce the final results and write them back to the memory banks.

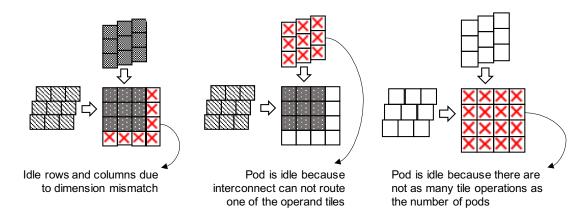

While a single unit of systolic array can effectively perform a GEMM operation, modern accelerators often deploy multiple of them in a single die (i.e., *multi-pod* designs) to allow data and task-level parallelism [Kung et al., 2019; Baek et al., 2020; Jouppi et al., 2021]. A multi-pod accelerator's effective throughput is a function of the overall utilization of processing elements both within and across pods. Therefore, maintaining a high utilization not only maximizes the gain from provisioned silicon resources but also improves the overall performance of an accelerator: Figure 3.2 illustrates three main causes of the underutilization in a multi-pod accelerator: (1) dimension mismatch [Samajdar et al., 2020] between array and workload resulting in underutilization within a pod, (2) poor connectivity resulting in underutilization across pods, and (3) sub-optimal tiling resulting in underutilization both within and across pods.

Utilization within a pod highly depends on the pod's systolic array granularity and the layer

Figure 3.2: Three main factors of underutilization in systolic arrays.

dimensions of a DNN workload. Prior multi-pod accelerators [Jouppi et al., 2017; Google, 2017; Baek et al., 2020] opt for larger array dimensions to reduce access to on-chip memory, provisioning higher power for processing elements. Unfortunately, larger arrays also increase the likelihood that the workload's layer dimensions are smaller than the number of array's rows or columns, resulting in idle processing elements and wasted throughput/Watt. In contrast, minimizing the array dimensions per pod reduces the mismatch between the workloads and the array, resulting in improved utilization. Smaller systolic arrays, however, increase the power required for on-chip memory access, undermining the overall throughput/Watt. In this chapter, we show that the optimal array size for DNN workloads is an order of magnitude smaller than that widely adopted by academia and industry and identify the optimal array size for widely used DNN workloads for computer vision and natural language processing applications.

The interconnect also plays a key role in utilization and effective throughput in multi-pod accelerators [Kung et al., 2019]. To achieve a scalable multi-pod accelerator architecture with high utilization, the interconnect should allow transferring data tiles between systolic pods and memory banks with minimal contention at high efficiency. Therefore, the selected network topology should satisfy several design requirements such as high bisection bandwidth, high combinatorial power, low latency, and good scalability. As these requirements are often contradictory to each other, the network topologies should be carefully evaluated from the perspective of scale-out architectures to ensure high performance and scalability of the accelerators. In this chapter, we perform a quantitative analysis of network topologies in the context of multi-pod accelerators and identify the optimal network topology to connect large numbers of pods efficiently.

Finally, the tile size for each pod fundamentally impacts utilization in multi-pod accelerators and should be tuned with care. We observe that conventional approaches to tiling for systolic arrays [Baek et al., 2020; Choi & Rhu, 2020] fall well short of generating a sufficient number of tile operations to populate a large number of pods, resulting in idle arrays during execution.