### Thèse n° 9501

# EPFL

### **Computational Imaging SPAD Cameras**

Présentée le 12 janvier 2023

Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Andrei ARDELEAN

Acceptée sur proposition du jury

Prof. D. Atienza Alonso, président du jury Prof. E. Charbon, Dr C. Bruschini, directeurs de thèse Prof. R. Henderson, rapporteur Prof. M. Gupta, rapporteur Dr G. Boero, rapporteur

2023

Examine every word you put on paper. You'll find a surprising number that don't serve any purpose. — William Zinsser

To Andrada...

# Acknowledgements

I will start by thanking my thesis advisor, Prof. Edoardo Charbon, for giving me the opportunity to do a PhD in the AQUA laboratory. He allowed me to pursue all of my curiosities in chip design, encouraged me to take risks and motivated and supported me when times were tough. I would also like to thank my thesis co-advisor, Dr. Claudio Bruschini, for his guidance and attention to detail which ensured that my work was of high quality.

I would like to give special thanks to Arin Can Ulku with whom I worked on the same research project, co-authored a paper and shared an office for the majority of my time at AQUA. He guided me at the begining of my PhD and was always there when I had any questions about our work on FLIM. In addition, I would like to acknowledge Kazuhiro Morimoto for his collaboration on our first 3D megapixel design and for teaching me a more methodical aproach to work.

I would like to thank all my colleagues from AQUA EPFL and TUDelft, starting with Preethi Padmanabhan, Francesco Gramuglia, Scott Lindner, Samuel Burri and Myung-Jae Lee who were there at the very begining of my PhD and continuing with Augusto Ximenes, Ivan Michel Antolovic, Chao Zhang, Andrea Ruffino, Jad Benserhir, Ermanno Bernasconi, Baris Can Efe, Simone Frasca, Utku Karaca, Pouyan Keshavarzian, Ekin Kizilkan, Yang Lin, Feng Liu, Tommaso Milanese, Paul Mos, Emanuele Ripiccini, Ming-Lo Wu, Halil Kerim Yildirim, Jiuxuan Zhao, as well as all the ones who have recently joined but I haven't had the chance to collaborate with.

I would also like to mention Brigitte Khan and Begonia Tora, who have helped me with personal issues that extended far beyond their duty as administrative staff. Additionaly, I would like to thank Michael and Fio for their friendship and support.

I would also like to acknowledge my parents and grandparents for supporting me throughout my academic career and Yuki, for sitting with me during the sleepless tapeout nights and reminding me I had to go home.

Last but definitely not least, I would like to thank Andrada for always being by my side throughout our 11 years of Bachelor, Masters and Doctoral studies and without whom I would not have been here today.

Neuchâtel, November 2022

Andrei Ardelean

## Abstract

Vision systems built around conventional image sensors have to read, encode and transmit large quantities of pixel information, a majority of which is redundant. As a result, new computational imaging sensor architectures were developed to preprocess the raw pixel data and reduce the amount of information that needs to be read from the sensor. With the emergence of large format single-photon avalanche diode (SPAD) imagers, the need for on-chip processing has become more evident, as the output data rate of such detectors is pushing the limit of even modern interfaces.

The aim of the thesis is to develop sensor architectures for computational imaging that overcome limitations of conventional SPAD imagers and can operate at high frame rates with manageable output data rates. Three sensors are designed in different technology nodes, from 180 nm 2D to 3D-stacked 45/22 nm and 180/16 nm, backside and front-side illuminated.

A novel token-based readout technique is developed to improve system frame rate by reducing the readout time through omission of dark pixels. The technique is implemented in *kilo*Phase, a  $32 \times 32$  gated SPAD imager with vector processing capabilities that can achieve 4.38 ns gates and can operate at 227 fps in 10 bit intensity mode, a 12% increase compared to conventional readout. An improved, massively parallel version of the architecture is implemented in *Mega*Phase, a 1-megapixel SPAD imager consisting of 16384 processing cores that can perform addition and multiplication operations on the raw pixel data. The SPADs can be binned with multiple granularities to increase the pixel dynamic range and reduce the required exposure time. Simulations show a frame rate increase of up to  $170 \times$  when operating as an intensity imager and  $56 \times$  in gated fluorescence lifetime imaging (FLIM) mode.

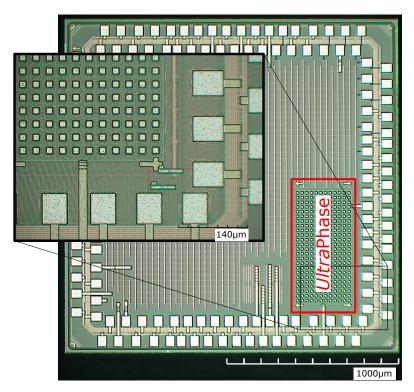

Finally, *Ultra*Phase, the first fully reconfigurable SPAD processing architecture is developed and consists of 18 independent processors running at 140 MOPS with a power consumption of less than 94.6 GOPS/W. Each processor can execute up to 256 instructions per program and contains a reconfigurable front end that can implement a wide range of combinatorial functions and a timing module that can be configured to measure photon arrival timestamps. Key words: computational imaging, single-photon avalanche diode (SPAD), fluorescence lifetime imaging microscopy (FLIM), token-readout, parallel processing

## Résumé

Les systèmes de vision construits autour de capteurs d'images conventionnelles doivent lire, encoder et transmettre de grandes quantités d'informations de pixels, dont la majorité est redondante. Par conséquent, de nouvelles architectures de capteurs d'imagerie computationnelle ont été développées pour prétraiter les données de pixels brutes et réduire la quantité d'informations qui doivent être lues à partir du capteur. Avec l'émergence des imageurs grand format avec la diode à avalanche à photon unique (SPAD), le besoin d'un traitement sur puce est devenu essentiel, car le débit de données de sortie de ces détecteurs repousse les limites des interfaces, même modernes.

L'objectif de la thèse est de développer des architectures de capteurs pour l'imagerie numérique qui surmontent les limites des imageurs conventionnels SPAD et qui peuvent fonctionner à des fréquences d'images élevées avec des débits de données de sortie gérables. Trois capteurs sont conçus dans différents nœuds technologiques, de 180 nm 2D à 3D empilés 45/22 nm et 180/16 nm, éclairés à l'arrière et à l'avant.

Une nouvelle technique de lecture basée sur des jetons est développée pour améliorer la fréquence d'images du système en réduisant le temps de lecture par omission de pixels sombres. La technique est mise en oeuvre en *kilo*Phase, un imageur SPAD  $32 \times 32$  avec des capacités de traitement vectoriel qui peut atteindre des portes de 4.38 ns et peut fonctionner à 227 fps en mode d'intensité de 10 bits, soit 12% d'augmentation par rapport à la lecture conventionnelle. Une version améliorée et massivement parallèle à l'architecture est implémentée dans *Mega*Phase, un imageur SPAD de 1 mégapixel composé de 16384 cœurs de traitement qui peuvent effectuer des opérations d'addition et de multiplication sur les données de pixels brutes. Les SPAD peuvent être regroupés avec plusieurs granularités pour augmenter la plage dynamique des pixels et réduire le temps d'exposition requis. Les simulations montrent une augmentation de la fréquence d'images jusqu'à 170× lorsqu'ils fonctionnent comme un imageur d'intensité et 56× en mode de microscopie d'imagerie à durée de vie de fluorescence (FLIM).

Enfin, *Ultra*Phase est la première architecture de traitement SPAD entièrement reconfigurable qui se compose de 18 processeurs indépendants et qui fonctionnent à 140 MOPS, avec une consommation électrique inférieure à 94.6 GOPS/W. Chaque processeur peut exécuter jusqu'à 256 instructions par programme et contient un circuit frontal reconfigurable. Ces circuits peuvent implémenter un large éventail de fonctions combinatoires. De plus, le processeur contient un module de temporisation configurable pour mesurer les horodatages d'arrivée des photons.

Mots clés : imagerie computationnelle, diode à avalanche à photon unique (SPAD), microscopie d'imagerie à durée de vie de fluorescence (FLIM), lecture de jeton, traitement parallèle

# Contents

| Acknowledgements                    | i      |

|-------------------------------------|--------|

| Abstract (English/Français)         | iii    |

| List of figures                     | xi     |

| List of tables                      | XV     |

| List of acronyms                    | xvii   |

| 1 Introduction                      | 1      |

| 1.1 Computational imaging           | <br>1  |

| 1.2 FLIM                            | <br>5  |

| 1.2.1 Photon counting techniques    | <br>6  |

| 1.2.2 Phasor-based FLIM             | <br>8  |

| 1.3 SPAD                            | <br>11 |

| 1.3.1 Technology and implementation | <br>11 |

| 1.3.2 Metrology                     | <br>12 |

| 1.4 Research motivation             | <br>13 |

| 1.5 Scientific contributions        | <br>14 |

| 1.6 Thesis structure                | <br>15 |

| 2 <i>kilo</i> Phase                 | 17     |

| 2.1 Motivation                      | <br>18 |

| 2.2 Processing flow                 | <br>20 |

| 2.3 Architecture                    | <br>22 |

| 2.3.1 Pixel                         | <br>22 |

| 2.3.2 Token-passing readout         | <br>24 |

| 2.3.3 Bus manager                   | <br>26 |

| 2.3.4 Accumulator bank              | <br>26 |

| 2.3.5 Computational unit            | <br>27 |

| 2.3.6 RAM bank                      | <br>28 |

|   | 2.4 | Implementation       |                          |    |

|---|-----|----------------------|--------------------------|----|

|   | 2.5 | 2.5 Characterization |                          | 34 |

|   |     | 2.5.1                | Camera system            | 34 |

|   |     | 2.5.2                | Breakdown voltage        | 35 |

|   |     | 2.5.3                | Dark count rate          | 36 |

|   |     | 2.5.4                | Crosstalk                | 39 |

|   |     | 2.5.5                | PDP                      | 40 |

|   |     | 2.5.6                | Power consumption        | 40 |

|   |     | 2.5.7                | Gate profile             | 41 |

|   |     | 2.5.8                | Frame rate               | 43 |

|   |     | 2.5.9                | Data rate                | 47 |

|   |     | 2.5.10               | Microlenses              | 47 |

|   | 2.6 | Concl                | usion                    | 49 |

| 3 | Moo | a Phas               | e                        | 53 |

| 3 | 3.1 | •                    | e<br>ration              |    |

|   | 3.2 |                      | ssing flow               | 55 |

|   |     |                      | tecture                  |    |

|   | 0.0 | 3.3.1                | Pixel                    |    |

|   |     | 3.3.2                | Computational unit       |    |

|   |     | 3.3.3                | Readout                  |    |

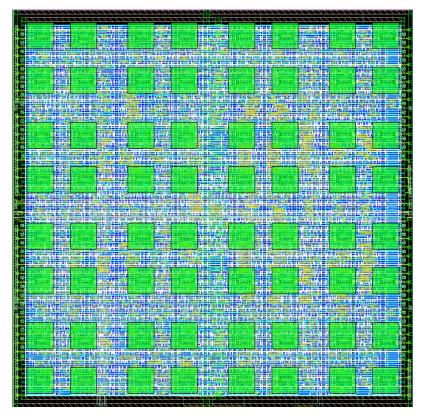

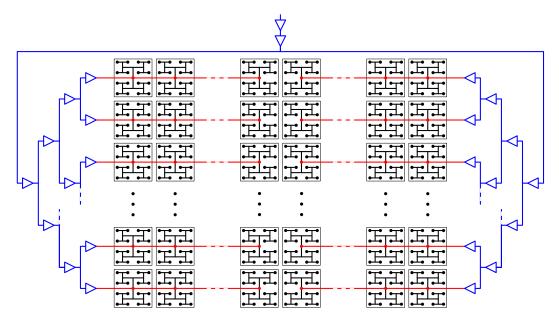

|   | 3.4 |                      | ementation               |    |

|   | 011 | 3.4.1                | Top tier                 |    |

|   |     | 3.4.2                | Bottom tier              |    |

|   | 3.5 |                      | n verification           |    |

|   | 3.6 | •                    | usion                    |    |

|   |     |                      |                          |    |

| 4 |     | aPhas                |                          | 73 |

|   |     |                      | ration                   | 73 |

|   | 4.2 |                      | tecture                  |    |

|   |     | 4.2.1                | Reconfigurable front end | 75 |

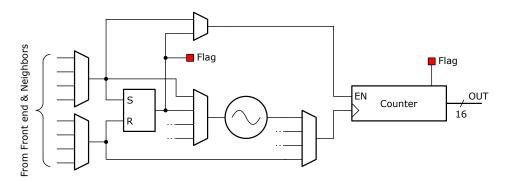

|   |     | 4.2.2                | Timing module            |    |

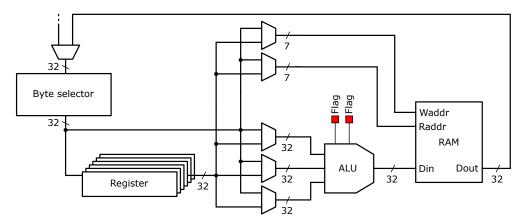

|   |     | 4.2.3                | Processing module        |    |

|   |     | 4.2.4                | Control module           | 80 |

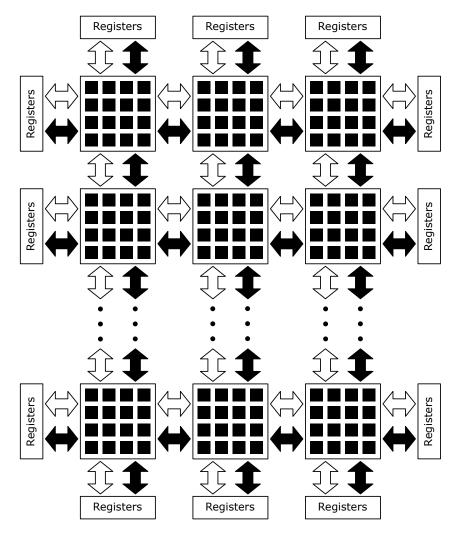

|   |     | 4.2.5                | Processor array          | 82 |

|   | 4.3 | Imple                | ementation               | 84 |

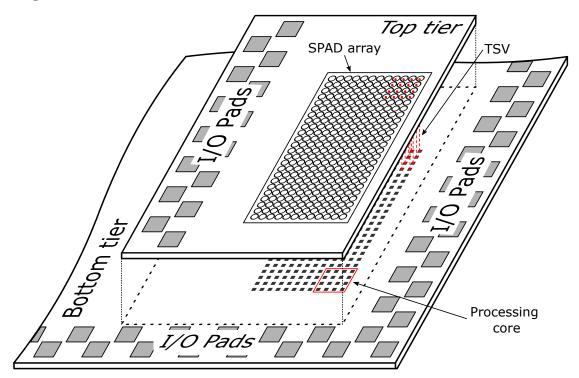

|   |     | 4.3.1                | Top tier                 | 84 |

|   |     | 4.3.2                | Bottom tier              | 87 |

|   | 4.4 | Progra               | amming                   |    |

|   |     | 4.4.1                | Instructions             | 91 |

#### Contents

|                      |       | 4.4.2  | Assembler                 | • • | 94  |

|----------------------|-------|--------|---------------------------|-----|-----|

|                      |       | 4.4.3  | Compiler                  | ••• | 95  |

|                      | 4.5   | Chara  | acterization              | ••• | 96  |

|                      |       | 4.5.1  | Power consumption         | ••• | 96  |

|                      |       | 4.5.2  | Timing performance        | ••• | 97  |

|                      | 4.6   | Applic | cations                   |     | 98  |

|                      |       | 4.6.1  | ToF histogram compression |     | 98  |

|                      |       | 4.6.2  | LSTM LiDAR                |     | 102 |

|                      | 4.7   | Concl  | lusion                    |     | 107 |

| 5                    | Con   | clusio | n                         |     | 111 |

| 5                    |       |        |                           |     |     |

|                      | 5.1   |        | nary                      |     |     |

|                      | 5.2   | Future | e work                    | ••• | 113 |

|                      |       |        |                           |     |     |

| Ap                   | openo | dix    |                           |     | 115 |

| Bibliography         |       |        |                           | 119 |     |

| Chip gallery         |       |        |                           | 137 |     |

| List of publications |       |        |                           | 139 |     |

| Curriculum vitae     |       |        |                           | 141 |     |

# List of Figures

| 1.1  | Analog CVIS architecture                                                 | 3  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Digital CVIS architecture                                                | 4  |

| 1.3  | Bandwidths of common interfaces                                          | 5  |

| 1.4  | TCSPC vs. time gating.                                                   | 6  |

| 1.5  | Phasor FLIM plot                                                         | 9  |

| 1.6  | Phasor FLIM plot for a double-exponential decay                          | 10 |

| 1.7  | SPAD operation                                                           | 11 |

| 1.8  | Example SPAD cross section                                               | 13 |

| 2.1  | kiloPhase readout scheme                                                 | 18 |

| 2.2  | <i>kilo</i> Phase theoretical maximum speedup                            | 19 |

| 2.3  | <i>kilo</i> Phase block diagram                                          | 20 |

| 2.4  | <i>kilo</i> Phase pixel schematic                                        | 23 |

| 2.5  | <i>kilo</i> Phase pixel layout                                           | 23 |

| 2.6  | <i>kilo</i> Phase token-passing schematic                                | 24 |

| 2.7  | <i>kilo</i> Phase token-passing principle                                | 25 |

| 2.8  | <i>kilo</i> Phase Bus manager circuit schematic for one row of the array | 27 |

| 2.9  | <i>kilo</i> Phase computational unit schematic                           | 28 |

| 2.10 | <i>kilo</i> Phase RAM schematic                                          | 29 |

|      | <i>kilo</i> Phase gate and recharge propagation                          | 31 |

| 2.12 | <i>kilo</i> Phase gate and recharge tree                                 | 31 |

| 2.13 | <i>kilo</i> Phase power distribution and decoupling capacitors           | 32 |

| 2.14 | <i>kilo</i> Phase CoB PCB                                                | 34 |

| 2.15 | <i>kilo</i> Phase system                                                 | 35 |

| 2.16 | <i>kilo</i> Phase breakdown voltage                                      | 36 |

| 2.17 | <i>kilo</i> Phase cooling assembly                                       | 37 |

| 2.18 | Median <i>kilo</i> Phase DCR                                             | 38 |

| 2.19 | <i>kilo</i> Phase DCR population distribution                            | 38 |

| 2.20 | Median <i>kilo</i> Phase DCR across the entire array                     | 39 |

| 2.21 | Average <i>kilo</i> Phase crosstalk                                      | 40 |

| 2.22 | Photon detection probability                                             | 41 |

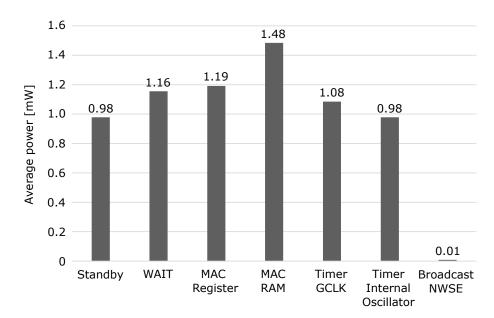

| 2.23 Average <i>kilo</i> Phase power consumption                | . 42 |

|-----------------------------------------------------------------|------|

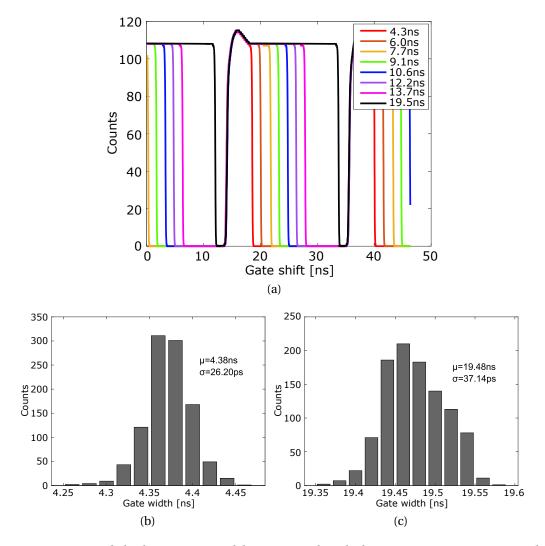

| 2.24 <i>kilo</i> Phase gate edge characteristics                | . 44 |

| 2.25 <i>kilo</i> Phase gate skew                                | . 44 |

| 2.26 <i>kilo</i> Phase gate width range                         | . 45 |

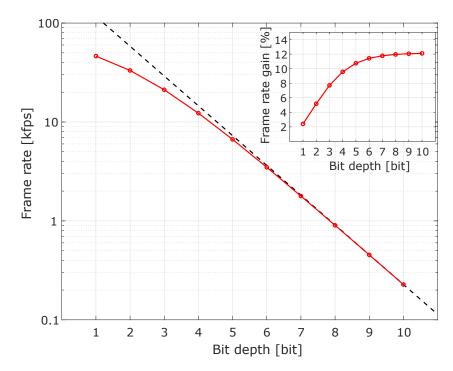

| 2.27 <i>kilo</i> Phase intensity mode frame rate                | . 46 |

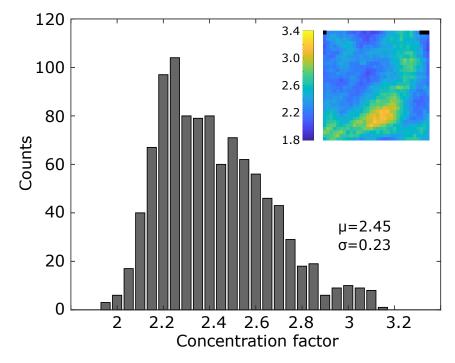

| 2.28 <i>kilo</i> Phase microlenses                              | . 48 |

| 2.29 <i>kilo</i> Phase microlense concentration factor          | . 49 |

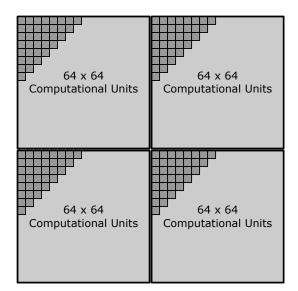

| 3.1 <i>Mega</i> Phase structure                                 | . 54 |

| 3.2 <i>Mega</i> Phase readout scheme                            | . 55 |

| 3.3 <i>Mega</i> Phase pixel schematic                           | . 58 |

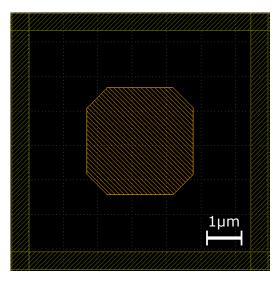

| 3.4 <i>Mega</i> Phase pixel layout                              | . 59 |

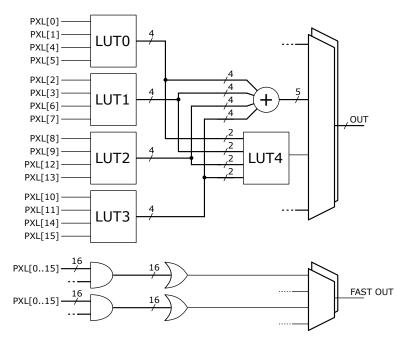

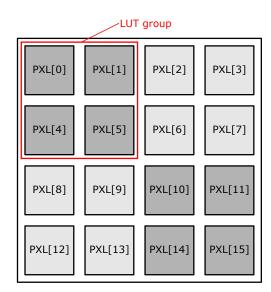

| 3.5 <i>Mega</i> Phase computational unit block diagram          |      |

| 3.6 <i>Mega</i> Phase SPAD binning                              |      |

| 3.7 <i>Mega</i> Phase quadrant readout                          |      |

| 3.8 <i>Mega</i> Phase ROI readout                               |      |

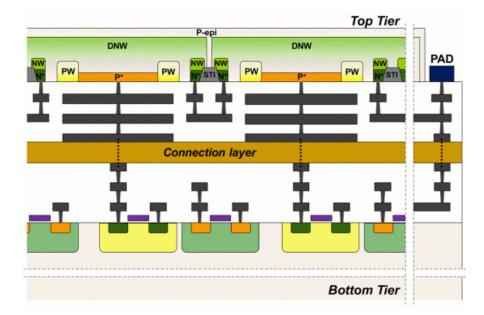

| 3.9 BSI 3D-stacked SPAD sensor structure                        |      |

| 3.10 <i>Mega</i> Phase top tier pixel layout                    |      |

| 3.11 <i>Mega</i> Phase processing core layout                   |      |

| 3.12 <i>Mega</i> Phase gate distribution                        |      |

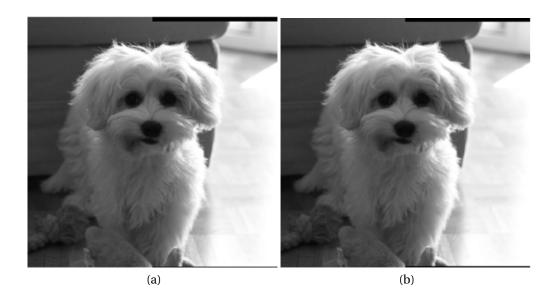

| 3.13 <i>Mega</i> Phase intensity mode simulation results        |      |

| 3.14 <i>Mega</i> Phase computational mode simulation results    |      |

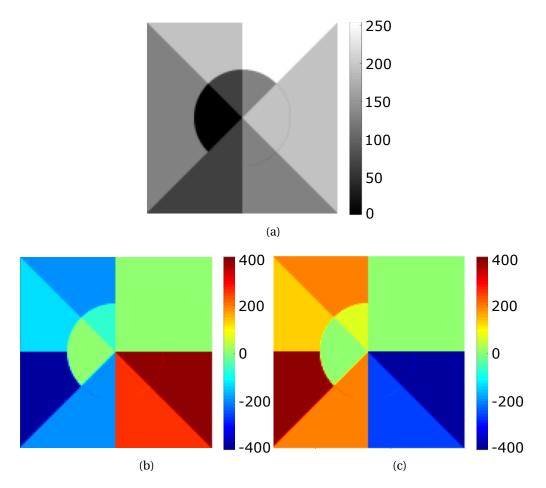

| 4.1 <i>Ultra</i> Phase processing core block diagram            | . 74 |

| 4.2 <i>Ultra</i> Phase processing core reconfigurable front end |      |

| 4.3 <i>Ultra</i> Phase processing core pixel grouping           |      |

| 4.4 <i>Ultra</i> Phase Timing module schematic                  |      |

| 4.5 <i>Ultra</i> Phase Processing module schematic              |      |

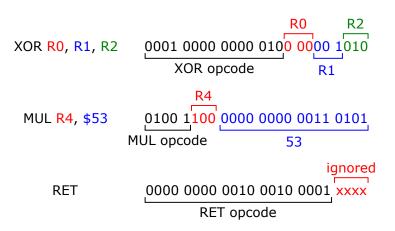

| 4.6 <i>Ultra</i> Phase instruction machine code                 |      |

| 4.7 <i>Ultra</i> Phase array of processing cores                |      |

| 4.8 <i>Ultra</i> Phase 3D structure                             |      |

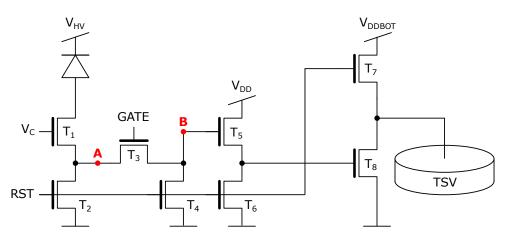

| 4.9 <i>Ultra</i> Phase top tier pixel schematic                 |      |

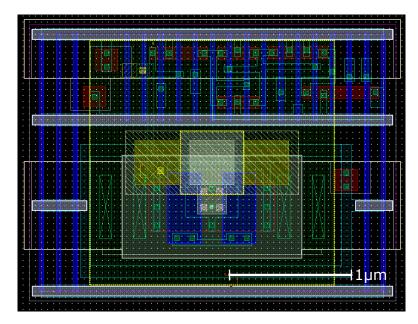

| 4.10 <i>Ultra</i> Phase top tier pixel layout                   |      |

| 4.11 <i>Ultra</i> Phase top tier micrograph                     |      |

| 4.12 <i>Ultra</i> Phase processing core layout                  |      |

| 4.13 <i>Ultra</i> Phase bottom tier                             |      |

| 4.14 <i>Ultra</i> Phase assembly language                       |      |

| 4.15 <i>Ultra</i> Phase power consumption                       |      |

| 4.16 <i>Ultra</i> Phase timing module single shot measurements  |      |

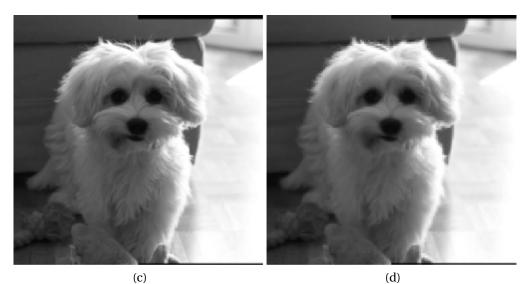

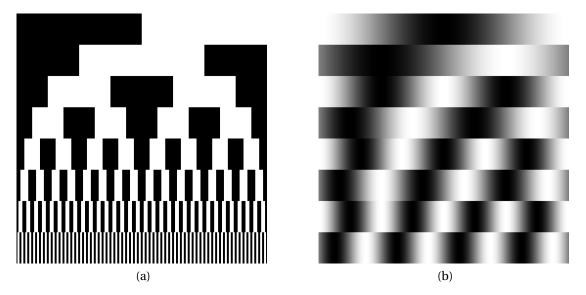

| 4.17 Encoding matrices                                          |      |

| 5                                                               |      |

### **List of Figures**

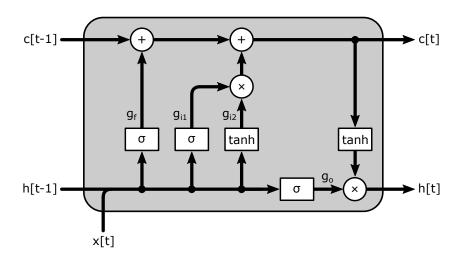

| 1 10 | LCTM coll structure                                         | 102 |

|------|-------------------------------------------------------------|-----|

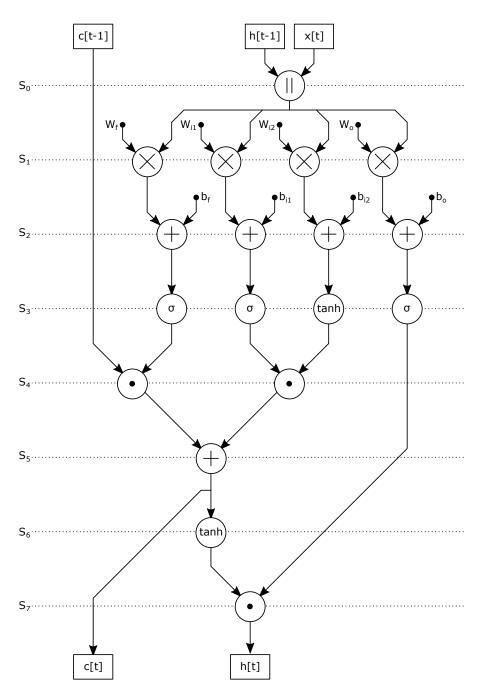

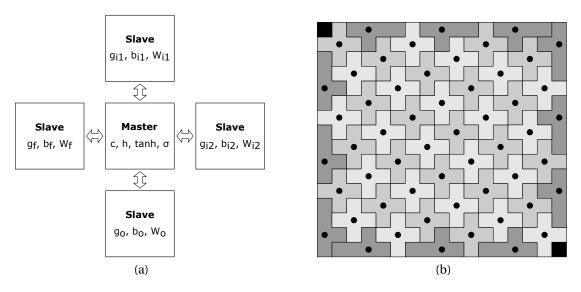

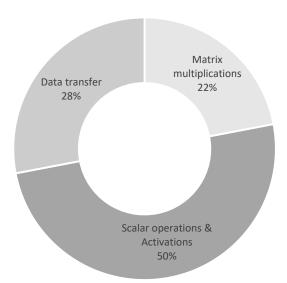

| 4.10 | LSTM cell structure                                         | 105 |

| 4.19 | LSTM scheduling graph                                       | 104 |

| 4.20 | Clustering of <i>Ultra</i> Phase cores for LSTM computation | 106 |

| 4.21 | LSTM execution time                                         | 106 |

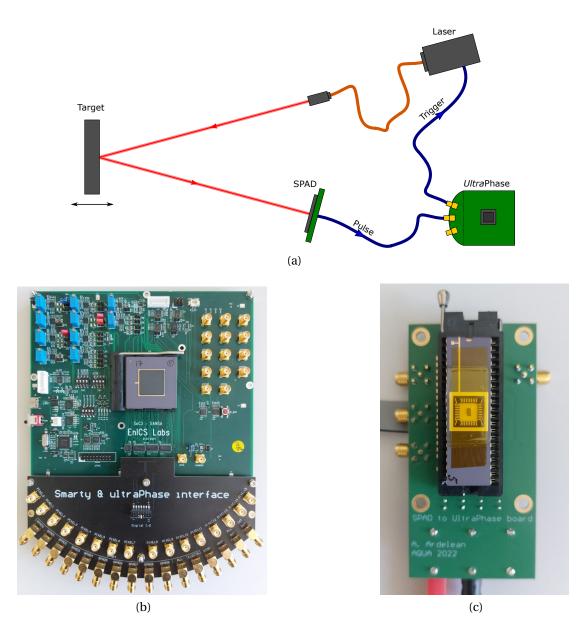

| 4.22 | <i>Ultra</i> Phase LSTM setup                               | 108 |

|      |                                                             |     |

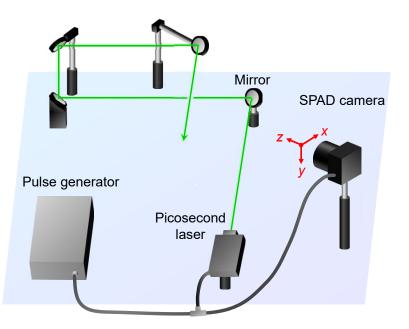

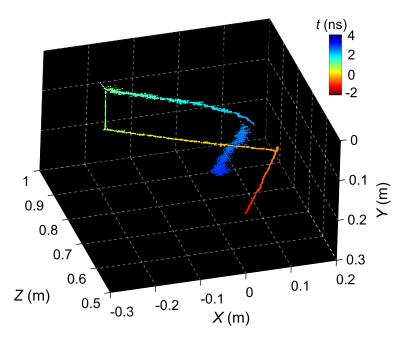

| 5.1  | Experimental setup for light-in-flight imaging              | 116 |

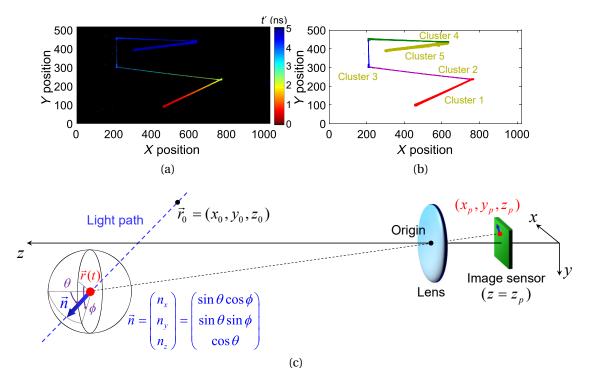

| 5.2  | Light-in-flight measured data                               | 117 |

| 5.3  | Reconstructed 4D light-in-flight path                       | 117 |

|      |                                                             |     |

# List of Tables

| 2.1  | <i>kilo</i> Phase power consumption                             | 41  |

|------|-----------------------------------------------------------------|-----|

| 2.2  | <i>kilo</i> Phase state of the art comparison                   | 51  |

| 3.1  | <i>Mega</i> Phase frame rate and throughput                     | 57  |

| 3.2  | Library corners used for the <i>Mega</i> Phase timing analysis  | 67  |

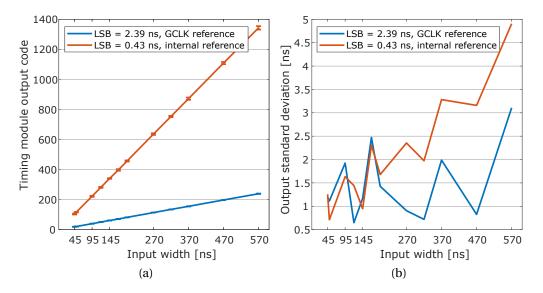

| 4.1  | <i>Ultra</i> Phase Timer module configurations                  | 78  |

| 4.2  | <i>Ultra</i> Phase Byte selector functions                      | 79  |

| 4.3  | <i>Ultra</i> Phase ALU operations                               | 80  |

| 4.4  | Library corners used for the <i>Ultra</i> Phase timing analysis | 90  |

| 4.5  | <i>Ultra</i> Phase instruction operands                         | 92  |

| 4.6  | <i>Ultra</i> Phase CMP instruction effect                       | 92  |

| 4.7  | <i>Ultra</i> Phase Timing module resolution                     | 97  |

| 4.8  | Histogram encoding performance                                  | 101 |

| 4.9  | <i>Ultra</i> Phase LSTM implementation RAM usage                | 105 |

| 4.10 | <i>Ultra</i> Phase state of the art comparison                  | 109 |

# List of acronyms

| ALU   | arithmetic and logic unit                |

|-------|------------------------------------------|

| APD   | avalanche photodiode                     |

| BEOL  | back-end-of-line                         |

| BSI   | backside illuminated                     |

| CCD   | charge-coupled device                    |

| CIS   | CMOS image sensor                        |

| CMOS  | complementary metal-oxide-semiconductor  |

| СоВ   | chip on board                            |

| CPU   | central processing unit                  |

| CVIS  | CMOS vision sensor                       |

| DCR   | dark count rate                          |

| DMUX  | demultiplexer                            |

| ESD   | electrostatic discharge                  |

| FEOL  | front-end-of-line                        |

| FLIM  | fluorescence lifetime imaging microscopy |

| FPGA  | field programmable gate array            |

| FSI   | front-side illumination                  |

| FSM   | finite state machine                     |

| G-APD | Geiger-mode avalanche photodiode         |

| GPU   | graphics processing unit                 |

| IRF   | impulse response function                |

| LiDAR | light detection and ranging              |

| LSTM  | long short-term memory                   |

| LUT   | lookup table                             |

| LVS   | layout versus schematic                  |

| MAC   | multiply-accumulate (operation)          |

| MUX   | multiplexer                              |

| NA    | numerical aperture                       |

| NMOS  | n-type metal-oxide-semiconductor         |

| PC    | program counter register                 |

| PCB   | printed circuit board                    |

| PDE   | photon detection efficiency              |

|       |                                          |

#### List of Tables

| PDP  | photon detection probability  |

|------|-------------------------------|

| PLL  | phase-locked loop             |

| QE   | quantum efficiency            |

| RAM  | random-access memory          |

| ROI  | region of interest            |

| ROM  | read-only memory              |

| SNR  | signal-to-noise ratio         |

| SoC  | system on a chip              |

| SPAD | single-photon avalanche diode |

| TDC  | time-to-digital converter     |

| TEC  | thermoelectric cooler         |

| ToF  | time-of-flight                |

| TSV  | through-silicon via           |

| XOR  | exclusive or                  |

## **1** Introduction

### 1.1 Computational imaging

Computational imaging can be defined as the process of recovering optically encoded scene information from measured data through the use of image processing algorithms. The technique has applications in a variety of fields such as fluorescence lifetime imaging microscopy (FLIM) [1]–[3], compressive imaging [4]–[6], depth imaging [7]–[11], spectral imaging [12]–[14], light field imaging [15]–[17] and computed tomography [18]–[20], to name only a few. In addition, computational imaging techniques can overcome hardware limitations of both optics and sensors by transferring the burden to the software domain where algorithm improvements are easier to come by. Good examples of this are coded aperture imaging systems [21]–[23] or super-resolution microscopy techniques [24]–[28].

The constant evolution seen by CMOS image sensors (CIS) in the last decades has resulted in sensors of 71 megapixels, pixel pitch of 1.1  $\mu$ m, data rates above 10 Gpx/s and architectures that include preprocessing electronics to enhance image quality [29]–[33].

However, this increase in speed and resolution comes at a cost when the image sensors are used in complex hardware-software vision systems where they capture images that are then delivered for processing to other blocks [34], [35]. Raw pixel data is largely redundant and reduced subsets of samples can successfully be used to extract the same information contained in the original data [36]. As a result, a vision system built around a conventional image sensor needs to read, encode, transmit and store a large quantity of data, some of which contains no information [29]. For this reason, a new type of image sensor was developed, the *computational imager* or *CMOS vision sensor* (CVIS), a device that outputs image *features* or *decisions* resulting

from performing vision tasks right at the imager plane [29].

In general, CVIS can be classified into two categories [29]:

- *Specific-purpose* architectures that are dedicated to a specific task implemented in hardware, such as histogramming photon arrival times [37]–[40], kernel convolutions [41] or biomorphic architectures [42]–[45].

- *General-purpose* architectures which contain analog and digital circuits capable of storing and executing user-selectable instruction sequences [46]–[53].

Contemporary general-purpose CVIS are mixed signal designs that try to combine the best of both worlds. The analog front ends integrate well with the CMOS pixel and are a fast and low power method of implementing nonlinear functions commonly used in image processing algorithms. The digital processing blocks are flexible, robust and can be reconfigured through software. The most efficient architectures so far employ arrays of multi-functional mixed-signal processing elements that complete computationally intensive vision tasks in a fully parallel fashion for all the pixels or for one subsection at a time [29], [54].

Massively parallel vision sensors with image formats of up to  $256 \times 256$  have already been developed in academia [47], [48]. These devices can operate at high frame rates and are very well suited for implementing simple image processing algorithms such as edge detection, thresholding and median filtering. The disadvantages come from performing these operations in the analog domain, which requires the use of a large number of biasing signals, therefore multiple digital to analog converters, and analog memories. Every operation to and from the memory contains a signal dependent error component which accumulates with every iteration and limits the maximum processing speed of the device. In addition, stored analog values degrade over time at rates of up to 2.8 % per second, which makes it necessary to switch to and from the digital domain in order to use long term memories for applications where inter-frame storage is required, such as motion detection [47].

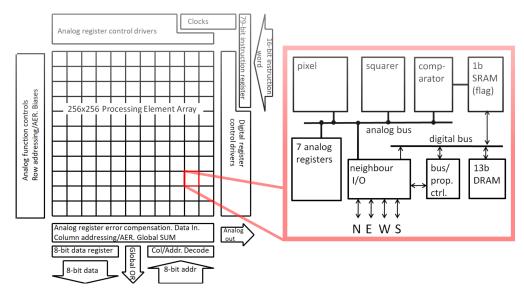

Figure 1.1 is a block diagram of the large format CVIS architecture described in [48]. The design consists of an array of analog processing elements, one for each pixel, that can communicate with their nearest neighbors and can simultaneously execute the same instruction. As described before, computing in the analog domain requires the use of biasing, control and error correction circuitry, which can be seen in this design as well. The chip has been successfully used in complex applications such as convolutional neural networks [55], [56].

Figure 1.1: Block diagram of the large format CVIS architecture from [48]. The design consist of an array of analog processing elements that can communicate with their nearest neighbors and can simultaneously execute the same instruction. Biasing, control and error correction circuitry, typical for analog processing implementations, can be seen in the design. Figure sourced from [56].

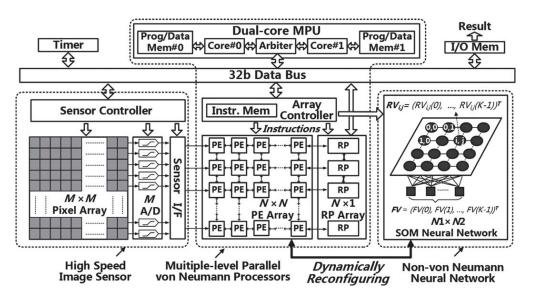

More recent architectures, like the one shown in Figure 1.2, rely on an analog-to-digital conversion right after the pixel, followed by processing on small digital elements. These types of CVISs have already been proven capable of running more complex tasks such as gesture classification with neural networks at frame rates of more than 1000 fps and even facial recognition [49].

Commercial systems such as Teledyne Eye-RIS [46] are currently available for industrial applications in machine vision, automotive and security. Achieving 10 kfps while processing 176 × 144 resolution images is now possible and can replace complex vision systems with a compact and low power alternative.

The CVIS systems previously described were all based on analog pixels consisting of photodiodes which operate in the linear regime, however, a completely digital pixel built around single-photon avalanche diodes (SPADs) is arguably better suited for processing architectures. Initially requiring custom processes, SPADs can now be fabricated using standard CMOS, allowing the integration of readout circuitry in the pixel [57]–[62]. SPAD imager architectures are now available with in-pixel digital counters, active quenching and recharging circuits and even time-to-digital converters (TDC) [39], [63]–[65]. Developments in deep submicron technology and 3D-stacked processes have increased pixel complexity even further and the spatial resolution of

Figure 1.2: Block diagram of the large format CVIS architecture from [49]. The design relies on immediate analog-to-digital conversion of the pixel value which is then processed by an array of small digital elements. In this case, an additional dual-core CPU is needed to manage the chip. Figure sourced from [49].

SPAD imagers has reached and surpassed the megapixel level [66]–[68]. More details about the SPAD structure and metrology are given in Chapter 1.3.

The emergence of large format SPAD imagers has made the significant advantage of the reduced output data rates of computational imagers even more relevant. The amount of raw data that large format SPAD imagers generate is excessive, as state of the art pixels can operate at hundreds of Mcps [69], [70], resulting in data rates in the order of tens of GB/s, a challenge even for modern data interfaces.

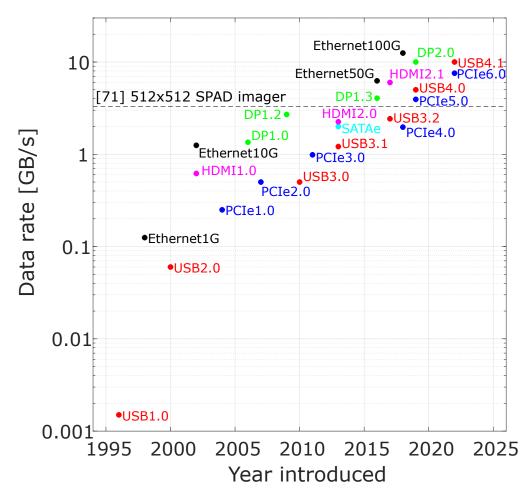

Figure 1.3 shows a comparison between the data rates of common interfaces and the data rate of a 512 × 512 SPAD imager published in 2019 operating at full speed [71]. Even in this case, convenient interfaces such as USB3.0 and PCIe are either insufficient or require multiple channels. The interfaces that can natively handle this data rate are either newly standardized and not yet available or extremely demanding on hardware, requiring for example high speed grade FPGAs and storage solutions. There is a clear conclusion that in order to take full advantage of the high speed single-photon capabilities of these types of detectors, data processing needs to take place on chip, to reduce data rates and, among others, the associated power consumption.

Figure 1.3: Bandwidths of common interfaces compared with the output data rate of [71], a state of the art large format SPAD imager published in 2019 operating at full speed.

### **1.2 FLIM**

Fluorescence lifetime imaging microscopy (FLIM) is a computational imaging technique based on the differences in timing response of fluorescent molecules. The average delay between the excitation and emission of a fluorophore follows an exponential distribution characterized by a specific decay rate or *lifetime* that is dependent on the biochemical environment but immune to signal intensity variations. As a result, high contrast images with selectively labelled features can be formed even when background light or photon scattering effects are present. The dependency on the environment can be used to determine pH levels, viscosity, oxygen and ion concentrations, as well as conformal changes of molecules and interactions between them at distances below the diffraction limit [72]–[80].

### 1.2.1 Photon counting techniques

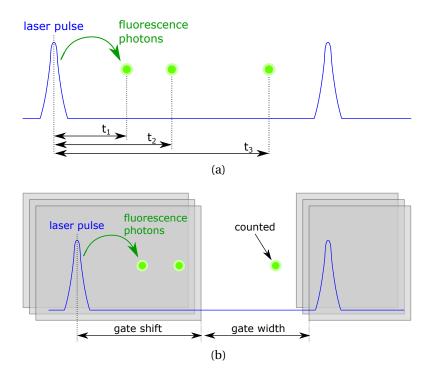

Figure 1.4: (a) In TCSPC the three distinct photon arrival times  $t_1$ ,  $t_2$  and  $t_3$  are recorded w.r.t. the laser pulse. (b) In time gating, only the photon that arrives inside the gate window is registered and assigned to the time bin corresponding to the current gate shift.

#### TCSPC

Time-correlated single-photon counting (TCSPC) is a technique that measures the difference in arrival times between the excitation pulse and the photons emitted by the sample (see Figure 1.4a). The process is repeated multiple times until the fluores-cence decay profile is obtained. Due to the high signal-to-noise ratio (SNR), TCSPC is the primary reference for many time-resolved measurements, from FLIM to light detection and ranging (LiDAR) and optical tomography [81].

TCSPC performance is mainly affected by two factors: dead time and timing resolution; characteristics of both the photodetector and the electronics. Early TCSPC hardware was limited to single channel systems that suffered from performance degradation when extended to multi channel versions. However, the invention of laser scanning confocal microscopes lead to TCSPC-based FLIM becoming widely used at the start of the XXI-st century [82]. State-of-the-art commercial TCSPC systems can achieve picosecond timing resolutions and sub nanosecond dead times, however, these devices are bulky pieces of equipment that can handle only up to 64 channels [83]. Recently, widefield TCSPC architectures have emerged based on position-sensitive detectors, most commonly microchannel plates (MCP) coupled with charge-coupled devices (CCD) or CMOS cameras or arrays of native single-photon detectors such as SPADs or superconducting nanowires. Unfortunately, MCP-based systems are limited to MHz frame rates, while SPAD arrays have low fill factor and a limited number of timing channels.[37]

#### **Time gating**

Time gating consists of acquiring timing information using square-shaped sampling windows created in the readout electronics that are phase-shifted with respect to the excitation pulse (see Figure 1.4b). Initially, heterodyning was used to implement the required phase shifts and modulation of the photodetector gain was required, but state of the art electronics can now achieve picosecond shifts with ease through the use of high frequency phase-locked loops (PLL) or delay lines while keeping the photodetector bias constant [84].

In addition, multiple sampling windows can be generated simultaneously, achieving 100 % duty cycle w.r.t. the excitation period and as a result, high count rates. Conversely, the temporal resolution is inferior to TCSPC because the latter can achieve narrower time bins. In addition, narrower gates require more parallel channels in order to maintain the same duty cycle, which leads to fill factor degradation and substantial data rate increases.

Time-resolved CCD and CMOS cameras implement digital time gates as multitap pixels and use external voltage modulation to direct photoelectrons to the tap corresponding to the current sampling window. On the other hand, SPAD imagers use gating transistors between the photodiode and the memory cell.

The difficulties of implementing in-pixel time tagging electronics without degrading the fill factor, coupled with the count rate penalties associated with sharing these circuits among multiple pixels has caused time-gating to become the main method of implementing large format time-resolved SPAD imagers [66], [67], [71] and for this reason was implemented in all the architectures presented in this thesis.

#### 1.2.2 Phasor-based FLIM

Both previously mentioned photon counting techniques are capable of reaching videorate speeds while detecting sufficient photons to estimate the fluorophore lifetime with acceptable precision. The bottleneck has historically been the data processing step that employs slow and resource intensive lifetime estimation methods. Initially, exponential curves were fitted to the measured photon arrival time histograms using least squares or maximum likelihood estimation methods. [85], [86] These iterative tuning methods are computationally complex and perform poorly in terms of speed when handling multi-exponential decays. In addition, they require a priori information about the exponential models, which in some cases is undesirable.

Various methods of improving lifetime estimation speeds have been developed, starting from the use of graphics processing units (GPU) to parallelize algorithm execution in detriment of power consumption and cost [87], to the use of less complex estimation algorithms such as Laguerre expansion [88], rapid lifetime determination [89]–[91] and the center of mass method [92]–[94]. Unfortunately, the less complex algorithms suffer from reduced lifetime precision or require narrow time bins.

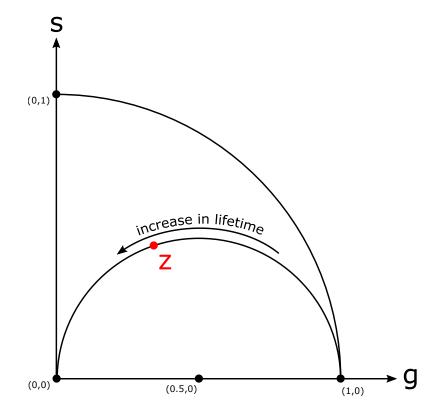

Phasor-based FLIM has become a popular method for fast lifetime analysis because it only involves elementary arithmetic operations, doesn't require a priori information and offers a graphical representation of all the lifetimes from the sample [95]. The method is commercially available in data analysis systems such as [96] used by [97], [98]. The method consists of using the measured photon count  $I_k$  of each time bin with associated delay  $t_k$  to compute the phasor given by:

$$z = g + js = \frac{\sum_{k=1}^{N_{bins}} I_k [cos(2\pi f t_k) + jsin(2\pi f t_k)]}{\sum_{k=1}^{N_{bins}} I_k},$$

(1.1)

where  $N_{bins}$  is the total number of bins/gates and f is the phasor frequency, typically chosen to be equal to the laser repetition frequency. When plotted on the complex plane, all phasors z corresponding to a single exponential decay are located in the first quadrant on a semicircle centered at (0.5, 0), with long lifetimes closer to the origin (see Figure 1.5). The lifetime of a single-exponential decay can be determined as:

$$\tau = \frac{1}{2\pi f} \frac{s}{g}.$$

(1.2)

Figure 1.5: For a single-exponential decay, phasor z is located on the semicircle centered at (0.5,0), with lifetimes increasing counterclockwise.

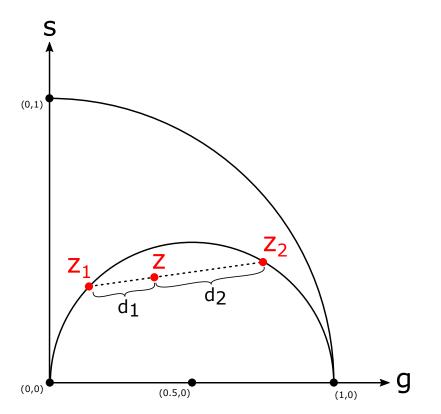

In the case of multi-exponential decays, the phasors are located inside the semicircle, between the phasors of the single-exponential components. In the simplest case, a double-exponential, the phasor is located on the chord formed by the phasors of the two components (see Figure 1.6), splitting it into two segments of length  $d_1$  and  $d_2$ , the ratio of which can be used to determine the ratio of the two components:

$$r_1 = \frac{d_1}{d_1 + d_2},\tag{1.3}$$

where  $r_1$  is the phasor ratio of the first component. This technique was used in [99] to characterize various mixtures of Rhodamine6G and Cy3B.

It is easy to observe that the implementation of phasor-based FLIM is straightforward, the most complex operation being the division. The sine and cosine terms can be computed a priori and treated as constants because  $t_k$  and f are known. The numerator and denominator from (1.1) can be computed concurrently with the acquisition and the normalization can be skipped entirely if only  $\tau$  is of interest.

Another important advantage of this method is the ease with which the impulse

Figure 1.6: For a double-exponential decay, phasor z is located on the chord between the two single exponential components  $z_1$  and  $z_2$ . The ratio of the two segments of the chord can be used to determine the ratio of two components.

response function (IRF) of the setup can be compensated for. As the phasor-method is essentialy a normalized discrete Fourier transform, deconvolving the IRF consists of a division with complex phasor  $z_{IRF}$ . This phasor can be obtained by measuring a single-exponential sample with known lifetime  $\tau_{ref}$  and dividing the measured phasor  $z_{meas}$  with the theoretical  $z_{ref}$  mathematically obtained using  $\tau_{ref}$ . Compensation phasors  $z_{IRF}$  need to be computed for every phasor frequency f and pixel of the detector.

Phasor-based FLIM can be further sped up by using fewer time bins and undersampling the decay. In this case, the single-exponential phasors are no longer on the semicircle centered at (0.5, 0) and appropriate corrections need to be applied. The effect of undersampling has been analyzed in [100] and [99].

Because of all of the above mentioned advantages, the phasor-based FLIM method was chosen as a target application for two of the designs presented in this thesis.

### 1.3 SPAD

### 1.3.1 Technology and implementation

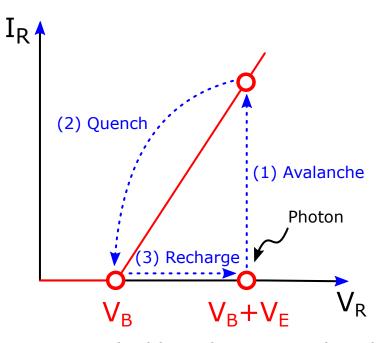

A single-photon avalanche diode (SPAD) or Geiger-mode avalanche photo diode (G-APD) is a solid-state device consisting of a pn junction reverse-biased above its breakdown voltage. Under these conditions, a photon that is absorbed in the depletion region where the electric field is very high, will excite additional electrons due to its kinetic energy, which in turn will cause a self-sustaining avalanche through impact ionisations. The avalanche current will quickly rise to levels that can be damaging to the device, therefore quenching circuitry is normally connected in series with the diode. The simplest version consists of a ballast resistor, but if the durations of the quenching and recharging of the SPAD need to be precisely controlled, active implementations are employed. Figure 1.7 shows the SPAD operating principle.

In contrast to avalanche photo diodes (APDs) operating in linear mode, the magnitude of the avalanche current of a SPAD cannot be used to determine the photon count and is instead converted into a digital voltage, with virtually no readout noise. The leading edge of this pulse can be used to indicate the detection of even a single photon with sub-ns resolution.

Figure 1.7: SPAD operation;  $V_B$  - breakdown voltage,  $V_E$  - excess bias voltage [101].

### 1.3.2 Metrology

The overall noise characteristic of a SPAD imager is dominated by dark counts due to the absence of the readout noise component. A dark count is a spurious avalanche pulse that was triggered in the absence of an incident photon through thermal generation, tunneling and/or trap-assisted processes. These effects are aggravated by increases in temperature or SPAD bias voltage. The average count rate under dark conditions normalized to one second is referred to as *dark count rate (DCR)*. If a SPAD pixel has a DCR at least two orders of magnitude greater than the median value of all the others, it is labelled as *hot* and usually excluded from further analyses [102], [103].

Both photon and noise generated events can in turn trigger a secondary avalanche, either in the same pixel or in the neighboring ones in the case of an array. The former is called afterpulsing and is characterized by the *afterpulsing probability*, while the latter constitutes crosstalk, it too reported as a *crosstalk probability*. The two metrics can be determined using inter-arrival statistics between photons in the same pixel for afterpulsing and in neighboring pixels for crosstalk [104]. An additional method for measuring crosstalk probability is by comparing the DCR of a neigbour of a hot pixel to the average DCR of the entire array [105]. In the case of gated SPAD sensors, the afterpulsing probability is significantly reduced by the long periods when the gate is turned off and the SPAD is insensitive. Conversely, there is no such effect on crosstalk which has to be reduced either through pixel design or by turning off possible aggressors, such as hot SPADs.

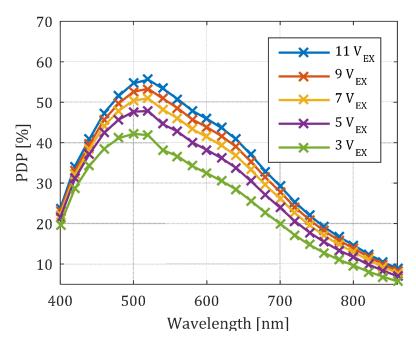

The light sensitivity of the SPAD is characterised by the *photon detection probability* (PDP), a quantity that represents the probability that an impinging photon will trigger an avalanche [106]–[108]. The metric is dependent on wavelength and can be defined as:

$$PDP(\lambda) = QE(\lambda) \times P_t, \tag{1.4}$$

where QE is the quantum efficiency of the detector and  $P_t$  is the avalanche triggering probability. By including the geometric characteristics of the SPAD, we can define the *photon detection efficiency* (PDE) as:

$$PDE(\lambda) = PDP(\lambda) \times FF,$$

(1.5)

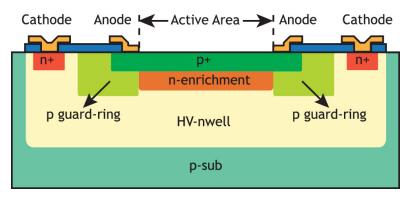

where *FF* is the detector fill factor. PDP can be measured as the ratio between the number of detected photons and the number of incident photons on the entire pixel area. The FF is a purely geometric parameter that depends on the pixel pitch and the distance between two neighboring SPAD active regions. As SPADs operate at high

reverse biases, premature edge breakdown needs to be prevented at the border of the main junction by using guard rings. In addition, strong contacts to the deeper side of the junction also need to be implemented, as shown in the example from Figure 1.8. These regions are insensitive to light and limit the maximum achievable fill factor of a round SPAD to 78.5%, however, the pixel pitch would need to be very large to achieve this [109]. A more convenient method is the use of on-chip microlenses [110]–[112], a method also used for one of the designs in this thesis.

Figure 1.8: Example SPAD cross section: the active region is the junction between the p+ shallow diffusion and the n well, surrounded by the p-doped guard ring [113].

### 1.4 Research motivation

With current developments in large format SPAD imagers and the novel applications that make use of the single photon sensitivity and sub nanosecond resolutions of these sensors, the need to more efficiently manipulate the pixel data arises. Focus can be directed towards two major objectives: **frame rate increase** and **output data rate reduction**. The former will allow the monitoring or compensating for short time scale phenomena [114], [115] while the latter will reduce hardware and system constraints, as current SPAD imagers have already reached the maximum data rates of modern interfaces. Both problems can be solved through the use of on-chip processing elements and the adoption of computational imaging architectures. The digital nature of SPADs is well suited for these types of architectures as it does not require any analog-to-digital conversions and the pixels can be directly interfaced with the processing electronics.

The current trend with SPAD imagers is, as it was with the CIS counterparts, to reach larger, multi-megapixel formats [68] which implies that the computational architectures will have to be scalable, to not limit future developments, but also flexible to implement state-of-the-art computational imaging techniques. New, 3D-stacked

CMOS technologies allow the use of different nodes for the top, photodetector tier, and the bottom processing tier, so complex and scalable architectures can be designed without compromising the optical sensitivity. However, mature 2D technologies are still relevant and require different design paradigms, so research has to be conducted in parallel. In the end, a scalable and flexible architecture is needed to take advantage of SPAD-based imager characteristics, regardless of the technology used for fabrication.

### 1.5 Scientific contributions

The aim of this thesis was to develop sensor architectures for computational imaging that overcome current limitations of SPAD imagers and are capable of running at high frame rates while maintaining manageable output data rates. Three sensors have been designed and implemented in this thesis, all containing on-chip processing capabilities of varying complexities, from application-specific vector processing of pixel columns to fully customizable pixel clustering. The scientific contributions found in these architectures can be summarized as follows:

A token-based pixel readout was developed for SPAD imagers fabricated in 2D technologies and implemented in *kilo*Phase. As opposed to a conventional array readout, the token-based implementation only reads the pixels where a photon has been detected during the exposure, using dedicated channels for each row. As a result, readout time is proportional to the light levels of the scene, which depending on the application, can be sufficiently low to result in significant speed-up.

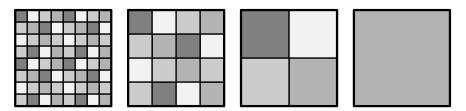

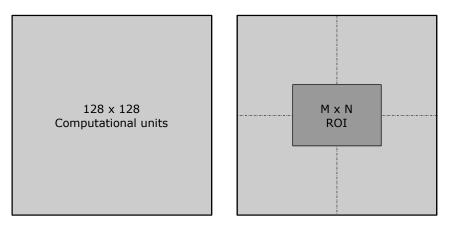

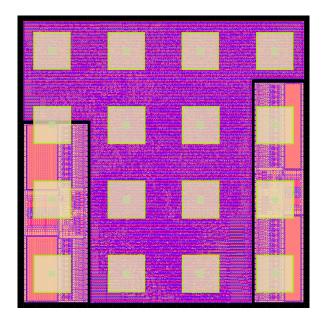

A scalable FLIM processing architecture that takes advantage of advancements in 3D stacking technologies which resulted in *Mega*Phase, the first 3D megapixel SPAD imager with on-chip computational imaging capabilities. The detector consists of multiple processing units operating independently, in parallel, each connected to clusters of SPADs that can be treated as individual binary pixels or binned together into pixels with larger dynamic range. The high degree of parallelism that this architecture employs results in an increase in frame rate of up to two orders of magnitude. Additionally, processing the SPAD data on chip on such a large scale reduces the output data rate by up to three orders of magnitude.

A fully reconfigurable processing architecture was developed and implemented in *Ultra*Phase as a proof of concept non application-specific computational imager. The design can be easily scaled to larger formats and can implement newly developed image processing algorithms without the need of hardware redesign. The result is an array of independent cores, each with connections to pixel front ends, each capable of running software programs with inter-core communication at over one hundred million operations per second.

# 1.6 Thesis structure

Chapter 2 presents *kilo*Phase, a 2D chip architecture developed for FLIM. The system architecture, trade-offs and characterisation results are all discussed. Chapter 3 is dedicated to *Mega*Phase, a megapixel imager in 3D CMOS also developed for FLIM, with the focus on system architecture and comparison with other large format SPAD imagers. Chapter 4 describes *Ultra*Phase, a fully reconfigurable imager with multicore processing and presents a couple of applications that can be easily implemented using the flexibility of the system. Finally, Chapter 5 summarizes the conclusions of the thesis and also contains future work proposals.

# 2 kiloPhase

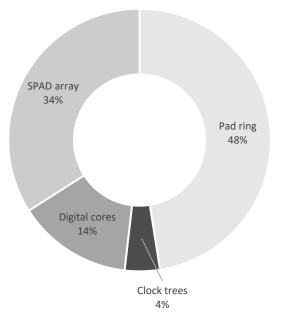

*kilo*Phase is a  $32 \times 32$  SPAD imager developed in 180 nm 2D CMOS technology, with a pixel pitch of 28.5 µm and a fill factor of 28%. The chip contains two accumulator banks each capable of storing one 10 bit image, 32 computational units that each implement one accumulate and two multiply-accumulate (MAC) operations, 3.072 kbit of ROM and 76.8 kbit of RAM. Readout of the SPAD array can be performed by using conventional column addressing or a novel token-passing technique that increases the frame rate by ignoring dark pixels, i.e., pixels that did not fire because no photons were detected or that are dead.

*kilo*Phase can execute the operations shown in equation (2.1) for each pixel, without the need of being read out and can simultaneously process one frame while exposing another.

$$\begin{cases} D = \sum_{m=1}^{128} \left( \sum_{n=1}^{1024} b[n] \right) \times \alpha[m] \\ I = \sum_{m=1}^{128} \left( \sum_{n=1}^{1024} b[n] \right), \end{cases}$$

(2.1)

where *D* is a complex output value, *I* is a real output equivalent to the intensity value of the pixel, *b* is the binary value of the pixel after exposure and  $\alpha$  is a complex coefficient.

At the moment of writing this thesis, *kilo*Phase has been fabricated and tested. The functionality of the token-based pixel readout was successfully validated, together with all the on-chip processing circuitry. The pixel was completely characterized and the chip was operated as a 10-bit imager. The firmware required for FLIM operation is still in development.

# 2.1 Motivation

*kilo*Phase was designed as a proof of concept for real-time computational imaging architectures when only 2D integration technologies are available. The improvements brought forward by this implementation target a frame rate increase through the reduction of the SPAD array readout and off-chip communication along with on-chip data processing.

The objective was achieved by following a set of design guidelines:

- Only pixels with valid information are read.

- All binary frames are accumulated into grayscale frames on chip.

- Grayscale frames are further processed on chip.

- Coefficients needed for processing are loaded at startup.

- Processing of a frame and accumulation of another are done simultaneously.

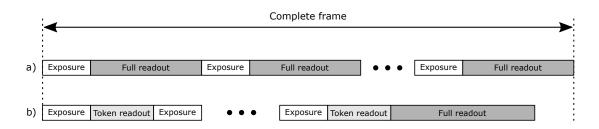

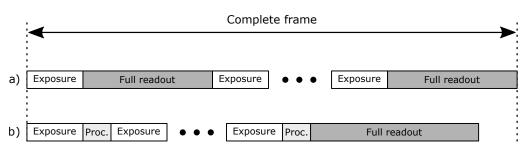

Figure 2.1: Comparison between the readout schemes of a conventional SPAD imager operating with global shutter a) and *kilo*Phase b). In the case of the latter, each binary exposure is followed by a token-based readout that on average is faster than the conventional one. A full readout is only required at the end of the acquisition.

The resulting chip operation no longer requires the off-chip readout of binary frames and instead condenses all the information into a single processed frame, read out at the end of the computation. Figure 2.1 shows a comparison between conventional gated SPAD imagers like the ones presented in [66], [71], [116] operating with a global shutter and *kilo*Phase. Assuming that the conventional chips are used for gated FLIM (as described in Chapter 1.2.1), we can compute the total time  $T_{frame}$  required to acquire one FLIM frame as:

$$T_{frame} = (N_{EXP} \times T_{laser} + T_{binaryreadout}) \times N_{ACC} \times N_G, \tag{2.2}$$

where  $N_{EXP}$  is the number of openings of the gate signal during the exposure of one binary frame,  $N_{ACC}$  is the number of binary frames being accumulated into a grayscale image,  $N_G$  is the number of gates used for the FLIM computation,  $T_{laser}$  is the pulse repetition period of the laser and  $T_{binaryreadout}$  is the total time needed for the readout of a binary frame.

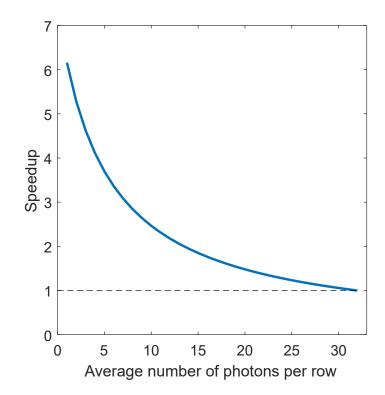

Figure 2.2: Theoretical maximum speedup of *kilo*Phase compared to conventional SPAD imagers when operating in gated-FLIM with 128 gates

For *kilo*Phase, two readout durations need to be taken into account: the time required to transfer the binary frame into the on-chip accumulator bank  $T_{binaryreadout}$  and the chip readout  $T_{readout}$ . The equation for  $T_{frame}$  becomes:

$$T_{frame} = (N_{EXP} \times T_{laser} + T_{binaryreadout}) \times N_{ACC} \times N_G + T_{readout}.$$

(2.3)

In practice,  $T_{readout} >> T_{binaryreadout}$  and the latter can be computed using:

$$T_{binaryreadout} \le N_{col} \times T_{CLK},\tag{2.4}$$

where  $T_{CLK}$  is the period of the system clock and  $N_{col}$  is the number of columns in the detector. In the case of conventional detectors with column-parallel readout, the equation is an equality. However, in *kilo*Phase each row is read independently and only the pixels that have fired are used. Similar architectures have been presented in literature, however, this is the first autonomous implementation and the first one to have pixel level granularity [117], [118]. As a result, depending on the illumination, a binary frame can be read out in fewer clock cycles. This leads to the maximum increase in gated-FLIM frame rate as shown in Figure 2.2 given for a 128 gate configuration.

# 2.2 Processing flow

(b)

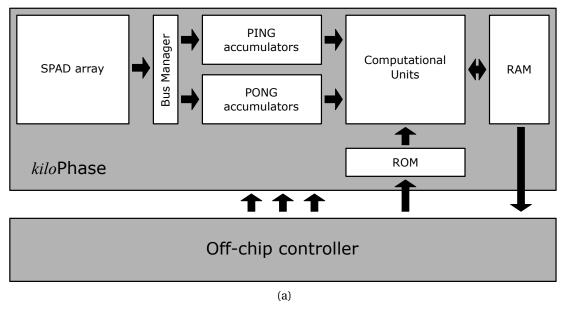

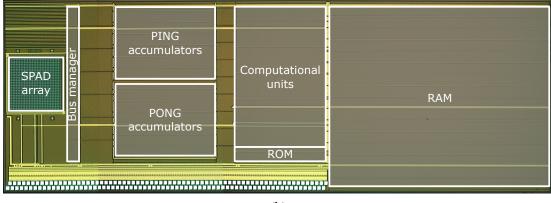

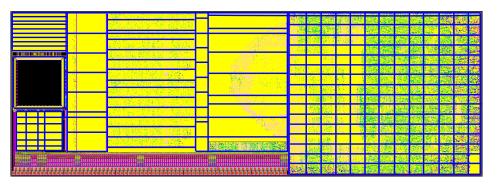

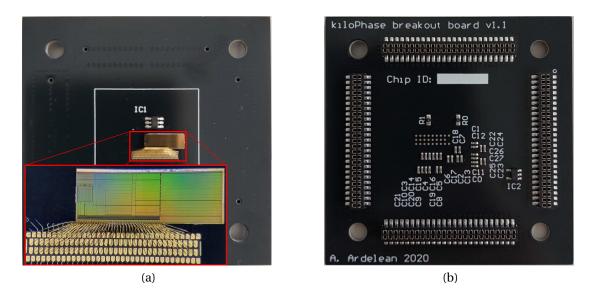

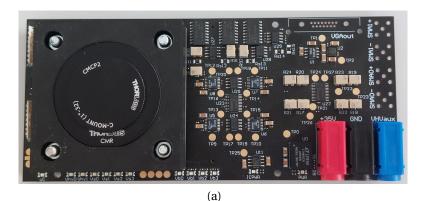

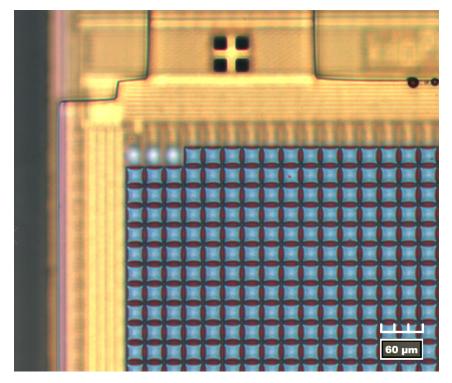

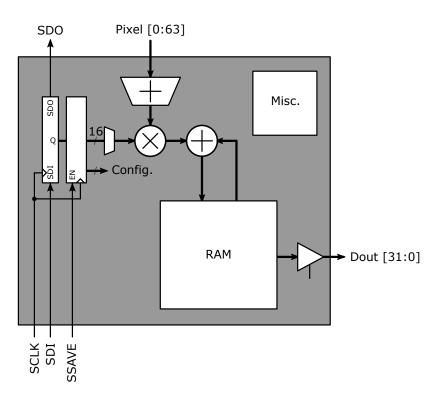

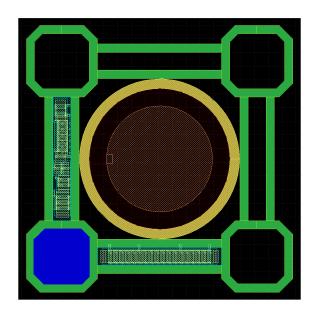

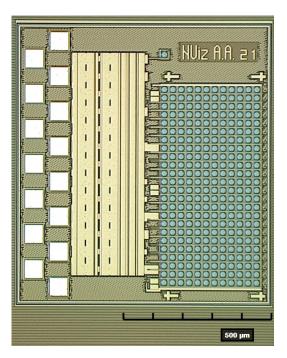

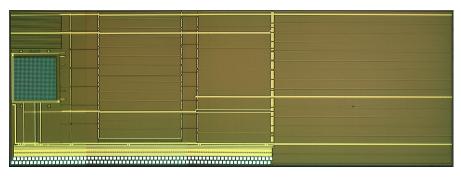

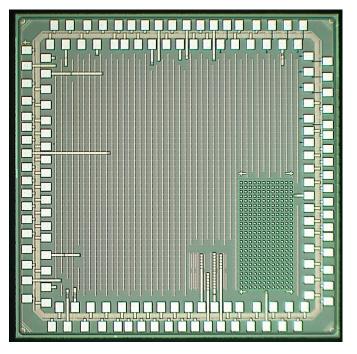

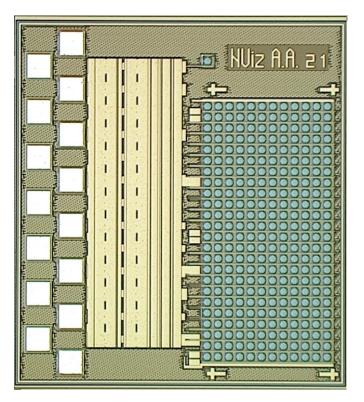

Figure 2.3: (a) *kilo*Phase block diagram consisting of the SPAD array, a Bus Manager for token-passing readout, two accumulator banks, a group of 32 Computational Units and memory blocks. The chip is controlled by an external circuit implemented on FPGA. (b) The same elements highlighted over the chip micrograph. Die size is  $9.5 \times 3.3 \text{ mm}^2$ .

A high level block diagram of *kilo*Phase is presented in Figure 2.3. The seven functional blocks and the communication between them are controlled by a separate external circuit implemented on FPGA. This configuration allows for a high level of customisation but comes at the cost of simplicity of the chip interface which requires 29 control signals.

Normal sensor operation consists of three stages: exposure, computation and readout. The first two can function simultaneously through the use of the PING-PONG accumulator architecture, but chip readout must be performed separately.

Exposure begins with  $N_{EXP}$  openings of the gate signal that result in a 32 × 32 binary image being stored in the *SPAD array* in-pixel memory. This data is then transferred to one of the accumulators via the *Bus manager* either one column at a time or through token-passing (subsection 2.3.2). The cycle is repeated  $N_{ACC}$  times until a grayscale image of the desired bit depth is formed in the accumulator. Total exposure  $T_{EXP}$  for one gate configuration can be computed using equation (2.5) as:

$$T_{EXP} = N_{ACC} \times N_{EXP} \times W_G, \qquad (2.5)$$

where  $W_G$  is the width of the gate signal. A new exposure cycle can begin by switching to the second accumulator bank, which leaves the data that has already been collected intact.

The computation stage lasts exactly 32 clock cycles  $T_{CLK}$  during which the 32 *computational units* will process the data stored in the accumulator bank, one array column at a time, together with the corresponding values from the RAM and ROM. Two MAC and one accumulation operation are simultaneously computed for each pixel p at every iteration n of the computation stage:

$$\begin{cases} D_{G}^{p}[n] = D_{ACC}^{p} \times \alpha_{G}[m] + D_{G}^{p}[n-1] \\ D_{S}^{p}[n] = D_{ACC}^{p} \times \alpha_{S}[m] + D_{S}^{p}[n-1] \\ D_{I}^{p}[n] = D_{ACC}^{p} + D_{I}^{p}[n-1], \end{cases}$$

(2.6)

where  $D_G$  and  $D_S$  are the 29 bit fixed point real and imaginary parts of the complex pixel value,  $D_I$  is the 17 bit integer intensity component,  $D_{ACC}$  is the 10 bit integer value stored in the accumulator and  $\alpha_G$  and  $\alpha_S$  are 12 bit fixed point real and imaginary parts of the complex coefficient stored in the ROM at address *m*. All fixed point values are signed and have 10 fractional bits.  $D_G$ ,  $D_S$  and  $D_I$  are stored in the RAM and reset to 0 at startup and after chip readout, while  $D_{ACC}$  is reset at the begining of the exposure cycle.  $\alpha_G$  and  $\alpha_S$  are loaded at startup. The widths of the variables were chosen to accommodate as many accumulations as possible while respecting the area constrains of the design. The fractional representation results in a relative rounding error of less than 2% when used to store sine and cosine values.

As long as the duration of the exposure is longer than  $32 \times T_{CLK}$ , there will be no dead time of the detector, as the two accumulator banks allow simultaneous processing of the previous frame while exposing the current one. The exposure and computation stages can be repeated multiple times until the desired processing is completed, the only limitations being the ROM size of 128 coefficients and the bit widths of the accumulator and RAM. For example, in the case of FLIM, *kilo*Phase can accommodate 128 gate positions with 10 bit grayscale images for each, or 32 gate positions at 12 bit.

Once all the necessary exposure and computation cycles are performed, the RAM can be read out in  $1024 \times T_{CLK}$  using a 75 bit parallel bus. The readout stage is incompatible with the normal operation of the chip due to pad multiplexing, therefore, the chip must be kept idle.

# 2.3 Architecture

# 2.3.1 Pixel

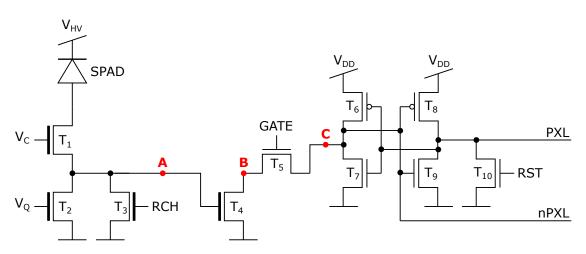

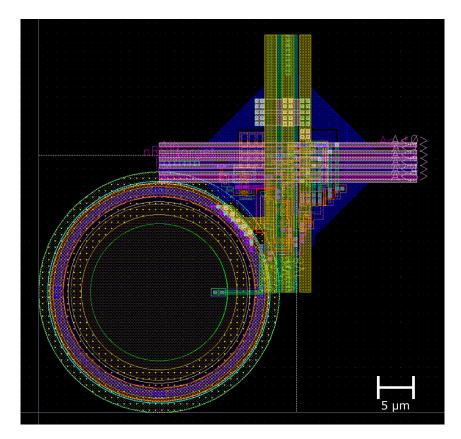

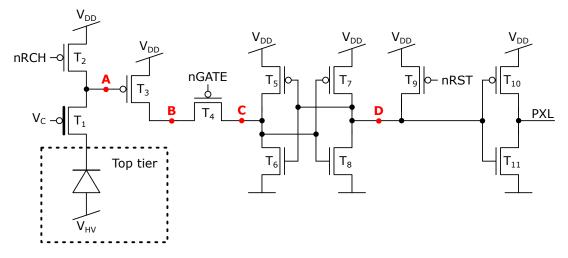

The pixel schematic implemented in *kilo*Phase is shown in Figure 2.4 with the associated layout in Figure 2.5. A total of 10 NMOS transistors are used, with both thin and thick oxide variants. The SPAD structure and  $28.5 \,\mu m$  pixel pitch is identical to the one presented in [37] in order to allow the reuse of an existing microlense design for increasing the 28 % native fill factor.

Cascode transistor  $T_1$  is used to extend the bias voltage range of the pixel and increase the PDP as demonstrated in [119]. Passive quenching of the SPAD is implemented with transistor  $T_2$  and tunable analog voltage  $V_Q$ , while  $T_3$  is used for the clock-driven active recharge controlled by digital signal *RCH*. When an avalanche is formed in the SPAD, the voltage at node *A* will rise and drive transistor  $T_4$  which in turn will bring node *B* to ground. Practically,  $T_4$  serves as a voltage level shifter between the thick oxide transistor section ( $T_1$  to  $T_4$ ) that operates at 3.3 V and the rest of the 1.8 V circuitry. When the *GATE* signal is asserted, transistor  $T_5$  shorts together nodes *B* and *C* which will result in two possible outcomes: if  $T_4$  is also active, node *C* will be pulled to ground and cause the memory cell formed by  $T_6$ ,  $T_7$ ,  $T_8$  and  $T_9$  to toggle. Otherwise,

Figure 2.4: *kilo*Phase pixel schematic containing 4 thick oxide and 6 thin oxide NMOS transistors. Cascode transistor  $T_1$  is used to extend the SPAD bias voltage range.  $T_2$  acts as a passive quenching method and  $T_3$  implements a clock-driven recharge scheme. A pair of back-to-back inverters that can be reset by  $T_{10}$  form a static memory cell. Transistor  $T_5$  is used to gate the pixel.

Figure 2.5: *kilo*Phase pixel layout. The NMOS transistors are all located in the upper right corner of the SPAD. Metallisation is patterned so that the pixel can be abutted to form the desired array with 28.5  $\mu$ m pitch.

node *C* will not change because node *B* will be at high impedance and the memory cell will remain in the reset position. At the beginning of each exposure cycle, *RCH* is pulsed right before the arrival of the first *GATE* which assures that any avalanches that have occurred before the arrival of the gate signal will be ignored. Transistor  $T_{10}$  is used to reset the memory. Both the pixel output signal *PXL* and its inverted value *nPXL* connect to the token-passing cell presented in the following subsection.

# 2.3.2 Token-passing readout

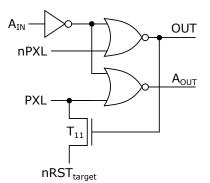

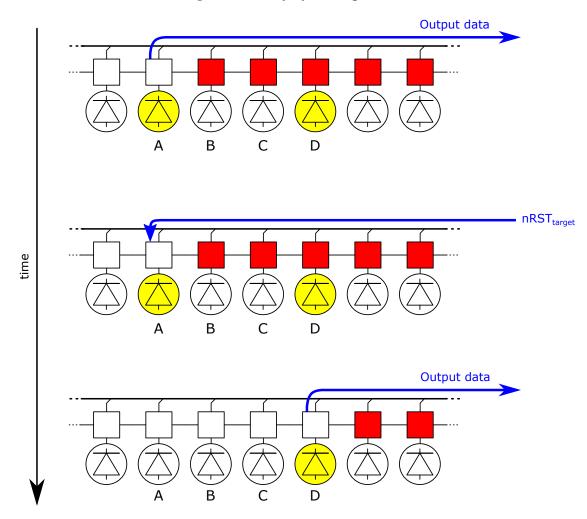

Figure 2.6: *kilo*Phase token-passing schematic consisting of two NOR gates, an inverter and an NMOS transistor. The pixel output PXL is not allowed to pass unless token signal  $A_{IN}$  is high. In this state, if PXL is driven high,  $A_{OUT}$  will be driven low and cause all further token-passing cells to restrict bus access for their corresponding pixels.  $T_{11}$  can be used to perform a targeted reset of the pixel if and only if the pixel currently has access to the output bus.

The token-passing readout mechanism used to reduce the array readout time by skipping pixels that have not fired is implemented independently for each row of the array. Each pixel is assigned a priority, starting with the leftmost pixel in the row that has the highest and decreasing all the way to the lowest priority rightmost pixel. Only the highest priority pixel that has detected a photon can access the row readout bus. In addition, this is also the only pixel that will react to a targeted reset signal  $nRST_{target}$ and will clear its memory and pass the bus access *token* to the next lower priority pixel that requests it.

Figure 2.6 shows the schematic for the token-passing logic circuitry. The pixel output signal PXL and its inverted value nPXL connect to two NOR gates along with the negated value of token signal  $A_{in}$ . When  $A_{in}$  is low, both OUT and  $A_{OUT}$  will be kept low, regardless of the value of PXL. Therefore, the pixel loses access to the bus by having its output signal gated and in turn also blocks the next pixel by not having any token to pass. When  $A_{in}$  is high, the top NOR gate acts as an inverter and the

*OUT* signal has the same value as *PXL*; in other words, the pixel is granted access to the bus because it holds the token. If the access is needed, i.e. *PXL* is high, then the bottom NOR gate will drive  $A_{out}$  low which will block the next pixel's access to the bus. If, however, there has been no photon detection and *PXL* is low, the token is passed to the next pixel by driving  $A_{OUT}$  high. If the pixel has the token and needs access to the bus, gating transistor  $T_{11}$  will be on, driven by the output signal, and  $nRST_{target}$  can be used to reset the in-pixel memory by forcing *PXL* low.

Figure 2.7: *kilo*Phase token-passing principle. Three states of the same pixel row at different moments in time are shown, chronologically from top to bottom. Both pixels *A* and *D* have detected an avalanche, but because the former has priority it receives access to the data bus and blocks the remaining pixels. After the targeted reset signal is received, pixel *A* will reset and release the bus. The token is passed directly to pixel *D* as it is the next highest priority pixel with a detected avalanche.

Figure 2.7 is a representation of the token-passing principle applied for the readout of one row in the case of two detected photons. Both pixel A and pixel D have detected

a photon. However, pixel A has the highest priority and therefore has access to the output bus and holds the token. When the  $nRST_{target}$  signal is asserted, only pixel A will respond by resetting its internal memory and passing the token to pixel B. Because pixel B does not need bus access, it will automatically pass the token to pixel C, which for the same reasons, will pass it to pixel D. In this case, bus access is needed and the token is kept until the arrival of another targeted reset. The entire process takes place after the exposure, when the pixel gate is closed and the output cannot change. As a result, there is no risk of corrupting the readout.

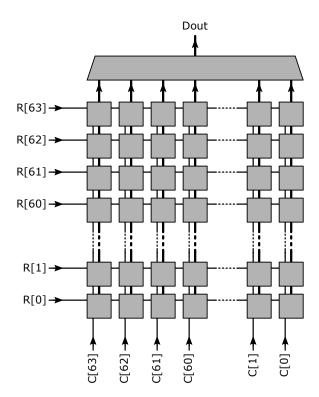

## 2.3.3 Bus manager

The role of the Bus manager circuit block is to convert the pixel output information that comes in the form of individual addresses for every row into the 1024 bit input to the accumulator banks. It also needs to accommodate both token-passing and column addressing readouts.

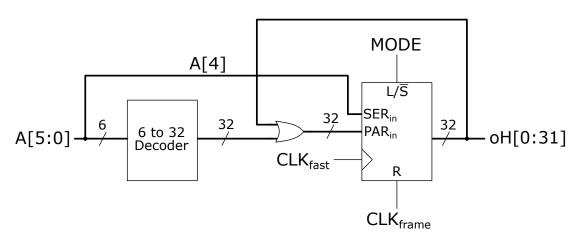

Each pixel row is connected to the circuitry shown in Figure 2.8. In token-passing readout, when a pixel has access to the bus, it will transmit its 5 bit address A to the bus manager where it will be decoded into a one-hot 32 bit representation using a 6-to-32 decoder. The redundant use of 6 bits comes from the fact that all pixel addresses are offset by 1 in order to use bus address 0 as a representation of the free state of the bus. When the rising edge of  $CLK_{fast}$  arrives, the output oH of the bus manager is updated with the one-hot representation of the current token holder pixel through the use of the OR gate. The process repeats when the token is passed to another pixel and ends when the bus is free, at which point oH stores a complete representation of all the pixel states in the row. Asserting  $CLK_{frame}$  clears oH and prepares the circuit for a new readout cycle.

When MODE is at logic zero, the bus manager operates in column addressing readout. Under these conditions, the output of the in-pixel memory is connected to A[4] by a column select signal. The values for each pixel are then serially loaded into the bus manager at every rising edge of  $CLK_{fast}$ . Readout is complete after 32  $CLK_{fast}$  cycles.

# 2.3.4 Accumulator bank

Each accumulator bank consists of 1024 10 bit counters arranged in a  $32 \times 32$  grid that mirrors the pixel array. Each row of 32 counters shares a 10 bit output bus, access to which is controlled using a 5 bit selector signal common to all the rows. The output buses for each row are concatenated into a  $32 \times 10$  bit bank bus.

Figure 2.8: *kilo*Phase Bus manager circuit schematic for one row of the array. The 6 bit pixel output bus *A* containing the column address of the current token holder is decoded into a 32 bit one-hot representation and then combined with the Bus Manager output with an OR gate.  $CLK_{fast}$  is used to update the output with the new value while  $CLK_{frame}$  acts as a reset signal. If *MODE* is held low, conventional readout is used and the *oH* output is updated serially by shifting the values on bit 4 of the input bus.

Each individual counter can be enabled using the corresponding bit from a 1024 bit input bus, considering that the top left counter has index 0 and the bottom right one has index 1023. A global synchronous reset signal is used to clear all the counters in the accumulator banks.

The 1024 bit inputs to the two accumulator banks are driven by a 1-to-2 demultiplexer (DMUX) which in turn is driven by the Bus manager. The two 32 × 10 bit bank outputs are merged using a 2-to-1 multiplexer (MUX) and then serve as inputs to the computational units. The DMUX and MUX control signals are independent from each other, therefore, the accumulator banks can operate in three modes: PING-PONG, PING only and PONG only.

### 2.3.5 Computational unit

A total of 32 computational units are used in *kilo*Phase, one for each row in the array/accumulator. Using the accumulator selector signal, the pixel data corresponding to an entire array column is presented to the computational unit inputs and processed in parallel.

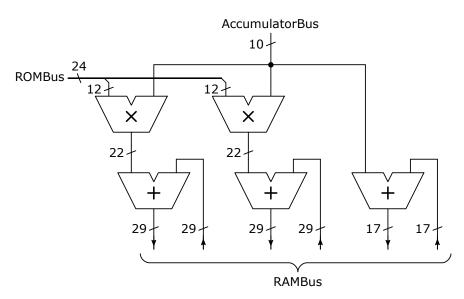

Figure 2.9 shows the schematic for a single computational unit composed of two

Figure 2.9: *kilo*Phase computational unit schematic showing the two 22 bit signed multipliers and the 29 bit, 29 bit and 17 bit accumulators. The operands for the MAC and accumulate operations originate from the upstream pixel accumulators and downstream RAM. The constants required for the two MAC operations are read from a common ROM.

multipliers and three adders. The operations are signed and represented using a fractional fixed point format with 10 fractional bits. The only exception is the standalone 17 bit integer adder used for intensity imaging.

The 10 bit pixel data stored in the accumulators is provided via the *AccumulatorBus*. The value is multiplied with two 12 bit constants stored in ROM and then accumulated with a 29 bit value read from the RAM. A third adder circuit performs a 17 bit accumulation operation with the pixel data. The results are written back to the RAM using the *RAMBus*.

The *ROMBus* used to transmit the two multiplication constants is 24 bits wide and is split between the two multipliers in order to represent a complex number. The *RAMBus* consists of a 75 bit input and a 75 bit output signal.

# 2.3.6 RAM bank

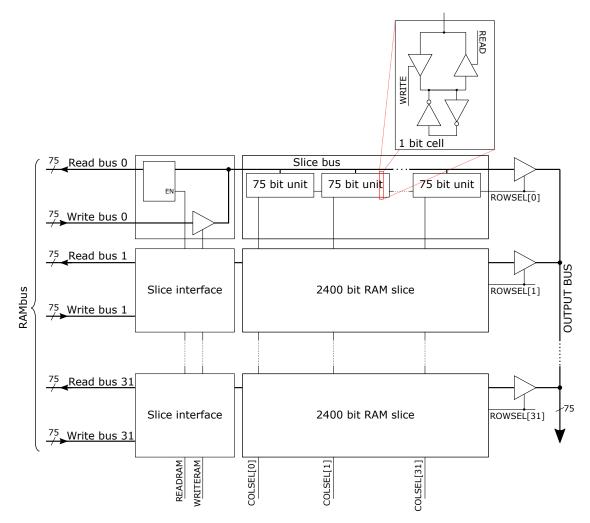

Figure 2.10 shows a high level schematic of the RAM bank implemented in *kilo*Phase. The total available memory is  $1024 \times 75$  bit, organized as 32 *slices* of 32 *units*, each composed of 75 1-bit *cells*. A cell consists of two back-to-back inverters connected to a *slice bus* through two tri-state buffers. The bidirectional slice bus connects to

a computational unit through a *slice interface* block that splits it into a latched *read bus* and a buffered *write bus*. The other end of the slice bus is buffered to a common *OUTPUT BUS* that is used for external readout of the RAM.

Figure 2.10: *kilo*Phase RAM schematic illustrating the complex structure consisting of 32 slices of 32 units. Reading and writing operations are performed using 32 bidirectional buses of  $2 \times 75$  bit. During chip readout, the RAM is read using a row and column addressing scheme, one 75 bit unit at a time, on a separate 75 bit tristate bus.

During the computation stage, one unit from each RAM slice is granted access to the corresponding slice bus and its value is latched into the read bus. At the next clock cycle, the computational unit output which is present on the write bus is propagated to and then stored into the aforementioned slice. The two steps are repeated until all 32 units from the slice have been processed. This arrangement allows the simultaneous processing of an entire 32 pixel column of the array.

During the readout stage, the 1024 RAM units are sequentially given access to the OUTPUT BUS using a row and column addressing scheme. As this procedure also utilizes the slice bus, the readout is incompatible with the computational stage and the chip needs to be kept idle.

# 2.4 Implementation

*kilo*Phase was implemented as distinct sections that were then manually integrated to form the complete system. The design for the pixel array was done by hand while all of the remaining blocks shown in Figure 2.3 were synthesized with Cadence RTL Compiler and routed with Cadence Encounter.

### Pixel

The various transistors from the pixel were sized using SPICE simulations were the SPAD was replaced with an equivalent model like the one shown in [120]. With the layout completed, SPICE simulations with the extracted parasitic components were run in multiple library corners to ensure the validity of the circuit.

When performing the parasitic extraction, the SPAD had to be replaced with a black box as the layout versus schematic (LVS) step of the process couldn't recognize the structure. This is the only point in the design were manual verification had to be used to confirm the final layout.

### Gate and recharge signals

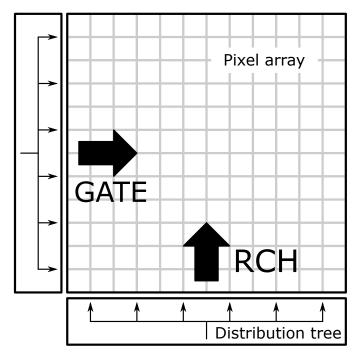

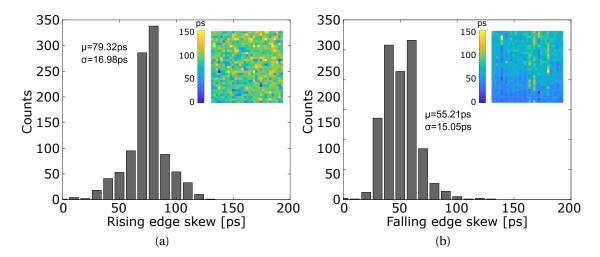

The gate and recharge signals propagate across the pixel array in two orthogonal directions in order to reduce the coupling between them and maintain good signal integrity as the shape of the gate is essential to the operation of the chip. This propagation scheme, shown in Figure 2.11, results in a diagonal skew in the measured gate signal as seen in Section 2.5.7, but the small size of the array reduces the significance of the effect.

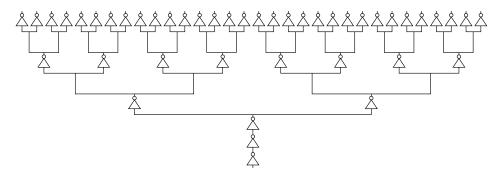

The gate and recharge signals connect to the pixel array through two 1 - to - 32 trees that minimize the skew between the propagation channels. The schematic is shown in Figure 2.12. The trees are built using custom inverter cells that are sized to maintain the propagation delay through the tree as short as possible when driving a 500 fF load on each output. The load was estimated based on the post layout parasitic report.

Figure 2.11: *kilo*Phase gate and recharge propagation scheme across the array. The quadrature arrangement reduces the coupling effect between the two signals.

The final tree design was validated through post layout SPICE simulations in a test bench that used a VerilogA component to act as a load and to measure the delay and skew across all 32 channels simultaneously. The simulations were run in 5 separate transistor library corners: Typical, Fast-Fast, Slow-Slow, Fast-Slow and Slow-Fast.

The power distribution network for the two trees was designed to have low impedance to reduce the voltage drop seen by the inverters in the middle of the tree. A total of 11 pF of decoupling capacitance was added to each tree, in between all the standard cells.

Figure 2.12: *kilo*Phase gate and recharge tree. The inverters were sized to drive a 500 fF load at each of the 32 outputs with minimal propagation delay.

### Timing constraints

As each *kilo*Phase module was synthesized and routed separately, they each had their own timing constraints. The accumulator banks, ROM and RAM were designed for an operation at 200 MHz. The combinational components, namely the MUX, DMUX and computational units were constrained with a virtual clock of 300 MHz. After timing closure was confirmed, the histogram of signal slacks was examined to ensure that the designs were not over or under constrained.

It is important to mention that because the modules were synthesized separately, the input and output constraints had to be written in such a way as to account for the extra delay and parasitic loads that result from the manual integration. For this purpose, all of the designs assumed a minimum sized inverter as their input diver and the input of an  $8 \times$  inverter as their load. The RAM was an exception as it drives a 75 bit output bus that is significantly longer than the other interconnects. In this case, the load was estimated using the interconnect parasitic capacitances reported by the foundry.

## Power distribution

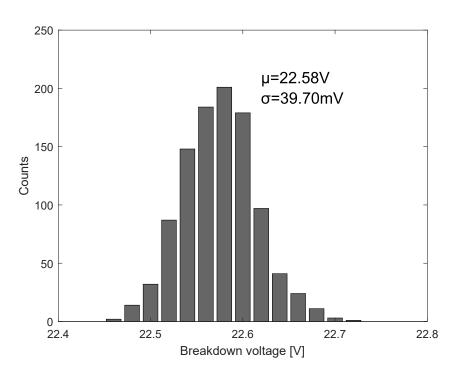

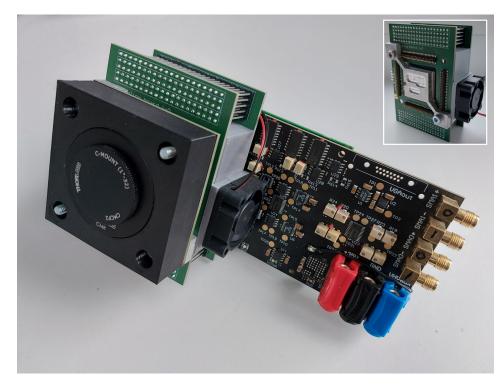

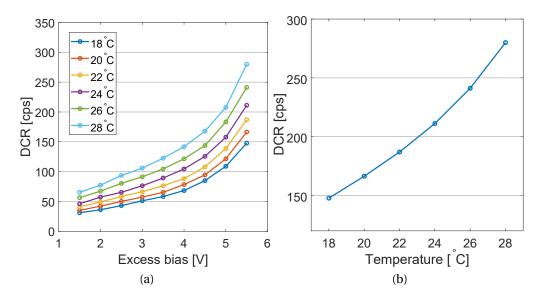

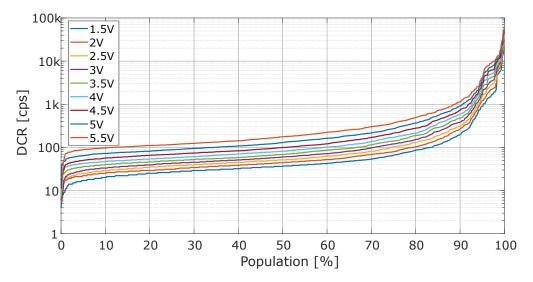

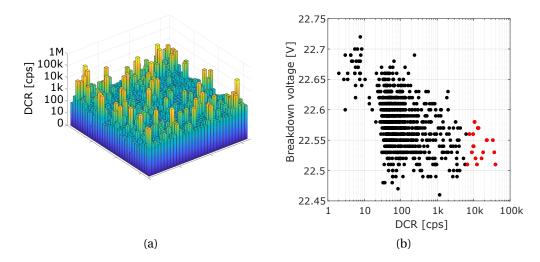

The power grid was routed on the top two available metals that are significantly thicker compared to the rest and exhibit lower resistance. Each *kilo*Phase block was surrounded with a wide power ring that was connected with every standard cell row to assure uniform power distribution. The rings were then stitched together at the top hierarchical level with horizontal and vertical metal stripes as shown in Figure 2.13. The stripes then directly connect to the wide pad ring metals.