## Progress in CMOS SPADs and digital SiPMs for fast timing applications

Claudio Bruschini and Edoardo Charbon

Francesco Gramuglia, Emanuele Ripiccini, Andrada Muntean

> Fast Timing in Medical Imaging Workshop, Valencia, Spain 05/06/2022

École

Polytechnique

Fédérale de

Lausanne

EPFI

#### Introduction

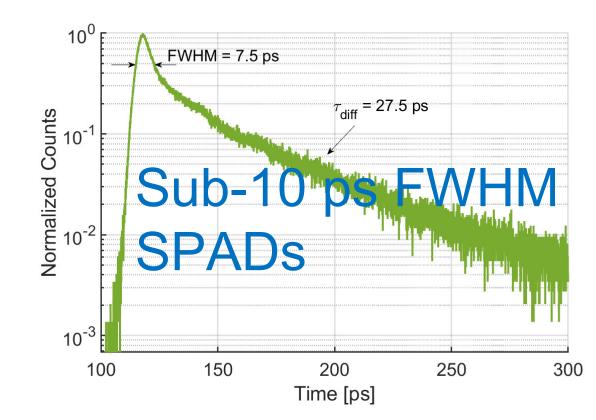

- Sub-10 ps FWHM SPADs

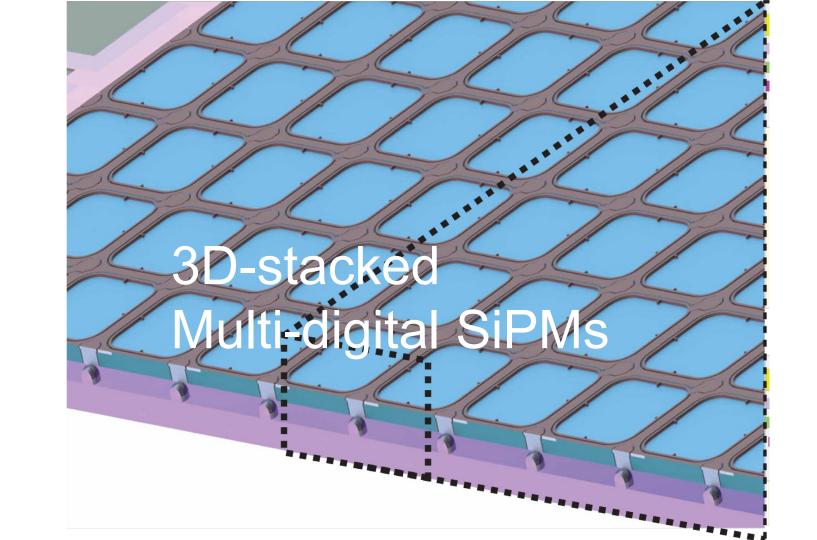

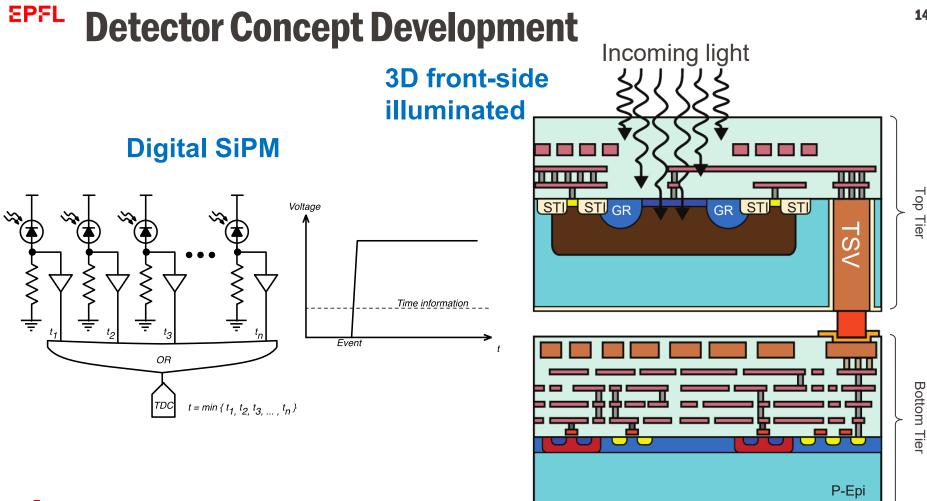

- 3D-stacked multi-digital SiPMs

- Conclusions

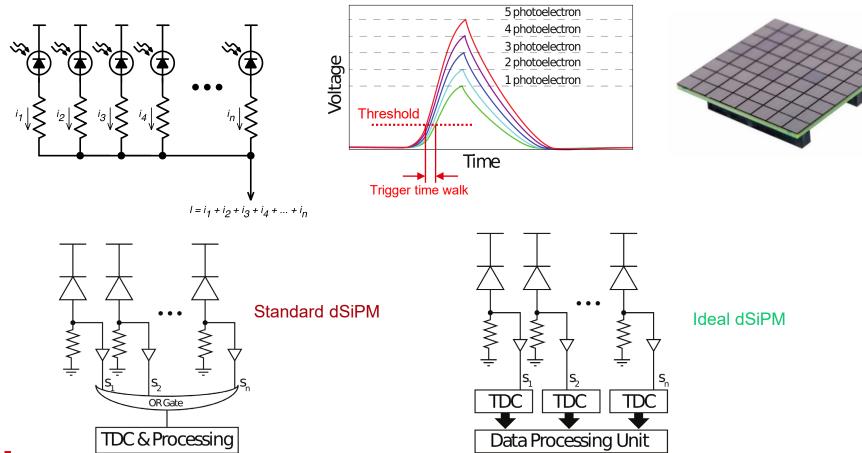

#### **EPFL** Analog vs. Digital Silicon Photomultiplier

# Introduction – Timing in SPADs and SiPMs

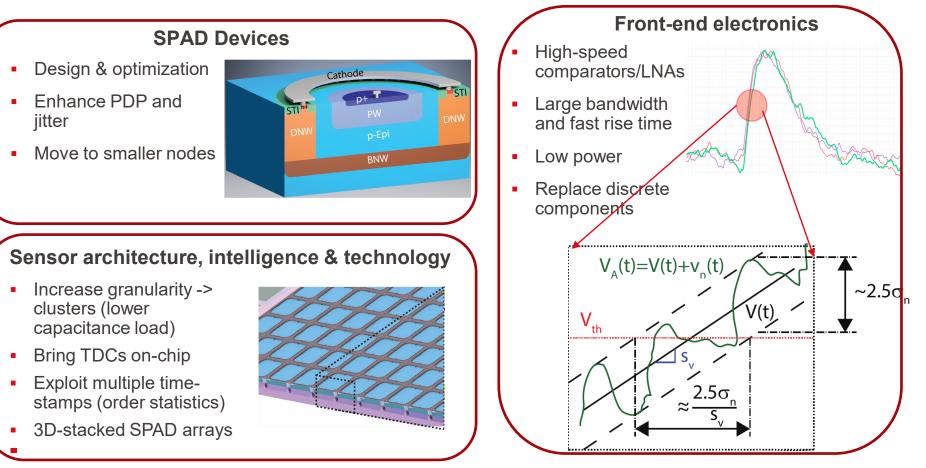

## **EPFL** Routes to high timing precision

EPFL

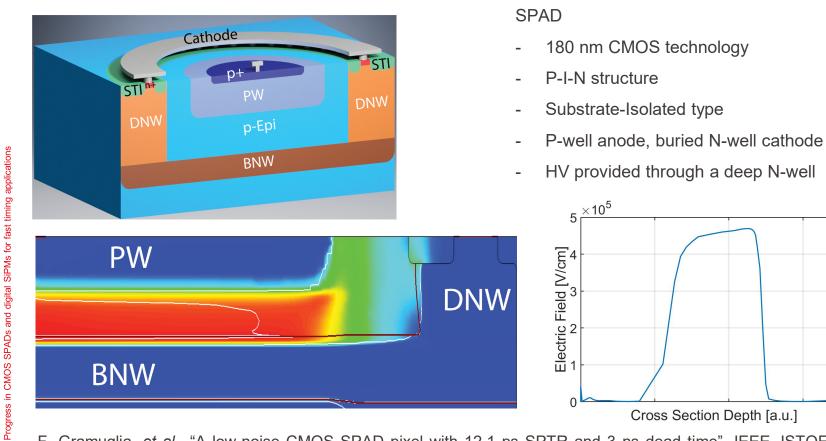

#### **EPFL** SPAD structure

F. Gramuglia, *et al.*, "A low-noise CMOS SPAD pixel with 12.1 ps SPTR and 3 ns dead time", IEEE JSTQE, 2021.

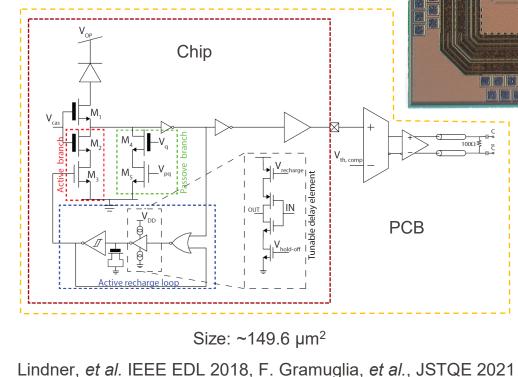

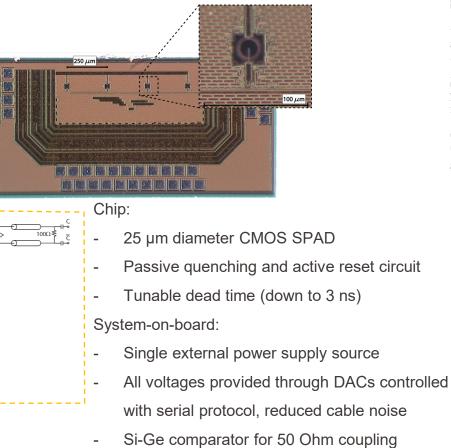

#### **EPFL** SPAD & chip structure and read-out PCB

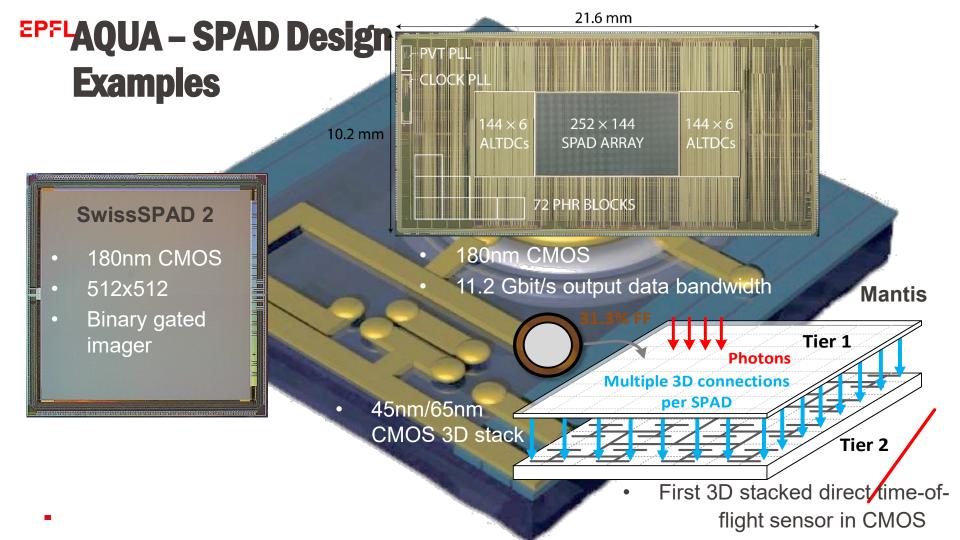

CMOS SPADs and digital SiPMs for fast timing applications

High signal slew rate (≥ 1.6 V/ns)

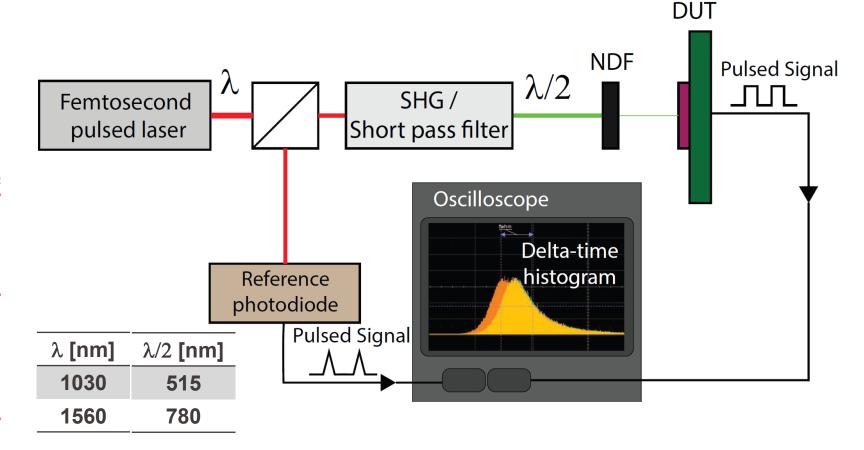

#### **EPFL** Optical Setup

#### **EPFL** Optical measurements (SPTR)

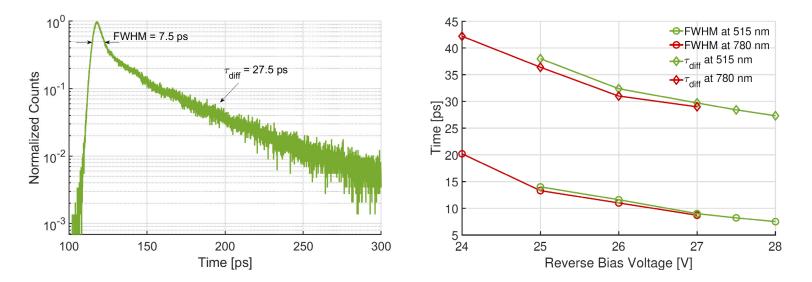

- Jitter of 7.5 ps FWHM at 6.5 Vex for green light, diffusion tail:  $\tau$  = 27.5 ps

- Jitter of 8.5 ps FWHM at 5.5 Vex for red light

(First results @NSS-MIC 2021: 12.1 ps FWHM)

Progress in CMOS SPADs and digital SiPMs for fast timing applications

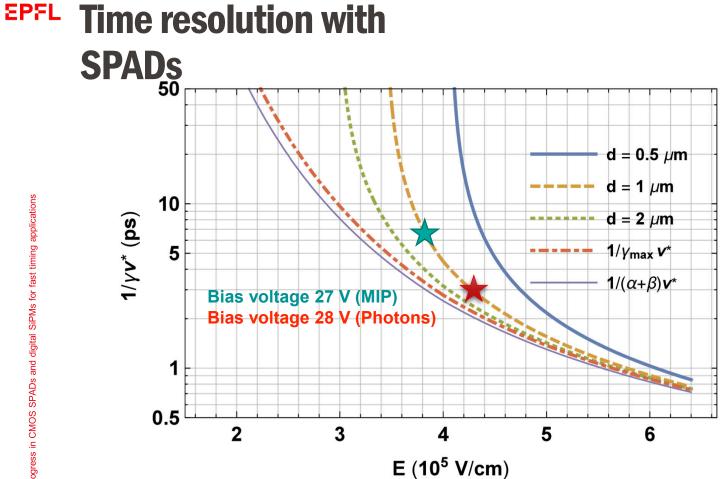

W. Riegler, P. Windischhofer, P. Time Resolution and Efficiency of SPADs and SiPMs for Photons and Charged Particles. Nucl Instr Methods Phys Res Section A: Acc Spectrometers, Detectors Associated Equipment (2021)

EPFL

Bottom Tier

14

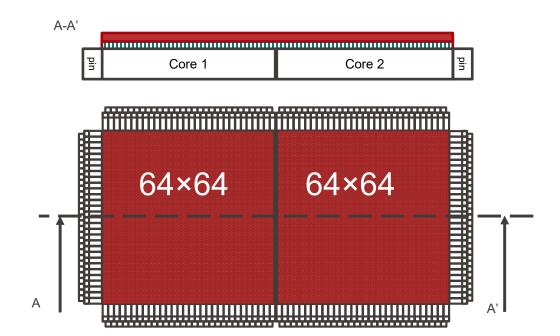

#### **EPFL** Chip Architecture

#### Multi digital SiPM:

- 2 cores

- 64 clusters per core

- 64 SPADs per cluster

- Array of 8192 SPADs (2×4096)

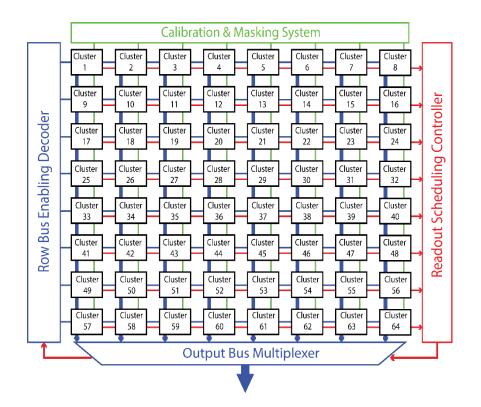

## **EPFL** Chip Architecture

#### Multi digital SiPM:

- 64 clusters per core

- 64 SPADs per cluster

- Random access readout architecture

- Single SPAD masking

- TDC calibration

- Fixed priority scheduling system

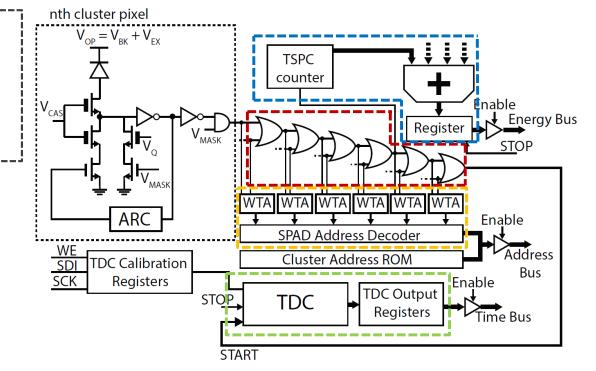

## **EPFL** Pixel & Cluster Architecture

#### **Pixel:**

- Cascode-based passive quenching to allow higher V<sub>ex</sub>

- Active recharge circuit (ARC)

- Single SPAD logic masking

#### **Cluster:**

fast

CMOS SPADs and digital SiPMs

- OR-tree for data propagation

- Single shared TDC

- Photon counting capability

- Fired SPAD address calculation

- Shared bus access through high impedance buffers

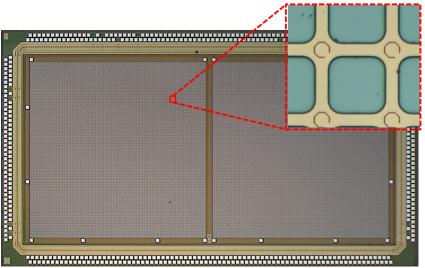

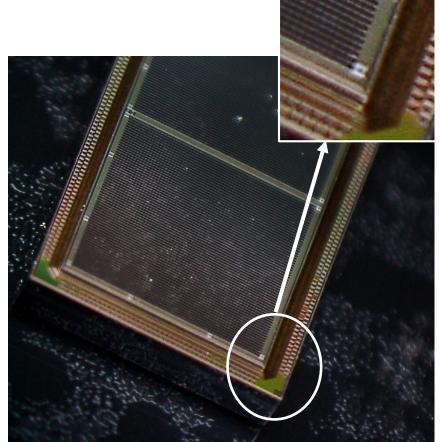

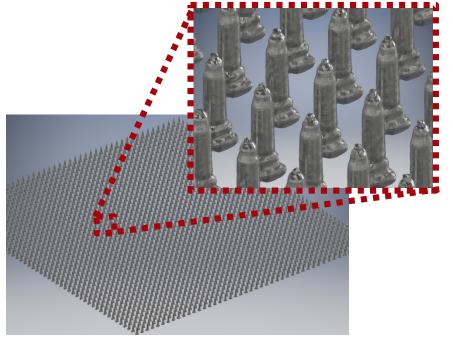

## **EPFL Blueberry TOF Sensor**

#### **3D Stacked Chip:**

- Array size: ~ 7.5×4.2mm<sup>2</sup>

- Number of SPADs: 8192

- Technology node: 180nm CMOS

## **EPFL** Imaging Inspection

- X-Ray tomography

- Voxel 1.42 μm

- Not destructive inspection of TSV structure on large area

SEM images of Microbump detail before (top) and after (bottom) 3D bonding

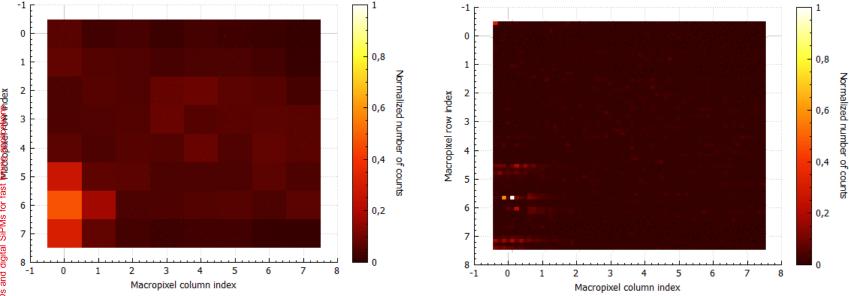

#### **DCR vs Integration Time**

Intensity map built with the output of the photon counting system

Map of the pixel that fired first each frame during the acquisition

Process yield estimation ~90%

21

## Conclusions

#### **EPFL Summary & Conclusions**

Optimized CMOS SPADs in 180 nm technology:

- 7.5 ps FWHM jitter demonstrated noise reduction and front-end optimization are essential at the 10 ps level

- Tunable dead time down to 3 ns, PDP: 55%, AP: 0.12%, DCR: 0.23 cps/µm<sup>2</sup>

- Can also detect minimum ionizing particles (MIPs) @ 6.4 ps sigma

Development ongoing in 55 nm BCD technology:

- 30 ps FWHM demonstrated, tunable dead time down to 1.5 ns

- PDP: 62%, AP: 0.13%, DCR: 2.6 cps/µm<sup>2</sup>

- Amenable to 3D back-side illumination integration

- Potential for lower power consumption & reduced area

Progress in CMOS SPADs and digital SiPMs for fast timing applications

#### **EPFL Summary & Conclusions**

Blueberry 3D-stacked FSI MD-SiPM:

- Experiments on dedicated test structures

- TDC:

- LSB = 15ps

- DNL = [-1;2.57] LSB

- INL = [-10;5.76] LSB (<u>uncalibrated</u>)

- P<sub>peak</sub>= ~1.4 mW/TDC

- P<sub>tot</sub>= ~130mW (expected)

- Preliminary results on the whole structure were shown

- Demonstrated basic functionality of the chip

- DCR over temperature

More comprehensive testing is ongoing

# EPFL Acknowledgments & Sources FNSNE KS T-Micro

- Sub-10 ps FWHM SPADs: Francesco Gramuglia, Ming-Lo Wu, Myung-Jae Lee, Claudio Bruschini, Edoardo Charbon

- JSTQE(28) 2021, Frontiers in Physics(10) 2022

- 3D-stacked digital SiPM ("Blueberry"): Francesco Gramuglia, Andrada Muntean, Carlo Alberto Fenoglio, Esteban Venialgo, Myung-Jae Lee, Scott Lindner, Makoto Motoyoshi, Andrei Ardelean, Claudio Bruschini, Edoardo Charbon

- NSS-MIC 2021, IISW 2021

- MIP detection: Francesco Gramuglia, Emanuele Ripiccini, Carlo Alberto Fenoglio, Ming-Lo Wu, Lorenzo Paolozzi, Claudio Bruschini, Edoardo Charbon

- Frontiers in Physics(10) 2022