Thèse nº 9117

## EPFL

#### DESIGN AND MANAGEMENT OF THREE-DIMENSIONAL MULTI-PROCESSOR SYSTEMS-ON-CHIP WITH INTEGRATED FLOW CELL ARRAYS

Présentée le 2 décembre 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire des systèmes embarqués Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

#### Halima NAJIBI

Acceptée sur proposition du jury

Prof. A. P. Burg, président du jury Prof. D. Atienza Alonso, directeur de thèse Dr S. Nassif, rapporteur Prof. A. Coskun, rapporteuse Prof. K. Choo, rapporteur

École polytechnique fédérale de Lausanne

2022

Logic will get you from A to B. Imagination will take you everywhere. — Albert Einstein

To my family and loved ones...

## Acknowledgements

Before describing the scientific work accomplished during my Ph.D. at ESL, I wish to say a few words about some of the people that held my hand, both figuratively and literally, during this significant period of my life.

First and foremost, I should thank my thesis supervisor Professor David Atienza for being a great mentor and role model and for giving me the opportunity to work in a friendly yet ambitious environment. By being supportive and invested in my progress, he inspired me never to give anything less than my best for my research. He never held back any constructive comments about my work or failed to assist me when I needed it. He created an exceptionally supportive and comfortable atmosphere in the workplace, and went above and beyond to plan events for us to relax and enjoy each other's company (even virtually during a global pandemic). David has been an exemplary supervisor for whom I will always be grateful.

Then, I would like to express my gratitude to the talented post-doctoral researchers who provided me with continuous support. Prof. Marina Zapater was my first supervisor when I joined the laboratory. Her assistance was instrumental for guiding me to choose the direction of my work. Given her experience in the field, she provided crucial advice in terms of technical work. She also was of tremendous help in publishing my research the right way and to the right community. Next, Dr. Alexandre Levisse has always been an inspiration for innovative thinking, optimism, and enthusiasm. He shared many insightful tips based on his experience as a Ph.D., which were particularly helpful during my first years. His assistance continued to be valuable throughout the entirety of my Ph.D., allowing me to enhance the quality of my work. Finally, Dr. Giovanni Ansaloni joined in during the second half of my Ph.D. but quickly became a real asset to my research. He is friendly, encouraging, and always available to brainstorm and develop new ideas. It has always felt comforting to work with a brilliant, highly motivated, and collaborative researcher like him, always enjoying the work at hand.

I am also grateful for the help of other post-doctoral researchers in the lab (in particular Dr. Miguel Peon and Dr. Tomas Teijeiro) and technical staff (Rodolph, Michael, Christoph, and John) who assisted with certain tasks, and helped resolving a few "crises".

Next, I want to thank ESL's administrative assistant, Ms. Homeira Salimi, first of all for her friendship, then for all the help she provided with miscellaneous requests throughout the years. Moreover, I thank her for the exceptional job she has done organizing monthly birthday celebrations, sports and game activities, fancy dinners, and many other events for everyone in the lab to get together and have fun.

#### Acknowledgements

I have also had the chance to meet some wonderful people and develop many friendships inside ESL family. Perhaps the most significant one has been with Dr. Dionisije Sopic, who opened up to me from the first few weeks after arriving at the lab and quickly became the best friend with whom I shared precious moments inside and outside of work. I am also especially appreciative of the great friendships I had with Dr. Soumya Basu, Dr. Arman Iranfar, and Mr. Renato Zanetti. Moreover, I have spent memorable times with other friends and colleagues: Adriana, Ali, Andrew, Artem, Benoît, Elisabetta, Fabio (CH), Fabio (IT), Farnaz, Grégoire, Lara, Marco, Nacho, Saleh. Finally, I thank all the rest of the ESL family, and in particular the Android App Development course team, for forming a great work environment.

I'd like to thank my best EPFL friends outside ESL (Dr. Behnoush Attari and Dr. Yasmine Zakari) for being a constant presence during this whole period, doing activities like exercise, travel, dinners, drinks, and in general for sharing a special bond that will remain for life.

Finally, I am immensely grateful for my wonderful parents for their love and support of my goals and dreams, my brothers Ali and Youssef, and cousin Sarah for always being my most loyal confidants and my number one fan club, my uncle Taoufiq, aunt Margreth, and cousin Elias for embodying the comfort of a family far from home, and finally my loving partner Maxime for the countless words of encouragement and for facilitating life in moments of stress.

Lausanne, September 13, 2022

H. N.

### Abstract

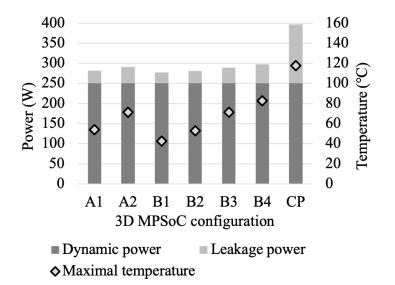

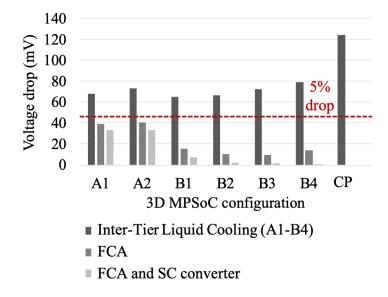

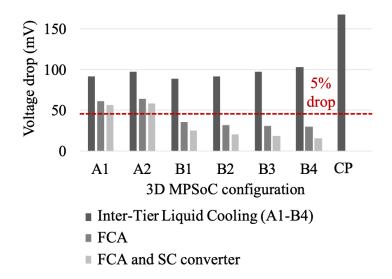

Three-Dimensional Multi-Processor Systems-on-Chip (3D MPSoCs) are promising solutions for highly intensive Artificial Intelligence (AI) and Big Data applications. They combine remarkably dense computation capabilities and massive communication bandwidths. However, due to their high density, 3D MPSoCs present heat dissipation, and power delivery challenges. Flow Cell Arrays (FCAs) have the potential to solve both issues. They consist of micro-channels etched in the Silicon substrate of stacked dies, filled with an electrolytic flow that absorbs the generated heat and produces power through electrochemical reactions. Hence, FCAs enable concurrent on-chip liquid cooling and electrochemical power generation in 3D MPSoCs. In this context, this thesis focuses on the system-level integration of FCAs as an effective cooling solution and power source for next-generation 3D MPSoCs. First, a comprehensive framework is proposed to model 3D MPSoCs with FCAs in fine grain and analyze their thermal and power performance. Simulations demonstrate temperature reductions of up to 40°C and voltage drop reductions of up to 90% when using FCAs, even for 3D MPSoCs fabricated using deeply-scaled CMOS technologies, which are characterized by extremely high power densities. Next, the thesis introduces design-time techniques to enhance the performance of FCAs. It advocates the use of Switched Capacitor (SC) converters as an interface between the channels and the power delivery grid. SCs enable FCAs to operate at their optimal voltage to maximize power generation, resulting in gains of up to 2x compared to direct connectivity to the power grid. Then, considering FCA's interdependent thermal and power generation capacities, several design configurations are explored, highlighting trade-offs and revealing opportunities to increase the power budget of 3D MPSoCs without violating design constraints. Finally, the thesis illustrates a novel strategy to manage the cooling and power generation capabilities of FCAs at run-time. Such an optimization strategy boosts the operating frequencies of dies, increasing the computing performance up to 24% while reducing coolant flow requirements.

**Keywords:** 3D integration, 3D multi-processor systems-on-chip (MPSoC), Flow cell arrays, Thermal performance, Power performance, Design-time management, Run-time management.

### Résumé

Les systèmes multiprocesseurs tri-dimensionnels sur une puce (MPSoCs 3D) sont des solutions prometteuses pour l'exécution de certaines applications modernes très intensives, telles que l'intelligence artificielle (IA) ou le traitement de données massives (Big Data). Ces plateformes combinent des capacités de calcul extrêmement denses et d'énormes largeurs de bande de communication entre les différents éléments. Cependant, les MPSoCs 3D souffrent de dissipation thermique difficile et d'alimentation complexe, en raison de leur énorme densité de puissance. Les Flow Cell Arrays (FCAs) ont le potentiel de résoudre ces deux problèmes. Elles consistent en des micro-canaux gravés dans le substrat en silicium des puces électroniques empilées. Elles sont remplies d'un flux électrolytique qui permet d'absorber la chaleur générée par l'activité des composantes. Ce flux produit également de l'énergie grâce à des réactions électrochimiques entre les électrolytes. Ainsi, les FCAs permettent le refroidissement et la production d'énergie dans les MPSoCs 3D.

Dans ce contexte-là, cette thèse se concentre sur l'intégration des FCAs au niveau système, en tant que solution efficace pour le refroidissement et comme source d'énergie additionnelle pour les MPSoCs 3D de la nouvelle génération. Tout d'abord, une démarche complète est proposée pour la modélisation granulaire des MPSoCs 3D avec des FCAs, ainsi que l'analyse de leur performance thermique et énergétique. Les simulations démontrent des réductions de température allant jusqu'à 40°C et des réductions de chute de tension allant jusqu'à 90% lors de l'utilisation des FCAs. Ceci reste valide même pour les MPSoCs 3D fabriqués en utilisant des technologies CMOS avancées, qui se caractérisent par des densités de puissance extrêmes. Ensuite, la thèse présente des techniques de conception en vue d'améliorer les performances des FCAs. Elle préconise l'utilisation de convertisseurs de tension comme interface entre les micro-canaux et le réseau de distribution d'énergie. Les convertisseurs permettent de faire fonctionner les FCAs à leur tension optimale, maximisant ainsi la production d'énergie. Cela entraîne d'importants gains, allant jusqu'à doubler l'énergie produite par rapport à une connectivité directe des FCAs au réseau électrique. Ensuite, en considérant l'interdépendance des capacités de refroidissement et de production d'énergie des FCAs, plusieurs configurations sont explorées. Celles-ci mettent en évidence les compromis existants et révèlent la possibilité d'augmenter la capacité énergétique des MPSoCs 3D tout en respectant les contraintes phy-

#### Résumé

siques. Enfin, la thèse illustre une nouvelle stratégie pour gérer les capacités de refroidissement et de production d'énergie des FCAs en cours d'exécution d'applications. Cette stratégie a pour objectif d'augmenter la vitesse de fonctionnement des composantes électroniques. Ainsi, elle permet d'intensifier la performance de calcul jusqu'à 25%, tout en réduisant le coût de refroidissement des FCAs.

**Mots-clés :** Intégration en 3D, systèmes multiprocesseurs 3D sur une puce, Technologie des Flow Cell Arrays, Performance thermique, Haute performance, Gestion de la puissance, Techniques de conception, Stratégies de gestion.

## Contents

| Acknowledgements             |                  |        |                                                                   |    |  |

|------------------------------|------------------|--------|-------------------------------------------------------------------|----|--|

| Abstract (English/Français)  |                  |        |                                                                   |    |  |

| 1                            | Intr             | oducti | on                                                                | 1  |  |

|                              | 1.1              | 3D int | tegration for high performance                                    | 1  |  |

|                              | 1.2              | 3D the | ermal dissipation challenges                                      | 4  |  |

|                              | 1.3              | 3D po  | wer delivery challenges                                           | 5  |  |

|                              | 1.4              |        | ibutions                                                          | 5  |  |

| 2                            | Bac              | kgrour | ıd                                                                | 7  |  |

|                              | 2.1              | Inter- | tier liquid cooling for 3D ICs                                    | 7  |  |

|                              | 2.2              | Simul  | ation of inter-tier liquid-cooled 3D ICs                          | 8  |  |

|                              | 2.3              | Flow o | cell arrays (FCAs)                                                | 9  |  |

|                              | 2.4              | Electr | o-thermal simulation of 3D ICs with integrated FCAs               | 11 |  |

| 3                            | <b>3D</b> ]      | MPSoC  | design with integrated FCAs                                       | 13 |  |

|                              | 3.1 Introduction |        |                                                                   |    |  |

|                              | 3.2              | Relate | ed work                                                           | 16 |  |

|                              |                  | 3.2.1  | 3D integration trends and challenges                              | 16 |  |

|                              |                  | 3.2.2  | Power delivery grid modeling                                      | 16 |  |

|                              |                  | 3.2.3  | Integrated FCAs                                                   | 17 |  |

| 3.3 Framework for modeling a |                  | Frame  | ework for modeling and analysis of 3D MPSoCs with integrated FCAs | 18 |  |

|                              |                  | 3.3.1  | Framework overview                                                | 18 |  |

|                              |                  | 3.3.2  | Flow cell electrical model                                        | 19 |  |

|                              |                  | 3.3.3  | 3D power delivery network modeling                                | 20 |  |

|                              | 3.4              | Target | t 3D MPSoC architecture                                           | 23 |  |

|                              |                  | 3.4.1  | 3D MPSoC and 3D PDN description                                   | 23 |  |

|                              |                  | 3.4.2  | 3D MPSoC utilization scenarios                                    | 26 |  |

|                              | 3.5              | 3D M   | PSoC performance evaluation                                       | 28 |  |

|                              |                  | 3.5.1  | 3D MPSoC configurations                                           | 28 |  |

|                              |                  | 3.5.2  | TSV placement exploration                                         | 30 |  |

|                              |                  | 3.5.3  | Experimental flow                                                 | 31 |  |

|                              |                  | 3.5.4  | Experimental results                                              | 32 |  |

|   |                   |                          | 3.5.4.1                              | Evaluation of 3D MPSoC temperature using FCAs            | 32              |  |  |

|---|-------------------|--------------------------|--------------------------------------|----------------------------------------------------------|-----------------|--|--|

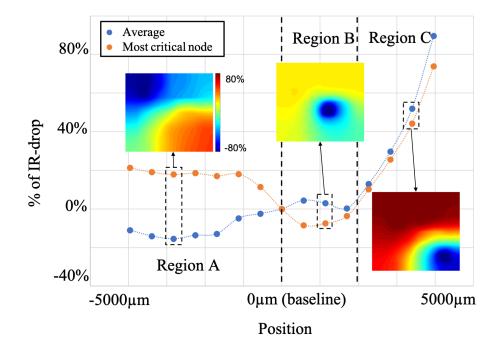

|   |                   |                          | 3.5.4.2                              | Evaluation of IR-drop reduction using FCAs               | 33              |  |  |

|   |                   |                          | 3.5.4.3                              | TSV placement evaluation                                 | 37              |  |  |

|   | 3.6               | Evalu                    | valuation of deeply-scaled 3D MPSoCs |                                                          |                 |  |  |

|   |                   | 3.6.1                    | 3D MPS                               | oC scaling                                               | 40              |  |  |

|   |                   |                          | 3.6.1.1                              | Architecture overview                                    | 40              |  |  |

|   |                   |                          | 3.6.1.2                              | Technology scaling methodology                           | 40              |  |  |

|   |                   | 3.6.2                    | Experin                              | nental setup                                             | 43              |  |  |

|   |                   |                          | 3.6.2.1                              | Experimental flow                                        | 43              |  |  |

|   |                   |                          | 3.6.2.2                              | 3D MPSoC cooling strategies                              | 43              |  |  |

|   |                   |                          | 3.6.2.3                              | Power network modeling at advanced technology nodes      | 44              |  |  |

|   |                   |                          | 3.6.2.4                              | PDN modeling and IR-drop analysis                        | 46              |  |  |

|   |                   | 3.6.3                    | Experin                              | nental results                                           | 47              |  |  |

|   |                   |                          | 3.6.3.1                              | FCA on-chip cooling capabilities                         | 47              |  |  |

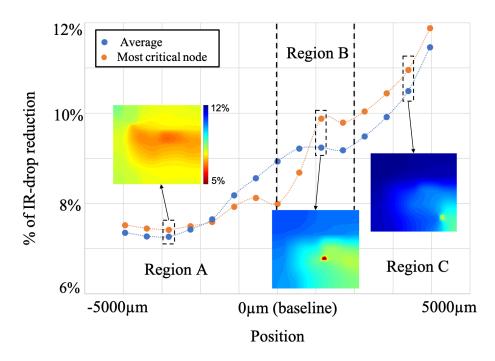

|   |                   |                          | 3.6.3.2                              | FCA IR-drop reduction capabilities                       | 48              |  |  |

|   | 3.7               | Concl                    | usion                                |                                                          | 51              |  |  |

| 4 | Dee               | i~~ +i~                  |                                      | noment strategies for 2D MDSeCowith ECAs                 | 50              |  |  |

| 4 | <b>Des</b><br>4.1 | -                        |                                      | gement strategies for 3D MPSoCs with FCAs                | <b>53</b><br>53 |  |  |

|   | 4.1               |                          |                                      |                                                          | 55<br>56        |  |  |

|   | 4.2               | 4.2.1                    |                                      | oCs trends and challenges                                | 56              |  |  |

|   |                   | 4.2.2                    |                                      | l management strategies for 3D MPSoCs                    | 56              |  |  |

|   |                   | 4.2.3                    |                                      | nanagement strategies for 3D MPSoCs                      | 57              |  |  |

|   |                   | 4.2.4                    |                                      | CoC design with integrated flow cell arrays              | 57              |  |  |

|   |                   | 4.2.5                    |                                      | converters for efficient power delivery                  | 59              |  |  |

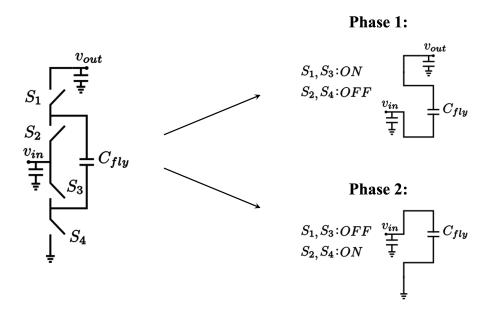

|   | 4.3               |                          | -                                    | ower generation with switched capacitor (SC) converters  | 60              |  |  |

|   | 110               | 4.3.1                    | -                                    | rerter design                                            | 60              |  |  |

|   |                   | 1.0.1                    |                                      | SC converter state-space model                           | 60              |  |  |

|   |                   |                          | 4.3.1.2                              | SC converter design space parameters                     | 63              |  |  |

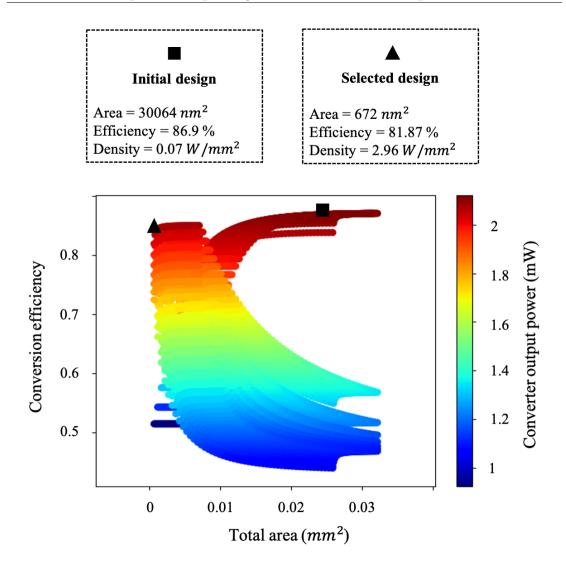

|   |                   |                          | 4.3.1.3                              | SC converter design exploration                          | 64              |  |  |

|   |                   | 4.3.2 Experimental setup |                                      |                                                          |                 |  |  |

|   |                   | 11012                    | 4.3.2.1                              | 3D MPSoC with FCAs and SC converters                     | 66<br>66        |  |  |

|   |                   |                          | 4.3.2.2                              | Processor utilisation scenarios                          | 67              |  |  |

|   |                   |                          | 4.3.2.3                              | Experimental flow                                        | 68              |  |  |

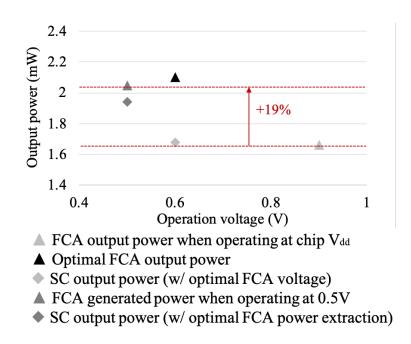

|   |                   |                          |                                      | nental results                                           | 68              |  |  |

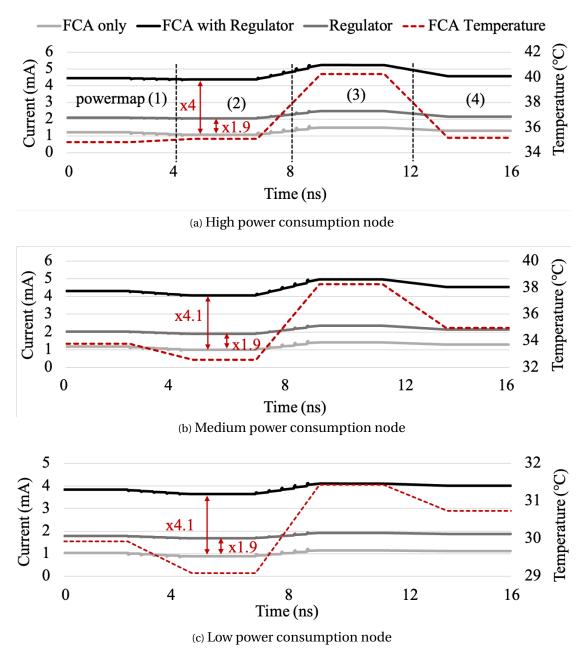

|   |                   | -                        |                                      | FCA power generation with SC converters                  | 68              |  |  |

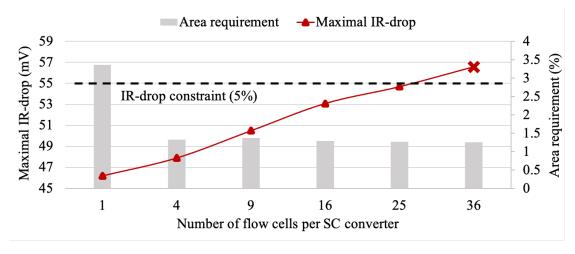

|   |                   |                          | 4.3.3.2                              | SC converter area optimization                           | 70              |  |  |

|   |                   |                          | 4.3.3.3                              | FCA power generation resource management                 | 71              |  |  |

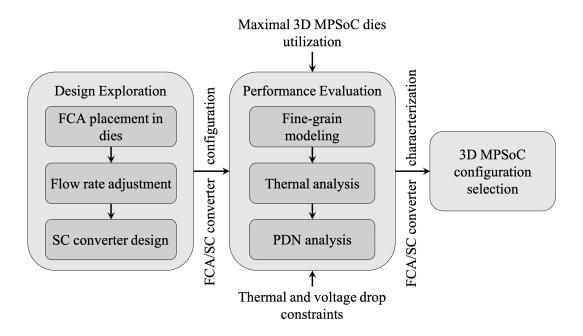

|   | 4.4               | Desig                    |                                      | naracterization of 3D MPSoCs with FCAs and SC converters | 73              |  |  |

|   |                   | -                        |                                      |                                                          | 74              |  |  |

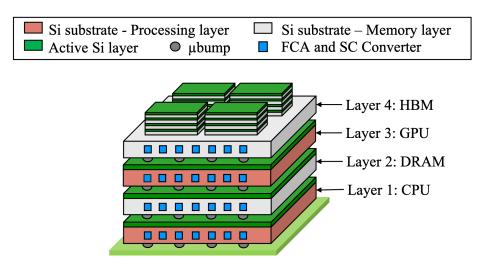

|   |                   |                          | 4.4.1.1                              | Target 3D MPSoC                                          | 74              |  |  |

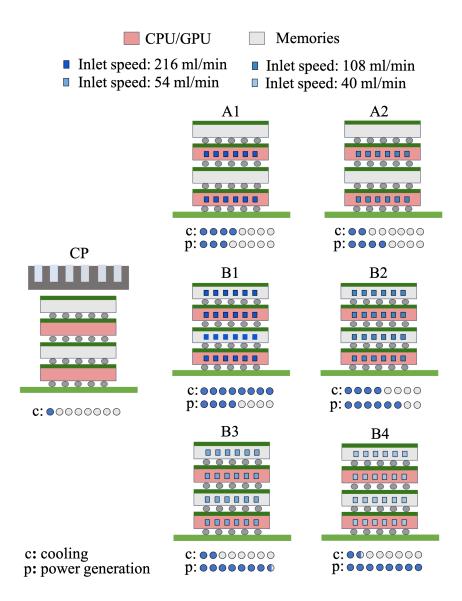

|   |                   |                          | 4.4.1.2                              | FCA placement and flow rate configuration                | 76              |  |  |

|   |                   |                          |                                      | r                                                        |                 |  |  |

|   |                                                                                                              | 4.4.1.3 SC converter configuration                             |     | 78  |

|---|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----|-----|

|   |                                                                                                              | 4.4.1.4 Experimental flow                                      |     | 79  |

|   |                                                                                                              | 4.4.2 Experimental results                                     |     | 81  |

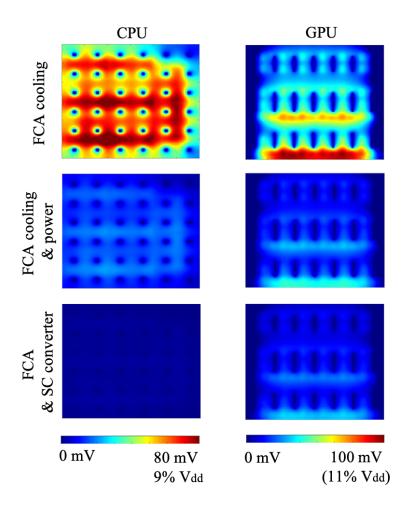

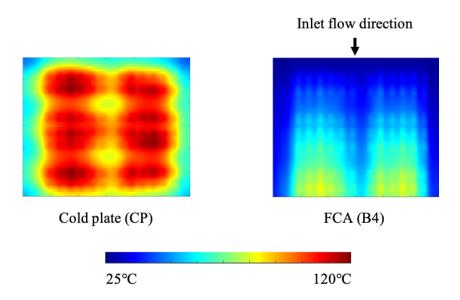

|   |                                                                                                              | 4.4.2.1 Temperature and total power consumption                |     | 81  |

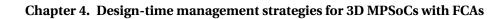

|   |                                                                                                              | 4.4.2.2 Voltage drop recovery                                  |     | 83  |

|   | 4.5                                                                                                          | 5 Conclusion                                                   |     | 85  |

| 5 |                                                                                                              | 87                                                             |     |     |

|   | <ul> <li><b>5 Run-time management strategies for 3D MPSoCs with FCAs</b></li> <li>5.1 Introduction</li></ul> |                                                                |     | 87  |

|   | 5.2                                                                                                          | 2 Related work                                                 |     | 89  |

|   |                                                                                                              | 5.2.1 3D MPSoC thermal and power challenges                    |     | 89  |

|   |                                                                                                              | 5.2.2 3D MPSoC run-time management strategies                  |     | 89  |

|   |                                                                                                              | 5.2.3 3D MPSoC with integrated FCAs                            |     | 90  |

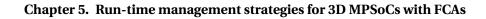

|   | 5.3                                                                                                          | 3 Target 3D MPSoC                                              |     | 92  |

|   |                                                                                                              | 5.3.1 Stack composition                                        |     | 92  |

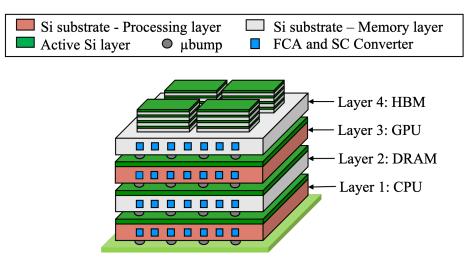

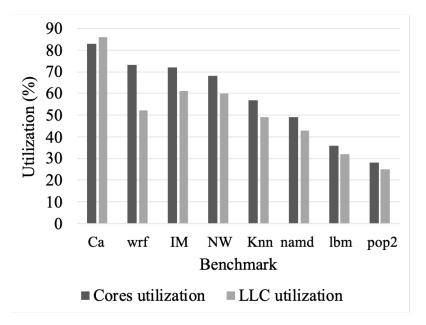

|   |                                                                                                              | 5.3.2 Target workloads                                         |     | 93  |

|   | 5.4                                                                                                          | Thermal and power-aware 3D MPSoC frequency optimization .      |     | 97  |

|   |                                                                                                              | 5.4.1 Offline frequency optimization                           |     | 97  |

|   |                                                                                                              | 5.4.2 Online frequency control                                 |     | 102 |

|   |                                                                                                              | 5.4.3 Experimental results on target 3D MPSoC                  |     | 104 |

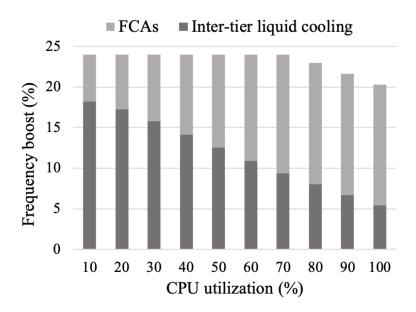

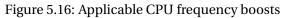

|   |                                                                                                              | 5.4.3.1 Frequency boosts                                       |     | 104 |

|   |                                                                                                              | 5.4.3.2 Workload speedups                                      |     | 105 |

|   | 5.5                                                                                                          | 5 Thermal and power-aware flow rate and frequency co-optimizat | ion | 110 |

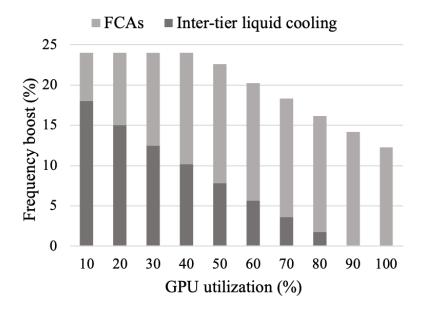

|   |                                                                                                              | 5.5.1 Offline frequency and flow rate optimization             |     | 110 |

|   |                                                                                                              | 5.5.2 Online frequency and flow rate control                   |     | 112 |

|   |                                                                                                              | 5.5.3 Experimental results on target 3D MPSoC                  |     | 113 |

|   |                                                                                                              | 5.5.3.1 Optimal flow rates and frequency boosts                |     | 113 |

|   |                                                                                                              | 5.5.3.2 Workload speedups                                      |     | 115 |

|   |                                                                                                              | 5.5.3.3 Cooling energy savings                                 |     |     |

|   | 5.6                                                                                                          | 6 Comparison with other DTM strategies                         |     | 117 |

|   | 5.7                                                                                                          | <sup>7</sup> Conclusion                                        |     | 118 |

| 6 | Con                                                                                                          | onclusion                                                      |     | 119 |

|   | 6.1                                                                                                          | Summary                                                        |     | 119 |

|   | 6.2                                                                                                          |                                                                |     | 121 |

|   |                                                                                                              | 6.2.1 3D MPSoC architecture design with FCAs                   |     |     |

|   |                                                                                                              | 6.2.2 Workload optimization on 3D MPSoCs with FCAs             |     | 122 |

|   |                                                                                                              | 6.2.3 3D MPSoC thermal and power management with FCAs .        |     | 122 |

|   |                                                                                                              | 6.2.4 FCA design for high-performance 3D MPSoCs                |     | 123 |

#### Bibliography

Contents

| List of Figures  | 135 |

|------------------|-----|

| List of Tables   | 138 |

| Curriculum Vitae | 141 |

## Introduction

This thesis considers three-dimensional multi-processor systems-on-chip (3D MPSoCs) as an effective solution to the increasing demand for high-speed and high-density computing due to their numerous advantages compared to two-dimensional (2D) systems. 3D MPSoCs employ 3D integration techniques to stack multiple IC components and construct compact, powerful, and efficient computational platforms. This introductory section presents the fundamentals of 3D integration and the motivations behind adopting this technology when targeting high-performance systems that respond to the demands of modern applications. Then, this section describes the primary challenges constraining the design of high-power 3D systems, namely the intense heat generation and complex power delivery. Finally, the section introduces the main contributions of this thesis, which consist of proposing solutions to address these challenges and enable a reliable implementation of high-performance 3D MPSoCs.

#### 1.1 3D integration for high performance

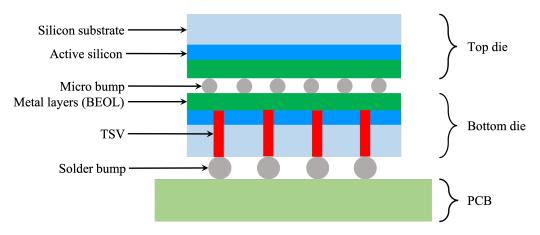

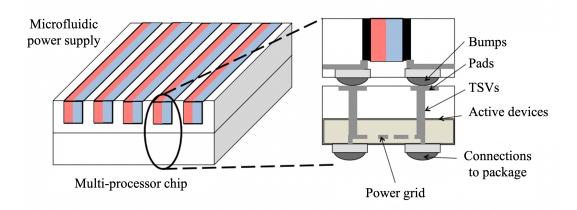

Figure 1.1: 3D integration of ICs using TSV and microbump technology

Figure 1.2: Bonding technologies for 3D integration [3]

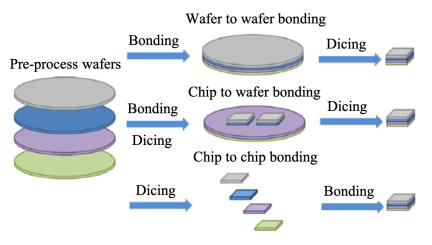

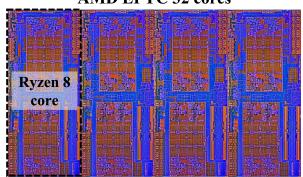

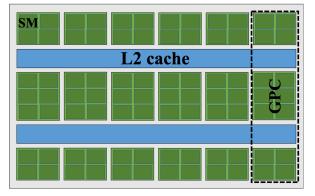

Over the last decades, significant advances in lithography and device technology have continuously increased the performance and efficiency of microelectronic systems in response to the needs of customers and applications. In particular, the semiconductor industry development has long been dominated by transistor shrinking to increase computing density and reduce IC fabrication costs. In recent years, however, three-dimensional (3D) integration based on through-silicon-vias (TSV) [1] has become a well-accepted and promising approach achieving compact IC systems, overcoming the performance bottleneck related to the lack of interconnect scaling [2]. 3D integration consists of constructing a system with multiple component dies fabricated using conventional processes, stacked on top of each other, and connected through TSVs and microbumps, as illustrated in Figure 1.1. It is possible, for instance, to bond entire wafers and then dice them into separate 3D ICs, or stack individual dies [3] (shown in Figure 1.2). Moreover, many combinations are feasible for post-back-end-of-line die-stacking. In a face-to-face configuration, the front-end electronics of two chips are directly connected through microbumps (similarly to Figure 1.1). In a back-to-back configuration, the back ends (silicon substrate) of two dies are connected using TSVs and microbumps. Finally, in a face-to-back configuration, the front end of a die is connected to the back end of a second die through TSVs and microbumps.

A critical challenge in IC system design comes from signal propagation delays and power losses, mainly determined by wiring lengths, resistances, and capacitances. These delays are exacerbated by the increasing distances between components in modern System-on-Chips (SoCs). Therefore, 3D integration with TSVs is an effective solution to overcome this challenge by providing vertical links for communication and power delivery, hence improving system performance without increasing power consumption [1]. In addition, 3D integration significantly reduces the area demand of multi-component SoCs and augments their computing density [4]. Finally, 3D integration is recognized as a key enabler of heterogeneous IC systems, offering the opportunity to compactly integrate dies fabricated with different architectures and CMOS technologies [2].

Many semiconductor technology suppliers and research organizations have developed full 3D integration processes using TSV technology, demonstrating their manufacturability and reliability. In fact, different 3D integrated ICs have been conceptualized and/or manufactured. They can be categorized as follows:

- **Memory-on-memory architectures** are perhaps the most representative application of 3D integration. 3D-stacked DRAM structures have become commercially available, providing exceptionally high bandwidths. As an example, the low-power Hybrid Memory Cube (HMC) [5], developed by Micron, is a 3-D-stacked DRAM with one logic layer and multiple DRAM layers providing abundant parallelism with hundreds of banks per device [2]. The layers are connected through thousands of TSVs. Then, with high-speed serial links, HMC achieves up to 320 GB/s of external bandwidth. The High-Bandwidth Memory (HBM) [6] is another example of a successful 3D memory architecture adopted by Samsung, AMD, and SK Hynix. HBM achieves a breakthrough bandwidth of over 256GB/s. Similar to HMC, it is an attractive solution for high-performance systems as it provides scalability of memory capacity and a small footprint.

- Memory-on-processor and processor-on-memory architectures are also gaining popularity in the IC design industry and research community because they fundamentally increase data access speed and computing performance in general. Hence, designers from Intel have proposed stacking large SRAM caches on a microprocessor, dramatically increasing on-die storage [7]. Their proposed architectures improve cache access time by up to 55% and reduce required off-die bandwidth by up to 66%, while simultaneously reducing power consumption. In addition, the authors of [8] developed a massively parallel processor with a stacked SRAM chip built using face-to-face 3D integration technology. Each core communicates with a dedicated block, enabling negligible data transfer delays. Alternatively, the authors of [9] stack embedded DRAM (eDRAM) lastlevel caches (LLC) on top of processing cores. Compared to SRAM cells, eDRAM cells have a smaller area and less leakage power. Finally, a 3D-stacked Logic-in-Memory (LiM) system has been introduced by the authors of [10], integrating multiple DRAM layers with an application-specific accelerator for the data-intensive parts of applications. It can achieve up to two orders of magnitude power efficiency improvements compared to optimized FPGA, GPU, and CPU implementations.

- **Processor-on-processor architectures** have also been proposed as a promising system integration alternative because they reduce the power dissipation related to core-to-core communication. Researchers in [11] presented a 3D modular and scalable network-on-chip (NoC) architecture for telecommunication applications. The NoC is scalable to up to 4 processing layers communicating via 3D links achieving 7.4 GB/s data rate with reasonable energy consumption. In addition, engineers in [12] developed an architecture composed of six multi-core chiplets on an active interposer integrating on-chip power management, flexible communication support, and memory control. This architecture enables high-efficiency computing and over 50× faster execution of state-

of-the-art applications. Finally, Intel has introduced a 3D stacking technology, called Foveros [13], which enables logic-on-logic integration of IP blocks through low-impact connection paths. This technology provides tremendous flexibility and is compatible with their high manufacturing process. It opens the way for systems with heterogeneous high-performance and high-intensity processing elements.

This thesis thoroughly assesses the benefits and pitfalls of 3D integration by exploring different 3D stacks representing combinations of memory-on-memory, memory-on-processor, and processor-on-processor architectures. In particular, it considers the thermal and power-related challenges that such systems encounter (described in Sections 1.2 and 1.3). Then, the thesis proposes different design and management solutions to overcome these challenges, using integrated microfluidic channels for combined cooling and power generation in 3D IC systems (introduced in Section 2.3).

#### 1.2 3D thermal dissipation challenges

Heat dissipation is a significant challenge in 3D IC design. As more devices are packed into a smaller area, the power density drastically increases [14], therefore generating an extremely high heat flux [15]. In addition, the dies in a TSV-based 3D stack are thinned, which causes their thermal resistance to decrease, creating severe conditions for on-chip hotspots. For instance, when analyzing the thermal behavior of 3D processors, the authors of [16] demonstrated that both memory-on-logic and logic-on-logic topologies incur a temperature rise of up to 11°C compared to an equivalent 2D processor. This issue is exacerbated by the high number of stacked dies and the small gap between overlapping heat sources [15]. In particular, chips further away from the heat sink suffer from the highest temperatures.

Indeed, stacking multiple chips using TSVs and fine-pitch microbumps complicates heat dissipation during operation. For a conventional chip package, the thermal path from the active circuits to the heat sink is principally through the silicon substrate (heat spreader) and the thermal interface material. For a 3D stack, the back-end-of-line (BEOL), the microbump layers between dies, and the insulating materials used for bonding the dies are in the thermal path. These materials have much lower thermal conductivity [17] than silicon. For instance, the BEOL layers have an equivalent thermal conductivity of  $2.25\mu W/\mu mK$  versus  $150.9\mu W/\mu mK$ for silicon [18]. Hence, the heat generated by the bottom die in a 3D chip has to travel many layers of low conductivity before reaching a heat sink.

In this context, effective thermal management strategies and design guidelines are needed for the widespread use of 3D integration [15]. This thesis advocates the use of Flow Cell Array (FCA) technology as a candidate solution to solve the thermal dissipation issues of high-performance 3D stacks.

#### 1.3 3D power delivery challenges

The second major challenge that hinders the mainstream adoption of 3D integration technology is the complexity of power delivery. In particular, floorplanning and power/ground (P/G) network design play an essential role in the power efficiency of 3D ICs [19]. These two tasks, already critical for 2D ICs, are particularly challenging for 3D ICs. In fact, floorplanning needs to balance the needs of inter-tier communication efficiency against power density when placing components, especially given the limited thermal margins [20]. Then, the P/G network design must target the minimization of the voltage drops across the inter-die and on-die power lines (IR-drop), which produce worst-case operating conditions and have a negative impact on the performance of the circuits [21].

As power in 3D ICs is delivered from the bottom die to other dies through P/G TSVs, the floorplanning and power delivery network design must consider TSV insertion to reduce wire length overheads [20]. P/G TSV placement, in turn, is also impacted by the locations of the logic blocks and the inter-tier communication requirements, which can cause interference with P/G lines and signal TSVs. In addition, IR-drop in the dies is impacted by P/G TSV placement [22]. The farthest TSVs are from the core area, the more critical the IR-drop, particularly for highly-scaled CMOS technologies with small wire widths and higher resistances along power lines. Then, the increasing power density and temperature (hence leakage) of 3D ICs incur additional stress on the power delivery components, which must drive high amounts of current, further aggravating IR-drop.

Consequently, the floorplanning and P/G network design are exceptionally complex problems for 3D ICs that many researchers tackle by developing new physical design guidelines and tools specifically tailored for 3D circuits [20]. This thesis complements these efforts by proposing to use FCAs as an additional on-chip power source, alleviating the need for complex power delivery network structures.

#### 1.4 Contributions

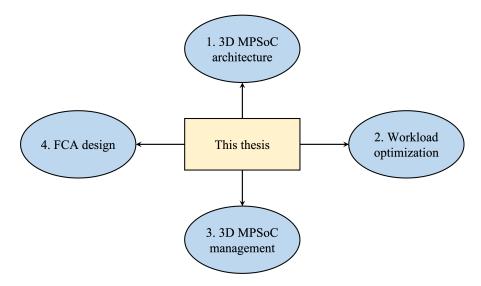

This thesis advocates for the design of heterogeneous high-performance 3D multi-processor systems-on-chip (3D MPSoCs) that achieve high-density and high-speed computing capabilities for next-generation applications. Considering the highly challenging thermal and power aspects attributed to such systems (described in Sections 1.2 and 1.3), it proposes to use a novel technology called Flow Cell Arrays (FCAs; introduced in Section 2.3) to enhance heat dissipation and recover losses in the power delivery circuitry. This technology combines intertier microfluidic cooling (described in Section 2.1) and on-chip power generation (described in Section 2.3) to efficiently address the previous challenges.

After introducing the inter-tier cooling and power generation technologies (Chapter 2), this thesis proposes a comprehensive system-level design and analysis methodology for high-performance 3D systems with integrated FCAs. Then, it presents design and run-time strate-

#### **Chapter 1. Introduction**

gies to maximize the benefits of FCAs and enhance the power performance of 3D stacked dies in general. In summary, the contributions are as follows:

- Chapter 3 introduces a novel thermal-aware 3D power delivery network modeling and analysis framework for 3D MPSoCs with integrated FCAs. This framework builds a granular model of the 3D MPSoC power network, including FCAs as an additional temperature-dependent power source. This model serves to quantitatively assess the benefits of FCAs on power delivery. It can be used in early design stages to ensure specific power and performance requirements, explore different design space configurations, and predict the performance of FCAs as CMOS technology scales down to nanometric sizes.

- Then, Chapter 4 propose design-time strategies and guidelines to maximize the efficiency of FCAs when integrated into high-performance 3D MPSoCs. First, inserting voltage regulators between the flow cells and power delivery lines permits to operate FCAs optimally, enhancing their power generation capacity. Then, the design space exploration of the different FCA-related parameters unveils the existing trade-offs between cooling and power generation. It also showcases the opportunities to efficiently manage the power performance of 3D MPSoCs, leveraging FCA capabilities in the most advantageous way.

- Next, Chapter 5 introduces a thermal and power-aware run-time performance management strategy for 3D MPSoCs, harnessing the leakage reduction and power supply potential of FCAs. Hence, depending on 3D stack architecture and level of utilization, the operating frequencies of dies are dynamically boosted while remaining within safe temperature, voltage, and timing margins. The run-time strategy also targets the optimization of the electrolytic flow rate settings, involving the inter-dependent cooling and power generation capabilities. Thus, the optimal frequency operation conditions are guaranteed while reducing the FCA cooling cost. This strategy enables considerable execution speedups of benchmarks targetting high-performance 3D MPSoCs.

- Finally, Chapter 6 concludes the thesis by highlighting the impact of its findings in the design and management of high-performance 3D MPSoCs. The chapter also discusses other 3D MPSoC and FCA design challenges that were exposed in the different chapters. These challenges can be tackled in a future work, complementing the work in this thesis to provide a comprehensive guideline for designing next-generation 3D MPSoCs.

## 2 Background

#### 2.1 Inter-tier liquid cooling for 3D ICs

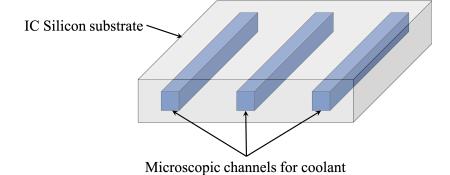

Figure 2.1: Microchannel-based inter-tier liquid cooling

3D ICs are characterized by unprecedented power densities, leading to exceptionally high heat generation that restricts performance. Traditional cooling techniques such as fan-based cooling or cold-plate-based liquid cooling can sometimes be insufficient to dissipate the high amount of heat produced by 3D ICs, particularly when increasing the number of stacked dies. Instead, liquid cooling using inter-tier microchannel heat sinks is now considered one of the most promising solutions to keep the temperature of 3D ICs under control. The idea of scaling liquid-based heat-exchange technology to microscopic dimensions was introduced 40 years ago as a potential enabler of high circuit power densities [23]. The technology involves etching miniaturized channels directly in the Silicon substrate of dies (Figure 2.1), where a liquid coolant (commonly water) is injected using a pump to absorb the generated heat via convection. By directly attaching microchannels to dies, the intermediate thermal resistances between the heaters and the heat sinks are significantly reduced, hence attaining heat removal capabilities as high as  $800W/cm^2$ .

#### Chapter 2. Background

In more recent years, inter-tier liquid cooling technology has regained popularity, and it is now an active area of research. In fact, extensive studies are performed to validate the existing theory on heat transfer and to set benchmarks for the fabrication and testing of future 3D ICs with inter-layer liquid-cooling [24]. Several works also address the design and optimization of microchannels [25] [26] and the management of 3D ICs with inter-tier liquid cooling [27]. Other works address some of the challenges that this technology encounters. For instance, the authors of [28] explore different channel sizes and geometries to limit the thermal gradients along the channels and mitigate the resulting non-uniform heat distributions. Then, the authors of [29] propose to use other fluid compositions to improve the heat absorption capacity inside the microchannels (e.g., mixing water with nanoscale metals and metal oxides). Finally, the authors of [30] address the design of micropumps to achieve high flow rates, which directly impact the cooling capability of microchannel heat sinks.

Inter-tier microfluidic channels are more suitable for 3D stacks than other advanced cooling technologies. Indeed, even though liquid cooling using a cold plate [31] achieves high cooling capacity, it does not scale well when stacking multiple dies on top of each other. Similarly, cold plates that use thermoelectric (Peltier) cells [32] do not solve the problems related to the poor heat dissipation between 3D stacked IC layers. Finally, immersion cooling is only suitable for entire servers, limiting options to efficiently manage localized heat generation. In this regard, this thesis considers inter-tier liquid cooling as the primary solution to 3D thermal dissipation problems, provided by Flow Cell Array technology (introduced in Section 2.3).

#### 2.2 Simulation of inter-tier liquid-cooled 3D ICs

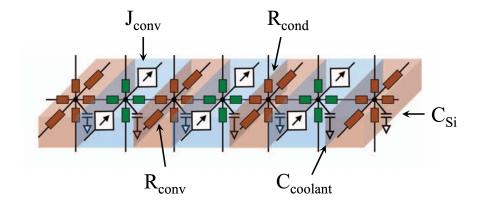

Figure 2.2: 3D-ICE model for a small section of a microchannel layer [33]

Fine-grained thermal simulations of 3D ICs are essential for measuring the effectiveness of inter-tier liquid cooling. To this end, the 3D Inter-layer Cooling Emulator (3D-ICE) is used throughout all the thermal experiments in this thesis to assess the performance of different 3D multi-processor architectures. 3D-ICE is ideally suited for the early-stage thermal-aware

design of 3D computing architectures with integrated microfluidic channels because it has a complexity similar to conventional compact resistive thermal models for air-cooled ICs. In comparison, other available IC thermal simulators, such as HotSpot [34] do not specifically support inter-tier liquid cooling. Then, commercially available fluid dynamics simulators such as Ansys CFX [35] have others of magnitude slower simulation times.

3D-ICE is a compact modeling and analysis tool for the thermal simulation of 3D ICs with inter-tier microchannel liquid cooling [33]. 3D-ICE uses compact transient thermal modeling (CTTM) to significantly reduce simulation time and memory consumption compared to other fine-grained simulators for liquid-cooled ICs (e.g., Ansys CFX). The CTTM is constructed by identifying the equivalent electrical representations of heat conduction in solids and convective heat transport in fluid flows, starting from the governing heat transfer equations. Thus, the temperature is represented as a voltage, the heat flow as an electric current, the heat conduction of materials as resistance (R), the heat storage as a capacitance (C), and the convective heat transfer of microchannels as a voltage-controlled current source ( $J_{conv}$ ). This way, the 3D IC is modeled as a mesh of cells connected through equivalent conductances between them (Figure 2.2), similarly to an electrical circuit. This model is then simulated to extract the temperature distribution across the chip.

An extensive evaluation has been performed using measurements from a real liquid-cooled 3D stack to validate the accuracy of 3D-ICE [33]. It is an open-source software in continuous development, with 3D-ICE 3.0 becoming available in 2022 [36].

## Inlet Anode electrode Fuel Outlet Oxidant Cathode electrode

#### 2.3 Flow cell arrays (FCAs)

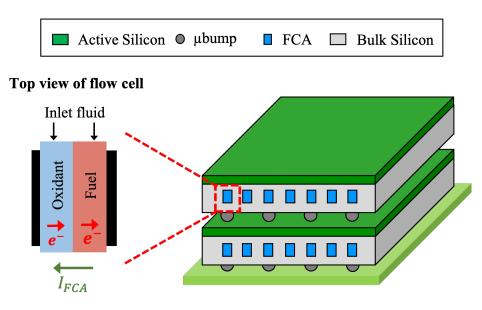

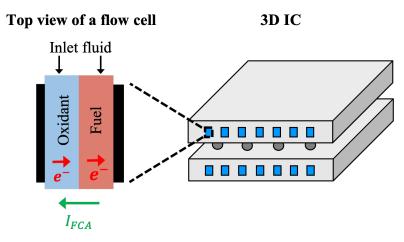

Figure 2.3: Planar view of a microfluidic channel with electrochemical flow and electrode contacts

Recently, a novel concept was proposed to extend inter-tier microchannel cooling with power generation capabilities [37]. This new technology replaces the non-conductive coolant (e.g., water) inside the microchannels with a solution containing electrochemical reactants responsible for power generation. At the same time, the fluid flow dissipates the heat generated by

Figure 2.4: Architecture of multi-core processor with microfluidic power supply and cooling, as proposed in [37]

the encompassing chip. Therefore, both power supply and coolant are delivered through the same medium. This technology is referred to as microfluidic Flow Cell Array (FCA), and it has the potential to solve the challenges related to 3D IC design and disruptively improve the achievable power performance.

FCA technology uses a reduction-oxidation (redox) flow cell structure where two separate fluids flow inside a single microchannel in a co-laminar fashion, as illustrated in Figure 2.3. These two fluids are referred to as fuel (or reductant) and oxidant. The fuel contains chemical elements that transfer electrons to an electrode (anode in Figure 2.3), and the oxidant contains elements that receive electrons from another electrode (cathode in Figure 2.3). At each electrode, the corresponding redox species convert from an oxidized form (Ox) to a reduced (Red) form via the following electrochemical reaction (where n is the number of exchanged electrons):

$$Ox + n.e^- \rightleftharpoons Red$$

Hence, the electrolytes are responsible for storing energy, and the continuous redox flow provides a steady energy supply. In addition, the microscopic dimensions of channels result in a sufficiently small Reynolds number, enabling a co-laminar flow of the two electrolytic streams without convective mixing [38]. Therefore, there is no need for a membrane separating them and complicating the fabrication process. Different chemical compositions can be used for power generation inside flow cells, such as vanadium [39], polysulfide bromide [40], and iron redox [41]. In this thesis, vanadium redox is selected. This redox structure is the most commercially available and is commonly used in batteries. Furthermore, vanadium redox presents advantages over other chemistries: they are stable, achieve high concentrations, have negligible cross-contamination rates, are low cost, and most importantly, match the voltage and temperature window of high-performance CMOS systems [42].

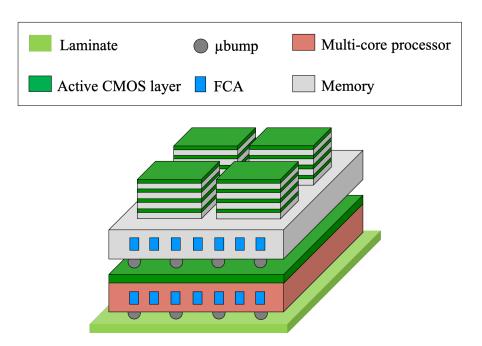

The authors of [37] have proposed and evaluated the concept of a multi-processor 3D architecture with a vanadium-based microfluidic flow cell array, illustrated in Figure 2.4, where the fuel cells supply their generated power to nearby active circuits through TSVs and microbumps. The authors implemented analytical and numerical models of the fuel cells taking into account several design parameters such as channel dimensions, flow rate, and inlet temperature. Their results demonstrated the possibility of fully supplying the memory subsystem of a high-performance processor while efficiently cooling the whole chip. Alternatively, this thesis proposes to deploy FCA technology to solve the power dissipation problems in entire high-performance dies, including the parts with the highest power densities that suffer from the most critical voltage drops. This way, FCAs can increase the power performance across the chip while avoiding resistive losses related to transporting their power to specific loading areas (e.g., memories). Compared to other novel power delivery technologies, such as backside interconnect [22], FCA power can locally supply the gates without extra wiring. Moreover, this technology is not limited to face-to-face bonded 3D-ICs. Finally, it can scale with the number of stacked dies without requiring more TSVs to deliver their power, otherwise limiting die-to-die communication.

#### 2.4 Electro-thermal simulation of 3D ICs with integrated FCAs

Detailed simulation of FCA power generation capabilities is necessary to understand the practical impact of integrating this technology as an additional power supply for 3D ICs. Thus, this thesis uses a novel tool called PowerCool to develop a compact thermal-aware electrical model of FCAs (Chapter 3). This model is integrated into the global power network of dies to assess the electrical performance for different target systems and usage scenarios. As of this writing, PowerCool is the only available electro-thermal simulator specifically targeting microfluidic cells for on-chip cooling and power generation.

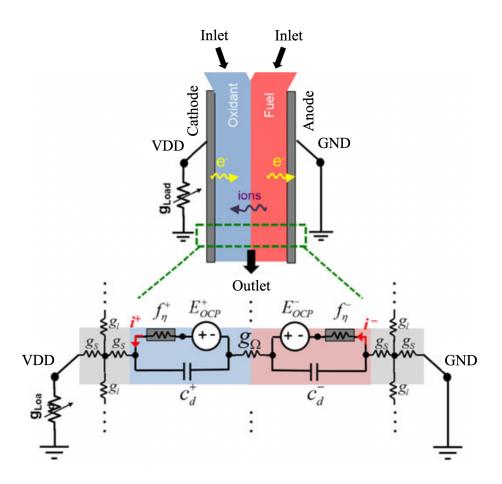

PowerCool is a mathematical model introduced by the authors of [44] to simulate the electrochemical behavior of the integrated power-generating microfluidic flow cell arrays in 3D ICs. PowerCool uses the fundamental characteristics of the electrochemical reactions in vanadium redox flow cells to establish a compact model for each small section of the microchannel, depicted in Figure 2.5. This model comprises various components representing the phenomena and electrical properties involved in microfluidic power generation. Hence, the open circuit potentials (OCP) generated by redox reactions are represented as voltage sources near the electrodes ( $E_{OCP}$ ). The potential losses due to the transport of ions near electrode surfaces are modeled as non-linear resistors ( $f_{\eta}$ ), which limit the amount of current that can be supplied by flow cells. Then, the interaction between the changing potentials of various sections along the flow cell and the electrodes is modeled by a distributed resistance network ( $g_s$ ,  $g_l$ ) connecting the flow cell sections. Next, a resistance between the fuel and oxidant half-cells exists, representing the flow of ions between them ( $g_{\Omega}$ ). Finally, the accumulation of ions near charged electrodes acts as a capacitance during the flow cell operation, represented as a parallel capacitor ( $c_d$ ). Given the circuit parameters described above, the flow cell circuit

Figure 2.5: PowerCool compact model for microfluidic flow cell, proposed in [43]

equations are defined and combined to construct the global differential equations for the entire microchannel. These equations are then solved using techniques for non-linear systems to compute the voltage and current levels between the electrodes [44].

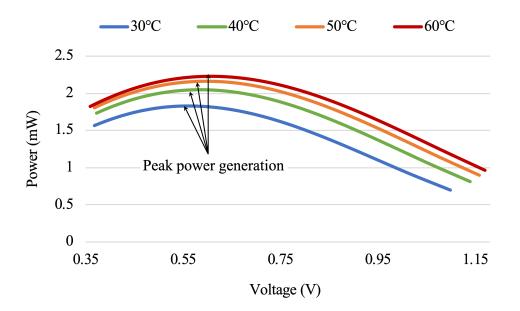

The accuracy of the PowerCool model was validated against fine-grained multiphysics simulations of individual flow cells and flow cell arrays using the COMSOL tool [45]. The model was also validated using measurement data from the literature. Then, it was applied to a multi-processor architecture with integrated microfluidic power generation and cooling, demonstrating the power generation capabilities of FCAs. In [43], 3D-ICE (Section 2.2) was incorporated in PowerCool also to evaluate the cooling capabilities of FCAs and analyze the effect of temperature on the electrochemical reactions of the redox flow. Hence, it was demonstrated that the generated power significantly increases with higher fluid temperatures, demonstrating FCA's capability to transform the heat generated by the chips into a valuable resource.

# **3** 3D MPSoC design with integrated FCAs

#### 3.1 Introduction

Over the years, the increasing demand for High-Performance Computing (HPC) has driven Integrated Circuit (IC) industry to increase logic density by scaling down CMOS transistors. Furthermore, significant innovations have been introduced and adopted to improve device performance [46][47]. Although aggressive technology scaling achieves high transistor densities and improves computing performance, system communication bandwidth remains limited as off-chip interconnect scaling lags behind.

In this context, 3D integration became a promising solution to overcome the interconnect scaling limitations of Multi-Processor Systems-on-Chip (MPSoCs) [48]. 3D integration enables tangible improvements in power performance and area [4]. It also enables designing heterogeneous systems in terms of technology and architecture, with massive communication bandwidths [49] alleviating the gap between computing and data access time.

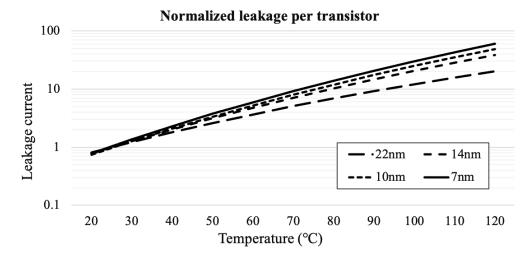

However, 3D MPSoC design faces two major challenges: heat extraction and power distribution/delivery [4], which exacerbate as CMOS technology scales down. The difficulty of *heat removal* fundamentally increases as heat traverses several layers of low thermal conductivity before reaching the environment (i.e., heat sink). Thus, dies reach high temperatures resulting in an exponential increase in leakage [50]. 3D MPSoC *power delivery challenges* derive from supply voltage decrease along power metal lines, before reaching the gates, due to the resistivity of the delivery network. This phenomenon, referred to as IR-drop, manifests with local  $V_{DD}$ drops that result in slower transitions of the affected gates and lead to timing violations [51]. Many techniques have been proposed to improve heat dissipation and minimize IR-drop in 3D MPSoCs, by increasing the number of thermal [14] and power and ground (P/G) TSVs [51], respectively. However, these techniques generally involve a high TSV area overhead, making their implementation impractical and costly.

Integrated Flow Cell Array (FCA) technology addresses the challenges above by providing combined on-chip liquid cooling and power generation in 3D MPSoCs [43]. FCAs consist of

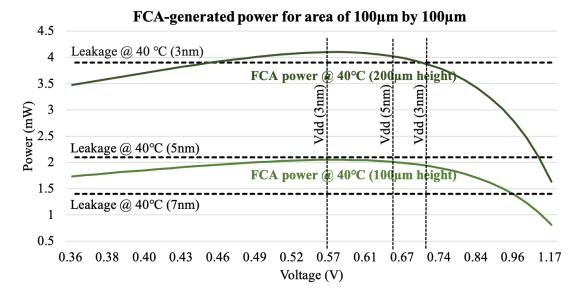

micro-channels filled with an electrolytic solution etched in the silicon substrates of dies. They extend inter-tier liquid cooling [25] with power generation, enabled by the electrochemical reactions between electrolytes. Their capabilities were experimentally validated in [43], showing that they can generate up to 3.6W per  $cm^2$  under optimal voltage and load conditions. However, previous analyses used an analytic model that did not cover important 3D MPSoC design aspects, such as the connectivity of the FCAs to 3D power delivery networks. This previous work also did not consider power generation variations between different flow cells with respect to temperature and voltage levels across the dies. Considering these aspects is important to accurately predict the effects of FCA integration on the power performance of 3D MPSoC.

Fulfilling the aforementioned requirement to predict FCA integration effects, this chapter proposes a novel thermal-aware 3D Power Delivery Network (PDN) modeling framework that analyzes the effects of connecting FCAs to 3D MPSoC power delivery (P/G) grids in detail. It can be used in early 3D MPSoC design stages to meet specific power and performance requirements. The framework uses real power maps to extract the load sinks, estimate the power grid densities of the dies, and calculate the FCA temperature maps using a fine-grained thermal analysis tool [33]. It then builds a fine-grained electrical model of the 3D P/G network and calculates the voltages across the dies. First, the proposed framework is used to assess the performance of a target system considering multiple configurations in terms of physical placement of dies, FCAs, and power TSVs. Then, the framework is deployed to predict the performance of FCAs as 3D MPSoC designers move towards deeply-scaled technologies with extreme power and thermal challenges. The summarized contributions of this chapter are as follows:

- The introduction of a fine-grained 3D P/G network model to quantify the effects of FCAs on 3D MPSoC power delivery. The model includes a compact electrical representation of FCAs and other power delivery components. Simulations of this model indicate that FCA technology outperforms other state-of-the-art power management methods. FCAs reduce the average IR-drop by up to 53% for dies with uniform power consumption and up to 30% for dies containing high power density regions (i.e., power hotspots). In addition, they do not require any additional TSV area.

- The analysis of the variation of FCA current generation along FCAs due to temperature and voltage gradients, using multiple real processor power traces. Simulations show that, while the average IR-drop reduction increases by 10% at the power hotspots, it remains 21% below the average value. Therefore, it is critical to have an accurate P/G delivery network modeling approach for 3D MPSoC design instead of qualitative profiling approaches.

- The introduction of an optimization algorithm using the proposed modeling methodology to find the best placement of P/G TSVs in 3D MPSoCs. The proposed algorithm ensures optimal FCA IR-drop reduction across dies. Moreover, it runs in under 4 min-

utes per 3D MPSoC sub-grid and per TSVs placement for a case study based on a high-performance processor, with 16 P/G sub-grids of 3362 nodes and 15 TSV placement options. These results prove the scalability of the optimization algorithm for large 3D MPSoCs.

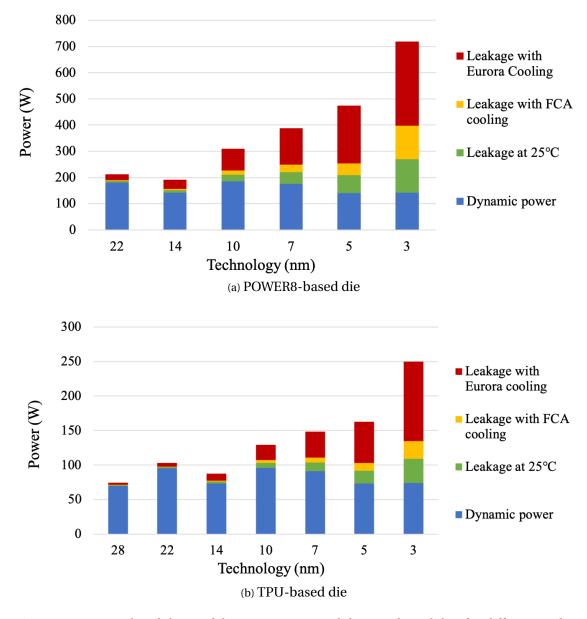

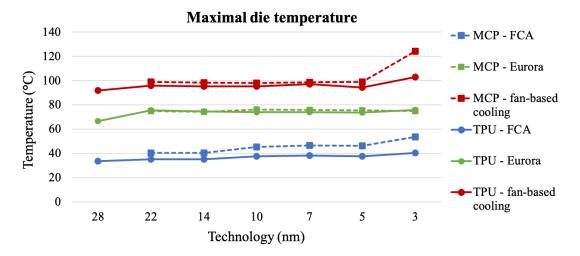

- The analysis of FCAs sustainability as 3D MPSoC dies are fabricated using deeply-scaled technologies. Their on-chip cooling and IR-drop reduction benefits are quantified when scaling a computing die down to 3*nm*. Using as a starting point power values of a 22*nm* multi-core processor (MCP) and 28*nm* Machine Learning (ML) accelerator, a novel methodology is proposed to estimate the leakage and dynamic power, at a constant area and operation frequency, following industry-reported [52][53][54][55] and predictive [46][47] scaling ground rules.

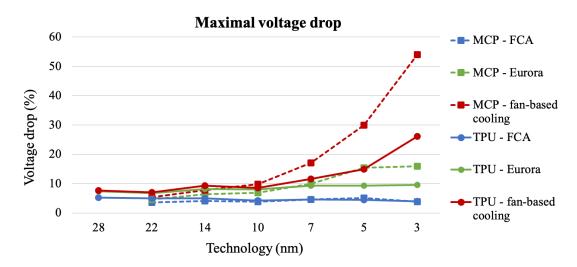

- The simulation of deeply-scaled 3D MPSoCs using the thermal-aware modeling and analysis framework, showing that FCAs can achieve 35°C lower temperature than offchip liquid cooling strategies. In addition, FCAs eliminate up to 12% IR-drop when scaling the 3D MPSoC computing die from the 22*nm* to the 3*nm* process, compared to a direct liquid cooling scenario.

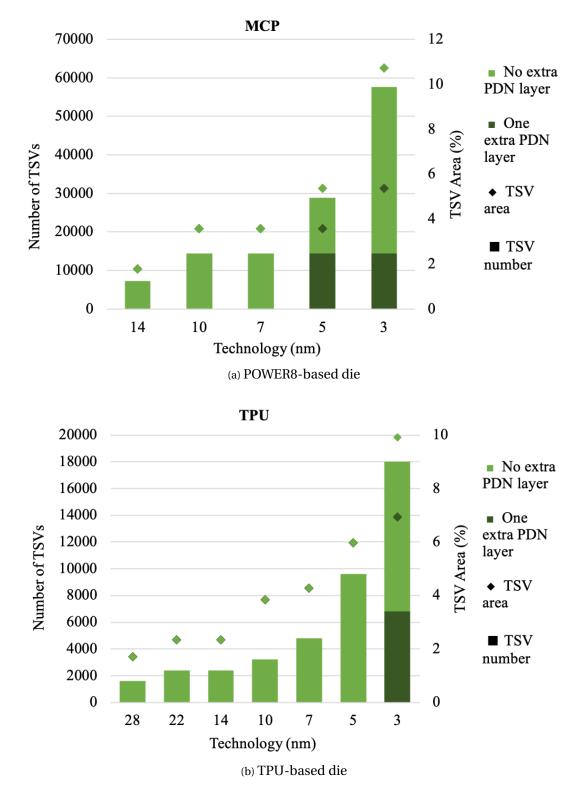

- The demonstration of the significant potential of FCAs for power and thermal management of 3D MPSoCs with advanced technologies. The results motivate the design of power-efficient next-generation 3D systems with FCAs. Such designs can save over 10% of the total area for power TSVs and up to two layers of metallization with respect to a state-of-the-art high-performance direct liquid cooling system [56][57].

The rest of the chapter is organized as follows. Section 3.2 summarizes the state-of-the-art of 3D integration, its challenges, and power delivery design and modeling techniques. It also provides an introduction to FCA technology. Then, Section 3.3 introduces the novel framework for modeling and analysis of 3D MPSoCs with integrated FCAs. The target 3D MPSoC used as an experimental vehicle is presented in Section 3.4. In section 3.5, the framework is used to evaluate the performance of FCAs, considering different 3D MPSoC configurations in terms of placement of dies and FCAs. The section also proposes a PDN optimization algorithm. The experimental results showcase the cooling and IR-drop reduction potential of FCAs. Next, Section 3.6 uses the proposed framework to analyze the scalability of FCA technology as the IC design industry moves towards ultra-scaled CMOS processes. It proves that FCAs remain an efficient solution for thermal and power management of next-generation 3D MPSoCs. Finally, Section 3.7 concludes the chapter.

#### 3.2 Related work

#### 3.2.1 3D integration trends and challenges

3D integration using TSV technology offers opportunities to increase the integration density of ICs, enable mixed technologies and architectures, and minimize the interconnect delays and power dissipation. 3D integration was successfully adopted in the memory industry with the High Bandwidth Memory (HBM) [6] and the Hybrid Memory Cube (HMC) [5]. Both achieve breakthrough bandwidths (over 256GB/s and 320GB/s, respectively) while consuming a lower energy-per-bit compared to 2D DRAMs. Following the emergence of 3D memories, efforts were directed toward memory-on-processor architectures to speed up memory-intensive applications and lower communication power consumption and delays [58][49]. However, these 3D MPSoCs face two significant challenges: heat extraction difficulty and voltage distribution complexity [20], particularly due to the non-uniformity of power consumption across chips.

In this context, methodologies were proposed to manage the thermal aspect of 3D MPSoCs in early floorplanning stages [59]. In particular, the insertion of thermal TSVs has been suggested to improve heat extraction in 3D MPSoCs [14]. Nonetheless, using thermal TSVs can have up to 47% total area overhead to reduce the maximal temperature of dies by 38%. Similarly, researchers proposed a technique to co-optimize the locations, sizes, and the number of P/G TSVs, as well as the floorplan of major 3D MPSoC blocks to prevent IR-drop constraints violations [51]. This method recovers up to 11.8% of IR-drop but uses a high number of TSVs (up to 200 TSVs for a grid of 300 nodes) of large diameter ( $20\mu$ m).

This chapter proposes accurately modeling FCAs and exploiting this technology to address the above challenges. Simulations indicate that FCAs achieve 42% better IR-drop reduction than state-of-the-art methods without additional power TSV requirements. In addition, FCAs improve the temperature of 3D MPSoC by 4% compared to traditional cooling methods.

#### 3.2.2 Power delivery grid modeling

Power delivery analysis is critical in the early design and floorplanning stages of high-performance MPSoCs. As interconnect dimensions shrink and the currents traversing them increase, IRdrop becomes critical [51]. Therefore, it is crucial to accurately model the P/G grid to ensure a correct chip operation. A typical P/G grid consists of intersecting horizontal and vertical metal lines dedicated to voltage delivery [60]. Then, the lines are interconnected with each other and then connected to the gates using vertical vias. Each element has specific electrical resistivity and dimensions, which allows to estimate the resistances between the nodes and the sources. This model is commonly used for P/G delivery network design and analysis [61] [62]. In this chapter, it is extended by integrating FCAs as additional power supply components.

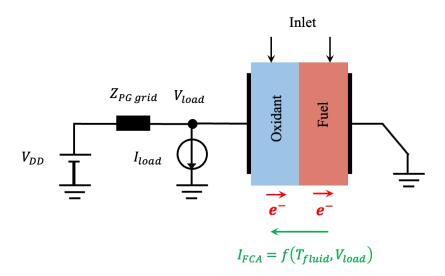

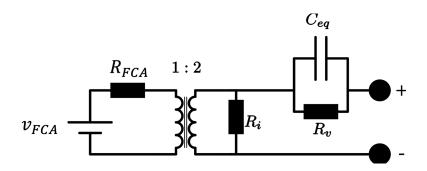

Figure 3.1: A single flow cell connected to the load and P/G grid of a 3D MPSoC die, as presented in [63]

#### 3.2.3 Integrated FCAs

FCA technology consists of inter-tier micro-channels placed in the silicon substrate of 3D MPSoC dies, where an electrolytic solution flows. Similarly to on-chip inter-layer liquid cooling [25], they absorb the heat generated in the chip. At the same time, a continuous and stable electrical current is generated when a load is inserted between FCA electrodes due to electrochemical reactions between the electrolytes (Figure 3.1). The rate of these reactions increases with temperature, hence generating an electric current. Thus, FCAs effectively transform heat into available power to partially supply logic gates. Regarding the fabrication costs of 3D MPSoCs with FCAs, industrial collaborators expect it to be marginally higher (<10%) than inter-layer cooling. As this technology already requires the additional etching and coating processes that micro-scale FCAs require, only the positioning of electrodes to channel walls is needed as an extra step [37][43].

Electro-thermal simulations of 3D MPSoCs with integrated FCAs can be performed using PowerCool [43]. It is a combination of the original PowerCool simulator [44], which enables compact electrochemical simulation of FCA power generation, and the 3D-ICE simulator [33], which analyzes the FCA cooling capabilities. The accuracies of PowerCool and 3D-ICE were validated against fine-grained physical models and actual measurements, respectively. The authors of [43] showed that FCAs could generate up to 3.6W per  $cm^2$ . Nonetheless, they considered optimal load and voltage conditions without examining the impact of connecting FCAs to 3D power delivery networks. Moreover, they did not study the current generation variations along FCAs due to voltage and temperature gradients. Hence, they missed evaluating the effects of power map non-uniformities. Thereby, this chapter accurately models 3D MPSoC P/G delivery networks with integrated FCAs and evaluates the effects of high-power density regions (i.e., power hotspots) on FCA IR-drop reduction capabilities.

#### 3.3 Framework for modeling and analysis of 3D MPSoCs with integrated FCAs

This section presents a modeling and analysis framework to quantitatively assess FCA benefits on 3D MPSoC thermal and power performance. Hence, the framework models the temperature-aware power delivery network in fine-grain. It then measures the effects of FCAs on the voltage drop across dies. The framework enables exploring different dies, FCAs, and TSV configurations, quantifying their thermal and voltage drop performance.

#### 3.3.1 Framework overview

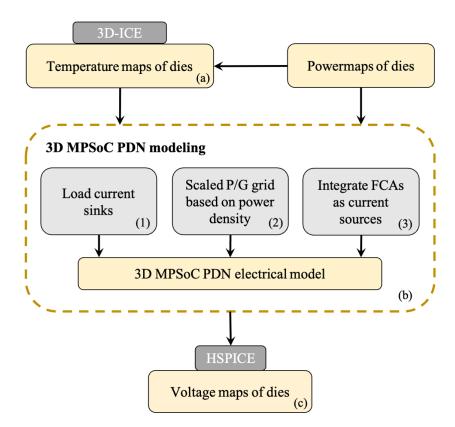

Figure 3.2: Thermal-aware modeling and analysis framework for 3D power delivery networks

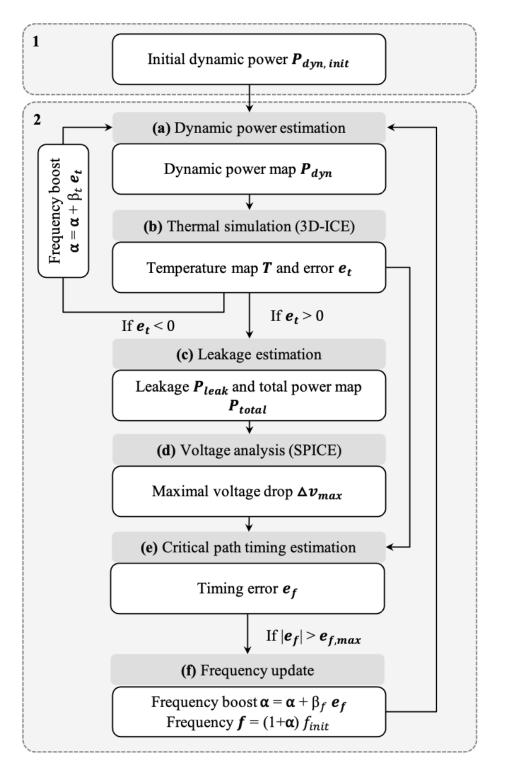

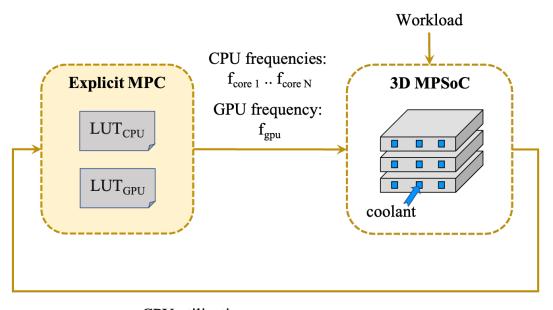

The framework comprehensively evaluates the power generation performance of FCAs, and analyzes the voltage delivery across dies. The different steps are summarized in Figure 3.2:

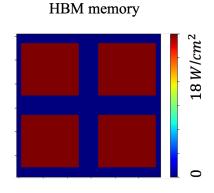

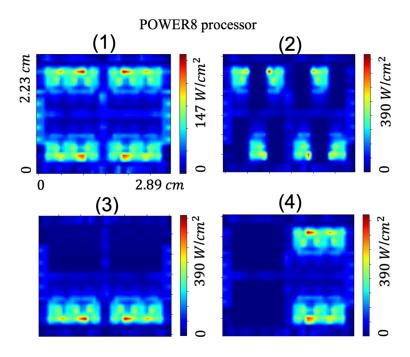

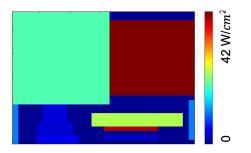

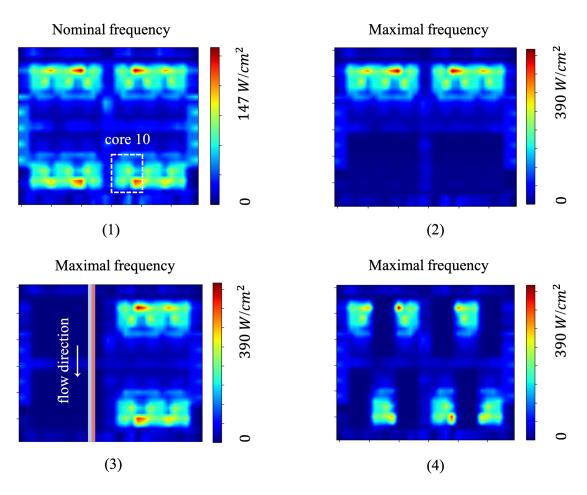

• The power distributions of dies (i.e., different power maps) are used to evaluate their thermal behavior (box (a) in Figure 3.2). Using the fine-grained thermal simulator 3D-ICE [33], the framework extracts the temperature maps of the different 3D MPSoC dies.

- The power maps and temperature maps of dies are used to build a fine-grain model of the power delivery network (box (b) in Figure 3.2). In particular, the current sinks are calculated using the power consumption distribution of dies (box (1) in Figure 3.2). Then, the P/G metal lines and TSVs are modeled as a mesh of resistances estimated based on their physical properties and the power densities at the nodes (box (2) in Figure 3.2). Finally, FCAs are included in the model as additional voltage and temperature-controlled current sources (box (3) in Figure 3.2). Due to their stability [43][64], FCAs are directly connected to the P/G grids.

- The fine-grain electrical model of the 3D power network is analyzed using HSPICE (box (c) in Figure 3.2). As a result, the framework extracts the voltage maps of stacked dies and assesses the effect of FCAs on IR-drop reduction across the 3D MPSoC.

The following sections 3.3.2 and 3.3.3 describe in detail the proposed modeling methodologies for FCAs and 3D PDNs, respectively.

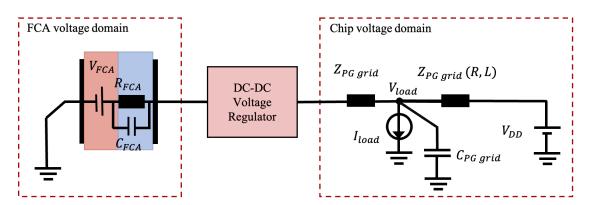

#### 3.3.2 Flow cell electrical model

The framework models each flow cell as a voltage and temperature-controlled current source. It then connects its electrodes to the nearby source  $(V_{DD})$  and ground  $(V_{GND})$  metal lines in the P/G grid. Hence, the voltage between the metal lines generates a continuous and stable current between flow cell electrodes. This current is directly supplied to the gates through the P/G grid.

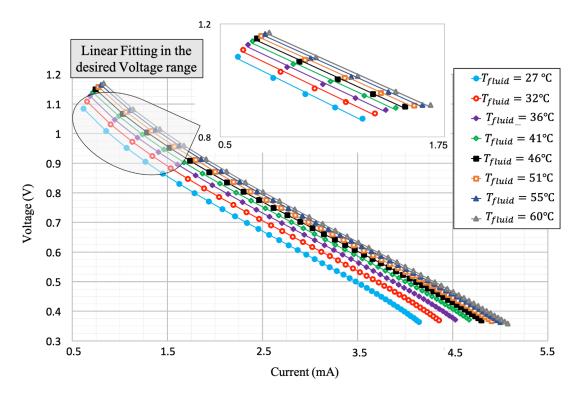

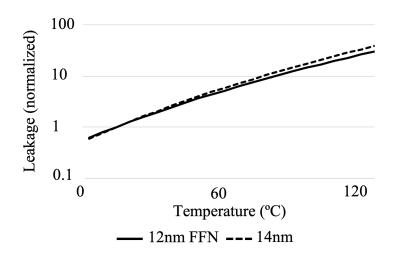

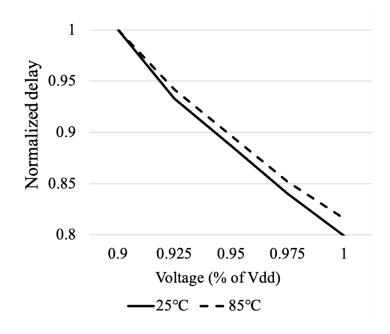

PowerCool [43] is used to assess the relationship linking the current and voltage between the flow cell electrodes (I-V curve). Moreover, this tool enables analyzing the effects of fluid temperature on FCA power/current generation. Figure 3.3 shows the I-V curve of a single flow cell of length  $200\mu m$ , for different fluid temperatures ranging from  $27^{\circ}$ C and  $60^{\circ}$ C. The selected length minimizes the temperature variation inside the flow cell (<  $0.5^{\circ}$ C) and the number of flow cells per channel (112 cells for the target 3D MPSoC presented in Section 3.4.1). The I-V curve is not linear in the complete analysis range but has a linear behavior around 1V, which is a typical  $V_{DD}$  value for sub-30nm technologies. Furthermore, the slope of the linear relationship in this range is independent of temperature. Instead, the temperature of the FCA fluid only affects the voltage/current offset of the I-V curve.

Following the above analysis using PowerCool, the flow cell at a position (i, j) is modeled using Equation (3.1).  $V_{FCA,i,j}$  and  $I_{FCA,i,j}$  are the voltage and current between the flow cell electrodes,  $R_{FCA}$  is the resistance of the flow cell and  $V_{offset}(T_{fluid,i,j})$  is the voltage offset corresponding to the fluid temperature  $T_{fluid,i,j}$  extracted from the temperature map:

$$V_{FCA,i,j} = V_{offset}(T_{fluid,i,j}) - R_{FCA}I_{FCA,i,j}$$

$$(3.1)$$

19

Figure 3.3: Current-voltage relationship (I-V curve) for a single 200µm-long flow cell

#### 3.3.3 3D power delivery network modeling

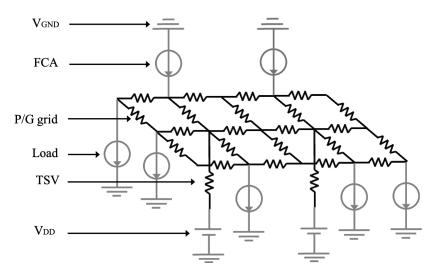

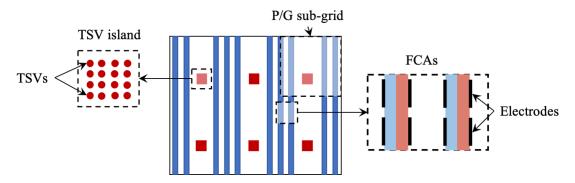

The 3D MPSoC power delivery network model includes different components: the TSVs delivering power from the PCB to the stacked dies, the individual 2D power grids of dies and the FCAs connecting to the PDN. In order to perform a fine-grain simulation of the 3D MPSoC power network, the layers of the stack are partitioned into nodes representing cells with uniform power-per-surface units. These nodes are interconnected horizontally via the equivalent resistances of the 2D P/G grids. Then, they are vertically connected to the PCB via the equivalent TSV resistances. Each FCA cell is connected to the node it supplies, representing the closeby area of the chip that it covers. Consequently, a power delivery network is constructed for each stack layer, as shown in Figure 3.4.

The different PDN elements are modeled as follows:

- Current sources represent the flow cells (Box (3) in Figure 3.2). The output current is governed by the voltage between the FCA electrodes and the temperature of the electrolytic liquid, corresponding to Equation 3.1 in Section 3.3.2.

- Current sources represent the loads of the dies. Their values are extracted from the power maps of dies and the operating voltages at the corresponding nodes (Box (1) in

Figure 3.4: Electrical model of a 3D power delivery network

Figure 3.2). Hence, the load current at a node with coordinates (i,j) is:

$$I_{(i,j)} = \frac{P_{(i,j)}}{V_{(i,j)}}$$

(3.2)

• TSV resistances, which are a function of their length  $L_{TSV}$ , radius  $r_{TSV}$ , and the copper resistivity  $\rho_{Cu}$  [51]:

$$R_{TSV} = \frac{\rho_{Cu} L_{TSV}}{\pi r_{TSV}^2} \tag{3.3}$$

with:

$$\begin{cases} \rho_{Cu}: \text{ Copper resistivity} \\ L_{TSV}: \text{ TSV length} \\ r_{TSV}: \text{ TSV radius} \end{cases}$$

• 2D grid resistances, which are calculated as the sum of the equivalent resistances of the wires in all metal layers dedicated to voltage delivery [61]. The full equivalent resistance of a path between two nodes  $N_1$  and  $N_2$  in the power network is obtained as follows:

$$R_{N_1 \to N_2} = \sum_{M_i} R_{M_i} \tag{3.4}$$

with:  $\begin{cases} M_i: \text{ metal layer dedicated to power delivery} \\ R_{M_i}: \text{ equivalent resistance of the wire in metal layer } M_i \end{cases}$

The resistance of a wire between two nodes in a metal layer  $M_i$  is computed as follows:

$$R_{M_i} = p_{usage} R_{sM_i} \frac{L_{wire}}{W_{wire}}$$

(3.5)

21

with:  $\begin{cases} p_{usage}: \text{ power grid usage} \\ W_{wire}: \text{ wire width} \\ R_{sM_i}: M_i \text{ sheet resistance} \\ L_{wire}: \text{ wire length} \end{cases}$

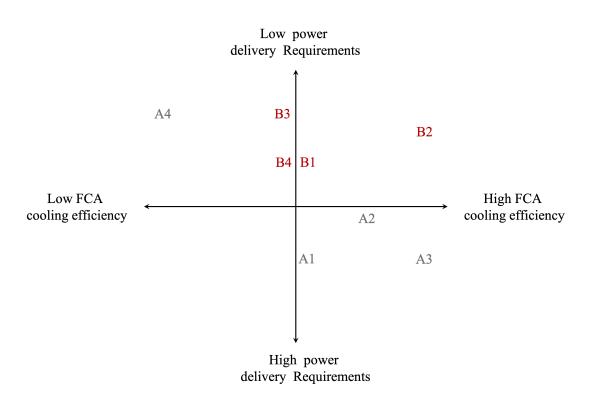

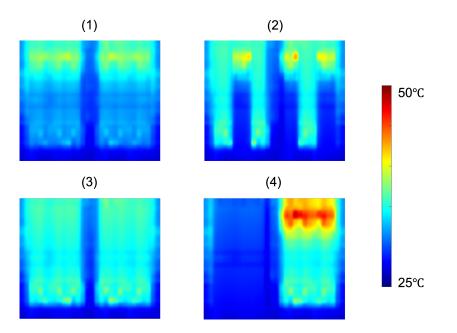

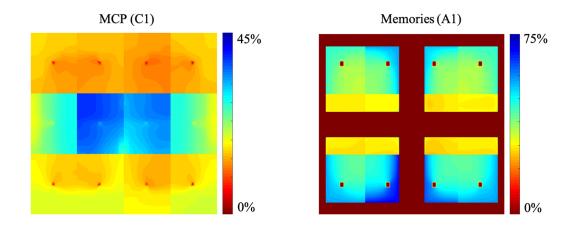

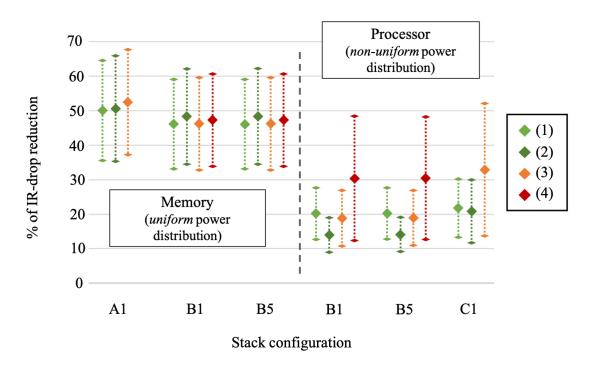

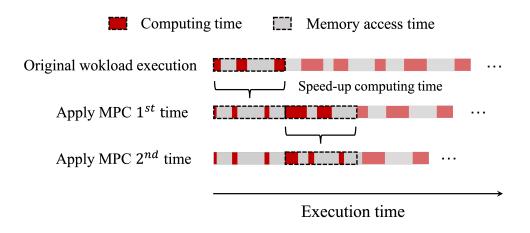

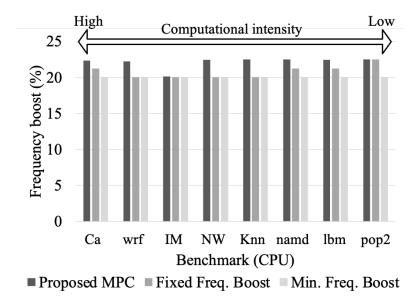

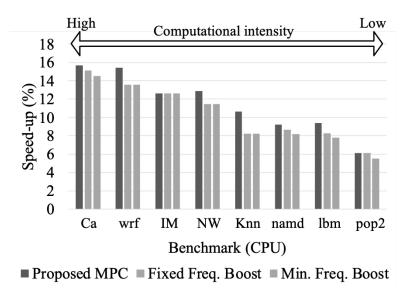

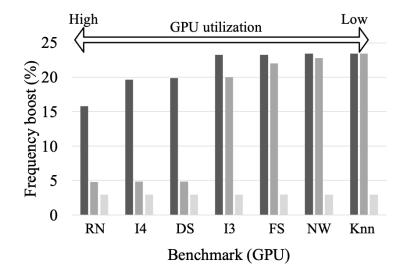

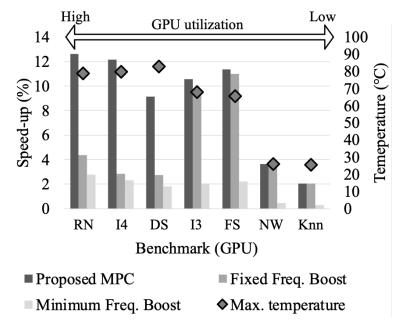

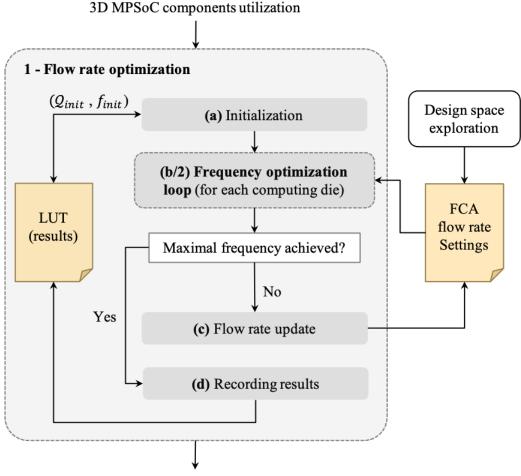

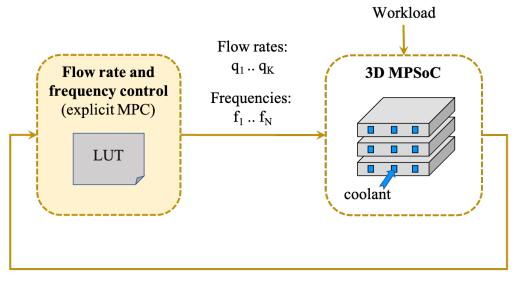

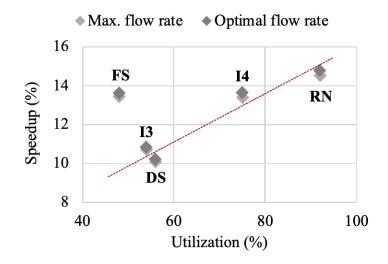

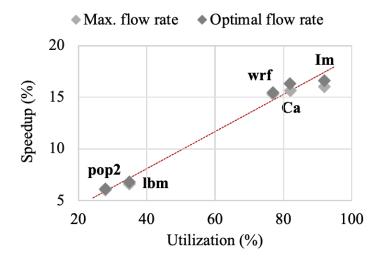

The power grid usage refers to the percentage of available power delivery lines and vias. As the exact locations and routing paths between the gates are unknown during the pre-layout design stages, the power grid usage is scaled to the power consumption density at the nodes[61] (Box (2) in Figure 3.2).