Medipix4, a high granularity four sides buttable pixel readout chip for high resolution spectroscopic X-ray imaging at rates compatible with medical CT scans

Présentée le 2 décembre 2022

Faculté des sciences et techniques de l'ingénieur Groupe de scientifiques IEL Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Viros SRISKARAN

Acceptée sur proposition du jury

Dr A. Schmid, président du jury Dr J.-M. Sallese, Dr A. Koukab, directeurs de thèse

Prof. A. Rivetti, rapporteur

Prof. C. Fröjdh, rapporteur

Prof. M. Kayal, rapporteur

## Acknowledgments

I came to CERN in early 2016 in the framework of my master thesis. I want to express my gratitude to Adil Koukab and Stefano Michelis for giving me the chance to work at CERN. I am thankful to my professors from Phelma at Grenoble, Politecnico di Torino and EPFL at Lausanne for introducing me to the world of nanosciences and microelectronics.

This PhD thesis would not have been possible without Jean-Michel Sallese, who took me as a doctoral student in his laboratory at EPFL and supported me throughout the doctoral thesis period. I want to thank Adil Koukab again for his advice and support since 2016.

I am grateful to Michael Campbell, who allowed me to continue working in his team as a doctoral student after my master thesis and recently opened the fellowship at CERN. Thank you for the trust you are continuing to put in me. I admire his ability to manage our small design team into building extensive systems such as Timepix and Medipix.

I have learned a lot about the design of chips under the supervision of Xavier Llopart and Rafael Ballabriga. Xavier taught me the importance of chip floorplan before the transistor-level design of analog blocks. I am very impressed by the expertise of Xavier in the different subjects related to the project: digital and analog designs, implementation of the chip, verification, and testing. I feel grateful to continue to work with him and learn how to become a complete engineer.

My knowledge of front-end design and analog building blocks comes from Rafael's teaching during those five years. I admire Rafael for his involvement in many projects, his positive attitude to keep learning, and his effort to disseminate his knowledge to the next generation. Rafael is, in many ways, a reference to the type of person I would like to become in the future.

I am grateful to the Medipix Collaboration for giving me the chance to work on Timepix2, Timepix4, and Medipix4. In the Microelectronics group at CERN, I would like to thank Lukas, Jerome, Iraklis, Markus, Nuria, Jose, Erik Heijne, Ana, Pinelopi, Winnie, Thanushan, Giacomo for working with me, for their help and availabilities.

Special thanks to Thanushan for the continuous advice and help throughout those years.

Many thanks to Markus for helping me with the English in this thesis.

I want to thank all the people who shared the office with me during those five years. Edinei and Moritz for introducing me to the design tools at my arrival. Jose for providing help when I was stuck in design, and special thanks for those non-technical discussions.

Thanks to all the people who made my stay in Geneva very enjoyable outside of work. Thanks to Vladimir, Jorgen, Marco, and Walter for the lunch break jogs. I am grateful to the 'Lazyboys Track Club' for having me within their circle. Thanks to my cycling friends, running friends, and my alpinism buddies. You all contributed to the love I have for the mountain activities.

Thanks to my parents, Kumar and Selvi, who provided the best to our family throughout the many difficulties. My father, for being an example that hard work pays off. I am grateful to my mother for trusting my competencies and pushing me to work hard during my first years in France while teachers were having doubts. Thanks to my siblings Ramya and Rageeth for their support throughout my life.

I hope that I have not forgotten anyone in these acknowledgments; I am sorry in advance for the person who is reading this thesis and who has not been mentioned on this page...

Geneva, October 2021

Viros Sriskaran

## **Abstract**

Medipix4 is the latest member in the Medipix/Timepix family of pixel detector chips aimed at high rate spectroscopic X-ray imaging using high-Z materials. The chip address the limitations of conventional hybrid pixel detectors for X-ray imaging. Its predecessor, Medipix3RX, covered some of those limitations and demonstrated the possibility of spectroscopic X-ray imaging at a fine pitch while keeping the spectral fidelity using a charge-sharing correction algorithm. However, its use in medical imaging, synchrotron applications, material analysis, and other applications highlighted some limitations. Indeed, the 3-side buttable architecture in Medipix3RX and other actual X-ray imaging systems introduces a dead zone in the imaging that closes the door to constructing large-area detectors. Moreover, the improvement in the dynamic energy range, the count-rate capability, and the energy resolution will benefit those applications.

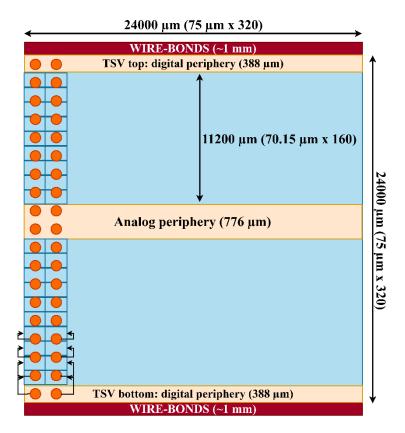

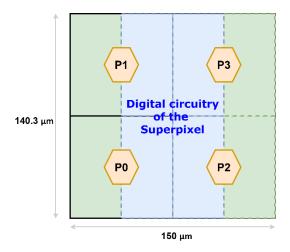

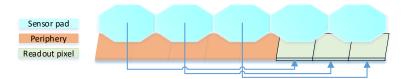

This thesis describes the Medipix4 chip implementation and discusses the proposed new pulse processing electronics in the analog pixel. The readout architecture relies on single photon counting with charge sharing correction for the energy binning of incoming hits. The chip consists of 320 x 320 pixels of 75  $\mu$ m x 75  $\mu$ m. It can work in Fine Pitch Mode (FPM) with 75  $\mu$ m pixel pitch and two threshold bins per pixel or in Spectroscopic Mode (SM) with 150  $\mu$ m pitch and up to eight energy threshold bins. Unlike its predecessor, Medipix3RX, it will be possible to tile the ASIC fully in both x and y directions, permitting seamless large area coverage. The chip size is 24 mm x 24 mm and covers 99.37% active area when using TSV connections only.

The ASIC is designed in a commercial CMOS 130 nm process technology with a power supply of 1.2 V. The new analog front-end architecture improves the energy dynamic range, the count-rate capability, and the energy resolution compared with Medipix3RX while the charge sharing correction is still supported. Those improvements come at the expense of power consumption and spatial resolution. The latter should not be a problem since studies have shown that the optimal pixel pitch for CdTe or CdZnTe should be slightly larger than the Medipix3RX pixel in order to account for a larger fraction of fluorescence photons.

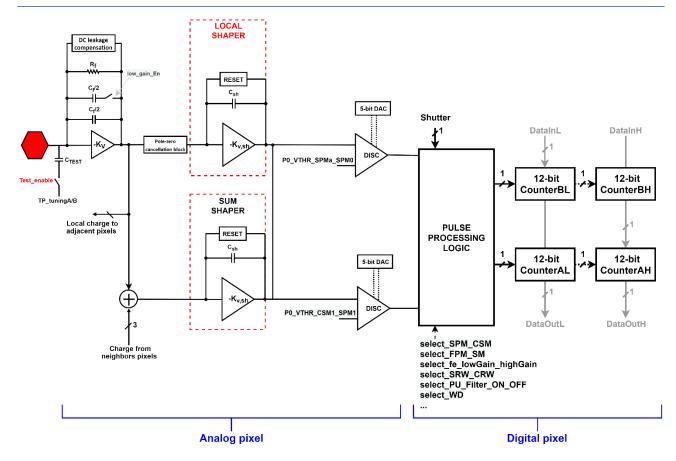

Each analog pixel contains a Charge Sensitive Amplifier with a DC leakage compensation network up to 50 nA. Two pulse-shaping circuits in the second stage implement the charge sharing correction mode. The new shaper amplifier has a reduced baseline drift at high flux compared to the amplifier implemented in the previous Medipix/Timepix chips. The implemented ASIC has three modes of operation: High Dynamic Range Mode (HDRM), Low Noise Mode (LNM), and Ultra-Fast Mode (UFM). In HDRM, the chip can process X-ray photons with energies up to 154 keV with a CdTe sensor, implying 40% improvement compared to Medipix3RX. In LNM, the expected energy resolution has been improved by 55 %. In UFM, the post-layout simulated count-rate capability of the front-end is  $19 \times 10^6$  photons.mm<sup>-2</sup>.s<sup>-1</sup> at 10% hit loss for a 150 µm pixel pitch and not affected by charge sharing effect, showing an improvement by a factor of 5. In addition, the pixel includes a digital pile-up filtering method that improves spectral fidelity at high rates.

## Keywords

Front-end electronics, Charge sharing, Photon counting, Photon processing, Hybrid pixel detectors, Medipix, Timepix, X-ray imaging, Pile-up.

## Résumé

Medipix4 est le dernier détecteur hybride de pixels conçu dans la famille Medipix/Timepix destiné pour la spectroscopie avec rayons X à haut taux de comptage. Cette puce est compatible avec les semi-conducteurs avec un numéro atomique élevé et résout les limitations des détecteurs hybrides de pixels utilisés pour l'imagerie par rayons X. Son prédécesseur, Medipix3RX, avec l'algorithme pour corriger le partage de charges, a permis de résoudre quelques limitations et a démontré que la spectroscopie par rayons X était possible en utilisant des pixels de très petites tailles tout en conservant la fiabilité spectrale. Cependant, ses utilisations dans les applications médicales, synchrotrons, analyse de matériaux, et autres applications ont signalés quelques limitations. En effet, Medipix3RX mais aussi les autres systèmes d'imagerie par rayons X actuels permettent seulement la butée des puces contre trois côtés, ce qui limite la construction des détecteurs de grandes surfaces. De plus, une amélioration du gamme d'énergie, du taux de comptage, et de la résolution d'énergie peuvent bénéficier ces applications.

Cette thèse explique l'architecture de Medipix4 et décrit une nouvelle électronique pour le traitement de photons dans la partie analogique du pixel. L'architecture de lecture utilise le comptage de photons avec un algorithme de correction du partage de charges pour la répartition des évènements en fonction de leurs énergies. La puce est une matrice de 320 x 320 pixels ayant une taille de 75  $\mu$ m x 75  $\mu$ m. Deux seuils sont disponibles en Fine Pitch Mode (FPM) pour un capteur dont le pas de pixel est de 75  $\mu$ m. En Spectroscopic Mode (SM), pour un capteur avec un espacement entre les pixels de 150  $\mu$ m, on dispose de huit seuils. Contrairement à Medipix3RX, la puce est apte à venir en butée contre les quatre côtés, cela permet la construction des détecteurs couvrant une grande surface sensible. La taille de la puce est de 24 mm x 24 mm et a une zone sensible de 99.37% lorsque les connections TSV sont utilisées.

Medipix4 a été conçu avec une technologie commerciale CMOS 130 nm à partir d'une alimentation d'entrée de 1.2 V. La nouvelle architecture pour l'électronique analogique du pixel améliore la gamme d'énergie, le taux de comptage, et la résolution d'énergie par rapport à Medipix3RX tout en conservant la correction pour le partage de charges. Ces améliorations ont été possibles aux dépens d'une petite augmentation de la consommation de puissance et de la résolution spatiale. Une plus grande taille du pixel permettrait de capturer les photons de fluorescences qui déposent leurs énergies loin du point initial d'interaction dans les capteurs de CdTe ou CdZnTe.

Chaque pixel analogique comporte un amplificateur sensible à la charge avec un mécanisme de compensation du courant de fuite jusqu'à 50 nA. Deux circuits de mise en forme d'impulsions permettent d'assurer la correction du partage de charges. Ces deux circuits ont une faible dérive de la ligne de base à haut taux de comptage par rapport aux précédents amplificateurs des puces Medipix/Timepix. On propose trois modes de fonctionnement pour la puce : High Dynamic Range Mode (HDRM), Low Noise Mode (LNM), et Ultra-Fast Mode (UFM). Avec HDRM, la puce peut détecter des rayons X avec une gamme d'énergie allant jusqu'à 154 keV pour un capteur de CdTe, suggérant une expansion de 40% par rapport à Medipix3RX. Avec LNM, on prévoit une amélioration de 50% sur la résolution d'énergie. Après la disposition du layout, les simulations indiquent un taux de comptage de photons jusqu'à 19 x 106 photons.mm<sup>-2</sup>.s<sup>-1</sup> avec 10% de perte d'évènements lorsque l'électronique est configurée pour les pixels de 150 µm et avec correction du partage de charges. Le taux de comptage est cinq fois élevé qu'avec Medipix3RX. Et enfin, la partie digitale du pixel comporte un mécanisme de filtrage des évènements qui s'empilent. Ce procédé de filtrage permet d'améliorer la fiabilité spectrale à haut taux de comptage.

### Mots-clés

Electronique Frontale, Partage de charge, Comptage de photon, Traitement de photon, Détecteur hybride de pixels, Medipix, Timepix, Imagerie par rayons X, Pile-up.

# Contents

| Acknowledg     | ments  |                                                   | v   |

|----------------|--------|---------------------------------------------------|-----|

| Abstract       |        |                                                   | vi  |

| Keywords       |        |                                                   | vi  |

| Résumé         |        |                                                   | vii |

| Mots-clés      |        |                                                   | vii |

| List of Figure | es     |                                                   | xi  |

| List of Tables | s      |                                                   | 17  |

| Chapter 1      | Introd | duction                                           | 18  |

| Chapter 2      | Introd | duction to X-ray imaging                          | 20  |

| 2.1            | Intera | nction of X-rays with matter                      | 20  |

|                | 2.1.1  | Photoelectric absorption                          | 20  |

|                | 2.1.2  | Compton (or incoherent) scattering                | 21  |

|                | 2.1.3  | Electron-Positron pair production                 | 21  |

|                | 2.1.4  | Rayleigh (or coherent) scattering.                | 21  |

| 2.2            | Detec  | tors for X-ray imaging                            | 22  |

|                | 2.2.1  | Direct versus indirect conversion.                | 22  |

|                | 2.2.2  | Integrating versus pulse processing architecture  | 22  |

| 2.3            | Towar  | rds an ideal X-ray imaging detector system        | 23  |

|                | 2.3.1  | Ideal X-ray spectroscopic imaging system?         | 23  |

|                | 2.3.2  | Hybrid pixel detectors for X-ray imaging          | 23  |

| 2.4            | Summ   | nary                                              | 24  |

| Chapter 3      | Pulse  | processing for X-ray imaging                      | 25  |

| 3.1            | Semic  | conductors detectors                              | 25  |

|                | 3.1.1  | Charge transport in semiconductors                | 25  |

|                | 3.1.2  | Limiting factors in sensors for X-ray imaging     | 28  |

| 3.2            | Bump   | bond connection                                   | 31  |

| 3.3            | Reado  | out electronics for X-ray imaging                 | 32  |

|                | 3.3.1  | Quantum processing in pixels                      | 32  |

|                | 3.3.2  | Limiting factors in electronics for X-ray imaging | 35  |

| 3.4       | Summary                                                                            | 45 |

|-----------|------------------------------------------------------------------------------------|----|

| Chapter 4 | Medipix family of chips                                                            | 46 |

| 4.1       | Medipix1: Photon counting detector for X-ray imaging                               | 46 |

|           | 4.1.1 Architecture of Medipix1                                                     | 46 |

|           | 4.1.2 Limitations and motivation for the design of Medipix2                        | 46 |

| 4.2       | Medipix2: dual-threshold X-ray imaging detector                                    | 47 |

|           | 4.2.1 Architecture                                                                 | 47 |

|           | 4.2.2 Applications using Medipix2                                                  | 48 |

|           | 4.2.3 Limitations and motivation for the design of Medipix3                        | 48 |

| 4.3       | Medipix3: Spectroscopy imaging with charge sharing correction                      | 50 |

|           | 4.3.1 Charge sharing correction method                                             | 50 |

|           | 4.3.2 Architecture                                                                 | 51 |

|           | 4.3.3 Applications using Medipix3                                                  | 53 |

|           | 4.3.4 Limitations of Medipix3RX and ideas for the design of Medipix4               | 54 |

| 4.4       | Summary and specifications for the design of Medipix4                              | 59 |

| Chapter 5 | Timepix family of chips                                                            | 60 |

| 5.1       | Timepix                                                                            | 60 |

|           | 5.1.1 Architecture                                                                 | 60 |

|           | 5.1.2 Some applications                                                            | 61 |

|           | 5.1.3 Limitations and motivation for the design of Timepix3                        | 62 |

| 5.2       | Timepix3                                                                           | 62 |

|           | 5.2.1 Architecture                                                                 | 62 |

|           | 5.2.2 Some applications                                                            | 63 |

| 5.3       | Timepix2                                                                           | 63 |

|           | 5.3.1 Architecture and motivation                                                  | 63 |

|           | 5.3.2 Design of a fast Rail-to-rail buffer for monitoring the front-end of a pixel | 64 |

|           | 5.3.3 Voltage and current DACs for the periphery                                   | 66 |

|           | 5.3.4 Few measurements result from Timepix2                                        | 67 |

| 5.4       | Timepix4                                                                           | 69 |

|           | 5.4.1 Motivation and architecture                                                  | 69 |

|           | 5.4.2 Design of analog blocks for the periphery of Timepix4                        | 71 |

|           | 5.4.3 Few measurement results from Timepix4                                        | 73 |

| 5.5       | Summary                                                                            | 74 |

| Chapter 6 | Implementation and design of Medipix4                                              | 75 |

| 6.1       | Motivation for the Medipix4 chip                                                   | 75 |

| 6.2       | Towards a 4-side buttable chip                                                     | 77 |

|           | 6.2.1 The Medipix4 chip and pixel architecture                                     | 77 |

|            |          | 6.2.2    | Redistribution layer for 4-side buttable chip                      | 78    |

|------------|----------|----------|--------------------------------------------------------------------|-------|

|            |          | 6.2.3    | Power distribution                                                 | 80    |

| 6          | 5.3      | Details  | of the analog front-end of the pixel                               | 84    |

|            |          | 6.3.1    | First stage amplifier                                              | 84    |

|            |          | 6.3.2    | Baseline holder                                                    | 93    |

|            |          | 6.3.3    | Pulse shaping circuit                                              | 96    |

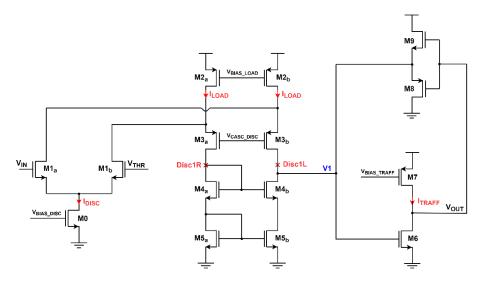

|            |          | 6.3.4    | Comparator                                                         | . 103 |

|            |          | 6.3.5    | Digital-to-Analog Converter                                        | . 104 |

|            |          | 6.3.6    | Implementation of the charge sharing correction                    | . 106 |

|            |          | 6.3.7    | A configurable pixel for spectroscopic imaging                     | . 108 |

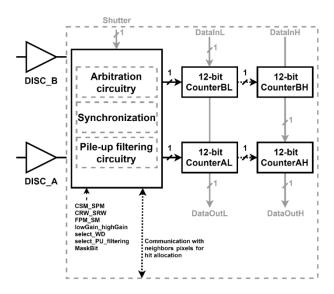

| 6          | 5.4      | The pix  | el digital circuitry                                               | . 113 |

|            |          | 6.4.1    | Techniques to improve the spectroscopic performances at high-rates | . 113 |

|            |          | 6.4.2    | Architecture                                                       | . 119 |

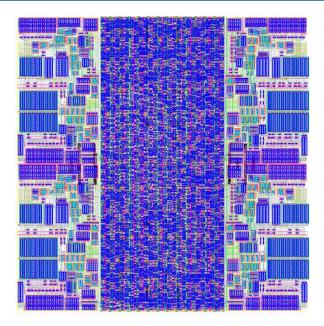

|            |          | 6.4.3    | Full pixel layout                                                  | . 119 |

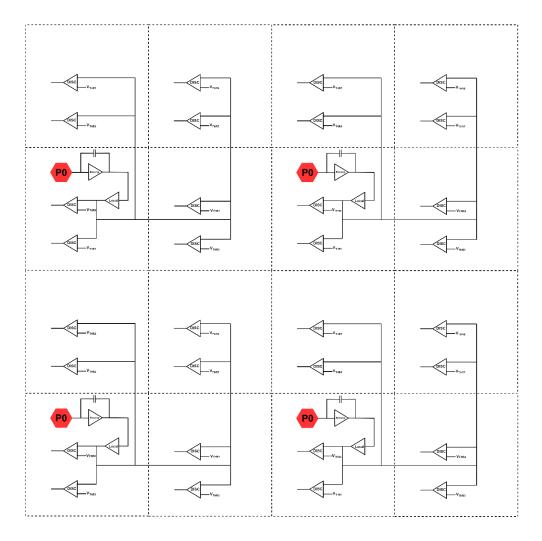

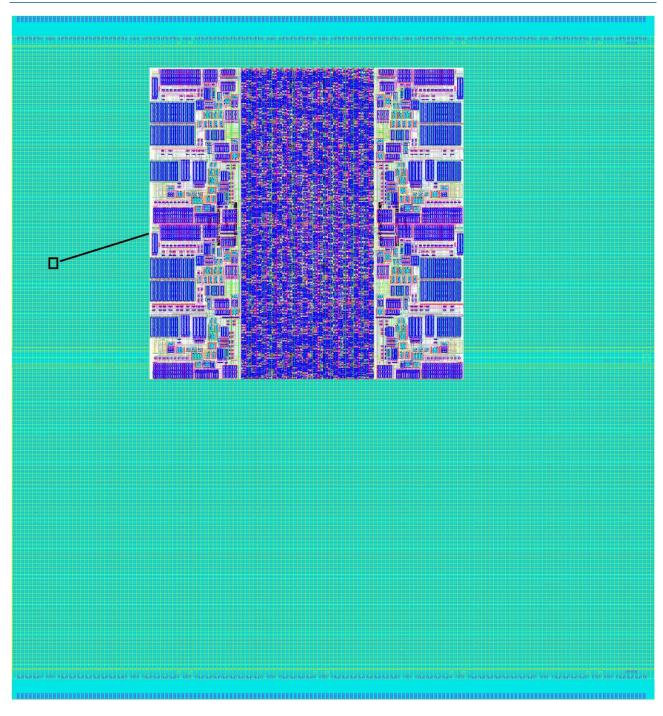

| 6          | 5.5      | Full chi | p implementation                                                   | . 120 |

| 6          | 5.6      | Summa    | ary                                                                | . 121 |

| Chapter    | 7        | Conclu   | sion                                                               | . 123 |

| Appendi    | x: Nois  | e calcu  | lation                                                             | . 125 |

| Bibliogra  | phy      |          |                                                                    | . 127 |

| Curriculu  | ım Vita  | ae       |                                                                    | . 136 |

| List of Pu | ublicati | ions     |                                                                    | . 138 |

## List of Figures

| Figure 1.1. A fixed target Pb-Pb event reconstruction with 153 tracks, using a seven-plane pixel telescope in WA97. Each 'Window' represents 5 x 5 cm², having 72000 pixels. The pixel dimension is 75 x 500 $\mu$ m². The tracks have been reconstructed with a trigger precision of 1 $\mu$ s and a radiation tolerance of around 30 kRad. The red dots on the figure represents the detected hits in the silicon detectors [4]18                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

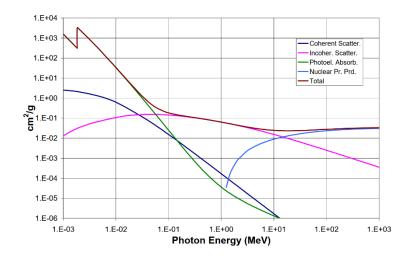

| Figure 2.1. The cross-section in a silicon sensor versus the energy of the incoming X-ray photon. The four interactions with the material are highlighted [11]                                                                                                                                                                                                                                                                                                      |

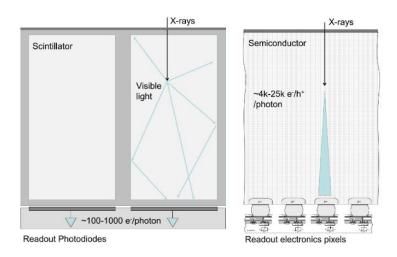

| Figure 2.2. Illustration of an indirect detection system on the left and direct detection on the right [12].                                                                                                                                                                                                                                                                                                                                                        |

| Figure 2.3. Operation principle of an integrating energy system in the central plot and a pulse processing architecture in the bottom plot. The time of arrival of 5 photons having different energies is shown in the top plot. Three thresholds are applied in the case of the pulse processing system. The 4 <sup>th</sup> and 5 <sup>th</sup> events suffer from pile-up in the pulse processing architecture and recognized wrongly as a single event [12]. 23 |

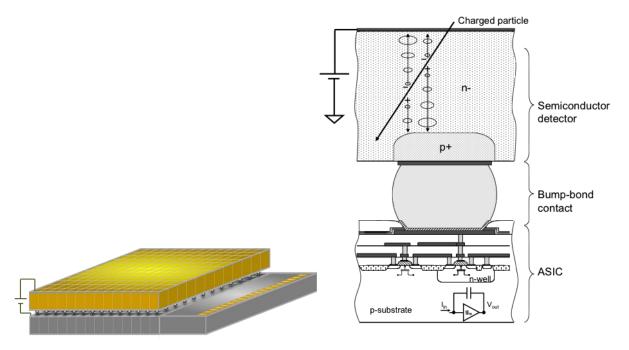

| Figure 2.4. 3-Dimensional view of the architecture of a hybrid pixel detector in the left plot. The yellow array at the top represents the semiconductor sensor. The grey array at the bottom is the readout pixels. The connection between both parts is made with flip-chip technology. The 2-Dimensional view is shown in the right plot [11]                                                                                                                    |

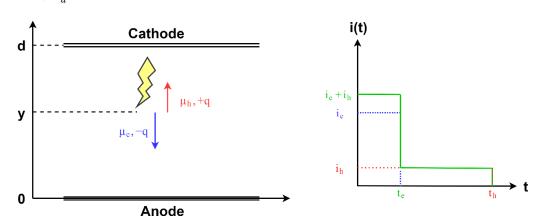

| Figure 3.1. Parallel plate geometry sensor, the carriers induce a current during the drift movement towards the electrode. The right plot represents the induced current as a function of time26                                                                                                                                                                                                                                                                    |

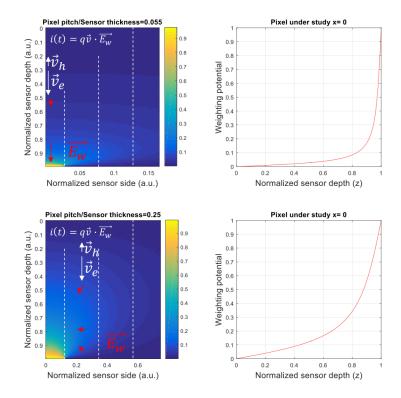

| Figure 3.2. Illustration of the weighting potential in a 2 mm thick segmented sensor with a pixel pitch of 110 µm (top) and 500 µm (bottom) [12]27                                                                                                                                                                                                                                                                                                                  |

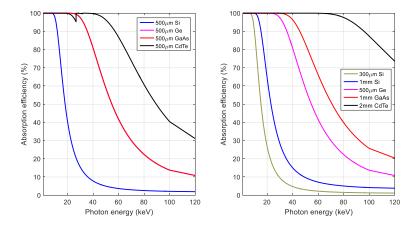

| Figure 3.3. Absorption efficiency of different semiconductor materials (Si, Ge, GaAs and CdTe) (left), and for different thicknesses of the sensor (right) [13] [22]                                                                                                                                                                                                                                                                                                |

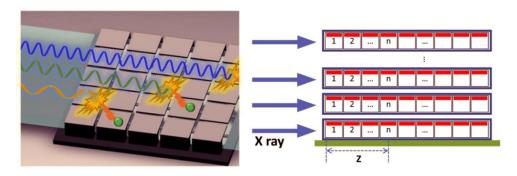

| Figure 3.4. In edge-on detectors, the photon comes from the edge-side of the detector. The long active                                                                                                                                                                                                                                                                                                                                                              |

| distance gives a higher chance of absorbing a high-energy X-ray photon than conventional face-on geometry [25]                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

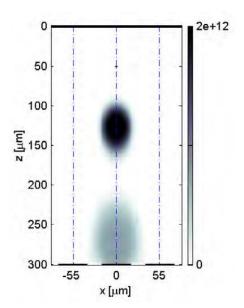

| Figure 3.5. Simulation of the charge deposition in a pixelated silicon sensor of a 10 keV photon after deposition at 50 μm depth. The black cloud represents the charges after 4 ns of drift (and diffusion), and the gray cloud after 14 ns of drift motion [10]                                                                                                                                                                                                   |

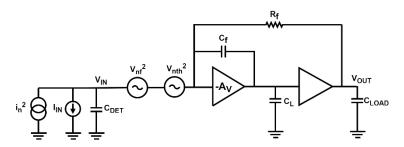

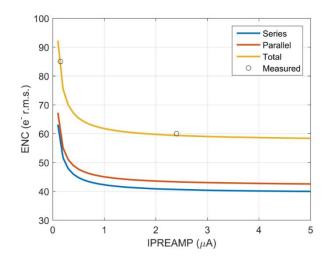

| Figure 3.14. Equivalent Noise Charge versus the input transistor current in the front-end pixel of Timepix ASIC [46]                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

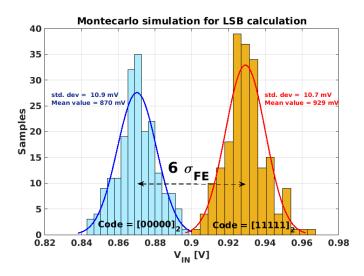

| Figure 3.15. Procedure for the choice of I <sub>LSB</sub> in the threshold adjustment per pixel39                                                                                                                                                                                                                                                   |

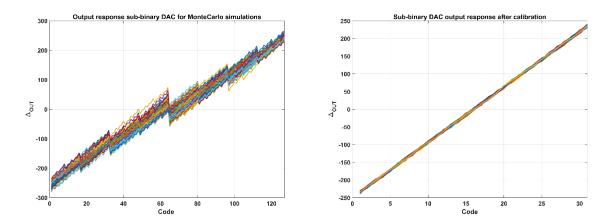

| Figure 3.16. Non-linear and non-monotonic transfer function of a 7-bit sub-binary radix DAC on the left Linear transfer function after calibration on the right (7 bits are necessary to achieve the same dynamic range as a 5-bit binary-weighted DAC).                                                                                            |

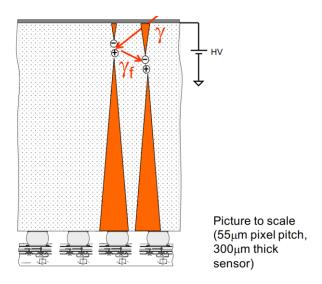

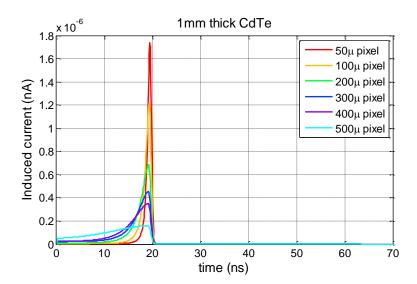

| Figure 3.17. Simulated induced signal at the input of the readout pixel for a 1mm thick CdTe sensor as a function of the pixel size dimension. The sensor bias voltage is 600 V, and a 60 keV input photon was taker for the simulation [13]                                                                                                        |

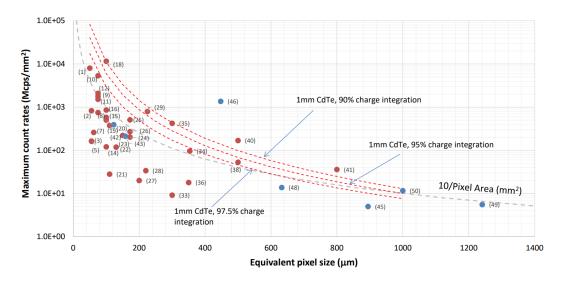

| Figure 3.18. Maximum count-rates for different hybrid pixel detectors as a function of the pixel pitch [12]                                                                                                                                                                                                                                         |

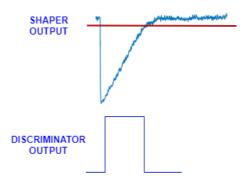

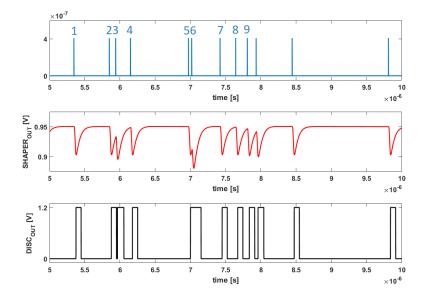

| Figure 3.19. Explanation of pile-up events. The blue plot represents the incoming input charges; the recurve is associated with the output of the shaper and the discriminator output in black41                                                                                                                                                    |

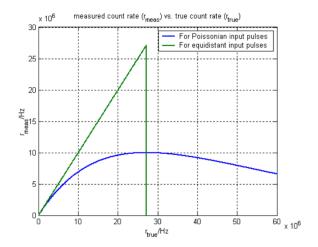

| Figure 3.20. Observed count-rate versus incident count-rate for a Poisson distribution in blue and equidistant arrival pulses in green [55]                                                                                                                                                                                                         |

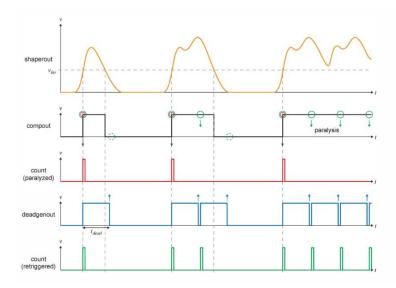

| Figure 3.21. Signal waveforms illustrate the operation of the instant retrigger technology. The output of the shaper (in orange) is fed to the comparator (in black). The registered counts for the paralyzed mode are shown in red; the retriggered counts are shown in green. The blue waveform shows the dead-time set for the measurement [57]. |

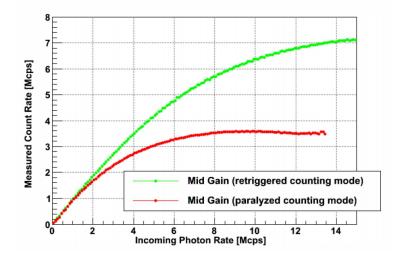

| Figure 3.22. The measured count-rate of the PILATUS3 X-ray detector versus the incoming photon rate. The red curve corresponds to the paralyzed counting mode, and the green curve shows the retriggered counting                                                                                                                                   |

| mode. The input source is monochromatic with an energy of 8 keV; the threshold is set at the mid-range for the measurement [57]                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

| for the measurement [57]                                                                                                                                                                                                                                                                                                                            |

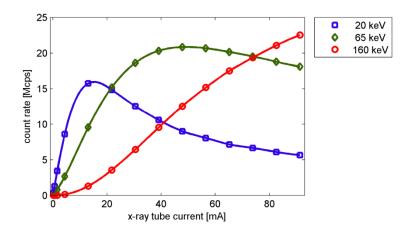

| Figure 3.23. The count-rate capability of the ASIC using an unattenuated 140 kVp input spectrum at calibrated energy thresholds, increasing the threshold voltage permits to lower the degree of paralyzation of the chip [58]                                                                                                                      |

| Figure 3.23. The count-rate capability of the ASIC using an unattenuated 140 kVp input spectrum at calibrated energy thresholds, increasing the threshold voltage permits to lower the degree of paralyzation of the chip [58]                                                                                                                      |

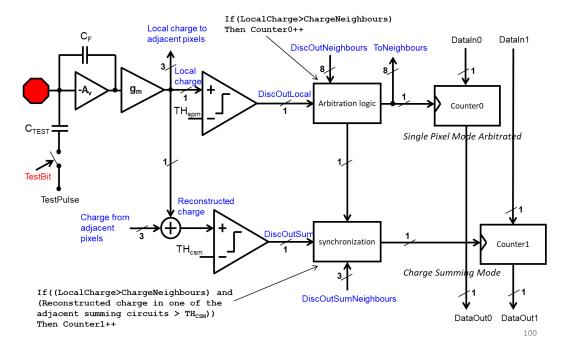

| Figure 4.8. Block diagram of the pixel cell in the Medipix3 chip. The analog pixel contains a CSA followed by a first-order semi-gaussian shaper, then a current comparator. The communications between neighboring pixels permit correct the charge sharing between pixels. The digital circuitry contains two 12-bit counters, an arbitration circuitry, and some control logic [85]. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.9. Color X-ray imaging of a wrist of a subject was obtained from the MARS detector using Medipix3RX as a readout system [97]. The bone, soft tissues, and metallic watch are identified54                                                                                                                                                                                      |

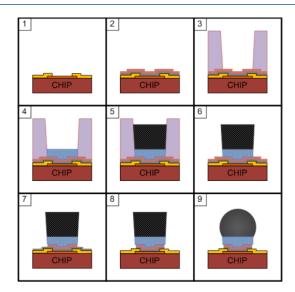

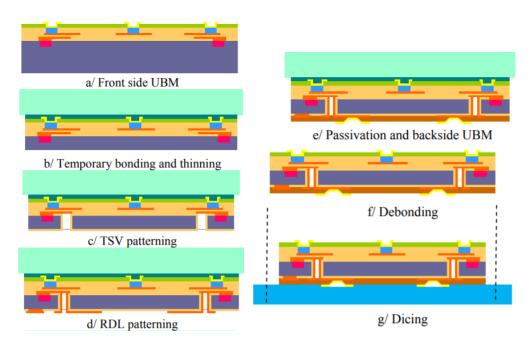

| Figure 4.10. Process flow for the TSV last technology [106]                                                                                                                                                                                                                                                                                                                             |

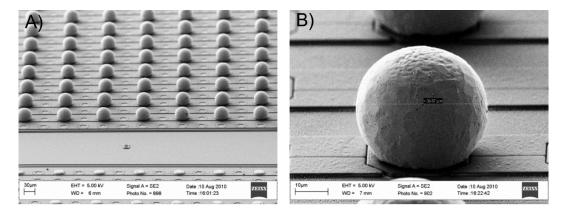

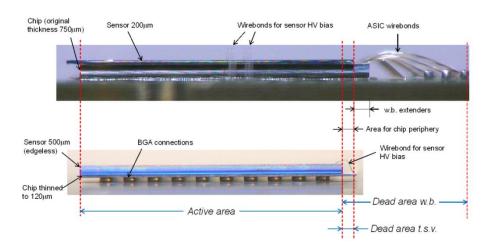

| Figure 4.11. Lateral view of the Medipix3RX on chipboard (Top). The bottom view shows the Medipix3RX chip after TSV processing and connecting to the chipboard using BGA [13]55                                                                                                                                                                                                         |

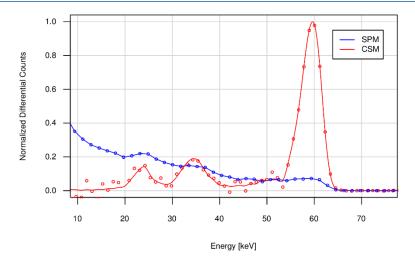

| Figure 4.12. the measured spectrum of a 60 keV input source on a 2 mm thick CdTe sensor using Medipix3RX in SPM (blue) and CSM (red) [109]                                                                                                                                                                                                                                              |

| Figure 4.13. Semi-gaussian shaper implemented in the analog pixel of Medipix3RX [11]56                                                                                                                                                                                                                                                                                                  |

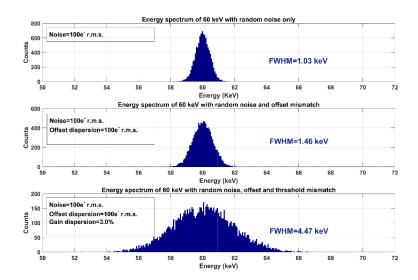

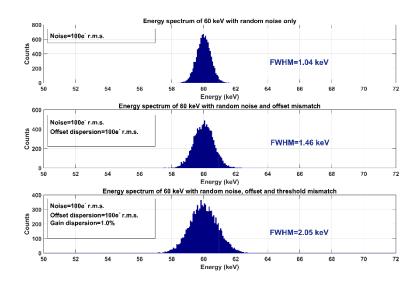

| Figure 4.14. The energy spectrum of a 60 keV monochromatic source, adding the readout noise of 100 e <sup>-</sup> rms, the offset mismatch of 100 e <sup>-</sup> rms and the gain mismatch of 3%. The energy spectrum has a FWHM of 4.47 keV [108]                                                                                                                                      |

| Figure 4.15. The energy spectrum of a 60 keV of a monochromatic source, adding a readout noise of 100 e-, offset mismatch of 100 e- rms, and a gain mismatch of 1% rms. The FWHM is 2.05 keV [108] $58$                                                                                                                                                                                 |

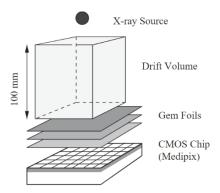

| Figure 5.1. The structure of a Time Projection Chamber (TPC) with a 100 mm drift volume and using a stack of three Gas Electron Multiplier (GEM) and a Medipix2 chip for readout [79]60                                                                                                                                                                                                 |

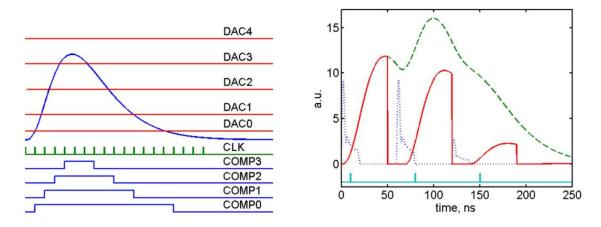

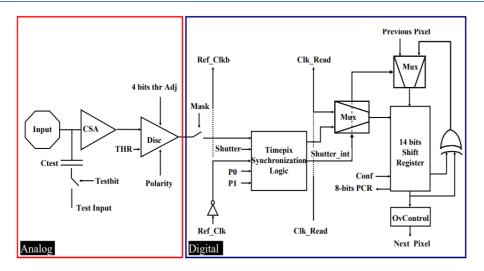

| Figure 5.2. Block diagram of the Timepix pixel cell [37].                                                                                                                                                                                                                                                                                                                               |

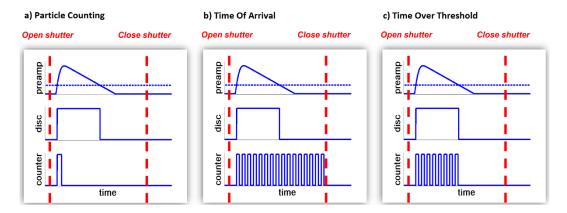

| Figure 5.3. Illustration of the working principle of the different modes of operation in Timepix chip. The chip can be configured in (a) Particle Counting mode (PC), (b) Time of Arrival mode (TOA), and (c) Time over Threshold mode (TOT) [113].                                                                                                                                     |

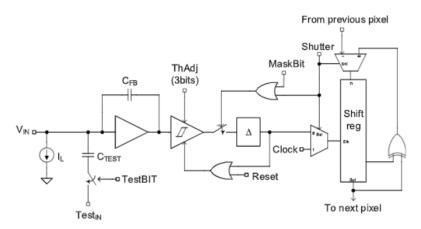

| Figure 5.4. Block diagram of the Timepix3 pixel cell [38] [139].                                                                                                                                                                                                                                                                                                                        |

| Figure 5.5. Block diagram of the Timepix2 pixel cell [151]                                                                                                                                                                                                                                                                                                                              |

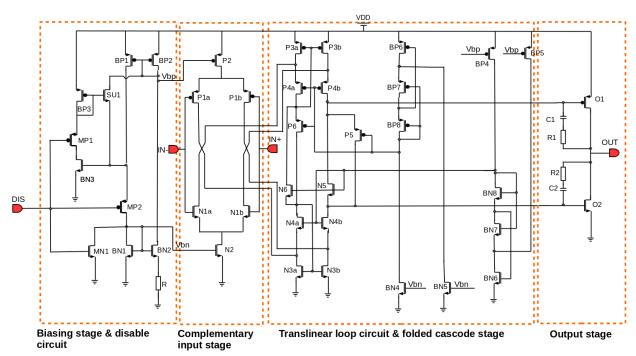

| Figure 5.6. Architecture of the RtR buffer achieving full linearity. The circuitry is self-biased using a beta-<br>multiplier topology                                                                                                                                                                                                                                                  |

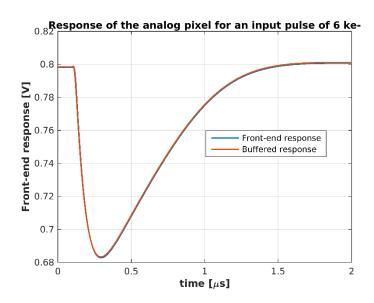

| Figure 5.7. Front-end response of the pixel in bleu for an input charge of 6 ke <sup>-</sup> and the output signal monitored by the RtR buffer in red                                                                                                                                                                                                                                   |

| Figure 5.8. Layout of the analog periphery block containing 7 voltage DAC, 8 current DACs, and bandgap circuit. The size dimension of the block is 3550 x 664 $\mu$ m <sup>2</sup> 67                                                                                                                                                                                                   |

| Figure 5.9. Timepix2 readout bonded to a 300 μm thick silicon sensor and connected to a printed circuit board using wire bonds extenders (courtesy J. Alozy)                                                                                                                                                                                                                            |

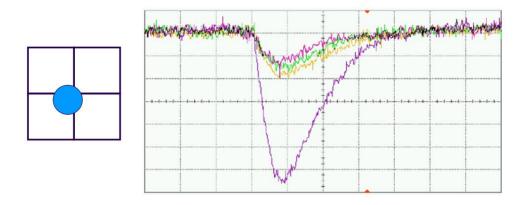

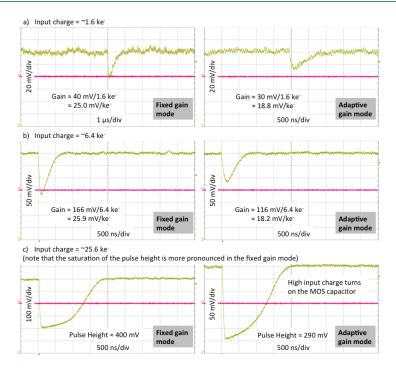

| Figure 5.10. Monitoring of the pixel response through the RTR buffer. The Fixed Gain and Adaptive Gain modes are tested by injecting 1.6 ke <sup>-</sup> , 6.4 ke <sup>-</sup> and 25.6 ke <sup>-</sup> [151]68                                                                                                                                                                         |

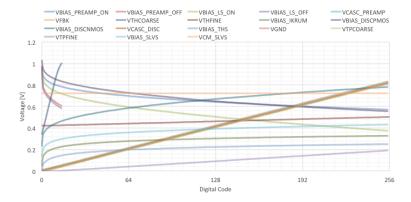

| Figure 5.11. DAC scans from 0 to 255. The current and Voltage DACs follow the simulated linearity [151].                                                                                                                                                                                                                                                                                |

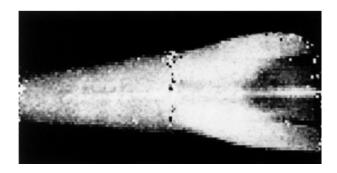

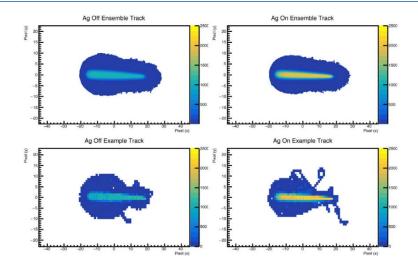

| Figure 5.12. Tracks created by Si <sup>28</sup> ions detected using Timepix2 readout bonded to a 500 µm thick silicon sensor and operated at a bias voltage of 100 V. The tracks are shown with the Fixed Gain Mode on the left, and using the Adaptive Gain Mode on the right [158]                                                                                                    |

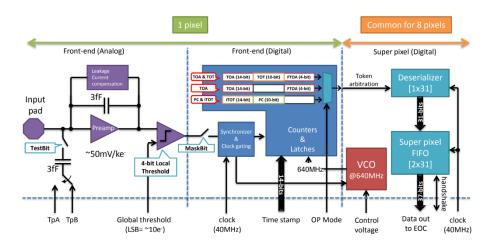

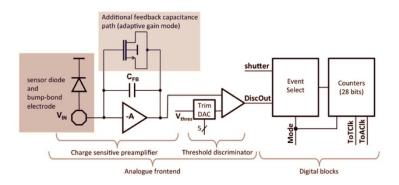

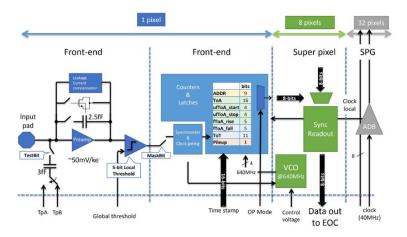

| Figure 5.13. Block diagram of the Timepix4 pixel cell [113]                                                                                                                                                                                                                                                                                                                             |

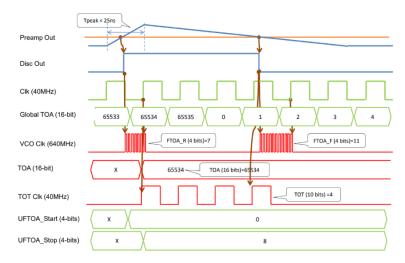

| Figure 5.14. Illustration of the TOT and TOA information measurement in Timepix4 pixel cell [113].70                                                                                                                                                                                                                                                                                    |

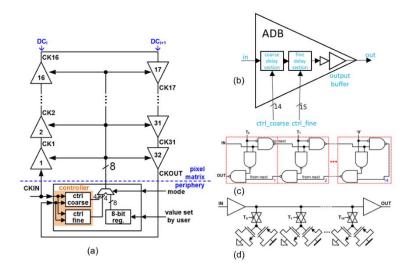

| Figure 5.15. Description of the dDLL in Timepix4. (a) The 16 super pixel group blocks of the double-column contain 2 ADBs, one for the propagation upward of the clock, while the other one for the downwards                                                                                                                                                                           |

| elements. (c) is the schematic of the coarse delay element, and (d) is the topology of the fine delay element  [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

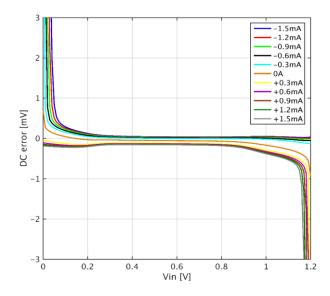

| Figure 5.16. Simulated linearity error in the slow RtR buffer from 0 to 1.2 V for an output DC current load varying from -1.5 mA to 1.5 mA. The error increases to 3 mV near the extreme rails values for high DC at the output                                                                                                                                                                                                                                                                                                                                                                          |

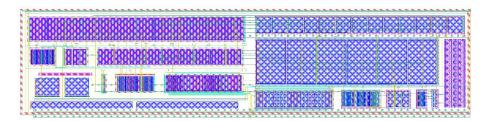

| Figure 5.17. Layout of the slow rail-to-rail buffer in Timepix4. The size dimension of the layout is 39 x 157 $\mu m^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

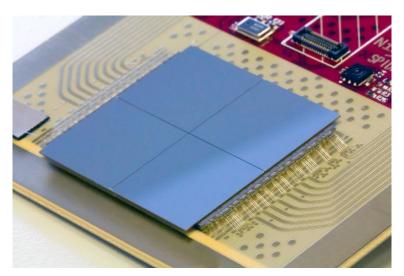

| Figure 5.18. Timepix4 is connected to four silicon sensors. The chip is connected to the circuit board using wire bonds for testing purposes. Photo courtesy to M.Fransen (Nikhef)                                                                                                                                                                                                                                                                                                                                                                                                                       |

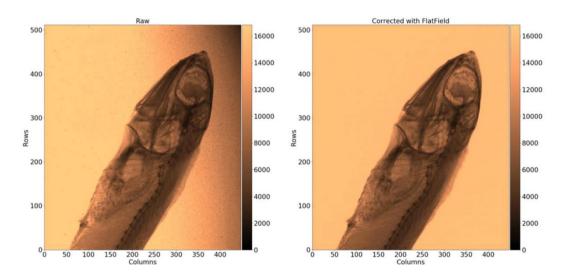

| Figure 5.19. X-ray images of a dried fish taken using Timepix4 in frame-based mode; the readout is bonded to a 300 μm thick silicon sensor and mounted on the Nikhef chip carrier board [159]74                                                                                                                                                                                                                                                                                                                                                                                                          |

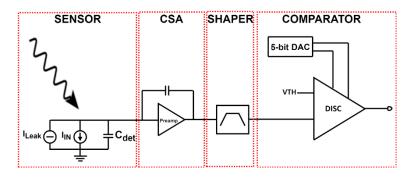

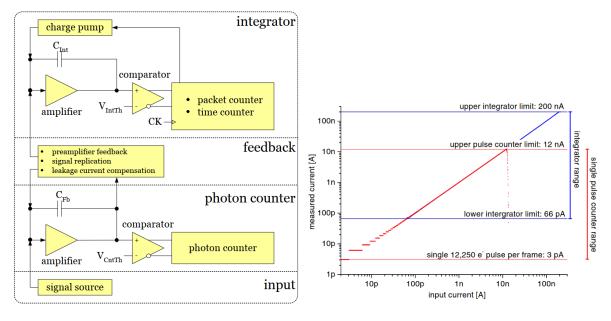

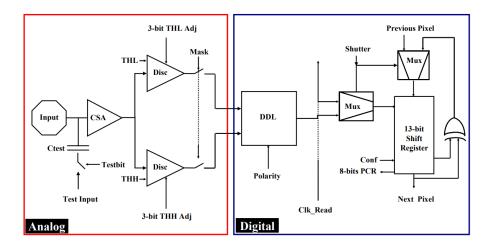

| Figure 6.1. Block digram of the pixel cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

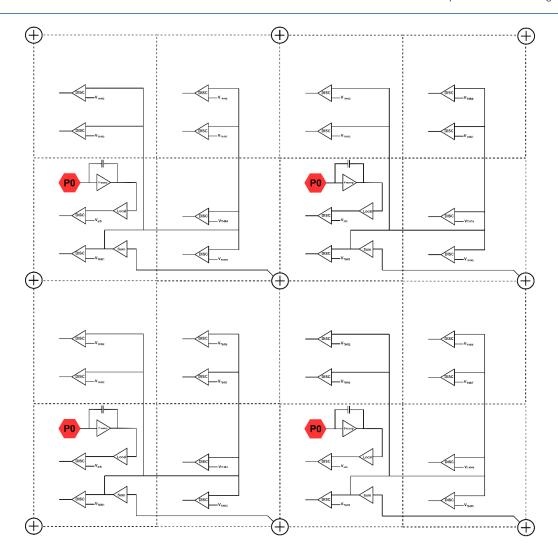

| Figure 6.2. Floorplan of the Medipix4 chip. The ASIC contains 320x320 pixels with a pixel pitch of 75 $\mu$ m. The readout pixels in the blue area are slightly shifted to the sensor pixels. The analog periphery is in the middle. The chip has two digital peripheries at the bottom and top extremities77                                                                                                                                                                                                                                                                                            |

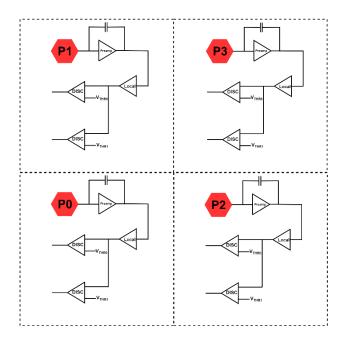

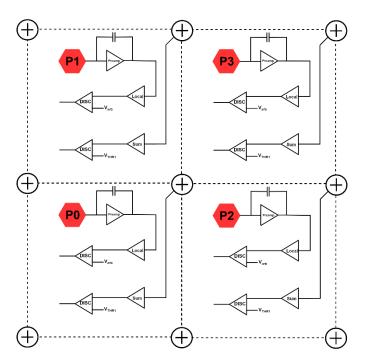

| Figure 6.3. The superpixel is composed of 2x2 regular pixels. The digital circuitries are common to the four pixels and located at the center of the superpixel                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 6.4. Illustration of the sensor pads covering the readout pixels and the periphery. RDL connects the sensor pad to its associated readout pixel                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

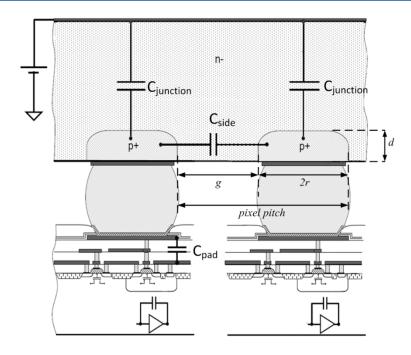

| Figure 6.5. Input capacitances for a semiconductor pixel detector [11], [40]79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

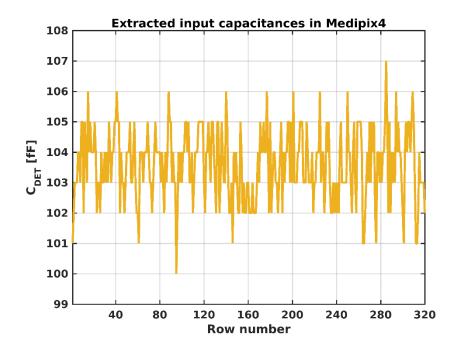

| Figure 6.6. Extracted input capacitances in Medipix4 (courtesy X.Llopart)80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

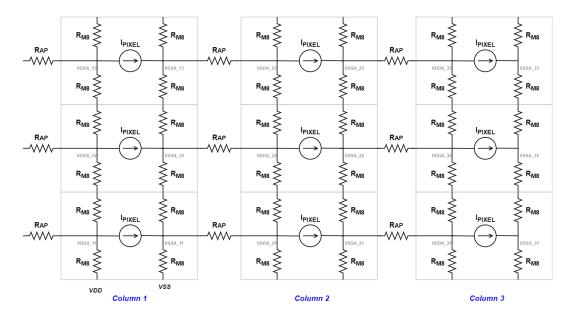

| Figure 6.7. Example of power distribution scheme of the critical nets VDDA and VSSA in a 3x3 cluster of pixels. The schematic of the pixel is simplified as a series of resistances for the vertical and horizontal power lines and a constant current flowing in the analog pixel. $R_{M8}$ is the resistance of a 70.15/2 $\mu$ m long Metal 8, $R_{AP}$ is the resistance of 75/2 $\mu$ m long metal AP. The current flowing in each pixel is 23.4 $\mu$ A. The position of the power pads influences the horizontal power drop. In this example, only the first column has the power pads at its end |

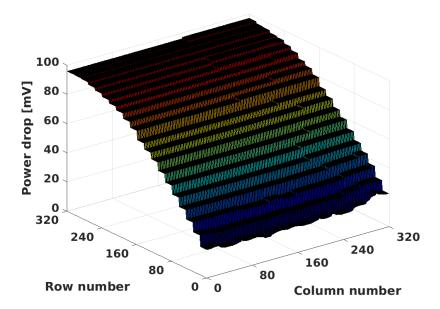

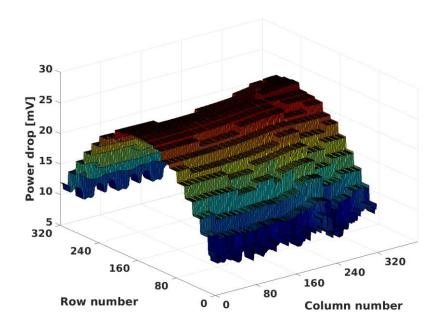

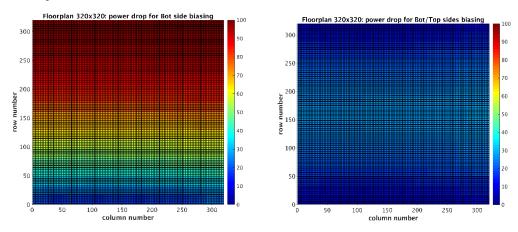

| Figure 6.8. 3-D representation of the power drop $\Delta(VDDA) - \Delta(VSSA)$ in the Medipix4 chip. The power drop increases when moving further from the bottom of the chip where the power pads are located. The horizontal power distribution remains relatively constant thanks to the uniformly spaced power pads. The worst power drop is 92 mV at the top of the matrix. The staircase shape comes from the meshing used in the simulation                                                                                                                                                       |

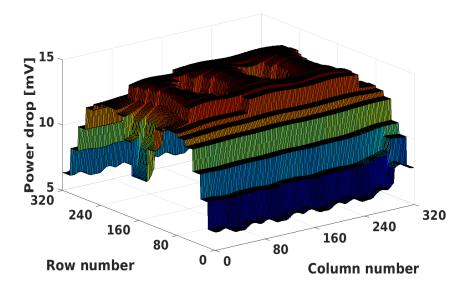

| Figure 6.9. 3-D representation of the power drop $\Delta(VDDA) - \Delta(VSSA)$ in the Medipix4 chip for two sides biasing. The power drop is maximal at the center of the chip, giving the worst power drop of $\Delta(VDDA) - \Delta(VSSA) = 27 \text{ mV}$ .                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.10. 3-D representation of the power drop $\Delta(VDDA) - \Delta$ (VSSA) in the Medipix4 chip for Bot, Center, and Top biasing. The power drop is still maximal at the center of the chip as the two sides are biasing. This is because only 8 power pads are placed in the central analog periphery leading to a non-uniform power distribution at the center of the chip! In the worst case, the power dop is equal to 13 mV83                                                                                                                                                                 |

| Figure 6.11. 2D representation of the power drop over the chip for the one-side biasing (left plot) and the two-sided biasing (right plot)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

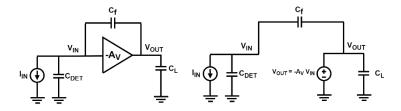

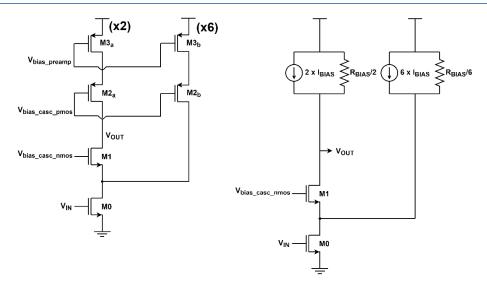

| Figure 6.12. CSA core amplifier called telescopic cascode amplifier (left) and its simplified model (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

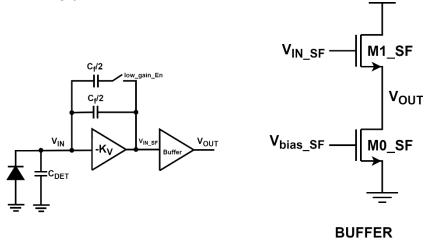

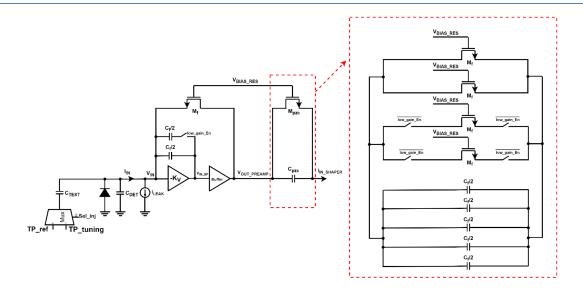

| Figure 6.13. Block diagram of the CSA (left) and its buffer (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

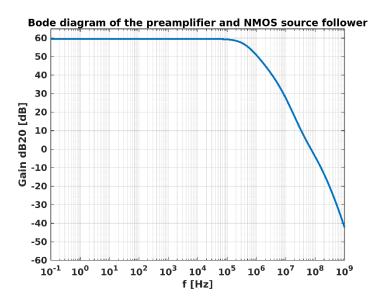

| Figure 6.14. Bode diagram of the core amplifier followed by the NMOS type source follower86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

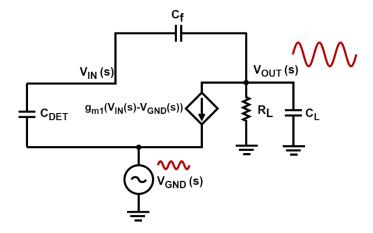

| Figure 6.15. Small-signal model for the analysis for the ground supply rejection in the front-end. 87                                                                                                                                                                                                   |

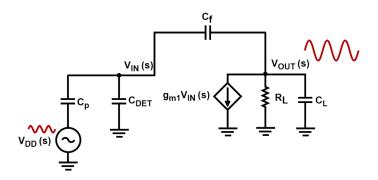

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.16. Small-signal model for the analysis for the power supply rejection in the front-end in the case of having some parasitic capacitances referenced to the power supply VDD87                                                                                                                 |

| Figure 6.17. Block diagram of the CSA with the feedback reset MOSFET                                                                                                                                                                                                                                    |

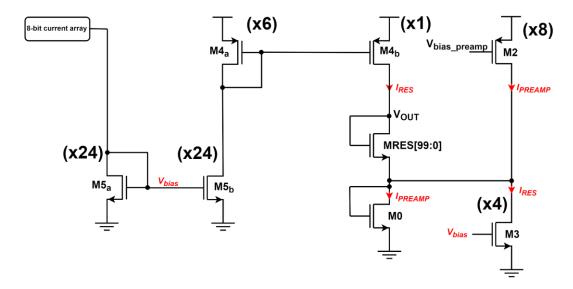

| Figure 6.18. Scheme of the replica circuit to bias the reset feedback element in the analog pixels.89                                                                                                                                                                                                   |

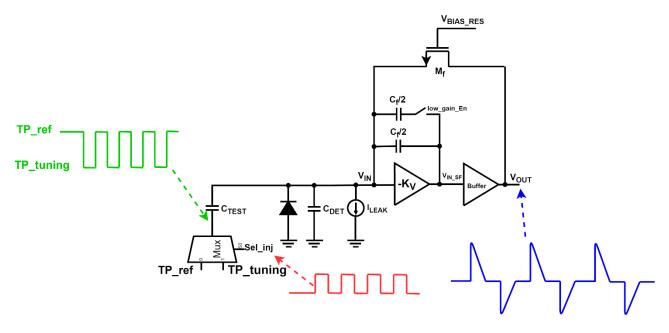

| Figure 6.19. Test pulse circuit to test the linearity of the front-end after fabrication90                                                                                                                                                                                                              |

| Figure 6.20. Simplified block diagram of the CSA with a pole-zero cancellation network90                                                                                                                                                                                                                |

| Figure 6.21. Scheme of the CSA followed by a pole-zero cancellation circuit. The equivalent resistance provided by $M_{PZC}$ is twice lower than with $M_f$ when low_gain_En = 1 and four times lower when low_gain_En=092                                                                              |

| Figure 6.22. CSA response for a 60 keV input photon versus DC leakage current92                                                                                                                                                                                                                         |

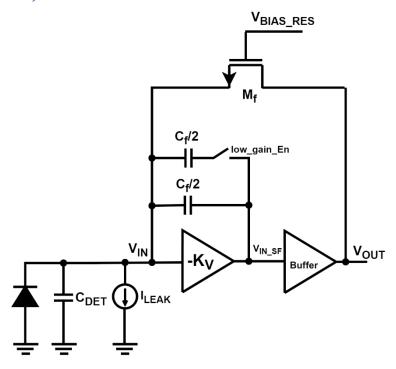

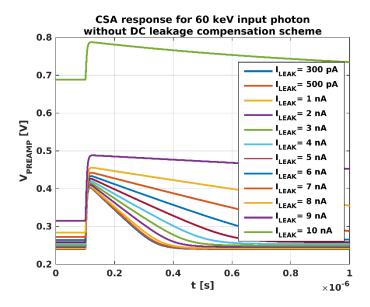

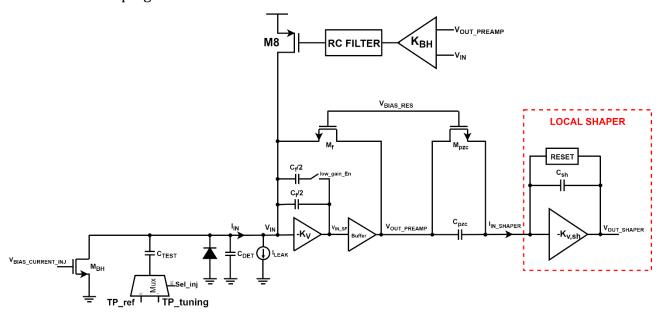

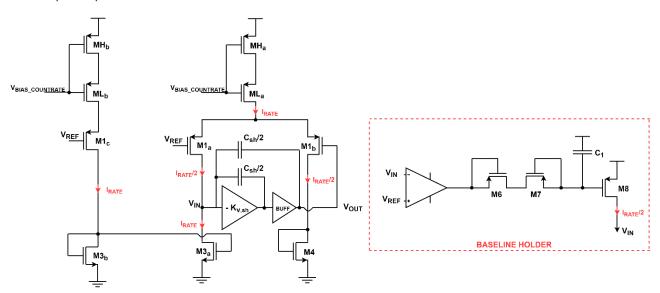

| Figure 6.23. Scheme of the baseline holder for compensating the DC leakage current coming to the sensor.                                                                                                                                                                                                |

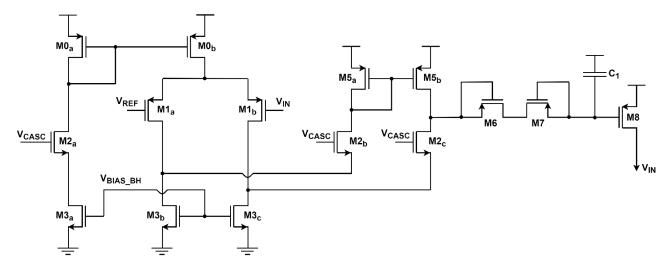

| Figure 6.24. Transistor implementation of the baseline holder94                                                                                                                                                                                                                                         |

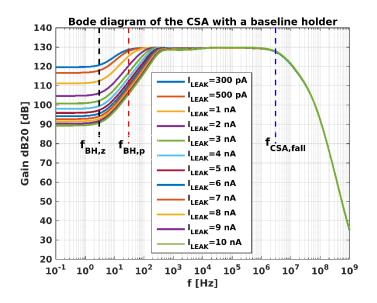

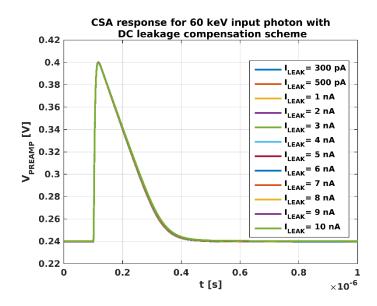

| Figure 6.25. Bode diagram of the CSA with the baseline holder circuit for leakage current going from 300 pA to 10 nA95                                                                                                                                                                                  |

| Figure 6.26. The response of a CSA has a DC leakage compensation circuit for a 60 keV input photon and a varying leakage current from 300 pA to 10 nA95                                                                                                                                                 |

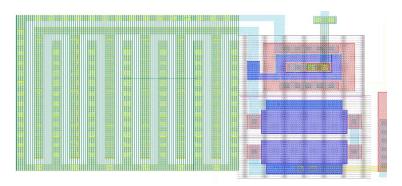

| Figure 6.27. Layout view of the sensitive components in the baseline holder. M6, M7, and M8 are drawn as thick oxide MOSFETs to suppress the gate leakage current. M8 is implemented as ELT to minimizing its drain leakage. The green block is drawn in a 'comb shaped' providing 20 fF capacitances96 |

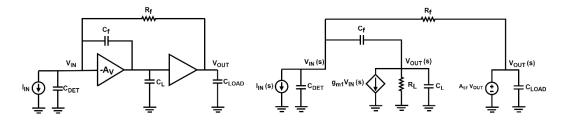

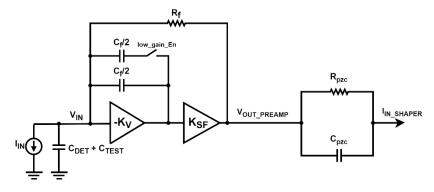

| Figure 6.28. Block diagram of the CSA followed by a pole-zero cancellation circuit then fed to a pulse-shaping amplifier                                                                                                                                                                                |

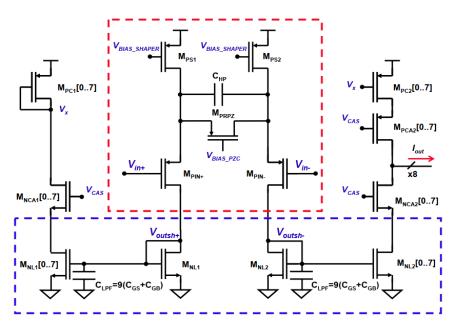

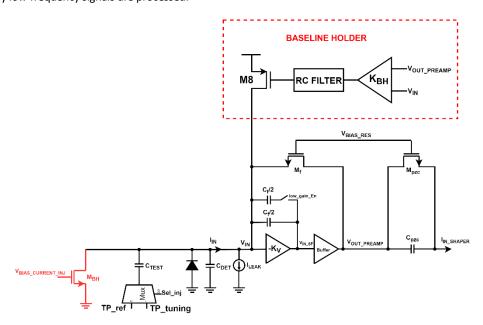

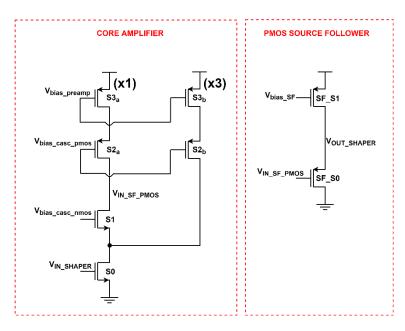

| Figure 6.29. Transistor implementation of the core amplifier for the shaper in the left plot and the PMOS type source follower in the right plot97                                                                                                                                                      |

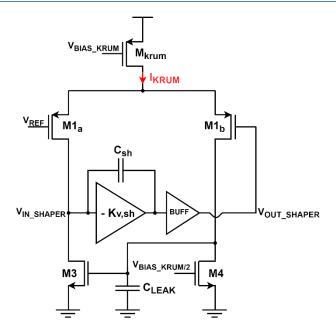

| Figure 6.30. Krummenacher amplifier topology used in Medipix/Timepix front-end pixels98                                                                                                                                                                                                                 |

| Figure 6.31. Schematic of the new shaper. A baseline holder compensates for all residue DC leakage current at the shaper's input                                                                                                                                                                        |

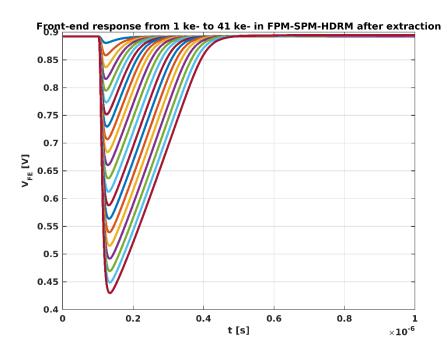

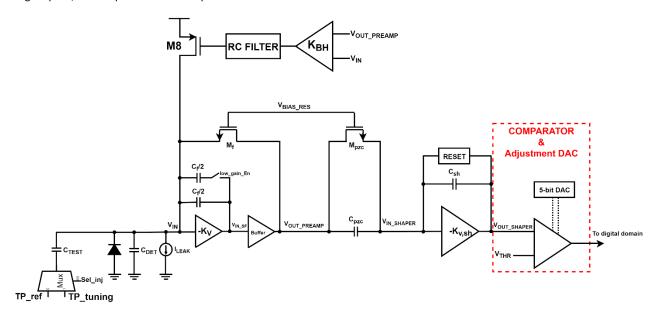

| Figure 6.32. Front-end response from 1 ke <sup>-</sup> to 41 ke <sup>-</sup> in FPM-SPM-HDRM after parasitic extraction.101                                                                                                                                                                             |

| Figure 6.33. Front-end response from 1 ke <sup>-</sup> to 21 ke <sup>-</sup> in FPM-SPM-LGM after parasitic extraction.101                                                                                                                                                                              |

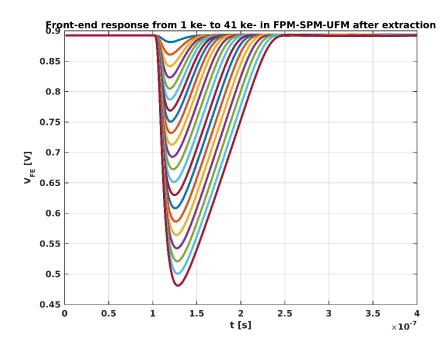

| Figure 6.34. Front-end response from 1 ke <sup>-</sup> to 41 ke <sup>-</sup> in FPM-SPM-UFM after parasitic extraction.102                                                                                                                                                                              |

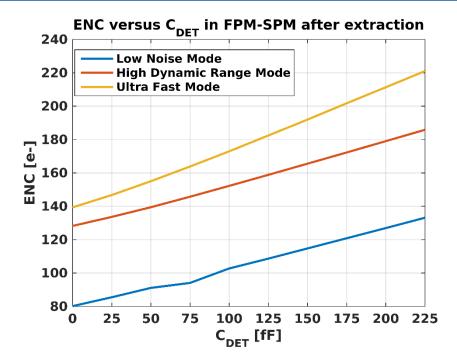

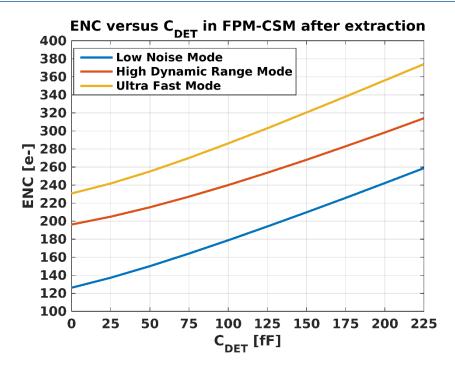

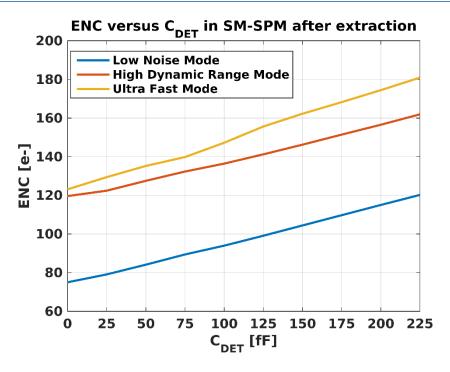

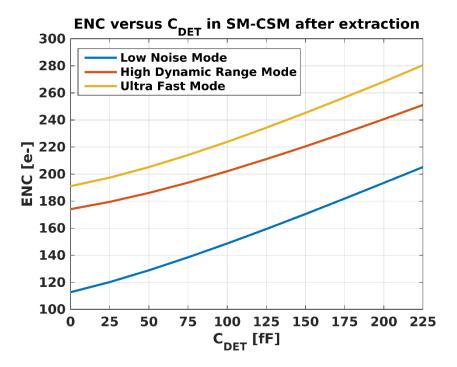

| Figure 6.35. Equivalent Noise Charge versus detector capacitance for the three analog configuration modes                                                                                                                                                                                               |

| Figure 6.36. Block diagram of the two stages amplifiers fed to a comparator. A 5-bit local tuning DAC enables threshold adjustment                                                                                                                                                                      |

| Figure 6.37. Scheme of the comparator                                                                                                                                                                                                                                                                   |

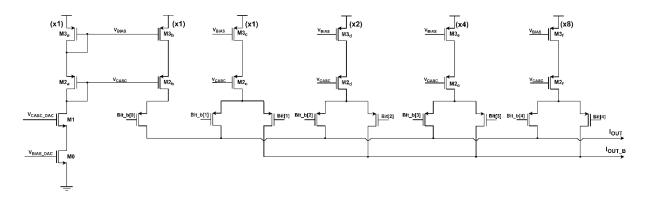

| Figure 6.38. Schematic of the 5-bit DAC used for the threshold calibration105                                                                                                                                                                                                                           |

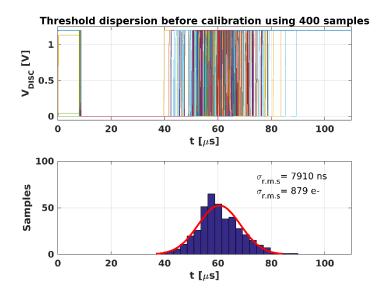

| Figure 6.39. Simulated threshold dispersion of the front-end without threshold tuning. The offset mismatch is 879 e-r.m.s. in LNM                                                                                                                                                                       |

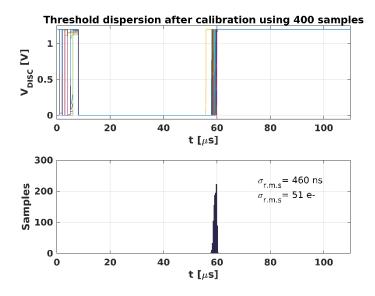

| Figure 6.40. Simulated threshold dispersion of the front-end after threshold calibration using 5-bit tuning DAC. The offset mismatch is 51 e <sup>-</sup> r.m.s. in LNM.                                                                                                                                |

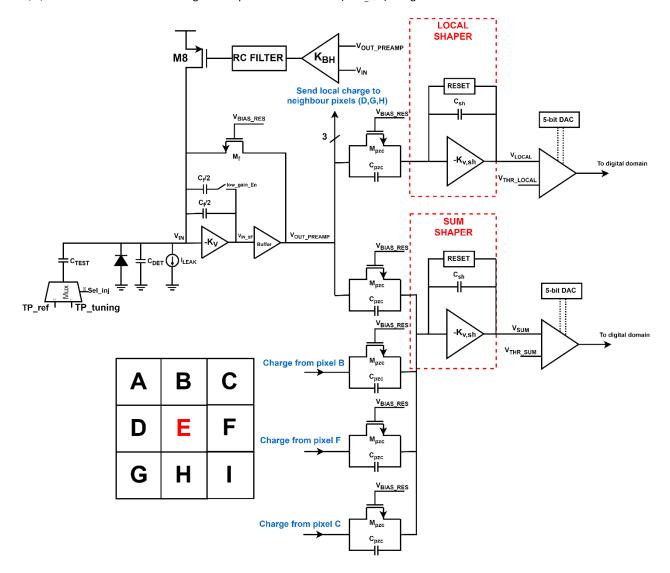

| Figure 6.41. The architecture of the analog front-end configured in Charge Summing Mode 107                                                                                                                                                                                                             |

| Figure 6.43. Configuration of the analog pixel in FPM-SPM                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.44. Configuration of the analog pixel in FPM-CSM                                                                                                                                                                                              |

| Figure 6.45. Configuration of the analog pixel in SM-SPM                                                                                                                                                                                               |

| Figure 6.46. Configuration of the analog pixel in SM-CSM                                                                                                                                                                                               |

| Figure 6.47. ENC versus detector capacitance in SM-SPM for the three analog configuration modes.112                                                                                                                                                    |

| Figure 6.48. ENC versus detector capacitance in SM-CSM for the three analog configuration modes.112                                                                                                                                                    |

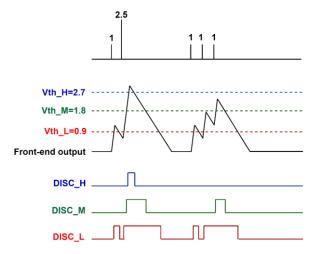

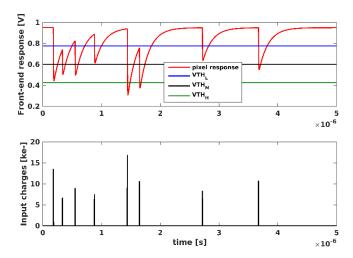

| Figure 6.49. Illustration of pile-up pulses in the front-end with multi-thresholds                                                                                                                                                                     |

| Figure 6.50. Model of the front-end response for a polychromatic input source having a Poisson distribution for the time arrival                                                                                                                       |

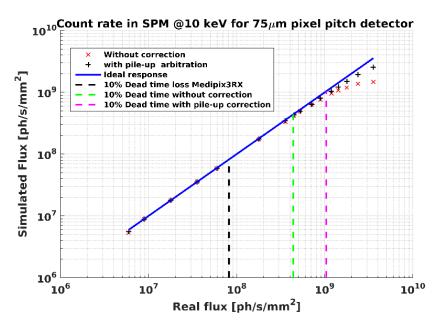

| Figure 6.51. Simulated count-rate capability of the Medipix4 with and without pile-up correction for 10 keV input monochromatic source and threshold at 7 keV. The 10% dead-time loss is improved by a factor 2 when activating the pile-up correction |

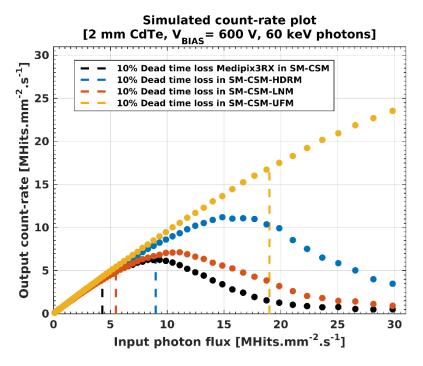

| Figure 6.52. The count-rate capability of the chip in SM-CSM for a 60 keV input source and a 2 mm think                                                                                                                                                |

| CdTe sensor (courtesy to A. Pulli)                                                                                                                                                                                                                     |

| CdTe sensor (courtesy to A. Pulli)                                                                                                                                                                                                                     |

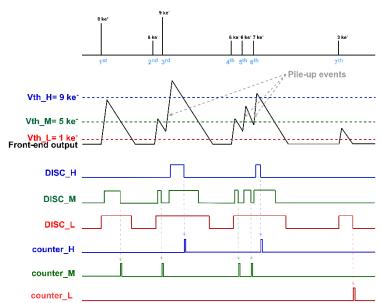

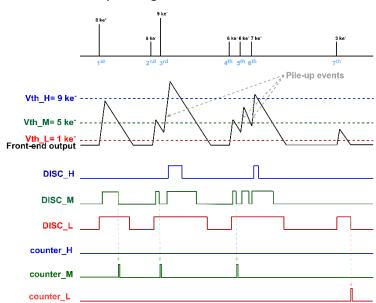

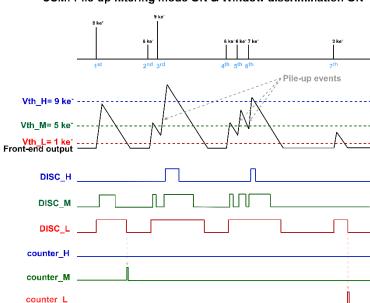

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and                                                                                                                                              |

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and Window Discrimination mode OFF                                                                                                               |

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and Window Discrimination mode OFF                                                                                                               |

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and Window Discrimination mode OFF                                                                                                               |

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and Window Discrimination mode OFF                                                                                                               |

| Figure 6.53. Working principle of the digital pixel configured in SPM with Pile-up Filtering mode OFF and Window Discrimination mode OFF                                                                                                               |

## List of Tables

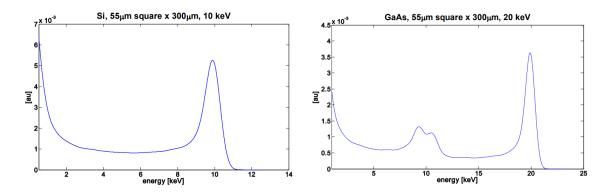

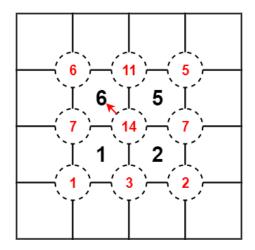

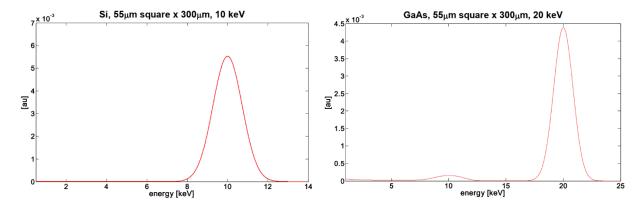

| Table 2-1: fluorescence properties of some semiconductor detector materials [10]. The ato K and L –edges are indicated along the $K_{\alpha 1}$ and $K_{\alpha 2}$ energies of the generated fluorescence pld $_{\alpha 1}$ give the mean free path of those generated photons. $\eta$ [%] is the fluorescence yield | hotons. $d_{\alpha 1}$ and |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Table 3-1: Physical properties of semiconductors frequently used for radiation detection [12]                                                                                                                                                                                                                        | <b>2] at 300 K.</b> 25     |

| Table 3-2: Electron and hole trapping length for different semiconductor materials undelectrical field. The probability of the charge trapping/recombination is given for a 1 mm the                                                                                                                                 | · ·                        |

| Table 3-3: Summary of the contributions of serial and parallel noises expressed as Equivaler (ENC)                                                                                                                                                                                                                   |                            |

| Table 4-1: Summary of the performances of the Medipix1 chip                                                                                                                                                                                                                                                          | 47                         |

| Table 4-2: Summary of a few applications using Medipix2 as readout. The size of the detector material is indicated                                                                                                                                                                                                   |                            |

| Table 4-3: Summary of the measured performances of Medipix2 chip.                                                                                                                                                                                                                                                    | 50                         |

| Table 4-4: Performances of the Medipix3RX chip.                                                                                                                                                                                                                                                                      | 53                         |

| Table 4-5: Some applications using the Medipix3 readout                                                                                                                                                                                                                                                              | 53                         |

| Table 4-6: Specifications for the design of the Medipix4 ASIC.                                                                                                                                                                                                                                                       | 59                         |

| Table 5-1: Some applications using Timepix readout. The size of the detector and the mater sensor are highlighted                                                                                                                                                                                                    |                            |

| Table 5-2: Some applications using Timepix3 readout. The size of the detector and the mater sensor are highlighted                                                                                                                                                                                                   |                            |

| Table 5-3: Simulated performances of the Rail-to-Rail buffer after post-layout extraction                                                                                                                                                                                                                            | 66                         |

| Table 5-4: List of voltage and current DACs in the periphery of Timepix2.                                                                                                                                                                                                                                            | 66                         |

| Table 5-5: Simulated performances of the slow and fast RtR buffer after post-layout extract                                                                                                                                                                                                                          | ion73                      |

| Table 5-6: Main features of the Timepix family of chips.                                                                                                                                                                                                                                                             | 74                         |

| Table 6-1: DAC response value versus the digital code of threshold adjustment DAC                                                                                                                                                                                                                                    | 105                        |

| Table 6-2: Mode of operations in Medipix4. The charge collection area can be increased wh is used with high-Z materials. The number of thresholds is indicated in the last column                                                                                                                                    |                            |

| Table 6-3: Summary of simulated performances of Medipix4 for the different modes of of measured performances of the Medipix3RX are shown in the first column as reference                                                                                                                                            | •                          |

# Chapter 1 Introduction

The idea of using pixel detectors to identify the nature of incident particles by detecting their characteristic patterns in the pixel matrix is proposed in [1]. In 1988, a CERN team design introduced hybrid pixelated devices in which a sensor matrix is connected to a readout chip on different substrates. The hybrid pixel technology became a candidate for particle tracking along with the monolithic pixel detectors [2], which were developed under the RD19 collaboration at CERN. The first pixelated chip with 9 x 12 pixels, manufactured in a 3  $\mu$ m CMOS process, was designed at CERN in collaboration with the microelectronics group at EPFL (the designers are Enz, Krummenacher, and Vittoz), and with the support of the particle physics group at the ETHZ and the Swiss National Fund [2]. The first measurements with wire-bonded instead of external connections between the sensor and the readout pixels are published in [3]. Using bump bonded connections allowed exact matching of the readout matrix to the sensor matrix.

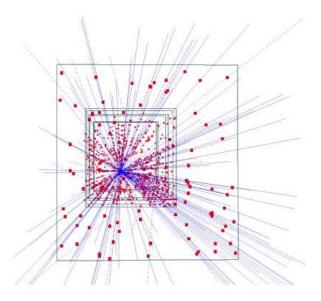

Many chips followed the hybrid pixel design and allowed the collaboration to gain experience in designing such detectors. The WA97 heavy-ion experiment implemented a detector called Omega2, with a large sensitive area of 13 x 63 pixels and with a pixel dimension of 75 x 500  $\mu$ m<sup>2</sup>. Total area coverage of 5 cm<sup>2</sup> was obtained by connecting six ladders of 6 chips. Figure 1.1 shows the tracking capability of this hybrid pixel detector with an excellent spatial resolution. The figure shows that every dot is associated with a track. This experiment demonstrated the unique features of hybrid pixel detectors: the ability to take noise hit free tracks at a high rate.

Figure 1.1. A fixed target Pb-Pb event reconstruction with 153 tracks, using a seven-plane pixel telescope in WA97. Each 'Window' represents 5 x 5 cm², having 72000 pixels. The pixel dimension is 75 x 500  $\mu$ m². The tracks have been reconstructed with a trigger precision of 1  $\mu$ s and a radiation tolerance of around 30 kRad. The red dots on the figure represents the detected hits in the silicon detectors [4].

The Medipix collaborations have been created to transfer the technology of hybrid pixel detectors, from the original use in High Energy Physics (HEP) applications, into other fields of science like medical imaging, synchrotron applications, material analysis using X-ray sources, electron microscopy, and others [5].