Thèse n° 9596

# EPFL

# Exploring negative capacitance and neuromorphic devices based on CMOS-compatible ferroelectric HfO<sub>2</sub>

Présentée le 11 novembre 2022

à la Faculté des sciences et techniques de l'ingénieur Laboratoire des dispositifs nanoélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

## Carlotta GASTALDI

Acceptée sur proposition du jury

Prof. L. G. Villanueva Torrijo, président du jury Prof. M. A. Ionescu, Dr I. Stolichnov, directeurs de thèse Prof. S. Salahuddin, rapporteur Prof. T. Mikolajick, rapporteur Prof. P. Muralt, rapporteur

I can live with doubt and uncertainty and not knowing. I think it's much more interesting to live not knowing than to have answers which might be wrong.

-Richard Feynman

# Acknowledgements

The doctorate years were a challenging personal and professional journey. Although this was a solitary work in many ways, it was only possible through the collaboration and support of many friends and colleagues around me. Here I could write a whole other manuscript just to mention all of them.

Firstly, I want to thank my supervisor, Prof. Adrian Mihai Ionescu, for choosing me for this project and giving me the chance to challenge myself. During these four years, he had incited me to push forward and, at the same time, gave me the freedom to follow my scientific investigation. Being part of this lab gave me the opportunity to access state-of-the-art equipment and be surrounded by a cohesive teem. Among them, I foremost would like to acknowledge my co-supervisor Dr. Igor Stolichnov, which introduced me not just to the world of ferroelectrics, but also to mirror-less cameras. Together we worked on the 3eFerro project: he was always ready to listen to my latest result and offer insightful comments. Then I would like to thank my Ph.D. jury president, Prof. Guillermo Villanueva, and the jury members, Prof. Paul Muralt, Prof. Thomas Mikolajick, and Prof. Sayeef Salahuddin, who despite their packed schedules, found time to read my work and provided valuable feedbacks and comments.

I thank all my colleagues not just for their collaboration, but also for all the fun moments in the lab and outside work. Among the Nanolab members, I would like to thank Francesco, Ali, and Eamon, who transmitted to me their knowledge, introduced me to the lab and guided me in the first months of my Ph.D. A big thanks go to Matteo, he is a great co-worker and an inspiring person. My thanks go also to Niccolò, Emanuele, and Chiara, who introduced me to the Lausanne life. Together with several other friends (Teodor, Giulia, Georgi, etc.), we shared numerous dinners, ski days, board games, and parties. The colleague with whom I probably spent most of the time in the lab and outside is Luca, he started right after me and, since then, we have been always there for each other, thank you. During these years, I had the pleasure of sharing the office with Fatemeh and Sadegh, always available to help, great Farsi teachers (together with AliG), and excellent dancers (from Rock and Roll to traditional Perisian dances). In these last two years, several Nanolab members arrived, among which Fabio, Felix, and Lotte, with whom I quickly bonded. In conclusion, thanks to all the Nanolab members old and new, whom I did not mention (Taha, Maneesha, Hung Wei, etc.), it was great working and spending time with you all.

#### **Chapter 0**

Outside of work, I met Nadia, a unique companion for crazy experiences and adventurous holidays, together with a great group of buddies (Marco, Vale, Alexa, JP, etc.). Then I spent time also with Francesco and Eleonora during which we played board games and had some memorable parties. I have also great memories with Mariazel, she was a flatmate and now also a dear friend, and thanks to her I also met a splendid couple, Cosimo and Rachele. I thank all my Lausanne friends, also the ones not mentioned (Francesca Helen Pavo etc.), for your support and for all the great moments spent together.

Finally, I am immensely grateful to my family, in particular to my mother and father, who always believed in me and encourage me. A special mention goes also to Zia Mariuccia who is a great model and will always be part of me. A big thanks go, also to Brenda, Chicco, Irene, and Alessia, who, despite the distance, have always been close to me. And lastly, words cannot express my gratitude to Jacopo, with whom I shared these last four years. He supported me in the most challenging moment giving me strength and cheering me up, with Rock and Roll dances, delicious dinners, and picnics along the lake.

Lausanne, 11 November 2022

Carlotta Gastaldi

## Abstract

Ferroelectric materials are explored for numerous applications thanks to their properties associated with electrically switchable spontaneous polarization. Perovskites are an established class of ferroelectrics used for sensors and actuators. However, they present limitations if integrated into microelectronics since they are neither CMOS compatible nor easily scalable. The game-changing solution came from the new family of ferroelectric materials based on HfO<sub>2</sub> that emerged within the last decade, which shows integrability in scaled CMOS devices.

HfO<sub>2</sub>-based ferroelectrics are considered a rising candidate for different applications, among which neuromorphic devices and negative capacitance (NC) logic switches. Neuromorphic devices rely on the gradual polarization switching capability, which can reproduce synaptic plasticity. By mimicking the analog operation of the human brain, neuromorphic computing is expected to be more energy-efficient than the digital Von Neumann architecture. On the other hand, in logic switches, hysteresis is usually avoided, and a steep subthreshold swing is desired. For this purpose, negative capacitance field-effect transistors (NC-FETs) show a strong promise of overcoming the thermionic Boltzmann constraint of 60 mV/dec and continuing CMOS scaling. NC-FETs rely on exploiting the NC region of the polarization-electric field curve predicted by the Landau-Ginzburg-Devonshire (LGD) model.

This thesis aims to study the NC effect and its interplay with the polarization switching mechanisms of one of the best-known members of  $HfO_2$ -based ferroelectrics, the Si-doped  $HfO_2$ (Si:HfO<sub>2</sub>), and then to integrate it onto electronic devices. Temperature-dependent switching in Si:HfO<sub>2</sub> capacitors were studied, and the results were used to calibrate the LGD model, confirming the intrinsic switching mechanism experimentally. Then Si:HfO<sub>2</sub> was integrated into gate stack transistors to verify its functionality. In this framework, two structures were studied, one with an inner metal gate (IG) between the insulator and ferroelectric and one without it. Thanks to nanosecond-range pulse measurement, the S-shaped curve, predicted by the LGD model, was extracted, and the NC region was observed.

Following the previous study, the two gate stacks were implemented in a junctionless transistor (JLFET) platform with a Si channel of 12 nm, resulting in a device with Ion/Ioff of 6 orders of magnitude. The ferroelectric-JLFET (Fe-JLFET) without IG presented a hysteresis-free transfer characteristic and an improved subthreshold swing of 35% over 1.3 decades of drain current with pulse gate voltages compared to DC. On the contrary, the Fe-JLFET with IG showed a ferroelectric hysteretic behavior, and the Si:HfO<sub>2</sub> gradual switching is exploited to mimic the

synaptic plasticity. Additionally, the back-gate voltage biasing is used to tune the synaptic weight by more than 400x. Overall, this Ph.D. work confirms the potential of Fe-JLFET for both neuromorphic synapses and NC logic devices and highlights the requirements and limits of operation by studying how HfO<sub>2</sub>-based ferroelectric properties evolve from the capacitor to integration into the gate stack.

**Keywords**: ferroelectricity, HfO<sub>2</sub>, intrinsic switching, Landau-Ginzburg-Devonshire (LGD) theory, negative capacitance (NC), neuromorphic synapses, junctionless transistor (JLFET), ferroelectric transistor (Fe-FET), Silicon-On-Insulator (SOI) wafer.

## Sommario

I materiali ferroelettrici sono studiati per numerose applicazioni grazie alle loro proprietà, associate alla polarizzazione spontanea commutabile elettricamente. Le perovskiti sono una classe consolidata di materiali ferroelettrici utilizzati per sensori e attuatori. Tuttavia, presentano limitazioni se integrati nella microelettronica poiché non sono né compatibili con circuiti CMOS né facilmente scalabili. La soluzione rivoluzionaria è arrivata dalla nuova famiglia di materiale ferroelettrico a base di HfO<sub>2</sub> emersa nell'ultimo decennio, che mostra l'integrabilità nei dispositivi CMOS in scala.

I ferroelettrici a base di HfO<sub>2</sub> sono considerati un candidato in ascesa per diverse applicazioni, tra cui dispositivi neuromorfici e interruttori logici a capacità negativa (NC). I dispositivi neuromorfici si basano sulla capacità di commutazione graduale della polarizzazione, che può riprodurre la plasticità sinaptica. Imitando il funzionamento analogico del calcolo neuromorfico del cervello umano, ci si aspetta che questi dispositivi siano più efficienti dal punto di vista energetico rispetto all'architettura digitale di Von Neumann. Negli interruttori logici, l'isteresi viene solitamente evitata e si desidera meccaanismo di sepgnimento e accensione a basso consumo energetico. A tal fine, i transistor a effetto di campo a capacità negativa (NC-FET) mostrano una forte promessa di superare il vincolo termoionico di Boltzmann di 60 mV/dec e di continuare lo scaling della tecnologia CMOS. Gli NC-FETs si basano sullo sfruttamento della regione NC della curva di polarizzazione-campo elettrico prevista dal modello Landau-Ginzburg-Devonshire (LGD).

Questa tesi si propone di studiare l'effetto NC e la sua interazione con i meccanismi di commutazione della polarizzazione di uno dei più importanti componenti dei ferroelettrici a base di HfO<sub>2</sub>, l'HfO<sub>2</sub> drogato con Si (Si:HfO<sub>2</sub>), per poi integrarlo in dispositivi elettronici. In primo luogo i condensatori con Si:HfO<sub>2</sub> sono stati misurati in un ampio intervallo di temperature e i risultati sono stati utilizzati per calibrare il modello LGD, confermando sperimentalmente il meccanismo di commutazione intrinseco. Quindi Si:HfO<sub>2</sub> è stato integrato nei gate del transistore per verificarne la funzionalità. In questo lavoro sono state studiate due strutture, una con un gate metallico interno (IG) situato tra l'isolante e il ferroelettrico e una struttura senza IG. Grazie alle misure con impulsi di nanosecondi, è stata estratta la curva a forma di S, prevista dal modello LGD, ed è stata osservata la regione NC.

In seguito allo studio precedente, i due stack gate sono stati integrati in una piattaforma

di transistor senza giunzioni (JLFET) con un canale Si di 10 nm e con Ion/Ioff di 6 ordini di grandezza. Il JLFET ferroelettrico (Fe-JLFET) senza IG ha una transcaratteristica priva di isteresi e una pendenza di sottosoglia migliorata del 35% con tensioni di gate a impulsi rispetto che a corrente continua. Al contrario, il Fe-JLFET con IG ha mostrato un comportamento isteretico ferroelettrico e la commutazione graduale Si:HfO<sub>2</sub> viene sfruttata per imitare la plasticità sinaptica. Inoltre, la tensione di back-gate viene utilizzato per regolare il peso sinaptico di oltre 400 volte.

Nel complesso, questo lavoro di dottorato conferma il potenziale del Fe-JLFET sia per le sinapsi neuromorfiche che per i dispositivi logici NC e mette in evidenza i requisiti e i limiti di funzionamento studiando come le proprietà ferroelettriche a base di HfO<sub>2</sub> si evolvono dal condensatore all'integrazione nel gate stack.

**Parole chiave:** ferroelettricità, HfO<sub>2</sub>, commutazione intrinseca, Landau-Ginzburg-Devonshire (LGD), capacità negativa (NC), sinapsi neuromorfiche, transistor senza giunzioni (JL) (JLFET), transistor ferroelettrico (Fe-FET), Silicon-On-Insulator (SOI) wafer. italian

# List of Figures

| 1.1  | Cover of "Crystal Triode", an electronic magazine, showing Bardeen, Brattain,                 |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | and Shockley in the Bells Lab where they built the first transistor. (Adapted from            |    |

|      | [4])                                                                                          | 2  |

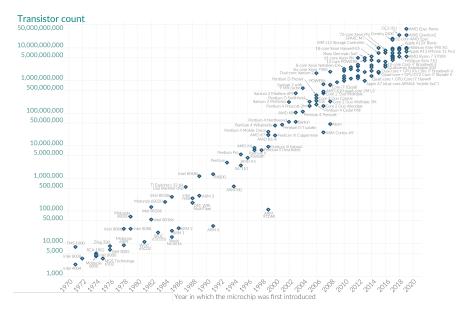

| 1.2  | Exponential growth projection of transistor count in integrated circuits plotted              |    |

|      | vs the year of introduction (taken from [6])                                                  | 3  |

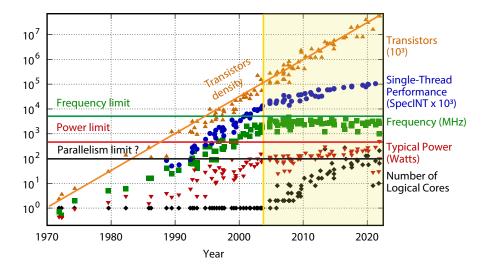

| 1.3  | Microprocessor scaling trends throughout 52, highlighting the end of Dennard                  |    |

|      | scaling after the 2000s (adapted from [11])                                                   | 4  |

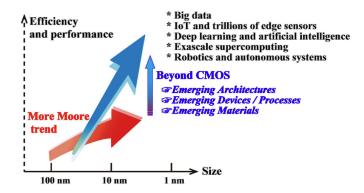

| 1.4  | Schematic showing the objective of Beyond CMOS vs More Moore approach                         |    |

|      | (taken from [18])                                                                             | 4  |

| 1.6  | Map of FET design space (adapted from [21]).                                                  | 6  |

| 1.8  | Schematic of a synaptic transmission mechanism showing a firing pre-synaptic                  |    |

|      | neuron releasing neurotransmitters binding to receptors of the post-synaptic                  |    |

|      | neuron                                                                                        | 8  |

| 1.9  | Venn diagram showing the relationship between dielectric, piezoelectric, pyro-                |    |

|      | electric, and ferroelectric materials.                                                        | 10 |

| 1.10 | (a) Displacement current vs. electric field and (b) hysteresis loop (P-E) derived             |    |

|      | from it (adapted from [48]).                                                                  | 11 |

| 1.11 | Schematic of the energy landscape and polarization behaviour in the ferroelec-                |    |

|      | tric phase $(T < T_C)$ and in the paraelectric $(T > T_C)$ .                                  | 12 |

| 1.12 | Schematic of spontaneous polarization temperature dependence in case of first                 |    |

|      | order (a) and second order (b) phase transition.                                              | 13 |

| 1.14 | Polarization-Voltage (black) and Dielectric constant-Voltage (red) characteris-               |    |

|      | tics of a series of capped $HfO_2$ capacitors showing a gradual transition from               |    |

|      | ferroelectric to anti-ferroelectric behavior with the increase of the Si doping               |    |

|      | (reproduced from [46])                                                                        | 15 |

| 1.15 | Qualitative schematic of the phase transitions of HfO <sub>2</sub> and its trend with anneal- |    |

|      | ing, doping, crystallization and film thickness (reproduced from [80]).                       | 16 |

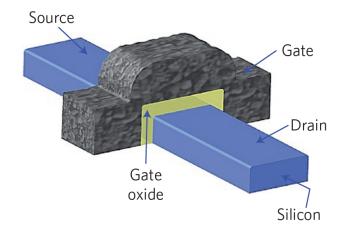

| 1.16 | Schematic of a JLFET with a highly uniform doped silicon channel and no drain                 |    |

|      | and source implantation. Reproduced from [85]                                                 | 17 |

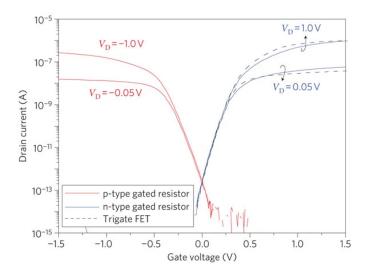

| 1.17 | Transfer characteristic taken of a JLFET of n-type, p-type compared to a classical            |    |

|      | trigate MOSFFET n-type. Reproduced from [85].                                                 | 17 |

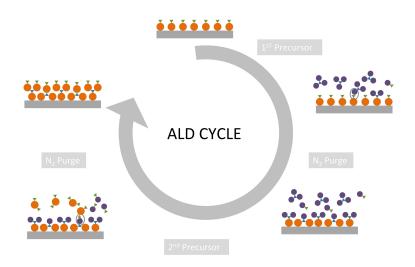

| 2.1  | Schematic of an ALD cycle (reproduced from [87])                                              | 22 |

| 2.1  |                                                                                               | 22 |

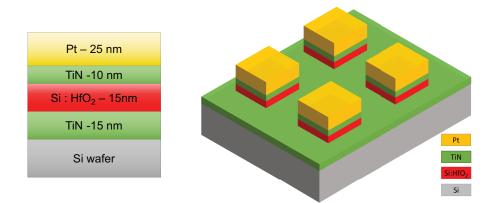

| 2.2  | Schematic of the chip's capacitor cross-section and 3D view.                                  | 23 |

|------|-----------------------------------------------------------------------------------------------|----|

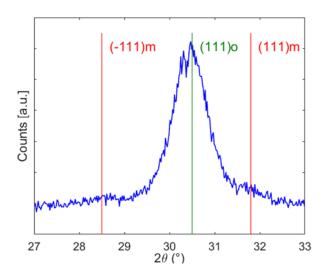

| 2.4  | GI-XRD pattern of ferroelectric capacitor showing the ferroelectric orthorhombic              |    |

|      | peaks at 30.4°                                                                                | 26 |

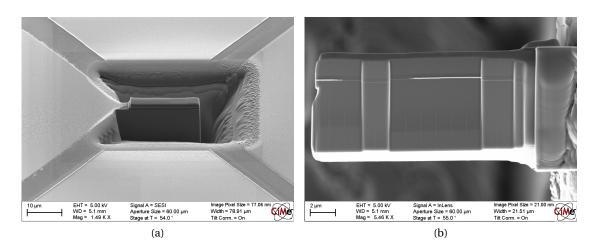

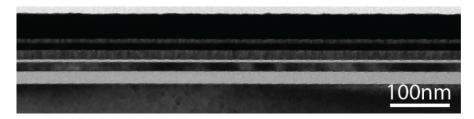

| 2.5  | Cross-section STEM of the capacitor structure.                                                | 26 |

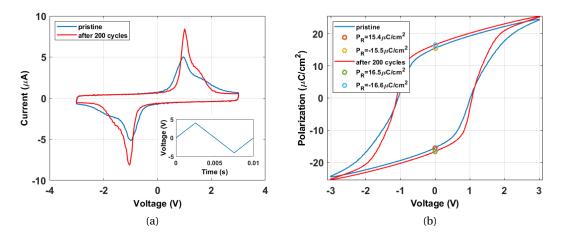

| 2.6  | IV curve (a) and PV loop (b) of MFM cap before and after wake-up procedure                    |    |

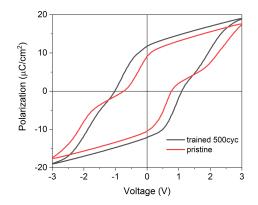

|      | measured at a frequency of 500 Hz (see inset).                                                | 27 |

| 2.7  | PV hysteresis before and after wake-up (500 cycles).                                          | 28 |

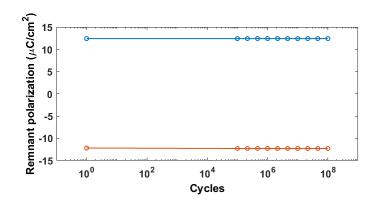

| 2.8  | Endurance test performed wake-up procedure (200 cycles)                                       | 29 |

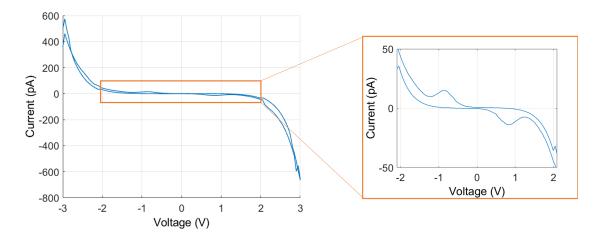

| 2.9  | IV plot with an insert highlighting the switching current peaks.                              | 29 |

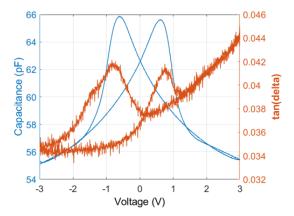

| 2.10 | (a) Capacitance–voltage trend. (b) Corresponding loss tangent measurement.                    | 30 |

| 2.11 | Schematic showing the basic principles of AFM measurement system (repro-                      |    |

|      | duced from [90])                                                                              | 31 |

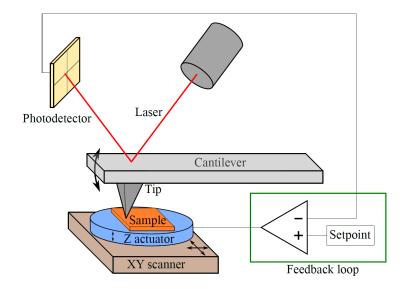

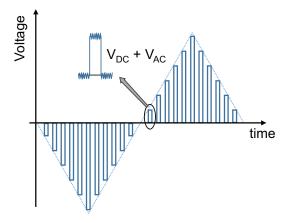

| 2.12 | Schematic of the voltage applied in time during a PFM loop in point spectroscopy              | 33 |

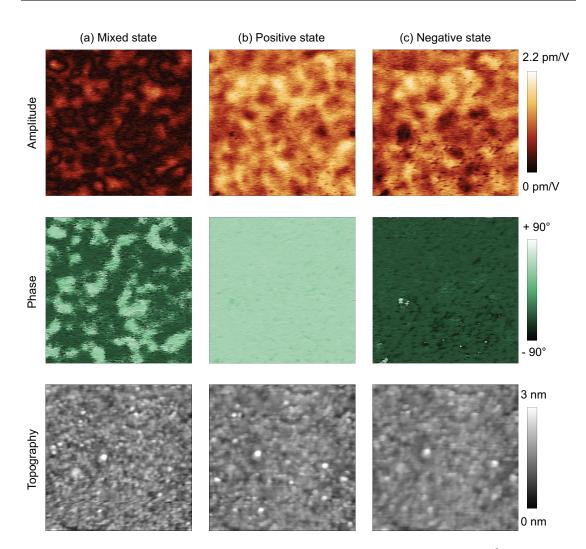

| 2.13 | PFM maps of phase and amplitude of the same device area (1 $um^2$ ) in different              |    |

|      | polarization conditions: (a) mixed-state phase and amplitude (after the applica-              |    |

|      | tion of -1 V), (b) positive state phase and amplitude (after the application of +4            |    |

|      | V), and (c) negative state phase and amplitude (after the application of -4 V). $$ .          | 34 |

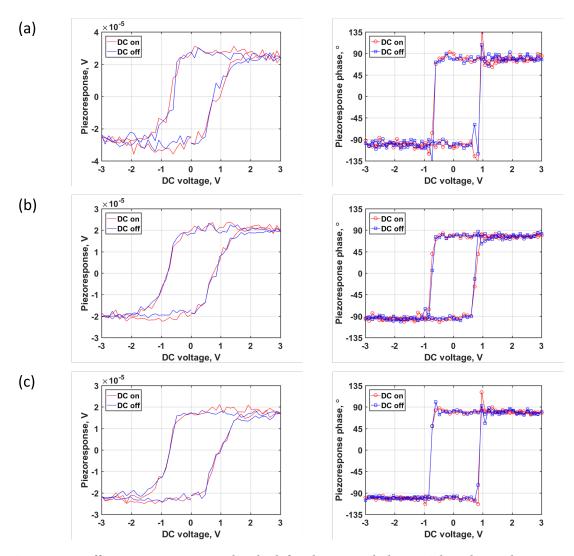

| 2.14 | Off-resonance PFM amplitude (left column) and phase (right column) loops                      |    |

|      | on 15nm Si:HfO <sub>2</sub> capacitors measured at 12 (a), 92 (b) and 230 (c) kHz with AC     |    |

|      | voltage of 500 mV                                                                             | 36 |

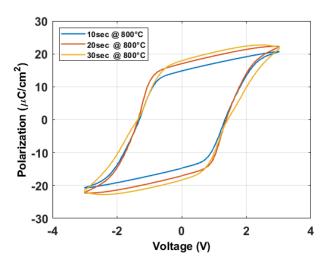

| 2.15 | PV loop taken at 1kHz of MFM capacitor under three different annealing anneal-                |    |

|      | 0                                                                                             | 38 |

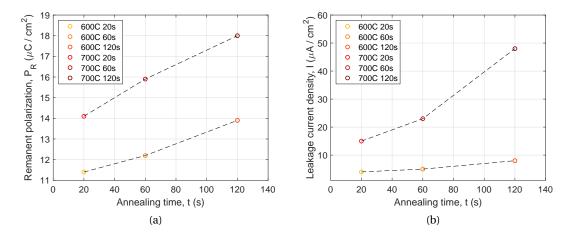

| 2.16 | Plot of remanent polarization and leakage current density versus annealing time               |    |

|      | at two temperatures 700 °C and 600 °C.                                                        | 38 |

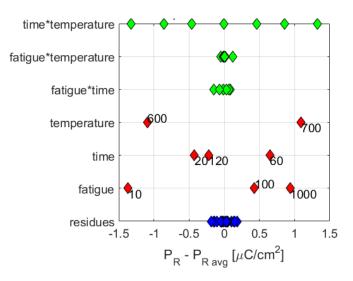

| 2.17 | Dot plot of the effects of the factor (w, t, T), the interaction (t*T w*T w*t) and            |    |

|      | residues ( $\epsilon$ )                                                                       | 39 |

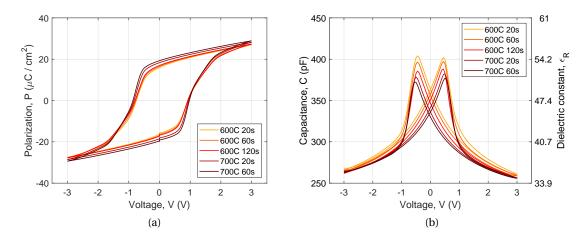

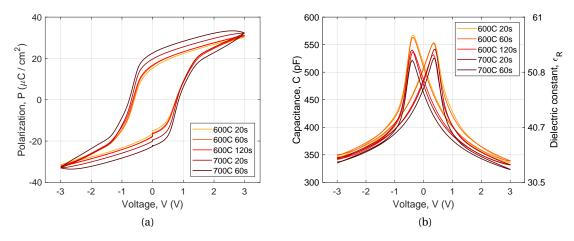

| 2.18 | Effect of different thermal budget on ferroelectric properties of 12 nm Si:HfO <sub>2</sub> : |    |

|      | P-V (a), C-V and $\epsilon_R$ -V (b) curves.                                                  | 41 |

| 2.19 | Effect of different thermal budget on ferroelectric properties of 9 nm Si:HfO <sub>2</sub> :  |    |

|      | P-V (a), C-V and $\epsilon_R$ -V (b) curves.                                                  | 42 |

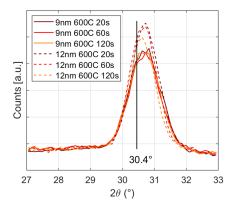

| 2.20 | GI-XRD taken on 9 nm and 12 nm Si:HfO <sub>2</sub> capacitors annealed at 600 °C for          |    |

|      | different annealing times.                                                                    | 43 |

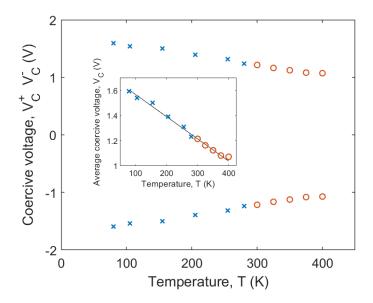

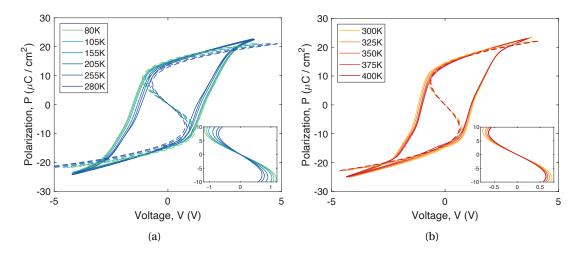

| 2.22 | Positive, negative and averaged coercive voltage versus temperature.(Reproduced               |    |

|      | from [86])                                                                                    | 45 |

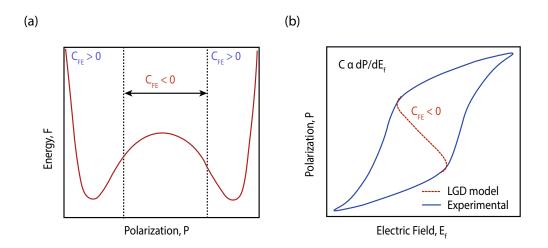

| 3.1  | (a) Free energy profile predicted by LGD theory. (b) LGD S-shaped polarization                |    |

|      | curve (red) and experimental hysteretic polarization curve in capacitors (blue).              |    |

|      | (Reproduced from [111])                                                                       | 52 |

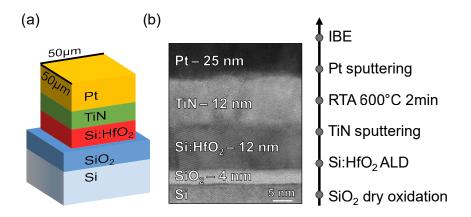

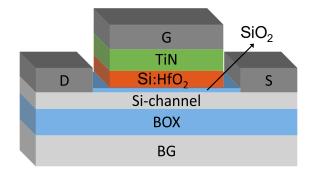

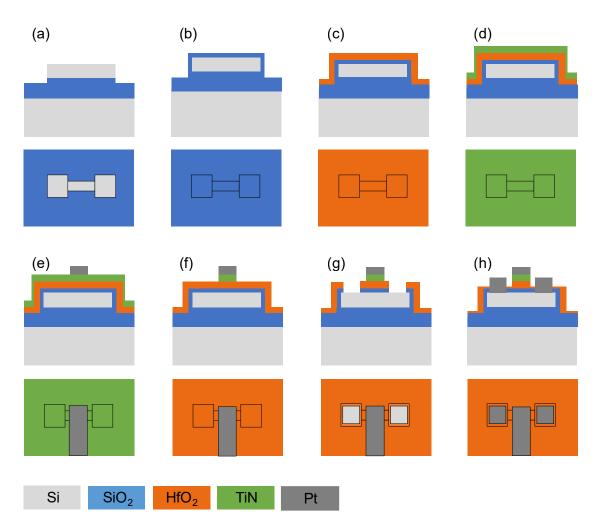

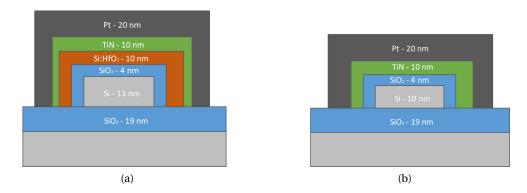

| 3.2  | MFIS gate stack. (a) Cross section schematic. (b) Cross-section HR-TEM of the                 |    |

|      | fabricated device structure and process steps.                                                | 53 |

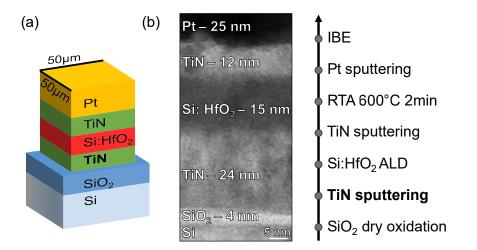

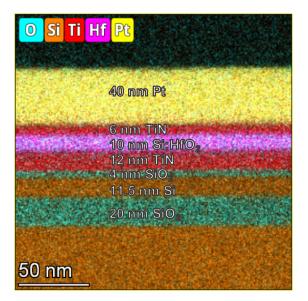

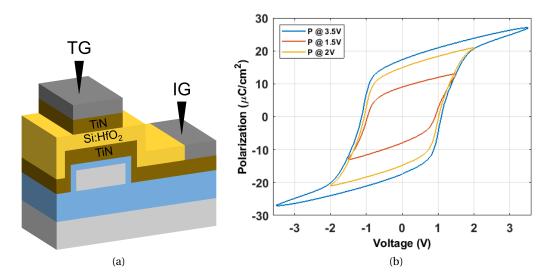

| 3.3  | MFMIS gate stack. (a) Cross section schematic. (b) Cross-section TEM of the                   |    |

|      | fabricated device structure and process steps.                                                | 54 |

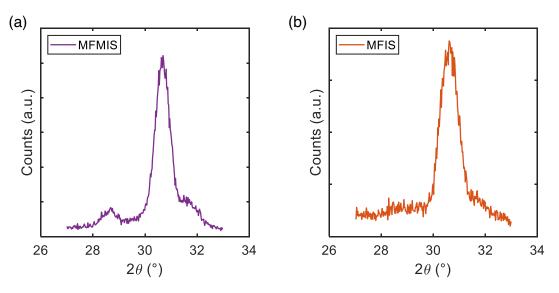

|      |                                                                                               |    |

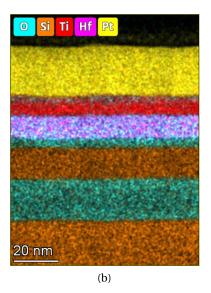

| 3.4  | GI-XRD pattern of the MFMIS (a) and MFIS (b) showing the ferroelectric or-<br>thorhombic peaks at 30.4°.(Reproduced from [111])                                                                                                | 54 |

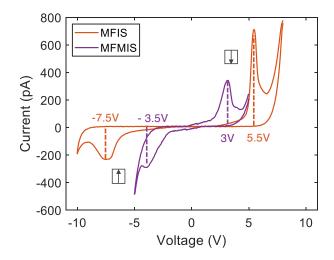

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Quasi-DC current-voltage measurements on 50x50 $\mu m^2$ MFMIS and MFIS gate stacks with the extracted polarization switching voltage for the two polarization                                                                 |    |

|      | states (black arrows). (Reproduced from [111])                                                                                                                                                                                 | 55 |

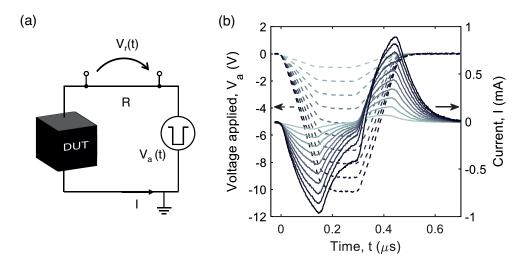

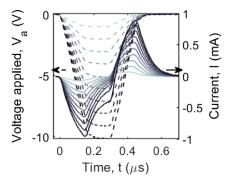

| 3.6  | (a) Measurement set-up to extract the S-shaped P-Ef curve. (b) Applied voltage pulses and current flow with respect to time for the MFMIS. (Reproduced from                                                                    | 50 |

| o =  |                                                                                                                                                                                                                                | 56 |

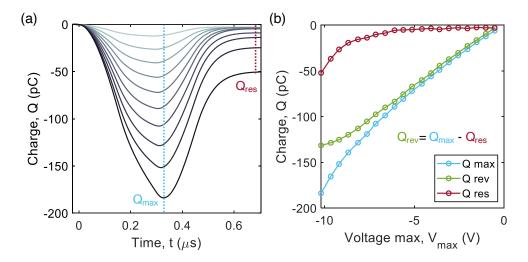

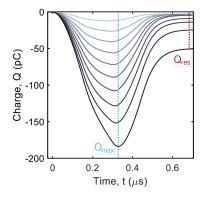

| 3.7  | (a) Charge as a function of time in MFMIS with dotted lines indicating the maximum charge and the residual charge (b) Maximum residual charge and reversible charge with respect to the maximum voltage applied at each pulse. |    |

|      | (Reproduced from [111])                                                                                                                                                                                                        | 57 |

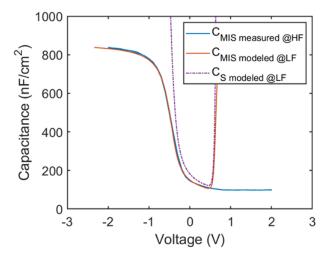

| 3.8  | MIS CV plot: measured at high frequency (HF) and curve modeled at low fre-<br>quency (LF)                                                                                                                                      |    |

| 2.0  |                                                                                                                                                                                                                                | 57 |

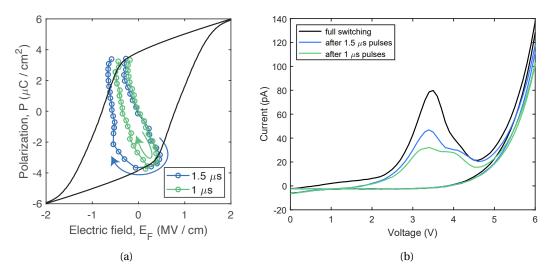

| 3.9  | Effect of the pulse width on the switching. (a) I-V curves extracted after the pulse measurement. (b) $P - E_F$ curves with increasing hysteresis for longer pulse widths.                                                     | 58 |

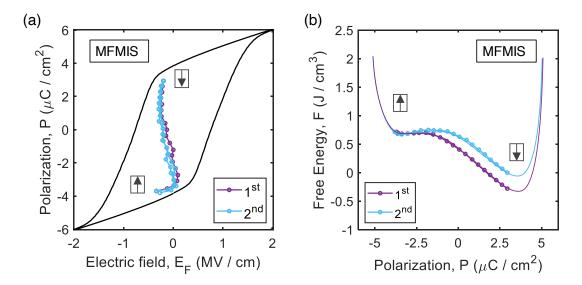

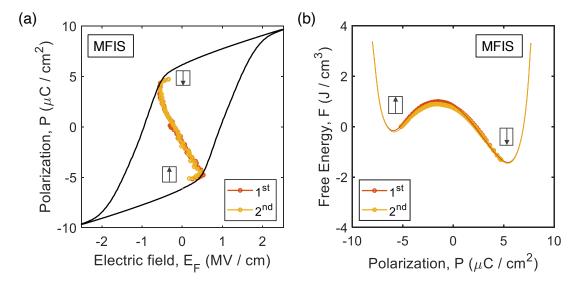

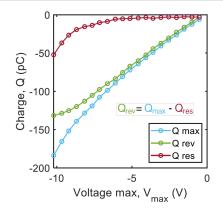

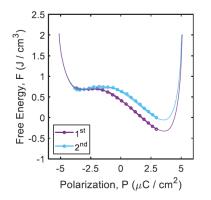

| 3.10 | (a) MFMIS S-shaped P-Ef curve extracted with the pulse method (b) MFMIS Free                                                                                                                                                   |    |

|      | energy landscape derived from the P-Ef curve. (Reproduced from [111])                                                                                                                                                          | 60 |

| 3.11 | (a) MFIS S-shaped P-Ef curve extracted with the pulse method (b) MFIS Free                                                                                                                                                     |    |

|      | energy landscape derived from the P-Ef curve. (Reproduced from [111])                                                                                                                                                          | 60 |

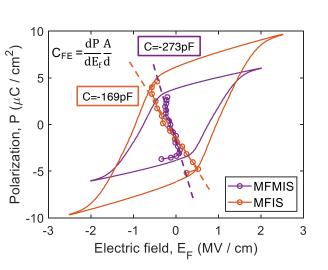

| 3.12 | Comparison between the S-shaped polarization cure of the MFMIS (purple) and of the MFIS (orange) with an insert showing the equivalent capacitance in the                                                                      |    |

|      | linear NC region. (Reproduced from [111])                                                                                                                                                                                      | 61 |

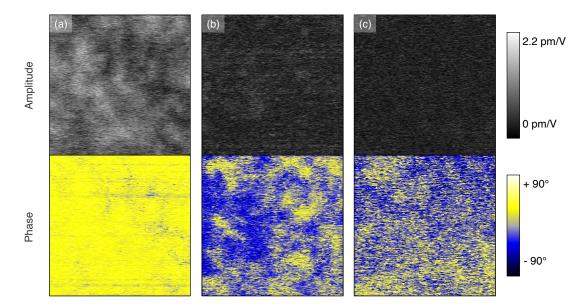

| 3.13 | PFM maps of the amplitude and the phase of the same area $(1x1\mu m^2)$ in different polarization states: (a) positive state (+5.5 V), (b) mixed state (-6.5 V) and (c)                                                        |    |

|      | negative state (-9.5 V). (Reproduced from [111])                                                                                                                                                                               | 63 |

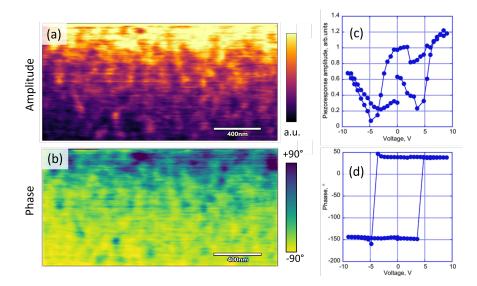

| 3.14 | Piezoresponse phase (b) and amplitude (c) loops of MFIS gate stack. (Repro-<br>duced from [111])                                                                                                                               | 63 |

| 2 10 | PFM maps of the phase (left) and amplitude (right) acquired with an AC voltage                                                                                                                                                 | 05 |

| 5.19 | of 1V at a frequency of 92kHz showing sequential poling. (Reproduced from [105])                                                                                                                                               | 69 |

| 2 20 | From (a) to (f) hysteresis loops of the phase of local piezoelectric response                                                                                                                                                  | 05 |

| 3.20 | measured on the single spot, with the maximum voltage amplitude increasing                                                                                                                                                     |    |

|      | from 5V to 7.5V. (g) Coercive field extracted from (a) to (f) and plotted vs. the                                                                                                                                              |    |

|      | maximum voltage applied. (Reproduced from [105])                                                                                                                                                                               | 72 |

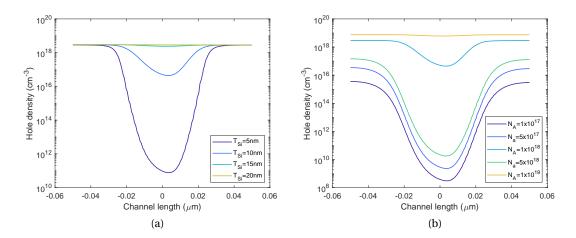

| 4.1  | Simulated JLFET structure with the cutline in the Si channel with $N_a = 5 \cdot$                                                                                                                                              |    |

|      | $10^{18} cm^{-3}$ , T <sub>Si</sub> = 10nm, V <sub>TG</sub> =0V, V <sub>DS</sub> =-0.05V and V <sub>BG</sub> = 0V                                                                                                              | 77 |

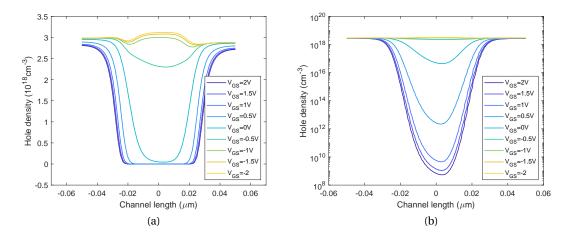

| 4.4  | Schematic of the Fe-JLFET with MFIS gate stack                                                                                                                                                                                 | 79 |

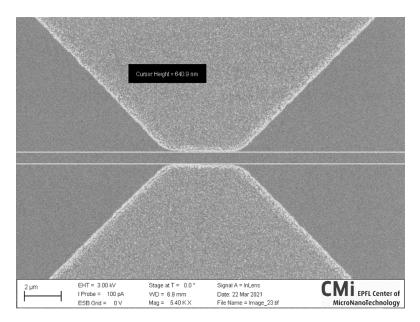

| 4.5  | SEM taken after channel patterning                                                                                                                                                                                             | 79 |

| 4.6  | Process flow MFIS JLFET                                                                                                                                                                                                        | 81 |

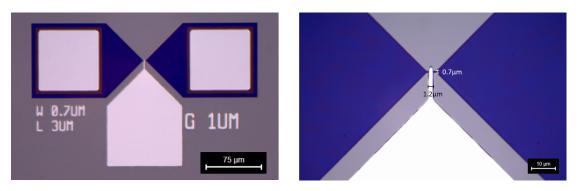

| 4.8  | Optical images of the device with the gate length of 700nm.                                                                                                                                                                    | 82 |

| 4 | 1.10 | PFM maps of amplitude (a) and phase (b) of piezoelectric response measured                           |    |

|---|------|------------------------------------------------------------------------------------------------------|----|

|   |      | on the ferroelectric gate through the top electrode. Single point hysteresis of                      |    |

|   |      | the amplitude (c) and phase (d) of the local piezoelectric response measured in                      |    |

|   |      | pulse mode (DC OFF) with the pulse/interval duration of 1 second                                     | 83 |

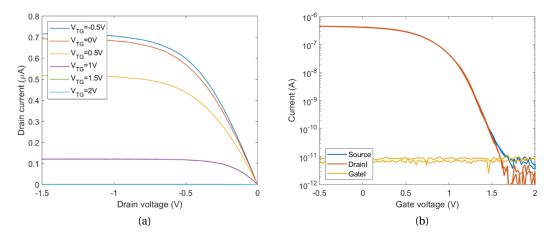

| 4 | 1.11 | (a) Output characteristics and (b) transfer characteristics of the produced UTBB-                    |    |

|   |      | SOI Fe-JLFET with the gate length of 700nm at $V_{DS}\mbox{=-}0.2V$ and $V_{BG}\mbox{=}0V$           | 84 |

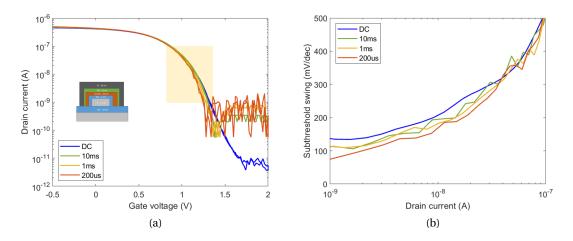

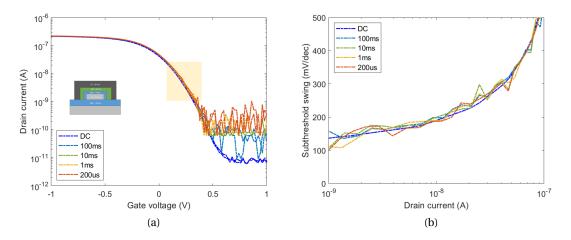

| 4 | 1.12 | Transfer characteristics of the Fe-JLFET with the gate length of 700 nm at $V_{SD}$ =-               |    |

|   |      | 0.2V measured in the dc and pulse modes (a), and respective subthreshold slopes                      |    |

|   |      | measured in mV/dec (b).)                                                                             | 85 |

| 4 | 1.13 | Transfer characteristics of the reference FET with the gate length of 700 nm with                    |    |

|   |      | $V_{SD}$ =-0.2V measured in the dc and pulse modes (a), and respective subthreshold                  |    |

|   |      | slopes measured in mV/dec (b).                                                                       | 86 |

| 4 | 1.14 | Comparison between the transfer characteristics of Fe-JLFET and reference FET                        |    |

|   |      | (a) and respective subthreshold slopes (b)                                                           | 87 |

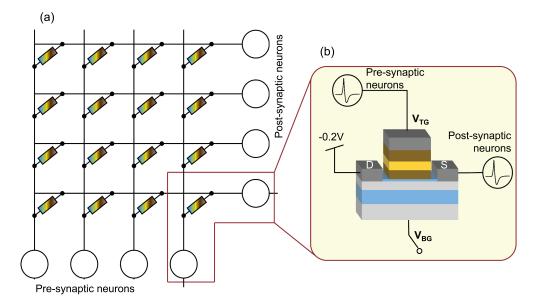

| 4 | 1.15 | (a) Schematic of a neural crossbar architecture with Fe-JLFET synapses (b)                           |    |

|   |      | Schematic of the synaptic Fe-JL-FET with an addition of a terminal for efficient                     |    |

|   |      | tuning of the synaptic weight                                                                        | 88 |

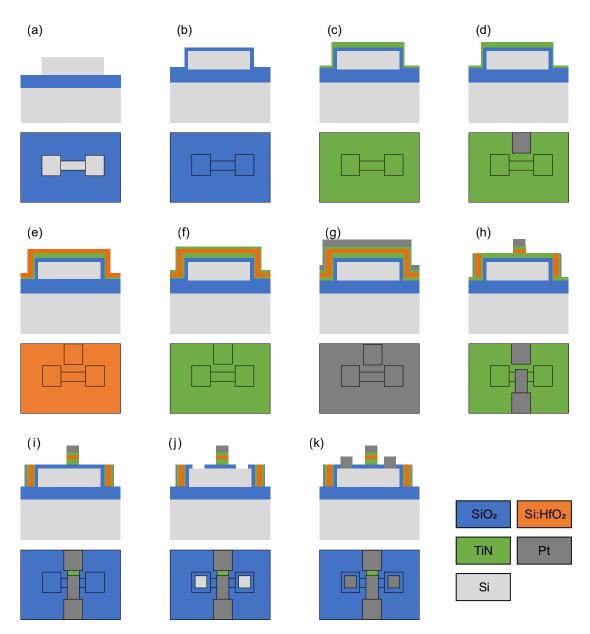

| 4 | 1.16 | Schematic showing the top view and the cross-section of Fe-JLFET with MFMIS                          |    |

|   |      | gate stack during the fabrication from (a) to (k) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 89 |

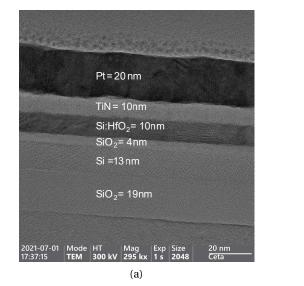

| 4 | 1.17 | Cross-sectional TEM image of a Fe-JLFET                                                              | 90 |

| 4 | 1.18 | Cross-sectional EDX map with the different thin film thicknesses of the gate stack.                  | 90 |

| 4 | 1.19 | (a) Fe-JLFET schematic of the device highlighting the contacts for the ferroelec-                    |    |

|   |      | tric testing (TG and IG) and (b) P-V hysteresis loops at different maximum bias                      |    |

|   |      | taken between the TG and the IG                                                                      | 91 |

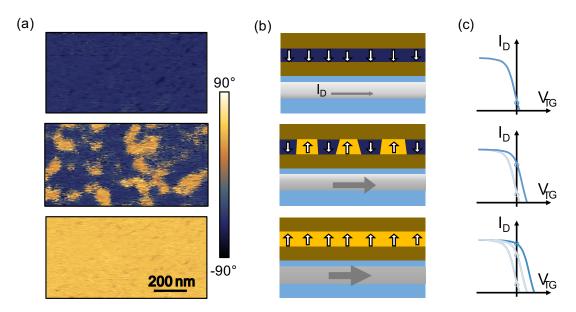

| 4 | 1.20 | (a) Phase PFM maps of domain switching in Si:HfO <sub>2</sub> (positive, mixed and nega-             |    |

|   |      | tive state) taken between the TG and the IG. (b) Qualitative schematic with focus                    |    |

|   |      | on the relationship between ferroelectric and Si channel. (c) Schematic of the                       |    |

|   |      | current change in the $I_D - V_{TG}$                                                                 | 92 |

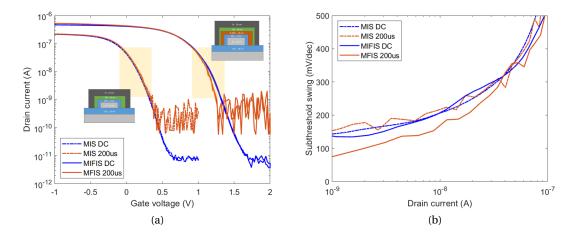

| 4 | 1.21 | (a) Transfer characteristics controlled by the top gate of the Fe-JLFET with 1.2                     |    |

|   |      | $\mu m$ channel width and 1 $\mu m$ length. (b) Comparison between the Fe-JLFET                      |    |

|   |      | (with MFMIS gate) and JLFET (with MIS gate) transfer characteristics                                 | 93 |

| 4 | 1.22 | Fe-JLFET transfer characteristics by sweeping the TG of the in the two ferroelec-                    |    |

|   |      | tric states with BG bias, from -2V to 2V.                                                            | 94 |

| 4 | 1.23 | Fe-JLFET transfer characteristics by sweeping the BG at different TG bias, from                      |    |

|   |      | -1V to 1V                                                                                            | 94 |

| 4 | 1.27 | Cycling for 2000 cycles, such as 128k, with the same condition of Figure 4.25a,                      |    |

|   |      | demonstrating the robustness of Fe-JLFET for tunable synapses                                        | 98 |

|   |      |                                                                                                      |    |

# List of Tables

| 2.1 | ANOVA results of the linear model with interaction obtained with MATLAB        | 39 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | Effect of different annealing conditions on remanent polarization and leakage  |    |

|     | current density (at 3V) taken on 12 nm Si:HfO <sub>2</sub> capacitor           | 41 |

| 2.3 | Effect of different annealing conditions on remanent polarization and leakage  |    |

|     | current density (at 3V) taken on 9 nm Si:HfO <sub>2</sub> capacitor            | 42 |

| 2.4 | Effect of film thickness variation on the coercive field at the same annealing |    |

|     | condition (600 °C for 120 s)                                                   | 43 |

| 4.1 | Fixed parameters for TCAD simulation of JLFET                                  | 77 |

# Contents

| Ac           | Acknowledgements iii |          |                                                                    |      |

|--------------|----------------------|----------|--------------------------------------------------------------------|------|

| Sommario vii |                      |          |                                                                    | vii  |

| Li           | List of figures viii |          |                                                                    |      |

| Li           | stof                 | tables   |                                                                    | xiii |

| Co           | onten                | its      |                                                                    | xiv  |

| 1            | Intr                 | oducti   | on                                                                 | 1    |

|              | 1.1                  | From     | More-Moore to Beyond CMOS approach                                 | 1    |

|              |                      | 1.1.1    | Evolution of semiconductor industry                                | 1    |

|              |                      | 1.1.2    | Negative capacitance FET as energy efficient logic device          | 4    |

|              |                      | 1.1.3    | Neuromorphic computing                                             | 7    |

|              | 1.2                  | Ferroe   | electricity                                                        | 8    |

|              |                      | 1.2.1    | History                                                            | 9    |

|              |                      | 1.2.2    | Fundamentals of ferroelectricity                                   | 10   |

|              |                      | 1.2.3    | Phenomenologoical theory of ferroelectric phase transitions        | 11   |

|              |                      | 1.2.4    | HfO <sub>2</sub> -based ferroelectric                              | 13   |

|              | 1.3                  | Juncti   | onless FET as the platform for a ferroelectric transistor          | 16   |

|              | 1.4                  | Thesis   | s outline                                                          | 18   |

| 2            | Stuc                 | ly of gi | owth and ferroelectric switching of Si:HfO <sub>2</sub> thin films | 21   |

|              | 2.1                  | Fabric   | cation                                                             | 21   |

|              |                      | 2.1.1    | Atomic layer deposition                                            | 21   |

|              |                      | 2.1.2    | Process flow                                                       | 22   |

|              | 2.2                  | Micro    | structural analysis                                                | 23   |

|              |                      | 2.2.1    | Method for microstructural analysis                                | 23   |

|              |                      | 2.2.2    | Results on the Si:HfO <sub>2</sub> capacitor                       | 25   |

|              | 2.3                  | -        |                                                                    | 26   |

|              |                      | 2.3.1    | Electrical characterization methods                                | 26   |

|              |                      | 2.3.2    | Electrical characterization result                                 | 27   |

|              | 2.4                  | Electr   | omechanical characterization                                       | 31   |

|              |                      | 2.4.1    | Introduction on piezoelectric force microscopy                     | 31   |

|   |      |                                                        | Flectrical characterization                                                                                                                                                  |          |  |

|---|------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|   |      | 4.3.3                                                  | Electrical characterization                                                                                                                                                  | 91<br>92 |  |

|   |      | 1.0.2                                                  | on Fe-JLFET functionality                                                                                                                                                    | 91       |  |

|   |      | 4.3.2                                                  | Integrated ferroelectric gradual Switching Transistor and its implications                                                                                                   | 00       |  |

|   | 1.0  | 4.3.1                                                  | Fe-JLFET fabrication                                                                                                                                                         | 88       |  |

|   | 4.3  |                                                        | FET with MFMIS gate structure exploiting gradual switching                                                                                                                   | 87       |  |

|   |      | 4.2.4                                                  | Pulsed electrical characterization                                                                                                                                           | 85       |  |

|   |      | 1.2.2                                                  | Electrical characterization in DC                                                                                                                                            | 84       |  |

|   |      | 4.2.2                                                  | Electromechanical characterization                                                                                                                                           | 80       |  |

|   |      |                                                        | MFIS Fe-JLFET fabrication                                                                                                                                                    | 79       |  |

|   | 4.2  |                                                        | FET with MFIS gate structure for logic application                                                                                                                           | 78       |  |

| - | 4.1  |                                                        | FET devices on a UTBB-SOI                                                                                                                                                    | 75       |  |

| 4 | Feri | roelect                                                | ric Junctionless FET                                                                                                                                                         | 75       |  |

|   | 3.4  | Sumn                                                   | nary                                                                                                                                                                         | 73       |  |

|   | . ·  | 3.3.4                                                  | Intrinsic switching: insight from PFM and pulse measurement                                                                                                                  | 70       |  |

|   |      | 3.3.3                                                  | Nanoscopic analysis                                                                                                                                                          | 67       |  |

|   |      | 3.3.2                                                  | Pulse measurements                                                                                                                                                           | 66       |  |

|   |      | 3.3.1                                                  | Device structure and leakage current considerations                                                                                                                          | 65       |  |

|   | 3.3  |                                                        | pilayer structure                                                                                                                                                            | 65       |  |

|   |      | 3.2.5                                                  | Experimentally calibrated NC-FET simulation                                                                                                                                  | 64       |  |

|   |      | 3.2.4                                                  | PFM evidences of imprint in the MFIS gate structure                                                                                                                          | 62       |  |

|   |      | 3.2.3                                                  | Pulse measurements                                                                                                                                                           | 55       |  |

|   |      |                                                        | the gate                                                                                                                                                                     | 54       |  |

|   |      | 3.2.2                                                  | Integrated silicon-doped hafnia XRD and electrical characterization of                                                                                                       |          |  |

|   |      | 3.2.1                                                  | Fabrication                                                                                                                                                                  | 53       |  |

|   | 3.2  | -                                                      | ped $HfO_2$ gate structures with and without metal interlayer                                                                                                                | 52       |  |

|   | 3.1  |                                                        | ferroelectric capacitor to ferroelectric multi-layers devices                                                                                                                | 51       |  |

| 3 | HfO  | fO <sub>2</sub> -based bilayer gate stack structure 5. |                                                                                                                                                                              |          |  |

|   |      | Cann                                                   | ,                                                                                                                                                                            | 10       |  |

|   | 2.7  |                                                        | nary                                                                                                                                                                         | 48       |  |

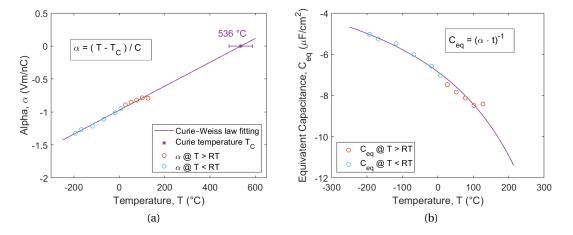

|   |      | 2.6.2                                                  | Curie-Weiss law                                                                                                                                                              | 46       |  |

|   | 2.0  | 2.6.1                                                  | Temperature-dependent polarization switching in Si:HfO <sub>2</sub> $\ldots$ $\ldots$ $\ldots$                                                                               | 44       |  |

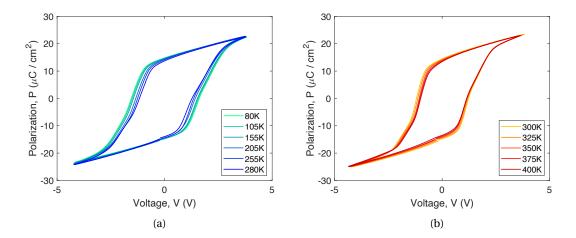

|   | 2.6  |                                                        | sic switching mechanism in Si:HfO <sub>2</sub> capacitor $\dots \dots \dots$ | 40       |  |

|   |      | 2.5.2                                                  | Thickness                                                                                                                                                                    | 40       |  |

|   | 2.0  | 2.5.1                                                  | Thermal budget                                                                                                                                                               | 37       |  |

|   | 2.5  |                                                        | cation optimization                                                                                                                                                          | 37       |  |

|   |      | 2.4.2                                                  | Electromechanical characterization results                                                                                                                                   | 33       |  |

### CONTENTS

| 5.3 Future Works                                              | . 104 |  |

|---------------------------------------------------------------|-------|--|

| A MATLAB algorithm for S-shaped polarization curve extraxtion | 107   |  |

| B Runcard of Fe-JLFET with MFIS gate stack                    | 111   |  |

| C Runcard of Fe-JLFET with MFMIS gate stack                   | 113   |  |

| Bibliography                                                  |       |  |

| Relevant publications                                         |       |  |

| Curriculum Vitae                                              |       |  |

# **1** Introduction

## 1.1 From More-Moore to Beyond CMOS approach

The events of these last two years were dramatic, with the entire world fighting against the first pandemic in a century. However, the need for remote communication, purchasing goods online, and handling business transactions pushed various parts of the electronics and informatics sector. Under normal circumstances, it would have taken far longer for so many technologies to grow naturally. Consequently, the market exploded in 2020, and in particular, consumer electronics revenues increased by 17% in the United States [1]. However, these last two years are just a continuation of the digital revolution that started in the 50s, which profoundly altered how we experience and interact with the world around us [2].

## 1.1.1 Evolution of semiconductor industry

Austrian physicist Julius Edgar Lilienfeld first introduced the basic principle of the fieldeffect transistor (FET) in 1926. As the cover of the electronic magazine "Crystal Triode" reported in Figure 1.1, the first working transistor was built by Shockley, Bardeen, and Brattain in 1947 at Bells Lab [3], for which they won a Nobel prize. Nevertheless, the discovery of Complementary Metal-Oxide-Semiconductor (CMOS) at Bell Lab in 1959 revolutionized the electronics industry. Thanks to the CMOS introduction, the digital electronic era enabled an increase in the transistor area density and, consequently, higher performance while keeping low power consumption.

Since the discovery of CMOS's capability, the semiconductor industry has spent its resources to shrink the physical size of transistors and increase their density. In 1965, Gordon Moore, thanks to his experience as co-founder of Intel and Fairchild Semiconductor, observed and predicted that the number of transistors in an integrated circuit doubles every two years. As shown in Figure 1.2, this empirical trend, called Moore's law, has been rigorously followed for several years till nowadays [5].

Figure 1.1: Cover of "Crystal Triode", an electronic magazine, showing Bardeen, Brattain, and Shockley in the Bells Lab where they built the first transistor. (Adapted from [4])

Reducing transistor size increased device density, i.e., less necessary space for a fixed transistor count. Furthermore, it improved performances by lowering the capacitances in the device and increasing the maximum operating frequency, as shown in Figure 1.3. Additionally, when transistors are scaled down, their power density remains constant, maintaining the power proportional to the area. This scaling principle is called Dennard's rules [7, 8] and allowed to follow Moore's trend strictly.

However, continuing this aggressive scaling was not a straightforward achievement [9, 10]. From the 1990s, power density became a critical concern due to the physical limitations of the transistor: scaling down transistor dimensions caused an increase in static consumption. In the 2000s, power density increased, reaching its maximum thermal limit above which the device's functionality and safety would have been affected. Since then, it became clear that Dennard's scaling was close to an end. Transistor density continues to increase at the expense of processor clock speed, which has remained invariant. However, to keep increasing the performance, multiple cores were added to split the tasks and reduce the power density per core, as highlighted in Figure 1.3. Although parallel calculations were proven effective, the system's complexity unavoidably grows as the number of cores increases. The processing design's complexity might also reach a limit beyond which increasing the parallelism is neither feasible nor efficient.

In the meantime, to continue the scaling several technological changes were made to sustain this rate of progress: lithography techniques were improved, new transistor designs from planar to 3D structure, the use of silicon-on-insulator wafer to reduce the off-current, and the use of strained silicon technique and novel dielectric materials to increase the on-current. Despite the substantial evolution of the CMOS technology, no significant changes were made in computer architecture. Indeed it had not been altered significantly since Von Neumann's introduction in 1945.

Figure 1.2: Exponential growth projection of transistor count in integrated circuits plotted vs the year of introduction (taken from [6]).

Nowadays, the technology node reaches 5 nm [12, 13], but the semiconductor manufacturers, TSMC and Samsung, announced the production of the 3 nm node by the second half of 2022 [14, 15]. However, continuing the scaling down may prove not economically viable, especially in developing infrastructures and lithographic tools, like extreme ultraviolet lithography [16]. This may be why GlobalFoundries, one of the biggest semiconductor industries, said it was stopping at the 10 nm technology. As a result, only Intel, Samsung, and TSMC remained in the semiconductor market to produce smaller transistors. Even these colossus may eventually be unable to balance the cost, revenues, and danger of continuing the node scaling down.

In contrast to the "More Moore" approach, which imposes speed and density limitations on devices due to heating issues, International Roadmap for Devices and Systems (IRDS) identified the "Beyond CMOS" approach as a possible future digital technology. This paradigm is focused on finding great performance systems working at low-lower consumption, as shown in Figure 1.4. The research focuses on alternatives to traditional random-access memory (RAM), such as Phase-Change RAM (PCRAM), Resistive RAM (ReRAM), Magnetic RAM (MRAM), and Ferroelectric RAM (Fe-RAM) [17]. Also, novel emerging devices with low power switching are investigated, like Negative Capacitance FET (NCFET) and Tunnel FET (TFET). Another approach is to change the computing architecture. Recently a heavy focus has been placed on novel computing paradigms like neuromorphic or quantum computing.

In the following sections, two energy-efficient solutions that operate with ferroelectric material are discussed in detail: NCFETs, as an emerging low-power device (Section 1.1.2), and neuromorphic computing, as a novel energy-efficient architecture (Section 1.1.3).

Figure 1.3: Microprocessor scaling trends throughout 52, highlighting the end of Dennard scaling after the 2000s (adapted from [11]).

Figure 1.4: Schematic showing the objective of Beyond CMOS vs More Moore approach (taken from [18]).

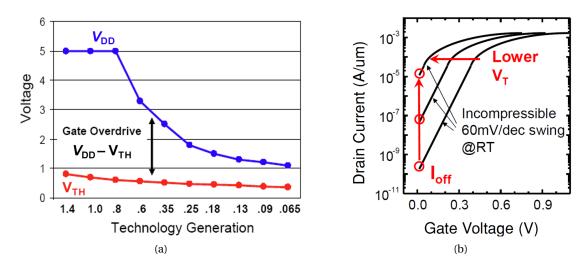

#### 1.1.2 Negative capacitance FET as energy efficient logic device

As mentioned in Section 1.1.1, starting from the 1990s, Dennard scaling arrived at the end. The supply  $(V_{DD})$  and the threshold voltages  $(V_{TH})$  could not be scaled anymore of the same factor, as shown in Figure 1.5(a). This choice was made to limit the exponential increase of off-current  $(I_{off})$  with the  $V_{TH}$  (Figure 1.5(b)) since  $I_{off}$  is proportional to static power (*Power*<sub>static</sub>):

$$Power_{static} = I_{off} V_{DD}.$$

(1.1)

A way of reducing the power dissipation is to increase the turn-on steepness, which means decreasing the average subthreshold swing (*SS*), which is defined as:

Figure 1.5: (a) Scaling trend of  $V_{TH}$  and  $V_{DD}$  with respect to CMOS technology (adapted from [19]). (b) Schematic showing that a linear increase of  $V_{TH}$  causes an exponential rise of  $I_{off}$  value because of the incomprehensibility of the swing (from[20]).

$$SS = \frac{\partial V_G}{\partial log I_D} = \frac{\partial V_G}{\partial \psi_S} \times \frac{\partial \psi_S}{\partial log I_D},$$

(1.2)

where  $V_G$ ,  $I_D$ , and  $\psi_S$  denote the gate voltage, the drain current, and the surface potential of the semiconducting channel, respectively. The first term of Equation 1.2 is the body factor, also called m-factor which is usually greater than 1. It can be rewritten as:

$$m = \frac{\partial V_G}{\partial \psi_S} = (1 + \frac{C_S}{C_{OX}}) \tag{1.3}$$

where  $C_{OX}$  and  $C_S$  are respectively the capacitance gate oxide and semiconductor capacitance. The second term on the right is known as the n-factor, and in the case of MOSFETs with thermionic injection mechanism is equal to:

$$n = \frac{\partial \psi_S}{\partial \log I_D} = \frac{KT}{q} \ln 10 \tag{1.4}$$

where k is the Boltzmann constant and T is the temperature. In this case, the minimal n-factor value is equal to 60 mV/dec at 300 K. This limits the transistor turn-on steepness by imposing a minimum *SS*.

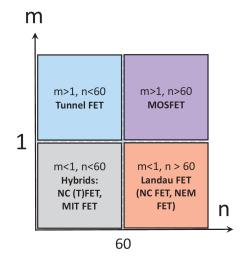

One of the techniques proposed to get energy-efficient devices is to reduce the SS. As shown in Figure 1.6 several steep switching devices are proposed, either by reducing the n-factor or the body factor.

Figure 1.6: Map of FET design space (adapted from [21]).

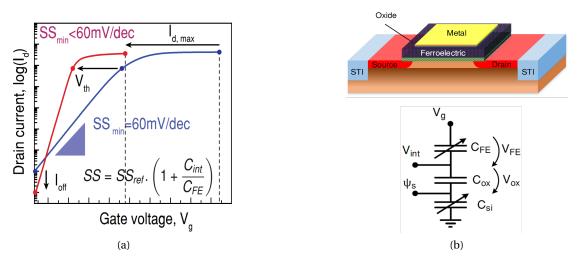

Among those TFET [20] is one of the most common devices proposed in the literature. Its *SS* is no more limited by the thermionic injection since it works based on a tunneling mechanism and, therefore, can be smaller than 60 mV/dec. Another method to reduce the SS is to have m-factors smaller than 1. It can be obtained by introducing a negative capacitance inside the field-effect transistors using a so-called Negative Capacitance FET, (NC-FET) [22]. Figure 1.7(b) shows the comparison between transfer characteristics obtained with a MOSFET (blue curve) and a NC-FET (red curve).

The turn-on steepness is obtained by adding a ferroelectric material to the gate stack on top of the linear insulator, as shown in the schematic of Figure 1.7(b). The subthreshold swing  $(SS_{FE})$ , can be rewritten as follows:

$$SS_{FE} = SS_{min} \left(1 + \frac{C_{OX-S}}{C_{FE}}\right) = 60 \frac{mV}{dec} \left(1 + \frac{C_{OX-S}}{C_{FE}}\right)$$

(1.5)

where  $C_{OX-S}$  is the series capacitance of the gate oxide and the silicon, while  $C_{FE}$  is the equivalent ferroelectric capacitance. Consequently, if  $C_{FE} < 0$ , the  $SS_{FE}$  becomes steeper than 60 mV/dec an internal amplification of the voltage occurs. This happens when the transistor works in a negative capacitance regime offered by the intrinsic ferroelectric switching described in Section 1.2.3. This idea, which aroused great interest in the device community, was first proposed by Salahuddin in 2008 [22] and then validated by several experimental results[24, 23, 25, 26, 27].

Figure 1.7: (a) Comparison of transfer characteristics obtained with a MOSFET (blue line) and a NC-FET (red line); SS improvement and threshold voltage reduction highlighted.(Adapted from [23]) (b) Structure of a generic ferroelectric transistor (from[24]) and its equivalent capacitance model.

### 1.1.3 Neuromorphic computing

In von Neumann's architecture, the exchange of data between the central processing units and the main memory is performed by share buses, which limit the throughput and increase the processing time and power consumption [28] [29]. Nowadays, to overcome Von Neumann's bottleneck, other emerging computing systems are proposed. Among the different strategies, one of the most studied is quantum computing, which makes use of physical phenomena like superposition and entanglement to solve some categories of classically intractable problems [30]. Another potential new solution, which attracted much attention in the last few years, is neuromorphic computing. This paradigm is intuitively inspired by a computing technology existing already in the realm of biology: the brain. Contrary to Von Neumann, the human brain can achieve efficient data processing thanks to combining memory and computation in the same unit by mean neurons and synapses.

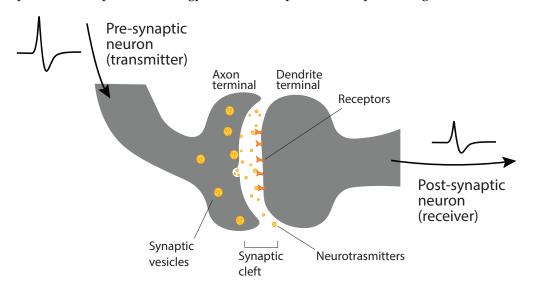

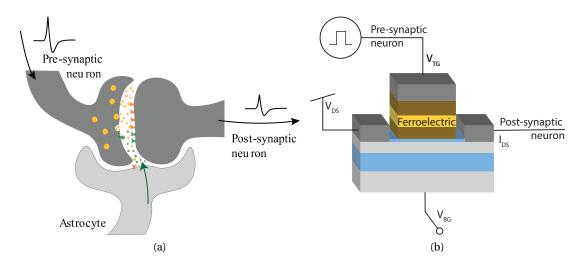

The neuron is a nerve cell generally composed of a nucleus called soma, several dendrites, which receive the information to the pre-synaptic neurons, and an axon that transmits the information to a post-synaptic neuron. The soma processes the signal coming from dendrites. If it is strong enough, an electric signal, called an action potential, is fired to the axon terminal. The communication between neurons occurs through a specialized structure called synapses, shown in Figure 1.8. The pre-synaptic neuron contains neurotransmitters packed into vesicles. When a pre-synaptic neuron is excited by an action potential, the neurotransmitters are released into the synaptic cleft and interact with post-synaptic receptors, causing the generation of an action potential in the dendrites terminal. The connection strength between two neurons depends on the transmission history, and it is called synaptic weight. Synaptic

plasticity refers to the increase (potentiation) or decrease (depression) of the synaptic weight change. In conclusion, thanks to the massive interconnection between 10<sup>11</sup> neurons and 10<sup>15</sup> synapse, the brain performs energy-efficient and parallel data processing.

Figure 1.8: Schematic of a synaptic transmission mechanism showing a firing pre-synaptic neuron releasing neurotransmitters binding to receptors of the post-synaptic neuron.

Up to now, the potential of neuromorphic computing has been mainly tested using machine algorithms and classical CMOS-based hardware. However, these solutions require high power consumption and have a low learning speed [31, 32], and bio-inspired hardware has to be introduced to mimic the low power computing of neurons and synapses.

Several emerging memories [33] have been considered to mimic the synaptic functionality. Among those, ferroelectric transistors (Fe-FET) have attracted considerable attention as promising candidates thanks to multistate capabilities, which emulate synaptic plasticity, and low-power switching [34, 35, 35].

## 1.2 Ferroelectricity

As discussed above, one possibility to improve power efficiency in systems and devices is the introduction of ferroelectric materials. They are a dielectric material class that possesses a spontaneous electric polarization reversible by an external electric field. Thanks to their broad spectrum of properties, they are suitable for numerous applications, such as:

- memory and neuromorphic application [36, 37] (due to their highly reversible polarization)

- negative capacitance [22] (thanks to the intrinsic polarization switching)

- sensors and actuators [38, 39] (given their piezoelectric and pyroelectric properties)

• electrostatic supercapacitors and energy harvesting [40, 41] (due to energy conversion based on piezoelectric and pyroelectric effect)

This dissertation will focus on two energy-efficient applications, negative capacitance and neuromorphic applications. In the first class of application, the digital information is stored through spontaneous polarization, and having a large hysteretic window is fundamental for a correct reading of the stored data.

In the second class, hysteresis is avoided, and the ferroelectric is used to have a steeper subthreshold swing in the transistor by an internal amplification of the voltage. Ferroelectric NC devices rely on the exploitation of the NC region of the polarization-electric field (P-E) curve predicted by the Landau-Ginzburg-Devonshire (LGD) model, as discussed in Section 1.2.3).

#### 1.2.1 History

Ferroelectricity was discovered 100 years ago, in 1921 [42] by a Ph.D. student called Joseph Valasek, working under the supervision of William Swann at the University of Minnesota in Minneapolis. He was investigating the dielectric properties of Rochelle salt while noticing that the polarization switched in a hysteretic way by applying an electric field. However, from an application point of view, one of the major turning points was the discovery in 1946 of BaTiO3 [43], an inorganic compound with a perovskite structure. Unlike Rochelle salt, it is insoluble in water, chemically stable at room temperature, and with better electromechanical properties. Since then, ferroelectric material has been widely used in diverse fields, including sensors, actuators, and memories. After these discoveries, many structural families of ferroelectric were identified; among them, it is worth remembering the first ferroelectric polymer (PVDF) in 1971 [44].

In the meantime, the discussion about the theoretical backgrounds of these materials progressed considerably with the work of Devonshire. He developed the phenomenological theory of ferroelectrics built upon the earlier ideas of Landau and Ginzburg. It resulted in the LGD theory published in 1949 [45], which takes as a reference BaTiO3. One of the last breakthroughs is the discovery of a new major class of ferroelectric materials based on HfO<sub>2</sub>. This occurred in 2011 with the identification of Si-doped HfO<sub>2</sub> (Si:HfO<sub>2</sub>) ferroelectricity by Böscke et al [46]. Ferroelectric HfO<sub>2</sub> became the focus of significant attention because, contrary to conventional ferroelectric, it offers CMOS compatibility in thin layers, making it the perfect candidate for Fe-RAM [36, 47].

In this section, the basic concepts of ferroelectricity, relevant to the present thesis work, are briefly introduced, together with the thermodynamic switching model. To conclude the section,  $HfO_2$ -based ferroelectric are presented.

#### 1.2.2 Fundamentals of ferroelectricity

Ferroelectric materials are part of the dielectric material category. Among 32 symmetry point groups of crystalline materials, 20 non-centrosymmetric groups are compatible with piezoelectricity. Thanks to their lack of symmetry, it is possible, by applying mechanical stress, to polarize the material by displacing the atoms inside the unit cell. This effect is called the direct piezoelectric effect and is used for sensors application. Moreover, also the opposite effect is valid; by applying an external voltage drop, one can observe the deformation of the piezoelectric. The inverse piezoelectric effect is the working principle of actuators.

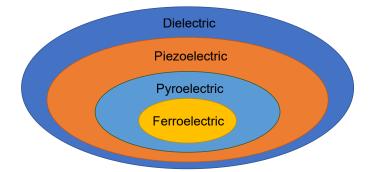

Out of the 20 point groups of crystalline materials, 10 groups are polar i.e. possess at least one unique direction that cannot be altered by symmetry operations. This direction is called polar because electric polarization in this direction is permitted by symmetry. A variation in temperature affects material polarization. In view of their properties, they were called pyroelectric. Ferroelectric materials are a subgroup of pyroelectric. Even though they share the same crystallographic structure, ferroelectric polarization can be switched in the opposite direction by the application of an electric field. Figure 1.9 depicts the classification of dielectric materials by means of the Van diagram, which enforces the concept that not all piezoelectric crystals are ferroelectric, but all ferroelectric crystals are piezoelectric.

Figure 1.9: Venn diagram showing the relationship between dielectric, piezoelectric, pyroelectric, and ferroelectric materials.

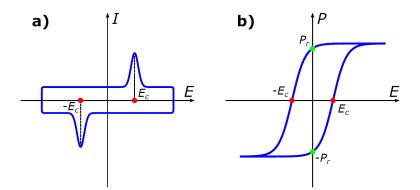

Even in the absence of an electric field, a ferroelectric material has a spontaneous electric polarization ( $P_S$ ), which can be switched by applying an external electric field larger than the coercive field ( $E_C$ ). This behavior gives rise to a hysteretic behavior observable in the polarization vs. electric-field plot (P - E).

In capacitor structure, the ferroelectric response is typically studied by monitoring the transient current while applying an electric field, as shown in Figure 1.10(a). The polarization is obtained by integrating the current in time, obtaining the hysteretic P - E plot depicted in 1.10(b). The intercept of the y-ax is called remnant polarization ( $P_R$ ), and the intercept of the x-axis is the coercive electric field.

However, if the temperature increases over a certain threshold called Curie temperature  $(T_C)$ ,

the material loses ferroelectricity because it transitions to a centrosymmetric crystal, and as a consequence, it behaves as paraelectric. In the next section, the thermodynamic theory is briefly outlined.

Figure 1.10: (a) Displacement current vs. electric field and (b) hysteresis loop (P-E) derived from it (adapted from [48]).

### 1.2.3 Phenomenologoical theory of ferroelectric phase transitions

The phenomenological thermodynamic theory, also called LGD theory, arose from the necessity to explain the ferroelectric to paraelectric phase transformation when the temperature is higher than Curie temperature. Here, for the sake of simplicity, the thermodynamic theory is described in a one-dimensional case, and polarization and applied electric field vector are considered parallel. The Gibbs free energy density (*G*) described within LGD theory [49, 50, 51, 45], can be expressed as a polynomial expansion up to the sixth order:

$$G = \frac{\alpha}{2} P^2 + \frac{\beta}{4} P^4 + \frac{\gamma}{6} P^6 - P E$$

(1.6)

where  $\alpha$ ,  $\beta$  and  $\gamma$  are Landau coefficients dependent on the material. The order parameter of Equation 1.6 is the polarization (*P*) since the dielectric displacement is equal to *P* when no electric field (*E*) is applied. Notably, the coefficient  $\alpha$  represents the reciprocal of the dielectric susceptibility, and it deserves particular attention because it is the only temperaturedependent Landau coefficient. The following conditions must be satisfied to derive its temperature dependence: the minimization of G, to change of sign  $T_C$  and guarantee continuity below and above  $T_C$ . Following the requirement,  $\alpha$  can be expressed with a linear temperature dependence:

$$\alpha = \frac{(T - T_C)}{C} \tag{1.7}$$

11

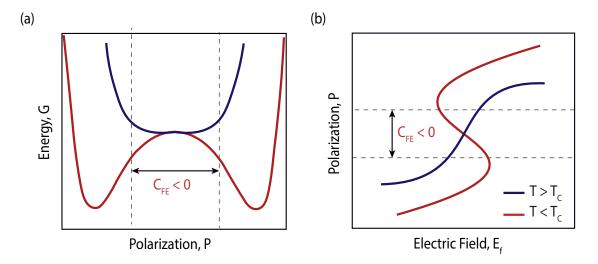

Equation 1.7 is called Curie-Weiss law, and *C* is the Curie constant. If the temperature is lower than  $T_C$ ,  $\alpha$  is negative, and the energy state has two minimum in correspondence to the stable ferroelectric states. On the contrary, if it is higher than  $T_C$ ,  $\alpha$  is positive, and it shows just one minimum at P = 0, which means that the material encountered a phase transition from ferroelectric to paraelectric. Figure 1.11(a) illustrates the effect of the phase change on the energy landscape and on the polarization.

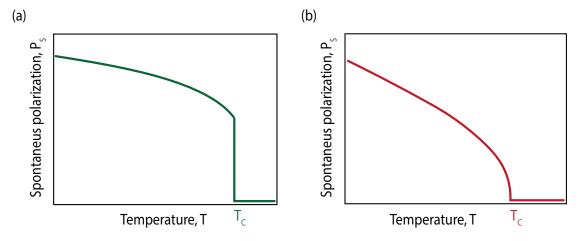

The sign of the  $\beta$  coefficient defines the phase transition type. If positive, the phase transition is called the second-order transition. On the contrary, if it is negative, the phase transition is called first-order. Conversely to the other coefficients,  $\gamma$  is always positive, and its value is smaller than the others.

By minimizing G with respect to the polarization in Equation 1.6, the equation of state of ferroelectric is derived, which yields the relation between the electric field across the ferroelectric and the polarization:

$$\frac{\mathrm{d}G}{\mathrm{d}P} = 0 \quad \Rightarrow \quad E = \alpha P + \beta P^3 + \gamma P^5 \tag{1.8}$$

As shown in the red curve of Figure 1.11(b), Equation 1.8 displays an S-shaped polarization curve, which has a negative slope region with negative equivalent permittivity ( $\epsilon_R \propto dP/dE$ ). This region corresponds to the area where there is the local maximum of the energy, as illustrated by red curve in Figure 1.11(a). The negative capacitance region is unstable and can not be experimentally observed in standard ferroelectric capacitor measurements. However, it can be exploited to get a differential voltage amplification in FET if integrated into the gate stack of a FET.

Figure 1.11: Schematic of the energy landscape and polarization behaviour in the ferroelectric phase ( $T < T_C$ ) and in the paraelectric( $T > T_C$ ).

Furthermore, from Equation 1.8 one can retrieve essential parameters related to polarization hysteresis in terms of the Landau coefficients. The free energy presents one maximum around P = 0, which is the unstable NC state, and two minima, which are the two stable states, such as the positive and negative spontaneous polarization  $P_S$ , which can be calculated as follow:

$$P_{S} = \pm \sqrt{\frac{-\beta + \sqrt{\beta^{2} - 4\alpha\gamma}}{2\gamma}}$$

(1.9)

It can be shown that if  $\beta > 0$  and  $T < T_C \gamma \approx 0$ , and LGD theory offers a simpler description of  $P_S$ :

$$P_S = \pm \sqrt{-\frac{\alpha}{\beta}} \tag{1.10}$$

In this last case, with negative  $\beta$ , the spontaneous polarization value reduces gradually with temperature until it reaches  $P_S = 0$  at the Curie temperature (Figure 1.12(b)). On the contrary, if  $\beta > 0$  and  $\gamma > 0$ , the spontaneous polarization value decreases little with temperature and at  $T = T_C$  jumps to zero. As it is illustrated in Figure 1.12(a), it generates a discontinuity of a first-order, from which it takes its name.

Figure 1.12: Schematic of spontaneous polarization temperature dependence in case of first order (a) and second order (b) phase transition.

#### **1.2.4** HfO<sub>2</sub>-based ferroelectric

Perovskites, which are arguably the most studied and used ferroelectrics, have excellent ferroelectric properties and a very high dielectric constant. For this reason, they are used for different ranges of applications. However, if integrated into microelectronic technology, they have two main disadvantages: Pb diffusion that leads to CMOS incompatibility and instability of the material at smaller thickness [47].

The extensive investigation of  $HfO_2$  as a high- $\kappa$  gate dielectric [52, 53, 54] brought to light that

if this material is subjected to certain stress, it reveals ferroelectricity. One of the first studies appeared in 2011 when Böscke et al. [46, 55] revealed ferroelectricity in Si:HfO<sub>2</sub> thin films deposited with ALD technique.

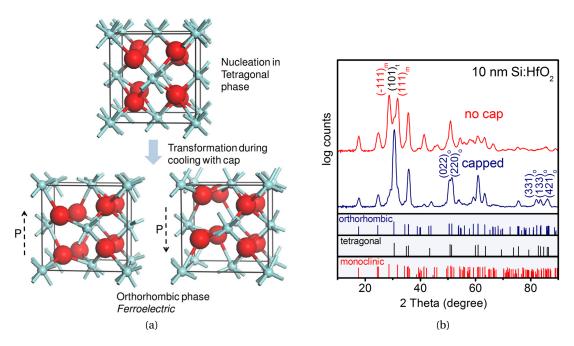

Figure 1.13: (a) Schematic of the Si:HfO<sub>2</sub> unit cell before the annealing with TiN as capping electrode and after, showing the transformation from tetragonal phase (paraelectric) to or-thorhombic (ferroelectric). (b) Grazing incidence x-ray diffraction measurements with the TiN capping (typical for orthorhombic phase) and without (typical for tetragonal/monoclinic phase). Reproduced from [46])

At room temperature, the most stable crystal structure of  $HfO_2$  is the monoclinic one, but if subjected to higher temperature (T), it shows a phase transformation into tetragonal (T > 1700 °C) and then cubic phase (T > 2600 °C) [56]. However, new studies [46, 55] showed that, if enough pressure is applied, it can transform into a non-centrosymmetric orthorhombic phase, which is believed to be the origin of ferroelectricity. In this crystallization phase, the unit cell is composed of Hf<sup>4+</sup> cations (at corners) and O<sup>2-</sup> the anions (at the eight tetrahedral interstitial sites). As depicted in Figure 1.13a the polarization switching originates from a movement of O<sup>2-</sup> anions inside the interstitial sites of the orthorhombic unit cell.

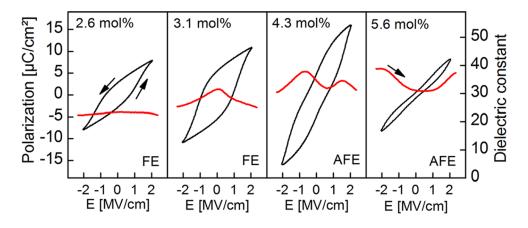

In the first studies, [46], the stabilization of the orthorhombic phase, together with some monoclinic one, was reached by capping Si:HfO<sub>2</sub> with TiN before the annealing step, to build an in-plane strain in the thin film (Figure 1.13b). Furthermore, Figure 1.14 shows that an optimal concentration window between 2.6 mol% and 4.3 mol% is needed to observe ferroelectricity. When the concentration is larger than 4.3 mol%, it leads to an anti-ferroelectric HfO<sub>2</sub>, and above 6 mol%, to a linear dielectric behavior.

Later it was shown that, by creating a lattice distortion into HfO<sub>2</sub>, other dopants could help

Figure 1.14: Polarization-Voltage (black) and Dielectric constant-Voltage (red) characteristics of a series of capped  $HfO_2$  capacitors showing a gradual transition from ferroelectric to anti-ferroelectric behavior with the increase of the Si doping (reproduced from [46]).

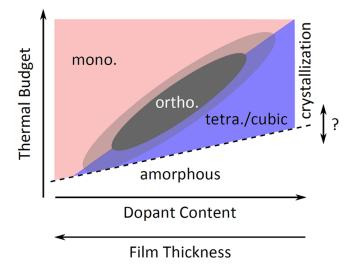

stabilize the orthorhombic phase. It was demonstrated with Al [57], Gd [58], La [59], Sr [60], Zr [61] and Y [62], but remarkably also undoped HfO<sub>2</sub> was proven to show ferroelectricity below 7 nm [63].

Another important property that influences ferroelectricity is thickness. It was discovered that thin HfO<sub>2</sub> layers (< 30 nm) show a higher remnant polarization [64]. Later it was proven that this trend originated from the fact that the small grains in thin films tend to favor the crystallization of the orthorhombic phase [65]. However, this trend does not continue for very thin layers [66], below 10 nm, the polarization degrades. A root cause can be found in the formation of a dead layer that forms between the ferroelectric and the electrode. As it is known from previous studies on perovskite material, when the dead layer becomes comparable to the ferroelectric one, the depolarization gets stronger and reduces the spontaneous polarization [67]. It's worth mentioning that in the presence of TiN electrodes, one can observe the generation of a non-ferroelectric layer rich in oxygen vacancy, which tens to stabilize in the tetragonal phase [68, 69]. This behavior is attributable to the scavenging propriety of TiN, which binds to oxygen atoms and forms a rutile TiO<sub>2</sub> and TiO<sub>x</sub>N<sub>y</sub> layer [70, 69]. Nevertheless, TiN remains a good candidate in CMOS application [71], thanks to its thermal stability, good electrical conductivity, and chemical stability (it is used as a diffusion barrier).

As already mentioned at the beginning, one of the most essential factors in stabilizing the orthorhombic phase is the annealing conditions, in terms of thermal budget (time and temperature) [72] and atmosphere condition [73]. Also, the deposition temperature influences  $HfO_2$  ferroelectricity, it was proven that the best condition to deposit it by ALD is a temperature between 300 °C and 800 °C, based on the doping type [72, 74].

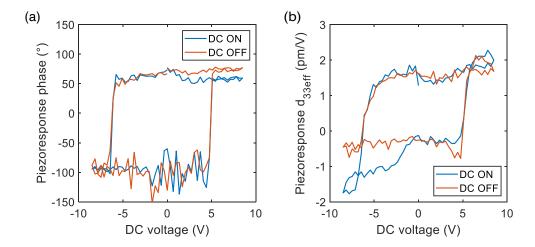

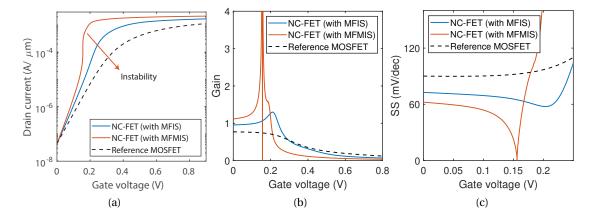

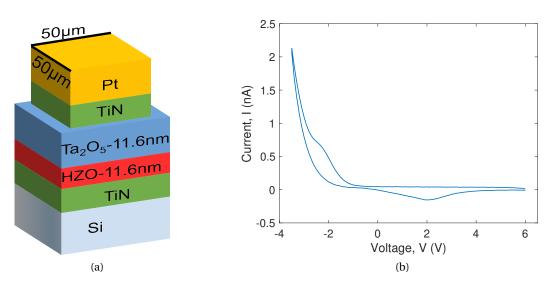

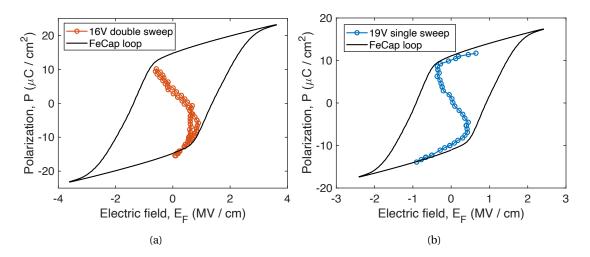

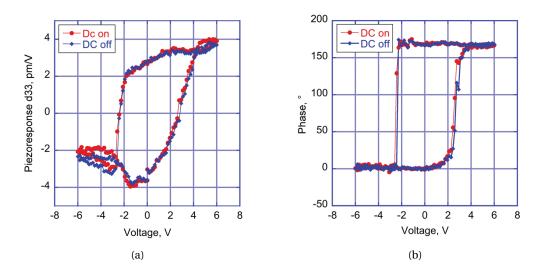

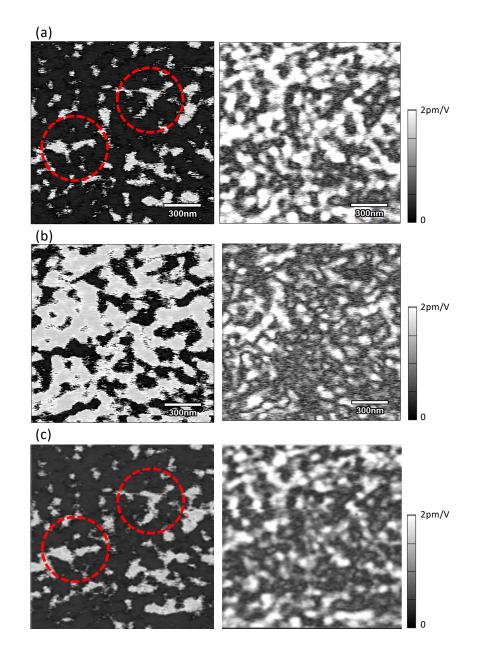

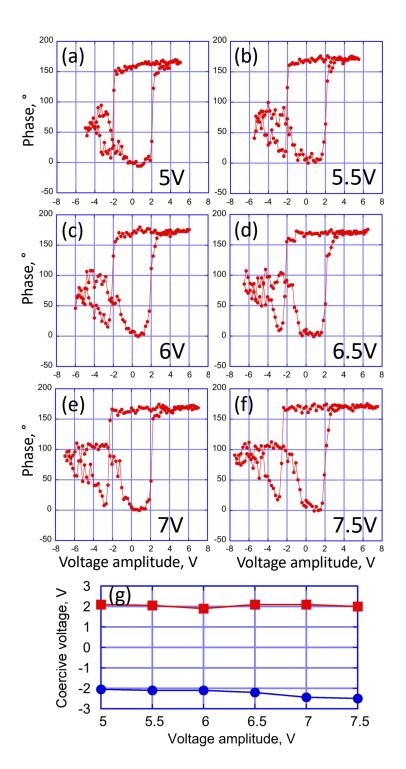

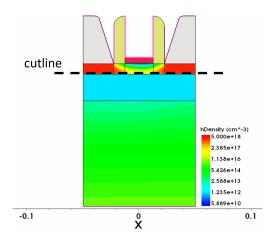

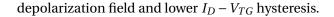

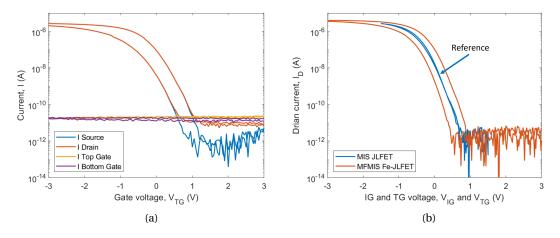

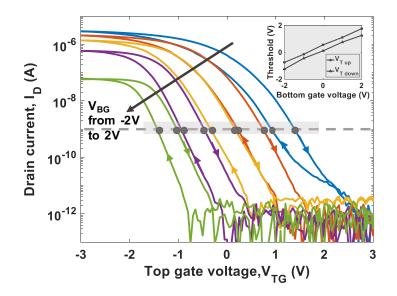

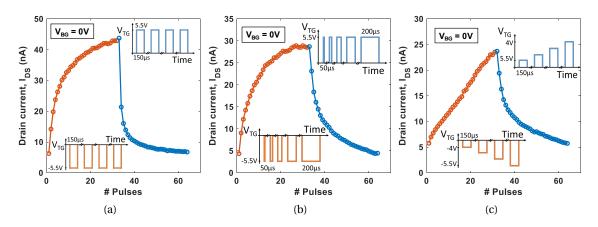

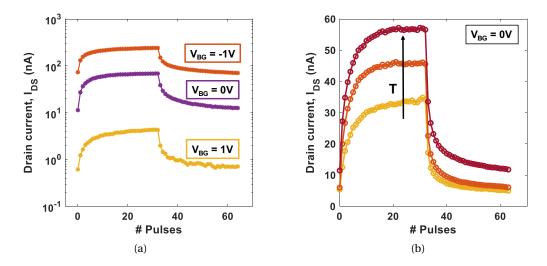

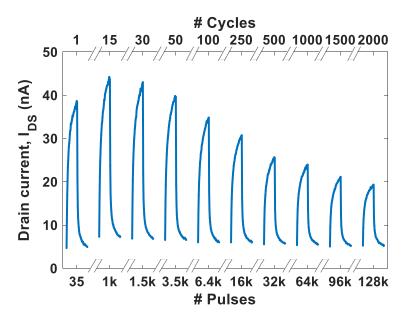

Furthermore, another factor that is affecting ferroelectricity is electric field cycling [75, 76, 68]. HfO<sub>2</sub> based ferroelectric generally requires some electrical cycling to improve the polarization