# High frequency IGCT operation for DC transformer

Présentée le 23 septembre 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire d'électronique de puissance Programme doctoral en énergie

pour l'obtention du grade de Docteur ès Sciences

par

# Gabriele ULISSI

Acceptée sur proposition du jury

Prof. K. A. J. Mulleners, présidente du jury

Prof. D. Dujic, directeur de thèse

Dr S. Alvarez, rapporteur

Prof. B. Li, rapporteur

Prof. E. Matioli, rapporteur

École Polytechnique Fédérale de Lausanne Power Electronics Laboratory Station 11 1015 Lausanne, Switzerland

http://pel.epfl.ch

© 2022 by Gabriele Ulissi

# **Abstract**

In spite of the dominance of ac technology for the vast majority of power transmission and distribution since the late 19<sup>th</sup> century, the past decades have seen an increase in use of dc electrical power. In particular, this has been the case both in high voltage transmission, and in low voltage islanded dc grids such as shipboard power distributions systems, or dc buildings. The increase in interest for dc electrical power is mainly due to its overall decreased losses compared to its ac counterparts, increased flexibility, and ability to more easily integrate renewable generation and energy storage. In this context, medium voltage dc grids currently lack in standardisation and are still an active research topic.

The dc transformer is expected to be a key technology for the operation of future medium voltage dc systems. Essentially, its function is equivalent to the traditional ac transformer in providing an isolated interface between dc buses at different voltage levels. Yet, unlike the purely passive traditional transformer, the dc transformer is also expected to integrate additional functionality, particularly regarding system protection. Most embodiments of the dc transformer proposed in academic publications are based on the dual active bridge, with IGBTs being the semiconductor of choice and with galvanic isolation provided by a medium frequency transformer. Compared to this solution, alternative technologies have been somewhat overlooked, in terms of topologies and devices. In particular, resonant conversion for dc transformer applications has not gained much popularity.

The focus of this thesis is on a medium voltage dc transformer employing IGCTs as semiconductor devices, in a bidirectional series resonant LLC topology. The principle behind the selection of this topology and device is the synergy between the IGCT, which contributes the lowest conduction losses of any actively controlled semiconductor switch, and the series resonant LLC converter principle of operation, which provides low switching loss through soft turn-on and low current turn-off. With this goal in mind, a significant technical challenge to be overcome is the increase of switching frequency of the IGCT well beyond the sub-kHz level at which it traditionally finds application, and into the multi-kHz range, targeted by dc transformer applications.

This thesis contains three main contributions aiming to acquire sufficient knowledge for the design of dc transformer lab demonstrator. For this purpose, the boundary between zero-voltage and zero-current switching of the IGCT is initially explored to identify the lowest switching loss condition through the variation of turn-off current value. Then, in these low-loss conditions, thermal steady state operation of the IGCT is demonstrated at the frequency of 5 kHz for the first time, proving that the IGCT is a device capable of medium frequency operation. Engineering samples of IGCTs optimised on the technology curve through varying levels of electron irradiation are also explored in order to quantify potential benefits in the dc transformer application. Finally, medium frequency operation of the device is extended to an increased voltage level through series connection of IGCTs, through custom ultra-low capacitance, purely capacitive snubbers, designed for the challenges of 5 kHz operation.

Ultimately, the thesis demonstrates that while the IGCT has traditionally found use in sub-kHz, hard-switched applications, its ruggedness and reliability allow its use well beyond its intended applications, and place it comfortably among devices capable of medium frequency operation.

**Keywords** medium voltage, dc transformer, series resonant converter, IGCT, series connection, soft switching

# Sinossi

A partire dalla fine del diciannovesimo secolo, la quasi totalità della trasmissione e distribuzione di energia elettrica ha avuto luogo corrente alternata. Ciononostante, negli ultimi vent'anni si è assistito ad un aumento della presenza di soluzioni in corrente continua, in particolare nella trasmissione di energia su lunghe distanze ad alta tensione, ed in micro-reti isolate dalla rete elettrica. Alcuni chiari esempio di questo fenomeno risultano essere un crescente numero di edifici alimentati in corrente continua, e diversi sistemi di distribuzione di energia elettrica ad uso navale. Il rinnovato interesse per queste tecnologie è una conseguenza dell'aumento dell'efficienza in trasmissione, flessibilità, e della facilità di integrazione della generazione da fonti rinnovabili e sistemi di stoccaggio di energia. In questo contesto, non esiste al momento uno standard determinante le principali caratteristiche di interesse in reti in corrente continua ed in media tensione, che restano tutt'ora un acceso tema di ricerca.

Il funzionamento di future reti in corrente continua ed in meda tensione richiede la presenza di trasformatori in grado di interfacciare linee a diversi livelli di tensione fornendo isolazione galvanica. In pratica, le funzionalità richieste ad un trasformatore in corrente continua sono equivalenti a quelle di un tradizionale trasformatore, ma con l'aggiunta di funzioni di protezione che sono inevitabilmente assenti nei tradizionali trasformatori, essendo questi ultimi componenti completamente passivi. La maggior parte dei trasformatori in de presentati in pubblicazioni accademiche consistono in un inverter e raddrizzatore, separati da un trasformatore ac a media frequenza. Sia l'inverter che il raddrizzatore devono essere bidirezionali per garantire in transito di energia nelle due direzioni quando necessario. In termini di topologie e semiconduttori, le tecnologie prese in considerazione sono numerose.

L'attenzione di questa tesi verte in particolare su un trasformatore in de basato sull'uso dell'IGCT come semiconduttore, in una topologia SRC-LLC. La scelta dei semiconduttori e topologia sono la conseguenza di un lavoro di ricerca già iniziato nel laboratorio negli anni scorsi, sul quale si basa il contenuto presentato in questa tesi. Il criterio che ha determinato questa scelta è il potenziale aumento di efficienza ottenuto grazie al basso livello di energia dissipata in conduzione dall'IGCT, unito al soft-switching offerto dall'SRC-LLC, che offre una riduzione dell'energia dissipata in commutazione.

Questa tesi si divide in sei capitoli, tre dei quali contenenti le sue principali innovazioni. Il loro obiettivo è di acquisire sufficiente comprensione dei fenomeni risultanti dall'utilizzo dell'IGCT nella topologia SRC-LLC per consentire la realizzazione di un prototipo di trasformatore in dc per use in laboratorio. A questo fine, un primo capitolo esplora il confine tra la regione di commutazione in zero-voltage e zero-current per l'IGCT, identificando le condizioni di minima energia dissipata attraverso la variazione della corrente di turn-off. Determinate queste condizioni, si è dimostrata l'operazione continua dell'IGCT alla frequenza di commutazione di 5 kHz nella topologia SRC-LLC. Questo colloca per la prima volta l'IGCT tra i semiconduttori in grado di operare a media frequenza. Questa modalità di operazione viene estesa alla connessione in serie di due IGCT ottenuta con l'ausilio di snubber capacitivi progettati *ad hoc* per la commutazione dell'IGCT in media frequenza.

Questa tesi dimostra quindi che nonstante l'IGCT abbia tradizionalmente trovato applicazione a frequenze inferiori a 1 kHz, il suo uso può essere esteso ben oltre questi livelli, collocandolo tra i semiconduttori capaci di operare in media frequenza.

Parole chiave media tensione, trasformatore dc, LLC-SRC, IGCT, connessione in serie, soft switching

# Acknowledgments

Quote me! Quote me! Amanda Klaeger

First and foremost, my thanks go to my advisor, Prof. Drazen Dujic, for offering me the opportunity of being part of the research activities of PEL. I am grateful not only for the technical and professional advice received, but also for the many insightful conversations about the widest range of topics over the years. These have been just as important a part of my time spent here and have helped me many times, whether with small or big decisions.

Second, I wish to thank Dr. Jakub Kucka, whose enthusiasm and professional brilliance during his time spent in PEL made a significant part of the work of this thesis possible. I am also very grateful to the team of jury members that agreed to examine my thesis: Prof. Binbin Li (external examiner), Dr. Silverio Alvarez (external examiner), Prof. Elison Matioli (internal examiner), and Prof. Karen Mulleners (jury president). The time they spent examining my work has provided me with valuable feedback. On a similar note, I also want to thank Dr. Umamaheswara Vemulapati and Dr. Thomas Stiasny, who are currently with Hitachi ABB Power Grids, Semiconductors, Lenzburg, for the great support received during these past two years.

It goes without saying that I am thankful to my family and friends back in Italy (and also Pascal), who were always there for me during the many good (and a few less good) days.

Last but definitely not least, I want to thank all of my friends from PEL, who have been the central part of my life in the past four years. Whether working, travelling, hiking, drinking, cycling, or just having one of our very many coffees, I cannot imagine spending this time without them. I wish all of them the best, and I want to particularly thank Nikolina, Xiaotong, Philippe, Stefan, Marko, and Miodrag for the very many great days and evening spent together. I will miss seeing all of you at work.

Lausanne, July 2022 Gabriele Ulissi

# List of Abbreviations

DAB dual active bridge

DCT dc transformer

DCT DC transformer

DP double pulse

DUT device under test

EMI electromagnetic interference

EV electric vehicles

GTO gate turn-off thyristor

HVdc high voltage dc

IEGT injection-enhanced gate transistor IGBT insulated-gate bipolar transistor

IGCT integrated gate-commutated thyristor

LVdc low voltage dc

MFT medium frequency transformer MMC modular multilevel converter

MV medium voltage MVac medium voltage ac MVdc medium voltage dc

NPC neutral point clamped

PDN power distribution network

PEBB power electronics building block

PET power electronics transformer

RC-IGCT reverse-conducting IGCT

RMS root mean squared

SCR silicon controller rectifier

SOA safe operating area

SRC series resonant converter SST solid-state transformer

WCU water cooling unit

ZCS zero current switchingZVS zero voltage switching

# Contents

| A  | bstrac | ct                                                                             | i   |

|----|--------|--------------------------------------------------------------------------------|-----|

| Si | nossi  |                                                                                | iii |

| A  | cknov  | wledgments                                                                     | v   |

| Li | st of  | Abbreviations                                                                  | vii |

| 1  | Intr   | roduction                                                                      | 1   |

|    | 1.1    | Background and motivation                                                      | 1   |

|    | 1.2    | Goals and contributions of the thesis                                          | 5   |

|    | 1.3    | Outline of the thesis                                                          | 5   |

|    | 1.4    | List of publications                                                           | 6   |

| 2  | Stat   | ee of the Art                                                                  | 7   |

|    | 2.1    | Introduction                                                                   | 7   |

|    | 2.2    | DC-DC Bulk versus Fractional Conversion                                        | 8   |

|    | 2.3    | Main Topologies for medium voltage dc (MVdc) DC transformer (DCT) Applications | 10  |

|    |        | 2.3.1 Dual Active Bridge                                                       | 10  |

|    |        | 2.3.2 Series Resonant LLC                                                      | 11  |

|    |        | 2.3.3 Modular Multilevel Converter                                             | 14  |

|    | 2.4    | medium voltage (MV) Semiconductor Devices in DCT Applications                  | 15  |

|    |        | 2.4.1 IGBT                                                                     | 15  |

|    |        | 2.4.2 IGCT                                                                     | 18  |

|    | 2.5    | Series Connected Operation of integrated gate-commutated thyristors (IGCTs)    | 22  |

|    | 2.6    | Soft-Switched MV Applications                                                  | 24  |

|    | 2.7    | IGCT Characterisation Test Setup                                               | 26  |

|    | 2.8    | Summary                                                                        | 28  |

| 3  | IGC    | CT Commutation in ZVS and ZCS Conditions                                       | 29  |

|    | 3.1    | Introduction                                                                   | 29  |

|    | 3.2    | IGCT Switching Frequency Limitations and Employed Devices                      | 30  |

|    | 3.3    | Series Resonant LLC Operation                                                  | 32  |

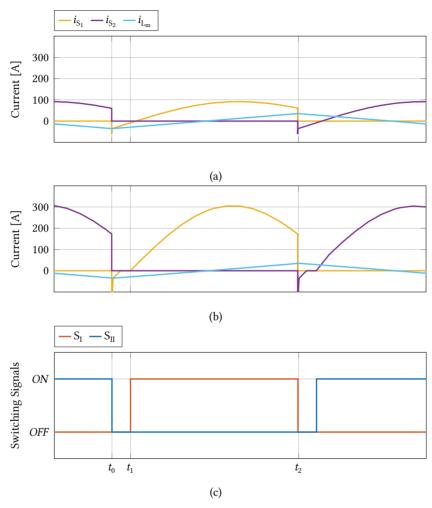

|    |        | 3.3.1 Superresonant Operation                                                  | 32  |

|    |        | 3.3.2 Subresonant Operation                                                    | 33  |

|    | 3.4    | Configuration of the IGCT Test Setup                                           | 37  |

|    | 3.5    | IGCT Switching Losses at Ultra-Low Turn-Off Current                            | 39  |

|    |        | 3.5.1 Understanding the ZVS/ZCS Transition                                     | 39  |

|    |        | 3.5.2 Effect of Pre-Flooding and Irradiation                                   | 42  |

|    | 3.6    | Summary                                                                        | 46  |

| 4  | Stea   | ady State Operation at 5 kHz                                                   | 47  |

|    | 4.1    | Introduction                                                                   | 47  |

|    | 4.2    | Configuration of the IGCT Test Setup                                           | 49  |

|   | 4.3 | Demonstration of 5 kHz Operation                              | 50 |

|---|-----|---------------------------------------------------------------|----|

|   |     | 4.3.1 Steady-State Operation                                  | 50 |

|   |     | 4.3.2 Switching Transients                                    | 51 |

|   | 4.4 | Computation of Losses in Target Application                   | 54 |

|   | 4.5 | Test Setup Thermal Modelling and Junction Temperatures        | 56 |

|   |     | 4.5.1 Junction Temperature Estimation                         | 58 |

|   | 4.6 | Summary                                                       | 61 |

| 5 | Res | onant Operation of Series Connected IGCTs                     | 63 |

|   | 5.1 | 63                                                            |    |

|   | 5.2 | IGCT series connection in SRC-LLC                             | 64 |

|   |     | 5.2.1 Static Voltage Balancing                                | 64 |

|   |     | 5.2.2 Dynamic Voltage Balancing                               | 66 |

|   | 5.3 | Configuration of the Test Setup for Series Connected DP Tests | 68 |

|   | 5.4 | IGCT Low Current Turn-Off                                     | 70 |

|   |     | 5.4.1 Commercial reverse-conducting IGCTs (RC-IGCTs)          | 70 |

|   |     | 5.4.2 Higher Electron Irradiated RC-IGCTs                     | 73 |

|   | 5.5 | Resonant Operation                                            | 76 |

|   | 5.6 | Conclusion                                                    | 79 |

| 6 | Sun | nmary and Future Work                                         | 81 |

|   | 6.1 | 6.1 Summary                                                   |    |

|   |     | 6.1.1 1: Optimal Turn-Off Current                             | 81 |

|   |     | 6.1.2 2: Demonstration of 5 kHz Operation                     | 83 |

|   |     | 6.1.3 3: Ultra-Low Snubber Capacitance                        | 84 |

|   | 6.2 | Conclusion                                                    | 85 |

|   | 6.3 | Future Work                                                   | 86 |

|   |     | 6.3.1 10 kV Side                                              | 86 |

|   |     | 6.3.2 Protection                                              | 88 |

|   |     | 6.3.3 Thermal Effects                                         | 88 |

# 1 Introduction

#### 1.1 Background and motivation

The second half of the 19<sup>th</sup> century saw the beginning of large-scale electrification with both dc and ac systems coexisting in urban and private illumination applications. While dc systems initially gained the upper hand thanks to the availability of dc generators, this advantage was soon lost. The late 1880s saw the advent of both the transformer and the induction generator, two key technologies that enabled transmission of electrical power with smaller losses and over a significantly increased distance compared to the established 110 V dc systems. The reduced operating cost, together with the ease of interruption of ac current, allowed ac systems to definitively prevail over their dc counterparts by the end of the century. To this day, ac power transmission and distribution is by far the prevailing technology, having been well-established for over a century and leveraging vast amounts of accumulated technical know-how. Nevertheless, as early as the 1950s, dc power transmission once again found application in the first commercial long-distance 110 kV high voltage dc (HVdc) line connecting mainland Sweden with Gotland and employing mercury-arc line commutated converters. This installation was the first of its kind and demonstrated the feasibility of HVdc transmission, but the number of new installations remained modest in the following years: the advantages of dc transmission were offset by the comparatively high maintenance, low reliability and high operating temperatures of mercury-arc valves. It was only with the advancements in material sciences and semiconductor technologies that characterised the following decades which allowed lower maintenance solutions based on thyristor technology in the 1970s, and with GTOs and IGBTs later becoming the prevalent devices.

**Fig. 1.1** a) ASEA Mercury-arc valve, 1971 (photo courtesy of ABB); b) Experimental thyristor valve tested in Gotland link, 1967 [1]; c) Contemporary GE IGBT-based MMC valve hall.

1

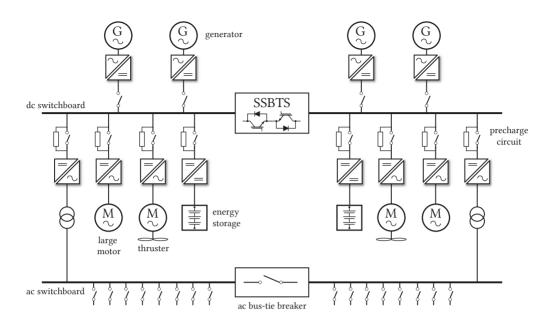

**Fig. 1.2** LVdc shipboard PDNs can achieve higher efficiency and operate without the need for bulky low-frequency transformers [6], [7].

With the use new semiconductor devices, the dc transmission of electrical power has numerous advantages over traditional ac systems. First of all, the absence of reactive power transmitted over the lines reduces losses for a given transmitted active power. Additionally, the line voltage at the receiving end of the line will be less sensitive to the operating conditions compared to that of an ac link, as there is no reactive voltage drop, nor capacitive currents providing reactive power and increasing the line voltage in low-load conditions. Finally, the reduced presence of skin and proximity effects mitigates the increase of line resistance due to these phenomena, and ultimately the resulting loss.

Naturally, these benefits are not limited to the voltage levels of several hundreds of kV present in HVdc systems: low voltage dc (LVdc) systems have already become a commercial reality at voltage levels below 1 kV. Such systems are particularly popular in applications which are intrinsically stand-alone installations, and therefore do not suffer from the inertia associated with the adoption of solutions in grid-connected operation, such as marine power distribution networks (PDNs) and offshore applications. As seen in Fig. 1.2, in this context dc distribution has the additional benefits of eliminating the need for bulky line frequency transformers, and of rendering the synchronisation of the micro-grid's generators unnecessary through the rectification of their output [2], [3].

Such LVdc systems leverage well established, efficient, and affordable semiconductor technologies available at the 1 kV voltage level. Nevertheless, they also required the addition of innovative solutions, in particular concerning the protection of the system: fault evolution in dc systems is several orders of magnitude faster than in traditional ac systems due to the significantly reduced inductance levels, and therefore requires the use of ultra-fast solid state protection solutions instead of slow conventional mechanical breakers [4], [5].

With LVdc shipboard PDNs having proved the commercial viability of dc systems, the next step in

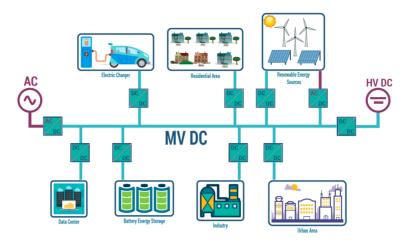

$\textbf{Fig. 1.3} \quad \text{Medium voltage dc distribution networks facilitate the integration of dc loads, generation, and storage.}$

the drive for ever-increasing efficiency is the increase of the dc PDN voltage to the medium voltage (MV) level, enabling installed power similar to those of medium voltage ac (MVac) shipboard PDNs, but maintaining the increased efficiency and flexibility of dc systems.

While shipboard PDNs lend themselves to innovative solutions thanks to their islanded operation, the replacement of MVac systems with medium voltage dc (MVdc) systems offers significant advantages also in energy distribution. These advantages go beyond system efficiency, in particular thanks to the changing nature of modern electrical loads. Fig. 1.3 displays how an MVdc distribution network can reduce the number of required conversion stages in the integration of dc loads, generation, and energy storage, allowing for more compact and less costly solutions [8], [9].

In spite of these benefits, MVdc networks are not yet a reality. The main impediment in their development and commercial use lies in limitations of existing technologies, with examples being suitable protection devices, and the dc transformer (DCT). The DCT in particular has been the object of much research in the past years, as it is required to perform the crucial function of providing an isolated interface between dc buses at different voltage levels. Currently, no commercial embodiments of a DCT are deployed, and the device exists only as part of research installations, in which various

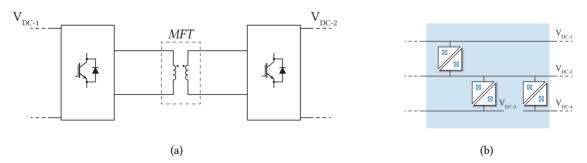

**Fig. 1.4** a) A generic dc transformer concept is consituted by a bidirectional inverter and rectifier stage separated by a medium frequency transformer (MFT); b) the role of the dc transformer is to interface buses at different voltage levels in dc networks.

solutions based on different topologies and semiconductor devices have been proposed [10]-[12].

Figs. 1.4(a) and 1.4(b) display a generic concept of DCT and its integration in a dc network, respectively. In principle, the device is composed of bidirectional inverter and rectifier stages separated by a MFT, and is intended to perform a very similar role to that of a conventional transformer in an ac system. More specifically, just like an ac transformer, the device is expected to provide galvanic isolation, bus interconnection at different voltage levels, and, in the context of this thesis, open-loop operation without the need to be externally provided with an operating setpoint. In addition to the functionality of an ac transformer, the DCT is also expected to provide some protection functions and limited ancillary services to the dc grid.

One of the more significant advantages of the use of a DCT with respect to a traditional ac line frequency transformer is the significant decrease in weight and footprint. This is achieved through the reduction in volume of required magnetic material allowed by the increase in fundamental operating frequency. To capitalise on this benefit, switching frequencies in high-power DCT applications are in the range of several kHz (or for SiC devices several tens of kHz). To achieve such switching frequencies, the use of the SiC MOSFET as a semiconductor device has steadily being gaining interest, but the preferred solution remains today the Si IGBT, being widely available and having a demonstrated track record of reliability, good switching characteristics and ease of gate drive [13], [14].

Nevertheless, in spite of the popularity of the IGBT in many applications, the few decades have seen the emergence of an alternative device providing reliable performance at the MV level in the form of the IGCT, but with its application mainly being reserved to the power level of several MW and switching frequencies below 1 kHz [15]–[18]. Compared to the IGBT, the IGCT features comparable switching losses, but being a thyristor-based device it benefits from lowered conduction loss, improved reliability, larger safe operating area (SOA), and lower thermal resistance between junction and case in press packed devices thanks to the excellent utilisation of the silicon wafer area.

It is the IGCT's low conduction loss that highlight it as an interesting candidate for the high-power ratings of DCT applications. This is particularly the case in combination with soft-switched topologies such as the LLC-SRC, which can combine the device's intrinsically low conduction loss with the low switching losses deriving from the topology's operation. The combination of these two technologies has been shown in [19] to allow the operation of IGCTs at unprecedented frequencies for this kind of device.

The work presented in [19] demonstrated through a custom configurable test setup the feasibility of high-frequency IGCT operation in operating conditions equivalent to those witnessed by the device during operation in the LLC-SRC topology. In particular, it has demonstrated that through the reduction of the devices' turn-off current to a very low level, the switching loss can be reduced sufficiently to allow operation at a frequency an order of magnitude higher than what is possible to achieve in traditional hard-switched applications, placing the IGCT comfortably among the suitable semiconductor options for use in DCTs.

#### 1.2 Goals and contributions of the thesis

The goal of this thesis is to expand on the work presented in [19] and lay the groundwork for the prototype realisation of a DCT demonstrator interfacing two dc buses at voltages of 5 kV and 10 kV, respectively. In practise, this implies several steps. First, to increase the IGCTs' switching frequency

to the desired level of 5 kHz. As such a significant increase in switching frequency inevitably results in increased switching loss, the work is started by a comprehensive investigation of the switching behaviour of IGCTs in zero voltage switching (ZVS) and zero current switching (ZCS) conditions. This builds a strong understanding of the IGCT behaviour in various soft-switching conditions, and demonstrates that ZVS operation is advantageous for the minimisation of switching loss in resonant operation. The operation of the IGCT is described as part of the thesis as it is relevant to the understanding of the presented work. Second, to enable operation of the solution at a voltage level of 5 kV, series connection of the employed 4.5 kV IGCTs is required. Therefore, the switching behaviour of the devices in series connection and with low turn-off current is investigated. This is done with particular focus on the sizing of dynamic voltage sharing snubbers and turn-off current values. Finally, steady state operation of the IGCTs at a frequency of 5 kHz is demonstrated for both individual and series connected devices. Therefore, the main contributions of the thesis can be summarised as:

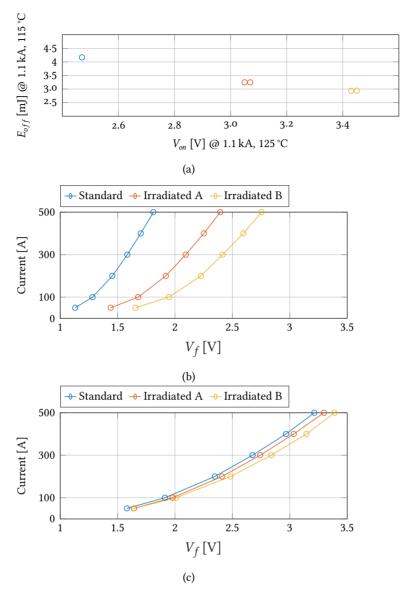

- The identification, through the use of the same test setup presented in [19], of optimal switching conditions resulting in minimised switching loss for 4.5 kV, 68 mm IGCTs having undergone varying level of electron irradiation. ZVS and ZCS switching conditions are compared, and ZVS switching is found to be beneficial as it results in lower overall loss in resonant switching conditions. Optimal turn-off current levels resulting in minimal loss are determined for the varying electron irradiation levels of the devices.

- The demonstration, with the identified optimal turn-off current level and ZVS switching conditions, of steady state soft-switched operation of the devices at a frequency of 5 kHz at a dc link voltage of 2.5 kV, and varying levels of load. The very effective water cooling system available in the laboratory installation allows for safe test conditions for the devices, but junction temperature estimation based on the device losses predicts the feasibility of high frequency operation also with a reduced cooling effort.

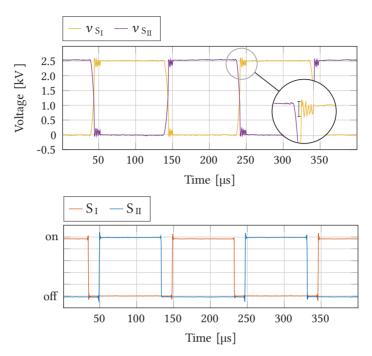

- The demonstration of resonant operation in soft-switched conditions at 5 kHz at increased voltage level through the series connection of 4.5 kV, 68 mm devices. This is achieved with the use of purely capacitive dynamic voltage sharing snubbers with ultra-low values of capacitance, which are designed specifically for use with the ultra-low levels of turn-off current characteristic of subresonant LLC operation.

## 1.3 Outline of the thesis

This thesis is organised in 6 chapters, as follows:

- Chapter 2 covers the state of the art of high power dc converters and their application in MV systems. Existing work on converter topologies by academic and industrial players is presented, together with the most commonly employed semiconductor devices and their applicability to the LLC-SRC topology.

- *Chapter 3* discusses in detail the operation of the LLC-SRC topology and justifies the selection of IGCT switching mode between ZVS and ZCS. The switching energy in the two operating conditions is compared and the measured trends justified. GCTs differing by level of electron irradiation are compared and optimal switching conditions for the various devices identified, considering the effect of current pre-flooding.

- Chapter 4 demonstrates the operation of IGCTs at a frequency of 5 kHz in the conditions occurring in a series resonant LLC converter, considering standard, commercially available device, and custom engineering samples optimised on the technology curve through varying levels of electron irradiation. The switching and conduction losses of the devices in these conditions are discussed and compared.

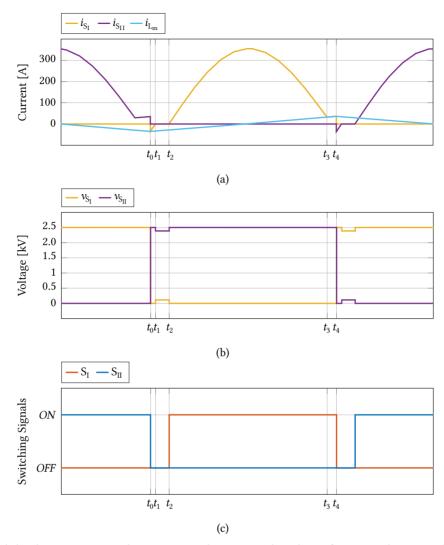

- *Chapter 5* deals with series connection of IGCTs under ultra-low turn-off current conditions, allowing for increased operating voltage of the IGCT-based LLC-SRC topology. The effects of such conditions on snubber sizing are analysed and purely capacitive snubbers ensuring adequate voltage sharing of series connected devices at the 5 kV are designed and tested in double-pulse tests. Finally, 5 kHz series connected operation of the devices is demonstrated.

- *Chapter 6* concludes the thesis summarising the main obtained results and suggesting future work on the topic.

#### 1.4 List of publications

Journal papers:

- J1. G. Ulissi, U. R. Vemulapati, T. Stiasny, and D. Dujic, "High-frequency operation of series-connected igcts for resonant converters," *IEEE Transactions on Power Electronics*, vol. 37, no. 5, pp. 5664–5674, 2022

- J2. G. Ulissi, J. Kucka, U. R. Vemulapati, T. Stiasny, and D. Dujic, "Resonant igct soft-switching: Zero-voltage switching or zero-current switching?" *IEEE Transactions on Power Electronics*, vol. 37, no. 9, pp. 10775–10783, 2022

Other publications, related to research work carried out during the PhD but not included in this thesis:

- J1. G. Ulissi, S.-Y. Lee, and D. Dujic, "Solid-state bus-tie switch for shipboard power distribution networks," *IEEE Transactions on Transportation Electrification*, vol. 6, no. 3, pp. 1253–1264, 2020

- J2. G. Ulissi, S.-Y. Lee, and D. Dujic, "Scalable solid-state bus-tie switch for flexible shipboard power systems," *IEEE Transactions on Power Electronics*, vol. 36, no. 1, pp. 239–247, 2021

- J3. G. Ulissi, S. Kim, and D. Dujic, "Solid-state technology for shipboard dc power distribution networks," *IEEE Transactions on Industrial Electronics*, vol. 68, no. 12, pp. 12 100–12 108, 2021

- J4. S. Kim, J. Kucka, G. Ulissi, S.-N. Kim, and D. Dujic, "Solid-state technologies for flexible and efficient marine dc microgrids," *IEEE Transactions on Smart Grid*, vol. 12, no. 4, pp. 2860–2868, 2021

- J5. S. Kim, G. Ulissi, S.-N. Kim, and D. Dujic, "Protection coordination for reliable marine dc power distribution networks," *IEEE Access*, vol. 8, pp. 222 813–222 823, 2020

- C1. G. Ulissi, S.-Y. Lee, and D. Dujic, "Four quadrant bus-tie switch for protection of shipboard power systems," in 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), 2020, P.1–P.9

- C2. G. Ulissi, S.-Y. Lee, and D. Dujic, "Scalable marine bus-tie switch for switchboard interconnections," in *PCIM Europe digital days* 2020, 2020, pp. 1–10

C<sub>3</sub>. S. Kim, G. Ulissi, S.-N. Kim, and D. Dujic, "Marine dc power distribution networks," in *PCIM Europe 2019*, 2019, pp. 1–8

#### Patents:

P1. G. Ulissi, D. Dujic, S. H. Kim, D. Y. You, and S. Y. Lee, "bus tie switch and bus tie switch apparatus", KR Patent 20200138476, 2021

# 2 State of the Art

High power MVdc applications have seen a number of different solutions being proposed in an equally wide range of use case scenarios. Different concepts, topologies, semiconductors, and operating modes can be combined to tailor the performance of the conversion stage to the application at hand, providing plenty of degrees of freedom in design. This chapter provides an overview of the most frequent technologies considered for MV dc transformers, gradually narrowing down the many possible options and justifying the selection of the technologies discussed in this thesis.

#### 2.1 Introduction

The new solutions offered by MVdc power collection and distribution grids offer a strong alternative to existing ac networks at the same voltage level in several applications. However, the absence of adequate conversion or protection technologies is almost always a hindrance to practical implementations of MVdc, no matter the advantages they can bring [20]. Additionally, and perhaps more importantly, the lack of standardised technologies currently brings the cost of such installations to levels significantly higher than those of their comparable traditional ac counterparts, creating a chicken-and-egg problem which currently has not yet been solved.

In applications such as wind farm collection networks, on- and off-shore, MVdc networks are considered for the collection of energy generated by each turbine, with the whole MVdc collection network then being interfaced to the on-shore grid. The interfacing of the rotating generators in the wind turbines to the MVdc collection network requires rectification and voltage step-up, which can be achieved either in a single ac-dc stage or by cascaded ac-dc and dc-dc stages [21]. Several important advantages have been identified in the use of such connection networks, ranging from increased efficiency and lowered cost, to system scalability and lowered footprint and filtering efforts. Nevertheless, the absence of suitable protection and conversion technologies, together with the absence of standardised dc voltage levels, result in the absence of large scale installations of MVdc collection systems, with photovoltaic installations suffering from the same issues [22]. The replacement of MVac distribution with MVdc distribution in certain applications can be seen to be another example in which MVdc is the next logical step.

The use of all-electric ship power systems has already taken place at the low voltage (LV) level. Many advantages are evident in the application: first and foremost the elimination of bulky MVac transformers resulting in significant space savings and easier integration of alternative energy sources and energy storage, overall resulting in significant expected fuel and therefore cost savings [23], [24]. Additionally, the need to synchronise multiple generators to create an ac power distribution network is removed. But again in this application a large technology gap is still to be bridged, with similar

observations as those applying to on-shore microgrids [25], [26]. Finally, large data centers internally employ LVdc distribution and can be considered as large dc loads, with dc distribution improving overall efficiency and eliminating ac-dc conversion [27]–[30].

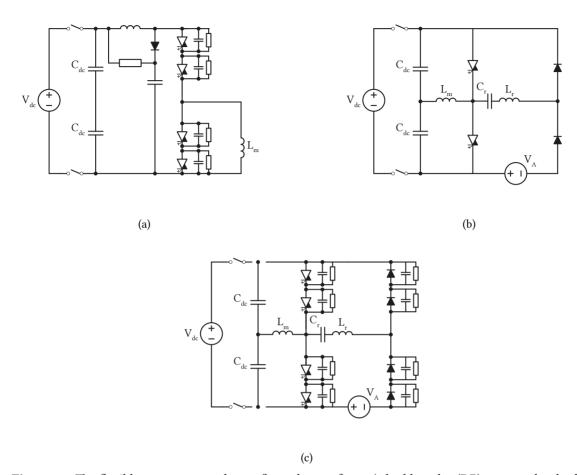

MVdc networks can connect various loads and sources to the existing ac system. Existing commercially available technologies such as monolithic multilevel converters and the modular multilevel converter (MMC) can be used for MVdc to MVac interconnection, but dc-dc conversion between different voltage levels is still an open research question both in terms of operating principles and technologies. Modern means of power generation and new loads, such as electric vehicles (EV) charging stations, energy storage systems, and many more require a solution in terms of energy systems power flows and its control. In this context, this thesis proposes an IGCT-based DC transformer (DCT) solution differentiating itself from most of the existing literature by relying on bulk power transfer, as opposed to the more commonly advertised fractional or nowadays popular modular solutions. To achieve this, several choices are made regarding employed topology, devices, and operating mode, which are contextualised and justified as part of this chapter.

#### 2.2 DC-DC Bulk versus Fractional Conversion

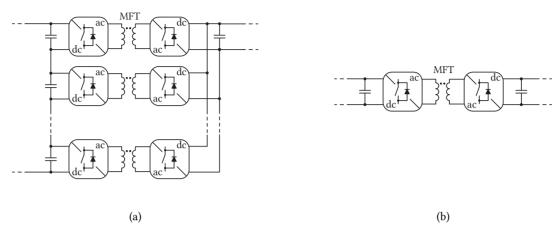

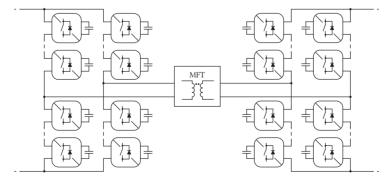

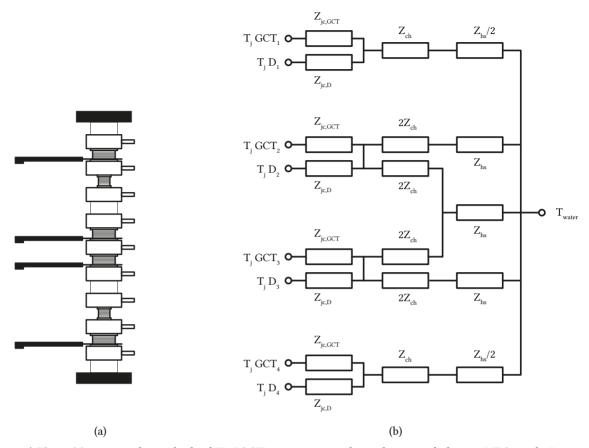

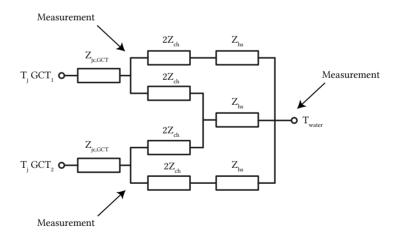

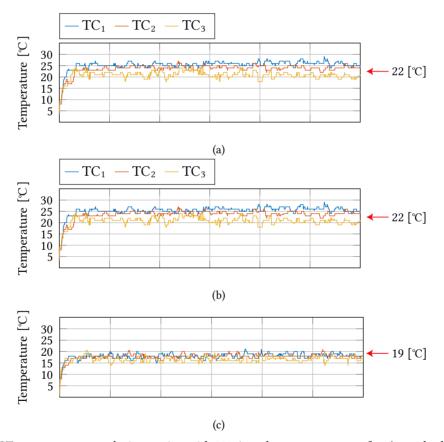

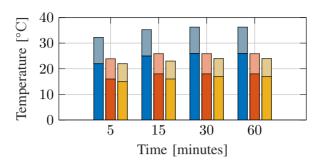

The variety of voltage and power levels of MVdc networks impose scalability as a necessary feature of any DCT solution. Such scalability in power processing can be achieved by two radically different approaches: the first considers series or parallel connection of PEBBs, each containing an MFT unit. Each PEBB has a lower power rating than the complete system, but the use of multiple units in the appropriate configuration achieves the rating of the overall system. The second approach uses semiconductor devices specifically sized for the application, resorting to series or parallel connection where necessary and a single MFT, as seen in Fig. 2.1. In practise, this results in a single PEBB rated for the full power of the application. The two methods result in different implications on the overall power electronics system.

Arguably, a significant amount of work carried out on the topic of MVdc conversion stems from the solid-state transformer (SST) concept initially reported in [33]. Over time, numerous embodiments of this concept have been reported, with [34]–[37] being examples resulting from the work of the *UNIFLEX* consortium, *HEART*, *GE*, and *ABB*, respectively. Over time, the concept has found application in both the traction and smart-grid domains, but its idustrial implementations remain few and far inbetween whether in fractional or bulk power processing configurations. Compared to its industrial applications, many more academic examples [34], [38]–[47] exist, with multiple laboratory-scale prototypes having been realised and based on different topologies and control schemes. Among these existing examples, there is a prevalence of modular solutions based on individual PEBBs processing a fraction of the power of the overall converter [48], [49].

Fractional power processing has many benefits, which derive from the necessary underlying modularity of such topologies. The use of several PEBBs to achieve the required power rating allows parallel or series connection of such units, allowing simple scaling of the overall converter voltage and power rating without requiring the redesign of the PEBB. Additionally, redundant units can be employed to reduce the voltage stress on semiconductor devices, and can be bypassed in the event of a fault, allowing uninterrupted operation for the remaining duration of the maintenance interval. Further, depending on the PEBB configuration, plug-and-play functionality can be explored, where the failed PEBB can be replaced by a new unit with minimal effort and in minimal time.

**Fig. 2.1** a) In fractional power processing, each ISOP power electronics building blocks (PEBBs) processes a fraction of the total rated power of the converter, while in b) bulk processing a single monolithic structure handles the full power of the topology.

Nevertheless, fractional power processing topologies also have their disadvantages. As each PEBB is a standalone unit, it is equipped with semiconductors, passive, and magnetic components, and will be equipped with its own control unit. This significantly increases the overall component count of the topology with inevitably undesirable consequences both on the overall system reliability, and both electrical and mechanical complexity. Additionally, each employed PEBB must be designed in terms of insulation coordination for the highest system voltage. This results in a component than cannot be employed with higher system voltages, and that is oversized for lower voltage applications. Finally, power sharing between the PEBBs must be addressed either in design or through control, while bypass elements must be added if operation of the topology is to be continued in the event of PEBB failure.

Compared to fractional power processing solutions, configurations providing bulk power processing are simpler, have lower mechanical and electrical component count, and benefit from reduced control complexity. These benefits are nevertheless offset by the need to provide a custom design for each application's voltage and power rating, with limited options for reusing existing solutions. In addition, the effects of a failure in the power stage cannot be contained as easily as in a topology employing multiple PEBBs, and must rely on an increase of the number of employed semiconductors.

Nevertheless, the goal of the DCT is to provide functionality as close as possible to that of a conventional ac transformer. With this in mind, the crucial bus interfacing role of the DCT requires its implementation to achieve high levels of reliability, that benefit from the relatively low component count achieved through the parallel and series connection of individual semiconductor devices. The complexity, high component count, and increased control effort are particularly undesirable in the DCT application, and bulk power processing solutions are therefore preferable in this context and for this reason. Therefore, a bulk power processing solutions is selected in the context of this thesis.

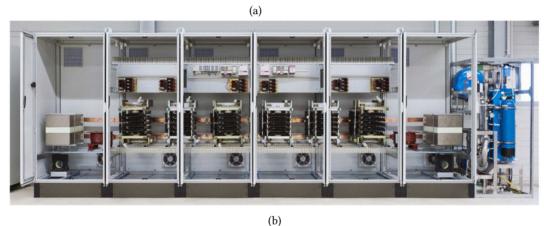

**Fig. 2.2** a) 1.2 MW power electronics traction transformer prototype described in [31] and employing several power processing units in an ISOP configuration; b) 5 MW, 5 kV monolithic three-phase dual active bridge (DAB) converter from [32].

# 2.3 Main Topologies for MVdc DCT Applications

Among the suitable topologies to achieve bulk power conversion in MVdc systems, three in particular are promising and have been well-investigated.

#### 2.3.1 Dual Active Bridge

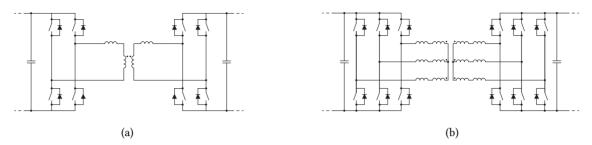

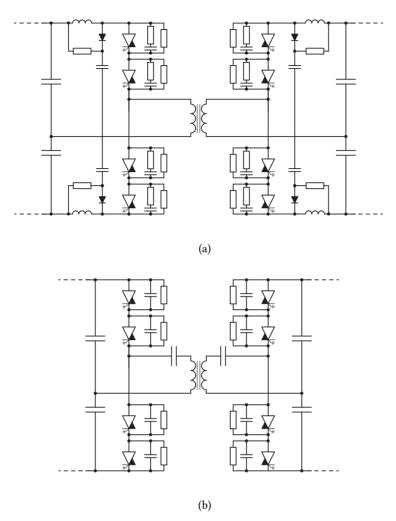

The first considered topology, that has seen the most research effort for DCT applications, is the DAB. The topology has been thoroughly explored both in academic and industrial settings starting with [50]–[52], which first introduced the concept as far back as in 1990. Leveraging improvements in both magnetic and semiconductor components, the DAB is once again at the centre of research attention both in its single-phase and three-phase implementation, as displayed in Fig. 2.3. References [53]–[59] describe the steady state operation, design, control strategies and dynamic modelling of the topology. In essence, its foremost benefit is its simple operating principle of an inverter and active

rectifier interfaced by a medium frequency transformer. This leads to a phase-shift power transfer control similar to well-known ac network principles, which in an ideal case results in active power transfer being described by

$$P = \frac{nV_1V_2}{f_{sw}L}\Phi(1 - 2\Phi) \tag{2.1}$$

as the two bridges are operated with constant duty cycle approaching 50 %, the phase angle  $\Phi$  is the only degree of freedom available for control, which is simple and easy to implement.

Operation of the converter at medium frequency ensures that the DAB can provide both isolation and voltage transformation through the use of a high power density transformer. For three-phase DAB, continuous active power flow is provided, reducing voltage ripple and therefore allowing for smaller sizing of dc capacitors. The power flow of the topology is regulated through the stray inductance of the transformer by phase shifting the operation of the inverter and rectifier stage that both operate producing square wave voltage waveforms. In such an operating mode, semiconductor devices operate in soft-switched condition (ZVS specifically), reducing switching losses and resulting in high conversion efficiency.

Recently, there have been ongoing research efforts focusing on the improvement of the DAB performance with the purpose of enabling its use in dc grid distribution substations in the role of DCT. By employing three-level inverter and rectifier stages, or by using auxiliary circuitry, the ZVS operation of the topology can be extended, potentially enabling increased switching frequencies by the employed medium voltage semiconductor devices [60]. Additionally, fault ride-through capability and short circuit current control can be achieved through variable duty cycle control [60], [61], which reduced or potentially eliminated the need for additional current breaking componentry in dc grid applications. Nevertheless, the main notable advantage of the topology remains a low component count and relatively small size and weight (depending on the operating frequency).

On the other hand, while the converter can operate in ZVS, its operating range in such a condition is relatively limited. Circulating currents also represent a drawback of the topology, limiting efficiency by causing inevitable losses in both semiconductor components and transformer windings (although this is not exclusive to the DAB topology). Additionally, the topology requires bulky input and output dc-link capacitors to supply the high root mean squared (RMS) values of current, which have the ulterior disadvantage of limiting the power density of the converter [62]. Finally, while the control of the topology based on the power transfer characteristic described through 2.1 is simple, it does not strictly correspond to the description of DCT as intended in this thesis. The power transfer in the DAB topology is determined by an externally provided setpoint, and not by the relative voltages of the interfaced buses, as is the case in a traditional transformer.

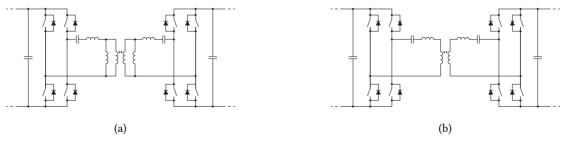

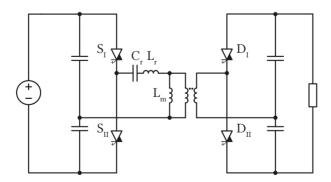

#### 2.3.2 Series Resonant LLC

The second considered topology is the LLC variant of the series resonant converter (SRC), which was first introduced in [65], [66] for a galvanically isolated dc transformer-type application. Reference [67] discusses and develops theory for a non-isolated application, but it is relatively straightforward to extend the presented concepts to isolated topologies. The operating principle of the SRC-LLC is to have a three-element series resonant circuit excited by a rectangular input voltage. Due the the impedance of the resonant tank, the square wave voltage excitation results in in quasi-sinusoidal currents. The topology's voltage transfer characteristic is obtained based on the first harmonic

Fig. 2.3 a) Single and b) three-phase DAB topologies [63], [64].

approximation [68] and is well known in literature. The approximation is based on power transfer happening only at the converter's tank resonant frequency. As discussed in [68]

$$\frac{v_{out}}{v_{in}} = \frac{mf_n^2}{(f_n^2(m+1)-1)^2 + (f_n mQ(f_n^2-1))^2}$$

(2.2)

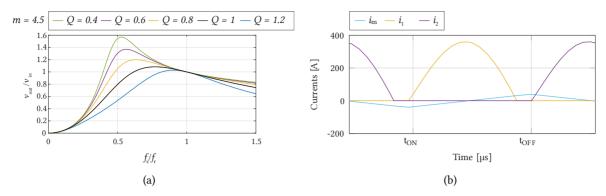

where m is the ratio of inductances  $L_m/L_r$ , Q is the load parameter given as a the ratio  $Z_r/n^2R_{ac}$  between the natural impedance  $Z_r = \sqrt{L_r/C_r}$ , and the equivalent ac resistance of the load referred to primary. An example of the topology's voltage transfer characteristic is displayed in Fig. 2.5(a). In many low power applications, regulation of output voltage is achieved by varying the switching frequency taking advantage of the relatively linear behaviour of the characteristic around the resonant frequency. The ratio between resonant frequency  $f_r$  and switching frequency  $f_s$  affects different aspects of the operation of the topology. In many low power application, the ratio between resonant and switchign frequency is used to control output voltage, leveraging the almost linear slope of the transfer characteristic in Fig. 2.5(a) around  $f_s = f_r$  [68]–[72]. While this achieves output voltage control, the current level interrupted by the semiconductor devices varies depending on the value of  $f_s$  and on load condition. This results in semiconductor switching losses being time-varying and potentially hard to predict, which is not desirable in the envisioned DCT application.

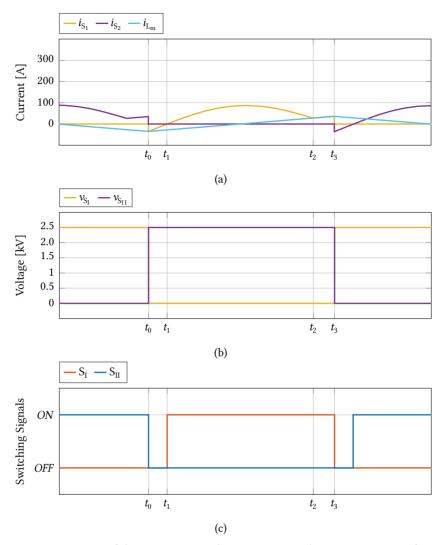

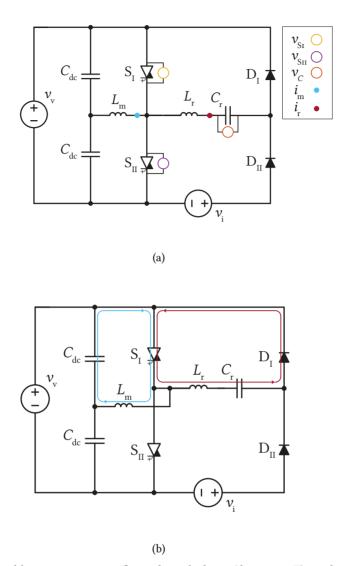

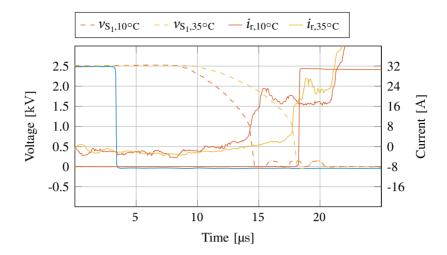

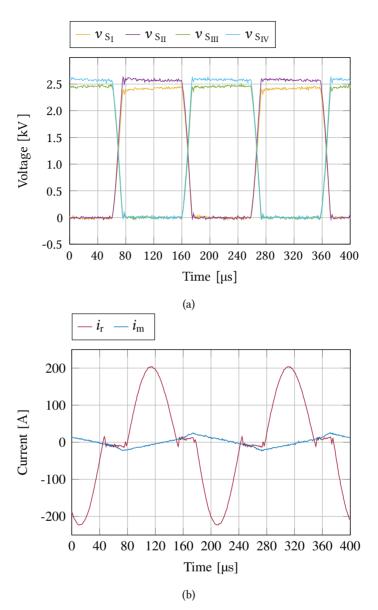

Significantly more interesting for the DCT is the subresonant operating mode. In this mode, the switching frequency is kept constant and such that  $f_s < f_r$ . Typical waveforms for this operating mode are displayed in Fig. 2.5(b). In subresonant operation, the value of the turn-off current can be set by design and is independent of load, and the transfer characteristic is stiff, guaranteeing almost constant output voltage under load variation. This thesis will only look into subresonant operation of the SRC-LLC, as it is in this condition that turn-off current is maintained almost constant over the

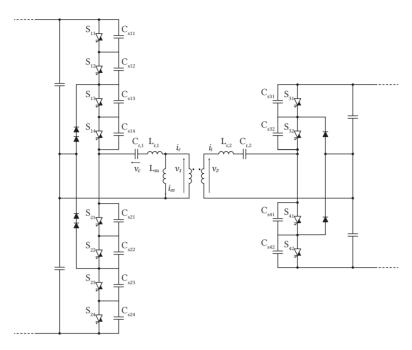

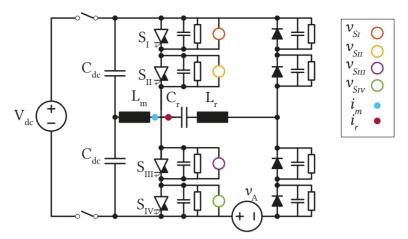

**Fig. 2.4** a) A bidirectional SRC-LLC topology (shown here with split resonant capacitor) is able to operate in open loop without external setpoint and has a relatively low transformer magnetising inductance compared to the b) LC resonant converter.

**Fig. 2.5** a) An example of SRC-LLC transfer ratio displays has close to unity value in an interval around  $f_s = f_r$ , which is leveraged in b) subresonant operation of the topology.

operating range of the converter. Of the topologies discussed in this section, the SRC-LLC has the very significant advantage of being capable of leveraging this stiff voltage transfer ratio to allow operation of the converter in open loop. That is to say that no external power setpoint is to be provided to the converter, and the topology's voltage transfer characteristic ensures power transfer similarly to a traditional ac transformer. This is a unique feature of the SRC-LLC and lends itself particularly well to the DCT application which, in principle, is intended to operate without an external power setpoint. Additionally, the topology can operate in ZVS condition across the whole operating range (this is analysed in Chapter 3), resulting in low commutation loss and therefore potentially increased switching frequencies, which are beneficial in terms of reduction of size and weight of the topology's passive component. For this reason, the work of [19] has focused on this topology, which is also further analysed and explored in this thesis.

Although it is particularly well suited to the DCT application, the SRC-LLC has its own drawbacks. First, even in no load condition, a low, constant level of circulating current is present in the topology due to the transformer's magnetising inductance, the value of which is non-negligible. This results in first approximation in constant switching losses over the whole operating range. This results in a minimum level of loss being present in the topology on the primary side even if the load is disconnected, and potentially in relatively low efficiency in low power operation. On the other hand, this represents a trade-off, as this current also allows ZVS operation, which together with the constant turn-off current guarantees almost constant losses over the operating range. Additionally, while for the most part the inductive elements of the resonant tank can be integrated in the MFT, resonant capacitor banks capable of conducting the totality of the load current must be present, increasing the component count.

In spite of these shortcomings, the SRC-LLC still boasts a relatively low component count, simple scalability through series connection of semiconductor devices, and most importantly open loop operation in the DCT application, making it a very viable topology in this context.

#### 2.3.3 Modular Multilevel Converter

The final considered topology is the MMC: initially finding use in the HVdc domain [73], much research effort has been done in the direction of its MVdc applications. One of the main advantages of the topology is how it can be scaled up in voltage by increasing the total number of cells in each branch, and how it can be scaled up in current through the parallel connection of branches [74]. In

ac applications, increasing the number of switching cells has the benefit of allowing the accurate synthetisation of sinusoidal waveforms that significantly reduce, or even eliminate, the filtering needs at the ac terminals of the converter.

As the voltage rating of each cell is significantly lower of that of the overall converter, the use of LV semiconductor devices is possible, without their series connection, which allows the converter to benefit from the strongly reduced switching losses of these devices when compared to discrete MV devices achieving the same blocking voltages. Additionally, when synthesiszing ac waveforms, each cell switches at a frequency significantly lower than what is observed at the converter terminals, with positive impact on its losses. Another benefit is the switching loop being internal to the MMC cell, reducing the amount of electromagnetic interference (EMI) and the required shielding effort.

Finally, the MMC's cell structure guarantees a level of redundancy of the topology. Having additional cells in each converter branch allows for the reduction of the voltage stress on the cells' semiconductors, but additionally allows the bypassing of the cell in the event of a fault, with the remaining cells handling the full dc voltage. The failed cell can then be replaced during the following maintenance cycle [75]. In dc-dc conversion applications, the majority of existing work considers quasi-two-level operation of the topology [76]–[80], where an MFT is induced between an inverter and active rectifier stages generating quasi-square waveforms, therefore resulting in excitation similar to what is present in a DAB topology, as seen in Fig. 2.6. In its quasi-two-level dc-dc conversion arrangement, the MMC can be considered to be a bulk power transfer topology, as it employs a single MFT to achieve power transfer. Nevertheless it still has a highly modular structure, with many of the benefits and drawbacks of fractional power processing topologies.

First and foremost among these, is the topology's complexity, both in terms of hardware and control. In particular, control tasks are split between a central controller for the topology, and individual controllers for each cell, which must independently control each active power device to maintain the dc-link voltage of each cell within safe values. Additionally, the sinusoidal chopped current through each cell's dc-link capacitor is the converter's output current, which at low frequency imposes large capacitance values for each cell [81], [82]. Nevertheless, this is not an issued in the DCT application, as the medium frequency transformer operates at constant frequency, in principle allowing for downsizing of the MMC's cell capacitance. In conclusion, while the MMC is an established solution at the industrial level for HVdc transmission applications, it is not yet a common solution in MVdc contexts [83], [84].

The topology considered for the remaining work presented in this thesis is the SRC-LLC, as in

Fig. 2.6 Bidirectional quasi-two level MMC dc transformer.

reference [19] (except for the converter topology, which employs an NPC leg and split resonant capacitor). Thanks to its ability to operate without an externally provided setpoint, the SRC-LLC topology can provide a DCT which can truly perform a role which is equivalent to that of an ac transformer in an ac network.

### 2.4 MV Semiconductor Devices in DCT Applications

Having identified the SRC-LLC topology as the most beneficial based on the criteria put forward in the above section, the relative advantages and disadvantages of MV semiconductor devices are explored to justify another choice made in this thesis. Over time, many semiconductors have found application in the field of high-power MV conversion. These have included line-commutated silicon controller rectifiers (SCRs), gate turn-off thyristors (GTOs), and injection-enhanced gate transistors (IEGTs), but two most common devices today are the Si insulated-gate bipolar transistor (IGBT) and integrated gate-commutated thyristor (IGCT).

#### 2.4.1 IGBT

Of the two mentioned devices, the IGBT has been the object of a significantly larger volume of research in the past decades: the device has been considered by many authors [88]–[94], in both hard and soft-switched applications [88]–[90], [95], with voltage ratings of  $3.3 \,\mathrm{kV}$  [95] and  $6.5 \,\mathrm{kV}$ , and with varying levels of electron irradiation to control carrier lifetime in [88], [89], [94].  $6.5 \,\mathrm{kV}$  devices were also explored in soft-switched applications [90]–[92], with optimisation by means of anode engineering being presented in [93], and resulting in a reduction of switching losses, beneficial for fast-switching applications.

In contrast to BJTs and thyristors, IGBTs are voltage controlled semiconductors switches which can be turned ON and OFF by gate driver action, making them fully controllable devices.

Thanks to its ease of drive and good switching characteristics, the IGBT has progressively found its place among the most popular semiconductor devices nowadays. The device also has the additional benefit of allowing tuning of its switching performance through the alteration of the gate resistance,

**Fig. 2.7** a) IGBT dies [85] leave unused space reducing the total surface in contact with the press-packed device compared to the b) GCT wafer [86]; c) GCT integrated into the drive unit [87].

**Fig. 2.8** a) 6.5 kV rated module containing two IGBTs in common emitter configuration [96]; b) Ceramic press-pack IGBT with top surface being the emitter side of the device [97]

providing an additional degree of freedom in design and allowing for clampless operation in hard switching topologies. GDUs may have different values of gate resistors which can be selected and employed depending on the needed performance altering the duration of switching transition and enabling faster or lower switching, or limitation of short circuit current. In spite of these many advantages, the IGBT performs less favourably than thyristors or IGCTs in the same voltage class in terms of forward voltage in conduction.

In MV applications, the typical voltage classes are 4.5~kV and 6.5~kV, with current ratings of 900 A and 1200 A [98]. These devices allow junction operating temperature of up to of 125 °C and typically occur in module packaged IGBTs with plastic housings with insulation ratings of 7.2kV and 10kV for the respective voltage classes mentioned above.

The module's power terminals lead inside the housing and are at the potential of the emitter and collector of the chips located within the module's housing. Normally, IGBT chips are bonded to the metalized (Cu) ceramic substrate and soldered to an Aluminium Silicon Carbide (AlSiC) baseplate serving as the bottom metallic base of the modules [99]. Depending on requirements, packages can host one or more chips and can exist including or not including antiparallel diode chips.

The chips are supported by AlSiC plates which act both as a hard mechanical support and as a thermal interface between the module and heatsink, which can rely on air or water cooling for lower and higher power levels, respectively [100], [101].

The thermal interface between module and heatsink is always treated with thermal paste to provide improved and uniform heat extraction. The connection of chips to bus bars is achieved through wire bonds which are soldered or sintered to the chip on one side, and to the respective etched copper plating of the substrate on the other [102], [103]. The bus-bars connect to their part of the copper plate, realising a sturdy connection to the terminals. A silicon gel fills the inside of the module to improve electrical field distribution and limit the likelihood of flashovers. It is also possible to integrate other elements such as temperature sensors inside the module.

A relatively common issue in IGBT modules is the failure of wire bond connections related to thermal cycling [104], [105]. Different thermal expansion coefficients may lead to the wire bonds lifting and detaching, damaging connections to the power terminals. The introduction of the press-pack partially solves this problem, and was the package of choice for high power, high voltage thyristor switches and diodes before the introduction of the IGBT. The press-pack is designed for harsh environments like the ones found in smelting plants or mines, and as the application of the IGBT in these environments

became more common, so did IGBTs housed in this package.

The housing is made of insulating hard ceramic with the addition of pressure power contacts on both top and on the bottom. The thermal and electric contacts to the chips is achieved through copper discs in the role of contact plates, extending into the package [106], [107]. Thin Molybdenum (Mb) rectangular plates cover both sides of the chip and this plates come in direct contact with the emitter and collector carved Cu discs. This combination helps to greatly improve the thermal cycling capability of the IGBT chips within, the thermal expansion coefficients of Si and Mb being very similar. The majority of the compression and shear stress is transferred to the Mb. The interior of the package can be filled with inert gases such as  $SF_6$  to improve electrical field distribution.

In contrast to the module package having single-sided heat extraction, both sides of the chips present in press-packs are cooled. Press-pack IGBT are mounted between two heat sinks and the assembly is held together by the pressure provided by the external mechanical clamp. The most common mechanical implementation is in a stack of alternating heat sinks and IGBTs/diodes, at least in the case of a switching bridge or a phase leg of the converter. The pressure terminals help greatly in thermal energy extraction from the chip because of the massive and even contacts realized between Cu, Mb and Si.

Nevertheless, press-packs also have less advantageous features: firstly, compression forces applied on the housing must not exceed a specified range in both in cold or hot state of the switch, to avoid mechanical damage to the switch. Secondly, pressure on the package must be applied evenly from the centre to the sides to ensure adequate electrical and thermal contact and guarantee that no individual die undergoes excessive stress during thermal cycling. For this reason, extreme care must be taken in the manufacturing of the contact surfaces of the press-pack, specifically the flatness of the finish, which results in increased manufacturing costs. Similarly, this must be achieved also for the heatsink with which the package is interfaces, which are also required to be exactly parallel to each other.

The pressure distribution problem can be tackled by using spring contacts inside the package, which can even out external pressure variations over the surface of the contact. The drawback of this solution is that the thermal interface to the one side of the package is broken, increasing the thermal resistance between the IGBT dies and the heat sink. Due to the prevalence of this package in high power applications, in the vast majority of cases water cooling is employed, with air cooled solutions constituting a small minority of use cases.

Voltage classes higher than 4.5 kV, are not frequent due to the easy series connection achieved through the stacking of devices. Current ratings go up to 3 kA for most IGBT packages, but with relatively low switching frequencies of up to 1 kHz which are typical in high power applications.

ISOP connection of modules resulting in modular topologies are quite common, leveraging the use of relatively affordable LV devices for MV applications. Similarly, the series connection of the IGBTs is also common in order to reach the required voltage ratings, but at the price of reduction efficiency due to snubber circuits. Concerning resonant operation, the IGBT is characterised by increased turn-off energy loss compared to equivalent hard-switching operation. Due to the different profiles of the pre-flooding current of the IGBT, more carriers are generated during the resonant cycle, having to be extracted, as discussed in [93].

Another device leveraging the benefits of the press-pack and with conduction losses comparable to those of the high power thyristor, the IGCT is another device seriously competing with the IGBT in

**Fig. 2.9** a) In asymmetric IGCTs, IGCT fingers cover the full surface of the wafer; b) in reverse conducting IGCTs, the central portion of the wafer is allocated to the device's antiparallel diode [111].

high power MV applications.

#### 2.4.2 IGCT

In comparison to the IGBT, the IGCT exhibits specific advantages over the more popular device in certain applications: its thyristor structure guarantees best-in-class conduction losses among fully controllable devices, and with relatively similar turn-off energies compared to the IGBT.

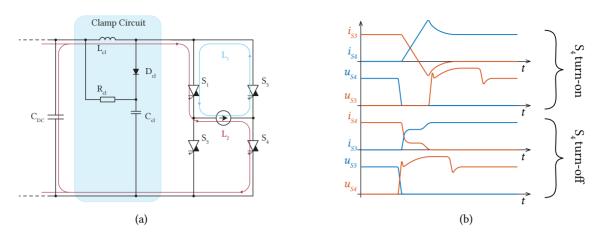

In conventional hard-switched applications, where the IGCT has traditionally found application, turn-on losses are normally neglected due to the use of a clamp circuit that protects the devices' antiparallel diode at the time of commutation, as seen in Fig. 2.10. This shifts the switching loss from the devices themselves to the clamp circuit. In a similar application, the turn-on of the IGBT can be better controlled through gate driver action and therefore a clamp circuit is not needed, therefore with the corresponding energy being dissipated in the device. For this reason the comparison between the devices is not straightforward, even though [108] has not found significant difference in overall system losses by using IGBTs with a clamp circuit.

In terms of rating, traditional uses of the IGCT have leveraged its high surge current capabilities and achieved switching frequencies usually at or below 1 kHz. Reference [109] uses 4.5 kV, 2.1 kA IGCTs, to achieve a rating of 1.5MVA using just two devices in a half-bridge configuration. In more recent years, advances in the technology have focused on increasing the power density by reduction of losses, increase of the maximum operating temperature, and maximisation of the device's peak turn-off current. Additionally blocking voltages of up to 10 kV have been achieved, though not yet in commercially available devices [110].

The first commercial application of the IGCT was a  $100\,\mathrm{MVA}$  back-to-back rail intertie in operation in Germany since  $1996\,[112]$ . The device has subsequently found use in a number of high power medium voltage installations and today exists in three distinct types, all of which, due to their high power ratings, are only available in the press-pack form: asymmetric, reverse conducting, and reverse blocking. Typical voltage ratings for all of these devices are of  $4.5\,\mathrm{kV}$ ,  $5.5\,\mathrm{kV}$  and  $6.5\,\mathrm{kV}$ .

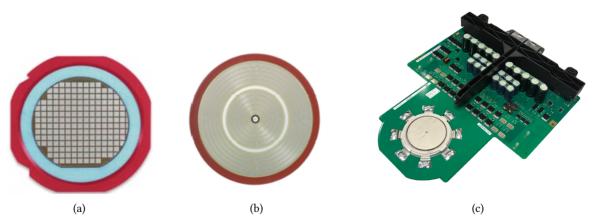

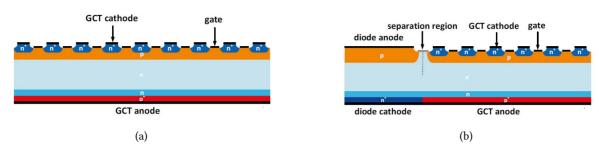

As described in Fig. 2.9, asymmetric IGCTs are capable of blocking forward voltage, but have very low reverse blocking capability (only around  $-20 \, \text{V}$ ). This kind of device is intended for use in combination with an external discrete antiparallel diode. Asymmetric IGCTs achieve the highest available current rating: devices up to 6 kA are commercially available.

Reverse conducting IGCTs integrate the anti-parallel diode on the same Si wafer as the IGCT and it is therefore not necessary to employ external discrete diodes, This reduces overall component count,

**Fig. 2.10** a) In most hard-switched applications both a clamp circuit and snubber resistor are required, but can be omitted in b) a soft-switched SRC-LLC topology.

but since part of the Si wafer area is occupied by the integrated diode, the overall surface available for GCT fingers is reduced when compared to an asymmetric IGCT of the same diameter. As a result, reverse conducting IGCT generally have comparatively lower turn-off current ratings of up to 2 kA. The devices employed in the rest of this thesis are all reverse conducting IGCTs.

Finally, symmetrical IGCT are capable of blocking both forward and reverse voltages, but at the price of decreased current ratings due to the increased wafer thickness needed for this capability resulting in increased conduction losses and more restrictive thermal limitations. The main application of symmetrical IGCTs are current source converters. GCTs are composed of multiple fingers arranged circularly in ring structures over the surface of the wafer. The central ring in the Fig. 2.8(b) is the gate terminal of the switch, while cathode and anode are on the top and bottom, respectively.

The high current rating of the device is in part achieved thanks to the GCT fingers being able to cover the entire surface of the wafer, therefore aiding thermal conduction to the top and bottom Cu package covers, especially compared to the press-pack IGBT. This results in IGCTs generally exhibiting lower

**Fig. 2.11** a) IGCT clamp circuit with highlighted current paths and b) waveforms at turn-on and turn-off of  $S_4$  [19].

junction-to-case thermal resistance for the same package size. This allows relaxed cooling constraints or increased the thermal excursion margin of the junction. Cooling is achieved on the both sides of the package through anode and cathode contacts.

An IGCT is a current driven device, owing it to the thyristor structure of the semiconductor. One of the benefits of current drive is an increased resilience to EMI, but at the cost of increased gate driver power consumption. At turn-off, the entire anode current is commutated from the collector to the gate driver. Therefore, increased turn-off current capability corresponds to an increased number of gate driver capacitors, which can be seen in Fig. 2.7(c) in black. These capacitors provide a stable voltage source during turn-off necessary for the commutation of the current. Due to the high current levels involved, it is also necessary that the inductance between the gate driver unit and the GCT is minimised, which can be achieved through wide parallel multilayer traces of the terminals, leading to the integration of the GDU with the GCT. Hence, the name of *Integrated Gate Commutated Thyristor*.

Unlike the IGBT, IGCTs generally cannot turn-off short circuit currents. Nevertheless, IGCTs are characterised by higher short circuit withstand capability and higher limiting load integral. The high thermal tolerance of the device allows relatively slow, external breakers or fuses to be employed for protection in case of short circuit.

Another difference compared to the IGBT is the inability of the rate of change of current in the IGCT to be controlled by the gate driver. For this reason, an external clamp circuit must be present to protect the anti-parallel diodes from damage due to excessive di/dt. Typical clamp circuits are visible in Fig. 2.10(a).

The typical switching process in presence of a clamp circuit is visualised in Fig. 2.11. At the beginning of the process and before the turn-on of  $S_4$ , the flow of load current is though the loop  $L_1$  in Fig. 2.11(a).  $S_1$  is on,  $S_3$ 's antiparallel diode is conducting the load current. The voltage on the load is of 0 V. For the load to be supplied with positive voltage,  $S_4$  is turned on. The voltage on the terminals of the device decreases to 0 V and the clamp inductor current rises with starting value equal to 0 A. The rate of change of the current in the clamp inductor is limited to  $U_{C_{dc}}/L_{cl}$ , and  $L_{cl}$  is designed based on the di/dt capabilities of the antiparallel diodes.

The current in  $i_{S_3}$  starts to fall gradually as the current in  $L_{cl}$  progressively rises with the safe and

limited di/dt; this can be seen in the top graph of Fig. 2.11(b). The reverse recovery process of the antiparallel diode of  $S_3$  starts after the current in  $S_3$  crosses 0 A. The voltage across  $S_3$  starts to build-up as the junction of the diode is free of charge carriers and the depletion region progressively forms, which is shown in the second graph of Fig. 2.11(b). The effect of the reverse recovery can also be observed in the form of a current overshoot in  $S_4$ .

Up until the time when the current  $i_{S_4}$  reaches its maximum, currents  $i_{S_4}$  and  $i_{L_{cl}}$  are equal. After  $i_{S_4}$  reaches its maximum,  $i_{L_{cl}}$  is greater than the load current and the excess starts flowing into the clamp capacitor  $C_{cl}$  through the diode  $D_{cl}$  until the  $i_{L_{cl}}$  becomes equal to the load current. Observing  $u_{S_3}$ , one can see the overvoltage resulting the voltage of  $C_{cl}$  exceeding the dc-link voltage during the equalisation of the currents.  $C_{cl}$  is later discharged through  $R_{cl}$  until the voltage at its terminals reaches the voltage of the dc-link, which is blocked by  $S_3$ .

The turn-off of  $S_4$  can be seen in the bottom two graphs of Fig. 2.11(b). Initially, the current decreases, and after it is extinguished the load current is commutated to the antiparallel diode of  $S_3$ . Upon  $S_3$  starting to block, the current  $i_{L_{cl}}$  is commutated into  $C_{cl}$  which stores the magnetic energy initially contained in  $L_{cl}$  and returns it to the dc-link. During this process,  $S_3$  experiences an over-voltage up until when the voltage of  $C_{cl}$  has returned to the dc-link voltage value.

A significant benefit of the clamping circuit is negligible turn-on energy loss of the IGCT. The overall conversion efficiency benefits greatly from this virtually lossless turn-on process.

Compared to the IGBT, the IGCT has lower voltage drop during conduction due to its thyristor nature, resulting in lower conduction losses. Concerning switching, turn-off energy for the two devices is comparable. The reduction in cooling effort related to the IGCT's reduces conduction losses leads to lower cooling requirements for the final converter in terms of space and cost.

The application of the IGCT in resonant applications has been mostly overlooked, with the work reported in [113], [114] being somewhat unique. Nevertheless the benefits from the use of the device in resonant applications are significant, as discussed in [19]. In particular, in the SRC-LLC discussed in this thesis the IGCT would operate in unique conditions beneficial for the device: the reduction of both turn-on (ZVS) and turn-off (low-current) losses achieved through the soft-switched topology increase the benefit of the device's low conduction loss. Additionally, clampless operation becomes possible thanks to the absence of terminal voltage on the device at the time of turn-on, and finally becasue of the low turn-off current a significant reduction of gate drive effort has been shown to be possible in [115], which sidesteps the high level of energy dissipation in the gate drive circuit that has traditionally been one of the most frequently identified drawbacks of the IGCT.

Therefore, while the IGCT is a less commonly used technology and there is little precedent for its use in MVdc DCT applications, there is relevant research interest in exploring whether the expected benefits of the device can be exploited in such an application. For this reason, the device is selected to be used in the application discussed in the thesis over the IGBT.

# 2.5 Series Connected Operation of IGCTs

While no standard voltage levels are currently defined, MVdc networks are expected to exist with voltage ratings of up to  $50 \, \text{kV}$  in monopolar networks, and  $\pm 50 \, \text{kV}$  in bipolar networks. Ratings of commercial IGCTs today do not exceed  $6.5 \, \text{kV}$ , and therefore series connection of the device is

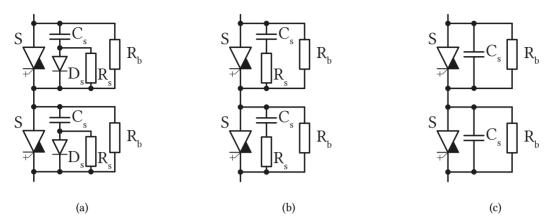

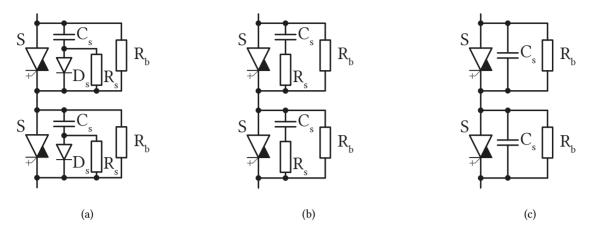

**Fig. 2.12** Series connected RC-IGCTs with a) RCD; b) RC; c) C parallel connected snubber for dynamic voltage balancing. Resistor  $R_h$  provides static voltage balancing.

required for use in bulk power transfer MV applications.

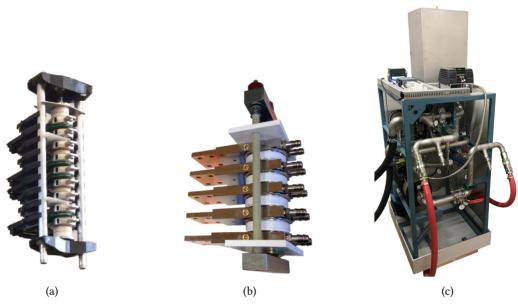

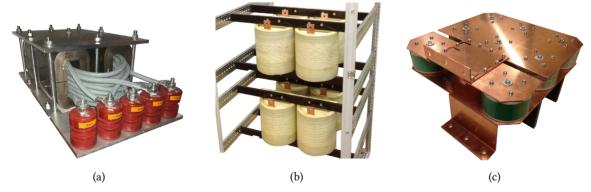

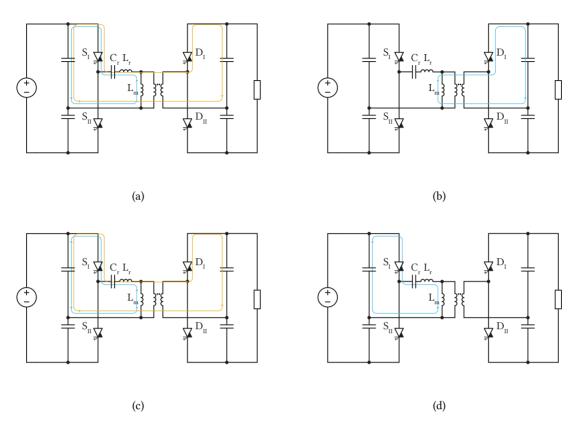

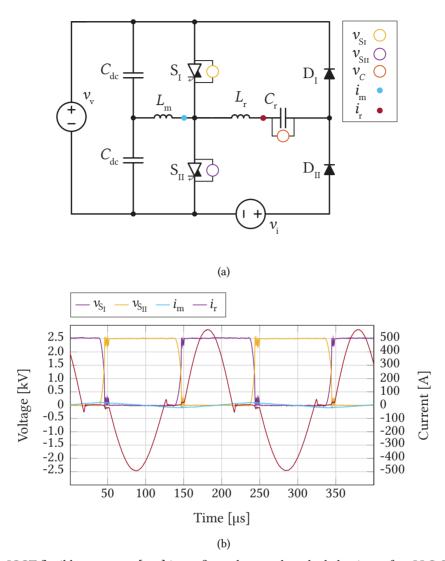

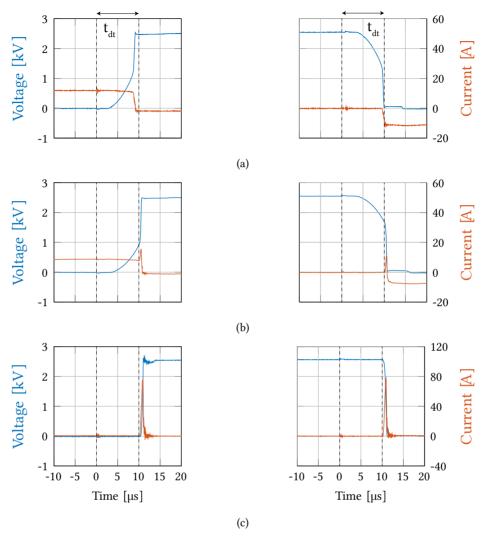

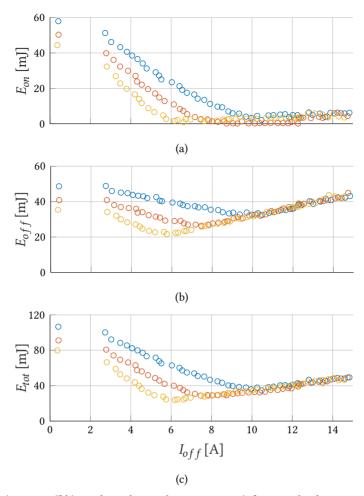

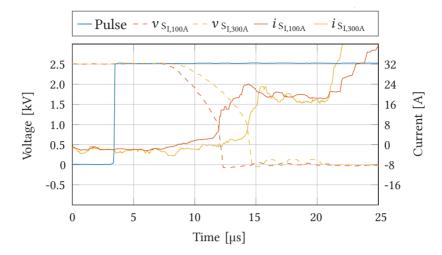

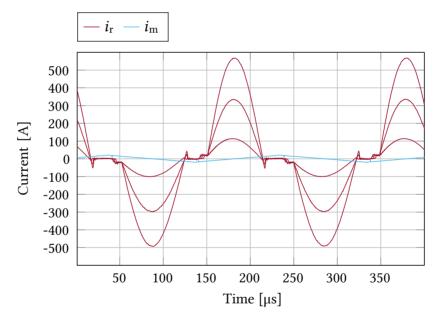

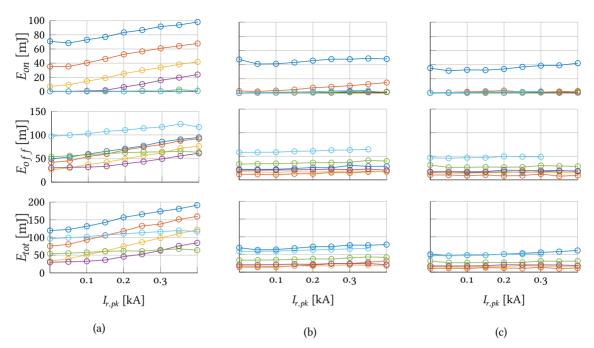

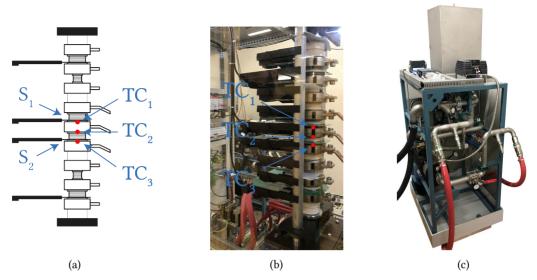

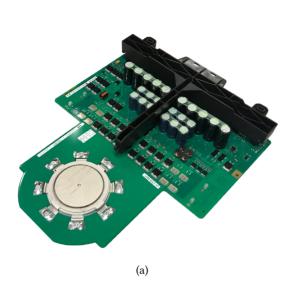

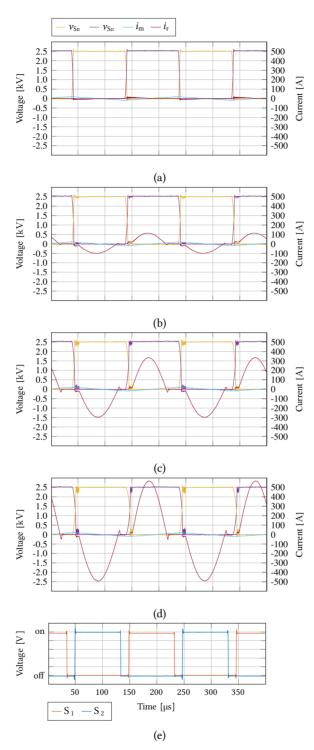

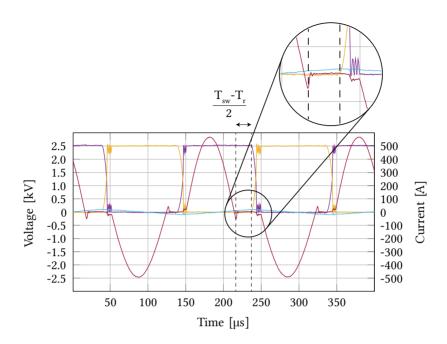

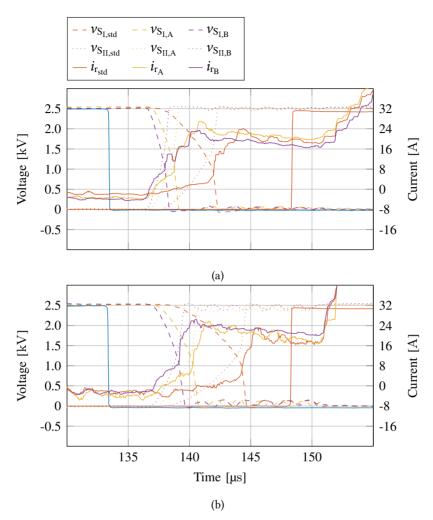

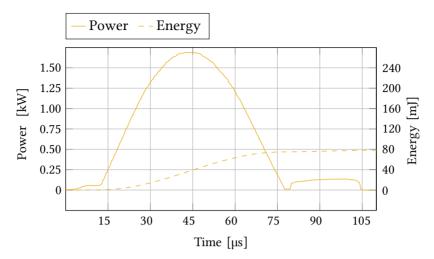

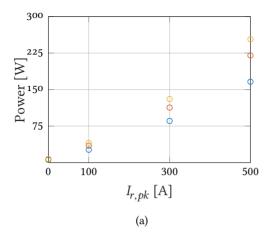

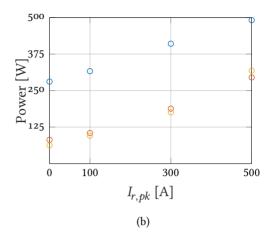

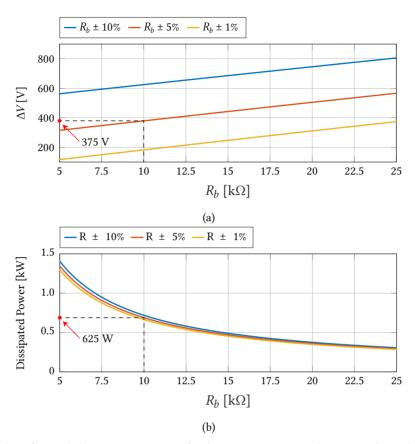

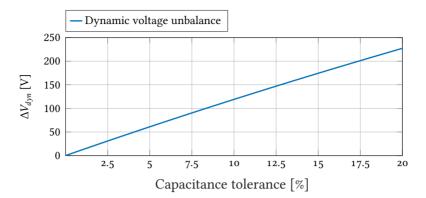

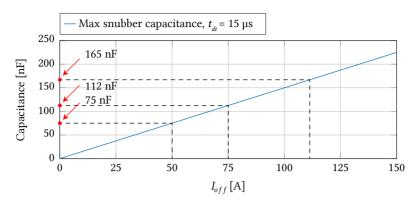

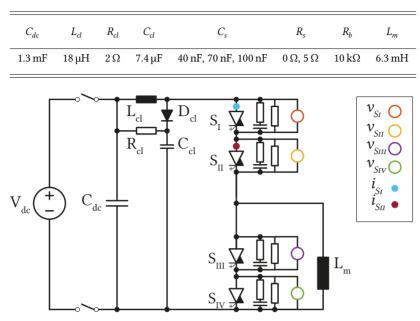

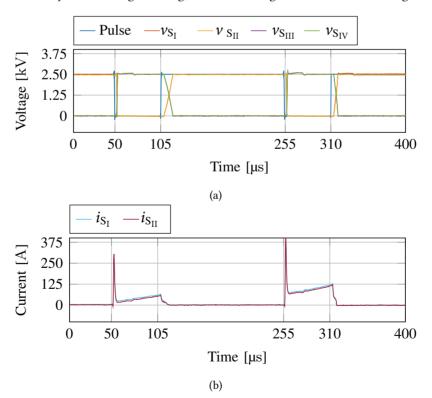

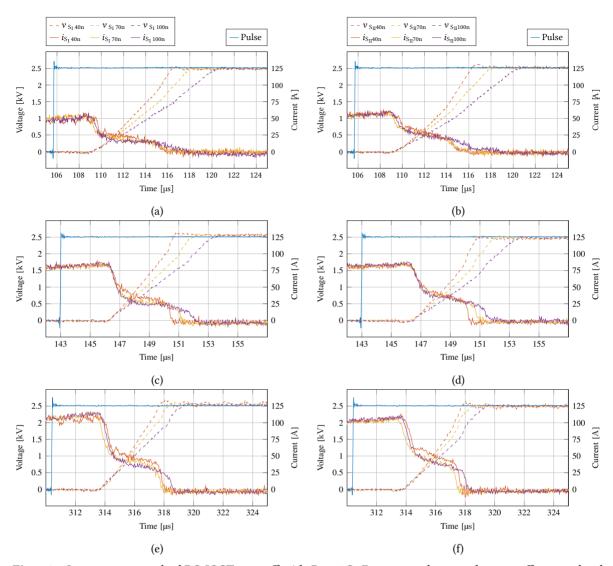

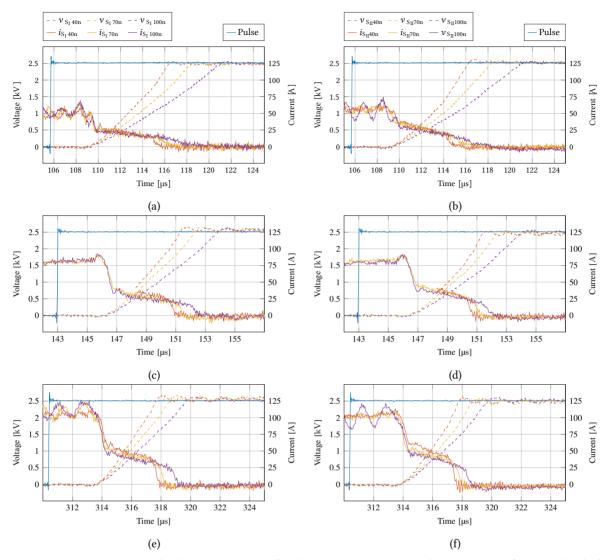

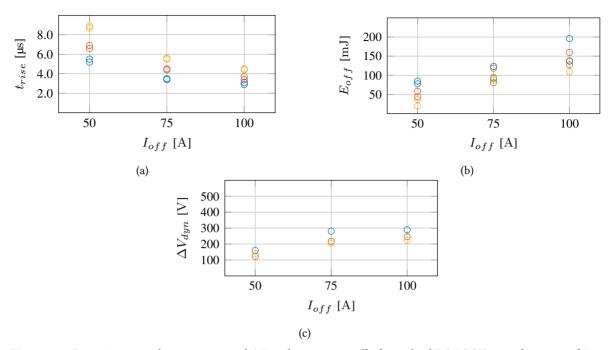

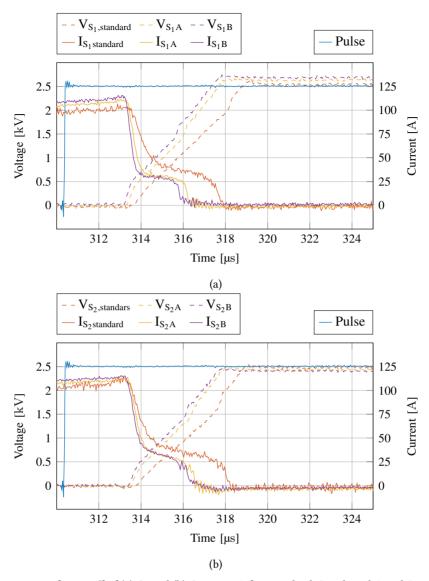

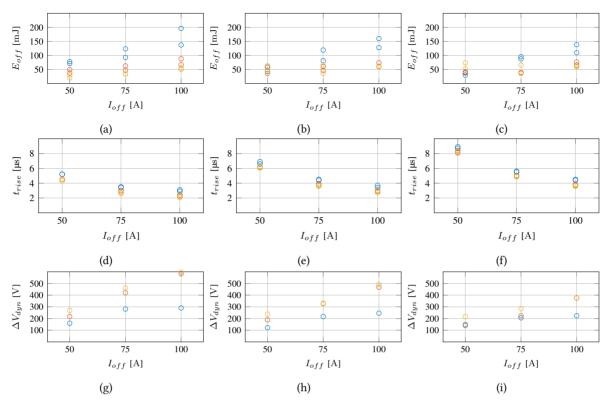

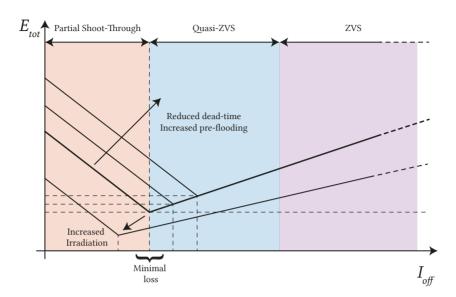

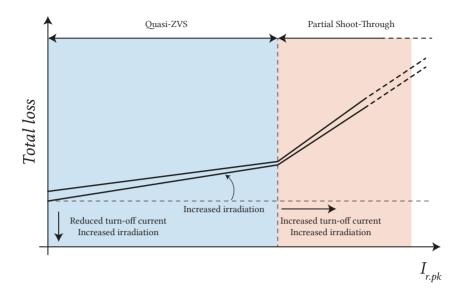

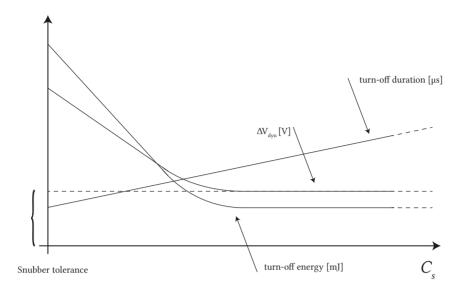

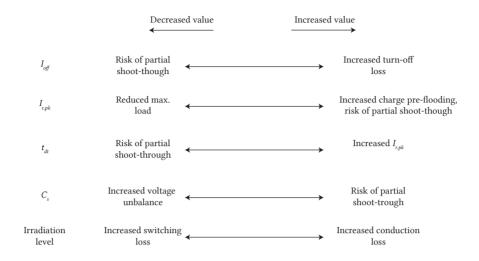

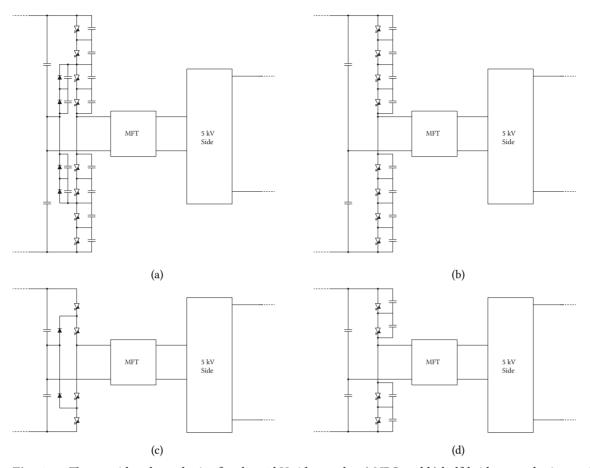

Indeed, series connection of IGCTs has been of interest almost since the device was first made available, allowing the increase of installed power ratings by a factor similar to that of the number of series connected devices [116]–[118]. In series connection, the most critical part of the period is that of device turn-off, when the dc voltage needs to build up at the terminals of the device and be correctly shared with the other devices connected in series. This is to happen in the limited duration of the dead time.