# Hardware and Software Support for RPC-Centric Server Architecture

Présentée le 5 septembre 2022

Faculté informatique et communications Laboratoire d'architecture de systèmes parallèles Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Mark Johnathon SUTHERLAND

Acceptée sur proposition du jury

Prof. M. Jaggi, président du jury

Prof. B. Falsafi, Prof. A. Daglis, directeurs de thèse

Prof. M. Silberstein, rapporteur

Dr S. Reinhardt, rapporteur

Prof. E. Bugnion, rapporteur

## Acknowledgements

Completing a PhD has unequivocally been the most challenging thing I have ever done, and moreover the journey was a task for which I was undoubtedly not mentally prepared to undertake. Entering the program, I naïvely expected only academic and intellectual growth. Upon leaving, I now realize that the personal growth required to complete the journey has reached almost every area of my character. It was only possible for me to finish this work with the support of my advisors, and a great many friends, family members, and colleagues, whom all are owed an extreme debt of gratitude and I will thank by name throughout this section. However, I wish to begin this section by mentioning the most important lesson I learned in the past six years, from the most influential person in my life.

If anyone would be first,

let him be last of all,

and servant of all.

— Jesus of Nazareth

It is only now, on the far side of the PhD journey, that I realize the depth and practical implications of Jesus' teaching in that statement. Although the value of this was difficult to see at first, and attempting to embody it was even more difficult, I look forward to attempting to live and work with as much of an "others-focused" mindset as I can possibly muster. To those readers who know me, and have tolerated my many lapses towards a selfish attitude, I want to thank you for your patience and forgiveness! To those who do not, I can only say that I have benefitted from many people who have sought my good over or beside their own, and those experiences are the ones I am most thankful for and wish to create for others.

At this point, I wish to thank my two advisors, Babak and Alex, for all of their effort, collaboration, and perseverance in working with me and helping me grow as a professional and researcher. Babak and I share the trait of perfectionism, and his method of doing research results in some of the most consistently high-quality output that I know of. From him, I learned how to communicate ideas much more clearly, focus only on the important questions, and prioritize all the various interests and possibilities bouncing around in my brain. Although these lessons were undoubtedly important for me, I am the most thankful for two specific moments where he encouraged me to keep pushing, despite my lack of belief that I could reach the finish line. I am also grateful for the fact that Babak plays as hard as he works. All of his students get to enjoy arguably the best coffee at EPFL (and maybe even beyond), lab dinners, ski trips, and movie nights, all of which objectively made my PhD experience more enjoyable. He also made sure that we absolutely never needed to worry about funding our research, freeing us up to work in any direction for which we can make a strong case.

Alex is one of the most knowledgeable and well-rounded people I have ever met, and I am very thankful that he joined my PhD journey as an official co-advisor in my fourth year. He was kind enough to invest a major amount of his time into working with me and improving my research, all in addition to his own students at Georgia Tech. Additionally, being my immediate predecessor in the lab working on the systems and networking research angle, I benefitted significantly from his insights in both of those areas. In particular, Alex had a knack for asking questions about my ideas or results that revealed shortcomings in the work, with a remarkable degree of prescience. We also were extremely productive in working together, and found that our writing styles meshed extremely well. Alex is also the closest person I know to attaining five nines of availability – there were many times I wrote to him at five in the morning on a Sunday, not expecting a response for days, and I heard back within hours. I have no idea how he keeps going, but I know that I am thankful for all those responses. His students are very blessed to have an advisor like Alex.

The next two people I wish to thank were my first contacts in the world of computer architecture: Natalie Enright Jerger and Andreas Moshovos, at the University of Toronto. Natalie was kind enough to extend an offer to me to supervise my Master's thesis, and consistently exceeded my expectations in treating me like a colleague and a fellow researcher even though

I was not a PhD student. Natalie's expertise, demeanour, and infectiously positive attitude made my first research experience outstanding. Without the phenomenal experience I had in her group, I might not have continued on in the research world. She also continues to stay in touch even long after I left her group in Toronto. Andreas taught me to love the intimate details of out-of-order processor microarchitecture (and everything related to speculation!), and even gave me the opportunity to help teach it by assisting his class. His recommendation to choose EPFL over other offers helped me become the person I am today.

As one can see, I have been blessed with a great number of outstanding instructors, from Toronto to EPFL. At EPFL, I wish to thank Ed Bugnion, George Candea, and Katerina Argyraki for teaching me about computer systems, and broadening my horizons beyond traditional computer architecture. From the first few days of their course called "Principles of Computer Systems" (POCS), I knew that I wanted to work on systems for the long term. During my PhD, I had the opportunity to be part of POCS three times – once as a student and twice as a teaching assistant – and I learned a huge amount each time. I cannot say enough about how rich my POCS experience was; it was without a doubt the best course I have ever taken.

I would also like to thank the many collaborators I had who reside a bit further abroad than my immediate EPFL orbit. Specifically, I would like to thank Dionisios Pnevmatikatos at NTUA, and Virendra Marathe at Oracle Labs. Both of them graciously gave their time to help me during my first publication, Dionisios from a network perspective and Virendra from a distributed memory one. Additionally, I thank my thesis committee members Ed Bugnion, Mark Silberstein, and Steve Reinhardt for graciously investing their time in reviewing my thesis proposal, giving me feedback, and helping guide my final two years towards a more productive conclusion. Thank you also to Martin Jaggi for agreeing to serve as my thesis jury president on such short notice.

Next, I have to thank the people in two labs at EPFL, beginning with all of my fellow PARSA students. We are all walking the same journey, and although I was slightly less connected to the lab's social life than others were, I greatly appreciated the moments where we were able to share in the positives and negatives of the PhD life together. In particular, I want to thank Arash Pourhabibi and Dmitrii Ustiugov, who were my two most frequent collaborators

other than my advisors. As a completely green first-year student, I will never forget my first experience of trying to do high-impact research work with Dmitrii. Dmitrii is probably the only person with whom I can technically argue at levels of intensity that would usually be considered far too high-volume for an office environment, and still have both of us come out smiling and believing we had a productive meeting. He is also one of the most persistent people I have ever met – he will never, ever give up. I am so proud of his many career successes, and I look forward to continuing to try to convince him of the concept of objective morality in our lunch meetings to come!

Arash and I worked together daily for two of the last three years of my PhD, and shared two publications. He is the exact opposite of Dmitrii in his level of personal intensity, but no less in his level of technical proficiency and persistence. I will always remember how the two of us worked in completely opposite time zones, both in the dark – me before the sunrise, and him after the sunset. During our years of working together, I learned a lot about software development that I would have not encountered otherwise – in particular, I have tried to take onboard his love for testing and good development practices even when it is inconvenient. Finally, Arash knows about good food, where to find it, and how to make legitimately good dishes, which I have been lucky enough to share many times. I am thankful for the time we spent working together and look forward to more in the future.

Next, I want to thank the rest of the students that were co-running threads during my time in PARSA: Javier, Mario, Hussein, Sid, Ognjen, Simla, Nooshin, Ali, Shanqing, Yuanlong, Rafael, Zilu, Dina, Canberk, and Fatih. Javier was the only other student as obsessed with out-of-order microarchitecture as me, until Ali came along... Javier, *put that coffee down!* Mario was our lab's resident programming languages expert and the only other person in the lab who followed the NHL. I still can't understand half the languages he knows, or how he knows more about hockey than Canadians. Sid is the master of getting from A to B, no matter the cost. If something must be done, and he is convinced of the need, he will give you a positive result on time. If I had to choose one person to get something done under a deadline with major consequences for failure, I am picking him with no hesitation.

Hussein and Ognjen were two students I shared many discussions about FPGAs with – Hussein

because of his love for them, and Ognjen because of his frustration. Although Hussein moved on to the enterprise world early, we shared a good year with our desks in the lab lounge – I will never forget being hit on the head many times with a rubber ball in the middle of work, because he decided to throw it at me from across the room without calling out. Ognjen might be the only person I know who worries about everything as much as me, and I am really thankful for the long discussions we had in an attempt to stop overthinking many issues. I really enjoyed all my lunch discussions with Rafael about finance and geopolitics, and arguing about subjects on which we both were objectively uneducated. Although I did not have as many interactions with Nooshin, Simla, Shanqing, Yuanlong, Zilu, Canberk, Dina, and Fatih as I would have liked, I enjoyed the few good times we had, such as at lab dinners.

I also thank the administrative and technical staff that keep PARSA running on a day-to-day basis. In particular, I want to acknowledge Stéphanie and Valérie for handling scheduling, travel, administration, and even sometimes translation. Both of them are not only helpful, but they do their jobs with a smile, which was more appreciated than they perhaps know. For the short time we were in PARSA together, I saw the wizardry of Rodolphe as a sysadmin. Then, when he moved on to new opportunities and left me the task of maintaining the infrastructure, I saw his wizardry even more clearly...

I want to also thank the students in the other labs that I was close to: Marios, Adrien, Rishabh, and Georg. Marios was sometimes like a third advisor to me, who was interested in incredibly similar problems and technical ideas. Like clockwork, I would think of a system connection to one of my ideas, and he had either considered the exact same and rejected it for solid reasons, or could give me helpful advice on the spot. Thank you Marios for all the time you spent answering my questions and early stage ideas. Adrien was one of the most open people I have ever met, almost brutally honest about himself and others. I think he is the only other EPFL student I know who is as emotional as me, something that I greatly appreciated. Rishabh has always impressed me with his ability to dive into a completely different research field than he originally intended to study, and still publish top-tier papers. Although I didn't get the chance to work with either of them much, I am looking forward to staying in touch in the future, and I am extremely grateful for the time they spent with me when I was completing the last few chapters of this thesis. Their feedback made the work objectively better. Georg, I appreciated

our connection in my first year very much, particularly your spontaneous invitations – this made me feel very welcome as a North American new to Europe.

I am also incredibly indebted to the wonderful people I met through Westlake Church Lausanne. When I first arrived in Lausanne on a Saturday, I searched on Google for "english speaking church Lausanne", showed up the next day, and have hardly missed a Sunday morning since then. It is not an exaggeration to say that without the many connections I made through Westlake, I would not have reached the end of my PhD, or have the life I have today. If I tried to list every person who encouraged me, or every conversation I enjoyed, I would go on for twenty pages. Let me just say that I love all of you, our church community, and hope that I can continue to be an encouragement to all of you for the long run. Among the many people I have come to know at Westlake, I have to specifically thank my closest friends for standing with me through every circumstance, friends that are so close I think of them like family: Ruan, Iddo, Anne-Lize, Clara, Noel, and the Rizzos.

During the past six years, Ruan and Iddo have been like the brothers I never had in my family, with whom I could share my competitive nature and intensity, but also my soft side. I have always been able to count on Ruan to be a calming influence, for relentless support, for our shared obsession with cycling and riding up mountains, and our many times of prayer at all hours of the day. I am deeply honoured that he stood with me as the best man at my wedding. Iddo's thoughtfulness and skill in active listening has always impressed me, in addition to his honesty in sharing the lessons which he learned from his father with all of us. Also, I could always count on Iddo to appreciate a nice bottle of red wine together. I will always treasure our conversations during the multiple times you came to visit, as well as on our shared holidays. Thank you both for all your support, and I very much look forward to the future of our friendship.

Anne-Lize, Noel, and Clara have become big and little sisters to me, who were there for me during many occasions. All three of them have always been a major encouragement to me in their attitude, faith, and kindness. In particular, I want to acknowledge Anne-Lize and her family, who probably prayed more for me than I did myself. Also, the shared obsession Noel and I have for Bible Project podcasts and videos led to many diversions from this thesis work

that refreshed my concentration and motivation. I have the privilege of being one of Tom and Karen Rizzo's many pseudo-adopted children, and I want to thank them as well as their daughter Fiona, and son-in-law Adrian for being there for me when recovering from a sudden hospitalization (twice). I will never forget the support and care I felt from all of them.

Next, I want to thank my parents, Gord and Kathy, as well as my sister Sam, for all of their support and patience while I was on my PhD journey, especially because I moved so far away from small-town Alberta to do it. My parents taught me almost everything foundational that helped me grow into the person that I am. Additionally, I am fortunate enough to not just have them as parents, but also now more so as friends. My dad was one of the earliest sources of my involvement with computers, and probably he did not ever imagine that I would one day be receiving a PhD in computer science because of our home PC on which I played Minesweeper, Rogue, and Clusterball. He taught me the importance and dignity of hard work, the value of showing up and being there for others, and was there countless times as support when I moved away from home to study, and then even further away to do a PhD. I imagine my mom did not much appreciate my spending time inside staring at a screen, but her patience with that part of my young life definitely was a foundation in me choosing computers as a career. Also, I am grateful that my mom and I share an interest in exercise physiology and sports science, which we often have long text conversations about. Sam has been a constant source of humility to me, and although that may seem to be a cliché, I actually deeply appreciate it. Without her, I might have still believed that I could be an athlete. Despite carrying some disadvantages from our family's unfortunate lack of height, her work ethic almost got her to the Canadian national women's hockey team, and I am so proud of her.

Last, and certainly not least, I want to say thank you to my wife Laurianne and everyone in the Imhof, Eberli, and Geiser families. I was probably not the one they were expecting for Laurianne, but they welcomed me with an extreme amount of kindness and patience, particularly in view of all the struggles I have with expressing myself in French. However, they made me feel welcome, accepted, and like a member of their family even before Laurianne and I made the membership official. Laurianne joined my PhD journey in my third year, and stuck with me through all my self-doubt and difficulty, even though it was initially incredibly confusing for her to understand the many demands of completing a PhD. I could not have

#### Acknowledgements

imagined having a more caring girlfriend, fiancé, and now wife, and for that I am eternally grateful. Her consistent support through 5:30AM phone calls for prayer, and her presence with me through many late nights helped me more than she will ever comprehend. Nothing can make me more joyful than thinking about spending the rest of our lives together, and about how I can make her the happiest person in the world.

Finally, I would also like to thank the many individuals and organizations that financially supported my PhD journey through funding arrangements. I would like to acknowledge the EPFL, the Swiss National Science Foundation (SNSF), and the Swiss citizens in general whose taxes supported my work. This thesis was funded by the following grants, projects, and awards: EPFL graduate student funding from the Computer Science department, the SNSF's "Memory-Centric Server Architecture for Datacenters" and "Hardware/Software Co-Design for In-Memory Services" projects, Facebook's "Full-System Accelerated & Secure ML Collaborative Research" program, a Google Faculty Research Award, and Oracle Labs' Accelerating Distributed Systems grant.

Lausanne, August 17, 2022

- MJS.

### **Abstract**

Online services have become ubiquitous in technological society, the global demand for which has driven enterprises to construct gigantic datacenters that run their software. Such facilities have also recently become a substrate for third-party organizations due to the advantages of moving infrastructure to the cloud. The task of developing, releasing, and maintaining software at datacenter scale has given rise to a software architecture employing many independent *microservices*, each accomplishing a single role and communicating using an enforced API, the most common of which is Remote Procedure Calls (RPCs). As microservices have become standard practice for datacenter-scale software, the datacenter's underlying components must support them efficiently.

The increasing adoption of microservice architectures implies a drastic growth in network communication, because each microservice receives and creates many RPCs that often execute for only a few microseconds ( $\mu$ s). Therefore, delivering users an interactive, low latency service becomes more challenging, because each request involves more interactions with the components implementing the communication stack. It is particularly difficult to ensure the latency of the slowest responses, called the "tail latency", is acceptable to the service's users. Datacenter system design is therefore undergoing a rapid shift to enable programmers to reap the benefits of microservices without their performance quandaries.

Handling RPCs from  $\mu$ s-scale software at the line rates of today's NICs – delivering up to 400Gbps – is an open challenge, which will require designing all layers of the communication stack to natively offer support for RPC semantics. Although the performance of the network and protocol layers has drastically improved by prioritizing RPCs as a primary design objective, server hardware has not yet done so. Therefore, we posit that now is the time for an RPC-centric server architecture to emerge to allow server endpoints to match the performance of their surrounding system components.

To that end, this thesis introduces hardware and software support for RPC-centric server architecture. We first make the case that today's hardware-terminated network transport protocols grossly over-provision buffering because they are agnostic to the latency constraints inherent in each RPC – simply exposing such RPC-level information to hardware allows  $1.25-2.2\times$  better performance. Motivated by prior work demonstrating the RPC stack's burdensome cost, we then show how a previously proposed RPC stack accelerator can be integrated with the implementation of our aforementioned NIC protocol. Finally, we propose new NIC-driven load balancing policies that boost microservice throughput via improved locality, while simultaneously maintaining tail latency guarantees. Our proposals improve 99th% tail latency in data stores by  $2-5.5\times$ , and reduce instruction cache misses in stateless microservices by  $1.1-1.8\times$ . In summary, we present evidence that designing and implementing a server's NIC hardware to natively support RPC semantics removes protocol scalability bottlenecks *and* enables microservices to enjoy further performance benefits.

Keywords: datacenters, servers, microservices, remote procedure calls, hardware, load balancing, tail latency, network protocols, queueing theory, co-design

### Résumé

Les services en ligne sont devenus omniprésents dans la société technologique forçant ainsi les grandes entreprises à construire des centres de données dédiés à ces services. Les tâches de développement, publication et gestion de logiciels à l'échelle d'un centre de données ont conduit à un paradigme divisant les services en plusieurs « microservices », chacun étant responsable d'un seul rôle et communiquant au moyen d'une interface applicative, la plus répandue prenant la forme d'appels de procédures à distance (RPC). Les microservices s'imposant aujourd'hui comme la norme pour le développement de logiciels à l'échelle d'un centre de données, les infrastructures doivent évoluer afin d'en favoriser l'exécution.

L'utilisation croissante de microservices augmente considérablement le trafic interne au centre de données. Chaque microservice reçoit et envoie plusieurs RPCs qui, pour la plupart, ne prennent que quelques microsecondes à s'exécuter. Par conséquent, il devient de plus en plus difficile de fournir aux utilisateurs un service en ligne interactif et rapide : chaque requête, aussi simple soit-elle, nécessite de nombreuses interactions sur le réseau. Il devient alors particulièrement difficile de garantir la latence des requêtes les plus lentes, aussi appelée « latence de queue ». La conception de systèmes pour les centres de données fait par conséquent l'objet d'une transformation visant à permettre le développement de microservices avec de bonnes performances et garanties de latence.

La gestion de RPCs à l'échelle des microsecondes sur des cartes réseau modernes - avec des débits allant jusqu'à 400 Go/s – est un véritable défi, qui ne peut être adressé qu'en exposant un support pour les RPCs à chaque couche de la pile de communication réseau. La mise en place de système de priorités associés aux RPCs permet déjà de meilleures performances. Cependant, le manque de support pour de tels mécanismes dans d'autres composants du centre de données empêche des gains encore plus grands. Nous suggérons qu'il est temps, pour l'architecture des serveurs, de s'adapter aux microservices et de libérer le plein potentiel

de certains de leurs composants.

Dans ce but, cette thèse présente la conception à la fois logiciel et hardware (matériel électronique) de serveur dédié à l'exécution de RPCs et favorisant les meilleures performances possibles. D'abord, nous montrons que l'implémentation en hardware de la terminaison de protocoles de communications approvisionnent excessivement les mémoires tampons dû à leur manque de compréhension des contraintes de latence de chaque RPC. Nous montrons qu'il suffit d'exposer ces informations de la couche RPC au hardware afin d'améliorer la performance par 1.25-2.2x. Ensuite, motivés par des études préexistantes montrant le coût considérable de la couche RPC, nous montrons comment un accélérateur RPC peut s'intégrer avec la mise en oeuvre de notre interface réseau. Enfin, nous proposons des techniques d'équilibrage de charge entre les cœurs d'un serveur, permettant aux microservices d'exécuter plus rapidement et simultanément, tout en maîtrisant la latence de queue. Ces propositions améliorent la latence de queue au 99eme centile par 2-5.5x pour les microservices qui stockent des données, et réduisent les « cache miss » d'instructions par 1.1-1.8x pour ceux qui sont « stateless ». En résumé, nous démontrons que la conception et l'implémentation de l'architecture des serveurs avec un support direct pour les RPCs supprime les goulots d'étranglement de ces protocoles, permettant ainsi de meilleures performances pour les microservices.

Mots-clefs : centres des données, serveurs, microservices, appels de procédure à distance, materiel, équilibrage de charge, latence de queue, protocoles de réseau, co-conception, théorie des files d'attente

# **Contents**

| A  | cknowledgements                                        | i     |

|----|--------------------------------------------------------|-------|

| Al | bstract (English/Français)                             | ix    |

| Li | ist of Figures                                         | xix   |

| Li | ist of Tables                                          | xxiii |

| Li | ist of Equations                                       | xxv   |

| 1  | Introduction                                           | 1     |

|    | 1.1 Thesis Goals                                       | 5     |

|    | 1.2 Thesis Statement                                   | 6     |

|    | 1.3 Thesis Contributions                               | 6     |

|    | 1.4 Thesis Organization                                | 8     |

|    | 1.4.1 Bibliographic Notes                              | 9     |

| 2  | Why Design Server Architecture for RPCs?               | 11    |

|    | 2.1 Microservices and μs-Scale RPCs                    | 12    |

|    | 2.2 Datacenter Networks and RPC Transport Protocols    | 13    |

|    | 2.3 Optimized Systems Software                         | 15    |

|    | 2.4 Curtailing Queueing with Inter-Core Load Balancing | 17    |

|    | 2.5 Network-Compute Co-Design                          | 19    |

| Ι  | Designing an RPC-Centric Server                        | 23    |

| 3  | System Overview                                        | 25    |

|    | 3.1 Novel Design Features                              | 25    |

|    |                                                        | xiii  |

#### **Contents**

|   |                      | 3.1.1                                                                          | In-Cache RPC Placement                                  | 26                                                             |

|---|----------------------|--------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|

|   |                      | 3.1.2                                                                          | Fully-Featured RPC Layer with Hardware Acceleration     | 28                                                             |

|   |                      | 3.1.3                                                                          | Enhanced Load Balancing                                 | 31                                                             |

|   | 3.2                  | Applio                                                                         | cability of RPC-Centric Design Extensions               | 32                                                             |

|   | 3.3                  | System                                                                         | m Modelling Techniques                                  | 34                                                             |

|   |                      | - 1 r                                                                          | NDOTE 66 M                                              | 00                                                             |

| 4 |                      |                                                                                | RPC Traffic Management                                  | 39                                                             |

|   | 4.1                  |                                                                                | nt Obstacles: Load Imbalance and Bandwidth Interference | 40                                                             |

|   |                      | 4.1.1                                                                          | Modelling Imbalance and Interference                    | 43                                                             |

|   |                      | 4.1.2                                                                          | System Configurations                                   | 46                                                             |

|   |                      | 4.1.3                                                                          | Results Discussion                                      | 47                                                             |

|   | 4.2                  | Design                                                                         | ning the NEBula Architecture                            | 49                                                             |

|   |                      | 4.2.1                                                                          | Achieving LLC-Resident Queues                           | 50                                                             |

|   |                      | 4.2.2                                                                          | Steering RPC Payloads to L1 Caches                      | 54                                                             |

|   | 4.3                  | NEBU                                                                           | La Operational Walkthrough                              | 56                                                             |

|   |                      | Classes                                                                        | C                                                       |                                                                |

|   | 4.4                  | Cnapi                                                                          | rer Summary                                             | 57                                                             |

| 5 |                      |                                                                                | ware Load Balancing                                     | 57<br><b>59</b>                                                |

| 5 |                      | ality-A                                                                        |                                                         |                                                                |

| 5 | Loc                  | <b>ality-A</b> v                                                               | ware Load Balancing                                     | 59                                                             |

| 5 | <b>Loc</b> : 5.1     | <b>ality-A</b> v                                                               | ware Load Balancing Can Load Balancing be Improved?     | <b>59</b>                                                      |

| 5 | <b>Loc</b> : 5.1     | How C<br>Tempo<br>5.2.1                                                        | ware Load Balancing Can Load Balancing be Improved?     | <b>59</b> 60 62                                                |

| 5 | <b>Loc</b> : 5.1     | How Control Tempor 5.2.1                                                       | ware Load Balancing Can Load Balancing be Improved?     | <b>59</b> 60 62 64                                             |

| 5 | <b>Loc</b> : 5.1 5.2 | How Control Tempor 5.2.1                                                       | ware Load Balancing Can Load Balancing be Improved?     | <b>59</b> 60 62 64 66                                          |

| 5 | <b>Loc</b> : 5.1 5.2 | ### Ality-And How Control                                                      | ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71                               |

| 5 | <b>Loc</b> : 5.1 5.2 | Ality-And How Control Tempor 5.2.1 5.2.2 Load 15.3.1 5.3.2                     | Ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71<br>73                         |

| 5 | 5.1<br>5.2<br>5.3    | Ality-And How Control Tempor 5.2.1 5.2.2 Load 15.3.1 5.3.2                     | Ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71<br>73<br>76                   |

| 5 | 5.1<br>5.2<br>5.3    | Ality-And How Control Tempor 5.2.1 5.2.2 Load 1 5.3.1 5.3.2 Enhant 5.4.1       | Ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71<br>73<br>76<br>80             |

| 5 | 5.1<br>5.2<br>5.3    | ality-And How (Control Tempor 5.2.1 5.2.2 Load 15.3.1 5.3.2 Enhart 5.4.1 5.4.2 | ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71<br>73<br>76<br>80             |

| 5 | 5.1<br>5.2<br>5.3    | ality-And How (Control Tempor 5.2.1 5.2.2 Load 15.3.1 5.3.2 Enhart 5.4.1 5.4.2 | ware Load Balancing Can Load Balancing be Improved?     | 59<br>60<br>62<br>64<br>66<br>71<br>73<br>76<br>80<br>80<br>82 |

| II | Im  | plementation and Evaluation of an RPC-Centric Server    | 95  |

|----|-----|---------------------------------------------------------|-----|

| 6  | Bui | lding NEBULA on Scale-Out NUMA                          | 97  |

|    | 6.1 | Baseline Architecture                                   | 97  |

|    | 6.2 | Architectural Additions                                 | 99  |

|    | 6.3 | RPC Software Interface                                  | 100 |

|    | 6.4 | NIC Extensions for Buffer Management                    | 102 |

|    | 6.5 | NIC Extensions for RPC Reassembly                       | 104 |

|    |     | 6.5.1 Reduced Associativity                             | 106 |

|    | 6.6 | NIC-to-Core RPC Steering                                | 108 |

|    | 6.7 | Methodology                                             | 109 |

|    | 6.8 | Evaluation                                              | 112 |

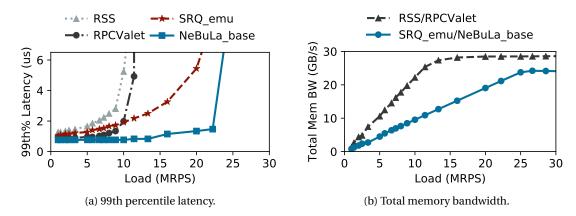

|    |     | 6.8.1 Removing Bandwidth Interference                   | 112 |

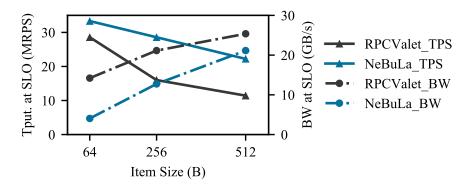

|    |     | 6.8.2 Impact of Varying Workload Parameters             | 113 |

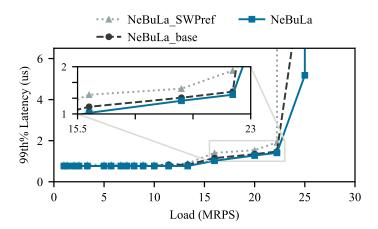

|    |     | 6.8.3 Performance Benefits of NIC-to-Core Steering      | 115 |

|    | 6.9 | Chapter Summary                                         | 117 |

| 7  | Mic | roarchitecture for Integrated RPC Protocol Accelerators | 119 |

|    | 7.1 | Why Couple NICs and RPC Accelerators?                   | 119 |

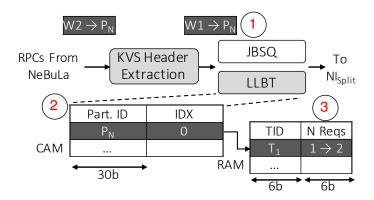

|    | 7.2 | Functional Overview of RPC Processing in CEREBROS       | 122 |

|    | 7.3 | The Architecture of Cerebros                            | 123 |

|    |     | 7.3.1 Multi-Buffer Management                           | 125 |

|    |     | 7.3.2 Distributing the RPC Processing Components        | 127 |

|    | 7.4 | NIC Pipelines for Cerebros                              | 129 |

|    |     | 7.4.1 Request Generation Pipeline                       | 129 |

|    |     | 7.4.2 Remote Request Processing Pipeline                | 130 |

|    | 7.5 | Chapter Summary                                         | 135 |

| 8  | The | Benefits of Locality-Aware Load Balancing               | 137 |

|    | 8.1 | Adding Affinity-Based Load Balancing to CEREBROS        | 137 |

|    | 8.2 | Evaluating Affinity-Based Load Balancing                | 139 |

|    |     | 8.2.1 Methodology                                       | 139 |

#### **Contents**

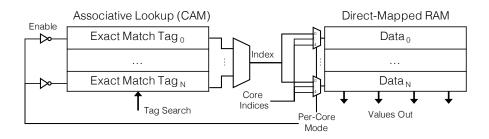

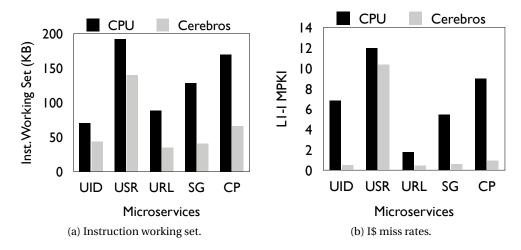

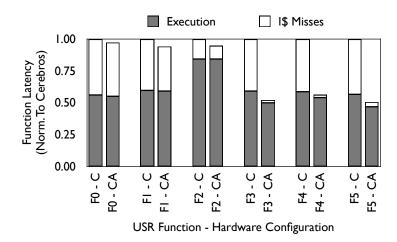

|    |      | 8.2.2          | Availability of Instruction Cache Locality         | 141               |

|----|------|----------------|----------------------------------------------------|-------------------|

|    |      | 8.2.3          | Eliminating Further Instruction Cache Misses       | 142               |

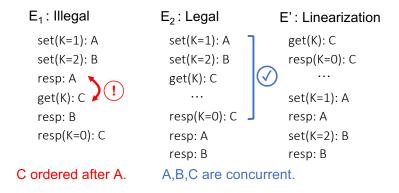

|    | 8.3  | Imple          | ementing Cooperative Concurrency Control           | 144               |

|    |      | 8.3.1          | NIC-Software Interface Modifications               | 145               |

|    |      | 8.3.2          | Instantiating Hardware Support for Write Balancing | 146               |

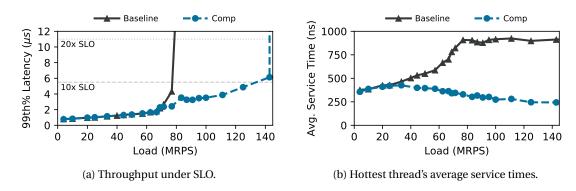

|    |      | 8.3.3          | Software Support for Compaction                    | 147               |

|    | 8.4  | Coop           | erative Concurrency Control in Action              | 148               |

|    |      | 8.4.1          | Methodology                                        | 148               |

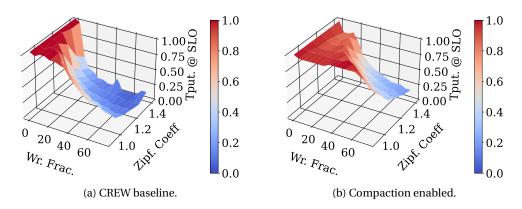

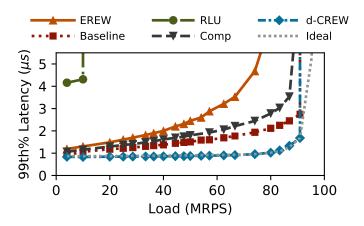

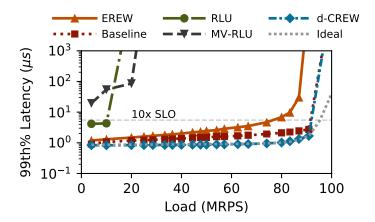

|    |      | 8.4.2          | Dynamic Write Partitioning                         | 150               |

|    |      | 8.4.3          | Software Write Compaction                          | 153               |

|    |      | 8.4.4          | Sensitivity Analysis                               | 156               |

|    | 8.5  | Chap           | ter Summary                                        | 157               |

|    |      |                |                                                    |                   |

| II | I R  | elated         | and Future Work                                    | 159               |

| 9  | Rela | ated W         | ork                                                | 161               |

|    | 9.1  | Towar          | rds Cache-Resident Network Traffic                 | 161               |

|    |      | 9.1.1          | Leaky DMA and Bandwidth Interference               | 161               |

|    |      | 9.1.2          | RPC Scalability Over Connected Transports          | 163               |

|    |      | 9.1.3          | Network-Compute Co-designs                         | 165               |

|    |      | 9.1.4          | Latency-optimized Systems Software                 | 166               |

|    |      | 9.1.5          | Hardware Support for Packet Placement              | 167               |

|    | 9.2  | RPC F          | Framework and Hardware Enhancements                | 168               |

|    |      | 9.2.1          | Other Systems Targeting RPC Acceleration           | 168               |

|    |      | 9.2.2          | Reducing CPU-Accelerator Control Overhead          | 171               |

|    | 9.3  |                |                                                    |                   |

|    | 0.0  | Appli          | cation-Aware Load Balancing                        | 172               |

|    | 0.0  | Applio 9.3.1   | Cation-Aware Load Balancing                        |                   |

|    | 0.0  |                |                                                    | 172               |

|    |      | 9.3.1          | Instruction Supply in Servers                      | 172<br>173        |

|    |      | 9.3.1<br>9.3.2 | Instruction Supply in Servers                      | 172<br>173<br>174 |

| Co                                                | ontents |

|---------------------------------------------------|---------|

| 10 Future Research Directions                     | 179     |

| 10.1 Virtualized and Multi-Tenant Deployments     | 179     |

| 10.2 Towards Asynchronous Microservices           | 180     |

| 10.3 Improved Server Simulation Methodologies     | 181     |

| 10.4 RPC Scheduling Based on End-to-End Latencies | 184     |

| 11 Conclusions                                    | 187     |

| Bibliography                                      | 189     |

| Curriculum Vitae                                  | 223     |

# **List of Figures**

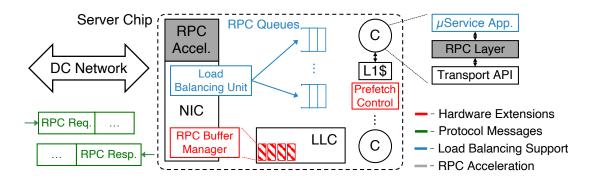

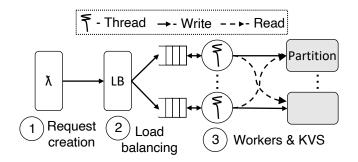

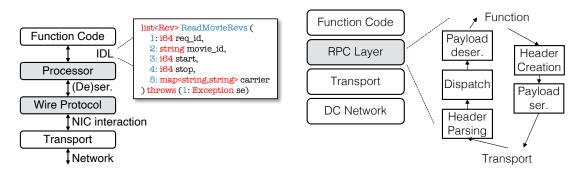

| 3.1 | System overview of an RPC-centric server architecture, with colour coding to                       |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | indicate logically grouped components that implement specific functionalities.                     | 26 |

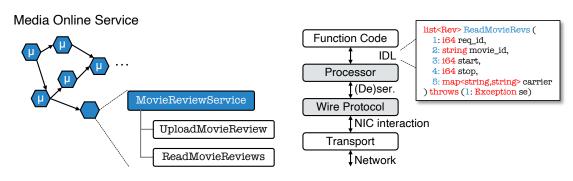

| 3.2 | The architecture of a microservice and a production RPC stack, and an example                      |    |

|     | of a function's specification in an Interface Description Language                                 | 28 |

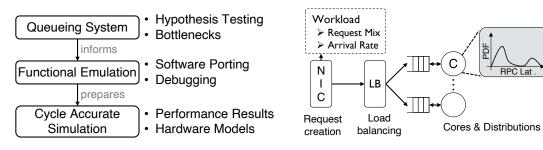

| 3.3 | Modelling techniques and their respective use-cases for studying RPC-centric                       |    |

|     | server architectures                                                                               | 35 |

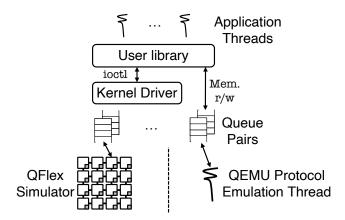

| 3.4 | Unified emulation and simulation stack, using QEMU and QFlex                                       | 36 |

| 4.1 | Queueing system model of the memory hierarchy interactions associated with                         |    |

|     | handling incoming RPCs                                                                             | 43 |

| 4.2 | Discrete-event simulation results, showing the impact of load imbalance and                        |    |

|     | memory bandwidth interference on the throughput and tail latency of $\mu s\mbox{-scale}$           |    |

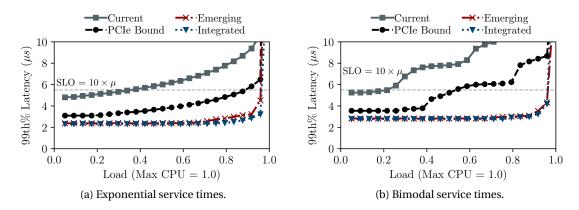

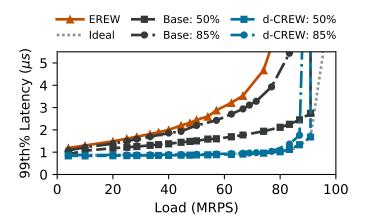

|     | RPCs                                                                                               | 47 |

| 4.3 | Relationship between offered load and $E\left[\hat{N}_q\right]$ for two different core counts (k). | 51 |

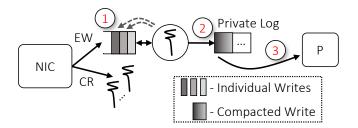

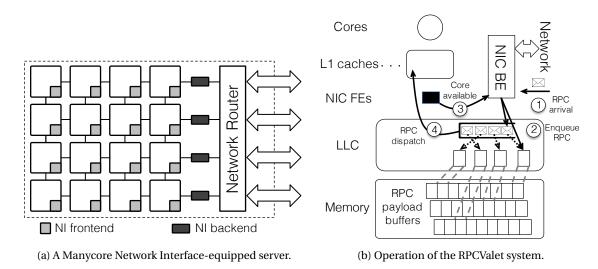

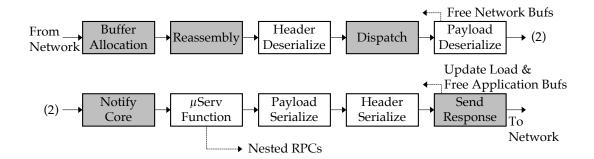

| 4.4 | Walkthrough of the process of RPC reception in NeBuLa                                              | 56 |

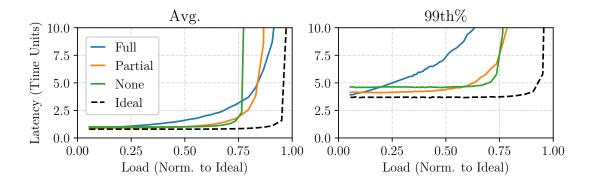

| 5.1 | Load vs. latency curves for different function partitioning strategies, assuming                   |    |

|     | an SLO of 10 units ( $10 \times \bar{S}$ )                                                         | 67 |

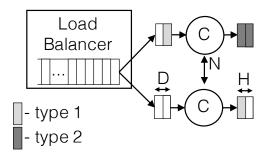

| 5.2 | Simulated queueing network for JBSQ(D) with history                                                | 68 |

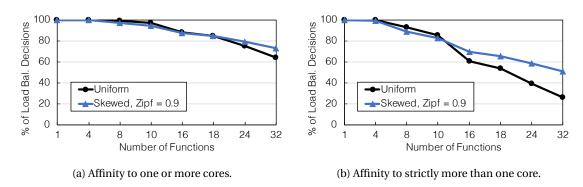

| 5.3 | Results demonstrating the availability of affinity at RPC dispatch time, for a                     |    |

|     | 16-core system                                                                                     | 70 |

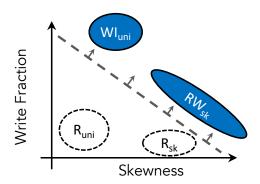

| 5.4 | KVS workload taxonomy, showing regions targeted by this thesis in blue                             | 74 |

| 5.5 | Queueing model for a server running a KVS                                                          | 76 |

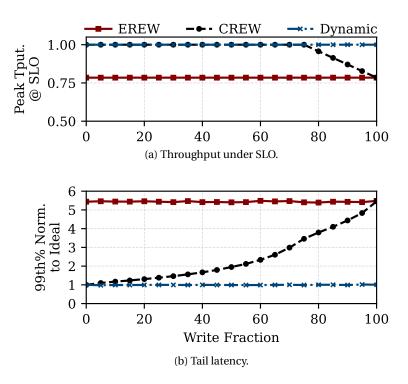

| 5.6 | Throughput and tail latency of concurrency control policies compared to an ideal                   |    |

|     | system with no synchronization overhead. Uniform key popularity distribution.                      | 78 |

|     |                                                                                                    |    |

| 5.7  | Throughput of a CREW KVS with and without write compaction, normalized to         |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | an ideal system with no synchronization overhead                                  | 79  |

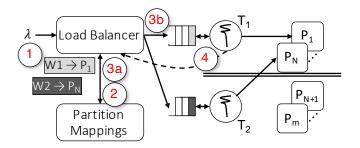

| 5.8  | Load balancing additions required to realize Dynamic CREW (d-CREW)                | 81  |

| 5.9  | Design of write compaction in C-4                                                 | 83  |

| 5.10 | Executions showing linearizable compaction                                        | 85  |

| 5.11 | Design of NIC extensions and software API for locality-aware load balancing       | 88  |

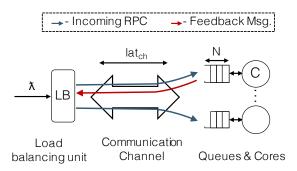

| 5.12 | 2 Queueing system model to study the impacts of load balancing unit proximity.    | 90  |

| 5.13 | B Load vs. latency curves showing performance attainable by load balancing units  |     |

|      | of various proximities to the workers they serve                                  | 92  |

| 6.1  | The baseline transport and load balancing architecture for NeBula                 | 98  |

| 6.2  | Location of implemented NeBula extensions, and updated system operation.          | 100 |

| 6.3  | Pseudocode of an RPC-handling event loop                                          | 101 |

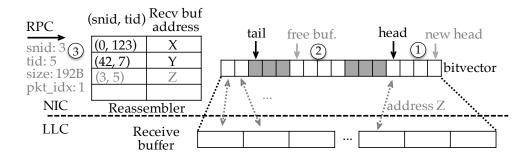

| 6.4  | NIC RPC reassembly and buffer management                                          | 102 |

| 6.5  | Relationship between reassembler associativity and upper bound on RPC con-        |     |

|      | flict probability.                                                                | 107 |

| 6.6  | Tail latency and bandwidth for all evaluated systems, using a 50/50 GET/SET       |     |

|      | query mixture                                                                     | 112 |

| 6.7  | Performance of RPCValet and NEBULA varying the MICA value size, using a           |     |

|      | 50/50 GET/SET query mix                                                           | 115 |

| 6.8  | Comparison of NeBula prefetching policies. MICA uses 512B values and a            |     |

|      | 50/50 GET/SET query mix                                                           | 116 |

| 7.1  | RPC stack layers, and the underlying runtime hardware operations                  | 120 |

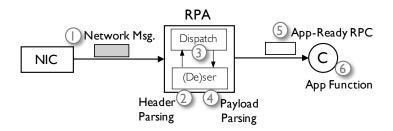

| 7.2  | Block diagram depicting the stages of an RPC as it is processed by Cerebros. $$ . | 122 |

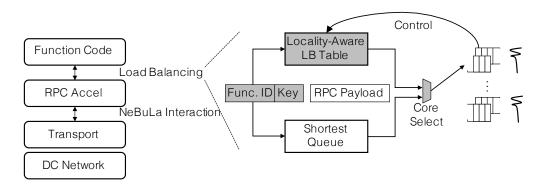

| 7.3  | NIC-interfaced RPC accelerator design                                             | 124 |

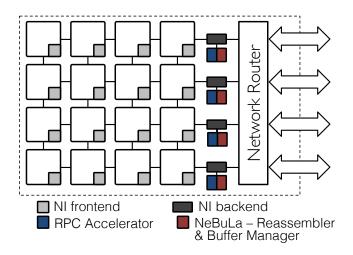

| 7.4  | Chip-level integration of Cerebros                                                | 128 |

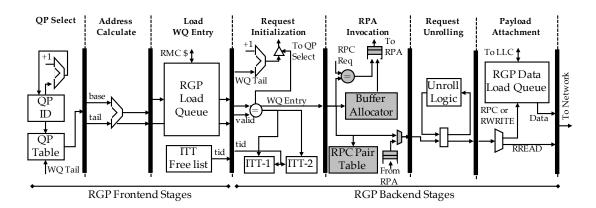

| 7.5  | RGP microarchitecture. Shaded structures are new in CEREBROS                      | 129 |

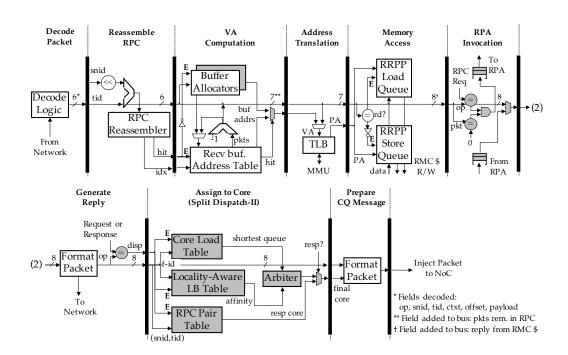

| 7.6  | RRPP microarchitecture. Shaded structures are new in CEREBROS                     | 131 |

| 7.7  | Microarchitecture of the Locality-Aware Load Balancing Table, showing associa-    |     |

|      | tive lookup array and RAM storage.                                                | 134 |

| 8.1 | Frontend behavior of microservices                                                         | 142 |

|-----|--------------------------------------------------------------------------------------------|-----|

| 8.2 | Breakdown of the USR microservice's functions into execution time and instruc-             |     |

|     | tion cache misses                                                                          | 143 |

| 8.3 | Modified NIC request assignment pipelines. The shaded portions are used to                 |     |

|     | implement C-4                                                                              | 146 |

| 8.4 | KVS throughput under SLO with uniform key popularity and $f_{wr}$ = 50%. The               |     |

|     | vertical axis terminates at the KVS' SLO                                                   | 150 |

| 8.5 | KVS throughput under relaxed SLO, using the same workload as Figure 8.4. $$                | 151 |

| 8.6 | Comparison of KVS throughput under SLO with varied $f_{wr}$ , using uniform key            |     |

|     | popularity                                                                                 | 152 |

| 8.7 | System performance comparison for a $RW_{sk}$ workload with $\gamma$ = 1.25 and $f_{wr}$ = |     |

|     | 5%                                                                                         | 153 |

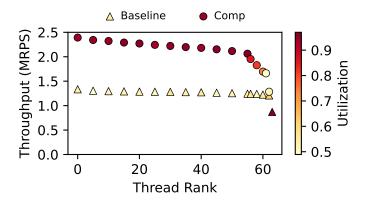

| 8.8 | Per-thread throughput, using the same $RW_{sk}$ workload as previously ( $\gamma=1.25$ ,   |     |

|     | $f_{wr}$ = 5%)                                                                             | 154 |

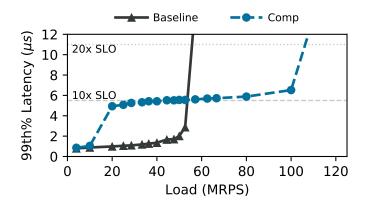

| 8.9 | Performance for $RW_{sk}$ with $\gamma = 0.99$ , $f_{wr} = 50\%$                           | 155 |

# **List of Tables**

| 3.1 | $Scope\ of\ applicability\ of\ contributions\ towards\ RPC-centric\ server\ architecture.$ |     |

|-----|--------------------------------------------------------------------------------------------|-----|

|     | Asterisks indicate that implementing a feature is possible, with reduced benefit.          | 34  |

| 4.1 | 99th% of the number of queued requests, for a many-core server at maximum                  |     |

|     | load under 10× SLO                                                                         | 52  |

| F 1 | Number of functions that can be entirely contained in basic and predictor driven           |     |

| 5.1 | Number of functions that can be entirely contained in basic and predictor-driven           |     |

|     | CPU frontends without incurring I\$ thrashing                                              | 65  |

| 5.2 | Values of $N$ in JBSQ(N) for various communication channel latencies and service           |     |

|     | time distributions                                                                         | 91  |

|     |                                                                                            |     |

| 6.1 | Parameters used for cycle-accurate simulation of NeBuLa on QFlex                           | 110 |

| 6.2 | Sensitivity to various MICA GET/SET query mixtures                                         | 113 |

|     |                                                                                            |     |

| 8.1 | USR Microservice function IDs, names, and functionalities                                  | 140 |

| 8.2 | Parameters used for cycle-accurate simulation of locality-aware load balancing.            | 141 |

| 83  | Impact of item size on write compaction                                                    | 157 |

# **List of Equations**

| 4.1 | NIC Traffic Miss Probability for Queueing Analysis                                | 45  |

|-----|-----------------------------------------------------------------------------------|-----|

| 4.2 | Expected number of queued requests at a many-core server with an exponential      |     |

|     | service time distribution                                                         | 51  |

| 5.1 | Threshold condition for microservice functions to cause thrashing in a CPU core's |     |

|     | L1 instruction cache                                                              | 65  |

| 5.2 | Software speedup potential from software write compaction                         | 83  |

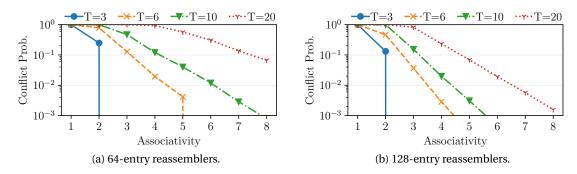

| 6.1 | Probability of a conflict in any possible bin, assuming independence              | 107 |

## 1 Introduction

Online services have become a multi-trillion dollar industry, with e-commerce corporations boasting a combined market capitalization of 9.9 trillion USD in 2019 [89] and the single biggest player generating global sales of 386 billion USD [15]. These massive profits have led to tremendous investments in hyperscale datacenters, to a degree that a single facility often consumes more than 100MW of electricity [31, §4]. In the drive to attract more customers, service providers are continually enhancing their first-party services with personalized user recommendations, curated advertisements, social network connections, and logging each action taken for legal privacy compliance [238]. Offering such features requires not only development effort, but also the necessary staff to debug, deploy, and maintain the entire service *in situ* while it is live. It is an understatement to say that such a task is merely complex.

In addition to the first-party online services that gave rise to today's hyperscale datacenters, software vendors operating at smaller scales have begun to shift their services to the cloud. The benefits of migrating to cloud-native software for small- to medium-scale enterprises are numerous. Not only is acquiring and managing dedicated hardware now unnecessary, but programmers can now take advantage of low-cost system infrastructure such as Amazon's plethora of Software-as-a-Service offerings [13, 14, 262] or simplified programming models such as serverless computing [5, 124]. The end result of the move to cloud-native software is an ongoing confluence between traditional first-party datacenter workloads (e.g., web search) and private enterprise applications now running in datacenters. Both styles of applications are beginning to share the same underlying software services [248] and platforms [31, §2.7.1],

and experience the same scalability and cost-reduction benefits.

As first-party and cloud-native applications continue to grow in scale and complexity, software architecture best practices have changed to match. In particular, datacenter providers and third-party enterprises have both turned towards using a software architecture that employs many independent *microservices*, which are modular and interact with each other to communally implement the online service's functionality. Each microservice is traditionally developed by a small independent team to maximize programmer productivity. A microservices architecture provides significant benefits for fault tolerance, scalability, debuggability, and perhaps most importantly, deployment velocity [31, 127, 179]. As such architectures mandate strict modularity between each component, they rely on a shared communication API to interact, the most common of which is Remote Procedure Calls (RPCs). Therefore, it is becoming commonplace for online service providers to develop a custom RPC layer which is used across the entire organization and exposed to third-party tenants – examples include Google's gRPC [92] and Facebook's own fork of Apache Thrift [19, 72].

The ongoing growth of RPC-connected microservices implies drastic growth in communication between microservices, and hence the performance of each server's communication stack is absolutely paramount. In particular, as every single message between microservices must traverse the RPC and transport protocol layers, as well as the datacenter network itself, the performance of all three modules is directly manifested to the end user. Compounding the challenge is the well-known fact that users are sensitive to even slightly delayed responses. For example, Akamai reports that a 100ms delay in page load time reduces sales conversion rates by 7% [7] and Google executives report that 0.5-second delays in search results reduce user traffic by 20% [91]. The common practice of auto-scaling each microservice across many servers [190] further complicates the task of providing a seamlessly interactive user experience, due to a challenge dubbed the "Tail at Scale". The Tail at Scale principle dictates that as the number of servers involved in handling a user request increases, it becomes highly probable that the slowest individual servers will dictate the latency experienced by the user [59]. Tail-tolerant computing has become one of the key challenges in the datacenter space, and has created a significant research impetus to curtail sources of tail latency in all layers of the system stack [54, 98, 163, 193, 223].

Although cross-stack research and development has delivered substantial performance gains in response to the need for rapid network communication, such innovations have exposed server-side inefficiencies as performance bottlenecks for datacenter-wide microservice deployments. In particular, optimized topologies [90,243] and production rollouts of multi-hundred gigabit NICs [153] have created a growing gap between server packet processing capabilities and what the network can supply. The fact that the roadmaps for future Ethernet and InfiniBand fabrics forecast bandwidth growth to 1Tbps [112,252] in the face of slowing silicon density scaling [57] will only make the gap more cavernous, especially considering that future optical networks promise richer connectivity with round-trip times of just a few nanoseconds [28]. The need to bridge the gap between network and server capabilities has prompted the development of fully customized protocol stacks to replace legacy TCP/IP (e.g., Google's Snap [178]), or at-scale deployments of hardware terminated protocols [44,93]. As systems aspire to allow communication-intensive microservices to operate as near to the hardware's raw capabilities as possible, server architecture itself will inevitably become an equally important optimization point.

In this thesis, we posit that in order for microservices to take advantage of current and future developments in networking technology, server architectures must also evolve to contain support for the underlying operations that comprise RPCs. We argue for such architectural adjustments on three grounds. Firstly, microservices are beginning to exhibit microsecond-scale runtimes; prominent applications such as data stores [54, 129, 176], software-defined network functions [274], state-machine replication [132], and user management [276] only occupy the CPU for a few  $\mu s$  at a time. This trend is not a problem by itself. However, recent work has shown that the computation cost of the software RPC protocols repeatedly invoked by such microservices is comparable to the runtime of the applications themselves [159, 276]. Therefore, it is logical to consider deploying specialized hardware accelerators for RPC processing [222]. Any RPC processing accelerator directly and repeatedly interacts with the server's NIC, memory hierarchy, and on-chip fabric, and therefore these components should be co-designed to function well together.

Secondly, the core counts of server processors have continued to grow, and therefore so does the importance of load balancing RPCs among those cores. Advances in chiplet manufacturing technology have made it possible for CPU vendors to construct many-core CPUs without prohibitive cost or yield concerns [134], and therefore many processors already feature 64 or more physical cores [36, 209, 266]. It is rigorously established that minimizing tail latency requires aggressively limiting the queueing time of RPCs, and that any load imbalance between CPU cores worsens with increased total core count. Therefore, deploying microservices with strict tail-latency constraints on such many-core servers mandates RPC load balancing to be a primary design concern, particularly because there is growing evidence that simple shortest-queue load balancing policies are not optimal for all applications [61, 182]. In particular, the fact that common microservices often have µs-scale latencies creates an emerging opportunity – an enhanced load balancing policy with the capability to improve cache locality while simultaneously limiting queueing delays can significantly boost the performance of such short RPCs.

Thirdly, the fact that underlying datacenter transport protocols have begun to be designed around the specific semantics and constraints of RPCs [150, 153, 193] creates opportunities for drastic server-side performance optimizations. In particular, hardware-terminated protocols that are agnostic to such RPC semantics contain significant inefficiencies in buffer management and data placement, which can be remedied by natively offering RPC support and exposing the application's tail latency goals to the NIC. We therefore conclude that it is time for an RPC-centric server architecture to emerge to complement the combination of latency-critical  $\mu$ s-scale software, improved networks and protocols with native RPC support, and powerful many-core server hardware.

To that end, this thesis leverages the power of integrating network and compute logic, a trend that is gaining traction in both academia [108, 109, 137, 199] and industry [121, 204, 207]. Our work begins with a highly optimized, integrated network interface baseline that has already eliminated common bottlenecks such as the server's I/O interconnect [199] and core-to-NI interactions [53]. Such a baseline is the ideal substrate for realizing the full benefits of an RPC-centric server architecture.

#### 1.1 Thesis Goals

Our primary goal is to design a bespoke server architecture which is purpose-built to support the needs of communication-intensive microservices relying on RPCs. We begin by investigating the tradeoffs inherent in deploying hardware-terminated protocol stacks at datacenter scale, because such protocols have begun to see large-scale deployments as a response to demands for increased bandwidth at lower latency [44, 93]. We find that the immense bandwidth of today's NICs can create memory bandwidth interference with the CPU cores when RPC payloads spill out of the server's caches and into its DRAM. Furthermore, we identify that the source of the problem is the buffer bloat created by scaling hardware-terminated protocols to many communicating nodes, and show that the resulting bandwidth contention can reduce the throughput of a server by 2×. Although it is possible to remove bandwidth interference with existing NIC technology, it comes at the cost of sacrificing inter-core load balancing. Therefore, we set out to remove bandwidth contention while maintaining the ability to balance load between a CPU's many cores.

We then turn our attention to the co-design of emerging RPC protocol accelerators with integrated network interfaces. Although multiple prior works have proposed hardware accelerator designs that remove the cost of production RPC layers [136, 276], we remark that such accelerators must explicitly be designed alongside the server's NIC or much of their potential performance will be lost due to pathological inefficiencies when interacting with the host server's memory hierarchy. Specifically, performance is lost due to excessive task offloading from the CPU to the accelerator, or the need to shuffle requests between CPU cores in software to implement RPC load balancing. In agreement with prior work that shows RPC accelerators must be directly interfaced with the NIC [276], the second goal of this thesis is to dovetail such support into the pipelines of an integrated network interface.

Finally, we study load balancing policies for RPC-centric servers, in the context of  $\mu$ s-scale applications where cache locality is critical and can drastically reduce application runtime. Although cache locality has already been discussed as a critical factor for software packet processing workloads [76], we look beyond such applications and demonstrate specifically how improved locality exists in stateless microservices comprised of many independent functions,

and well known data caching layers. However, identifying sources of locality is not enough to ensure improved performance under tail latency constraints. Our final goal is therefore to enhance load balancing policies with the aforementioned sources of locality in mind, while simultaneously maintaining the microservice's tail latency guarantees.

#### 1.2 Thesis Statement

Judicious design of a server's NIC hardware around RPC semantics removes bottlenecks to deploying microservices at datacenter-scale, and facilitates load balancing enhancements that boost throughput under tight tail-latency guarantees.

#### 1.3 Thesis Contributions

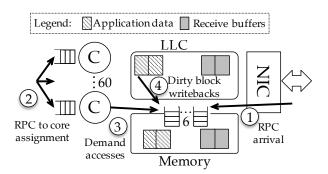

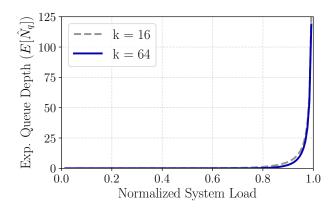

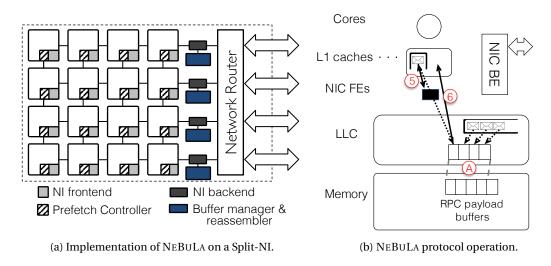

Our work proposes modifications to both NIC hardware and microservice software to form the first RPC-centric server architecture. The first contribution of our work is NeBuLa, a set of NIC hardware and protocol extensions that unblock hardware-terminated protocols from incurring memory bandwidth interference while retaining the flexibility of inter-core load balancing. The key insight enabling NeBuLa is that a given microservice's tail latency target is effectively an implicit constraint on the queue depth that a particular RPC can experience. Therefore, the buffer growth associated with scaling hardware-terminated protocol stacks is unnecessary and can be shrunk without introducing excess tail latency. Under heavy load, RPCs that would have arrived at the end of a long queue are eagerly rejected, and clients are informed that their tail latency would have been violated.

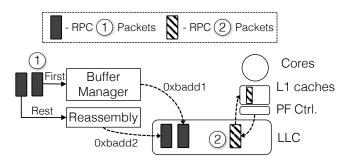

Our second contribution extends prior work that designs an accelerator for the de-serialization operations underlying production RPC layers [275] to implement CEREBROS, a NIC-integrated accelerator that is capable of executing the entire RPC stack. CEREBROS is specifically designed to dovetail into the pipelines of NEBULA and its state-of-the-art Manycore Network Interface [53], so that the raw performance potential of existing de-serialization accelerators can be preserved in the context of many-core chips and multi-hundred gigabit NICs. Specifically, we demonstrate how CEREBROS can be architected and implemented across many *distributed* NIC components. A critical feature of CEREBROS is that it provides full visibility into the protocol

headers of incoming RPCs, making it an ideal substrate for our final contribution: enhancing state-of-the-art load balancing policies to account for application-level cache locality based on RPC header fields.

Finally, our third contribution proposes architectural and software extensions to integrated NICs in order to facilitate load balancing decisions for increased application-level cache locality. We show that although existing NIC technologies can be employed to enhance the cache locality of microservices, current best-case designs can only employ static policies that sacrifice load balancing, and therefore tail latency guarantees, by design. In contrast, we contribute the insight that knowledge of the state of each thread's input queue of RPCs is sufficient to develop locality-aware load balancing policies that reduce the microservices' processing times while maintaining tail latency.

Concretely, we demonstrate the following two scenarios: firstly, for microservices that primarily execute stateless application logic, instruction cache (I\$) locality is plentiful but hidden by current policies that interleave the executions of various RPCs on the cores. Making load balancing decisions based on the temporal state of each CPU core's input queue reveals the hidden I\$ locality, reducing cycles stalled on I\$ misses and improving RPC throughput. Secondly, for microservices that cache data in key-value stores, locality manifests itself through concurrency control. Current policies treat all write requests equally, regardless of whether they are truly conflicting or not; we show that this decision leads to unnecessarily inflated tail latency *and* reduced throughput depending on the workload. We therefore introduce C-4, a simple NIC extension and matching software optimization which allows independent write requests to be balanced across cores, and creates batches of dependent writes that are applied as one to reduce synchronization events.

We implement and evaluate all the above contributions on top of the Scale-Out NUMA network protocol stack [199], extending its Remote Memory Controller to become a fully-fledged, RPC stack-terminating endpoint. Our evaluation focuses on throughput under tight 99th% latency constraints, showing that judicious hardware and software support for RPC-centric server architecture indeed fulfills our thesis design goals. In particular, we show that RPC-centric server architectures reap the following benefits:

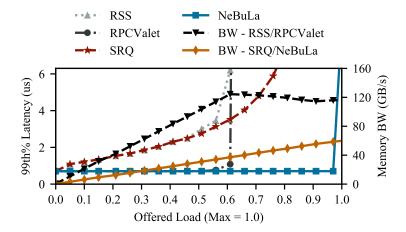

- 1. Evaluated on a simple key-value store microservice, NeBuLa grants  $1.9\times$  improved throughput under 99th% tail latency constraints, which is within 12% of the theoretical maximum our software stack can reach.

- 2. The RPC protocol acceleration of CEREBROS allows load balancing decisions to be made on fields comprising an RPC's header at the line rate of the server's NIC. Setting instruction cache locality as the primary goal reduces I\$ misses by  $1.1 1.8 \times$  in a representative microservice taken from the DeathStarBench suite [81].

- 3. When deployed with C-4's hardware support to balance independent writes and software support for write batching, it is possible for key-value store microservices to attain  $2-5.5\times$  better 99th% latency and  $1.3-1.7\times$  higher throughput.

#### 1.4 Thesis Organization

The remainder of this thesis is organized as follows. First, Chapter 2 makes the case for why server architecture should evolve to become RPC-centric, focusing on five critical software and technology trends. Then, we present the design, implementation, and evaluation of our work in three parts:

- Part I presents the design of an RPC-centric server architecture. Chapter 3 covers an overview of the architecture, the role of each contribution, and its relevant motivating trend(s) covered in Chapter 2. Chapter 4 then explains the design of NEBuLA, beginning with the quandary between memory bandwidth interference and load imbalance before explaining the mathematical insights underpinning our proposed set of NIC and protocol extensions. Finally, Chapter 5 shows how locality-aware load balancing policies can do much more than simply limit RPC queueing, namely reduce the processing times of a microservice's RPCs themselves.

- Part II presents our implementation and evaluation of the design contributions in Part I. Chapter 6 lays out how we build NEBULA on top of Scale-Out NUMA, enabling its integrated NIC and lean protocol stack to terminate traffic from thousands of communicating nodes without experiencing bandwidth interference. Chapter 7 demonstrates how existing accelerators for RPC de-serialization can be unified with NEBULA to form

CEREBROS, a full RPC accelerator. CEREBROS is a key enabler for locality-aware load balancing policies because it grants access to each RPC's header fields as they arrive at the NIC's load balancer. Finally, Chapter 8 concretely instantiates hardware support for the locality-aware load balancing policies in Chapter 5 and evaluates their effectiveness.

• Part III discusses the rich field of related work in Chapter 9, and presents future research directions in Chapter 10. We conclude the thesis in Chapter 11.

#### 1.4.1 Bibliographic Notes

This thesis was conducted under the supervision of my advisors: Babak Falsafi (EPFL), and Alexandros Daglis (Georgia Institute of Technology). Portions of it are based on collaboration with multiple colleagues: Arash Pourhabibi, Siddharth Gupta, Virendra Marathe, and Dionisios Pnevmatikatos. Chapters 4 and 6 are based on a publication in the *Proceedings of the 47th International Symposium on Computer Architecture (ISCA)* in 2020 [250]. Chapter 7, and parts of Chapters 5 and 8 are based on a publication in the *Proceedings of the 54th International Symposium on Microarchitecture (MICRO)* in 2021 [276], which is shared between this thesis and "Hardware-Software Co-Design of an RPC Processor" [222]. The contributions of Cerebros presented in this thesis are the microarchitectural integration with Nebula, and locality-aware load balancing. Finally, the remaining parts of Chapters 5 and 8 are based on a publication which has been accepted and will appear in the *2023 International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*.

# 2 Why Design Server Architecture for RPCs?

In this section, we provide a background on current trends in the datacenter hardware and software environment that form supporting pillars to our contribution of an RPC-centric server architecture. First, we discuss the trend of software decomposition, and explain how the choice to adopt a microservices architecture results in a single user request generating hundreds or thousands of fine-grained RPCs with only a few microseconds (μs) of runtime each. We then describe how datacenter networks and systems software have evolved to support such applications, by proposing latency-optimized topologies and protocols to reduce round-trip times. The confluence of these two trends implies that server-side latency will form the majority of the service's execution time, as traditional bottlenecks such as protocol processing and network traversal disappear. Systems software optimizations have exacerbated the increasing contributions of server-side latency by providing user-level network I/O and removing sources of latency jitter. Next, we identify that server architectures are increasingly characterized by high core counts, which increases the importance of request-level load balancing, and motivate further considerations for enhancing current policies with the notion of application-level locality. Finally, we note that the emerging industry and academic trend towards network-compute co-design is a powerful tool to enable specializing server architecture to handle challenging µs-scale RPCs at the bandwidth of today's NICs, with tight tail latency guarantees.

#### 2.1 Microservices and µs-Scale RPCs

Online service providers are faced with the challenging task of architecting highly available, interactive services that scale to billions of users, with new features being added weekly or daily [31]. To simultaneously achieve these challenging goals, software engineers are increasingly turning towards decomposing their services into many independent software modules which interact with each other to synthesize responses [81, 127]. When taken to the extreme, such software decomposition results in a *microservice architecture*, where each module performs only a single task and is isolated from the rest of the surrounding services by means of enforced modularity. Although microservices architectures are drastically more scalable and simpler to maintain, they rely heavily on a lightweight and scalable communication API, the most common of which is the Remote Procedure Call (RPC); examples of company-wide libraries include Google's gRPC [92] and Facebook's own fork of Apache Thrift [19,72].

Despite the benefits of microservice architectures for developers and cloud providers, deploying software in such a manner creates new performance challenges. The first challenge is that common microservice software tiers are becoming increasingly fine-grained, with runtimes as short as a few  $\mu$ s for applications such as data stores [54, 129, 176], network function virtualization [274], state-machine replication [132], and simple user management business logic [276]. Fine-grained applications like these increase the amount of time spent in the layers of the computing stack that *support* the microservices, rather than the microservices themselves, increasing the importance of rapid network communication.

Structuring applications as microservices also increases the difficulty of providing guarantees known as "Service Level Objectives" (SLOs) on the latency of the online service's *slowest* responses [59]. Each additional software layer in the microservice graph complicates the process of controlling the service's tail latency, because a single user interaction will have a higher chance of experiencing a transient event (e.g., a context switch) [81, §8]. The depth to which production services are layered is profound, with Amazon reporting that a single page load typically accesses more than 150 internal services [60], and the request tree that is generated on a single Google search reportedly spanning across 1000 servers [58, 227]. Each of these numerous inter-microservice RPCs must transit multiple software and hardware queues,

introducing additional latency and the potential for significant delays due to the well known non-linear behaviour of queueing systems.

Fine-grained applications also imply that traditionally non-consequential server-side events (e.g., context switches, TLB misses, interrupts) may now form tail events resulting in SLO violations at higher layers of the overall service. To illustrate, consider the Masstree in-memory data store, which employs a hybrid trie-tree as an index to all key-value pairs it contains [176]. The sequential nature of the tree traversal implies that a simple get RPC may encounter TLB misses for multiple tree nodes, each of which costs 200–400ns, depending on page table caching, DRAM latency, and the number of levels in the architecturally-defined page table. As the measured mean service time for gets is approximately 1.25µs [54], multiple TLB misses can easily result in response latencies falling in the latency tail; other events such as context switches or interrupts would have an even greater effect.

**Summary.** Although microservices and tiered architectures significantly improve ease of deployment, debuggability, and fault tolerance for software engineers, the commensurately decreasing software runtimes and growing network communication costs will inevitably result in worse average *and* tail latency. Therefore, systems architects have commenced a hunt for the "killer microseconds" [32] across the datacenter system stack, particularly focusing on the layers providing inter-microservice communication.

#### 2.2 Datacenter Networks and RPC Transport Protocols