# Efficient Analytical Query Processing on CPU-GPU Hardware Platforms

Présentée le 29 août 2022

Faculté informatique et communications Laboratoire de systèmes et applications de traitement de données massives Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Periklis CHRYSOGELOS

Acceptée sur proposition du jury

Prof. M. Grossglauser, président du jury

Prof. A. Ailamaki, directrice de thèse

Prof. A. Pavlo, rapporteur

Prof. P. Boncz, rapporteur

Prof. S. Kashyap, rapporteur

Give me a place to stand, and I will move the earth.

— Archimedes

To my parents, Nikos and Polina, and my partner, Georgia.

## Acknowledgements

This thesis materialized only because I was fortunate enough to be surrounded by many great people who supported me and provided invaluable feedback.

First and foremost, I would like to thank my advisor, *Anastasia Ailamaki*. She has been a great teacher; her structured way of guidance and her encouragement to seek perfection and set ambitious goals, both in research and life, have been invaluable. Her patience, support, and understanding provide a second-family-like lab environment that fosters great research ideas. Further, she takes great care in providing us with all the necessary infrastructure and peculiar hardware configurations, without which this thesis would not be possible. I will always be grateful for the environment she created in the lab, her guidance, and the opportunity she gave me to be a member of the DIAS family.

I would also like to thank my jury members for their time investment and their constructive comments. Specifically, I would like to thank *Peter Boncz* and *Andy Pavlo* whose work highly influenced my thesis and their insightful questions and guidance helped in shaping it. Further, I am grateful to *Sanidhya Kashyap* for his very detailed comments, and for helping me improve the content of this thesis. Last but not least, I also thank *Matthias Grossglauser* for serving as my thesis committee president and creating a pleasant thesis exam environment.

I would also like to thank *Weiwei Gong* for being a great mentor during my internship at Oracle, and for her continuous support even beyond the internship, *Danica Porobic* for helping me discover this great team, and *Shasank Chavan, Jim Kearney, Tirthankar Lahir, Kantikiran Pasupuleti, Gary Smith, Hong Su,* and *Garret Swart* for their valuable feedback and support.

During my PhD, I had the pleasure to closely collaborate with multiple great people, namely Manos Karpathiotakis, Raja Appuswamy, Aunn Raza, Panagiotis Sioulas, Viktor Sanca, Angelos Anadiotis, Ioannis Mytilinis, Odysseas Papapetrou, Anna Herlihy, Hamish Nicholson, Georgios Michas, Konstantinos Koukas, Vladimir Indjic, and Rubin Daija. In addition to the direct collaborations, I also thank all the DIAS family for the great discussions, coffee breaks and in general the great time in the office: Angelos, Anna, Aunn, Bikash, Christina, Darius, Diane, Dimitra, Eleni (x2), Erika, Fabienne, Foteini, Georgios, Hamish, Haoqiong, Ioannis, Konstantinos, Lionel, Manos, Margaret, Matt, Mirjana, Odysseas, Panagiotis, Srinivas, Stella, Tahir, Utku, and Viktor. Likewise, I would like to thank the extended (alumni from before I joined, RAW

Labs SA, EPFL system admins, etc) DIAS family for a great time at lab gatherings, BBOs, and meetups: Benjamin, Cesar, Danica, Ippokratis, Iraklis, Manos, Miguel, Pinar, Stéphane, and Thomas. I am especially thankful to a set of people in DIAS: Manos Karpathiotakis and Raja Appuswamy with whom I collaborated in the first years of my PhD and they introduced me to research. In addition to being brilliant researchers, they are always there to discuss and provide guidance. Aunn Raza is always there both as a friend and as a colleague – including late at night and during countless early morning deadlines. Thank you for all the awesome, endless brainstorming sessions and for being the sounding board for all the technical absurdities. Viktor Sanca, eager to explore everything, help, brainstorm about any topic, and deep-dive into even the most obscure research ideas, has been a great, enthusiastic collaborator and a source of motivation. Angelos Anadiotis has been a great collaborator, withstood the hardness of time and accommodated countless incompatible schedules, from daylight incompatibilities to providing his nonstop support even in the absence of a viable desk or chair. Odysseas Papapetrou, while supposedly a hard shell, has been a constant source of joy as well as interesting research discussions and a reminder of more theoretic directions. Dimitra Tsaoussis, Erika Raetz, Margaret Church and Fabienne Ubezio provided tremendous assistance with many, often just-in-time, administrative and organizational tasks. Stéphane Ecuyer and Lionel Sambuc, our brilliant and passionate system administrators, were always available to assist and quickly fix every issue, provided tremendous assistance in planning the hardware configurations, coordinating with the suppliers, and helping satisfy all the niche requirements. Thank you all!

I am thankful to all my friends who made my life enjoyable all these years: *Akhil, Angelos, Ankita, Anna, Antonia, Aunn, Batool, Christina, Eirini, Iro, Lionel, Panagiotis, Panayiotis, Panos, Stelios, Stella, Thanos,* and *Viktor*. In addition to being a great colleague, Aunn is a great friend, the go-to guy for everything, from board-game nights to excursions, and a saviour while waiting for the "insta"-people during the trips. Christina is a great, full of joy company, a source of countless what-if questions, and a tzatziki without tzatziki aficionado. Viktor is always eager to assist and a reliable source of information for all things, from approximate query processing to useful tips and tricks for life in Switzerland. Panayiotis has been of tremendous help settling in and feeling integrated in the first years. Anna and Stelios are a great company and I really enjoy our trips together – I am also deeply thankful to them for making me feel comfortable both in Cyprus and Chios. Thank you all for a great time!

I am grateful to *Georgia* for her love and support. Georgia is a highly motivated and persistent person. Not only has she endured multiple of my deadlines, but she has also been a continuous source of joy, relaxation, and many great excursions – a perfect escape from the Ph.D. hassles. Georgia's encouragement and faith in me have been a great motivation: trying to reach even close to these standards made me improve tremendously. I am deeply thankful to Georgia and look forward to all our future endeavors!

Last but not least, I would like to thank my parents, *Nikos* and *Polina*, for their great support, for taking care of me, and for providing me with two stellar examples to follow. I am deeply thankful for all their support, for teaching me how to be who I am today, and for encouraging me to push my limits. Thank you for everything!

This research has been supported by grants from the School of Computer and Communication Sciences, EPFL, the Swiss National Science Foundation, project No. 200021\_178894/1, "Efficient Real-time Analytics on General-Purpose GPUs", the European Union Seventh Framework Programme (ERC-2013-CoG), under grant agreement no 617508 (ViDa), the H2020 – UE Framework Programme for Research & Innovation (2014-2020), 2017 – ERC2017-PoC, grant agreement number 768910, ViDaR, and the European Union's Horizon 2020-ICT-2018-2020, SmartDataLake, project 825041.

Lausanne, July 29, 2022

P.C.

## **Abstract**

Timely insights lead to business growth and scientific breakthroughs but require analytical engines that cope with the ever-increasing data processing needs. Analytical engines relied on rapid CPU improvements, yet the end of Dennard scaling stopped the free lunch and resulted in a *heterogeneous hardware* landscape that challenges existing analytical engines. First, each device has its own specialized execution model and architecture, impeding interoperability. Second, the diversity in device microarchitectures requires a diverse range of optimizations. Third, while the multitude of devices provides additional acceleration opportunities, moving the data across devices is costly. Finally, with networking bandwidths similar to intra-server device connections, the server boundaries are blurred, providing optimization opportunities and requiring careful orchestration to avoid wasting resources.

In this thesis, we aim for engines tailored for heterogeneous hardware: abstracting out hardware heterogeneity to enable efficient execution across the devices despite their diversity. To this end, we design and implement techniques that are i) scalable through accelerator-level parallelism, and ii) efficient through query execution customization to the underlying accelerators and data transfer paths.

Regarding scalability, we propose a unifying execution model and a throughput-oriented system view to enable on-the-fly multi-device orchestration without requiring knowledge about hardware specifics. In addition, by decoupling data and control flow, this thesis enables late and direct data transfers within and across servers.

Regarding efficiency, we provide an execution model that limits operator instances to specific devices, enabling operators to customize themselves to a single device without concern for multi-device effects. In addition, by providing interconnect-aware transfer methods, this thesis minimizes the cost of offloading operations across devices.

This thesis redesigns analytical engines to exploit hardware heterogeneity. Instead of trading hardware efficiency for accelerator-level scalability, this thesis embraces heterogeneity. Our design enables scalable analytics across CPU-GPU hardware and achieves the analytical performance of optimally combining a CPU- and a GPU-optimized engine. As a result, users benefit from faster insights without requiring large clusters of machines. The proposed

#### Abstract

accelerator-centric design paves the way toward analytical engines that benefit from hardware improvements across the hardware spectrum – instead of relying on single-processor advancements.

**Keywords:** database management systems, analytical query processing, execution engine, code generation, heterogeneous hardware, accelerator-level parallelism, parallel execution, accelerators, GPU, RDMA

## Résumé

Des informations opportunes mènent au développement commercial et aux avancées scientifiques, mais nécessitent des moteurs d'analyse capables de gérer les besoins de traitement des données toujours plus nombreuses. Les moteurs analytiques se basaient sur des améliorations rapides du processeur (CPU), pourtant la fin de la mise à échelle de Dennard a abouti à un environnement hétérogène du hardware qui défie les moteurs analytiques existants. Tout d'abord, chaque appareil a son propre modèle d'exécution et d'architecture spécialisées, entravant l'interopérabilité. Deuxièmement, la diversité des microarchitectures des appareils nécessite une gamme variée d'optimisations. Troisièmement, alors que la multitude d'appareils offre des opportunités d'accélération supplémentaire, le déplacement des données entre les appareils est coûteux. Enfin, avec des bandes passantes réseau similaires à des connexions intra-serveur des appareils, les limites du serveur sont floues, offrant des opportunités d'optimisation et nécessitant une orchestration minutieuse afin d'éviter le gaspillage des ressources.

L'objectif de cette thèse est l'adaptation des moteurs à l'hétérogénéité du hardware : abstraire l'hétérogénéité du hardware pour permettre une exécution efficace sur tous les appareils malgré leur diversité. A cette effet, nous concevons et mettons en œuvre des techniques qui sont : i) évolutives grâce au parallélisme au niveau de l'accélérateur, et ii) efficaces grâce à la personnalisation de l'exécution des requêtes sur les accélérateurs sous-jacents et les voies de transfert de données.

Concernant la scalabilité, nous proposons un modèle d'exécution unificateur et un vue système orientée rendement pour activer l'orchestration des nombreuses appareils à la volée sans nécessiter la connaissance des spécificités du hardware. De plus, en découplant les flux de données et de contrôle, cette thèse permet les transferts de données tardifs et directs au sein et entre les serveurs.

En ce qui concerne l'efficacité, nous fournissons un modèle d'exécution qui limite les instances de l'opérateur à des appareils spécifiques, permettant aux opérateurs de se personnaliser sur un seul appareil sans se préoccuper des effets multi-appareils. De plus, en fournissant des méthodes de transfert compatibles avec les interconnexions, cette thèse minimise le coût des opérations de déchargement entre les appareils.

#### Résumé

Cette thèse redéfinit les moteurs analytiques pour exploiter l'hétérogénéité du hardware. Au lieu d'échanger l'efficacité du hardware pour une scalabilité au niveau d'accélérateur, cette thèse embrasse l'hétérogénéité. Notre modèle permet des analyses évolutives sur le hardware CPU-GPU et atteint les performances analytiques d'une combinaison optimale d'un processeur et d'un moteur optimisé pour le GPU. En conséquence, les utilisateurs bénéficient d'informations plus rapides sans nécessiter de gros clusters de machines. Le modèle proposé centré sur les accélérateurs ouvre la voie à des moteurs analytiques qui bénéficient d'améliorations hardware sur l'ensemble du spectre hardware - au lieu de compter sur les avancées d'un seul processeur.

**Mots clés :** systèmes de gestion de base de données, traitement analytique des requêtes, moteur d'exécution, génération de code, l'hétérogénéité du matériel informatique, parallélisme au niveau de l'accélérateur, exécution parallèle, accélérateurs, GPU, RDMA

# **Contents**

| 1.2 Pitfalls of Hardware Heterogeneity .  1.3 Thesis Statement and Contributions .  1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP   1.3.2 Thesis Roadmap .  2 Background .  2.1 Heterogeneity in Modern Servers .  2.2 Parallel Query Execution on CPUs .  2.3 Parallel Query Execution on GPUs .  2.4 Hardware-conscious Operators .  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine .  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism .  4.1 The HetExchange Framework .  4.2 Control Flow Operators .  4.3 Data Flow Operators .  4.4 Evaluation .  4.4.1 Scalability .  4.4.2 Microbenchmarking .  4.5 Conclusion .  5 Intra-device: Just-In-Time Hardware-conscious Pipelines .  5.1 Inter-operator: Generating Heterogeneous Pipelines . | Ac | knov  | wledgements                                                                              | V   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|------------------------------------------------------------------------------------------|-----|

| List of Tables  1 Introduction 1.1 Motivation 1.2 Pitfalls of Hardware Heterogeneity 1.3 Thesis Statement and Contributions 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines         | Ał | stra  | ct (English/Français)                                                                    | ix  |

| 1 Introduction 1.1 Motivation 1.2 Pitfalls of Hardware Heterogeneity 1.3 Thesis Statement and Contributions 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                         | Li | st of | Figures                                                                                  | xvi |

| 1.1 Motivation 1.2 Pitfalls of Hardware Heterogeneity 1.3 Thesis Statement and Contributions 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                        | Li | st of | Tables                                                                                   | xix |

| 1.2 Pitfalls of Hardware Heterogeneity .  1.3 Thesis Statement and Contributions .  1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP   1.3.2 Thesis Roadmap .  2 Background .  2.1 Heterogeneity in Modern Servers .  2.2 Parallel Query Execution on CPUs .  2.3 Parallel Query Execution on GPUs .  2.4 Hardware-conscious Operators .  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine .  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism .  4.1 The HetExchange Framework .  4.2 Control Flow Operators .  4.3 Data Flow Operators .  4.4 Evaluation .  4.4.1 Scalability .  4.4.2 Microbenchmarking .  4.5 Conclusion .  5 Intra-device: Just-In-Time Hardware-conscious Pipelines .  5.1 Inter-operator: Generating Heterogeneous Pipelines . | 1  | Inti  | roduction                                                                                | 1   |

| 1.3 Thesis Statement and Contributions 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators 3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine 4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                |    | 1.1   | Motivation                                                                               | 2   |

| 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GP 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                     |    | 1.2   | Pitfalls of Hardware Heterogeneity                                                       | 3   |

| 1.3.2 Thesis Roadmap  2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                    |    | 1.3   | Thesis Statement and Contributions                                                       | 5   |

| 2 Background 2.1 Heterogeneity in Modern Servers 2.2 Parallel Query Execution on CPUs 2.3 Parallel Query Execution on GPUs 2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                          |    |       | $1.3.1  \hbox{The End Goal: Efficient and Scalable Analytics on CPU-GPU Hardware} \ \ .$ | 6   |

| 2.1 Heterogeneity in Modern Servers  2.2 Parallel Query Execution on CPUs  2.3 Parallel Query Execution on GPUs  2.4 Hardware-conscious Operators  3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism  4.1 The HetExchange Framework  4.2 Control Flow Operators  4.3 Data Flow Operators  4.4 Evaluation  4.4.1 Scalability  4.4.2 Microbenchmarking  4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines  5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                            |    |       | 1.3.2 Thesis Roadmap                                                                     | 7   |

| <ul> <li>2.2 Parallel Query Execution on CPUs</li> <li>2.3 Parallel Query Execution on GPUs</li> <li>2.4 Hardware-conscious Operators</li> <li>3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine</li> <li>4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism</li> <li>4.1 The HetExchange Framework</li> <li>4.2 Control Flow Operators</li> <li>4.3 Data Flow Operators</li> <li>4.4 Evaluation</li> <li>4.4.1 Scalability</li> <li>4.4.2 Microbenchmarking</li> <li>4.5 Conclusion</li> <li>5 Intra-device: Just-In-Time Hardware-conscious Pipelines</li> <li>5.1 Inter-operator: Generating Heterogeneous Pipelines</li> </ul>                                                                                                                                     | 2  | Bac   | ekground                                                                                 | 9   |

| <ul> <li>2.3 Parallel Query Execution on GPUs</li> <li>2.4 Hardware-conscious Operators</li> <li>3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine</li> <li>4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism</li> <li>4.1 The HetExchange Framework</li> <li>4.2 Control Flow Operators</li> <li>4.3 Data Flow Operators</li> <li>4.4 Evaluation</li> <li>4.4.1 Scalability</li> <li>4.4.2 Microbenchmarking</li> <li>4.5 Conclusion</li> <li>5 Intra-device: Just-In-Time Hardware-conscious Pipelines</li> <li>5.1 Inter-operator: Generating Heterogeneous Pipelines</li> </ul>                                                                                                                                                                                   |    | 2.1   | Heterogeneity in Modern Servers                                                          | g   |

| <ul> <li>2.4 Hardware-conscious Operators</li> <li>3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine</li> <li>4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism</li> <li>4.1 The HetExchange Framework</li> <li>4.2 Control Flow Operators</li> <li>4.3 Data Flow Operators</li> <li>4.4 Evaluation</li> <li>4.4.1 Scalability</li> <li>4.4.2 Microbenchmarking</li> <li>4.5 Conclusion</li> <li>5 Intra-device: Just-In-Time Hardware-conscious Pipelines</li> <li>5.1 Inter-operator: Generating Heterogeneous Pipelines</li> </ul>                                                                                                                                                                                                                                 |    | 2.2   | Parallel Query Execution on CPUs                                                         | 10  |

| 3 Overview: Design Space of a Hybrid CPU-GPU Execution Engine  4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                       |    | 2.3   | Parallel Query Execution on GPUs                                                         | 11  |

| 4 Inter-device: Encapsulating Heterogeneous CPU-GPU Parallelism 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 2.4   | Hardware-conscious Operators                                                             | 13  |

| 4.1 The HetExchange Framework 4.2 Control Flow Operators 4.3 Data Flow Operators 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3  | Ove   | erview: Design Space of a Hybrid CPU-GPU Execution Engine                                | 15  |

| 4.2 Control Flow Operators  4.3 Data Flow Operators  4.4 Evaluation  4.4.1 Scalability  4.4.2 Microbenchmarking  4.5 Conclusion  5 Intra-device: Just-In-Time Hardware-conscious Pipelines  5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  | Inte  | er-device: Encapsulating Heterogeneous CPU-GPU Parallelism                               | 19  |

| 4.3 Data Flow Operators  4.4 Evaluation  4.4.1 Scalability  4.4.2 Microbenchmarking  4.5 Conclusion  Intra-device: Just-In-Time Hardware-conscious Pipelines  5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 4.1   | The HetExchange Framework                                                                | 20  |

| 4.4 Evaluation 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 4.2   | Control Flow Operators                                                                   | 21  |

| 4.4.1 Scalability 4.4.2 Microbenchmarking 4.5 Conclusion  Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 4.3   | Data Flow Operators                                                                      | 24  |

| 4.4.2 Microbenchmarking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 4.4   | Evaluation                                                                               | 26  |

| <ul> <li>4.5 Conclusion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | 4.4.1 Scalability                                                                        | 29  |

| 5 Intra-device: Just-In-Time Hardware-conscious Pipelines 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                                                                          | 29  |

| 5.1 Inter-operator: Generating Heterogeneous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 4.5   | Conclusion                                                                               | 32  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  | Inti  | ra-device: Just-In-Time Hardware-conscious Pipelines                                     | 33  |

| 5.1.1 Controlling Parallelism and Affinity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 5.1   | Inter-operator: Generating Heterogeneous Pipelines                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |       | 5.1.1 Controlling Parallelism and Affinity                                               | 39  |

xiii

#### **Contents**

|   |       | 5.1.2 Memory Management and Data Transfers                           | 40 |

|---|-------|----------------------------------------------------------------------|----|

|   | 5.2   | Intra-operator: Operator Portability                                 | 40 |

|   | 5.3   | System                                                               | 41 |

|   | 5.4   | Evaluation                                                           | 42 |

|   | 5.5   | Conclusion                                                           | 44 |

| 6 | Effic | cient Interconnect Utilization                                       | 47 |

|   | 6.1   | The Role of the Interconnect in CPU-GPU Analytics                    | 48 |

|   | 6.2   | Laconic: Minimizing Data Transfers for CPU-GPU Analytics             | 51 |

|   | 6.3   | Fine-granularity Accesses Without Regret                             | 52 |

|   | 6.4   | Modeling Pull-based Accesses                                         | 53 |

|   | 6.5   | Heterogeneity to Overcome the Curse of the First Column              | 55 |

|   | 6.6   | Pushing The Overfetch Away                                           | 56 |

|   | 6.7   | Evaluation                                                           | 57 |

|   |       | 6.7.1 Pull-based Data Accesses                                       | 58 |

|   |       | 6.7.2 Cooperative Data Accesses                                      | 60 |

|   | 6.8   | Conclusion                                                           | 62 |

| 7 | Inte  | r-server: Rack-Scale Analytics through Accelerator-Level Parallelism | 63 |

|   | 7.1   | Scalability of CPU-GPU Analytics                                     | 65 |

|   | 7.2   | RuSH: Rack-Scale Hybrid Analytics                                    | 66 |

|   | 7.3   | GPUs and RDMA in Modern Racks                                        | 67 |

|   |       | 7.3.1 Performance Bottlenecks in Analytics                           | 67 |

|   |       | 7.3.2 Optimizing for the Performance Bottlenecks                     | 68 |

|   | 7.4   | Coordination in CPU-GPU Racks                                        | 69 |

|   | 7.5   | Composable CPU-GPU Orchestation                                      | 71 |

|   |       | 7.5.1 Dataflow for Heterogeneous Processing                          | 71 |

|   |       | 7.5.2 Delayed Data Transfers                                         | 73 |

|   |       | 7.5.3 Buffer Allocations and Message Directionality                  | 76 |

|   | 7.6   | Inter-server Infrastructure                                          | 78 |

|   | 7.7   | System                                                               | 79 |

|   | 7.8   | Evaluation                                                           | 80 |

|   |       | 7.8.1 Evaluating the CPUs-GPUs-NICs Interplay                        | 81 |

|   |       | 7.8.2 Data Shuffling and Saturating the Network                      | 83 |

|   |       | 7.8.3 Locality-aware Rack-scale Execution                            | 85 |

|   |       | 7.8.4 Impact of Different Features                                   | 86 |

|   |       | 7.8.5 Adaptivity and Scalability                                     | 88 |

|   | 7.9   | Related Work                                                         | 89 |

|   | 7.10  | Conclusion                                                           | 91 |

| 8 | Con   | clusion and Outlook                                                  | 93 |

|   | 8.1   | Heterogeneous Hardware: Efficient and Scalable Analytics             | 94 |

|   | 8 2   | Looking Ahead: Heterogeneous Hardware heyond Analytics               | Q. |

|                  | Contents |

|------------------|----------|

|                  |          |

| Bibliography     | 97       |

| Curriculum Vitae | 111      |

# **List of Figures**

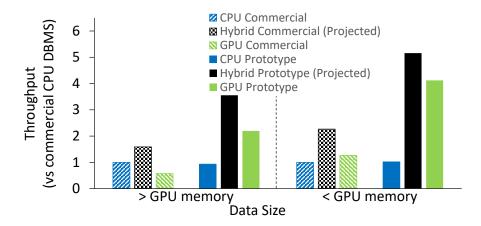

| 1.1 | Relative throughput of different systems and the unrealized potential of hybrid CPU-GPU engines. The reported throughputs are normalized, per data size, over |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | the corresponding throughput of the CPU commercial DBMS                                                                                                       | 2  |

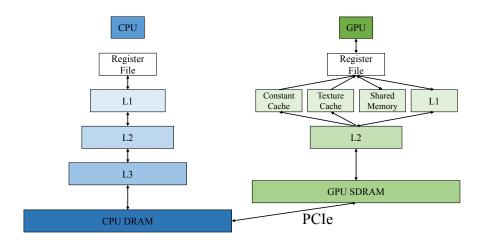

| 2.1 | CPU and GPU data cache hierarchy                                                                                                                              | 14 |

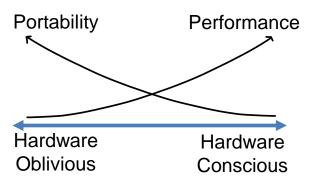

| 3.1 | Conceptual trade-off between portability and performance                                                                                                      | 15 |

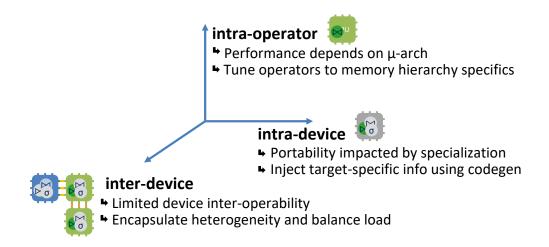

| 3.2 | Design axes for CPU-GPU OLAP engines                                                                                                                          | 16 |

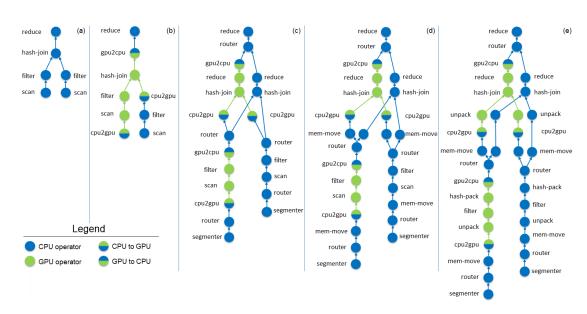

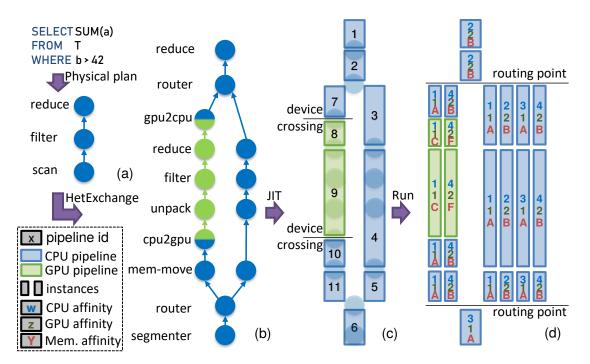

| 4.1 | Step by step introduction of HetExchange operators                                                                                                            | 21 |

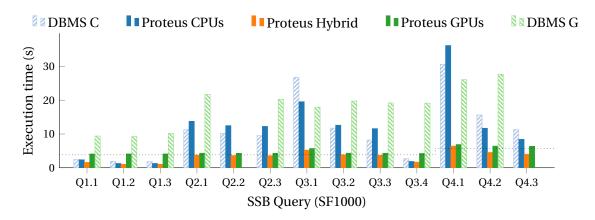

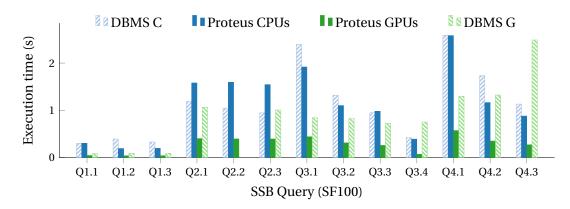

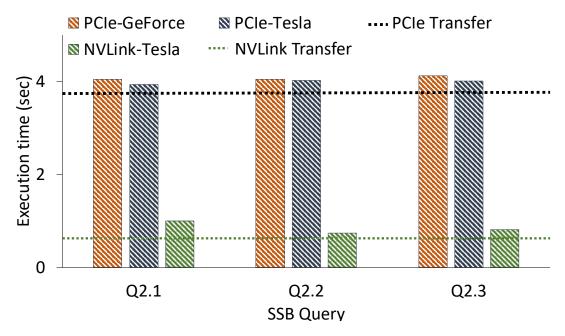

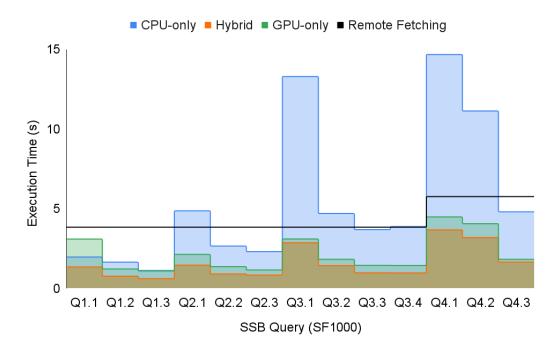

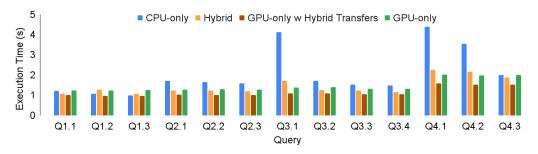

| 4.2 | SSB with non-GPU-fitting working sets that are pre-loaded in CPU memory for all systems.                                                                      | 27 |

| 4.3 | Scalability of Proteus on SSB SF=1000                                                                                                                         | 28 |

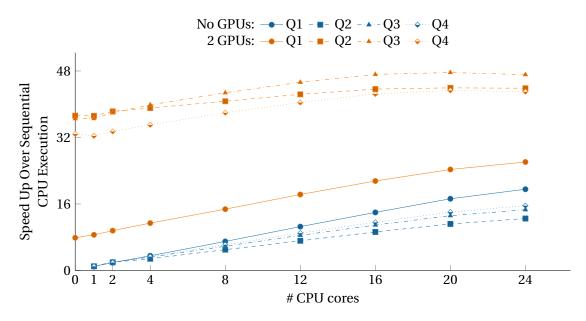

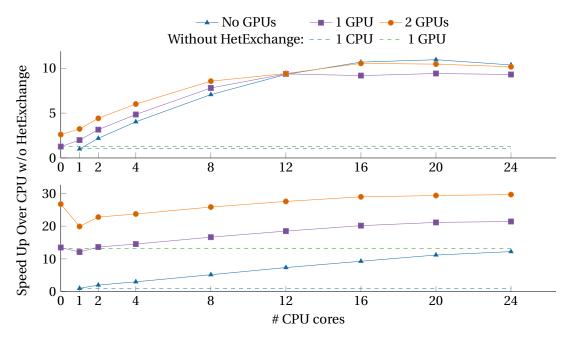

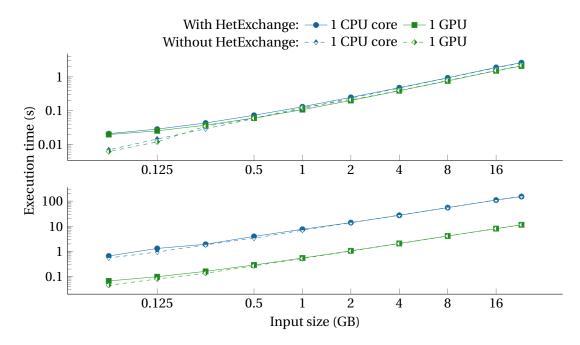

| 4.4 | Proteus scalability. Top: sum, Bottom: join                                                                                                                   | 30 |

| 4.5 | HetExchange for DOP=1. Top: sum, Bottom: join                                                                                                                 | 31 |

| 5.1 | Pipelines and affinities of a hybrid plan                                                                                                                     | 34 |

| 5.2 | Providers specialize code to the target device type                                                                                                           | 38 |

| 5.3 | SSB with GPU-fitting working sets. Data in GPU memory for GPU systems                                                                                         | 43 |

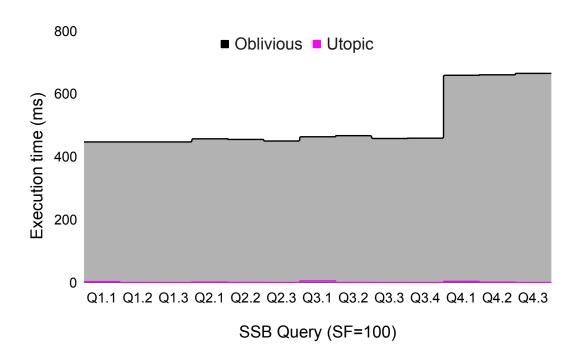

| 6.1 | In-GPU query execution using an eager (Oblivious) data transfer method, versus                                                                                |    |

| 6.2 | transferring only the qualifying tuples                                                                                                                       | 49 |

|     | architectures & interconnects                                                                                                                                 | 50 |

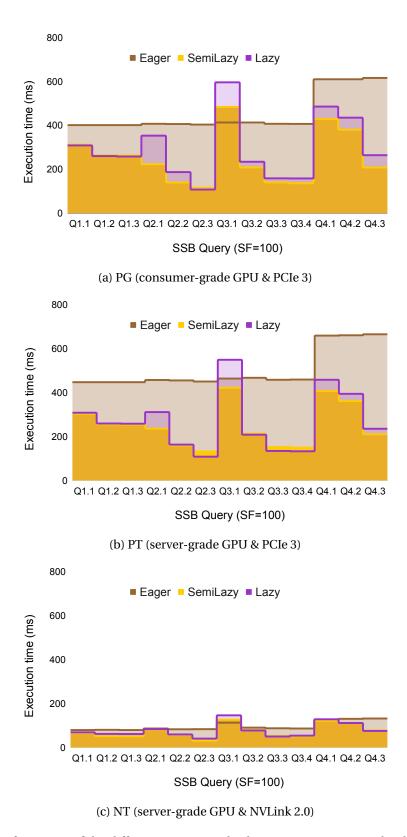

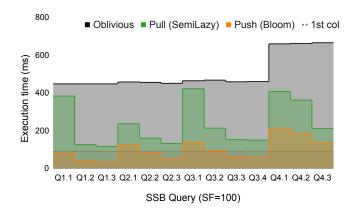

| 6.3 | Performance of the different access methods on SSB (SF=100) on the three                                                                                      |    |

|     | different configurations                                                                                                                                      | 59 |

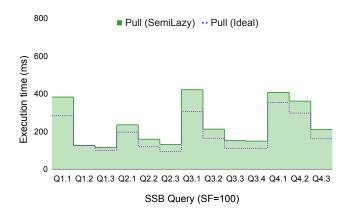

| 6.4 | Comparison of SemiLazy to the interconnect modeling ("ideal")                                                                                                 | 61 |

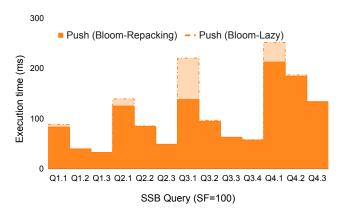

| 6.5 | Bloom filter push-down with and without repacking                                                                                                             | 61 |

| 6.6 | Push- vs Pull-based data accesses on SSB SF=100                                                                                                               | 62 |

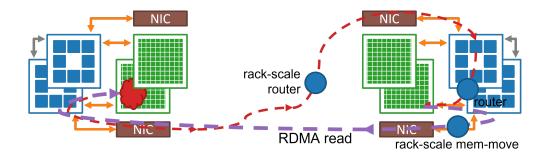

| 7.1 | The operators orchestrating execution of two servers. Cloud: a data chunk                                                                                     |    |

|     | generated on one of the GPUs. Red & purple arrows: a control message and a                                                                                    |    |

|     | data fetch.                                                                                                                                                   | 73 |

| 7.2 | Execution time vs network bandwidth                                                                                                                           | 81 |

#### **List of Figures**

| 7.3 | Bandwidths for various data placements and execution models, assuming PCIe             |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | 3 x16 and InfiniBand EDR 4x                                                            | 82 |

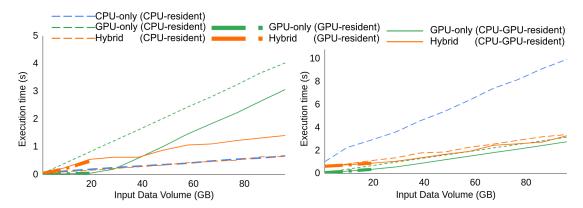

| 7.4 | Various execution methods and placements: i) an aggregation across 4 columns           |    |

|     | (left), ii) a 3-join query (right)                                                     | 83 |

| 7.5 | SSB (SF1000) with forced fact table shuffling to introduce network pressure. $$ . $$ . | 84 |

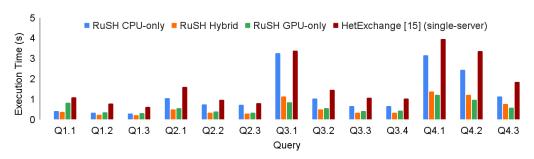

| 7.6 | SSB (SF1000) with CPU-resident data                                                    | 86 |

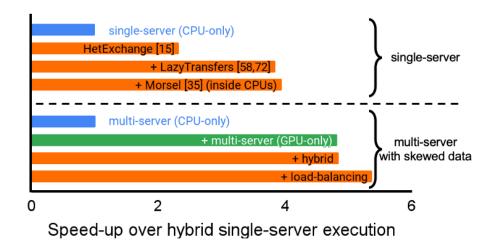

| 7.7 | Breakdown of the impact of different features                                          | 87 |

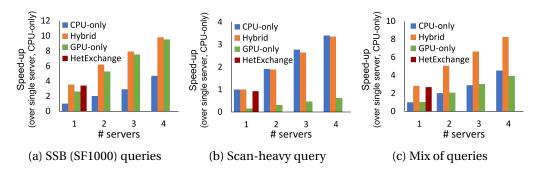

| 7.8 | Scalability on various workloads                                                       | 89 |

# **List of Tables**

| 4.1 | Execution traits in a heterogeneous server           | 20 |

|-----|------------------------------------------------------|----|

| 5.1 | Functions overloaded in device providers, per device | 35 |

## 1 Introduction

The demand for real-time intelligence increases as businesses from a wide range of domains increasingly require interactive data analytics to make insightful decisions in fast-breaking situations. As the amount of data accumulated by applications continues to grow faster than Moore's law, achieving real-time intelligence requires a computational infrastructure that can sift through billions of rows in milliseconds.

To optimize query execution, analytical query engine designs became hardware-conscious and specialized to the homogeneous multi-CPU architectures [6, 15, 47, 51, 60, 63, 78, 95]. State-of-the-art analytical engines use hardware-conscious algorithms [14, 78, 90, 92] that match the CPU microarchitecture. Techniques like *vector-at-a-time execution* [15] and *just-in-time code generation* [45, 46] reduce the query execution overheads, while the Exchange [30] operator and HyPer's Morsels [51] parallelize query execution in multi-core and multi-CPU configurations. Such parallelization techniques [30, 51] rely on the efficiency of CPU characteristics like cache coherence, efficient system-wide atomic operations, and shared memory.

Still, such approaches fall short in the new era of heterogeneous CPU-GPU hardware: The introduction of loosely coupled server architectures consisting of multiple accelerators, such as GPUs, breaks the traditional assumption of homogeneous CPU resources – bringing new challenges for hardware-efficient analytical processing. The heterogeneous devices come with a mix of shared and shared-nothing regions, even more acute NUMA effects, various programming models, and the closing bandwidth difference between intra- and inter-server interconnects breaks the traditional locality assumptions.

Figure 1.1 shows the throughput (working set size over time) of different systems when running all the SSB [71] queries<sup>1</sup>. We use two scale factors, SF=1000 for a working set that is bigger than the available GPU memory and SF=100 for a dataset that fits in the aggregated GPU memory. The performance of GPU-based DBMS highly depends on whether the data can fit in the GPU memory and the engine implementation. For example, the GPU commercial system is faster

<sup>&</sup>lt;sup>1</sup>Exact experimental setup in Section 4.4

Figure 1.1: Relative throughput of different systems and the unrealized potential of hybrid CPU-GPU engines. The reported throughputs are normalized, per data size, over the corresponding throughput of the CPU commercial DBMS.

than the CPU-based one when the data reside in the GPU memory. As a result, the preferred underlying devices depend on both the engine efficiency and the current system state, e.g., the data placement at query start time.

More importantly, CPU-only and GPU-only engines underutilize the hardware as they leave idle resources: the black bars represent the expected throughput of an ideal CPU-GPU integration. We observe that there is a 20%-80% throughput waste just due to idle resources.

To leverage the processing capabilities of such heterogeneous servers, the analytical query engine must 1) be flexible to *scale* across the diverse hardware resources and 2) *efficiently* use each of the underlying hardware devices, but without requiring manual optimization of the full stack for each target architecture. A key ingredient to achieving the aforementioned flexibility and efficiency is using accelerator-level parallelism [38] and customizable operators. For accelerator-level parallelism, multi-device execution must be decoupled from the internal device characteristics to enable arbitrary combinations of accelerators; for portable but efficient pipelines to be realized, the engine must abolish static hardware-dependent implementations in favor of dynamic pipeline specialization to the underlying hardware.

#### 1.1 Motivation

Existing analytical engine designs rely on specific, system-wide available features to achieve efficient execution on CPUs. As a result, 1) their design inherently fails to exploit the available accelerator-level parallelism, and 2) the fate of analytical performance improvements depends on continuous CPU improvements. This section discusses how these two artifacts generalize to the heterogeneous hardware case.

Specializing for a single type of processor, e.g., CPUs, seems the most straightforward approach for analytical engines, especially given the CPU ubiquity. However, this creates three main problems for analytical engines. First, there is up to 20%-80% performance penalty due to idle resources, as seen in Figure 1.1. Second, most of the recent hardware improvements are on specialized hardware, threatening a stagnation of the analytical engine performance, despite the continuous increase in data processing needs. Third, specialization to a single processing unit or feature relies on the survivability of a specific technology, risking invalidating today's specialization attempts if hardware vendors abandon this feature. In summary, analytical engines that rely on the features of a single processor risk underutilizing the available hardware resources, seeing limited performance improvements compared to the increased demand for analytics and observing technological lock-in.

Aiming for universal portability is the next straightforward alternative for analytical engines. In this case, the engine avoids specific hardware features and operates under minimal assumptions about hardware features. However, the pessimistic viewpoint toward hardware characteristics leaves significant performance unexploited. First, in contrast to CPU-only hardware-oblivious approaches, specialized hardware, like GPUs, imposes a higher penalty for deviating from its intended use or not considering its peculiarities. Second, such oblivious approaches have to rely on a minimal set of hardware characteristics: if, for example, one device does not support system-wide cache coherence or shared memory, then the entire engine has to operate without it, even if some of the available hardware devices support it. Third, the set of hardware characteristics supported by all the devices shrinks as the engine targets more types of processors. In summary, analytical engines that aim for universal portability observe diminishing returns as they have to abandon optimizations to support more accelerator types.

This thesis investigates the impact of hardware heterogeneity on analytical engines through the use case of GPU acceleration. GPUs provide an architectural platform that is relatively generic and ubiquitous but still has significant differences from the traditional CPU architectures. These differences range from microarchitectural and memory hierarchy differences to how they connect with the rest of the server processors, making it an ideal testbed. In the rest of this thesis, we use the terms device/accelerator interchangeably and to mean "either a CPU or a GPU", except if otherwise stated. This naming conversion aligns with our approach of treating heterogeneous devices equally for inter-device execution, independently of whether they are CPUs or GPUs.

## 1.2 Pitfalls of Hardware Heterogeneity

Databases are typically optimized for specific hardware – most commonly for the CPU – and make static assumptions about the system architecture, such as the existence of specific hardware features, the collocation of the fast memory tier with the processing units, and even the

meaning of data locality. However, the presence of heterogeneous hardware complicates the hardware behavior of modern servers, and existing static designs threaten to leave significant hardware resources underutilized.

Parallelization over heterogeneous CPU-GPU hardware. Modern server hardware is increasingly heterogeneous as hardware accelerators, such as GPUs, are used together with multicore CPUs to meet the computational demands of modern data-intensive workloads. Unfortunately, query parallelization techniques used by analytical database engines are designed for homogeneous multicore servers, where query plans are parallelized across CPUs to process data stored in cache-coherent shared memory. Thus, these techniques are unable to fully exploit accelerator-level parallelism available across heterogeneous devices, where one needs to combine the task-parallelism of CPUs and data-parallelism of GPUs for processing data stored in a deep, non-cache-coherent, disaggregated memory hierarchy with widely varying access latencies and bandwidth.

Hardware-consciousness across heterogeneous CPU-GPU hardware. Existing analytical engines are highly optimized for the CPU architecture to provide efficient and fast analytics: hardware-conscious operators use advanced CPU features, like vectorization, and are specialized for the CPU cache hierarchy and task-parallel architecture. However, GPUs come with a different programming model as well as different microarchitectural features. From their single instruction multiple threads execution model to the cache hierarchy, and their in-order instruction processing, GPUs fundamentally differ from CPUs in a variety of performance-critical features that are core to many hardware-conscious algorithms and state-of-the-art execution models. Furthermore, even hardware-oblivious analytical engine proposals rely on advanced CPU features absent in GPUs, such as data prefetching, big per-thread caches, and out-of-order execution. As a result, existing analytical engine solutions introduce a sharp tradeoff between portability and performance: either reoptimize and manually specialize the analytical engines for each device type or waste significant analytical performance relying on suboptimal but generic operations.

**Data access on heterogeneous CPU-GPU hardware.** The shared-memory, cache-coherent multi-socket CPU architecture has been a cornerstone for efficient analytics and their parallelization. However, diverse accelerators introduce additional processor boundaries. The devices are interconnected with a variety of special- or general-purpose interconnects. While these interconnects have seen significant bandwidth improvements over recent years, they are still orders of magnitude slower than accessing device-local memory, amplifying the NUMA effects. Furthermore, the device heterogeneity has, counterintuitively, changed a fundamental assumption on the importance of sending data over interconnects: traditionally, the processor homogeneity has provided 1) little reason for crossing slow interconnects without a functional need and 2) little processing gain, as the processor on the other side had similar capabilities. However, the advent of GPUs and their on-chip high-bandwidth memory (HBM) creates a different landscape: crossing a slow connection can provide significant analytical throughput

gains due to the processor on the other side. As a result, existing NUMA-aware solutions designed with the implicit assumption that crossing a slow connection should be avoided are now challenged by the new architecture that shifts the trade-off in a per-query case.

Disaggregation on heterogeneous CPU-GPU hardware. Current analytical engines scale out of a single machine as a necessity originating from limited single-server resources. Furthermore, scaling out has a performance penalty: whenever significant data-shuffling is required, the low network bandwidth and the relatively similar computational resources on the other side of the network highly penalize small-scale clusters compared to scale-up solutions. As a result, analytical engines face an uncanny valley where small numbers of machines could result in worse performance than scale-up alternatives. GPU-acceleration, however, combined with high-bandwidth networking solutions, fundamentally changes the prior assumptions about the networking overheads and the importance of data local computations as 1) the bandwidth of accessing remote data and processors is close to the intra-server bandwidth, and 2) significant analytical power is available remotely. However, existing designs for scale-out analytical engines fundamentally rely on servers as the unit of operation, providing poor scalability and load-balancing capabilities in the case of internally heterogeneous CPU-GPU servers.

#### 1.3 Thesis Statement and Contributions

Hardware heterogeneity significantly limits the efficiency and scalability of existing analytical engine solutions. Further, as hardware improvements shift from general-purpose advances to hardware specialization, existing analytical query processing techniques see reduced benefits. This thesis redesigns the analytical query execution engine so that execution across multiple, heterogeneous devices can be efficiently composed and orchestrated, with minimal effort for porting operator code across devices. The end goal is to enable efficient and scalable analytics by harnessing the available accelerator-level parallelism while maintaining the operator specification device-independent.

#### **Thesis Statement**

As hardware heterogeneity is increased, the trade-off between portability and performance of analytical query engines becomes more acute. Monolithic execution models are unable to fully exploit compute and memory devices. We can achieve both portability and performance by decoupling the execution model from device-specific characteristics while hiding the modularity and inter-connectivity overhead.

#### 1.3.1 The End Goal: Efficient and Scalable Analytics on CPU-GPU Hardware

Composability and orchestration of query execution on CPU-GPU hardware. While diverse hardware architectures bring new features into a hardware platform, they also (i) reduce the set of features supported by all the system processors and (ii) limit device interoperability. However, this clashes with existing parallelization techniques that rely on advanced CPU features, such as techniques that depend on efficient system-wide atomic operations, shared memory, or independent task execution. We present a parallelization framework that encapsulates hardware heterogeneity to enable efficient orchestration of the available CPU-GPU hardware resources while at the same time allowing subparts of the execution to use advanced processor-specific capabilities.

Portability and customization of query execution to underlying CPU-GPU hardware. We present a system design that bridges the gap between operator portability and operator efficiency. We leverage the hardware and pipeline boundaries to enable the analytical engine to customize execution pipelines for each targeted microarchitecture independently. Furthermore, we provide operator portability by delegating operator specialization to device-specific backends and leveraging code generation to erase this modularity cost. As a result, we provide an intra-device execution model tailored to each device while minimizing the necessary manual operator specialization.

**Data volume reduction and device cooperation on CPU-GPU hardware.** While the hardware heterogeneity provides an adaptive execution environment where the workload is distributed across the devices depending on the query requirements, the interconnectivity of such devices limits the actual performance improvements and offloading flexibility. We provide a solution that efficiently uses the available interconnects by combining the byte-addressability provided by inter-device interconnects and the pre-filtering capabilities of near-data processing power. As a result, we build analytical engines that operate on datasets well beyond the GPU-memory capacity, with efficient bandwidth utilization, despite such architectures' highly NUMA setup.

Scalability and hierarchical composability on disaggregated CPU-GPU hardware. Analytical engines rely on scaling out to overcome single-server deployments' limited memory capacity and analytical throughput. But, GPU acceleration challenges existing CPU scale-out solutions. Specifically, scalable analytics on CPU-GPU clusters require efficient coordination and direct point-to-point data transfers to exploit the disaggregated hardware. However, the server boundaries introduced by shared-nothing multi-server architectures conflict with the coordination and direct transfer requirements of such intra-server asymmetric architectures. We introduce a hierarchically scalable analytical engine design that reconciles distributed analytics with hardware accelerators by decomposing the orchestration decisions into a multi-step, throughput-optimized process. Lastly, we show how this architecture repurposes CPUs into a near-data processor in the presence of GPUs and high-bandwidth, RDMA-enabled NICs.

#### 1.3.2 Thesis Roadmap

The rest of the thesis is organized as follows:

- Chapter 2 introduces the necessary background.

- Chapter 3 proposes a decomposition of the analytical engine design space that drives the rest of the thesis.

- Chapter 4 proposes a parallelization framework that encapsulates the hardware heterogeneity to enable composable scale-up execution and CPU-GPU orchestration.

- Chapter 5 introduces an analytical engine design that optimizes intra-device query execution by providing portable, specialized operators coupled with an efficient intra-device execution model.

- Chapter 6 presents an optimization technique that reduces the inter-device data transfer volume. Specifically, it exploits byte-addressability and in-CPU pre-filtering opportunities to avoid wasteful transfer over the interconnect.

- Chapter 7 investigates the impact of shared-nothing architectures and high-bandwidth networking on GPU-accelerated analytics. Specifically, it shows how high-bandwidth networking distorts the traditional data locality definition and its effect on the role of CPUs and GPUs in data analytics. Then, it proposes a new analytical engine design that achieves scalable query execution and hierarchical composability by reconciling inter-server device orchestration.

- Chapter 8 concludes the thesis and presents future directions.

## 2 Background

In this chapter, we overview the typical hardware setup of today's heterogeneous compute servers and summarize related work on parallelizing query execution, hardware-conscious operators to set the context for our work.

#### 2.1 Heterogeneity in Modern Servers

Modern servers incorporate numerous accelerators – typically multiple GPUs, connected to each CPU socket via a PCIe, NVLink, or similar interconnect. Servers can also increase the number of available devices per socket using PCIe/NVLink switches. However, if the server relies on switches to connect multiple GPUs to a CPU socket, the per-switch GPUs have to share the PCIe bandwidth whenever they concurrently trigger PCIe traffic.

As a result, besides hardware heterogeneity, modern servers must cope with non-uniform memory access topologies. CPUs experience additional memory access latency when accessing the memory of another socket – a phenomenon dubbed NUMA (non-uniform memory access) [50]. Introducing GPUs exacerbates NUMA effects. When GPUs access CPU memory, they transfer data through the aforementioned interconnects, whose bandwidth is limited compared to CPU's local DRAM bandwidth (a few 100s of GBps) and to the bandwidth of a GPU's device memory (up to a few TBps). Specifically, a 16-lane PCIe 3.0 connection – typical for CPU-GPU connectivity – offers ~12.8GBps data bandwidth, while PCIe 4.0 used by more recent GPUs offer ~25GBps. IBM Power 8 and 9 CPUs support CPU-GPU communication through NVLink – an NVIDIA-specific interconnect that achieves up to 75 GBps CPU to GPU communication.

#### 2.2 Parallel Query Execution on CPUs

**Volcano and Exchange.** When a query reaches a database system, it is processed by a query planner / optimizer, resulting in an algebraic query execution plan. This plan, is generally expressed in the form of a tree, where each node is an operator, and it was traditionally interpreted using the Volcano iterator model [30]. Every operator of the plan exposes a general API, consisting of *open()*, *next()* and *close()* functions. When an operator's *next()* method is called, a request for a new tuple is sent to the operator's children.

The Exchange operator introduced in Volcano has been the standard approach for parallelizing a query plan. The Exchange operator encapsulates all three different types of parallelism (horizontal, vertical, and bushy) by exposing the same (iterator) interface as other operators in an interpreted query plan. Inserting an Exchange operator in a query plan splits it into two parts, with the sub-plan above the Exchange becoming the consumer and the sub-plan below being its producer. The Exchange operates as an asynchronous queue between the producer and the consumer. The producer inserts its results into the queue, while the consumer removes them and processes them. Both the producer and the consumer are not aware of the queue, and they interface with the Exchange operator in the same way as with any other operator. As both the producer and the consumer can execute in parallel on different processors. Exchange enables vertical parallelism. In addition, the Exchange controls the degree of parallelism of consumers and producers by spawning multiple instances of them and routing intermediary results between the different instances, introducing this way horizontal parallelism. Producers' results are either routed based on a policy to exactly one consumer or broadcasted to all of them. Lastly, introducing Exchange operators on both sides of a join creates bushy parallelism: each input of the join runs concurrently.

**JIT compilation and exposing parallelism.** Albeit Exchange makes it possible to parallelize sequential, single-threaded operator implementations without any code changes; it has certain drawbacks that limit its applicability as the mechanism of choice for parallelizing query execution in the modern in-memory data processing context. Interpreted query execution penalizes performance as the *next()* function is called for every tuple, resulting in frequent branch misprediction and poor code locality [46, 72].

State-of-the-art in-memory analytical engines avoid such interpretation overhead by eschewing interpreted execution in favor of JIT compilation [45, 46, 72]. JIT-based in-memory database engines split the query plan into non-blocking pipelines and use a compilation framework to translate a sequence of operators into straight-line code that loops over data one tuple at a time. Thus, these systems enable register-pipelining: a collection of non-blocking operators can be applied in one shot to a tuple stored in CPU registers. CPU-based JIT compilation techniques also do not use the traditional Exchange-based parallelism where operators, other than Exchange, are essentially sequential in nature. Instead, the typical approach, as exemplified by HyPer's morsel-driven parallelism [51], compiles and generates parallelization-

aware operators using atomic instructions in generated code for synchronizing access to shared data structures. Such code can then be executed in a task-parallel manner across multiple CPUs by using a thread pool.

**CPU parallelism in heterogeneous servers.** Unfortunately, the aforementioned approaches for parallelism can not be used in modern heterogeneous servers to parallelize queries across CPUs and GPUs. The traditional Exchange was not designed to work in heterogeneous parallel processing environments: pipelining across different processors requires Exchange's asynchronous queues of the operator to be placed such that they can be efficiently accessed by all processors. Morsel-based JIT-based Morsel parallelization requires system-wide, efficient cache coherence as it relies on atomic operations for synchronizing access to producer-consumer queues, or other shared data structures like joins' hash tables during the build phase. While these assumptions hold in homogeneous multicore CPU servers, in the general case, they are invalidated in heterogeneous servers with CPUs and GPUs due to a lack of global cache coherence.

Furthermore, unlike CPUs, executing an operator on the GPU requires moving the input data to GPU memory, launching a kernel to process the input, and potentially moving out the output data. As moving data is an expensive operation, it is important to move enough data so that the benefit gained from processing data on the GPU outweighs the data movement cost. Similarly, since kernel launches are expensive and slow, it is also important to minimize the number of kernel launches. Unlike a CPU-based JIT compiler, which has to generate executable code for just one processor, a GPU-based JIT compiler should generate both kernels that are executed on the GPU, and CPU code that invokes these GPU kernels. Thus, modern servers with heterogeneous CPU–GPU parallelism require rethinking traditional query execution and compilation strategies.

#### 2.3 Parallel Query Execution on GPUs

**Operator-at-a-time execution.** The inability of the commodity CPU to achieve unconditional scalability has led to numerous research and industrial efforts that utilize GPU co-processors for the acceleration of analytical database workloads [16, 35, 37, 44, 73, 76, 102]. Most GPU-powered DBMS operate as follows: The DBMS expresses the query plan as a sequence of (micro-)operators [16, 35, 37, 44, 102], and then translates each operator into a *kernel* – a data-parallel function. The DBMS then executes the kernels, one after the other, on a GPU, fully materializing intermediate results in order to provide them as input to the next kernel.

Initially, such "operator-at-a-time" GPU DBMS [16, 37] required every kernel to have its input available at operator invocation time, and thus complicated the overlap of (GPU) computation and (CPU-to-GPU) data transfer. Subsequent systems thus introduce the following optimizations. First, they overlap data transfer with computation to mask the data transfer cost as much as possible. For example, GPUDB [102] uses *Unified Virtual Addressing (UVA)*, an NVIDIA CUDA feature that allows a GPU to directly access memory of the CPU side, while

Rui and Tu [89] use CUDA memory copies and CUDA streams for a similar purpose. Stehle et al. [96] propose CPU-GPU co-processing to accelerate sorting tasks; their approach parallelizes the production of sorted runs and interleaves it with data transfers to and from the GPU. Sioulas et al. [94] propose a CPU-GPU co-processing radix join that uses the high CPU DRAM bandwidth to apply an initial partitioning before transferring the inputs to the GPU for the join. This partitioning step allows bigger-than-GPU-memory tables to be broken down to co-partitions that fit in GPU memory and thus perform the join with a single pass over the PCIe. Second, modern GPU DBMS have followed the MonetDB/X100 [15] paradigm to reduce materialization overheads [72] between GPU kernel invocations; every kernel operates over a subset (i.e., a vector) of the input and produces a vector as its output. Intermediate vectors fit in GPU memory for the next kernel to read, and the DBMS avoids unnecessary data transfers of intermediate results to the CPU. Still, result materialization - even when amortized using cache-resident vectors between kernel invocations – is wasteful in terms of memory bandwidth [27]; the GPU DBMS has to flush GPU registers and shared memory between kernel invocations, thus hurting locality. In addition, the vector-at-a-time paradigm requires multiple passes, further wasting (GPU) memory bandwidth.

**Pipelined GPU execution.** An alternative to vector-at-a-time processing is performing as much work as possible over data that already resides in GPU registers / shared memory. Such *pipelined* query execution typically reduces the number of kernels per query plan. GPL [73] pipelines operators by having each one of them running on a separate kernel and having the kernels communicate and transfer data through *OpenCL 2.0 pipes* [31]. HAWK [19] is a query compiler that generates OpenCL which can execute on a variety of parallel processors, such as CPUs and GPUs, but on only one of these platforms at a time. HorseCQ [27] departs from the use of data-parallel algorithms for operations such as reductions, and instead implements pipelined versions of said algorithms using GPU atomic instructions. Kernel Weaver [101] is a compiler that automatically tries to fuse multiple relational operations together into a single kernel, in order to i) reduce data movement and ii) enable additional compiler optimizations over the fused operators. Finally, MapD [2] ports the paradigm of CPU-based query compilation [63] in the context of GPU DBMS. MapD uses the LLVM compiler infrastructure to generate the code for its kernels just in time; the kernels contain code which is specialized for the current query, and try to minimize the amount of intermediate results per query.

**GPU** engines on heterogeneous servers. Most GPU-powered DBMS adopt one point in the design spectrum and make one or more of the following simplifying assumptions: First, they rely on the input dataset being GPU-resident or copartitioned to avoid the PCIe transfer overhead for input and intermediate data [2]. Second, they support query execution on a single GPU instead of multiple ones [35]. Third, their mechanisms for parallelizing queries are strictly GPU-tailored. This leaves a substantial amount of CPU-based processing capacity underutilized when used on heterogeneous servers, and misses out on potential co-processing opportunities where a query can be parallelized across CPUs and GPUs simultaneously. The few engines that support executing queries on both CPUs and GPUs [44] rely on wasteful full materialization. Finally, in HAPE [24] we envision specializing device-oblivious operators to

each device to achieve efficient, heterogeneity-aware execution, via code generation. HAPE assumes an abstraction that encapsulates inter-device execution and provides only an abstract system blueprint. In HetExchange we materialize these abstractions. We discuss both in the following sections.

#### 2.4 Hardware-conscious Operators