# In-Memory Hardware and Architectural Extensions for Workloads Acceleration

Présentée le 7 septembre 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire des systèmes embarqués Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### William Andrew SIMON

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury

Prof. D. Atienza Alonso, directeur de thèse

Prof. I. O'Connor, rapporteur

Dr A. Rahimi, rapporteur

Prof. A. Burg, rapporteur

# Acknowledgements

The last 4+ years have been some of the most exciting, formative, and challenging years of my life thus far. This is due in no small part to the people who I have had the honor to call my friends and colleagues, who have rejoiced with me in the highs and supported me in the lows. I am fully convinced that I could not have gotten to this point without their technical and/or emotional support. There is no way I can give everyone the proper recognition they deserve without this section being longer than the thesis proper, so I apologize in advance for my forgetfulness and generalizations; know that you are all appreciated and loved.

First of all, I would like to thank my jury members for graciously volunteering their time to read my thesis and provide valuable feedback. Specifically, I'd like to thank Prof. **Giovanni de Micheli**, who also supervised me during two Master's projects as well as attending my candidacy exam. I'd also like to thank Prof. **Andreas Burg**, who also attended my candidacy exam, and who has been a helpful colleague, both directly and indirectly through his excellent students in the Telecommunications Circuits Laboratory who I have had the good fortune of interacting with. Finally, I would like to thank Dr. **Abbas Rahimi** and Prof. **Ian O'Connor**, who don't know me from Adam but were more than happy to be external members of my jury.

Then, it is essential for me to thank Prof. **David Atienza**, without whom none of this would have been possible. Throughout my time here, I have seen him go above and beyond what is expected of any professor in terms

of supporting my work as well as the rest of the members of ESL. How he manages to maintain a real-time knowledge of the status of 30+ PhD students to the degree that he is able to make such meaningful contributions at our bi-weekly meetings is beyond me. Aside from his academic support, he also worked hard to build lab cohesion through many social events, including lab dinners, ski trips, paintball games, and races. A lab is only as good as its professor, and David has made ESL a fun and rewarding place to work. I can't thank him enough.

Of course, while David was more than happy to help out at any time, I didn't feel at liberty to pester him every time I ran into a problem. That role fell to my amazing post-doctoral advisors. First, Prof. Marina Zapater has been with me from the start, helping me to sharpen my initial visions into concrete actionable ideas. More than once she helped me through points when I felt like packing up my desk and being done. Next, it isn't an understatement to say that the expertise of Dr. Alexandre Levisse made this PhD possible. Alex joined the lab at the exact moment he was needed most, and without him this work would have looked very different and in all likelihood not nearly as successful. Finally, Dr. Giovanni Ansaloni, although late to the party (mine at least, he was in ESL years before me), has contributed immensely to the last year's work, effortlessly coming up with clever paper titles, extracting new insights from data, and contributing valuable proofreading feedback. These three people have been amazing mentors, but of course they aren't the only post-docs in the lab. I'd like to thank all of our mentors for their various contributions to our work; in particular, Drs. Miguel Peón, Adriana Valdes, Tomás Teijeiro, and Luis Costero have been good friends on this journey.

I'd also like to thank all of the members of ESL who made the time here so enjoyable. It's been so great being a part of such a diverse group of people who love to work hard and play hard. Thanks to **Elisabetta de Giovanni, Grégoire Surreal, Artem Andreev, and Renato Zanetti** for all the adventures around Switzerland. Thanks to **Marco Rios and Yasir Qureshi** for being hardworking colleagues, co-authors, and supportive friends. Thanks to **Homeira Salimi** for keeping all of our office related logistics in order and planning the various ESL activities. Thanks to **Rodolphe Buret, Mikäel Doche, and Christoph Müller** for keeping our servers running despite our best efforts to break them.

And finally, thanks to all the rest of the lab for the constant interesting lunch and coffee conversations, team building runs, and all-round general fantastic work environment.

Of course, work only represents half of my life here. Outside of the office I am indebted to so many people who have made my life in Switzerland a joy. I am forever indebted to the community of Westlake Church, among whom I count my oldest and closest friends in Switzerland. The countless evening and weekend events served to break up the sometimes monotony of work and refreshed my mind and soul. I would like to especially thank the **Slack** family, who adopted me during my time here and whose couch I slept on numerous times on lazy Sunday afternoons. I also want to thank Prof. **Thomas Rizzo** and his wife **Karen**, who have put much effort into connecting Christian academics on EPFL's campus through lunches and dinners. And of course, the young adults group contains too many names to mention. I started to list you, but really its impossible. I love you all so much.

Finally, a few special people I'd like to mention. None of this would have been possible without my incredibly supportive family, **Brad, Kelly, Jonathan, Brianna, and Kermit**, who I could always call upon for advice or just to talk about life. I owe them so much for pushing, encouraging, and supporting me in overcoming challenges both inside and outside of academia. Finally, I'd like to make a special thanks to **Una Pale** for being such an incredible person over the last year and some odd months. Thank-you so much for putting up with the sometimes tears and existential crises, as well as always being down for a weekend adventure or a cross country trip. Volim te bobice moja!

Lausanne, May 28, 2022

William Simon

## **Abstract**

TILIZATION of edge devices has exploded in the last decade, with such use cases as wearable devices, autonomous driving, and smart homes. As their ubiquity grows, so do expectations of their capabilities. Simultaneously, their form factor and use cases limit power availability. Thus, improving performance while limiting area and power consumption is paramount.

In this vein, in-Memory Computing (iMC) moves computation from the CPU into the memory hierarchy. This has multiple benefits. First, reduced data movement mitigates power consumption and latency. Second, the entire memory array can be utilized to perform hundreds of concurrent operations.

iMC has been proposed in various technologies, such as in SRAM, DRAM, and emerging Non-Volatile Memories (eNVRAMs). In particular, in-SRAM Computing (iSC) benefits from integration into existing products such as cache hierarchies, reducing area overhead and implementation complexity. Further, iSC operations are generally digital in nature, as opposed to analog, precluding the need for costly ADCs and improving application accuracy. Conversely, iSC accelerators face challenges in avoiding memory corruption, running at high frequencies, and kernel/application level integration.

This thesis exploits iSC while addressing the aforementioned challenges via a BitLine Accelerator for Devices on the Edge (BLADE). BLADE can be implemented in any SRAM system and utilizes local wordline groups to perform computations at a frequency 2.8x higher than state-of-the-art iSC architectures. BLADE is thoroughly simulated, fabricated, and benchmarked at the

transistor, architecture, and software abstraction levels. Experimental results demonstrate performance/energy gains over an equivalent NEON accelerated processor for a variety of edge device workloads, namely, cryptography (4x performance gain/6x energy reduction), video encoding (6x/2x), and convolutional neural networks (3x/1.5x), while maintaining the highest frequency/energy ratio (up to 2.2Ghz@1V) of any conventional iSC computing architecture, and a low area overhead of less than 8%.

With BLADE implemented, the possibilities for enhancement are manifold, with one such example being approximate computing. To this end, a CArryless Partial Product InExact Multiplier (CAPPIEM) halves multiplication latency while incurring negligible area overhead. As a standalone multiplier, CAPPIEM reduces the area/power-delay-product by 73/43%, respectively. Further, CAPPIEM has the unique property of computing exact results when one input is a Fibonacci encoded value. This property is exploited via a retraining strategy which quantizes neural network weights to Fibonacci values, ensuring exact computation during inference. Benchmarking on Squeezenet 1.0, DenseNet-121, and ResNet-18 demonstrate accuracy degradations of only 0.4/1.1/1.7%, while improving training time by up to 300x.

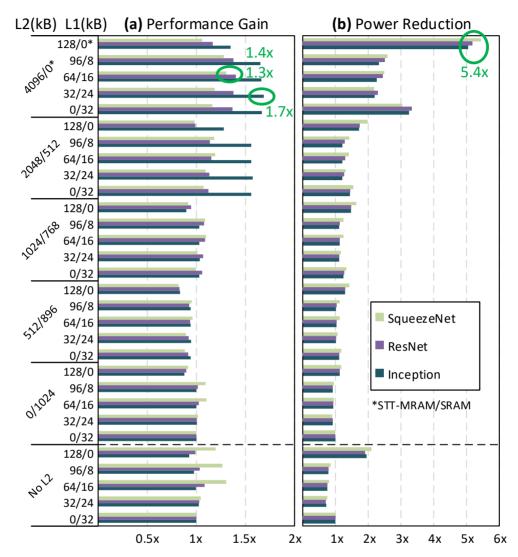

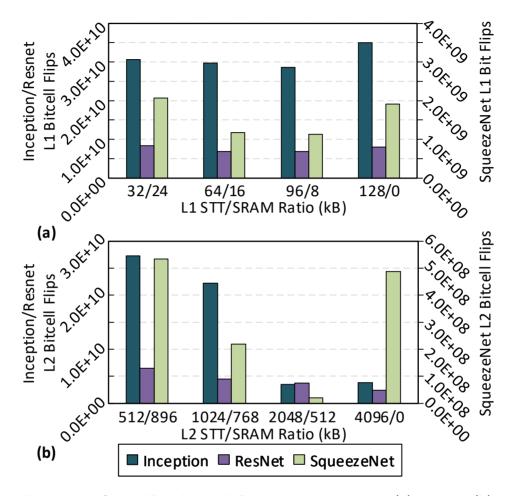

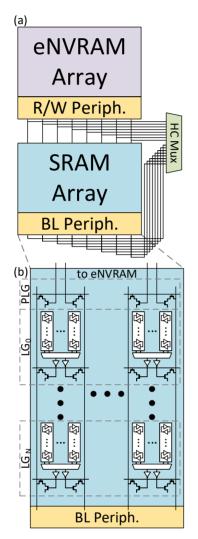

A second BLADE enhancement is the use of SRAM/eNVRAM Hybrid Caches (HCs). HCs increase capacity and power savings via eNVRAM's small area footprint and low leakage energy. However, eNVRAMs also incur long write latency and limited endurance. In this context, this thesis presents SHyCache, an HC architecture and supporting programming model. Variables with high read/write access ratios can be explicitly allocated to the eNVRAM array. This reduces access time, power consumption, and area overhead while maintaining maximal utilization efficiency and ease of programming. Benchmarks on a range of cache hierarchy variations using three deep neural networks demonstrate a design space that can be exploited to optimize performance, power consumption, or endurance, while demonstrating maximum performance and power gains of 1.7/1.4/1.3x and 5.1/5.2/5.4x, respectively.

**Keywords:** in-memory computing, in-cache computing, machine learning, artificial intelligence, neural networks, approximate computing, edge computing, edge AI, computing architectures, hybrid caches, SRAM memory, emerging non-volatile memories

## Résumé

L'UTILISATION des dispositifs périphériques a explosé au cours de la dernière décennie, avec des cas d'utilisation tels que les dispositifs portables, la conduite autonome et les maisons intelligentes. Leur omniprésence augmente, tout comme les attentes concernant leurs capacités. Simultanément, leur facteur de forme et leurs cas d'utilisation limitent la disponibilité de l'énergie. Il est donc primordial d'améliorer les performances tout en limitant la surface et la consommation d'énergie.

Dans cette optique, le calcul en mémoire déplace le calcul de l'unité centrale vers la hiérarchie de la mémoire. Cela présente de multiples avantages. Premièrement, la réduction des mouvements de données entre le CPU et la mémoire réduit la consommation d'énergie et la latence. Ensuite, la largeur totale de la mémoire peut être utilisée pour effectuer des opérations SIMD massives.

Le calcul en mémoire a été proposé dans diverses technologies, comme la SRAM, la DRAM et la eNVRAM. En particulier, le calcul en SRAM bénéficie de l'intégration dans des produits existants tels que les hiérarchies de cache, ce qui réduit la surcharge de surface et la complexité de mise en œuvre. En outre, les opérations in-SRAM sont généralement de nature numérique, par opposition à l'analogique, ce qui évite le recours à des convertisseurs analogiques-numériques coûteux et améliore la précision des applications. À l'inverse, les accélérateurs in-SRAM sont confrontés à des difficultés pour

éviter la corruption de la mémoire, pour fonctionner à des fréquences élevées et pour intégrer les niveaux noyau/application.

Cette thèse exploite le calcul in-SRAM tout en relevant les défis susmentionnés via BLADE. BLADE peut être implémenté dans n'importe quel système SRAM et utilise des groupes de lignes de mots locaux pour effectuer des calculs à une fréquence 2.8x plus élevée que les architectures de calcul in-SRAM les plus récentes. BLADE est soigneusement simulé, fabriqué et évalué aux niveaux du transistor, de l'architecture et de l'abstraction logicielle. Les résultats expérimentaux démontrent des gains de performance/énergie par rapport à un processeur accéléré NEON équivalent pour une variété de charges de travail de dispositifs périphériques, à savoir la cryptographie (gain de performance de 4 fois/6 fois la réduction d'énergie), le codage vidéo (6x/2x) et les réseaux neuronaux convolutifs (3x/1,5x), tout en maintenant le rapport fréquence/énergie le plus élevé (jusqu'à 2,2 GHz@1V) de toute architecture de calcul in-SRAM conventionnelle, et un faible surcoût de surface de moins de 8

Avec la mise en œuvre de BLADE, les possibilités d'amélioration sont multiples, l'un de ces exemples étant le calcul approximatif. À cette fin, CAPPIEM réduit de moitié la latence de la multiplication tout en introduisant un surcoût de surface négligeable. Lorsqu'il est mis en œuvre en tant que multiplicateur autonome, CAPPIEM réduit le produit surface/ puissance-retard de 73/43%, respectivement. En outre, CAPPIEM a la propriété unique de calculer des résultats exacts lorsqu'une entrée est une valeur codée Fibonacci. Cette propriété est exploitée par l'introduction d'une stratégie de réapprentissage qui quantifie les poids du réseau neuronal en valeurs codées Fibonacci, garantissant un calcul exact pendant l'inférence. L'évaluation comparative sur Squeezenet 1.0, DenseNet-121 et ResNet-18 montre une dégradation de la précision de seulement 0,4/1,1/1,7%, tout en améliorant le temps de formation jusqu'à 300 fois.

Une deuxième amélioration de BLADE est l'utilisation de caches hybrides composés de cellules binaires SRAM et eNVRAM. Les caches hybrides augmentent la capacité et les économies d'énergie grâce à la faible empreinte de la eNVRAM et à sa faible énergie de fuite. Toutefois, les eNVRAM présentent également une longue latence d'écriture et une endurance limitée. Pour at-

ténuer ces inconvénients, cette thèse présente SHyCache, une architecture de cache hybride et le modèle de programmation correspondant. SHyCache améliore les performances en allouant explicitement des variables avec des ratios élevés d'accès en lecture/écriture à la matrice eNVRAM, réduisant ainsi le temps d'accès, la consommation d'énergie et la surcharge de surface tout en maintenant une efficacité d'utilisation maximale et une facilité de programmation. Les tests de performance sur une gamme de variations de la hiérarchie de cache utilisant trois réseaux neuronaux, à savoir Inception v4, ResNet-50 et SqueezeNet 1.0, démontrent un espace de conception qui peut être exploité pour optimiser la performance, la consommation d'énergie ou l'endurance, tout en démontrant des gains de performance maximum de 1,7/1,4/1,3x et des réductions de consommation d'énergie de 5,1/5,2/5,4x.

**Mots-clés :** Calcul en mémoire, calcul en cache, apprentissage automatique, intelligence artificielle, réseaux neuronaux, calcul approximatif, caches hybrides, SRAM, mémoires non volatiles émergentes, architecture des processeurs, informatique en périphérie

# **Contents**

| Ac | knov  | wledge  | ments                                                  | i   |

|----|-------|---------|--------------------------------------------------------|-----|

| Ał | ostra | ct (Eng | dish/Français)                                         | v   |

| Li | st of | Figure  | s                                                      | xv  |

| Li | st of | Tables  |                                                        | xix |

| Ac | crony | ms      |                                                        | xxi |

| 1  | Intr  | oducti  | on                                                     | 1   |

|    | 1.1   | Edge    | Devices and the von Neumann Bottleneck                 | 2   |

|    |       | 1.1.1   | Where to compute: NMP vs. iMC                          | 3   |

|    |       |         | 1.1.1.1 Near Memory Processing (NMP)                   | 4   |

|    |       |         | 1.1.1.2 in-Memory Computing (iMC)                      | 4   |

|    |       | 1.1.2   | What to compute: Simple vs. Arithmetic Operations      | 6   |

|    |       | 1.1.3   | How to compute: iSC Architecture Challenges            | 7   |

|    | 1.2   | Thesi   | s Contribution                                         | 8   |

|    |       | 1.2.1   | BLADE: A BitLine Accelerator for Devices on the Edge . | 8   |

|    |       | 1.2.2   | CAPPIEM: in-Memory Approximate Computation             | 9   |

|    |       | 1.2.3   | SHyCache: A Hybrid Cache Framework for NN Accelera-    |     |

|    |       |         | tion                                                   | 9   |

| 2  | BLA   | ADE: A  | BitLine Accelerator for Devices on the Edge            | 11  |

|    | 2.1   | Motiv   | ration for BLADE Design Choices                        | 12  |

### **Contents**

|     | 2.1.1  | Accelerating via iMC                                    | 12 |

|-----|--------|---------------------------------------------------------|----|

|     | 2.1.2  | Implementing BLADE in the iSC Domain                    | 13 |

|     | 2.1.3  | Full-Stack Analysis Environment                         | 14 |

| 2.2 | Mitiga | ating Data Corruption while Operating at High Frequency | 16 |

|     | 2.2.1  | What are Local Bitlines?                                | 17 |

|     | 2.2.2  | BLADE Methods of Operation                              | 17 |

|     |        | 2.2.2.1 Standard Read/Write Operations                  | 18 |

|     |        | 2.2.2.2 Standard iSC Operations                         | 18 |

|     |        | 2.2.2.3 LBL Enhanced iSC Operations                     | 18 |

|     | 2.2.3  | LBL Enhanced iSC Cache Design Advantages                | 19 |

| 2.3 | Logic  | to Support Arithmetic Operations                        | 20 |

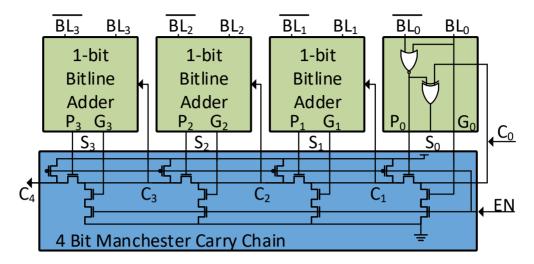

|     | 2.3.1  | Bitline Addition Architecture                           | 22 |

|     | 2.3.2  | Improving Operation Throughput                          | 25 |

|     |        | 2.3.2.1 Manchester Carry Chain (MCC)                    | 25 |

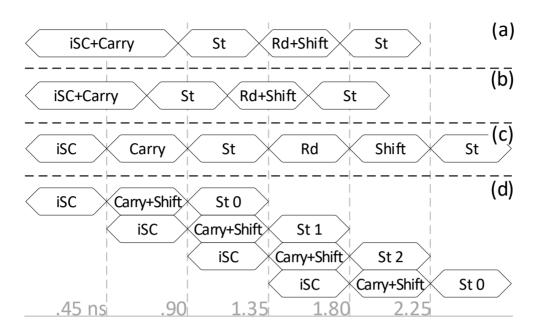

|     |        | 2.3.2.2 Arithmetic Operation Pipelining                 | 26 |

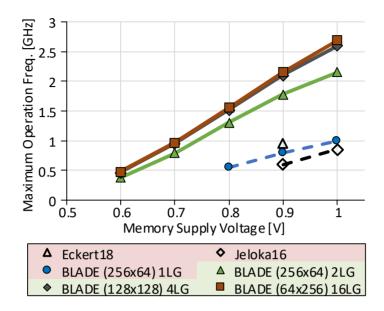

| 2.4 | Electr | ical Validation and Design Space Exploration            | 27 |

|     | 2.4.1  | Functional Validation of BLADE                          | 27 |

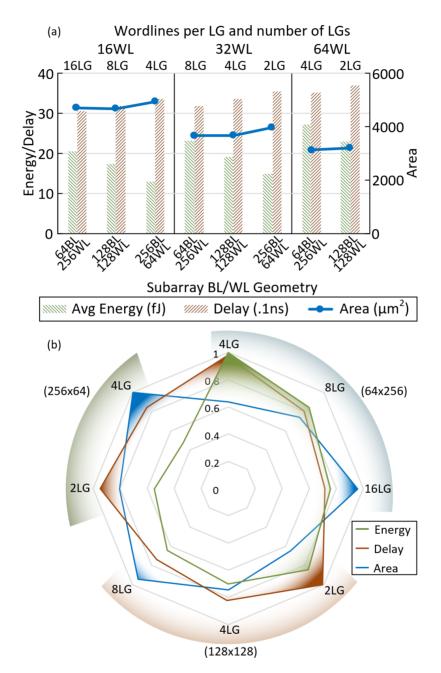

|     | 2.4.2  | Subarray Design Space Exploration                       | 29 |

| 2.5 | Syster | m-Level Integration and Functionality                   | 31 |

|     | 2.5.1  | Operand Locality Constraints                            | 34 |

|     | 2.5.2  | iSC Instruction Passing and ISA Support                 | 37 |

|     |        | 2.5.2.1 Memory-Mapped Implementation                    | 37 |

|     |        | 2.5.2.2 ISA Implementation                              | 38 |

|     | 2.5.3  | Issuing ISC Operations to Memory                        | 39 |

|     | 2.5.4  | Fetching and Allocating Operands                        | 39 |

|     | 2.5.5  | Integration in the gem5-X Architecture Simulator        | 39 |

| 2.6 | Syster | m-Level Benchmarking                                    | 40 |

|     | 2.6.1  | Edge Device Workloads                                   | 40 |

|     |        | 2.6.1.1 Cryptography                                    | 40 |

|     |        | 2.6.1.2 HEVC Video Processing                           | 41 |

|     |        | 2.6.1.3 Convolutional Neural Networks                   | 41 |

|     | 2.6.2  | gem5-X Parameters                                       | 41 |

|     | 2.6.3  | McPAT Support                                           | 42 |

| 2.7 |        | nmark Results                                           | 42 |

|     | 271    | Ritwise Operations/iSC Operation Count                  | 13 |

|   |     | 2.7.2   | FIR Filter/Cache Associativity                          | 44 |

|---|-----|---------|---------------------------------------------------------|----|

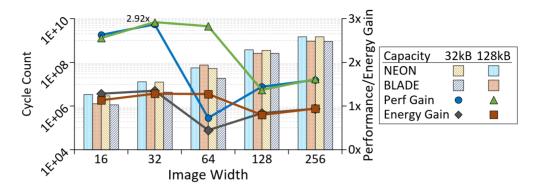

|   |     | 2.7.3   | Convolution/Cache Capacity                              | 45 |

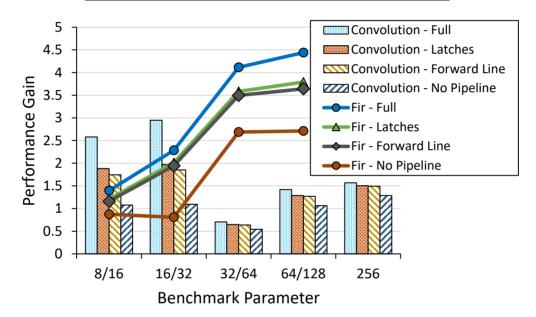

|   |     | 2.7.4   | Arithmetic Logic Optimization                           | 46 |

|   | 2.8 | Sumn    | nary and Concluding Remarks                             | 48 |

| 3 | Acc | elerati | ng iSC Operations via Approximate Computing             | 49 |

|   | 3.1 | CAPP    | IEM: A Carryless Partial Product Inexact Multiplier     | 52 |

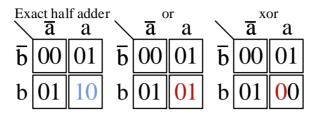

|   |     | 3.1.1   | Selection of Reduction Operator                         | 52 |

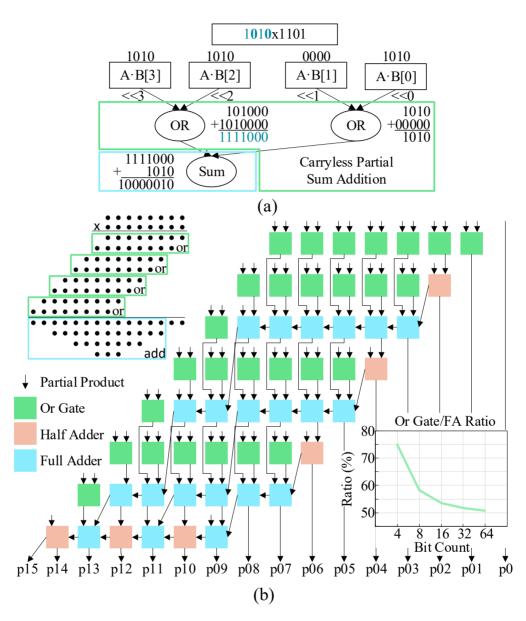

|   |     | 3.1.2   | CAPPIEM Hardware Implementation                         | 54 |

|   |     | 3.1.3   | Implementation of CAPPIEM in BLADE                      | 54 |

|   | 3.2 | Fibon   | acci Code Word Quantization for NNs                     | 57 |

|   |     | 3.2.1   | Motivation                                              | 57 |

|   |     | 3.2.2   | Countering Approximation Errors Via Fibonacci Code      |    |

|   |     |         | Word Quantization                                       | 57 |

|   |     | 3.2.3   | Quantization Parameters for Fibonacci Code Quantization | 58 |

|   | 3.3 | Impro   | oving Accuracy through Incremental Network Quantization | 60 |

|   |     | 3.3.1   | Incremental Quantization Strategies                     | 61 |

|   | 3.4 | Exper   | imental Setup                                           | 62 |

|   | 3.5 | Exper   | imental Results and Analysis                            | 63 |

|   |     | 3.5.1   | Hardware Synthesis and Analysis                         | 63 |

|   |     | 3.5.2   | Retraining Analysis                                     | 63 |

|   |     | 3.5.3   | Comparison to the State-of-the-Art                      | 66 |

|   | 3.6 | Concl   | usion                                                   | 68 |

| 4 | Imp | roving  | Capacity with Hybrid Caches                             | 69 |

|   | 4.1 | Relate  | ed Work                                                 | 72 |

|   |     | 4.1.1   | Resistive Random Access Memory                          | 72 |

|   |     | 4.1.2   | Hybrid Cache Design and Allocation Strategies           | 72 |

|   |     | 4.1.3   | Neural Networks                                         | 73 |

|   | 4.2 | Hybri   | d Cache Architectural Design                            | 73 |

|   | 4.3 | Integr  | rating SHyCache's Programming Model into Neural Net-    |    |

|   |     | work    | Frameworks                                              | 74 |

|   |     | 4.3.1   | Enabling HC allocation at the Operating System Level .  | 74 |

|   |     | 4.3.2   | Enabling HC allocation at the Application Level         | 75 |

|   |     | 4.3.3   | Co-Implementing SHyCache with Other HC Allocation       |    |

|   |     |         | Strategies                                              | 76 |

#### **Contents**

| Cı | ırricı | ulum V  | <sup>7</sup> itae                                   | 107 |

|----|--------|---------|-----------------------------------------------------|-----|

| Bi | bliog  | graphy  |                                                     | 95  |

|    | 5.4    | List of | f Publications                                      | 94  |

|    |        |         | and Architecture                                    | 92  |

|    |        | 5.3.4   | Further Refinement/Enhancement of BLADE Hardware    |     |

|    |        | 5.3.3   | BLADE Compiler Support                              | 92  |

|    |        | 5.3.2   | FPGA Implementation to Reduce Simulation Time       | 91  |

|    |        | 5.3.1   | Validation of BLADE Fabrication                     | 90  |

|    | 5.3    | -       | e Work                                              | 90  |

|    | 5.2    |         | ring Opportunities for Enhancing BLADE              | 89  |

| •  | 5.1    |         | E: A Base for Future iMC Exploration                | 87  |

| 5  | Con    | clusio  | n and Future Work                                   | 87  |

|    | 4.7    | Concl   | usion                                               | 85  |

|    |        | 4.6.2   | SHyCache/BLADE Operand Locality                     | 85  |

|    |        | 4.6.1   | Pseudo-Local Group Integration                      | 84  |

|    | 4.6    | Integr  | ation with BLADE                                    | 84  |

|    |        | 4.5.4   | Optimizing HCs for Performance, Power, or Endurance | 83  |

|    |        | 4.5.3   | Endurance Results                                   | 82  |

|    |        | 4.5.2   | Performance Results                                 | 80  |

|    |        | 4.5.1   | Power Results                                       | 79  |

|    | 4.5    |         | imental Results and HC Optimization Analysis        | 78  |

|    |        | 4.4.2   | Neural Network Benchmarks                           | 78  |

|    |        | 1.1.1   | Latency Simulation                                  | 77  |

|    | 1.1    | 4.4.1   | gem5-X Simulator Parameters and Hybrid Cache Access | 10  |

|    | 4.4    | Exper   | imental Setup                                       | 76  |

# **List of Figures**

| 1.1 | Devices connected to the internet. Embedded IoT devices have      |    |

|-----|-------------------------------------------------------------------|----|

|     | seen a 10x increase in the last decade                            | 2  |

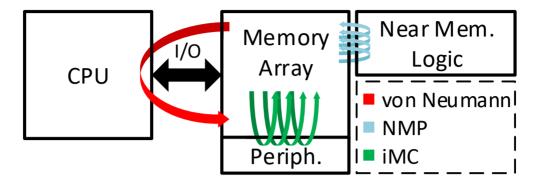

| 1.2 | The various computing paradigms. The von Neumann archi-           |    |

|     | tecture suffers from long access latency. Near Memory Pro-        |    |

|     | cessing (NMP) performs computation in tightly coupled logic       |    |

|     | near the memory array. in-Memory Computing (iMC) performs         |    |

|     | computation either directly in the memory or in the periphery     |    |

|     | immediately surrounding the array                                 | 3  |

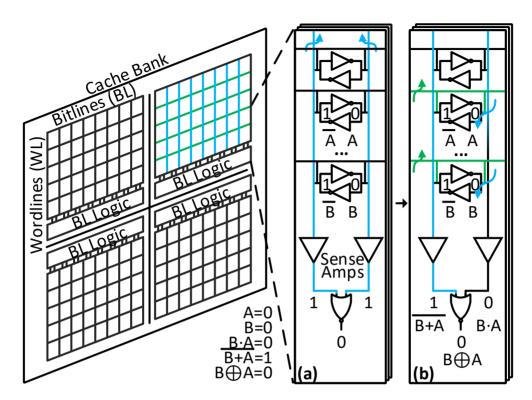

| 1.3 | Cache subarray with and/nor/xor bitline computing on val-         |    |

|     | ues A=0 and B=0. Bitwise operations are performed by first (a)    |    |

|     | precharging the bitlines, then (b) activating multiple wordlines, |    |

|     | thus discharging the bitlines through the connected bitcells      | 6  |

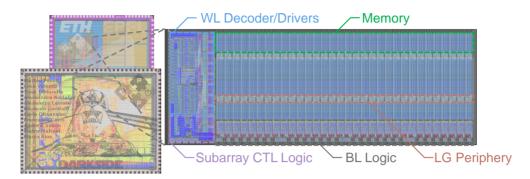

| 2.1 | BLADE fabricated on the Rosetta and Darkside chips in collabo-    |    |

|     | ration with the Integrated Systems Laboratory (IIS) at ETHZ       | 14 |

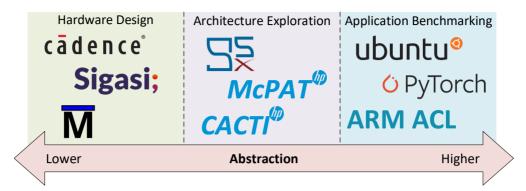

| 2.2 | A variety of applications are utilized throughout this thesis     |    |

|     | to implement and benchmark BLADE from the circuit level           |    |

|     | through the architecture and kernel up to the application level.  | 15 |

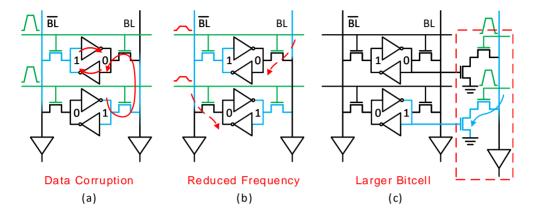

| 2.3 | (a) Bitcell shorting may cause one of the activated bitcells to   |    |

|     | flip. (b) avoids data corruption by lowering WL voltage, while    |    |

|     | (c) utilizes 8T bitcells to isolate bitcell contents              | 16 |

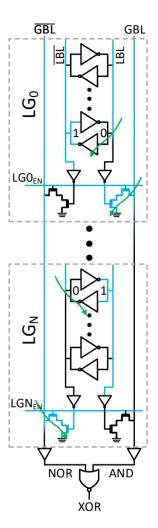

| 2.4 | LBL read ports prevent data corruption while performing iSC       |    |

|     | operations                                                        | 17 |

### **List of Figures**

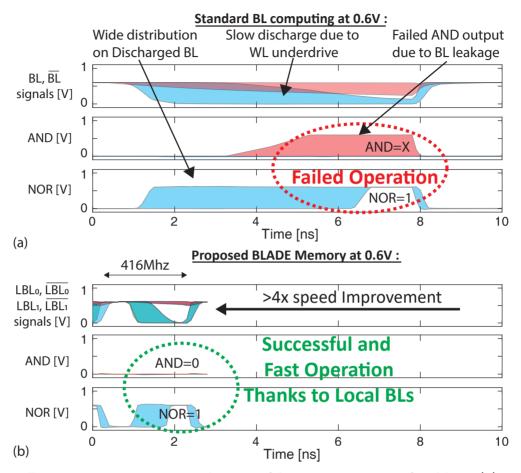

| 2.5  | Transient simulations of bitwise operations @0.6V on (a) previ-   |    |

|------|-------------------------------------------------------------------|----|

|      | ously published architectures, and (b) the BLADE architecture.    | 19 |

| 2.6  | Layout of a 256×2×32 BLADE memory with schematic diagram          |    |

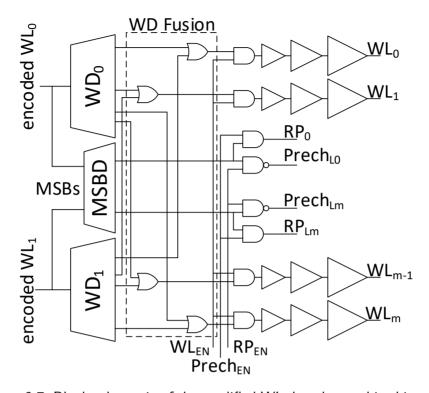

|      | of the BLADE periphery                                            | 21 |

| 2.7  | Block schematic of the modified WL decoder used in this work.     | 22 |

| 2.8  | 4-bit shift-and-add multiplication as performed by BLADE          | 24 |

| 2.9  | MCC architecture with reduced transistor count resulting from     |    |

|      | simplified Generate and Propagate signal generation               | 25 |

| 2.10 | Timing diagrams of multiplication with (a) no optimization, (b)   |    |

|      | MCC, (c) pipelining, and (d) add-forward line                     | 26 |

| 2.11 | Maximum frequency of bitwise operations vs. memory supply         |    |

|      | voltage at 28nm CMOS                                              | 28 |

| 2.12 | (a) Energy, area, and delay variations across cache geometries.   |    |

|      | (b) The normalized energy, area, and delay design space, with     |    |

|      | maximum values for each metric equal to 1                         | 30 |

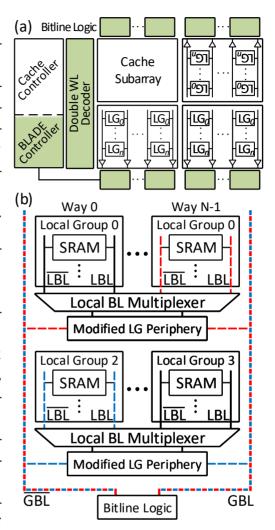

| 2.13 | a) BLADE implementation within the cache, represented by          |    |

|      | highlighted boxes. b) BLADE implementation under Local            |    |

|      | Group (LG) way multiplexers                                       | 32 |

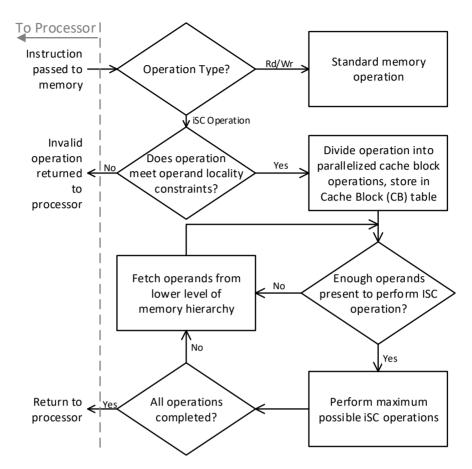

| 2.14 | Instruction flow in BLADE cache from time of issue by processor   |    |

|      | to operation completion                                           | 33 |

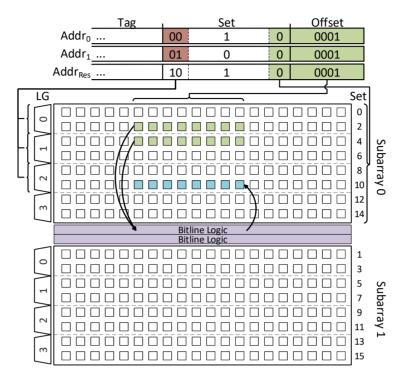

| 2.15 | The operands in sets 0 and 1 have matching offsets and set LSBs,  |    |

|      | and differing set MSBs. Hence, they share BL logic, but not LGs.  | 35 |

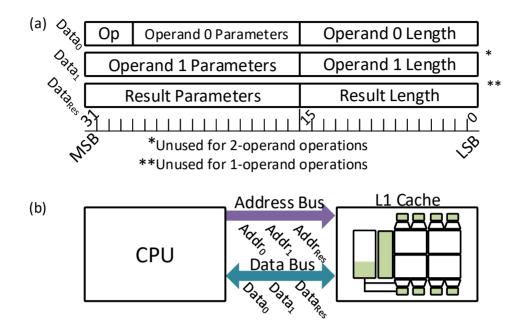

| 2.16 | a) iSC operand parameter format. b) Passing BLADE operands        |    |

|      | in ISA implementation mode utilizes both the address and data     |    |

|      | bus                                                               | 37 |

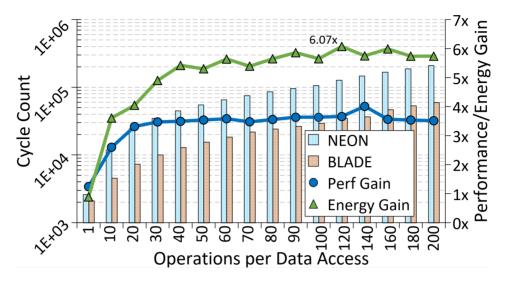

| 2.17 | NEON/BLADE runtime/energy results on bitwise operations           | 43 |

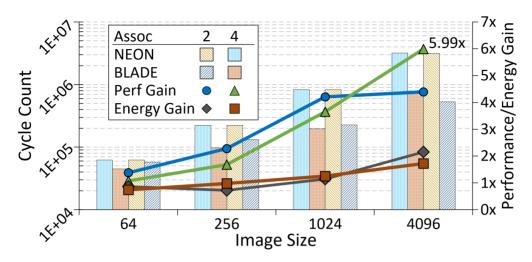

| 2.18 | Runtime/energy results for NEON/BLADE on FIR operations           | 44 |

| 2.19 | Runtime/energy results for NEON/BLADE on convolution op-          |    |

|      | erations                                                          | 45 |

| 2.20 | Performance trends for different levels of arithmetic pipelining. | 47 |

| 3.1  | Karnaugh maps for an exact half adder, as well as or and xor      |    |

|      | gates. While xor gates compute the sum value exactly in all       |    |

|      | instances, or gates provide the least error when the carry value  |    |

|      | is considered                                                     | 52 |

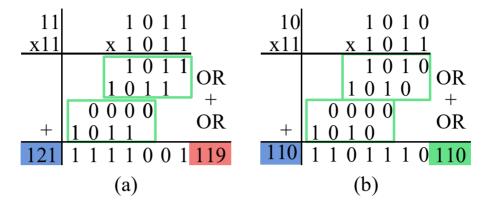

| 3.2  | (a) 4-bit multiplication with carryless partial product summa-     |    |

|------|--------------------------------------------------------------------|----|

|      | tion enabled by or gates. (b) 8x8 adder array with FA gates        |    |

|      | replaced by or gates to reduce area and power consumption.         |    |

|      | The ratio of replaced adders approaches a limit of 50% as bit      |    |

|      | width increases                                                    | 53 |

| 3.3  | 4-bit shift-and-add multiplication as performed by BLADE           | 54 |

| 3.4  | Embedded shift logic with CAPPIEM extension in green. Ex-          |    |

|      | tension performs an or operation between the current and           |    |

|      | previous bit of the operand                                        | 55 |

| 3.5  | Embedded shift logic with CAPPIEM extension in green. Ex-          |    |

|      | tension performs an or operation between the current and           |    |

|      | previous bit of the operand                                        | 56 |

| 3.6  | Naive carryless partial product multiplication will lead to er-    |    |

|      | rors and reduced accuracy (a). Such errors can be avoided by       |    |

|      | quantizing NN weights according to Fibonacci code words (b).       | 57 |

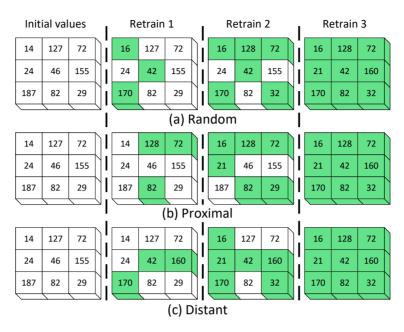

| 3.7  | Three incremental quantization strategies for Fibonacci incre-     |    |

|      | mental retraining; (a) Random, (b) Proximal, and (c) Distant. In   |    |

|      | each retraining step, a fraction of weight values are quantized    |    |

|      | to the nearest Fibonacci code word and frozen, represented by      |    |

|      | green boxes                                                        | 59 |

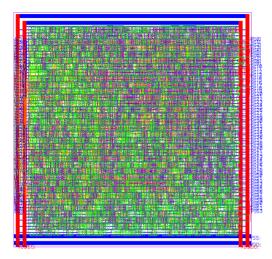

| 3.8  | Placed and routed 32 bit CAPPIEM in 28nm CMOS                      | 62 |

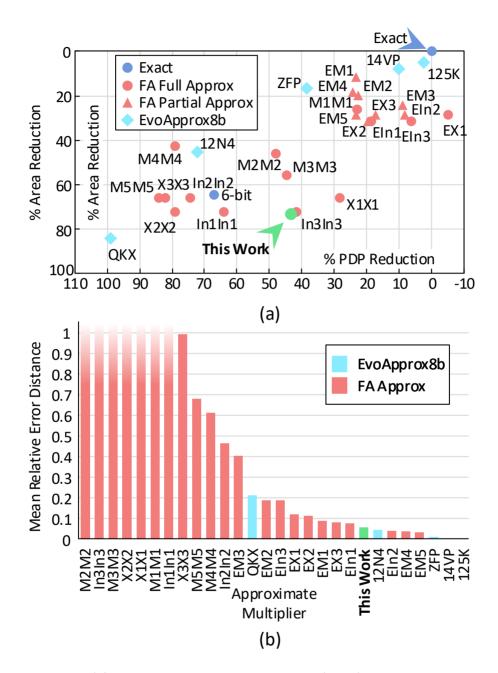

| 3.9  | (a) Area and Power-Delay-Product (PDP) reduction comparison        |    |

|      | between this work against other AMs for 8x8 multiplier archi-      |    |

|      | tectures. (b) Mean Relative Error Distance (MRED) of this work     |    |

|      | in comparison to other AMs. This work presents high area and       |    |

|      | PDP reductions in relation to its low MRED                         | 64 |

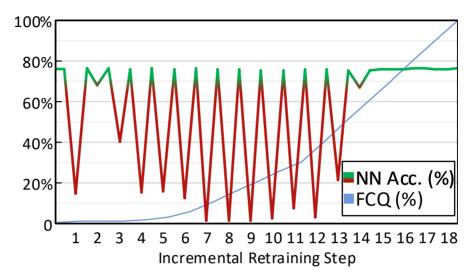

| 3.10 | DenseNet-121 accuracy during the quantization/retraining pro-      |    |

|      | cess utilizing the distant retraining strategy. Retraining enables |    |

|      | to recoup nearly all accuracy loss. Weights are quantized conser-  |    |

|      | vatively, as described in Section 3.3.1. The blue line represents  |    |

|      | the percentage of weights quantized at each step                   | 65 |

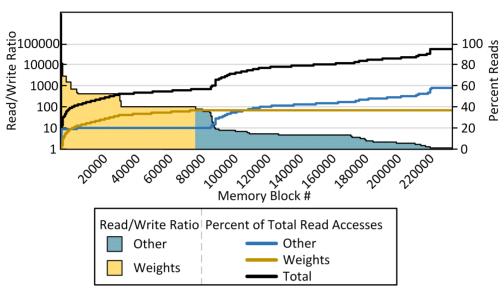

| 4.1  | Read/write access ratios in relation to total read accesses.       |    |

|      | Weight access accounts for nearly 40% of reads                     | 70 |

### **List of Figures**

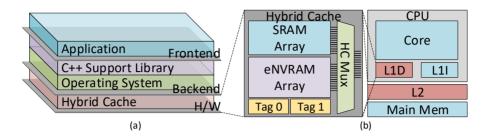

| 4.2 | SHyCache is a HW/SW stack (a) that enables efficient use of a |    |

|-----|---------------------------------------------------------------|----|

|     | hybrid cache (b)                                              | 72 |

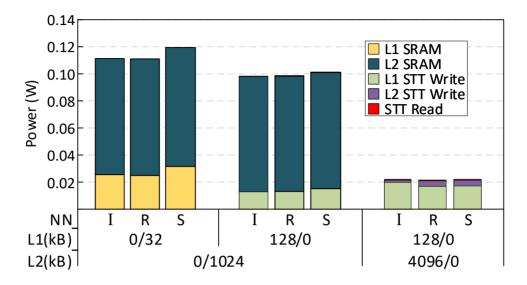

| 4.3 | Power consumption of all-SRAM, SRAM+eNVRAM, and all-          |    |

|     | eNVRAM caches for Inception (I), ResNet (R) and SqueezeNet    |    |

|     | (S) Neural Networks (NNs)                                     | 79 |

| 4.4 | caption                                                       | 81 |

| 4.5 | STT-MRAM bitcell flips across varying L1 (a) and Level 2 (L2) |    |

|     | (b) cache sizes                                               | 83 |

| 4.6 | a) SHyCache + BLADE architecture with eNVRAM output routed    |    |

|     | to SRAM subarray.                                             | 84 |

| - 1 |                                                               |    |

| 5.1 | Chips fabricated in collaboration with the Integrated Systems |    |

|     | Laboratory (IIS) at Swiss Federal Institute of Technology in  |    |

|     | Zürich (ETHZ)                                                 | 91 |

# **List of Tables**

| 2.1 | Worst Case iSC Energy/Frequency Values in a 256×64 array with      |    |  |  |  |

|-----|--------------------------------------------------------------------|----|--|--|--|

|     | 2 Local Groups (LGs)                                               | 29 |  |  |  |

| 2.2 | Simulator Parameters                                               | 42 |  |  |  |

| 2.3 | Cycles for 8/32-bit multiplication at different pipeline levels    |    |  |  |  |

|     | @2Ghz                                                              | 47 |  |  |  |

| 3.1 | Cumulative Fraction of Weights to Quantize at Each Incremen-       |    |  |  |  |

|     | tal Quantize-and-Retrain Step                                      | 61 |  |  |  |

| 3.2 | Accuracy Degradation for quantization strategies after INQ $$ . $$ | 66 |  |  |  |

| 3.3 | Comparison of this work to other approximate multiplier NNs        | 67 |  |  |  |

| 4.1 | Simulator Parameters                                               | 77 |  |  |  |

| 12  | Naural Natwork Banchmark Parameters                                | 79 |  |  |  |

# **Acronyms**

**BL** BitLine Bar. 7

**GBL** Global BitLine Bar. 18, 23

**6T** 6 Transistor. 8, 11, 16–18, 47, 48, 72, 73

**ACL** Arm Compute Library. 15, 41, 45, 76, 78

ADC Analog-to-Digital Converter. 4, 5, 13

**AM** Approximate Multiplier. 50–52, 56, 57, 60, 62, 63, 65–68

**ASIC** Application Specific Integrated Circuit. 12

**BL** BitLine. 5–7, 11, 15, 16, 19, 20, 22–24, 26, 27, 29, 31, 32, 34, 47

**BLADE** BitLine Accelerator for Devices on the Edge. iii, iv, xii, xiii, 2, 8–15, 17–25, 27, 28, 31–52, 54, 55, 68–71, 84, 85, 87–94

**CAPPIEM** CArryless Partial Product InExact Multiplier. iv, xiii, 9, 50–52, 54–57, 62, 63, 67, 68, 89

CNN Convolutional Neural Network. 41, 45, 46

**CPU** Central Processing Unit. iii, 2, 3, 5, 8, 9, 12, 31–34, 38–40, 42, 44, 45, 48, 77, 88, 93

**DAC** Digital-to-Analog Converter. 20

**DMA** Direct Memory Access. 39, 93

DRAM Dynamic Random Access Memory. iii, 2, 4, 5, 13, 36

**eNVRAM** emerging Non-Volatile Memory. iii, iv, 3, 4, 11, 13, 70–78, 80, 82, 84, 85, 90

ETHZ Swiss Federal Institute of Technology in Zürich. 90

**FA** Full Adder. 52, 54, 63, 65

FCQ Fibonacci Codeword Quantization. 50, 51, 58–63, 65, 66, 68

GBL Global BitLine. 17, 18, 29, 32, 55, 84

gemmlowp low-precision general matrix multiplication. 58

**GPU** Graphics Processing Unit. 2, 4, 50, 57, 62, 71

**HC** Hybrid Cache. iv, 70–72, 74, 76–85

**HEVC** High Efficiency Video Encoding. 41

**HMC** Hybrid Memory Cube. 4

IIS Integrated Systems Laboratory. 14, 90, 91

**iMC** in-Memory Computing. iii, 4–6, 8, 12, 13, 70, 87, 92

**INQ** Incremental Network Quantization. 50, 51, 59–63

**IoT** Internet of Things. 1, 40

**ISA** Instruction Set Architecture. 31, 37, 38, 42, 77, 88

**iSC** in-SRAM Computing. iii, iv, xii, xv, 5–8, 11, 13, 16–20, 23, 24, 26–29, 31, 34–39, 41, 42, 45–48, 71, 88

**L1** Level 1. 33, 42, 44–46, 74, 77, 79, 80, 82–84, 88, 93

**L2** Level 2. xiv, 33, 42, 74, 77, 79, 80, 82–84

**LBL** Local BitLine. 17–20, 31, 35, 36

**LG** Local Group. xii, xv, 17, 18, 27–29, 31, 32, 34, 48, 55, 56, 68, 92

**LSB** Least Significant Bit. 24, 34–36, 49, 63, 82, 85

**LVT** Low Voltage Threshold. 27

xxii

MCC Manchester Carry Chain. 25, 26, 28, 29

MRED Mean Relative Error Distance. 52, 62, 63

**MSB** Most Significant Bit. 23, 24, 34–36, 49, 55, 56, 75, 85

NMP Near Memory Processing. 4, 5

**NN** Neural Network. xiv, xv, 5, 7, 9, 10, 50, 51, 57, 58, 62, 66–71, 73, 74, 76, 78–80, 82, 83, 85, 90, 93

**PCM** Phase Change Memory. 3, 4

PDP Power-Delay-Product. 62, 63, 68

PLG Pseudo-Local Group. 84, 85, 92

PnR Place and Route. 15

**RVT** Regular Voltage Threshold. 27

SHA3 Secure Hash Algorithm 3. 41, 43

**SHyCache** HW/SW Stack for Hybrid Caches. iv, 10, 71, 73–80, 84, 85, 90

**SIMD** Single Instruction Multiple Data. iii, 3, 5, 8, 13, 41, 42, 48, 49, 84, 85

**SotA** State-of-the-Art. 4, 8, 50, 67, 76, 87, 88

**SRAM** Static Random Access Memory. iii, iv, 3, 5, 6, 10, 11, 13, 14, 16, 17, 20, 22, 27, 31, 32, 36, 47, 70–74, 76–82, 84, 85, 87, 90, 94

**STT-MRAM** Spin-Transfer Torque Magnetoresistive Random Access Memory. 3, 4, 77, 79, 80, 82, 83

WL WordLine. xi, xii, 5, 7, 16–18, 20, 22, 23, 27, 29, 31, 34–36, 42, 48

## Introduction

MBEDDED systems have seen explosive growth in the last decade. At a ☐ market value of \$86.5 billion and expected to grow to over \$125 billion by 2025 [1], the embedded systems market has been driven by multiple factors, such as the rise of autonomous driving [1] and the internet of things [2]. For the first time in 2020, there are more Internet of Things (IoT) devices connected to the internet than non-IoT devices, as illustrated in Figure 1.1, and this trend is only expected to continue [3]. The span of fields utilizing edge devices is ubiquitous, ranging from industrial control to transportation to medical [2]. As use cases increase, embedded systems are being tasked with increasingly complex applications, such as computer vision, speech recognition, seizure detection, and water and soil analysis, just to name a few. As their ubiquity increases, embedded devices are also becoming smaller and consuming less energy. This, coupled with the high cost of wireless transmission and exponential increases in sensor networks and the consequent "data explosion" [4] has led to the paradigm known as "edge computing", where data is preprocessed at the embedded level before being sent upstream to the cloud. This conflict of interest between enhanced computing power and reduced energy consumption has spurred research into innovative technologies that enhance embedded device capabilities while maintaining a low power budget. This thesis proposes and develops three such lines of research, namely, in-memory computing, hybrid memory systems, and inexact arithmetic units. All three fields extend from a novel in-

#### **Total Number of Connected Devices** Connected Devices (Billions) 45 40 Non-IoT 35 ■ IoT 30 25 10x growth 20 15 10 5 20234 ~ 2021E 2021 12018 2019 2020k Year

Figure 1.1: Devices connected to the internet. Embedded IoT devices have seen a 10x increase in the last decade.

memory computing architecture designed by the author and coined BLADE, or a BitLine Accelerator for Devices on the Edge, which will be the centerpoint of this work.

### 1.1 Edge Devices and the von Neumann Bottleneck

As edge devices become more ubiquitous, they are being increasingly utilized to perform compute intensive tasks traditionally reserved for servers with access to standard accelerators such as Graphics Processing Units (GPUs) [5, 6]. The need to improve performance while maintaining low area and energy overhead presents a unique challenge in embedded device research. This is further complicated by the challenge faced by embedded and server devices alike known as the von Neumann bottleneck [7], where limited I/O bandwidth between the compute and storage elements in an architecture further limit performance. To alleviate this bottleneck and improve embedded device performance while maintaining low energy and area overhead, a plethora of so-called smart memory device and strategies [8] have been proposed. These devices function by computing at the point of data storage instead of moving data to the Central Processing Unit (CPU). Such architectures

Figure 1.2: The various computing paradigms. The von Neumann architecture suffers from long access latency. Near Memory Processing (NMP) performs computation in tightly coupled logic near the memory array. in-Memory Computing (iMC) performs computation either directly in the memory or in the periphery immediately surrounding the array.

are implemented alongside a variety of storage devices, including Dynamic Random Access Memory (DRAM), Static Random Access Memory (SRAM), and emerging Non-Volatile Memory (eNVRAM) devices such as Spin-Transfer Torque Magnetoresistive Random Access Memory (STT-MRAM) or Phase Change Memory (PCM). All smart memories share two inherent benefits, namely, they reduce memory movement, and secondly, they enable massive Single Instruction Multiple Data (SIMD) operations by computing on full rows of data simultaneously.

When making design decisions for smart memories, balancing many competing factors is necessary, including functionality and generalizability, integration and implementation details, and area and energy costs. Specifically, three factors must be asked when considering the benefits and trade-offs of such architectures, namely, where to compute, what type of computation to perform, and what challenges arise in performing said computation.

### 1.1.1 Where to compute: NMP vs. iMC

Smart memories may be roughly broken into two categories, Near Memory Processing and in-Memory Computing. Figure 1.2 illustrates the locations of these compute paradigms relative to the CPU and memory array.

#### 1.1.1.1 Near Memory Processing (NMP)

Near Memory Processing (NMP) is the practice of placing compute logic near memory in an effort to reduce data movement latency between said logic and memory [9]. Many proposed NMP architectures allocate compute blocks on the logic layer of Hybrid Memory Cube (HMC) DRAM [10–13]. Other works couple GPU architectures with 3D stacked memories [14, 15]. Still others utilize reconfigurable logic near the DRAM [16–18].

While NMP computing shows promise, there is still much research to be done to validate its feasibility. First, from an integration standpoint, NMP poses a challenge in regards to virtual-physical memory translation and managing cache coherency [9]. Second, from an application viewpoint, few works provide potential solutions for optimizing algorithms to utilize NMP units while accounting for data locality [15, 19]. Finally, the HMC logic layer area/power budget is very constrained, thus limiting NMP logic complexity [11].

#### 1.1.1.2 in-Memory Computing (iMC)

The definition of in-Memory Computing (iMC) is fuzzier than NMP. At its core, it refers to computation done physically within the memory array. The ambiguity in the term iMC arises when considering the amount of periphery utilized to perform the computation. Some amount of periphery is always necessary to interpret the array output, whether that be an Analog-to-Digital Converter (ADC) for analog iMC devices, or logic gates for digital devices. How much periphery is acceptable while still classifying a device as iMC is debatable. The iMC device described in this work results in 8% periphery area overhead, well under the overhead many iMC State-of-the-Art (SotA) works incur, and therefore the term iMC is ascribed to this device.

In-memory computation can be accomplished in a variety of ways depending on the memory technology. In eNVRAM devices such as STT-MRAM and PCM, by far the most popular strategy to perform computation is the usage of crossbar arrays composed of the variably resistive memory elements [20–22]. By injecting input values into this array, Kirchhoff's circuit laws can be used to multiply input values by values stored in the memory elements before summing them on a single line and converting them into digital form via

ADC. While this strategy has the advantage of potentially performing a huge number of operations simultaneously, it has faced several long-standing challenges In particular, device non-ideality resulting in erroneous results leads to the necessity of area and energy hungry ADC.

On the other hand iMC performed in DRAM utilizes charge sharing between bitcells by activating multiple rows simultaneously and sensing the relative gain or drop in voltage on the bitline to perform majority functions [23]. Alongside the challenges of NMP introduced in the above section on NMP, such a strategy introduces many further difficulties in regards to data placement within the DRAM and the destructive nature of charge sharing. Thus, the data must be copied to dedicated compute rows, mitigating the energy and latency performance gains [23].

A final form of iMC is in-SRAM Computing (iSC). iSC architectures allocate compute logic immediately adjacent to SRAM bitcell arrays, either in dedicated iSC accelerators or in the preexisting cache of the memory hierarchy. iSC architectures take advantage of the SRAM array's BitLine/WordLine (BL/WL) structure to perform massive SIMD computations at a small area/energy cost [24]. Many iSC architectures have been proposed [25-27], with each demonstrating different aspects of the technology. These architectures exploit the inherent data locality found in applications such as Neural Networks (NNs) to perform these operations, similar to other SIMD accelerators such as ARM's NEON [28] and Intel's AVX [29] architectures. Further, when integrated into a cache hierarchy, iSC architectures reduce energy consumption by (a) taking advantage of the cache's set/way allocation scheme to align data and avoid unnecessary data movement, and, (b) reducing data movement between the cache and the CPU. This is accomplished at a minimal area overhead, as the iSC architecture augments preexisting hardware. However, previous works suffer from various shortcomings in relation to simulation methodology, electrical design, or application support. In particular, many of the works lack thorough analysis of system-level integration implications, as well as demonstration of functionality within a full software stack. Also, data corruption within the SRAM array is a prominent problem for iSC architectures [24, 30], and the solutions proposed so far within literature either greatly reduce operating frequency [31] or area efficiency [25].

Figure 1.3: Cache subarray with and/nor/xor bitline computing on values A=0 and B=0. Bitwise operations are performed by first (a) precharging the bitlines, then (b) activating multiple wordlines, thus discharging the bitlines through the connected bitcells.

The devices described in this thesis are implemented in the domain of iSC. The author prefers this form of iMC for various reasons, including the maturity of SRAM technology, the digital nature of the computation, the straightforward implementation within the architecture, and easy integration with the kernel and application. Therefore, the focus of the remainder of this thesis will reside within the iSC domain.

### 1.1.2 What to compute: Simple vs. Arithmetic Operations

Choosing which operations to support in iSC architectures is not trivial, as there is a complex interrelationship between operation complexity, latency, throughput, and area overhead. Many iSC architectures support only bitwise operations through a technique known as BL computing, first demonstrated by Jeloka *et al.* [31], and illustrated in Figure 1.3. BL computing operates similarly to a standard cache read operation. A read operation involves precharging a pair of BLs for each bitcell to be read (Figure 1.3-a), and then activating a single WL to connect the row of bitcells to the BLs, resulting in BL discharge according to the row's contents. In contrast, BL computing involves the simultaneous activation of multiple WLs (Figure 1.3-b), with the resulting BL discharge computing two bitwise operations between the bits, with the BL and BitLine Bar  $(\overline{BL})$  producing and and nor operations, respectively. Aga *et al.* extend this work by noring the two BLs, resulting in a xor operation [24]. This architecture forms the basis of many iSC publications [25, 32–36].

Conversely, multiple works support more complex workloads by implementing BL logic that performs arithmetic operations. Analog solutions such as those presented in [26, 37–40] modulate BL/WL voltages to perform arithmetic operations and utilize analog circuitry implemented under the subarray to sense and convert BL voltages to approximate digital results. On the other hand, solutions such as [27, 41, 42], as well as the accelerator presented in this work, utilize digital logic to compute exact solutions to arithmetic operations.

### 1.1.3 How to compute: iSC Architecture Challenges

The above iSC architectures have been successfully applied to a wide range of applications including query processing and in-memory checkpointing [24], cryptography [24, 32, 43], NNs [33, 37–40, 42, 43], finite state automaton [25], and video encoding [43], thus demonstrating their performance and energy benefits. However, iSC architectures face a variety of challenges at the system, architectural, and electrical level that must be overcome for such architectures to become widely adopted. These challenges include:

- Guaranteeing correct cache functionality at the electrical level.

- Supporting arithmetic operations such as addition and multiplication.

- Integration into the memory hierarchy while addressing issues such as memory translation, coherency, etc.

- Accurate benchmarking on a full software stack.

In the state-of-the-art literature, no single architecture succeeds in overcoming all of the aforementioned challenges. This thesis's contributions address each of these challenges in detail.

### 1.2 Thesis Contribution

In this thesis, I present contributions to the aforementioned iMC/NMP challenges. Namely, I present a BitLine Accelerator for Devices on the Edge (BLADE), an iSC accelerator that contains novel innovations allowing it to perform arithmetic computations and run at higher operating frequencies than previously reported in SotA works. I develop this architecture across the entire HW/SW stack, allowing for further modifications and enhancements from the hardware and architecture up to the kernel and application level. With this flexible platform in place, I proceed to propose various further modifications and enhancements that reduce operation latency, improve capacity, and improve application performance. Lastly, I provide insight on future work for continued exploration in the iSC space.

### 1.2.1 BLADE: A BitLine Accelerator for Devices on the Edge

Chapter 2 presents BLADE, the primary contribution of this thesis. BLADE is an iSC architecture targeted specifically for implementation in low-power edge devices. It performs massive SIMD bitwise and arithmetic computations required by emerging edge device workloads directly in-memory, obviating the need for costly data movement or time-consuming CPU computation. BLADE addresses each of the aforementioned shortcomings prevalent in other iSC architectures. Design choices are motivated from the transistor, architectural, and system levels in order to demonstrate the architecture's energy and performance characteristics at all levels of abstraction. BLADE divides wordlines into isolated subgroups called local groups, eliminating the risk of data corruption, and utilizes a carry lookahead adder and operation pipelining to improve iSC operating frequency by 2.3x-2.8x compared to previous iSC architectures. BLADE maintains a low (8%) area overhead and functions at the lowest operating voltage (0.6V) of any 6 Transistor (6T) bitcell iSC architecture. It is integrated into an edge device cache hierarchy and benchmarked within a fully functioning Linux environment, enabling consideration of system-level events such as cache misses, coherence requests, and CPU/cache hierarchy pipeline stalls. BLADE is validated in 28nm CMOS technology and benchmarked on the gem5-X architectural simulator using three edge device workloads, namely, cryptography, image processing, and NNs, demonstrating 4x/6x, 6x/2x, and 3x/1.5x performance/energy gains, respectively.

Using BLADE as a base, many further strategies are possible for enhancing its in-memory computing capabilities. The next chapters of this thesis implement and analyze two such possibilities, namely, hybrid caches, and approximate computing.

## 1.2.2 CAPPIEM: in-Memory Approximate Computation

One of the major drawbacks of BLADE's low area footprint is the high latency of multiplication, the core operation of NNs. In an effort to reduce multiplication latency, in Chapter 3 I introduce a CArryless Partial Product InExact Multiplier (CAPPIEM), that can be implemented in BLADE at a small area overhead, reducing multiplication latency by 2x. In order to mitigate accuracy loss due to approximated products during inference, I take advantage of a unique property of CAPPIEM, namely, if one of the operands has no consecutive ones in its binary representation, the product will be exact. By iteratively quantizing weights to such values, CAPPIEM acts as an exact multiplier. This quantization strategy accelerates retraining by up to 300x while reducing accuracy by <2% for three benchmarks. I also implement CAPPIEM as a standalone approximate multiplier, reducing area footprint and power-delay-product by 73/43%, respectively.

## 1.2.3 SHyCache: A Hybrid Cache Framework for NN Acceleration

Since Alexnet in 2012, the depth of NNs has exploded, reaching for example 1000 layers in the ResNet series [44]. Recent years have seen smaller networks coming back into fashion; however, the memory footprint of "small" NNs often still measure in the order of MBs [45]. As such, larger capacity memory arrays can help to improve runtime by reducing data movement. In this

#### **Chapter 1. Introduction**

vein, Chapter 4 introduces a HW/SW Stack for Hybrid Caches (SHyCache), a non-volatile/SRAM hybrid cache that increases the size of the cache available to the processor without increasing area overhead. A deterministic data allocation strategy that takes advantage of the static nature of NNs' weights is also introduced, along with a C++ support library that can be integrated into NN frameworks such as Pytorch or Tensorflow. I performed a design space exploration over a wide range of cache hierarchies and capacities to characterize SHyCache. Benchmarks of SHyCache with three NNs demonstrate 1.4/1.3/1.7x performance gain and 5.1/5.2/5.4x power consumption reduction. I finally provide suggestions for integration with BLADE in the Future Work section.

# BLADE: A BitLine Accelerator for Devices on the Edge

A s discussed in Chapter 1, BLADE is an iSC accelerator designed specifically for low power edge devices. The primary motivation in developing BLADE was to create an iSC accelerator that could be implemented in mature technology available on the market today. Hence, BLADE is implemented in SRAM, as opposed to the emerging eNVRAMs currently being developed. Development of a full hardware/software stack for BLADE accounts for each level of abstraction from the transistor level design up to application design. BLADE's compute architecture utilizes BL computing as described in Section 1.1.2, with further developments to run at high frequency and provide enhanced compute capability.

A summary of this chapter's contributions is presented as follows:

- BLADE is introduced. BLADE is a holistically designed and simulated iSC architecture capable of arithmetic operations, designed specifically for edge devices.

- BLADE utilizes local bitlines, operation pipelining, and carry-lookahead addition to achieve the best voltage/frequency Pareto curve of any 6T iSC architecture (0.6V/416MHz-1V/2.2GHz for bitwise operations). Its electrical design is validated in 28nm CMOS technology.

- BLADE is situated within the cache hierarchy. Its controller functionality and application level interface is detailed.

• BLADE is benchmarked on the gem5-X architectural simulator via three edge device workloads, namely, cryptography, image processing, and neural networks, demonstrating 4x/6x, 6x/2x, and 3x/1.5x performance/energy gains respectively.

The remainder of the chapter is organized as follows. Section 2.1 provides motivation for the high-level design choices made when designing and implementing BLADE. Section 2.2 details the subarray optimizations allowing BLADE to run at high frequency with a low energy consumption while avoiding data corruption. Section 2.3 explains how arithmetic operations are supported. Section 2.4 provides information on BLADE's electrical validation as well as subarray designn space exploration results. Section 2.5 details BLADE's integration in the cache hierarchy and its interaction with the rest of the architecture. Section 2.6 details the methodology for evaluating BLADE at the system level. Section 2.7 illustrates benchmark results. Finally, Section 2.8 provides concluding remarks.

## 2.1 Motivation for BLADE Design Choices

The concept of BLADE was born as an answer to the question, "What can be done to accelerate edge applications in a realistic, easily implementable manner, while mitigating area and energy overhead?" Answering this question led to a series of design choices that defined the parameters of BLADE. This section seeks to provide a high-level overview of these choices before delving into the specifics of the design.

## 2.1.1 Accelerating via iMC

In an effort to optimize edge devices, a wide variety of research is being performed into a range of technologies, such as systolic arrays [46], Application Specific Integrated Circuits (ASICs) [47], and simplified CPU pipelines [48]. A challenge facing all the aforementioned research avenues is the need to move data between memory and compute devices. On the other hand, as discussed in Chapter 1, iMC differentiates itself from other strategies by performing compute directly in-memory fabric. Such an architecture provides multiple benefits.

#### Namely, iMC:

- reduces data movement between memory and compute elements, along with the associated latency and energy consumption.

- can reuse existing architecture elements, thus reducing area overhead.

- enables SIMD operations in-memory, capable of performing 100s-1000s of simultaneous operations.

For these reasons, I chose to pursue an iMC solution in answering the above question. Once this broad domain space was established, narrowing down the type of iMC technology was addressed.

## 2.1.2 Implementing BLADE in the iSC Domain

As stated in Section 1.1.1.2, in-Memory Computing (iMC) accelerators can be implemented alongside a variety of memory devices. When considering the different options, namely SRAM, DRAM, and eNVRAMs, SRAM was chosen. iSC has several benefits:

- SRAM is a mature technology, having been in use since the 1960's [49].

Its well understood physical properties are widely supported via simulation tools and fabrication companies. SRAM designs are less complicated to implement and characterize, simplifying integration into existing commodity devices.

- SRAM is commonly found in architectures ranging from edge devices up to server systems. This enables BLADE integration at all levels of system complexity, Also, it enables reuse of existing components, greatly reducing its area overhead in comparison to a dedicated accelerator.

- iSC most commonly utilizes digital logic circuits as opposed to analog.

While this reduces the number of possible operations per cycle, the lack

of need for ADC greatly reduces area overhead. Digital computation

also produces exact operation results, obviating the need to consider

the impact of device utilization on application accuracy.

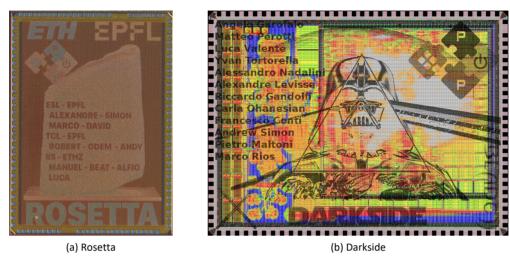

Figure 2.1: BLADE fabricated on the Rosetta and Darkside chips in collaboration with the Integrated Systems Laboratory (IIS) at ETHZ.

Beyond positioning BLADE in the SRAM domain, it is further targeted primarily at the cache hierarchy. The reasons for this design decision are explained in Section 2.5. It should be noted, however, that BLADE can indeed be implemented alongside any SRAM subarray. This is demonstrated by the two fabrication projects performed in collaboration with the Integrated Systems Laboratory (IIS), illustrated in Figure 2.1, in which BLADE is implemented in the chip's tightly coupled scratchpad memory. Such an architecture has the benefits of reduced area overhead due to the absence of tag arrays and more control over data placement, in exchange for increased application complexity. These fabrications will be further discussed in Chapter 5.

## 2.1.3 Full-Stack Analysis Environment

To make the most compelling argument possible for the utility of BLADE, I decided early in the design process to address every level of the HW/SW stack, from the hardware and circuit design level up to the application level. This was to avoid any possible oversights that could occur by making assumptions about implementation at different levels in the stack, such as overly optimistic hardware or architectural parameters, or simplistic benchmarks unrepresentative of real-world applications.

Figure 2.2: A variety of applications are utilized throughout this thesis to implement and benchmark BLADE from the circuit level through the architecture and kernel up to the application level.

Developing along the full stack requires a range of software to accomplish, as illustrated in Figure 2.2:

- At the hardware level, Cadence Virtuoso and Innovus [50,51] are used to layout and Place and Route (PnR) full-custom designs. Sigasi [52] is used to code semi-custom designs, and Modelsim [53] is used to simulate all designs in pre-and post-PnR.

- At the architecture level, the architectural simulator gem5-X [54] is used to integrate BLADE into a full-system architecture. Hewlett-Packard's McPAT [55] and Cacti [56] are used in conjunction with gem5-X activity traces to calculate energy consumption during application runtime. Energy values collected in hardware simulations are also used for this analysis. Further information is provided in Section 2.5.5.

- At the application level, all applications are benchmarked in a modern version of the Ubuntu Linux distro [57]. Applications are developed in multiple frameworks, including PyTorch [58], the Arm Compute Library (ACL) [59], and other sources. These benchmarks will be described in more detail in the relevant sections.

Beginning from the base concept of BL computing described in Section 1.1.2, the remainder of this chapter describes BLADE in increasing levels of abstraction, from the hardware implementation up to application development.

## 2.2 Mitigating Data Corruption while Operating at High Frequency

Figure 2.3: (a) Bitcell shorting may cause one of the activated bitcells to flip. (b) avoids data corruption by lowering WL voltage, while (c) utilizes 8T bitcells to isolate bitcell contents.

One of the biggest challenges for iSC architecture's based on BL computing as described in Section 1.1.2 is the avoidance of data corruption. When activating multiple WLs in a conventional 6T SRAM array, as detailed in Section 1.1.2, a short is produced between the activated bits. It is possible that, due to process variation during fabrication, the runtime content of the cells, or transistor aging and degradation, the contents of one bit can cause another bit to flip, as illustrated in Figure 2.3-a. Preventing data corruption has been achieved in previous literature via multiple methods. The first is to aggressively limit WL voltage, as done in [24,31,38,41] and illustrated in Figure 2.3-b. However, such a technique greatly reduces operating frequency, reported at 800MHz@1V [31] and 475MHz@1.1V [42]. Another method, demonstrated in Figure 2.3-c, is the introduction of 8T or larger bitcells, which isolate the bitcell's contents from the BLs [25, 27, 32, 40], at the cost of a significantly less area efficient SRAM subarray as 8T bitcells are up to 30% larger over 6T [60]. A third method is to use pulse width modulated WLs such that no two WLs are active simultaneously [37], removing the danger of data corruption, but at the cost of a 2.35x increase in periphery area. Finally, nonconventional

technologies can be used, such as monolithic 3D integration [34,35], or deeply depleted channel technology [61]. Emerging technologies present their own challenges however; for example, deeply depleted channel technology demonstrates stability issues [62] and disturb risks, and results in poor performance/voltage scaling, limiting the maximum clock frequency to 100Mhz@0.6V.

In contrast to previous literature, BLADE utilizes local bitlines to maintain a high operating frequency and low area overhead, avoid data corruption, and facilitate simple implementation in conventional 6T SRAM arrays.

#### 2.2.1 What are Local Bitlines?

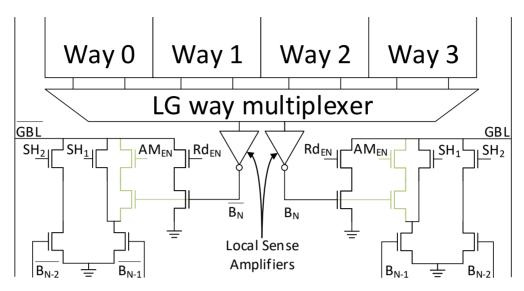

Local BitLines (LBLs), illustrated in Figure 2.4, are a cache optimization present in many architectures. LBLs divide groups of WLs into Local Groups (LGs), where all WLs in an LG share an LBL pair, which is connected to the Global BitLine (GBL) pair via I/O circuitry. LBLs reduce parasitic capacitance resulting from excessively long GBLs, thus improving cache energy efficiency and reducing delay. LBLs also improve static noise margin by isolating bitcells into small groups, reducing leakage interference. For these reasons, LBLs are already implemented in caches [63].

Figure 2.4: LBL read ports prevent data corruption while performing iSC operations.

## 2.2.2 BLADE Methods of Operation

BLADE re-utilizes LBLs, taking advantage of the isolation provided to perform high frequency iSC operations reliably. A BLADE enhanced cache can perform three sets of memory operations, namely, standard read/write, slow same-LBL iSC operations, and fast multi-LBL iSC operations.

#### 2.2.2.1 Standard Read/Write Operations

Accessing a single WL of the cache performs a standard read or write operation. In order to perform a read operation, the GBLs and the LBLs of the LG to which the target set belongs are first precharged to  $V_{dd}$ . Then, when the WL is activated, one of the LBLs discharges. This discharge is propagated through the local read port to the GBLs (illustrated in Figure 2.4, where the discharge is sensed by one of the two single-ended sense amplifiers attached to the GBLs. The addition of local read ports in fact transforms the standard 6T bitcells into pseudo two-port bitcells. Therefore, simultaneous read + write operations are possible if the accessed words are located in different LBLs.

#### 2.2.2.2 Standard iSC Operations

BLADE can also perform iSC operations in the manner described in Section 1.1.2. However, when performing operations between bitcells in opposing states, there is a risk of flipping a bitcell if the PMOS transistor of one bitcell is weaker than the access and pulldown transistors of the other bitcell, as shown in Figure 2.3-a. To counteract this problem, it is necessary to greatly reduce the WL voltages, resulting in a low operating frequency (<1GHz) [24,31].

#### 2.2.2.3 LBL Enhanced iSC Operations

In order to avoid the aforementioned bitcell flipping while maintaining high operating frequency, BLADE reuses LBLs and their resulting LGs. When WLs belonging to different LGs are simultaneously activated, the local read ports isolate bitcells from each other, eliminating the risk of bit flipping, as demonstrated in Figure 2.4. Activating each WL results in a simple read operation within the local group, which is propagated to the GBLs by local read ports, resulting in an iSC operation between LGs, where the GBL represents an and operation, while the Global BitLine Bar  $(\overline{\text{GBL}})$  represents a nor. LGs allow BLADE to maintain a high operating frequency without a reduction in WL voltage, while still utilizing small 6T bitcells. It should be noted that introducing LBLs induces a data placement constraint, namely, that operands cannot occupy the same LG, as discussed in Section 2.5.1.

Figure 2.5: Transient simulations of bitwise operations @0.6V on (a) previously published architectures, and (b) the BLADE architecture.

LBLs also enable iSC operation in low voltage environments. Figure 2.5 illustrates the difference in functionality between (a) standard iSC operations and (b) LBL enhanced operations at a  $V_{dd}$  of 0.6V. LBL enhanced operations complete 4x faster than standard operations, and in fact the and operation fails to converge, due to excessive BL leakage.

## 2.2.3 LBL Enhanced iSC Cache Design Advantages

Utilizing LBLs to enable iSC operations provides multiple advantages over state-of-the-art iSC architectures. As discussed in Section 2.2, most iSC architectures require a significant redesign of either the bitcell array or periphery

to enable computation. BLADE, on the other hand, introduces minimal changes to the cache architecture. The LBL design, as well as the use of digital computation in contrast to analog, allow BLADE to function over a large voltage range, thus easing implementation across a wide range of cache architectures and making BLADE suitable for low power edge devices. Ease of implementation is further facilitated by the fact that no modification to the bitcell array organization is necessary to implement BLADE, as all computation happens within the periphery. This greatly simplifies integration into existing SRAM fabrication design flows, where the most aggressive and complex design steps relate to the bitcell array. Finally, BLADE scales easily to larger cache arrays/subarrays without major loss of performance or energy savings, as LBL length is invariant with regard to subarray size, as will be discussed in Section 2.4.2.

## 2.3 Logic to Support Arithmetic Operations

While bitwise operations enabled by simple bitline logic may be sufficient to support applications such as cryptography or binary neural networks, more complex workloads necessitate arithmetic operations.

As discussed in Section 1.1.2, iSC architectures can perform either simple bitwise operations or arithmetic operations such as addition and multiplication. Supporting arithmetic operations introduces trade-offs in area overhead and latency as the BL logic becomes more complex. Carry logic may have to cross multiple BLs [27]. Alternatively, unorthodox methods of computation may be introduced, such as bit serial computation as in [41], which stores and operates on data in a transposed manner, limiting extra BL logic to a couple of latches, while also greatly increasing throughput. However, latency is also drastically increased, even quadratically for multiplication. Further, transposition presents challenges, requiring either extra hardware in the form of transposition functional units in the cache controller, 8T bitcells with extra BLs/WLs [42], which decreases subarray area efficiency as discussed in Section 2.2, or software transposition, introducing challenging programming complexity. For analog solutions, area overhead is a significant limitation, with reported overheads of 19% [37] and >30% [40], and the acknowledgement that WL Digital-to-Analog Converters (DACs) double array

Figure 2.6: Layout of a  $256 \times 2 \times 32$  BLADE memory with schematic diagram of the BLADE periphery.

Figure 2.7: Block schematic of the modified WL decoder used in this work.

periphery [38]. Analog designs also perform inexact computations, which may be unacceptable for high precision applications, limiting generalizability, and are very susceptible to process variation, temperature, and aging [39].

In order to accelerate the widest range of workloads possible, BLADE supports common arithmetic operations, such as addition, subtraction, multiplication, greater/less than, and shift. These operations are implemented by augmenting the standard BL logic explained in Section 1.1.2 with carry and shift logic. By utilizing digital logic as opposed to analog, BLADE guarantees calculation exactness, necessary for high precision workloads.

#### 2.3.1 Bitline Addition Architecture

Figure 2.6 illustrates BLADE's BL logic, as well as the transistor layout of a 4 way, 256x64 bitcell SRAM array with two local groups, each containing 32 WLs.

Algorithm 1 Modified add/shift multiplication for BLADE iSC computing.

```

Input: Op<sub>0</sub>: Multiplier, Op<sub>1</sub>: Multiplicand

Output: Res=Op_0 \times Op_1

1: Latch Op<sub>0</sub>

2: i = \#Bits_{Op_0} - 1

3: while i \ge 0 do

Res << 1

4:

tmp = Op_1 + Res

5:

if Op_0[i] = 1 then

6:

7:

Res \leftarrow tmp

else

8:

9:

Res \leftarrow Res

```

In order to support addition, a carry ripple adder is implemented underneath the array through the addition of two nor gates and a xor gate. Shift latches are also implemented within the BLADE controller to allow one cycle shifting. Each BL logic block receives a carry-in from the previous BL logic block, and provides a carry-out to the next block.

10:

In order to drive multiple WLs as required by iSC operations, two WL decoders are utilized to simultaneously decode two WL addresses. A bitwise or is performed on the decoded addresses before driving the WLs, as illustrated in Figure 2.7. In an area-constrained environment, one decoder could be omitted in exchange for latches placed before the WL drivers, with the WL addresses decoded sequentially, similarly to the work presented in [27].

The implementation of addition logic enables many arithmetic operations, achievable through series of simple operations. For example, subtraction can be performed by negating the subtrahend by reading and storing the  $\overline{GBL}$  value, then performing an addition between the operands with the first carry-in value set to 1.

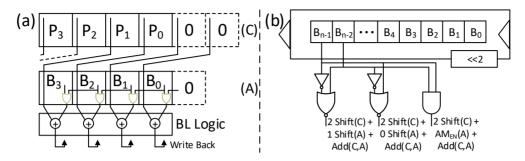

Greater/less than is similarly computed by subtracting the operands and sensing the Most Significant Bit (MSB). Multiplication can be performed via a variation of the classic add and shift algorithm, as codified in Algorithm 1 and

Chapter 2. BLADE: A BitLine Accelerator for Devices on the Edge

| Multiplicand (MU) Multiplier (M) Exp. Value (P) 0 1 0 |                                                 | 1 0 1 0<br>x 1 0 0 1<br>1 1 0 1 0    | Step 4: Add   | (   | 1 0 0 1 0<br>1 0 1 0<br>0 1 0 1 0 0     |

|-------------------------------------------------------|-------------------------------------------------|--------------------------------------|---------------|-----|-----------------------------------------|

| Step 0: Init                                          | M Shift Register<br>MU Mem. Loc.<br>P Mem. Loc. | MSB<br>1 0 0 1<br>1 0 1 0<br>0 0 0 0 | Step 5: Shift |     | 1 0 0 1 0 0<br>1 0 1 0<br>1 0 1 0 0     |

| Step 1: Shift                                         |                                                 | 1 0 0 1<br>1 0 1 0<br>0 0 0 0 0      | Step 6: Add   | 0 ( | 1 0 0 1 0 0<br>1 0 1 0 0<br>0 1 0 1 0 0 |

| Step 2: Add                                           | \$                                              | 1 0 0 1<br>1 0 1 0<br>0 1 0 1 0      | Step 7: Shift |     | 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0         |

| Step 3: Shift                                         | 0                                               | 1 0 0 1 0<br>1 0 1 0<br>1 0 1 0 0    | Step 8: Add   |     | 1 0 0 0<br>1 0 1 0<br>0 1 1 0 1 0       |

Figure 2.8: 4-bit shift-and-add multiplication as performed by BLADE.

illustrated in Figure 2.8, in which the product is shifted left each step (line 4) and the multiplier is processed from MSB to Least Significant Bit (LSB) to evaluate which partial products must be accumulated (lines 6-9).