### LiNiO Junction Gate for High-performance Enhancement-mode GaN Power Transistor

Présentée le 27 juillet 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire de dispositifs semiconducteurs de puissance Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

## **Taifang WANG**

Acceptée sur proposition du jury

Dr G. Boero, président du jury

Prof. E. D. N. Matioli, directeur de thèse

Prof. C. Gupta, rapporteur

Dr C. Ostermaier, rapporteur

Prof. A. Ionescu, rapporteur

## Acknowledgements

First, I would like to express my great appreciation to my professor Prof. Elison Matioli. Prof. Elison gave me the chance to enter such an interesting and impactful area. From a rookie PhD student to a person not only independent in research but also personally. He always supports me from mental, knowledge, experience, and resources. His patience and encouragement give me faith when I am in the early stages of research. From him, I know what kind of person I want to become and should become. The journey with Prof. Elison will be the most fruitful period in my life.

I would like to thank my thesis committee, Prof. Gupta, Prof. Ionescu, and Dr. Ostermaier. Their insights and questions help me better understand and rethink my work.

I am particularly grateful for the help from my colleague Prof. Jun, who always has the answer of the question. Moreover, he teaches me the right way to get along with people, the right way of communicating, and the right direction of doing research, especially at the beginning of my PhD period.

I also want to express my thanks to Prof. Chao. From him I learnt the attitude I should have on my work; Dr. Minghua's help during the COVID period and help on my job searching; Ms, Muriel's help on daily stuff; And Dr. Giovanni, Dr. Reza, Dr. Riyaz, Dr. Catherine, Dr. Remco, Dr. Armin, Mohammad Samizadeh, Dr. Luca, and Dr. Nirmana's help during my stay in Powerlab, their inspiring, and suggestion always let me think the question from different perspective.

I would also like to thank all the staff in CMi, CIME, and ICMP. They are always there when I need advice on process and characterization.

Finally, I am very grateful to my mom Hongyuan Di and father Zeyu Wang for their outspoken support and love.

Lausanne, April 2022

## **Abstract**

GaN metal-oxide-semiconductor high electron mobility transistors (MOS)HEMTs) offer outstanding properties for next-generation power electronics devices. The high conductivity, high voltage blocking capability, high operation frequency, and device-level integration can be achieved on the same technology platform. Moreover, the development of large-scale GaN-on-Si substrate reduces the cost of GaN lateral devices. That GaN power device has already been widely used in today's consumer electronics, and communications base stations with its superiority of power density, and energy efficiency.

Despite the ideal side of GaN material for power transistor, the junction less structure of HEMT made it hard to achieve enhancement-mode (e-mode) operation. Existing solutions either rely on complicated processes or sacrifice device performance. A simple process, high performance, and reliable operation e-mode device are desired.

This thesis proposes Li doped NiO as gate material combined with Tri-gate structure to achieve e-mode operation. This relied on a simple oxide deposition process, without using barrier recess or regrowth, and achieved a high-quality interface. These critical characteristics haven't been demonstrated on gate stack engineering for normally-off devices and reveal the outstanding stability of LiNiO as a junction gate.

Moreover, to maximize the GaN power transistor performance boundary, a multi-channel junction gate device was developed, which uses multiple 2DEG channels to significantly reduce the device resistance while still operating at high breakdown voltage ( $V_{BR}$ ). The multi-channel junction gate device presents state-of-the-art performance, stable operation, and simple process e-mode GaN transistor.

Apart from achieving e-mode operation, the possibility of device-level integration was also explored. Reverse current conduction ability was achieved together with good on-state performance and voltage blocking capability. And the alternative method of regulating electric field to Tri-gate by grayscale lithography was developed.

The results in this thesis reveal the great value of using oxide semiconductor LiNiO as junction gate, demonstrating high performance, e-mode, and reliable device, and unleashing the performance potential through multi-channel epitaxy.

## Keywords

GaN, LiNiO, Tri-gate, E-mode, Monolithic integration, freewheeling diode, slanted field-plate.

## Résumé

Les transistors à haute mobilité électronique (MOS)HEMT en métal-oxyde-semiconducteur GaN offrent des propriétés exceptionnelles pour les dispositifs électroniques de puissance de la prochaine génération. La conductivité élevée, la capacité de blocage de tension élevée, la fréquence de fonctionnement élevée et l'intégration au niveau du dispositif peuvent être obtenues sur la même plate-forme technologique. De plus, le développement du substrat GaN sur Si à grande échelle réduit le coût des dispositifs latéraux GaN. Le dispositif de puissance GaN a déjà été largement utilisé dans les produits électroniques grand public d'aujourd'hui et dans les stations de base de communication grâce à sa supériorité en termes de densité de puissance et d'efficacité énergétique.

Malgré le côté idéal du matériau GaN pour les transistors de puissance, la structure sans jonction du HEMT rend difficile le fonctionnement en mode amélioration (e-mode). Les solutions existantes reposent sur des processus compliqués ou sacrifient les performances du dispositif. Un processus simple, des performances élevées et un fonctionnement fiable en mode e sont souhaités.

Cette thèse propose du NiO dopé au Li comme matériau de grille combiné à une structure Tri-gate pour atteindre un fonctionnement en mode e. Elle s'appuie sur un processus simple de dépôt d'oxyde, sans utiliser d'évidement ou de recroissance de la barrière, et permet d'obtenir une interface de haute qualité. Ces caractéristiques critiques n'ont pas été démontrées dans l'ingénierie des piles de grille pour les dispositifs normalement éteints et révèlent la stabilité exceptionnelle du LiNiO comme grille de jonction.

De plus, pour maximiser la limite de performance des transistors de puissance GaN, un dispositif de grille de jonction multicanaux a été développé, qui utilise plusieurs canaux 2DEG pour réduire de manière significative la résistance du dispositif tout en fonctionnant à une tension de claquage élevée (VBR). Le dispositif à grille de jonction multicanaux présente des performances de pointe, un fonctionnement stable et un transistor GaN e-mode de processus simple.

Outre l'obtention d'un fonctionnement en mode électronique, la possibilité d'une intégration au niveau du dispositif a également été explorée. La capacité de conduction du courant inverse a été obtenue

avec de bonnes performances à l'état actif et une capacité de blocage de la tension. Une méthode alternative de régulation du champ électrique sur le tri-gate par lithographie en niveaux de gris a été développée.

Les résultats de cette thèse révèlent la grande valeur de l'utilisation du semi-conducteur d'oxyde Li-NiO comme porte de jonction, démontrant une haute performance, un mode e et un dispositif fiable, et libérant le potentiel de performance par l'épitaxie multicanaux.

## Mots-clés:

GaN, LiNiO, Tri-gate, E-mode, Monolithic integration, freewheeling diode, slanted field-plate.

# **Symbols and Acronyms**

| Symbol             | Quantity                  | Measurement unite or value |

|--------------------|---------------------------|----------------------------|

| $E_{\mathrm{G}}$   | Band gap                  | eV                         |

| Ecrit              | Critical electric field   | MV/cm                      |

| $\mu_{ m n}$       | Electron mobility         | $cm^2/V \cdot s$           |

| $n_{\mathrm{i}}$   | Intrinsic carrier density | cm <sup>-3</sup>           |

| $P_{SP}$           | Spontaneous polarization  |                            |

| $P_{ m pz}$        | Piezoelectro polarization |                            |

| $N_{ m s}$         | Carrier density           | cm <sup>-3</sup>           |

| $I_{D}$            | Drain current             | A/mm                       |

| $G_{ m m}$         | Transconductance          | mS/mm                      |

| $V_{ m BR}$        | Breakdown voltage         | V                          |

| $V_{ m G}$         | Gate voltage              | V                          |

| $V_{D}$            | Drain voltage             | V                          |

| $W_{ m fin}$       | Fin width                 | nm                         |

| $D_{\mathrm{fin}}$ | Fin-to-fin distance       | Nm                         |

| $R_{ m ON}$        | On-resistance             | $\Omega$ ·mm               |

| $V_{ m TH}$        | Threshold voltage         | V                          |

| $I_{ m ON,max}$    | Maximum on-current        | A/mm                       |

| Ev                 | Valence band offset       | eV                         |

| Ec                 | Conductance band offset   | eV                         |

| $R_{ m ON,SP}$     | Specific ON resistance    | $m\Omega\cdot cm^2$        |

| $R_{\rm S}$        | Sheet resistance          | $\Omega$ /sqr.             |

| $I_{ m OFF}$       | Off-state current         | A/mm                       |

| $D_{it}$           | Interface trap density    | $eV^{-1} \cdot cm^{-2}$    |

| $L_{Fin}$          | Fin length                | nm                         |

| $Q_{ m G}$         | Gate charge               | C/cm <sup>2</sup>          |

|                    |                           |                            |

**Abbreviation** Full name

GaN Gallium nitride

Si Silicon

SiC Silicon carbide

2DEG 2-Dimensional electron gas

EV Electric vehicle HV Hybrid vehicle

LED Light-emitting-diode

RF Radio frequency

FOM Baliga's Figure of Merit

GIT Gate injection transistor

HD-GIT Hybrid-drain-embedded gate injection transistor

LDMOS Lateral diffused MOSFETs

SS Subthreshold swing

IGBT Insulated-gate bipolar transistor

FP Field-plate

e-mode Enhancement-mode

ALD Atomic layer deposition

XRD X-ray diffraction

HfON Hafnium oxynitride

TOS Transparent oxide semiconductors

UV Ultraviolet

TFT Transparent thin-film-transistor

HTL Hole-transporting layer

PLD Pulse laser deposition

HRTEM High-resolution transmission electron microscopy

RHEED Reflection high-energy electron diffraction

SAED Selected area electron diffraction

MRAM Magnetic memory

TMOs Transition-metal oxides

RRAM Resistive random-access memory

RIE Reactive ion etching

PECVD Plasma-enhanced chemical vapor deposition

ICP Inductively coupled plasma

ESL Etching stop layer

NiO Nickel oxid

BHF Buffered hydrofluoric acid

EPD End-point-detection

EDX Dispersive X-Ray Analysis

IBE Ion beam etching

HADDF High-angle annular dark-field

STEM Scanning transmission electron microscope

EDS X-ray spectroscopy

FWHM Full-width half-maximum

XPS X-ray photoelectron spectroscopy

UV-Vis Ultraviolet-visible spectroscopy

TCAD Technology Computer-Aided Design

NBTI Negative bias temperature instability

PBTI Positive bias temperature instability

RCA The Radio Corporation of America

FIB Focused Ion Beam

**HTRB**

HSQ Hydrogen silsesquioxane(s)

SEM Scanning electron microscopy

RTA Rapid thermal annealing

RT Room temperature

TMAH Tetramethylammonium hydroxide

PR Photoresist

HRXRD High-resolution X-ray diffraction

RC-MOSHEMTs Reverse-conduction GaN-on-Si metal-oxide-semiconductor

high electron mobility transistors

High-temperature reverse bias

ILD Interlayer dielectric

SBD Schottky barrier diode

HBD Hard breakdownS-FP Slanted field plateFOX Flowable oxide

PEC Proximity effect correction

IDM Integrated device manufacturer

DUV Deep ultraviolet

# Contents

| Acknowl    | edgements                                                  | i   |

|------------|------------------------------------------------------------|-----|

| Abstract   |                                                            | ii  |

| Keyword    | S                                                          | iii |

| Résumé     |                                                            | iv  |

| Symbols    | and Acronyms                                               | vi  |

| List of Fi | gures                                                      | xii |

| List of Ta | ıbles                                                      | 21  |

| Chapter    | 1 Introduction                                             | 23  |

| 1.1        | GaN is an excellent material for power application         | 24  |

| 1.2        | Development of large-scale GaN-on-Si wafer                 | 26  |

| 1.3        | Requirements for future GaN transistors.                   | 26  |

|            | 1.3.1 Technologies to push the performance limits          | 27  |

|            | 1.3.2 High-performance e-mode GaN transistors.             | 28  |

|            | 1.3.3 GaN integration circuits.                            | 32  |

| 1.4        | Thesis outline                                             | 33  |

| Chapter :  | Slanted field-plate technology for higher $V_{\rm BR}$     | 35  |

| 2.1        | Introduction                                               | 35  |

| 2.2        | Motivation and approach                                    | 36  |

|            | 2.2.1 Grayscale lithography                                | 36  |

|            | 2.2.2 Fabrication process of S-FP by grayscale lithography | 38  |

| 2.3        | Results and discussion                                     | 40  |

| 2.4        | Conclusion                                                 | 41  |

| Chapter :  | LiNiO gate oxide for enhancement-mode tri-gate MOSHEMTs    | 43  |

| 3.1        | Introduction                                               | 43  |

|            | 3.1.1 Tri-gate technology                                  | 43  |

| 3.2       | Motivation                                                                              | .47  |

|-----------|-----------------------------------------------------------------------------------------|------|

| 3.3       | Existing enhancement-mode tri-gate (MOS)HEMT                                            | . 49 |

|           | 3.3.1 E-mode operation by structure engineering                                         | . 49 |

|           | 3.3.2 E-mode operation by gate stack engineering                                        | .51  |

| 3.4       | LiNiO: a promising candidate for p-type gate of lateral GaN transistors                 | . 53 |

| 3.5       | Process of LiNiO junction gate tri-gate device                                          | . 55 |

|           | 3.5.1 Etching properties of (Li)NiO                                                     | . 55 |

|           | 3.5.2 Process of LiNiO deposition, patterning, and integration with tri-gate structure. | . 57 |

| 3.6       | Device performance and optimization                                                     | . 65 |

|           | 3.6.1 Static performance                                                                | . 65 |

|           | 3.6.2 Device design optimization                                                        | . 68 |

|           | 3.6.3 High temperature operation performance                                            | . 70 |

|           | 3.6.4 Gate reliability and optimization                                                 | .71  |

|           | 3.6.5 Reliability performance                                                           | .72  |

|           | 3.6.6 Dynamic performance                                                               | . 73 |

|           | 3.6.7 LiNiO/AlGaN interface quality characterization                                    | .75  |

|           | 3.6.8 Benchmarks                                                                        | . 79 |

| 3.7       | Conclusion                                                                              | . 80 |

| Chapter 4 | E-mode multi-channel tri-gate device with LiNiO junction gate                           | .81  |

| 4.1       | Multi-channel lateral GaN transistor towards ultra-high performance                     | .81  |

| 4.2       | Process and optimization                                                                | . 85 |

|           | 4.2.1 Device design.                                                                    | . 85 |

|           | 4.2.2 Isolation optimization                                                            | . 87 |

|           | 4.2.3 LiNiO patterning process optimization                                             | .88  |

|           | 4.2.4 Other process optimization                                                        | . 89 |

| 4.3       | Static performance                                                                      | .90  |

| 4.4       | Gate charge and mobility measurements                                                   | .93  |

|           |                                                                                         |      |

| 4.5      | Conclusion                                                        | 96  |

|----------|-------------------------------------------------------------------|-----|

| Chapter  | Exploring the possibility of device-level integration: RC-MOSHEMT | 97  |

| 5.1      | Introduction                                                      | 97  |

| 5.2      | Motivation and approches                                          | 99  |

| 5.3      | Device performance                                                | 101 |

| 5.4      | Conclusion                                                        | 105 |

| Chapter  | 6 Conclusions                                                     | 107 |

| 6.1      | Results achieved                                                  | 107 |

| 6.2      | Future development                                                | 108 |

| Curricul | ım Vitae                                                          | 109 |

| Referenc | 2                                                                 | 110 |

| Appendix | x-1: Process flow of single-channel junction gate devices         | 119 |

| Appendix | x-2: Process flow of multi-channel junction gate devices          | 123 |

# **List of Figures**

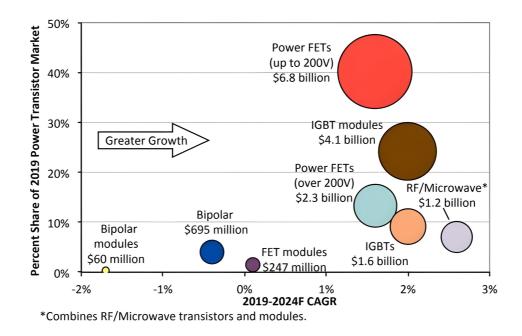

| Figure 1-1 The power market share of different categories of power electronic devices [1]23                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

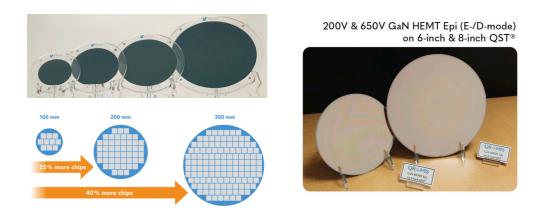

| Figure 1-2 12-inch crack-free 1200 V GaN-on-Si wafer, and 8-inch GaN-on-QST® wafer for RF application.                                                                                                                                                                                                                                                                                                                                                                           |

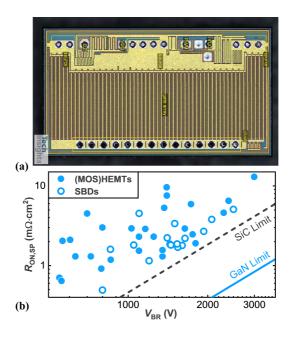

| Figure 1-3 (a) Optical microscope image of Navitas 650 V GaNFast Power IC [11]. (b) $(V_{BR})^2/R_{\rm on,sp}$ FOM of current GaN-on-Si devices                                                                                                                                                                                                                                                                                                                                  |

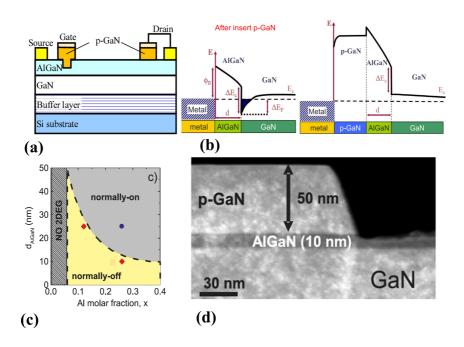

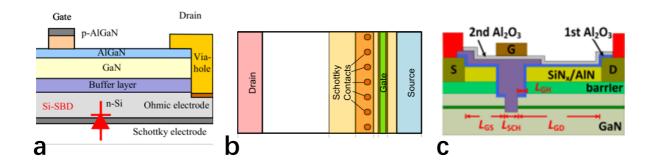

| Figure 1-4 (a) Schematic of p-GaN gate e-mode transistor [15, 16], (b) schematic of the operation principle of p-GaN gate e-mode device. (c) Device operation mode as a function of Al percentage and thickness of the AlGaN barrier, (d) cross-section TEM image of the p-GaN/AlGaN/GaN heterostructure after p-GaN dry etching [17]                                                                                                                                            |

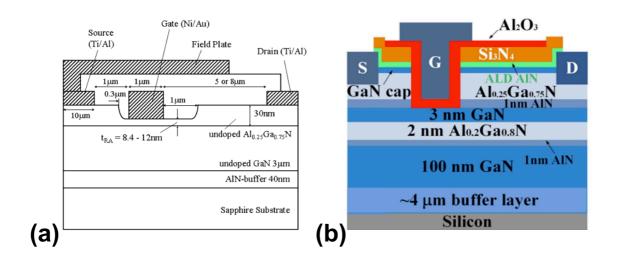

| Figure 1-5 (a) Cross-sectional structure of fabricated AlGaN/GaN HEMT with recessed-gate structure [24], (b) Cross-sectional structure of gate recess GaN MOSHEMT with AlN/Si <sub>3</sub> N <sub>4</sub> passivation and post-recess channel protection layers [25].                                                                                                                                                                                                            |

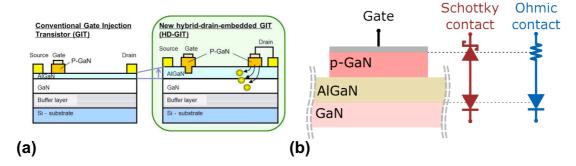

| Figure 1-6 (a) Configuration of HD-GIT device, (b) cross-section of gate region and equivalent circuits corresponding to the Schottky and ohmic gate [35]                                                                                                                                                                                                                                                                                                                        |

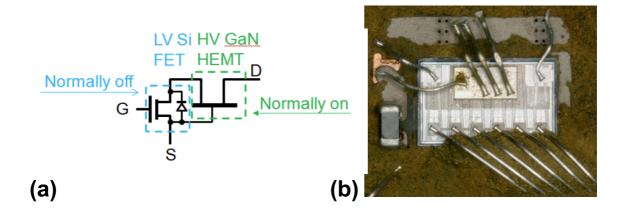

| Figure 1-7 (a) Transphorm GaN Switch [36]. (b) Tear down of Nexperia's GaN transistor (GAN063-650WSA).                                                                                                                                                                                                                                                                                                                                                                           |

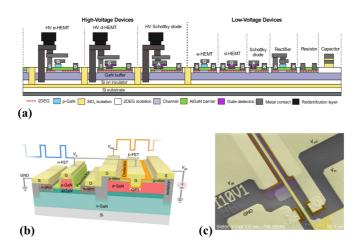

| Figure 1-8 (a) IMEC's 200 V GaN-on-SOI power IC technology [40]. (b) Schematic and (c) SEM image of GaN-based complementary logic integrated circuits [41]                                                                                                                                                                                                                                                                                                                       |

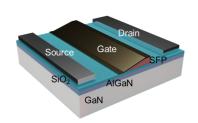

| Figure 1-9 Three devices achieved in this thesis, 1. Slanted field plate technology for better FOMs, 2. Using LiNiO semiconductor oxide as junction gate, which works together with trigate and multi-channel epitaxy. Enhancement-mode operation, high-performance, and good reliability was reported at the same time. 3. Based on tri-gate structure's concise process, and high-performance, monolithic integration of freewheeling diode and GaN MOSHEMTs was demonstrated. |

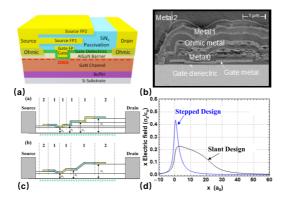

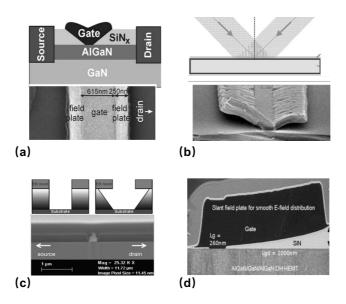

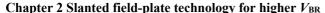

| Figure 2-1 (a) Schematic of multi-level field plate [46]. (b) Cross-section SEM of multi-level field plate [40]. (c) Schematic of multi-stage gate field plate and slanted gate field plate [47]. (d) Electric field along the drift region through simulation [47]                                                                                                                                                                                                              |

| Figure 2-2 (a) Schematic and top-view SEM image of slanted field plate using well-controlled CF <sub>4</sub> etching [13]. (b) Schematic and SEM image of S-FP using angle exposure during                                                                                                                                                                                                                                                                                       |

| lithography [45]. (c) Schematic and cross-section SEM image of S-FP using well-controlled SiCN etching [44]. (d) Schematic and cross-section SEM image of S-FP utilizing the surface tension of HSQ to achieve a slanted etching mask [43]                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-3 (a) SEM image of microfabricated fish relief structures using grayscale lithography (b) Confocal microscope image of a micro lens array in a honeycomb arrangement (Heidelberg Instruments)                                                                                                                                                       |

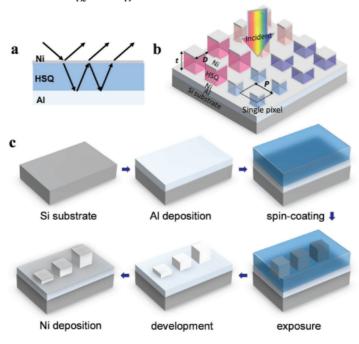

| Figure 2-4 Concept and process flow for visible color printing. (a) The basic configuration of an interference color pixel. (b) 3D schematic concept of color printing based on grayscale-patterned resonators. (c) The schematic flow shows process flow [52]                                                                                               |

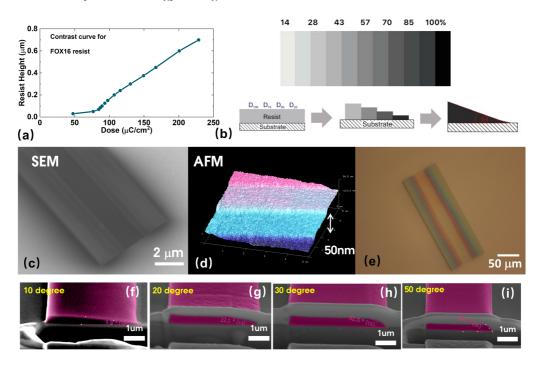

| Figure 2-5 (a) Contrast curve for FOX 16, using CD 26 as developer. (b) Schematic of dose adjust method to achieve grayscale lithography. (c) SEM result of the grayscale lithography test structure. (d) AFM results of step structure. (e) optical image of the test structure. (f)(g)(h)(i) cross-section SEM image of different angles of slanted oxide. |

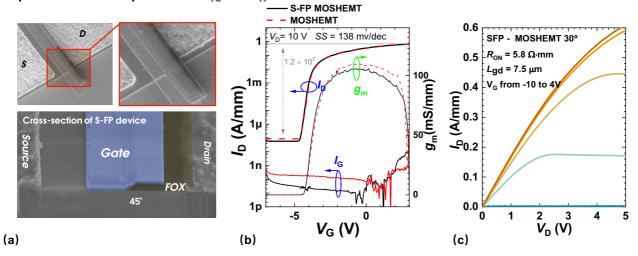

| Figure 2-6 (a) SEM images of fabricated slanted FP device. (b)Transfer characteristic of Slanted FP device. (c) The output characteristic of the S-FP device                                                                                                                                                                                                 |

| Figure 2-7 (a) Grounded substrate breakdown behavior comparison. (b) Breakdown voltage distribution of the different angles of field plate. (c) Floating substrate breakdown behavior comparison. (d) Benchmark FOM with state-of-the-art MOSHEMT (both floating substrate (flo) and grounded substrate(gnd)).                                               |

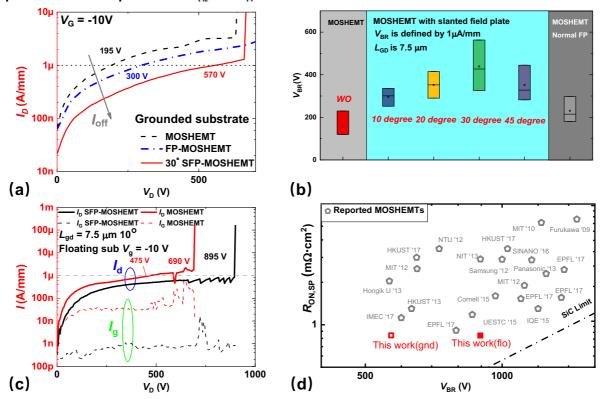

| Figure 3-1 Intel's first generation 22 nm manufacturing process tri-gate FinFET structure compare with 32 nm node planar structure [54].                                                                                                                                                                                                                     |

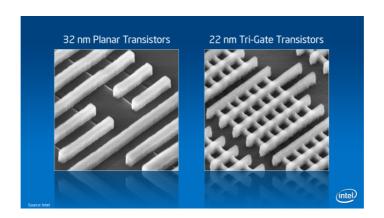

| Figure 3-2 (a) Schematic of tri-gate transistor, (b) cross-section schematic of tri-gate nanowire region, (c) equivalent circuit of tri-gate structure [14]                                                                                                                                                                                                  |

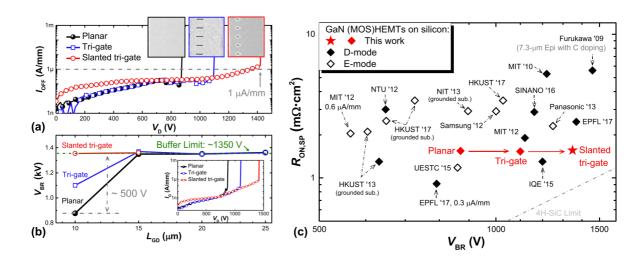

| Figure 3-3 (a) Typical breakdown characteristics of MOSHEMTs with planar gates, tri-gates and slanted tri-gates and (b) their $L_{\rm GD}$ -dependent $V_{\rm BR}$ (at 1 $\mu$ A/mm), measured at $V_{\rm G}$ of $-10$ V with a floating substrate, in which the $I_{\rm OFF}$ for all devices was normalized by their footpring width [60].                 |

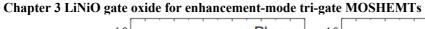

| Figure 3-4 Temperature-dependent $I_D$ - $V_D$ characteristics of the (a) planar and (b) Tri-gated HEMTs under similar gate driving voltage; (c) degradation in on-resistance ( $\Delta R_{\rm ON}$ ) versus temperature; (d) $I_D$ of the HEMTs versus temperature at $V_D$ = 25 V [61]                                                                     |

| Figure 3-5 Achieving e-mode operation by high work function metal: (a) Top-view image of device access region and the gate region is highlighted. The fin is covered with 25 nm ALD                                                                                                                                                                          |

| SiO, with Pt/Au as gate metal. (b) Zoomed SEM image of the nanowire region before gate oxide deposition. (c) FIB cross-section of the gate nanowires along the AA line. The fins are covered only by 20 nm ALD SiO <sub>2</sub> , on top of which Ni-Au or Pt-Au gate stacks were deposited [58]. Recess gate: (d) 3D schematic of recessed tri-gate MOSHEMT [77, 78]. P-GaN: (e) Schematic of fabricated p-GaN MOS tri-gate MOSHEMT [79]                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

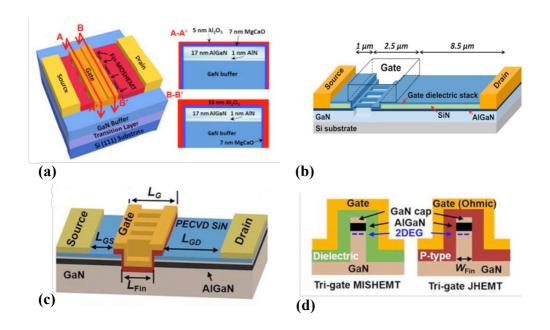

| Figure 3-6 (a) Schematic of GaN fin-MOSHEMT with atomic layer epitaxy MgCaO gate dielectric [67]. (b) Schematic cross-section of GaN tri-gate device with hybrid ferroelectric charge trap gate stack: HfZrO4/HfON [83]. (c) and (d) 3D schematic of a tri-gate GaN junction HEMT using NiO <sub>x</sub> as a p-type gate material. (b) Fin cross-section view of MIS tri-gate (left) and a junction tri-gate (right) [70]                                                                                                                                                                                                                                                                         |

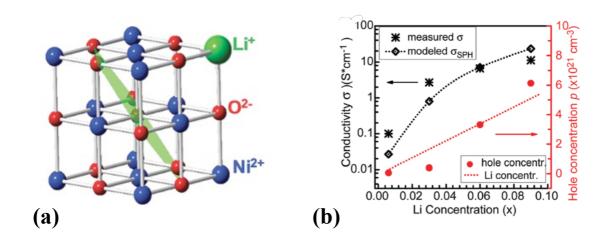

| Figure 3-7 Epitaxial growth of $Li_XN_{i1-x}O$ thin films on MgO (001). (a) Crystal structure of doped NiO with Li at Ni atom site. (b) From the combination of Seebeck measurements and film conductivity to get mobility and carrier concentrations [75]                                                                                                                                                                                                                                                                                                                                                                                                                                         |

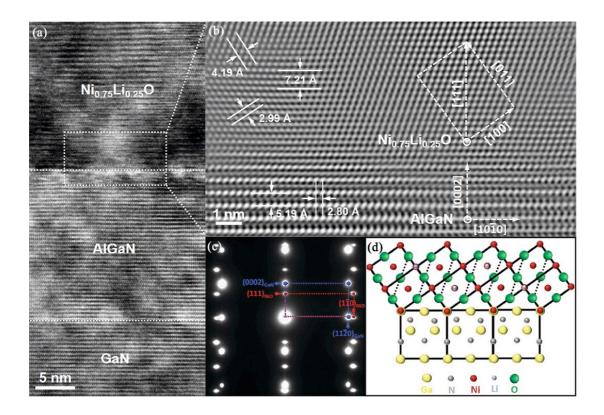

| Figure 3-8 Sectional HRTEM images of the (a) $\text{Li}_{0.25}\text{Ni}_{0.75}\text{O/AlGaN/GaN}$ heterostructure and the (b) $\text{Li}_{0.25}\text{Ni}_{0.75}\text{O}$ /AlGaN interface. (c) SAED pattern detected at the $\text{Li}_{0.25}\text{Ni}_{0.75}\text{O}$ /AlGaN/GaN interface. (d) Schematic diagram for the out-of-plane atomic epitaxy matching model of the $\text{Li}_x\text{Ni}_{1-x}$ O/AlGaN/GaN heterostructure [76]                                                                                                                                                                                                                                                         |

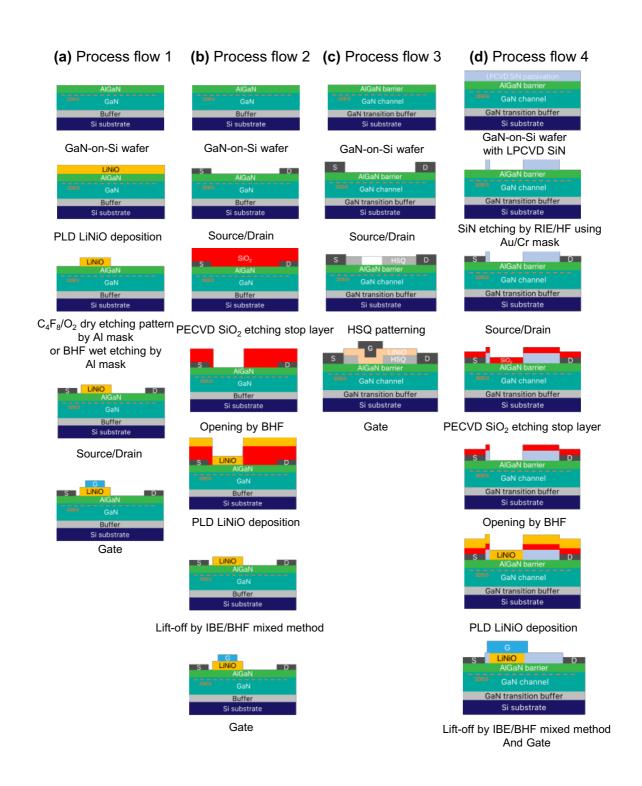

| Figure 3-9 Different process flow of LiNiO gate device: (a) direct dry etching of LiNiO using IBE etching or carbon/oxygen-based recipe. (b) LiNiO patterning by oxide lift-off method. (c) LiNiO patterning by HSQ lift-off method. (d) LiNiO patterning and passivation by SiN mixed etching method                                                                                                                                                                                                                                                                                                                                                                                              |

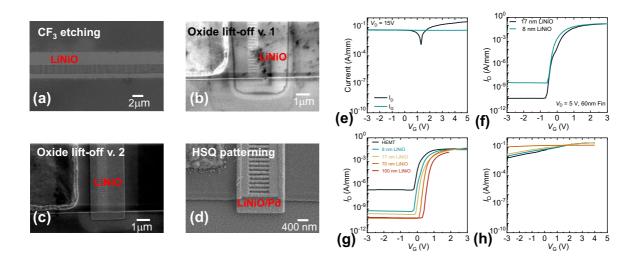

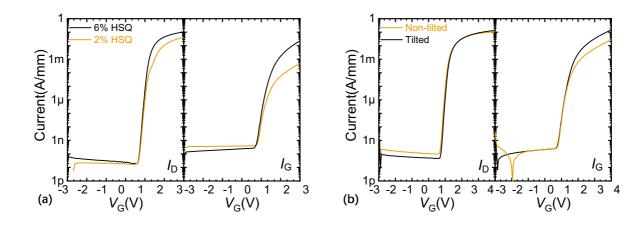

| Figure 3-10 (a) SEM image of gate region after LiNiO etching by carbon/oxygen method. (b) SEM image of gate region after LiNiO etching by oxide lift-off method with CHF <sub>3</sub> during the opening. (c) SEM image of gate region after LiNiO etching by oxide lift-off method with IBE during the opening. (d) SEM image of gate region after LiNiO etching by HSQ lift-off method. (e) transfer performance of the device by carbon/oxygen method. (f) transfer performance of the device by oxide lift-off method (CHF <sub>3</sub> RIE based). (g) transfer performance of the device by oxide lift-off method (IBE-based) (h) transfer performance of the device by HSQ lift-off method. |

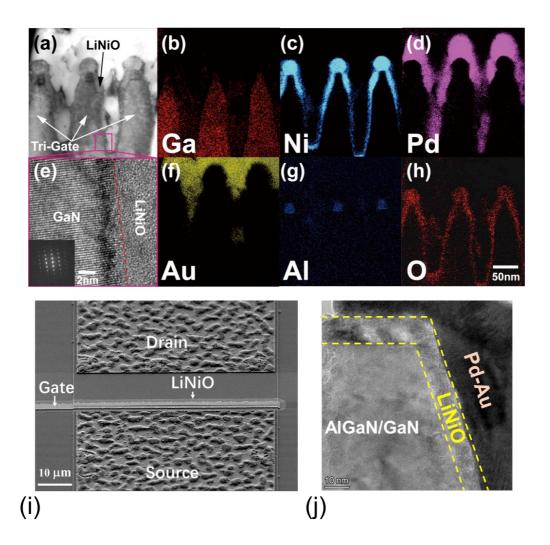

| Figure 3-11 (a) Cross-sectional high-angle annular dark field (HADDF) scanning transmission electron microscope (STEM) image. (b)(c)(d)(f)(g)(h) cross-sectional energy dispersive X-ray spectroscopy (EDS) mapping analysis of the LiNiO film on AlGaN/GaN tri-gate structure. (e) high-resolution transmission electron microscope (TEM) of LiNiO/GaN sidewall interface                                                                                                                                                                                                                                                                                                                         |

| MOSHEMT with LiNiO gate dielectric. (j) cross-sectional HRTEM image at the top of the fin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| region, good coverage can be observed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

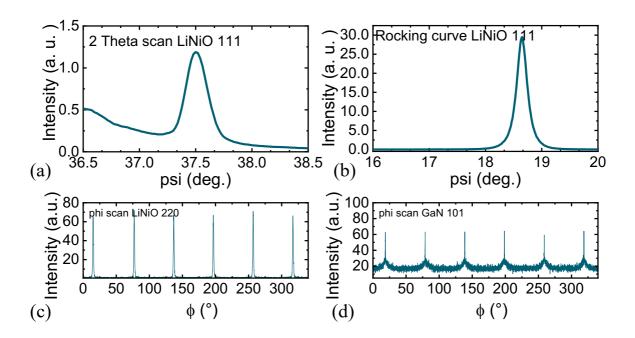

| Figure 3-12 X-ray diffraction patterns of LiNiO on AlGaN/GaN/Si substrate. (a) θ-2θ scan and (b) rocking curve of LiNiO (111). Φ-scan on (c) LiNiO (220) and (d) GaN (101)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

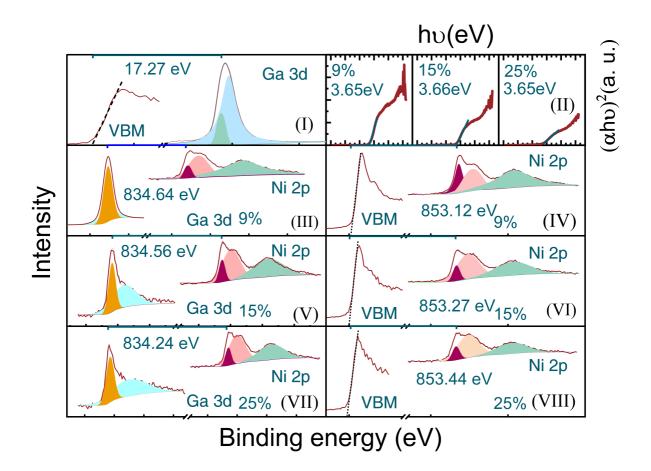

| Figure 3-13 X-ray photoelectron spectroscopy (XPS): (I) valence band and Ga 3d core level spectra for AlGaN/GaN. (III)(V)(VII) core level spectra of Ga 3d and Ni 2p from ~3nm thick 9%, 15%, 25% Li doped NiO on AlGaN/GaN. (IV)(VI)(VIII) Ni 2p core level spectra and valence band for ~60nm thick 9%, 15%, 25% Li doped NiO on AlGaN/GaN. (II) (αhv)² versus hv optical transmission spectra plot from ultraviolet-visible spectroscopy (UV-Vis) for different Li doping concentration LiNiO film on fused silica                                                                                                                                                                                                                                                                                                                                                        |

| with LiNiO with Li concentrations of 9%, 15%, and 25% and Pd/Au gate. Inset: schematic of gated hall structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

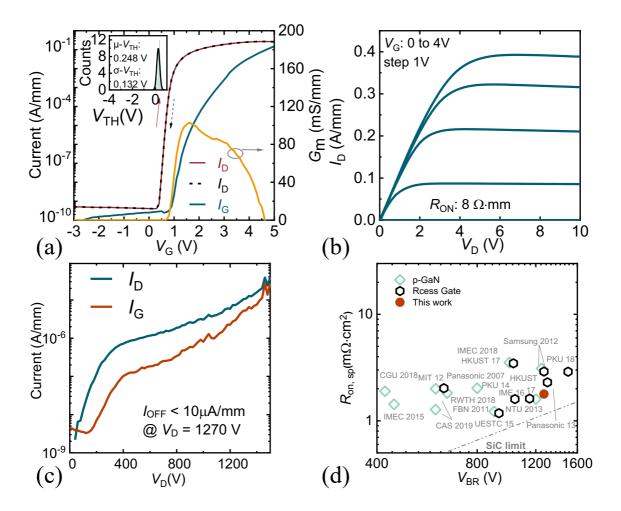

| Figure 3-15 (a) Transfer ( $V_D = 5$ V) inset: histograms of $V_{TH}$ distribution among 33 devices ( $W_{Fin} = 40$ nm, 9% Li doping LiNiO gate, and $V_{TH}$ is defined at $I_D = 1$ $\mu A/mm$ ). (b) Output characteristics of LiNiO tri-gate. $R_{ON}$ is extracted from linear fitting of $I_D$ at $V_G = 4$ V and $V_D = 1$ V. (d) Three terminal breakdown characteristics of the device at $V_G = 0$ V (under floating substrate with fluorinert). (d) $R_{On, sp}$ versus $V_{BR}$ by defining $V_{BR}$ at $I_{OFF} \le 10$ $\mu A/mm$ , for recess gate, floating substrate result was shown for a fair comparison. $R_{On, sp}$ was calculated considering a 1.5 $\mu$ m of transfer length for each ohmic contact was taken into account for $R_{On, sp}$ calculation. The $V_{BR}$ results in the literature were re-calculated by $I_{OFF} \le 10$ $\mu$ A/mm |

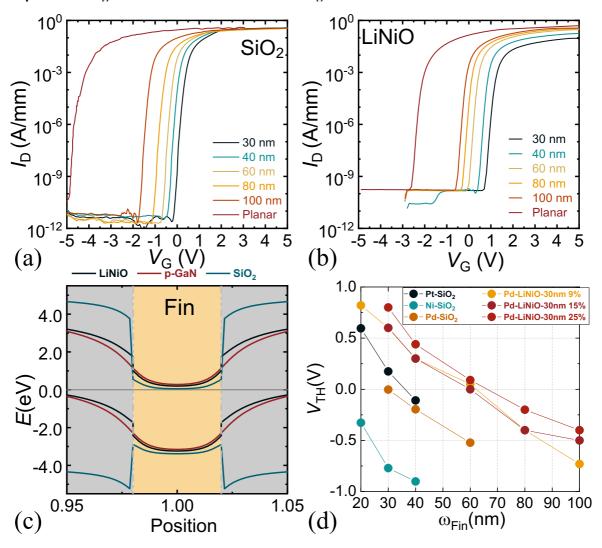

| Figure 3-16 Transfer characteristics of different tri-gate fin widths with (a) SiO <sub>2</sub> (Pt gate) and (b) LiNiO (Pd gate) oxide. (c) Simulated band diagram along the fin width direction, at the interface between AlGaN and GaN. Three different gate dielectrics (junction) were used: SiO <sub>2</sub> , LiNiO, p-GaN $V_{\rm G}$ , and $V_{\rm Sub.}$ = 0 V. (d) $V_{\rm TH}$ (defined at 1 $\mu$ A/mm) as a function of $W_{\rm Fin}$ and gate stack, in LiNiO all three doping concentration films are deposited at the same thickness of 30 nm.                                                                                                                                                                                                                                                                                                              |

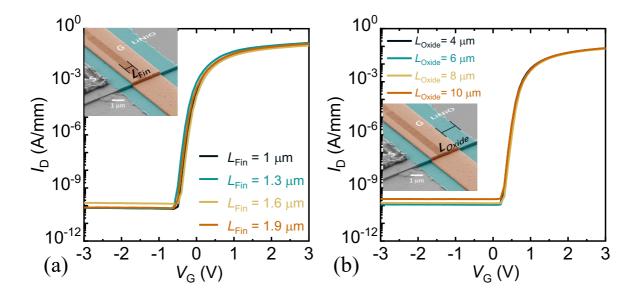

| Figure 3-17 (a) Transfer characteristic for different $L_{\text{Fin}}$ , devices deposited 9% doped LiNiO, measured at $V_{\text{D}} = 5 \text{ V}$ , $W_{\text{Fin}}$ is fixed at 60nm, and $L_{\text{Oxide}}$ is 4 µm (b) Transfer characteristic for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| different $L_{\text{Oxide}}$ , devices deposited 9% doped LiNiO, measured at $V_{\text{D}} = 5 \text{ V}$ , $W_{\text{Fin}}$ is fixed a                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60nm, and $L_{\text{Fin}}$ is 1 $\mu$ m.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

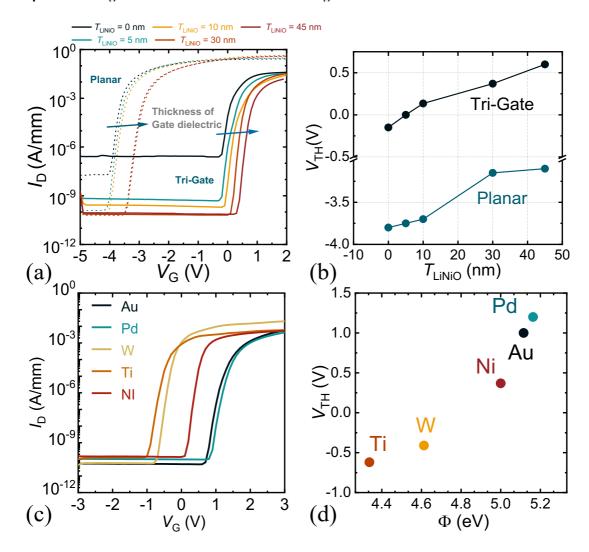

| Figure 3-18 (a) Transfer behavior of different $T_{\rm LiNiO}$ devices, both planar and tri-gate devices were fabricated to compare. Devices include 9% doped LiNiO, measured at $V_{\rm D} = 5$ V, $W_{\rm Fin}$ is fixed at 40nm. (b) $V_{\rm TH}$ (defined at 1 $\mu$ A/mm) as a function of $T_{\rm LiNiO}$ . (c) Transfer behavior of different gate metals measured at $V_{\rm D} = 5$ V, $W_{\rm Fin}$ is fixed at 30nm. (d) $V_{\rm TH}$ as a function of gate metal work function. |

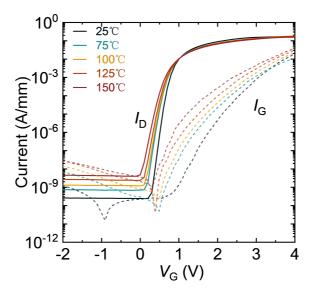

| Figure 3-19 Transfer characteristics of the device with measurement temperature from 25 $^{\circ}$ C to 150 $^{\circ}$ C ( $W_{\text{Fin}} = 40 \text{ nm}$ )                                                                                                                                                                                                                                                                                                                               |

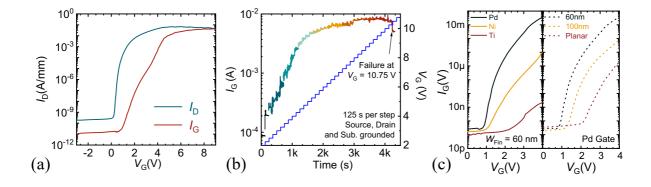

| Figure 3-20 (a) Transfer behavior of large $V_G$ sweep ( $V_D = 10 \text{ V}$ ). (b) Results of a step-stress test on the gate, by increasing positive gate bias levels. (c) Gate leakage characteristic of devices with different gate metal (left) on $W_{\text{Fin}} = 60 \text{ nm}$ , and with different $W_{\text{Fin}}$ (right) with Pd gate                                                                                                                                         |

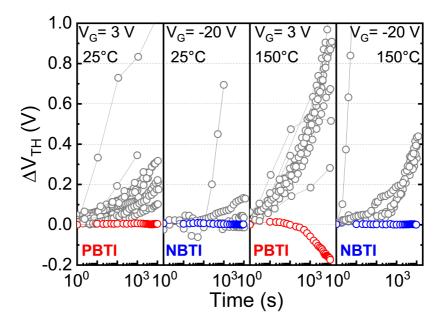

| Figure 3-21 (a) Transfer behavior during NBTI stress test. (b) Transfer behavior during PBT stress test $W_{\text{Fin}} = 40 \text{ nm}$ . (c) PBTI and NBTI test results [83, 103-115]                                                                                                                                                                                                                                                                                                     |

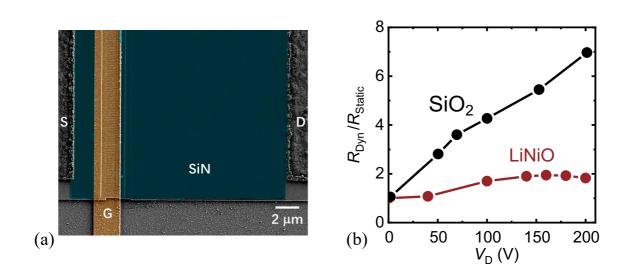

| Figure 3-22 (a)Top-view SEM image of LPCVD passivated SiN passivated LiNiO Tri-gate device. (b) Dynamic $R_{ON}$ increase ratio under different static drain bias stress ( $V_D$ ). Devices with LiNiO and SiO <sub>2</sub> gate stack were compared                                                                                                                                                                                                                                        |

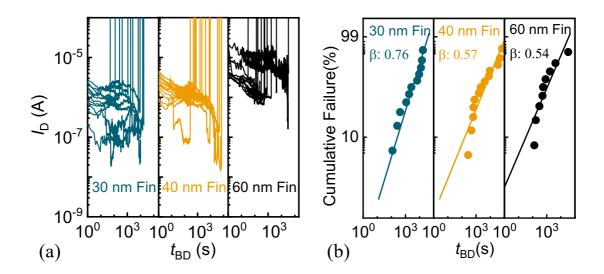

| Figure 3-23 (a) Constant voltage stress performed at ( $V_G = 0V$ , $V_D = 500V$ , and 150°C) on se of 12 identical devices, (b) Weibull distribution for three sets of devices                                                                                                                                                                                                                                                                                                             |

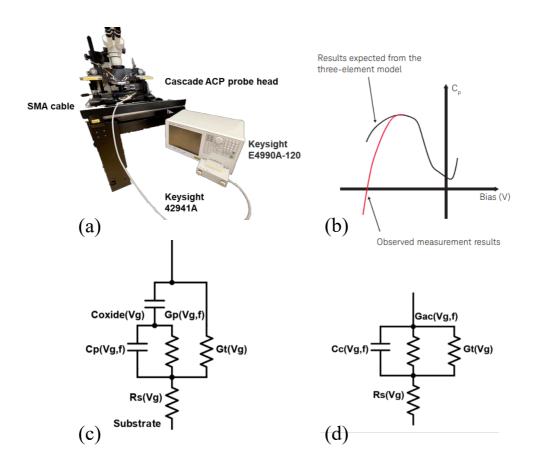

| Figure 3-24 (a) RF IV precise capacitance measurement setup, including cascade ACP probe head, Keysight 42941 A adapter, and Keysight E4990A-120 impedance analyzer. (b) negative capacitance behavior during leaky capacitor measurement [119]. (c) C&G model of LiNiO/AlGaN planar junction capacitor device. (d) simplify C&G model of LiNiO/AlGaN planar junction capacitor device.                                                                                                     |

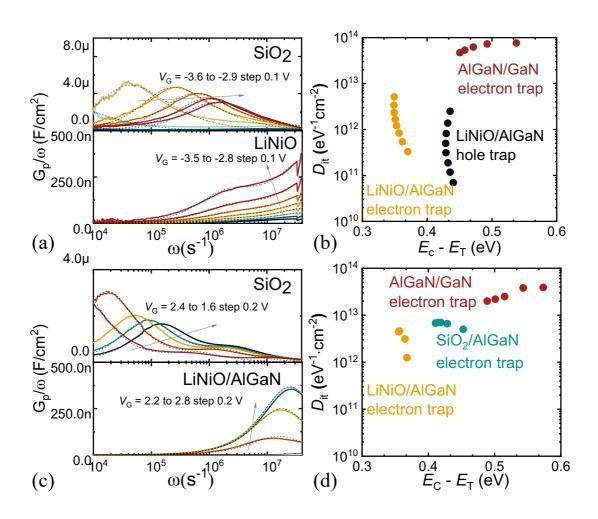

| Figure 3-25 Two methods of interface quality characterization through conductance dispersion method: (a)(b) results from the first plateau in CV curve. (c)(d) results from the second plateau in CV curve.                                                                                                                                                                                                                                                                                 |

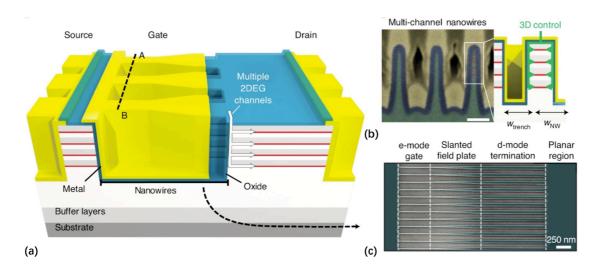

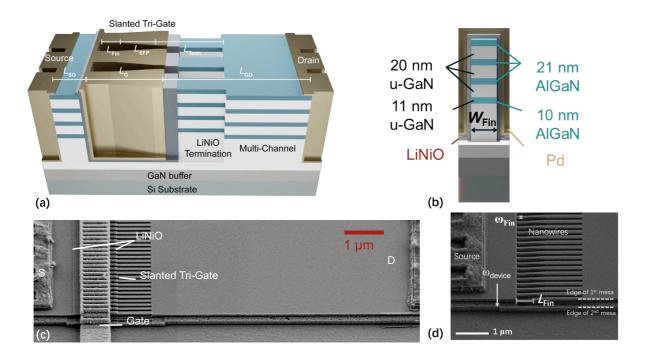

| Figure 4-1 Concept of multi-channel tri-gate devices. (a) Three-dimensional schematics of the proposed multi-channel device, featuring multiple parallel channels, to yield extremely low $R_{\text{ON}}$ , controlled 3-dimensionally by a tri-gate electrode. The tri-gate is terminated in the nanowire region, rather than on the planar region, to better distribute the electric field and result                                                                                     |

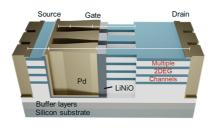

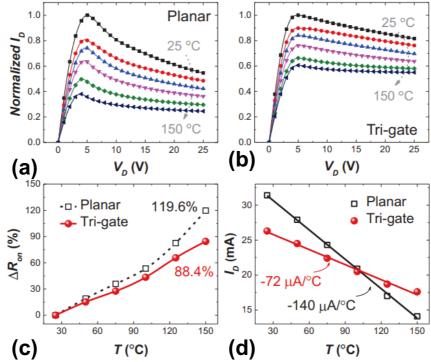

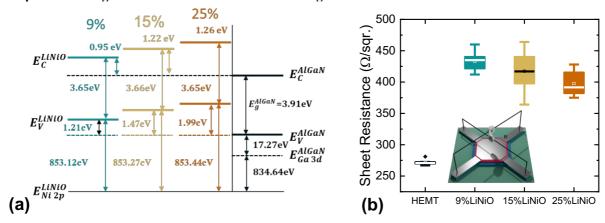

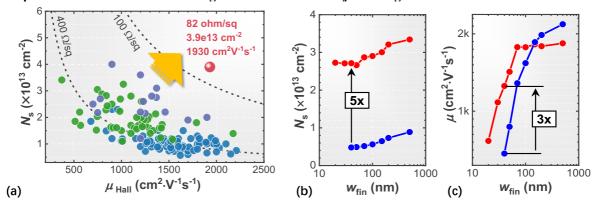

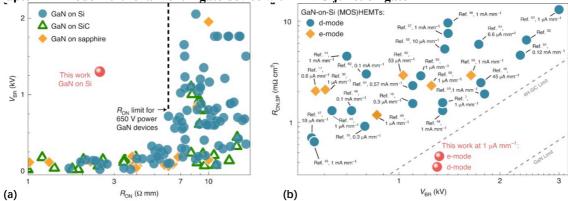

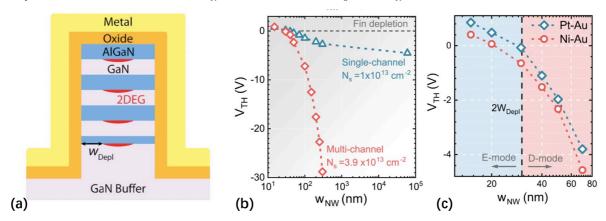

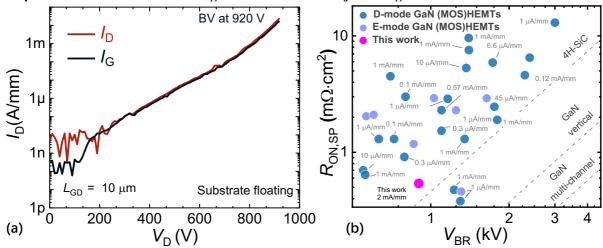

in high  $V_{\rm BR}$ . (b) FIB cross-section and schematics of the multi-channel nanowires covered by the tri-gate structure along the AB line in figure (a). The tri-gate enables simultaneous 3D control over all the multiple channels in the nanowire. The scale bar is 100 nm. (c) Top SEM image of the nanostructured gate area (before the gate oxide and electrode deposition) [73]. 81 Figure 4-2 (a) Benchmark of the sheet resistance  $(R_S)$  of the 4-channel heterostructure in this work against conventional single-channel GaN-based heterostructures in the literature, with AlGaN, InAlN, and AlN barriers. High  $\mu$  of 1930 cm<sup>2</sup>·V<sup>-1</sup>s<sup>-1</sup> was achieved in combination with a large  $N_s$  of 3.9 x 10<sup>13</sup> cm<sup>-2</sup>, resulting in  $R_s$  of 83  $\Omega/sq$ . (b)(c)  $N_s$  and  $\mu$  for multi-channel nanowires (red) and single-channel nanowires (blue) with different widths, measured by Hall Bars at room temperature. High  $\mu$  above 1800 cm<sup>2</sup>·V<sup>-1</sup>s<sup>-1</sup> was maintained down to 70 nm-wide nanowires along with a large  $N_s$ , in the range of  $2.8 - 3 \times 10^{13}$  cm<sup>-2</sup>. The multiple channels are defined into Tri-gate fin structure in the gate region of the device (Figure 4-1), threedimensional MOS gate was formed to control the parallel channels from the side gate and top gate. In the Tri-gate fin design, a slanted tri-gate fin was used to regulate the electric fields to high a high  $V_{\rm BR}$ . From the multi-channel tri-gate device a very high FOM was successfully demonstrated which surpassed the state-of-the-art result, offering a promising way for future Figure 4-3 (a)  $V_{\rm BR}$  versus  $R_{\rm ON}$  and (d)  $R_{\rm ON, SP}$  versus  $V_{\rm BR}$  benchmarks of the slanted tri-gate multi-channel MOSHEMTs against conventional single-channel GaN (MOS)HEMTs in the literature. Multi-channel devices surpass the material figure-of-merit limit of 4H-SiC, showing a substantial improvement with respect to single-channel devices and a record figure-of-merit of 4.6 GW/cm<sup>2</sup> for d-mode devices and 3.8 GW/cm<sup>2</sup> for e-mode devices. A transfer length of 1 Figure 4-4 (a) The depletion width indicates the minimum nanowire width to achieve e-mode operation since for  $W_{\text{NW}} < 2$   $W_{\text{Depl}}$  the depletion regions from the two sidewalls merge in the center and eliminate the 2DEG. (b) It should be noted that while in general a much higher gate voltage is required to turn off a multi-channel nanowire with respect to a single-channel one due to its larger carrier density, for small nanowire widths such difference becomes smaller and multi-channel devices show very similar  $V_{\rm TH}$  with respect to single-channel counterpart for  $W_{\rm NW}$  below 50 nm, despite the much larger  $N_{\rm s}$ . This is due to the predominant side gate control and to the strong sidewall depletion at such narrow widths, which is similar for multi- and single-channel nanowires. (c) The evaluation of the sidewalls depletion width is consistent with the device transfer curves, which indicate 30 nm as the minimum nanowire width to achieve positive  $V_{TH}$ . To further shift  $V_{TH}$  to positive values, the conventional Ni-Au gate metal stack

| was replaced by a Pt-Au gate metal, which resulted in a threshold voltage increase of about $0.\overline{5}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V. Such improvement, which is consistent for different $W_{\rm NW}$ , derives from the higher work-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| function of Pt with respect to Ni and allows to increase $V_{\mathrm{TH}}$ without any degradation of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| channel, resulting in large $V_{\text{TH}}$ of 0.85 V for 15 nm-wide nanowires [73]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4-5 (a) 3D schematic of fabricated multi-channel tri-gate HEMT with LiNiO gate oxide, featuring four parallel channels. In the slanted tri-gate region, the Gate metal and LiNiO gate oxide both terminated in the nanowire region. (b) cross-section schematic of single tri-gate structure covered with LiNiO gate oxide and Pd gate metal. (c) Tilted top-view SEM image of the fabricated device, a second mesa structure, and precise pattern LiNiO are included. (d) Tilted top-view SEM image of the device before LiNiO patterning and gate. A clear shrink design of the second mesa can be observed from the image. Apart from the second mesa, sharp results of slanted tri-gate Fin can also be observed. From tilted view. The narrow region of nanowires has the same height as other parts, the AlGaN barrier didn't consumed during the |

| dry etching process of the Fin. 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

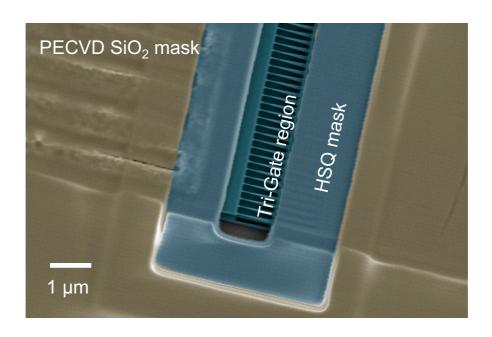

| Figure 4-6 Top-view SEM image of additional HSQ mask before LiNiO deposition. HSQ mask and PECVD mask can be observed from the image. Slanted tri-gate and second mesa were also shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

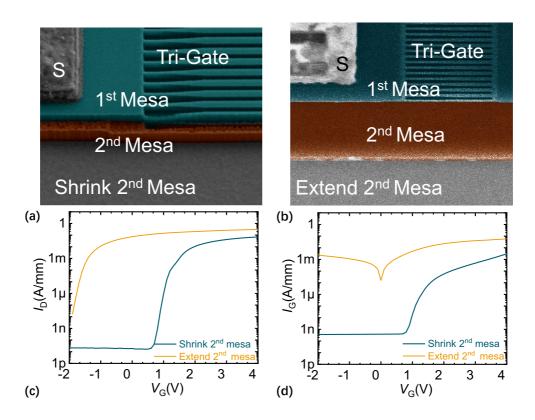

| Figure 4-7 (a) Tilted top-view SEM image of shrink second mesa process. (b) Tilted top-view SEM image of extend second mesa process. (c) $I_D$ versus $V_G$ of shrink and extend the second mesa. (d) $I_G$ versus $V_G$ of shrink and extend the second mesa. 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

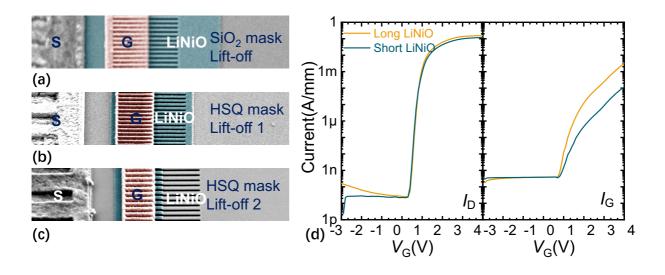

| Figure 4-8 (a) Fabricated device with PECVD SiO <sub>2</sub> lift-off mask patterned LiNiO. (b) Fabricated device with additional HSQ patterned LiNiO. LiNiO terminated outside of the Fin. (c) Fabricated device with additional HSQ pattern LiNiO, LiNiO terminated on the Fin. (d) Transfer behavior of two LiNiO termination devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4-9 (a) Comparison of transfer behavior with two different thicknesses HSQ used for tri-gate nanowire patterning. (b) Comparison of transfer behavior tilted and non-tilted deposition during the PLD deposition process of LiNiO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

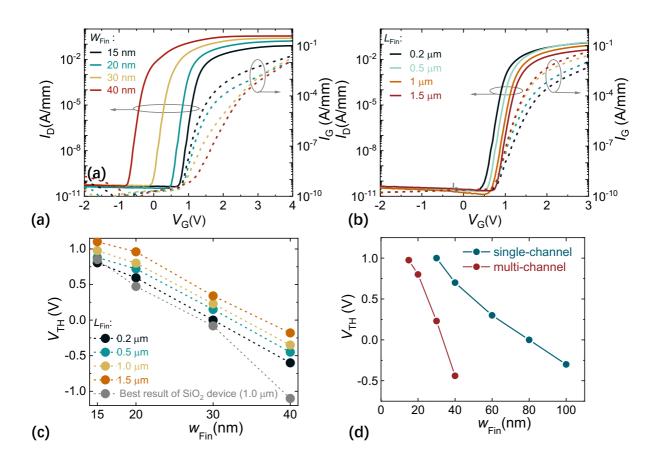

| Figure 4-10 (a) Transfer ( $V_D = 5 \text{ V}$ ) characteristics of multi-channel tri-gate HEMT with LiNiO. Different tri-gate Fin width ( $W_{\text{Fin}}$ ) devices are included, the length of Fin ( $L_{\text{Fin}}$ ) was set to 1 $\mu$ m. (b) Transfer ( $V_D = 5 \text{ V}$ ) characteristics of multi-channel tri-gate HEMT with LiNiO. Different Tri-gate Fin length ( $L_{\text{Fin}}$ ) devices are included, the width of Fin ( $W_{\text{Fin}}$ ) was set to 15 nm. (c) $V_{\text{TH}}$ (defined at 1 $\mu$ A/mm) versus $W_{\text{Fin}}$ and $L_{\text{Fin}}$ , compare to the most positive $V_{\text{TH}}$ ever achieved on                                                                                                                                                                                                                   |

| the same epitaxy, with different gate oxide and metal. Using LiNiO/Pd gate combination results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| in a nearly 0.5 V $V_{\text{TH}}$ shift towards positive in small $W_{\text{Fin}} \le 30$ nm and shift nearly 1 V at $W_{\text{Fin}} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 nm. (d) $V_{\rm TH}$ dependence of $W_{\rm Fin}$ of single-channel and multi-channel LiNiO junction gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

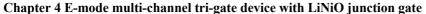

| Figure 4-11 (a) Output characteristic of different $W_{\text{Fin}}$ , the $L_{\text{Fin}}$ was set to 1.0 µm. (b) $R_{\text{ON}}$ (extracted at $V_{\text{G}}$ of 4 V) and $I_{\text{D, max}}$ versus $W_{\text{Fin}}$ . (c) $R_{\text{ON}}$ versus $V_{\text{TH}}$ benchmark for presented device compared state-of-the-art single-channel e-mode devices through p-GaN gate and gate recess methods from the literature. Multi-channel devices present a more than two times lower $R_{\text{ON}}$ for the same $V_{\text{TH}}$ with respect to the reported p-GaN gate e-mode devices, and most gate recess e-mode devices. $V_{\text{TH}}$ has been defined at 1 µA/mm. Recess gate devices always drive at a much higher $V_{\text{G}}$                           |

| Figure 4-12 (a) Three terminal breakdown characteristics of the device ( $W_{\rm Fin}$ = 20 nm, $L_{\rm Fin}$ = 1.0 µm) at $V_{\rm G}$ = 0 V (under floating substrate with fluorinert). (b) $R_{\rm ON,SP}$ versus $V_{\rm BR}$ benchmarks of the LiNiO multi-channel junction gate transistor against conventional single-channel GaN (MOS)HEMTs in the literature. It shows a very high figure-of-merit of 1.63 GW/cm <sup>2</sup> . A transfer length of 1 µm from each side has been considered to evaluate $R_{\rm ON,SP}$ . This is the highest FOM ever achieved on junction gate type GaN HEMT device, and only worse than the multi-channel                                                                                                                  |

| MOSHETM from our previous work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

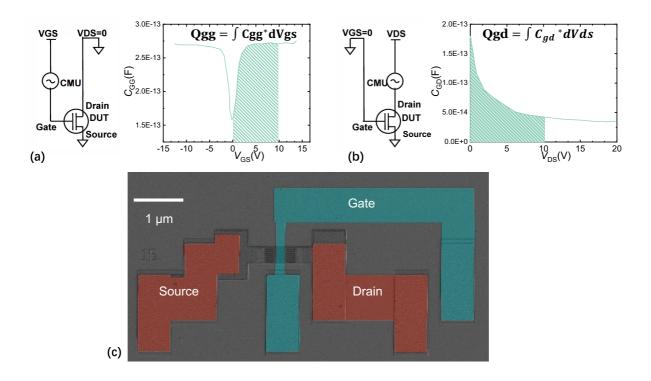

| Figure 4-13 CV integration method for measuring gate charge. (a) Plot shows the gate charge component ( $Q$ gg). The $Q$ gg is the integration of the shadow part in the curve. (b) Plot shows the gate charge component ( $Q$ gd). The $Q$ gd g is the integration of the shadow part in the curve. (c) top-view SEM image of long $L$ Fin (10 $\mu$ m) for accurate capacitance measurement                                                                                                                                                                                                                                                                                                                                                                          |

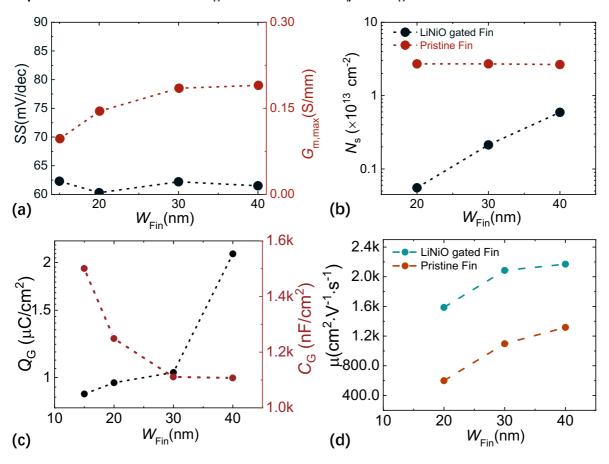

| Figure 4-14 (a) SS and maximum transconductance $(G_{\rm m, max})$ versus $W_{\rm Fin}$ . (b) Carrier density $(N_{\rm s})$ of pristine tri-gate Fin without gate oxide and device LiNiO gate stack (normalized on total top surface areas of Fins) versus $W_{\rm Fin}$ . Over 1 order of Ns was reduced by LiNiO gate stack. Ns in pristine Fin was extracted by hall measurement, details can be found in [73]. And Ns in LiNiO gate stack was extracted by CV measurement on large gate length $(L_{\rm G})$ device, details in [127]. (c) $Q_{\rm G}$ (integrated till 0 V) and $C_{\rm G}$ ( $V_{\rm G}=2$ V) dependence on $W_{\rm Fin}$ . (d) Field-effect mobility of LiNiO gated Fin and tri-gate nanowire without any process dependence on $W_{\rm Fin}$ . |

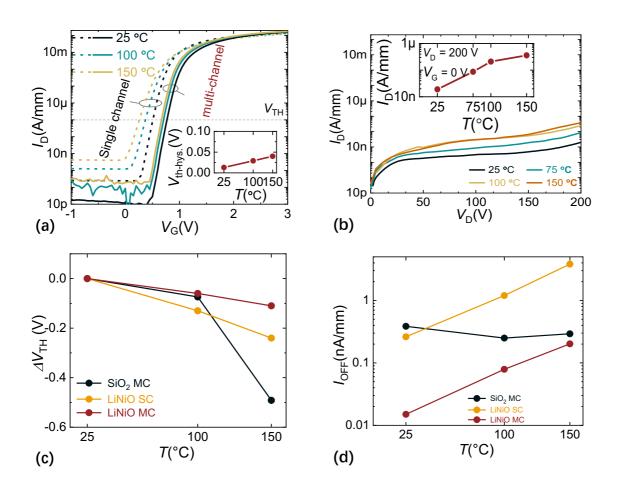

| Figure 4-15 (a) Temperature-dependent transfer characteristics of multi-channel ( $W_{\text{Fin}} = 20 \text{ nm}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and reference single-channel device ( $W_{\text{Fin}} = 40 \text{ nm}$ ) with measurement temperature from 25 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| to 150 °C, inset presents the $V_{TH}$ hysteresis (defined at 1 $\mu$ A/mm) of multi-channel device from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| a double sweep. (b) Temperature-dependent off-state leakage measurement with measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| temperature from 25 $^{\circ}$ C to 150 $^{\circ}$ C. $V_G$ was set at 0V with floating substrate, and fluorinert was    |

|--------------------------------------------------------------------------------------------------------------------------|

| used. Inset: $I_D$ ( $V_D = 200$ V) versus temperature. (c) Dependence of $V_{TH}$ and $I_{OFF}$ of the SiO <sub>2</sub> |

| MOS gate multi-channel device, LiNiO junction gate single-channel device, and LiNiO                                      |

| junction gate multi-channel device on the temperature. (d) Dependence of $I_{\rm OFF}$ of the SiO <sub>2</sub> MOS       |

| $gate\ multi-channel\ device,\ LiNiO\ junction\ gate\ single-channel\ device,\ and\ LiNiO\ junction\ gate$               |

| multi-channel device on the temperature95                                                                                |

| Figure 5-1 (a) Schematic of AlGaN/GaN HEMT intergrated with Si Schottky diode, ultilized                                 |

| the Si substrate and TSV technology [16]. (b) Schematic of monolithic integration of planar                              |

| MOSHEMT with Schottky diode [137]. (c) Schematic of monolithic integration of MOSHEMT                                    |

| and Schottky diode ultilizing double channel epitaxy [138]                                                               |

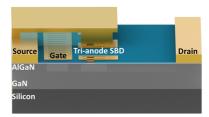

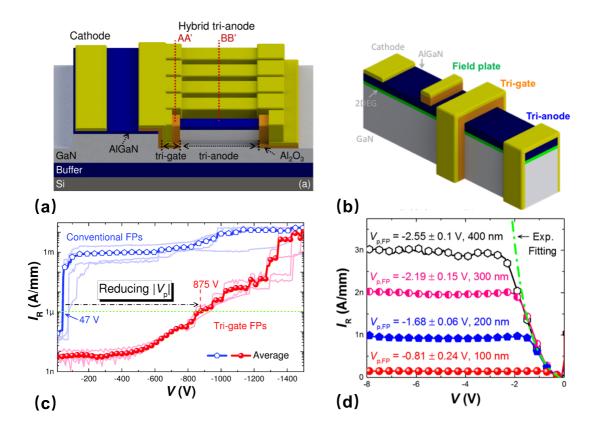

| Figure 5-2 (a) (c) Schematic of Tri-Anode Schottky diode, and breakdown behavior over                                    |

| normal SBD. (b) Shematic of single Tri-Anode Fin, and (d) off-state leakage and flat band                                |

| voltage versus different Tri-Anode fin width                                                                             |

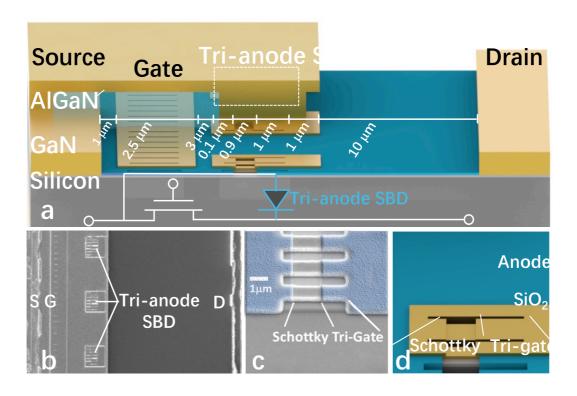

| Figure 5-3 (a) Schematic and (b) top-view SEM image of the RC-MOSHEMT, (c) zoomed-in                                     |

| SEM image after Schottky contact opening and (d) schematic of tri-anode region                                           |

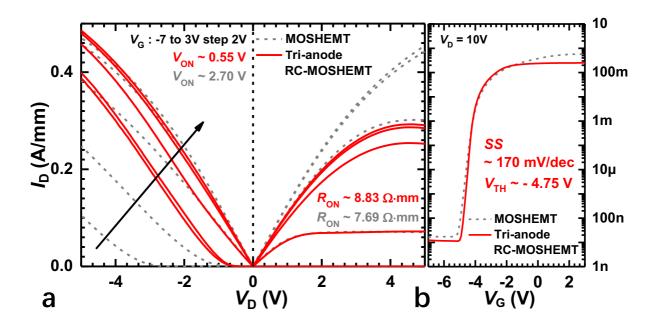

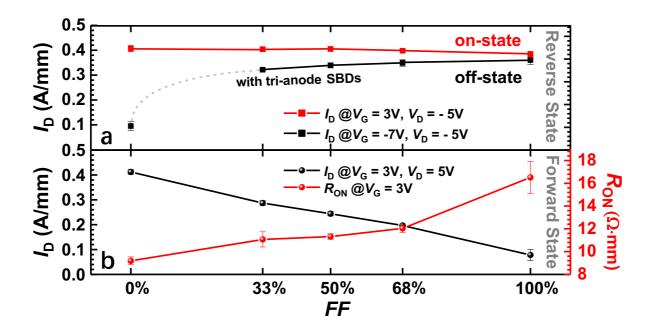

| Figure 5-4 (a) Output and (b) transfer characteristics of the tri-anode RC-MOSHEMT and                                   |

| MOSHEMT, normalized by the width of the device footprint                                                                 |

| Figure 5-5 (a) Reverse and (b) forward characteristics of the tri-anode RC-MOSHEMT versus                                |

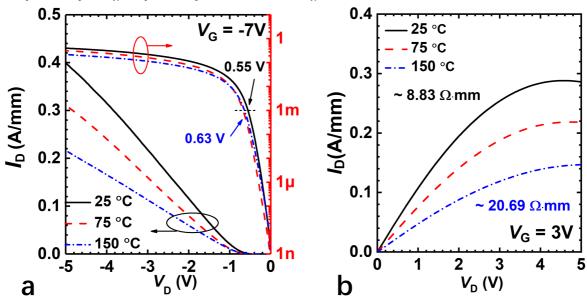

| different filling factor (FF)                                                                                            |

| Figure 5-6 Temperature-dependent (a) reverse and (b) forward output characteristics of the tri-                          |

| anode RC-MOSHEMT at 25 $^{\circ}\mathrm{C}$ , 75 $^{\circ}\mathrm{C}$ and 150 $^{\circ}\mathrm{C}$                       |

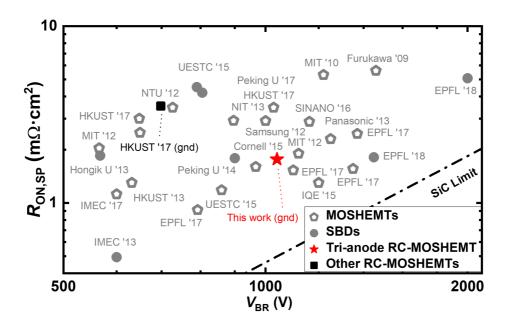

| Figure 5-7 Breakdown characteristics of the tri-anode RC-MOSHEMT and MOSHEMT with                                        |

| grounded substrate (gnd) and floating substrate (float)                                                                  |

| Figure 5-8 $R_{\rm ON, SP}$ versus $V_{\rm BR}$ benchmark of the tri-anode RC-MOSHEMT with against GaN-                  |

| on-Si power MOSHEMTs and lateral SBDs. A 1.5 $\mu m$ transfer length of source/drain was                                 |

| considered for the calculation of $R_{\rm ON, SP}$                                                                       |

## List of Tables

| Table 1-1, Comparison of Si, SiC, and GaN physical properties [3, 4]               | 24 |

|------------------------------------------------------------------------------------|----|

| Table 1-2 Substrate cost for different power devices [6].                          | 25 |

| Table 3-1 Comparison recent commercial GaN devices [62].                           | 47 |

| Table 3-2 Physical properties of various nickel compounds [84].                    | 55 |

| Table 3-3 Comparison of reported high-performance e-mode tri-gate AlGaN/GaN HEMTs. | 79 |

| Table 5-1 Comparison of the RC-MOSHEMT with other reverse-conduction transistors 1 | 05 |

Power electronic devices can control energy conversion by changing current, voltage, or frequency. Due to the rapid development of high-speed trains, electric or hybrid vehicles (EV &HV), and next generation communication technologies and smart devices, power electronics has gradually become an important technology in the era of solid-state electronics. The ability to control or convert higher electrical power and faster operating speed is a key requirement for power electronic devices. Looking at the size of the power electronics market, data for 2019 shows a market of \$17.1 billion accounted for by various forms of power electronics devices (Figure 1-1)[1].

Figure 1-1 The power market share of different categories of power electronic devices [1].

Power electronic devices include transistors, diodes, and thyristors with various functions. Silicon-based (Si) devices continue to dominate today's power electronic device market. However, after several decades of development, the Si power device has reached its limits due to the material limitations of Si. The low operating frequency and low critical electric field of Si lead to large size of Si power devices and bulky circuit design based on Si power devices. It is a challenge for Si power devices to meet the requirements of the growing demand for fast, compact, and ultra-high power density conversion systems.

On the other hand, gallium nitride (GaN) is fast becoming a popular material for next-generation power electronics. This is due to its superior material properties and the availability of low-cost, large-size GaN-on-Si or GaN-on-SiC wafers, which is benefited from mass investment in the light-emitting diode (LED) industry. GaN has been widely and rapidly adopted in consumer electronics, base station components RF and military RF /microwave applications.

In the following sections, we first review the history of GaN lateral device development and introduce the advantages of GaN as a power electronic material as well as its lateral structure over other structures or materials. Then, we discuss the key requirements and challenges of GaN devices for the next generation of power electronic devices before we propose the methods to meet these requirements for future GaN power electronics.

#### 1.1 GaN is an excellent material for power application.