# Enhancement-mode Multi-channel AlGaN/GaN Transistors with LiNiO Junction Tri-Gate

Taifang Wang, Yuan Zong, Luca Nela, and Elison Matioli, Senior Member, IEEE

Abstract - Multi-channel GaN power device, consisting of stacking multiple two-dimensional-electron-gas (2DEG) channels, has been demonstrated to achieve unprecedented on-state performance while maintaining high breakdown voltage ( $V_{\rm BR}$ ). However, the large carrier density (Ns) makes it more challenging to achieve high positive threshold voltages (V<sub>TH</sub>) on multi-channel epitaxies. In this work, we demonstrate enhancement-mode (e-mode) multi-channel GaN transistors based on conformally deposited p-type LiNiO over tri-gates to form a multi-channel junction gate structure. Compared to the normal MOS gate, the p-type LiNiO junction gate provides an additional depletion of the channels to yield a more positive  $V_{\text{TH}}$ , reaching a maximum V<sub>TH</sub> of 1.2 V (defined at 1 µA/mm). Moreover, high-quality LiNiO provided excellent on-state performance in multichannel tri-gate devices with a stable operation at high temperature, which present small V<sub>TH</sub> shift and hysteresis, and low off-state leakage current. The e-mode devices in this work presented a small specific  $R_{\rm ON}$  ( $R_{\rm ON, sp}$ ) of 0.62 m $\Omega \cdot \rm cm^{-2}$  along with a hard breakdown voltage (V<sub>BR</sub>) of 920 V. This work demonstrates the potential of LiNiO for high-performance e-mode power devices.

*Index Terms* – GaN, HEMT, Enhancement-mode, LiNiO, Tri-Gate, Multi-channel.

### I. INTRODUCTION

aN-based multi-channel tri-gate MOSHEMTs have been T demonstrated as a very promising technology for future high-performance power transistors for low/medium voltage rating applications [1-5]. The multiple vertically stacked 2DEG channels offer a way to break the trade-off between  $N_{\rm S}$  and mobility  $(\mu)$ . An excellent gate control and modulation of the multiple channels was demonstrated by tri-gate structures, resulting in a significant reduction of the device  $R_{ON}$ , without sacrificing  $V_{BR}$  [1, 2]. However, achieving e-mode operation with large  $V_{\text{TH}}$  is still very challenging in such high  $N_{\text{S}}$ structures. MOS tri-gate, which rely on sidewall depletion to pinch-off the multiple 2DEGs in the gate region, have achieved e-mode operation with  $V_{\text{TH}}$  of ~0.9 V (defined at 1  $\mu$ A/mm) [1, 2]. However, the use of gate dielectrics, such as SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, poses serious drawbacks in terms of  $V_{\rm TH}$  stability and reliability. This is due to their relatively low quality as these materials are typically deposited by low-temperature atomic layer deposition

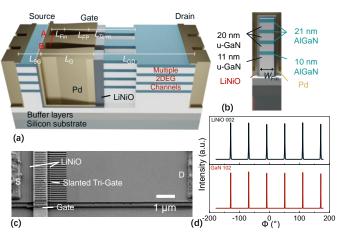

Fig. 1. (a) 3D schematic of multi-channel tri-gate HEMT with LiNiO junction gate, featuring four parallel channels. In slanted tri-gate field-plate region, the gate metal and LiNiO layer both are terminated in the nanowire region. (b) cross-section schematic of single tri-gate structure covered with LiNiO layer and Pd gate metal along the line AB in (a). (c) Tilted top-view SEM image of the fabricated device, a second mesa structure and precise pattern LiNiO are included. (d) XRD  $\Phi$  scan on LiNiO on AlGaN/GaN planar sample, patterns take on LiNiO (002) and GaN (1012) crystal planes, an epitaxial relationship of LiNiO (111)[110]//GaN(0002)[1120] could be determined.

(ALD) and plasma-enhanced chemical vapor deposition (PECVD). On the other hand, the high deposition temperature required for high-quality dielectrics may degrade the etched GaN surface, which can be particularly damaging for tri-gate structures [3, 6, 7]. Today, the most reliable technology to achieve e-mode is based on the p-(Al)GaN gate, which lifts the conduction band of the GaN channel to locally deplete the 2DEG [8-10]. Nevertheless, applying this technology to multichannel tri-gate structures is very challenging, due to the difficulty of p-(Al)GaN regrowth control over the nanoscale structure in tri-gates, and GaN surface degradation at the high growth temperature. Recently p-type NiO<sub>x</sub> [11, 12] and LiNiO [11] have been demonstrated for e-mode operation in singlechannel tri-gate structures. In particular, the LiNiO offers a significant advantage due to the small band offset to AlGaN, hole concentrations that can be tuned from  $1 \times 10^{16}$  cm<sup>-3</sup> to  $6 \times 10^{21}$  cm<sup>-3</sup>, and a low deposition temperature of 400 °C [13, 14]. In this work, we demonstrate the e-mode multi-channel junction tri-gate AlGaN/GaN HEMTs, by successfully integrating a high-quality low-temperature p-type LiNiO layer on a multi-channel tri-gate structure. The devices presented high performance with a positive and stable  $V_{\rm TH}$  at high temperatures.

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Corresponding authors: *Taifang Wang; Elison Matioli*. The authors are with the Power and Wide-band-gap Electronics Research Laboratory (POWERlab), École polytechnique fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland. (e-mail: <u>taifang.wang@epfl.ch</u>; <u>elison.matioli@epfl.ch</u>)

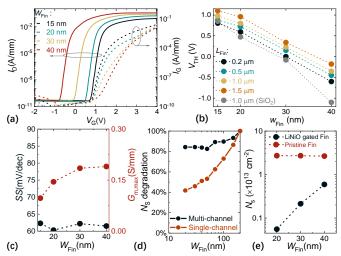

Fig. 2. (a) Transfer ( $V_D = 5$  V) characteristics of multi-channel junction tri-gate HEMT with LiNiO. Different tri-gate fin width ( $W_{\text{Fin}}$ ) devices are included, the length of fin ( $L_{\text{Fin}}$ ) was set to 1 µm. (b)  $V_{\text{TH}}$  (defined at 1 µA/mm) versus  $W_{\text{Fin}}$  and  $L_{\text{Fin}}$ , compare to most positive  $V_{\text{TH}}$  ever achieved on the same epitaxy, with different gate oxide and metal. Using LiNiO/Pd gate stack result in a nearly 0.5 V  $V_{\text{TH}}$  shift towards positive in small  $W_{\text{Fin}} \le 30$  nm and shift nearly 1 V at  $W_{\text{Fin}} =$ 40 nm. (c) SS and maximum transconductance ( $G_{\text{m, max}}$ ) versus  $W_{\text{Fin}}$ . (d) Carrier density ( $N_s$ ) degradation of pristine fin (without oxide and gate metal) with multichannel and single-channel epitaxy (relative to Ns for 200 nm wide fin). (e)  $N_s$  of pristine tri-gate fin and fins with LiNiO gate stack (normalized on total top surface areas of fins) versus  $W_{\text{Fin}}$ . Over 1 order of  $N_s$  was reduced by LiNiO junction gate.  $N_s$  in pristine fin was extracted by hall measurement, details can be found in [1]. And  $N_s$  in LiNiO junction gate were extracted by CV measurement on large gate length ( $L_G$ ) device, details in [4] ( $L_G = 10$  µm and  $V_G = 0$  V).

## II. DEVICE STRUCTURE AND FABRICATION

The epitaxial structure consisting of four AlGaN/GaN channels is the same as that described in Ref. [1], which presents a large Ns of  $3.9 \times 10^{13}$  cm<sup>-2</sup> and  $\mu$  of 1,930 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, resulting in a low sheet resistance ( $R_{\rm S}$ ) of 83  $\Omega$ ·sq<sup>-1</sup>. The device fabrication started with mesa isolation and the definition of the tri-gate fins by ebeam lithography (EBL). A 2 nm-thick Ti glue layer was used to enhance the Hydrogen silsesquioxane (HSO) adhesion to the GaN surface [15]. The mesa and fin structures were etched by Ar/Cl<sub>2</sub> inductively coupled plasma etching (ICP) with a depth of 250 nm. Four cycles of digital etching were used to remove sidewall damages during dry etching [1, 16]. To better isolate the device, a second mesa was patterned by a thicker HSQ layer (300 nm) and etched with a depth of 200 nm. The ohmic metal stack composed of Ti/Al/Ti/Ni/Au was defined in the source and drain regions, followed by rapid thermal annealing. A 250-nm-thick SiO<sub>2</sub> was deposited by PECVD as an etching stop layer (ESL) of ion beam etching (IBE) for the LiNiO patterning. To precisely define the LiNiO oxide layer in the gate region, a 180 nm thick HSQ layer was directly patterned by EBL exposure to serve as a lift-off mask. The LiNiO deposition was done by pulsed-laser-deposition (PLD) [14, 17] using a Li<sub>0.25</sub>Ni<sub>0.75</sub>O target at 400 °C with a thickness of 70 nm. The deposition was performed by laser ablation with a repetition rate of 5 Hz, and energy density of 400 mJ·cm<sup>-2</sup> with a 248 nm KrF laser. It was followed by IBE and BHF etching to lift-off LiNiO layer. Finally, the gate electrode was defined by EBL followed by deposition of the

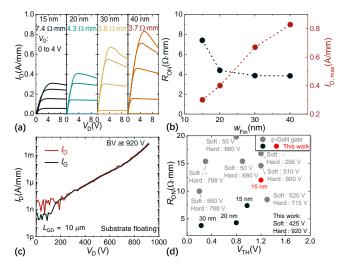

Fig. 3. (a) Output characteristic of different  $W_{\text{Fin}}$ , the  $L_{\text{Fin}}$  was set to 1 µm. (b)  $R_{\text{ON}}$  (extracted at  $V_{\text{G}}$  of 4 V) and  $I_{D, \text{max}}$  versus  $W_{\text{Fin}}$ . (c) three terminal breakdown characteristics of the device ( $W_{\text{Fin}} = 20 \text{ nm}$ ,  $L_{\text{Fin}} = 1.0 \text{ µm}$ ) at  $V_{\text{G}} = 0$  V (under floating substrate with fluorinert). (d)  $R_{\text{ON}}$  versus  $V_{\text{TH}}$  benchmark for presented device with state-of-the-art e-mode devices through p-GaN gate devices from the literature. Devices in this work present a much lower  $R_{\text{ON}}$  for the same  $V_{\text{TH}}$  with respect to the reported p-GaN gate e-mode devices, the reported hard and soft breakdown (at 1µA/mm) voltages are marked next to each point. Device with  $L_{\text{Fin}}$  of 1.5 µm and  $W_{\text{Fin}} = 15 \text{ nm}$  is marked red.

ohmic gate consisting of Pd/Au. Device performance was normalized by total device width of  $20\mu m$ .

## III. RESULTS AND DISCUSSION

Figure 1 (a) shows the schematic of the LiNiO junction trigate multi-channel HEMT [1]. The detailed multi-channel epitaxy and cross-section of the tri-gate fin structure are shown in Fig. 1(b). The device consisted of a source-gate distance ( $L_{SG}$ ) of 1 µm, gate-drain distance ( $L_{GD}$ ) of 10 µm, tri-gate slanted field plate length of 0.7 µm, LiNiO termination length ( $L_{Term}$ ) of 100 nm. The gate length ( $L_G$ ) is equal to the fin length ( $L_{Fin}$ ) plus 0.4 µm. Fig. 1 (c) shows the scanning electron microscopy (SEM) image of the fabricated device, where a precisely patterned LiNiO over the tri-gate can be observed. X-ray diffractometer (XRD)  $\Phi$ -scan taken on the (002) LiNiO and (1012) GaN crystal planes (on planar LiNiO on AlGaN/GaN sample) confirms the epitaxial relation between the high-quality rock-salt LiNiO on wurtzite AlGaN/GaN (Fig. 1 (d)) [13, 17].

The transfer characteristics of devices with different tri-gate fin widths ( $W_{\text{Fin}}$ ) and the same  $L_{\text{Fin}}$  of 1 µm are shown in Fig. 2 (a). The decrease of  $W_{\text{Fin}}$  results in fewer carriers in the channel, thus shifting  $V_{\text{TH}}$  towards positive values. E-mode operation ( $I_D = 1\mu A/\text{mm}$ ) was possible for all devices with  $W_{\text{Fin}}$  below 30 nm. The devices presented near-ideal SS of 61-63 mV/dec and an on/off ratio of over 9 orders of magnitude, which reveals the high-quality LiNiO and the excellent gate control of the tri-gate structure. All measurements in this work were normalized by the entire width of the device ( $W_D$ ). The  $I_G$  (for  $V_G > V_{\text{TH}}$ ) of devices with small  $W_{\text{Fin}}$  was larger compared to those with large  $W_{\text{Fin}}$  due to two reasons: first, the over etching of top AlGaN barrier, which is more prominent in small fin widths, especially at 15 nm. Second, the larger carrier depletion in smaller fins results in smaller turn-on voltage of gate diode.

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

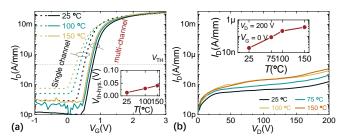

Fig. 4. (a) Temperature-dependent transfer characteristics of multi-channel ( $W_{\text{Fin}} = 20 \text{ nm}$ ) and reference single-channel device ( $W_{\text{Fin}} = 40 \text{ nm}$ ) with measurement temperature from 25 °C to 150 °C, inset presents the  $V_{\text{TH}}$  hysteresis (defined at 1  $\mu$ A/mm) of multi-channel device from double sweep. (b) Temperature-dependent off-state leakage measurement with measurement temperature from 25 °C to 150 °C.  $V_{\text{G}}$  was set at 0 V with floating substrate, and fluorinert was used. Inset:  $I_{\text{D}}$  ( $V_{\text{D}} = 200 \text{ V}$ ) versus temperature.

Figure. 2 (b) shows the increase in  $V_{\text{TH}}$  for longer  $L_{\text{Fin}}$  and narrower  $W_{\text{Fin}}$ . P-type LiNiO junction gate resulted in an over 0.5 V shift in  $V_{\text{TH}}$  compared with the most positive  $V_{\text{TH}}$  achieved on MOS multi-channel tri-gate structures with the same  $W_{\text{Fin}}$ . The maximum  $V_{\text{TH}}$  achieved on LiNiO multi-channel devices was 1.2 V (for  $W_{\text{Fin}}$  of 15 nm and  $L_{\text{Fin}}$  of 1.5 µm), which is very close to the theoretical prediction for e-mode tri-gate device [18]. While long-fin devices were fabricated to explore the maximum possible  $V_{\text{TH}}$  of proposed structure, a better balance between the  $V_{\text{TH}}$  and on-state performance was achieved for a device with  $L_{\text{Fin}}$  of 1 µm, which was chosen for the further characterizations.

The near-ideal SS and large peak  $G_m$  ( $G_{m, max}$ ) extracted from Fig. 2 (a) reveals excellent gate control and drive ability (Fig. 2 (c)). One advantage of multi-channel epitaxy over singlechannel is the much smaller  $N_S$  degradation as  $W_{\text{Fin}}$  decreases [1], which however results in a more difficult pinch-off of the channel purely by  $W_{\text{Fin}}$  scaling (Fig. 2 (d)). To elucidate the origin of the observed larger  $V_{\text{TH}}$ , the Ns of fins covered with LiNiO junction gate structure was measured by capacitancevoltage (CV) method, and compared with that of a pristine fin (without metal/oxide) obtained from hall measurements (Fig. 2 (e)) [1]. A clear depletion of carriers is observed for smaller  $W_{\text{Fin}}$  with LiNiO/Pd, which is not the case in pristine fins. The reduced  $N_S$  at  $V_G = 0$  V makes it easier to achieve e-mode.

Figure 3 (a) shows the dependence of the output characteristics on  $W_{\text{Fin}}$ . As summarized in Fig. 3 (b), devices with smaller  $W_{\text{Fin}}$  present a higher  $R_{\text{ON}}$  and lower maximum driving current ( $I_{\text{D, max}}$ ), which is due to their increased resistance as well as the over-etching of the fin, especially for the narrower fins ( $W_{\text{Fin}}$  of 15 nm). In addition, to keep the slanted tri-gate portion constant for a fair study, the number of tri-gate fins was fixed in each device, which resulted in a reduction of  $I_{\text{D, max}}$ , and in an increase in  $R_{\text{ON}}$  with a decrease in  $W_{\text{Fin}}$ , as they are normalized by the entire  $W_{\text{D}}$ . This degradation could be mitigated by increasing the number of fins in the same  $W_{\text{D}}$  as well as by improving the etching process for the narrow fins.

Figure 3 (c) presents the breakdown voltage characteristics of the proposed devices ( $L_{\text{Fin}}$  of 1 µm and  $W_{\text{Fin}}$  of 20 nm). Due to the well-distributed electric field by slanted tri-gate structure [2, 19-21], the device presents  $V_{\text{BR}}$  (hard breakdown) of 920 V, and the majority of the off-state current was through the gate ( $I_G \approx I_D$ ). The gate leakage current could be reduced by improving the step coverage and thickness of the LiNiO over the tri-gate, offering a large room for further improvement on  $V_{BR}$  [13]. An unprecedented low  $R_{ON}$  was achieved at similar  $V_{TH}$  when compared to state-of-the-art e-mode devices by p-GaN gate or p-oxide gate structures (Fig. 3 (d)), resulting in a  $R_{ON, sp}$  of 0.62 m $\Omega \cdot cm^2$  (by considering a 1 µm transfer length at each source/drain sides).

In addition, these devices presented outstanding stability at high temperatures compared with single-channel devices using LiNiO junction gate (with a similar  $V_{\text{TH}}$  for fair comparison). A temperature rise from 25 °C to 150 °C (Fig. 4 (a)) resulted in a small  $V_{\text{TH}}$  shift of -0.11 V, and the leakage level was kept below 1 nA/mm at 150 °C. Moreover, the proposed devices presented a very small  $V_{\text{TH}}$  hysteresis (from double sweep transfer measurement) of 0.05 V at 150 °C. This small hysteresis reveals the great quality of the LiNiO layer, as evidenced by XRD measurements (Fig. 1 (d)), which results in a small negative shift of  $V_{\text{TH}}$ .

The leakage current in off-state during positive drain voltage  $(V_D)$  stress could be maintained below 1 µA/mm at 150 °C and  $V_D = 200$  V (Fig. 4 (b)). This superior high-temperature voltage blocking capability is benefited from the depletion from three sides by the LiNiO layer, which results in deeper depletion inside of fin [11]. Finally, LiNiO junction gate structures have also presented excellent reliability performance on single-channel epitaxy [22].

## CONCLUSION

In this work, we presented high-performance multi-channel transistors based on the LiNiO junction gate, presenting a large positive  $V_{\text{TH}}$  of 1.2 V, near-ideal SS of 61 mV/dec, high on/off ratio over 9 orders of magnitude. This work unveils a promising technology path for future high-performance lateral GaN HEMT through structure, epitaxy, and gate material engineering.

#### REFERENCES

- L. Nela, J. Ma, C. Erine, P. Xiang, T. H. Shen, V. Tileli, T. Wang, K. Cheng, and E. Matioli, "Multi-channel nanowire devices for efficient power conversion," *Nature Electronics*, vol. 4, no. 4, p. 284, Apr 2021, doi: 10.1038/s41928-021-00550-8.

- [2] J. Ma, C. Erine, M. Zhu, N. Luca, P. Xiang, K. Cheng, and E. Matioli, "1200 V Multi-Channel Power Devices with 2.8 Ω•mm ON-Resistance," in 2019 IEEE International Electron Devices Meeting (IEDM), 7-11 Dec. 2019 2019, pp. 4.1.1-4.1.4, doi: 10.1109/IEDM19573.2019.8993536.

- [3] L. Nela, H. K. Yildirim, C. Erine, R. Van Erp, P. Xiang, K. Cheng, and E. Matioli, "Conformal Passivation of Multi-Channel GaN Power Transistors for Reduced Current Collapse," *IEEE Electron Device Lett.*, vol. 42, no. 1, pp. 86-89, Jan 2021, doi: 10.1109/Led.2020.3038808.

- [4] J. Ma, C. Erine, P. Xiang, K. Cheng, and E. Matioli, "Multi-channel trigate normally-on/off AlGaN/GaN MOSHEMTs on Si substrate with high breakdown voltage and low ON-resistance," *Applied Physics Letters*, vol. 113, no. 24, Dec 10 2018, doi: Artn 24210210.1063/1.5064407.

- [5] M. Xiao, Y. Ma, Z. Du, V. Pathirana, K. Cheng, A. Xie, E. Beam, Y. Cao, F. Udrea, H. Wang, and Y. Zhang, "Multi-Channel Monolithic-Cascode HEMT (MC<sup>2</sup>-HEMT): A New GaN Power Switch up to 10 kV," in 2021 IEEE International Electron Devices Meeting (IEDM), 11-16 Dec. 2021 2021, pp. 5.5.1-5.5.4, doi: 10.1109/IEDM19574.2021.9720714.

- [6] M. Y. Hua, Z. F. Zhang, J. Wei, J. C. Lei, G. F. Tang, K. Fu, Y. Cai, B. S. Zhang, and K. J. Chen, "Integration of LPCVD-SiN<sub>x</sub> Gate Dielectric with Recessed-gate E-mode GaN MIS-FETs: Toward High Performance, High Stability and Long TDDB Lifetime," 2016 IEEE International

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

*Electron Devices Meeting (IEDM)*, 2016, doi: 10.1109/IEDM.2016.7838388.

- [7] J. He, M. Hua, Z. Zhang, and K. J. Chen, "Performance and V TH Stability in E-Mode GaN Fully Recessed MIS-FETs and Partially Recessed MIS-HEMTs With LPCVD-SiN<sub>x</sub>/PECVD-SiN<sub>x</sub> Gate Dielectric Stack," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3185-3191, 2018, doi: 10.1109/ted.2018.2850042.

- [8] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3393-3399, Dec. 2007, doi: 10.1109/TED.2007.908601.

- [9] J. T. Asubar, S. Kawabata, H. Tokuda, A. Yamamoto, and M. Kuzuhara, "Enhancement-Mode AlGaN/GaN MIS-HEMTs With High  $V_{TH}$  and High  $I_{Dmax}$  Using Recessed-Structure With Regrown AlGaN Barrier," *IEEE Electron Device Lett.*, vol. 41, no. 5, pp. 693-696, 2020 2020, doi: 10.1109/led.2020.2985091.

- [10] L. Zhang, Z. Y. Zheng, S. Yang, W. J. Song, J. B. He, and K. J. Chen, "p-GaN Gate HEMT With Surface Reinforcement for Enhanced Gate Reliability," *IEEE Electron Device Lett.*, vol. 42, no. 1, pp. 22-25, Jan 2021, doi: 10.1109/Led.2020.3037186.

- [11] Y. W. Ma, M. Xiao, Y. H. Zhang, Z. H. Du, X. D. Yan, H. Wang, K. Cheng, M. Clavel, M. K. Hudait, L. Tao, F. Lin, and I. Kravchenko, "Kilovolt Tri-Gate GaN Junction HEMTs with High Thermal Stability," *Proc Int Symp Power*, pp. 139-142, 2021.

- [12] Y. Ma, M. Xiao, Z. Du, X. Yan, K. Cheng, M. Clavel, M. K. Hudait, I. Kravchenko, H. Wang, and Y. Zhang, "Tri-gate GaN junction HEMT," *Applied Physics Letters*, vol. 117, no. 14, 2020, doi: 10.1063/5.0025351.

- [13] T. F. Wang, M. S. Nikoo, L. Nela, and E. Matioli, "LiNiO Gate Dielectric with Tri-Gate Structure for High Performance E-mode GaN transistors," *Proc Int Symp Power*, pp. 135-138, 2021.

- [14] J. Y. Zhang, W. W. Li, R. L. Z. Hoye, J. L. MacManus-Driscoll, M. Budde, O. Bierwagen, L. Wang, Y. Du, M. J. Wahila, L. F. J. Piper, T.-L. Lee, H. J. Edwards, V. R. Dhanak, and K. H. L. Zhang, "Electronic and transport properties of Li-doped NiO epitaxial thin films," *J. Mater. Chem. C*, vol. 6, no. 9, pp. 2275-2282, Jan. 2018, doi: 10.1039/C7TC05331B.

- [15] D. S. Macintyre, I. Young, A. Glidle, X. Cao, J. M. R. Weaver, and S. Thoms, "High resolution e-beam lithography using a thin titanium layer to promote resist adhesion," *Microelectronic Engineering*, vol. 83, no. 4-9, pp. 1128-1131, Apr-Sep 2006, doi: 10.1016/j.mee.2006.01.103.

- [16] J. Y. Wu, S. Q. Lei, W. C. Cheng, R. Sokolovskij, Q. Wang, G. Xia, and H. Y. Yu, "Oxygen-based digital etching of AlGaN/GaN structures with AlN as etch-stop layers," *Journal of Vacuum Science & Technology A*, vol. 37, no. 6, Nov 2019, doi: Artn 06040110.1116/1.5115427.

- [17] G. Li, X. Li, J. Zhao, F. Yan, Q. Zhu, and X. Gao, "Design principle for a p-type oxide gate layer on AlGaN/GaN toward normally-off HEMTs: Li-doped NiO as a model," *J. Mater. Chem. C*, vol. 8, no. 3, pp. 1125-1134, Dec. 2020, doi: 10.1039/C9TC04467A.

- [18] Y. H. Zhang, A. Zubair, Z. H. Liu, M. Xiao, J. Perozek, Y. W. Ma, and T. Palacios, "GaN FinFETs and trigate devices for power and RF applications: review and perspective," *Semiconductor Science and Technology*, vol. 36, no. 5, May 2021, doi: ARTN 05400110.1088/1361-6641/abde17.

- [19] J. Ma and E. Matioli, "Slanted Tri-Gates for High-Voltage GaN Power Devices," *IEEE Electron Device Lett.*, vol. 38, no. 9, pp. 1305-1308, 2017, doi: 10.1109/led.2017.2731799.

- [20] B. Lu, E. Matioli, and T. Palacios, "Tri-Gate Normally-Off GaN Power MISFET," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 360-362, 2012, doi: 10.1109/led.2011.2179971.

- [21] J. Ma and E. Matioli, "High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 367-370, Mar 2017, doi: 10.1109/Led.2017.2661755.