### Thèse n° 8122

# EPFL

## Energy Efficient Sensing using Steep Slope Devices

Présentée le 15 juillet 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire des dispositifs nanoélectroniques Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

## **Teodor ROSCA**

Acceptée sur proposition du jury

Prof. E. D. N. Matioli, président du jury Prof. M. A. Ionescu, directeur de thèse Prof. D. Flandre, rapporteur Prof. N. Pryds, rapporteur Prof. C. Enz, rapporteur

École polytechnique fédérale de Lausanne

2022

The problem is not the problem The problem is your **attitude** towards the problem

— Captain Jack Sparrow —

## Acknowledgements

As I am writing these words at the end of a 6 years-long journey navigating PhD life I realize none of it would have been possible without the help and motivation provided by countless other people, to whom I am forever grateful and indebted.

First and foremost, I'd like to acknowledge and thank **Prof. Adrian Ionescu** for providing me with the opportunity to work in such a diverse, challenging, and fun place like Nanolab, for the valuable advice and countless research ideas and for the many "lessons in disguise" that he passed on to me during our interactions throughout the years, from which I feel I still have a lot to learn. Special thanks are due for the expert members of my PhD defence jury: **Prof. Nini Pryds**, **Prof. Denis Flandre** and **Prof. Christian Enz**, who took the time to review this work and provided me with the missing links and the key suggestions for the improvement of this manuscript. I sincerely enjoyed the discussions during the defence that was expertly presided by **Prof. Elison Matioli**, to whom I am also grateful. I need to also express my gratitude to **Prof. Peter Seitz**, who inspired me in more ways than I can count during the final year of my Master studies. Peter is a brilliant scientist and a great educator - I owe a good chunk of my physics knowledge to him and hope that someday we will work together again.

My EPFL adventure began many years ago, and the main culprits are none other than my very good friends **Alexandru** and **Anca Rusu**, who were kind enough to help and teach me all about Swiss life and the ups and downs of the academic lifestyle from the very moment I arrived, through countless "discussions" that we had - mostly on their balcony or downtown Lausanne and mostly extending until 4-5AM on Mondays. Daily office life in Nanolab was made even better by the scientific staff and my very dear colleagues. Here I would like to particularly mention **Dr. Daesung Park**, who is an amazing scientist strangely capable of solving more than 1000 problems at the same time in a professional manner without breaking a sweat and who was kind enough to provide the most valuable help when I needed it most, and for that I am truly grateful. On the same page, **Dr. Igor Stolichnov** is without a doubt the nicest and most patient person I had the privilege to meet, while at the same time being extremely knowledgeable and a great educator.

I'd like to give a shout out to the two best office mates anyone could wish for: **Dr. Emanuele Casu** and **Luca Capua**, who along with **Dr. Matteo Cavalieri**, **Dr. Nicolò Oliva**, **Dr. Jacopo Bronuzzi**, **Carlotta Gastaldi** and **Felix Risch** are part of what I now consider to be my extended (and almost completely italian) family. The only thing I regret at this point is that I could not spend enough time with them so I can properly learn their language, but I'm sure they will forgive me. Special thanks are due to the golden boy of Nanolab, **Sadegh Kamaei**, with whom I shared countless sessions of PMC work (and repairs, because that machine has a mind of its own sometimes), and to my BRO **Fatemeh Qaderi** with whom I performed some of the most fascinating experiments on VO<sub>2</sub>, some of which you will find out about by reading this manuscript. Although not a person, I would like to also (jokingly) acknowledge **the famous "IEDM wafer"**, which exhibited outstanding robustness and supported numerous experiments in our lab. Spoiler alert - it's Sample A in Chapters 4 and 5 of this thesis.

No mention of the Nanolab collective would be complete without the old guard, including - but not limited to - **Dr. Wolfgang Amadeus Vitale**, who taught me the basics of vanadium dioxide switches in my first month in the lab, **Dr. Clara Moldovan**, with whom I spent countless hours debating - sometimes random, sometimes serious - topics, **Dr. Francesco Bellando** with whom I shared one of the best business trips ever back in 2018 and **Dr. Cem Alper** and **Dr. Ali Saeidi**, both brilliant scientists who were instrumental in developing some of the topics addressed in this manuscript in Chapter 2. I would also like to express my gratitude to the administrative staff of the lab and EDEE doctoral school, and particularly **Karin Jaymes, Isabelle Buzzi** and **Valérie Maillard**, who were always there to help me navigate the bureaucratic side of EPFL life, and **Cédric Meinen** and **Pascal Morel**, who were always ready to help acquire parts, equipment and set up often complicated experiments.

#### Acknowledgements

In addition to the Nanolab group, I have been blessed with a number of very good and loyal friends, who supported me during my PhD journey. A special shoutout goes to "The doctor" **Stefan Mitrea**, with whom, in the past 6 years, I spent an unorthodox amount of time having fun, playing games, discussing very serious and interesting topics, and enjoyed a healthy amount of skiing - often aided by the effortless skills and energy of **Dr. Radek Skupienski**, who remains, to this day, the coolest half-polish guy I know. I must also thank my good friend **Denis Tudor** for providing me with never ending motivation to work harder and become a better person, and for inspiring me to pursue bigger and bigger goals in my career.

In closing, I must acknowledge my old friends from the Polytechnic Institute in Bucharest - Adrian and Suzana Gaspar, Bogdan Istrate, Ovidiu Alexandru and Mircea Zamfira for feeding my hunger for awkwardly technical hobbies like building robots, and for the precious times we spent together in competitions - often in very exotic places (some long trips to Austria and Japan come to mind here) - over the past 8-9 years. A special place on the acknowledgements podium is reserved for **Cristina Teodorescu**, who over the course of many years supported and motivated me to keep going no matter what, and who also taught me a few life lessons that will surely serve me good going forward.

Last but not least, I must confess nothing would have been possible - quite literally - without the help of my dear parents - **Irina** and **Gabriel Rosca**. I want to thank them for imparting me with the desire to pursue this path towards achieving greater knowledge and wisdom, which is a journey that will probably continue forever. Never ceasing to believe in me, their invaluable advice, help and support throughout the years are the reason I am here, today, writing these words, and for that, I am truly grateful.

Thank you all, and enjoy the reading!

Lausanne, June 2022

Teodor Rosca.

## Abstract

Today, we are witnessing the Internet of Things (IoT) revolution, which facilitates and improves our lives in many aspects, but comes with several challenges related to the technology deployment at large scales. Handling ever growing amounts of information that needs to be sensed, stored, transmitted and processed requires severe improvements in energy efficiency and smart distribution of computational power spanning from Cloud systems (handling Big Data in a massively parallel fashion) all the way to Edge devices (interfaces to the real world), where co-integration of sensing and computation plays a big role. Innovations in this field require the development of new device principles in existing technology platforms and/or new abundant and non-toxic materials that can enable electronic functions beyond the classical semiconductors, such as the field of oxide electronics that holds promise for both classical electronics functions and for future neuromorphic implementations. In this thesis, we explore both these aspects, having as a common denominator steep slope devices, which have the merit of offering a path for improved energy efficiency via voltage scaling. We particularly focus our work on their ability to serve energy efficient sensing functions that can be integrated with the computational platforms.

The first part of the thesis focuses on Tunnel Field Effect Transistors (TFETs) and how they can be used to perform similar tasks to Single Electron Transistors for qubit readout and also for serving as interfacing electronics. Such applications rely on cryogenic operation where conventional CMOS technology shows performance degradation due to low temperature effects such as dopant deactivation and carrier freeze-out. Our study shows that state-of-the-art heterostructure nanowire TFET arrays maintain excellent figures of merit over wide temperature ranges, down to the Kelvin regime, while simultaneously showing reduced temperature dependence once Trap Assisted Tunnelling mechanisms are removed below 150K. Leveraging such properties, we suggest that TFETs are promising candidates as charge sensing devices for qubit readout architectures with high sensitivity to single or few elementary charges.

In the second part of the thesis we focus towards sensing architectures more suitable for Edge-of-Cloud (EoC) applications, by exploring phase-transition materials such as Vanadium Dioxide (VO<sub>2</sub>). In this context, we explore the optimization of a Pulsed Laser Deposition (PLD) process in order to achieve high quality VO<sub>2</sub> thin films grown on CMOS compatible substrates, followed by electrical characterization of fabricated VO<sub>2</sub> two-terminal devices, which provides valuable data that aid us in developing compact SPICE-compatible device models. Built on top of the VO<sub>2</sub> resistor elements, we propose a novel Spiking Voltage-Controlled Oscillator (VCO) architecture that exhibits low device count (1 Transistor 1 Resistor - 1T1R) while at the same time providing frequency tuning capabilities in excess of 400% in the 10s of kHz range. We experimentally validate that the VCO cell can be used as a power-to-frequency transducer in a wide spectrum, ranging from near-UV, throughout the entirety of the visible domain, and as far as the Mid-Infrared and mmWave ranges, suggesting a new class of sensors capable of responding to a broad range of stimuli.

Key words: Steep-slope devices, tunnel field-effect transistor (TFET), band-to-band tunneling (BTBT), trap-assisted tunneling (TAT), low temperature electronics (LTE), cryogenic, charge sensing, metal-insulator transition (MIT), insulator-metal transition (IMT), vanadium dioxide (VO<sub>2</sub>), pulsed laser deposition (PLD), Complementary metal-oxide-semiconductor (CMOS), voltage controlled oscillator (VCO), sensor, sensing platform, visible light sensing, infrared sensing.

## Résumé

Nous assistons aujourd'hui à la Révolution de "l'Internet des Choses" (IoT en anglaise), qui facilite et améliore nos vies dans différents domaines, mais qui reste difficile, pour des raisons technologiques, à implémenter à large échelle. La gestion d'une quantité grandissante d'information qui doit être collectée, stockée, transféré et traitée requiert des améliorations significatives dans le domaine de l'efficacité énergétique et de la répartition "intelligente" de la puissance de calcul. Ces améliorations doivent s'étendre dans le domaine des systèmes "Cloud" (la gestion des Big Data de façon massivement parallèle) jusqu'aux dispositifs périphériques, qui font l'interface avec le monde physique et où la cointégration entre capteur et processeur joue un rôle majeur. Les innovations dans ce secteur nécessitent le développement de nouveaux principes dans les technologies existantes et/ou l'utilisation de nouveaux matériaux, si possible abondants et non-toxiques, qui permettraient de surclasser les matériaux semi-conducteurs classiques. A cet égard, un champ de recherche prometteur en électronique est celui des oxydes fonctionnels, qui peuvent servir à la fois dans les applications électroniques "classiques" ainsi que dans les futures implémentations neuromorphiques. Dans cette thèse, nous explorons ces différents aspects dont le dénominateur commun est le développement de dispositifs à pente raide ("Steep slope devices") qui montrent une meilleure efficacité énergétique en permettant le fonctionnement à des tensions plus basses. Nous concentrons particulièrement notre travail sur leur capacité à servir des fonctions de détection économes en énergie qui peuvent être intégrées aux plates-formes de calcul.

La première partie de la thèse se focalise sur les transistors à effet tunnel (TFETs), en particulier sur la manière dont ils peuvent être utilisés pour des taches similaires aux "transistors à un électron" (SET) pour la lecture des qubits ou pour servir d'interface électronique pour de tels systèmes. Ces différentes applications nécessitent des opérations cryogéniques, où la technologie CMOS classique montre des performances suboptimales à basse température (à cause des effects comme le "dopant deactivation" et "carrier freeze-out"). Notre travail démontre que des "heterostructure nanowire TFET arrays" maintiennent d'excellentes propriétés pour une large plage de température aussi basse que <10K tout en montrant une dépendance à la température réduite une fois que les effets tunnel assistés par pièges (TAT) sont supprimés en dessous de 150K. Forts de ces propriétés, nous suggérons que les transistors à effet tunnel sont d'excellents candidats comme dispositifs de détection de charge pour la lecture des qubits (sensibilité à des charges élémentaires uniques).

Dans la seconde partie de la thèse, nous nous focalisons sur l'architecture des dispositifs permettant l'implémentation de technologies « Edge-of-Cloud » (EoC), particulièrement, en explorant des matériaux à transition de phase tel que le Dioxyde de Vanadium (VO2). Nous investiguons l'optimisation d'un processus de déposition de VO2, directement sur des substrats compatibles avec la technologie CMOS, via un procédé de dépôt par laser pulsé (PLD). Une fois les dispositifs produits, nous procédons à leur caractérisation électrique, avec pour objectif de développer des modèles de dispositifs compacts compatibles avec des plateformes SPICE. Construit directement au-dessus d'éléments de résistance VO2, nous proposons une nouvelle architecture de oscillateur commandé en tension (VCO) qui démontre un nombre reduit de dispositifs tout en fournissant des capacités de modulation de la fréquence en excès de 400% dans la gamme 10 kHz. Nous avons démontré expérimentalement que les cellules VCO peuvent être utilisées comme transducteurs de puissance à fréquence, dans une large gamme entre les UV, l'entièreté du spectre visible et jusqu'au infrarouge et la gamme des ondes millimétriques, démontrant ainsi une nouvelle classe de capteurs capable de répondre à un large éventail de stimuli.

Mots clefs : Dispositifs à pente raide, transistors à effet tunnel (TFET), effet tunnel bande à bande (BTBT), effet tunnel assisté par pièges (TAT), électronique à basse température (LTE), cryogénique, détection de charge, transition métal-isolant (MIT), transition isolant-métal (IMT), dioxyde de vanadium (VO<sub>2</sub>), dépôt à laser pulsé (PLD), technologie complémentaire métal-oxyde-semiconducteur (CMOS), oscillateur controlé en tension (VCO), capteur, plate-forme de détection, détection de la lumière visible, détection de la lumière infrarouge.

## Riassunto

Oggigiorno, siamo testimoni della rivoluzione riguardante l'Internet delle Cose (IdC, in inglese Internet of Things), che facilita e migliora le nostre vite in molti settori, la quale peró é accompagnata da diverse sfide relative alla produzione di nuove tecnologie su larga scala. Manipolare il crescente volume di informazioni che bisogna rilevare ('sensing'), conservare, trasmettere e processare richiede profondi miglioramenti in termini di efficienza energetica e distribuzione intelligente di potenza computazionale, che si estende dai servizi di Cloud (manipolazione di Big Data in operazioni parallele) fino ai dispositivi 'Edge' (le interfacce al mondo reale), dove l'integrazione tra il mondo del sensing e della computazione gioca un ruolo fondamentale. Le innovazioni in questo settore richiedono lo sviluppo di dispositivi basati su nuovi principi compatibili con le piattaforme tecnologiche esistenti e/o nuovi materiali abbondantemente presenti in natura e non tossici, che permettono nuove funzioni elettroniche che vanno oltre quelle date dai semiconduttori classici. Un esempio é l'elettronica basata su ossidi a effetto di campo, una tecnologia promettente sia in termini di classiche funzioni elettroniche sia per future implementazioni nel campo del calcolo neuromorfico. In questa tesi, esploriamo entrambi questi aspetti, avendo come comune denominatore i cosidetti dispositivi ad 'alta pendenza' (dispositivi a steep slope), i quali hanno la capacitá di offrire una migliore efficienza energetica attraverso la riduzione del potenziale elettrico necessario. Concentriamo il nostro lavoro sulla loro abilitá di fornire funzioni ad alta efficienza energetica, che possono essere integrate nelle piattaforme computazionali esistenti.

La prima parte della tesi si focalizza sui Tunnel FETs (TFETs) e su come possano essere utilizzati per implementare funzioni simili ai transistori a singolo elettrone (Single Electron Transistor – SET) per la lettura di qubit (bit per quantum computer) e anche come interfacce elettroniche. Tali applicazioni si basano sul funzionamento a temperature criogeniche, temperature alle quali i dispositivi CMOS convenzionali sono caratterizzati da una degradazione delle prestazioni dovute a effetti esibiti a basse temperature, come la disattivazione dei dopanti e il congelamento dei portatori di carica. Lo studio che viene presentato in questa tesi mostra lo stato dell'arte dei nanowire TFET arrays, che mantengono un'eccellente figura di merito su un largo intervallo di temperature, fino a temperature minori di 10K mentre mostrano simultaneamente una minore dipendenza nel momento in cui meccanismi di Trap Assisted tunneling sono rimossi sotto i 150K. Sfruttando tali proprietá, consideriamo questi TFET promettenti candidati come sensori di carica per la lettura di architetture basate su qubit, con alta sensibilitá a singole o un ridotto numero di cariche elementari. Nella seconda parte della tesi, focalizziamo la nostra attenzione su architetture sensoriali piú adatte per applicazioni relative all' Edge-of-Cloud, esplorando materiali a transizione di fase come il diossido di vanadio (VO<sub>2</sub>). In questo constesto, esploriamo l'ottimizzazione di un sistema per deposizione a laser pulsato (Pulsed Laser Deposition – PLD), al fine di ottenere film sottili di VO<sub>2</sub> ad alta qualitá, depositati su substrati compatibili con tecnologie CMOS. Successivamente, presentiamo la caratterizzazione elettrica di dispositivi a due terminali basati su VO2, che forniscono dati preziosi che possono aiutarci nello sviluppo nuovi modelli SPICE compatti per questi dispositivi. Inoltre, proponiamo un nuovo Oscillatore controllato da voltaggio (VCO) basato su un elemento resistivo a VO<sub>2</sub>, il quale esibisce un basso numero di dispositivi (1 Transtore 1 Resistenza – 1T1R), mentre contemporaneamente fornisce capacitá di regolabilitá della frequenza di oltre il 400% nell'intervallo di decine di kHz. Abbiamo sperimentalmente convalidato che una cella VCO possa essere utilizzata come trasduttore potenza-frequenza per un ampio spettro, che si estende dal quasi-UV, attraverso tutto lo spettro visibile, fino al semi-infrarosso e onde millimetriche, suggerendo una nuova classe di sensori capaci di rispondere a un largo spettro di stimoli.

Parole chiave: Dispositivi ad alta-pendenza, FET a effetto tunnel (TFET), tunnelling banda-a-banda (BTBT), tunnelling assistito da trappole (TAT), elettronica a bassa temperature (LTE), criogenia, sensori di carica, transizione metallo-isolante (MIT), transizione isolante-metallo (IMT), diossido di vanadio (VO<sub>2</sub>), deposizione a laser pulsato (PLD), tecnologia complementare a metallo-ossido-semiconduttore (CMOS), oscillatore controllato da Voltaggio (VCO), sensore, piattaforma sensoriale, rilevazione di luce visibile, rilevazione di infrarossi.

# Contents

| Ac | knov    | vledge  | ments                                                             | i   |

|----|---------|---------|-------------------------------------------------------------------|-----|

| Ab | ostrac  | ct (Eng | lish/Français/Italiano)                                           | v   |

| Li | st of f | figures |                                                                   | XV  |

| Li | st of 1 | tables  |                                                                   | XXV |

| 1  | Intr    | oducti  | on and rationale                                                  | 1   |

| In | trodu   | uction  |                                                                   | 1   |

|    | 1.1     | Thesis  | Outline                                                           | 5   |

| 2  | Cha     | rge Sei | nsing for Qubit Readout using Tunnel FETs                         | 9   |

|    | 2.1     | Introd  | luction                                                           | 9   |

|    |         | 2.1.1   | The Tunnel FET                                                    | 11  |

|    | 2.2     | Cryog   | enic Tunnel FETs                                                  | 15  |

|    |         | 2.2.1   | Experimental Methods                                              | 16  |

|    |         | 2.2.2   | Devices under test                                                | 17  |

|    |         | 2.2.3   | Transfer Characteristic and Subthreshold Slope                    | 19  |

|    |         | 2.2.4   | Influence of temperature on device performance                    | 21  |

|    |         | 2.2.5   | Analog Figures of Merit                                           | 22  |

|    | 2.3     | Eleme   | entary Charge sensing with Tunnel FETs                            | 26  |

|    |         | 2.3.1   | Principle of DG-TFET as elementary charge sensor                  | 27  |

|    |         | 2.3.2   | Validation by simulation                                          | 29  |

|    |         | 2.3.3   | Experimental validation on a SiGe/Si Line Tunneling TFET $\ldots$ | 31  |

|    | 2.4     | Summ    | nary                                                              | 35  |

| 3 | Pha             | se transition characteristics of VO $_2$ thin films                                                 | 39  |

|---|-----------------|-----------------------------------------------------------------------------------------------------|-----|

|   | 3.1             | Introduction                                                                                        | 39  |

|   | 3.2             | Experimental Methods                                                                                | 44  |

|   |                 | 3.2.1 Pulsed Laser Deposition                                                                       | 44  |

|   |                 | 3.2.2 Device fabrication Process Flow                                                               | 50  |

|   |                 | 3.2.3 VO <sub>2</sub> thin film characterization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 52  |

|   |                 | 3.2.4 Electrical characterization of $VO_2$ two-terminal devices                                    | 54  |

|   | 3.3             | Optimization of the PLD process for $VO_2$ thin films $\ldots \ldots \ldots \ldots$                 | 55  |

|   |                 | 3.3.1 Laser Fluence                                                                                 | 55  |

|   |                 | 3.3.2 Oxygen partial pressure                                                                       | 61  |

|   | 3.4             | Summary                                                                                             | 65  |

| 4 | A 17            | $\Gamma$ -1R Voltage Controlled Spiking Oscillator based on VO <sub>2</sub>                         | 67  |

|   | 4.1             | Introduction                                                                                        | 67  |

|   | 4.2             | Circuit analysis and Modeling                                                                       | 68  |

|   |                 | 4.2.1 DC Operating point                                                                            | 68  |

|   |                 | 4.2.2 Dynamic analysis                                                                              | 71  |

|   |                 | 4.2.3 Oscillation condition and tuning range                                                        | 77  |

|   | 4.3             | Experimental validation of the analytical model                                                     | 78  |

|   |                 | 4.3.1 Frequency dependence on device and circuit parameters                                         | 86  |

|   | 4.4             | Summary                                                                                             | 91  |

| 5 | VO <sub>2</sub> | Oscillators for optical sensing (and beyond)                                                        | 93  |

|   | 5.1             | Visible light sensing                                                                               | 93  |

|   |                 | 5.1.1 Methods                                                                                       | 93  |

|   |                 | 5.1.2 Results and discussion                                                                        | 96  |

|   | 5.2             | Ghz/mmWave sensing                                                                                  | 102 |

|   |                 | 5.2.1 Methods                                                                                       | 103 |

|   |                 | 5.2.2 Results and discussion                                                                        | 104 |

|   | 5.3             | SPICE-Compatible modeling of vanadium dioxide steep slope switches                                  | 106 |

|   |                 | 5.3.1 Thermal hysteresis modeling                                                                   | 107 |

|   |                 | 5.3.2 Joule heating thermal network                                                                 | 111 |

|   |                 | 5.3.3 Oscillator simulation                                                                         | 116 |

|   | 5.4             | Summary                                                                                             | 118 |

| 6 | Per             | spectives                                                                                           | 121 |

CONTENTS

| Bibliography     | 125 |

|------------------|-----|

| Curriculum Vitae | 141 |

# List of Figures

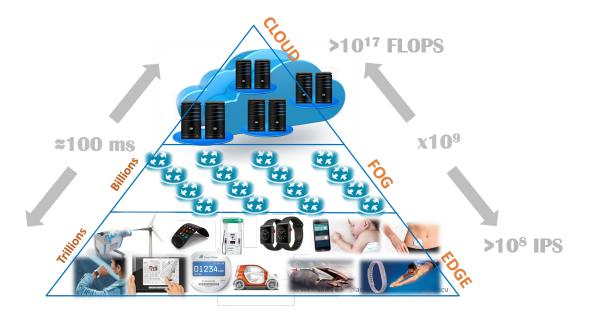

| 1.1 | The Edge-to-Cloud information processing model for AI, suggesting unsustainable, inefficient and slow zettabyte data movement. Adapted from [1]                                                                                                                                                                                                                                               | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

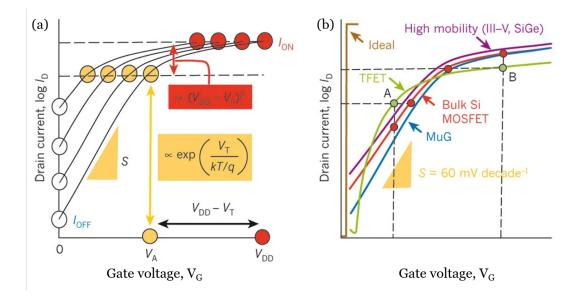

| 2.1 | (a) - Qualitative representation of the exponential increase in $I_{OFF}$ as a consequence of supply voltage reduction; (b) - A comparison of transfer characteristic for a bulk Si MOSFET alongside a Tunnel FET, a high-mobility channel MOSFET a multi-gate MOSFET and an ideal switch. The TFET can offer a steeper subthreshold slope at the cost of lower on-current. Adapted from [13] | 10 |

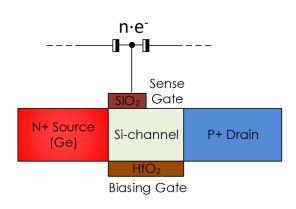

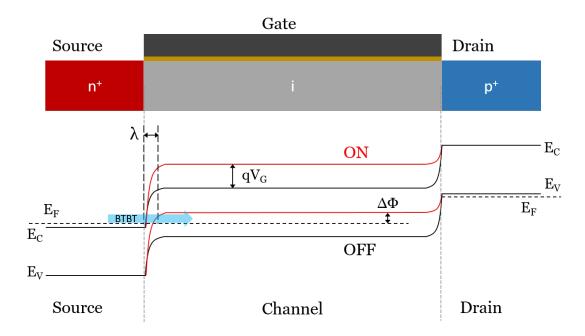

| 2.2 | (top) - Schematic diagram of a planar p-Type TFET and (bottom) - Quali-<br>tative band diagram showing how the gate bias $V_G$ can induce an overlap<br>between the source conduction band and the channel valence band<br>which enables band-to-band tunneling at the source-channel interface.                                                                                              | 11 |

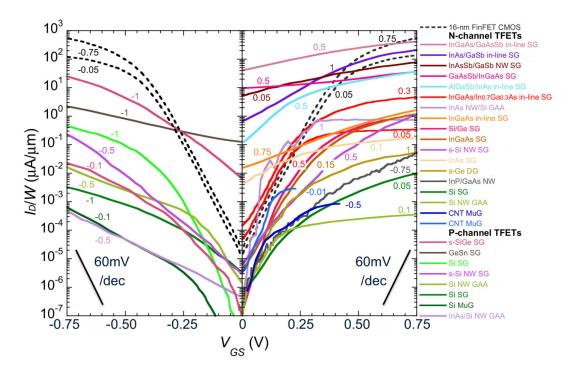

| 2.3 | A comparison of several published TFET transfer characteristics com-<br>pared to a commercial 16 nm low-power Fin-FET. Adapted from [14]<br>with data from [25–49]                                                                                                                                                                                                                            | 13 |

| 2.4 | The SUSS MicroTec PMC150 Cryogenic probing station                                                                                                                                                                                                                                                                                                                                            | 16 |

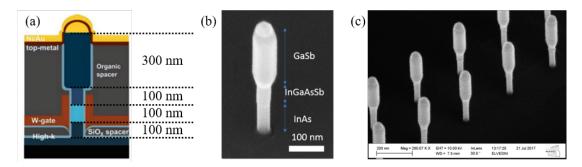

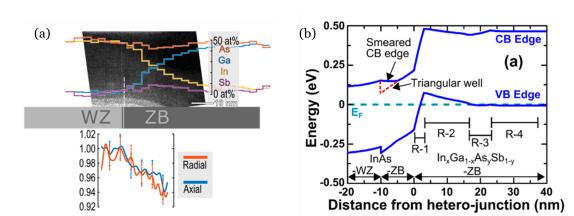

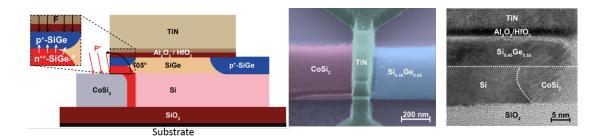

| 2.5 | (a) - Cross sectional view of the $InAs/In_xGa_{1-x}As_ySb_{1-y}/GaSb$ Nanowire<br>Tunnel FET; (b) - SEM image of a single nanowire, indicating the indi-<br>vidual segments; (c) - SEM image of a section of the 184 nanowire Large<br>Array - Adapted from [69]                                                                                                                             | 17 |

| 2.6 | (a) Illustration of the composition and strain profile changes across the graded tunneling junction; (b) - Simulation of the band edge diagram along the axis of the nanowire - From [68]                                                                                                                                                                                                     | 18 |

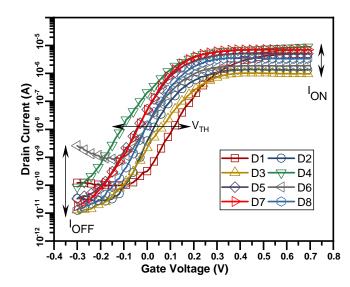

| 2.7  | Room temperature transfer characteristic of multiple distinct devices,              |    |

|------|-------------------------------------------------------------------------------------|----|

|      | showing considerable variability in on-current $I_{On}$ , off-current $I_{Off}$ and |    |

|      | threshold voltage $V_T$ . Measurements were taken at $V_D = 0.4V$                   | 19 |

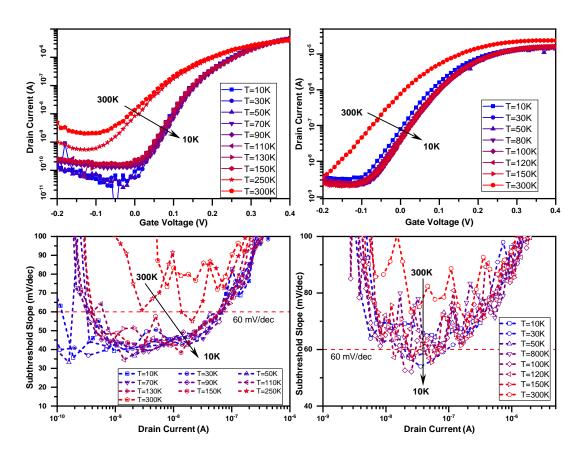

| 2.8  | Top - Transfer characteristic of the 4NW (left) and 184NW (right) devices           |    |

|      | at multiple temperatures from 300K down to 10K at drain voltage $V_D$ =             |    |

|      | 0.4V; Bottom - Subthreshold slope of the 4NW (left) and 184NW (right)               |    |

|      | devices                                                                             | 20 |

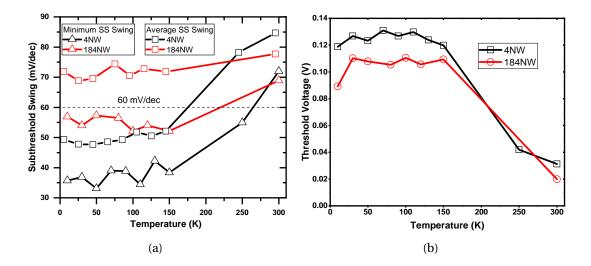

| 2.9  | (a) - Minimum and average subthreshold slope values for both devices                |    |

|      | at $V_D = 0.4V$ ; (b) - Effect of operating temperature on threshold voltage        | 21 |

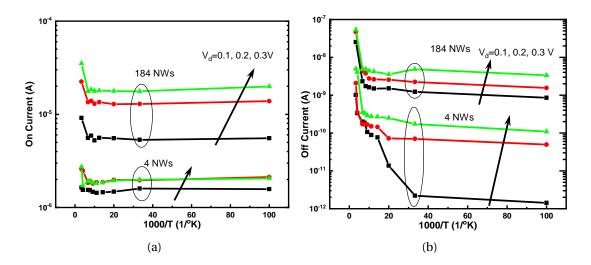

| 2.10 | Arrhenius plots of the On- and Off- current in both arrays                          | 21 |

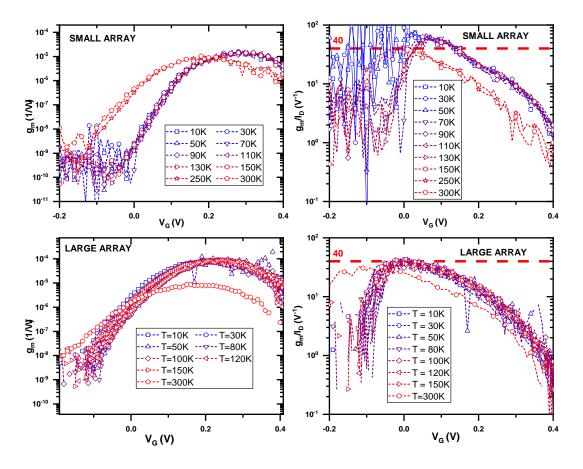

| 2.11 | Transconductance $g_m$ (left) and Transconductance efficiency $g_m/I_D$ (right)     |    |

|      | for both arrays between 300K and 10K, and $V_D = 0.4V$                              | 23 |

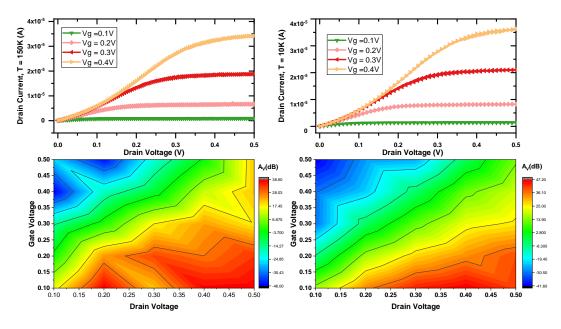

| 2.12 | Top: Output characteristics of the large array at gate voltages between 0.1         |    |

|      | and 0.4 V at 150K and 10K, Bottom - Color map distribution of intrinsic             |    |

|      | gain across the operating point space ( $V_G$ and $V_D$ between 0.1V and 0.5V)      | 24 |

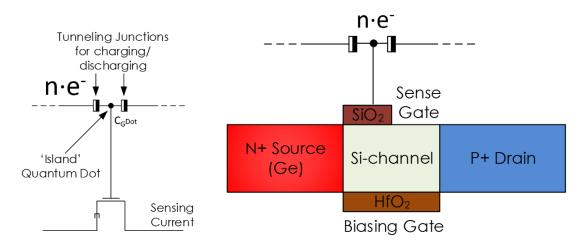

| 2.13 | Left: Charge sensor schematic; Right - DG-TFET coupled with island                  |    |

|      | (Quantum Dot)                                                                       | 28 |

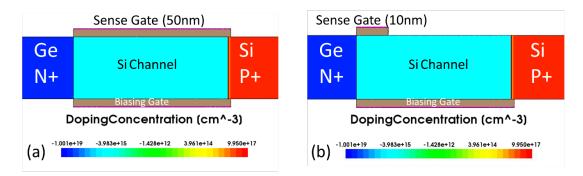

| 2.14 | (a) - DG-TFET structure used in simulation; (b) - Optimized version for             |    |

|      | high sensitivity                                                                    | 29 |

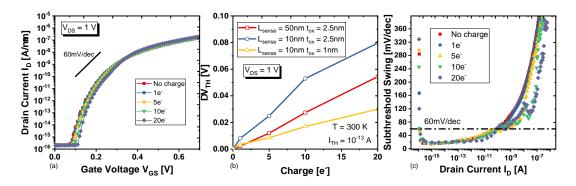

| 2.15 | (a) - Transfer characteristic with respect to sensed charge; (b) - Threshold        |    |

|      | voltage shift for standard and optimized structures; (c) - Subthermal               |    |

|      | subthreshold slope values at room temperature, measured at 100fA $$                 | 30 |

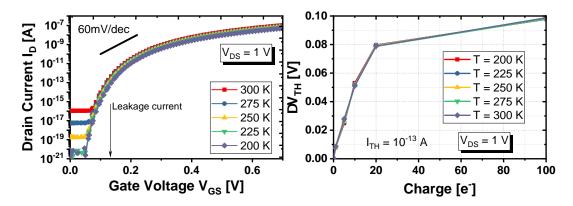

| 2.16 | (a) - Transfer characteristic between 200K and 300K showing decrease of             |    |

|      | leakage at lower temperature; (b) - Threshold voltage shift independent             |    |

|      | on temperature between 200K and 300K                                                | 31 |

| 2.17 | Left - TFET cross section outlining increased area for line tunneling;              |    |

|      | Center - SEM micrograph of the device; Right - TEM micrograph of the                |    |

|      | tunneling junction area. Adapted from [50]                                          | 31 |

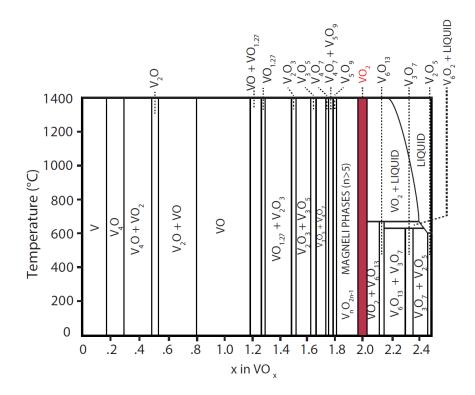

| 2.18 | (a) - Transfer characteristics of line TFET measured at 300K, 180K and              |    |

|      | 80K; (b) - Subthreshold slope values associated to transfer characteristics         |    |

|      | in (a); (c) - Forward transfer characteristics measured at 180K with back           |    |

|      | gate bias ranging from -6 to 6V; (d) - Measured shift in threshold voltage          |    |

|      | as a consequence of back gate bias                                                  | 32 |

|      |                                                                                     |    |

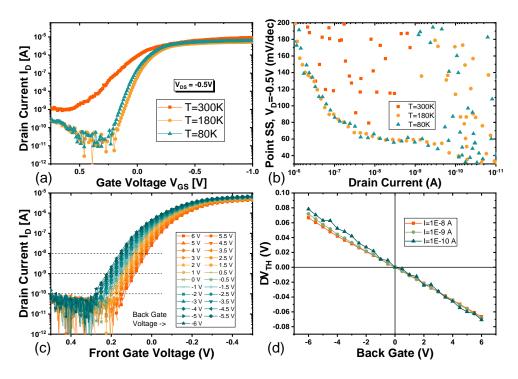

| 2.19 | (a) - Simulated transfer characteristics of the SET at temperature T=5K<br>and supply voltage $V_{DS} = 30 mV$ indicating considerable shift of the<br>threshold voltage with respect to background charge (model parame-<br>ter $\xi$ [81]); (b) - Simulated transfer characteristics and extracted sub-<br>threshold slope of the SET at temperatures between 5K and 50K; MIB<br>model parameters [81] used in simulation: $R_{TD} = R_{TS} = 1M\Omega$ , $C_G = 2aF$ ,<br>$C_{TD} = C_{TS} = 1aF$ | 34 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

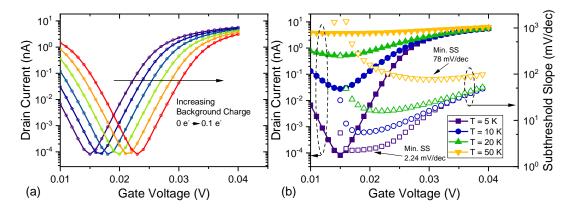

| 3.1  | Phase diagram of the V-O system. Adapted from [23], originally from [91]                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

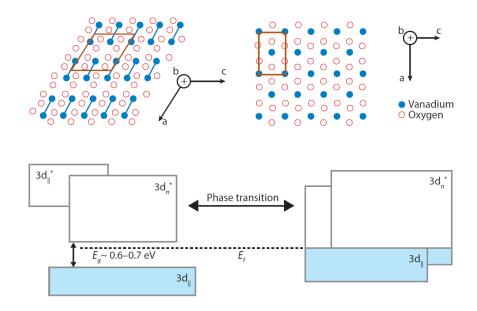

| 3.2  | Top - the IMT structural change of $VO_2$ from the insulating phase (mon-<br>oclinic) to the metallic phase (rutile); Bottom - Bandgap collapse due to<br>the structural change; Adapted from [93], originally from [90]                                                                                                                                                                                                                                                                             | 41 |

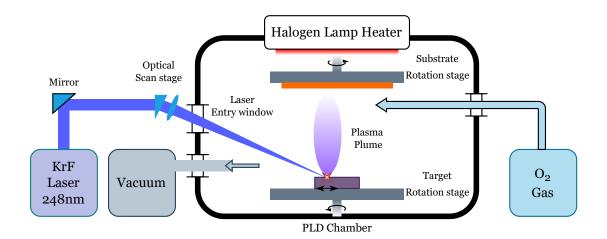

| 3.3  | Schematics for a pulsed laser deposition system including a vacuum chamber (a base pressure: $\approx 5 \times 10^{-8}$ mbar), KrF excimer laser ( $\lambda = 248$ nm), halogen lamp heater, target and substrate stages, optics for the alignment of incident laser to the surface of targets, and gas inlets (O <sub>2</sub> , Ar, and N <sub>2</sub> ).                                                                                                                                           | 44 |

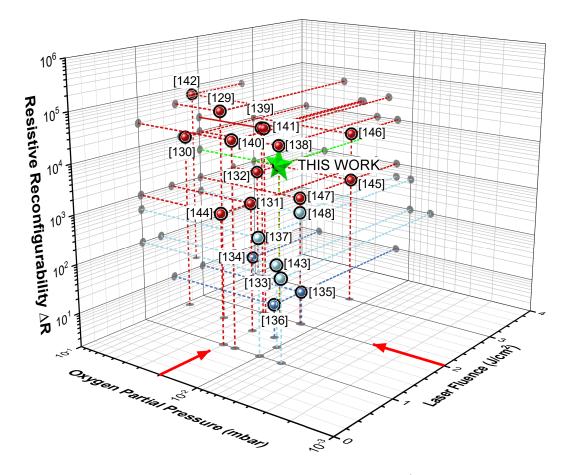

| 3.4  | A comparison of resistance switching ratios ( $\Delta R$ of various VO <sub>2</sub> films<br>grown by different PLD deposition parameters ( $P_O$ and laser fluence)<br>using data from [129–148]; Blue data points represent reported films<br>that show resistive switching ratios lower than 10 <sup>3</sup> while deep blue data<br>points correspond to switching ratios lower than 10 <sup>2</sup>                                                                                             | 49 |

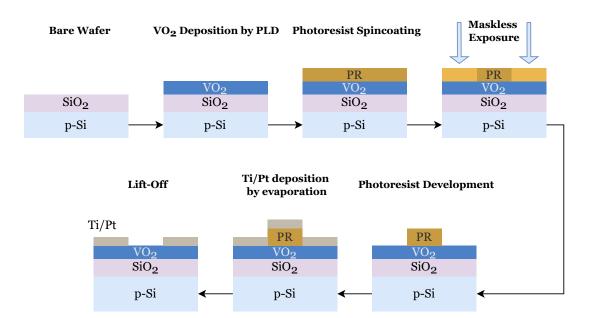

| 3.5  | An established process flow for the fabrication of two-terminal $VO_2$ devices                                                                                                                                                                                                                                                                                                                                                                                                                       | 51 |

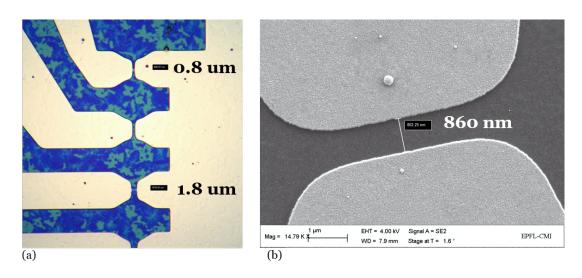

| 3.6  | Optical microscopy (a) and SEM (b) images for the fabricated two-<br>terminal $VO_2$ lateral devices                                                                                                                                                                                                                                                                                                                                                                                                 | 52 |

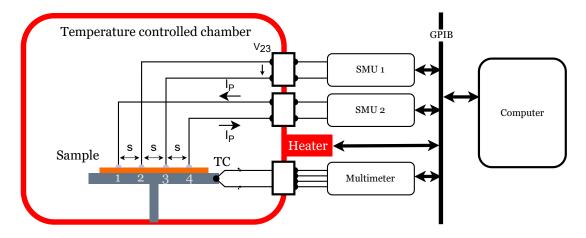

| 3.7  | Four-point probing setup used for resistivity measurement of the $VO_2$ thin films in a temperature-controlled environment $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                             | 53 |

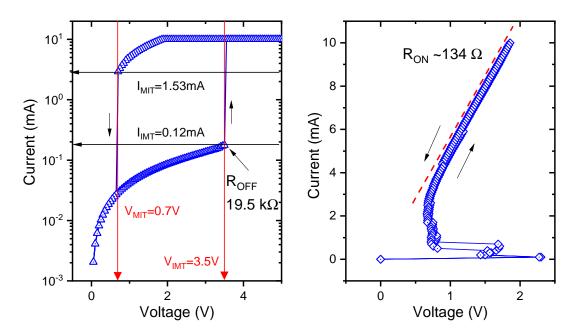

| 3.8  | Semiconductor parameter analyzer measurements: (a) - Current-Voltage characteristic allowing extraction of IMT and MIT threshold voltages along with IMT and MIT currents and off-state resistance, and (b) - Voltage-Current characteristic allowing extraction of on-state resistance $R_{ON}$                                                                                                                                                                                                     | 54 |

|      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

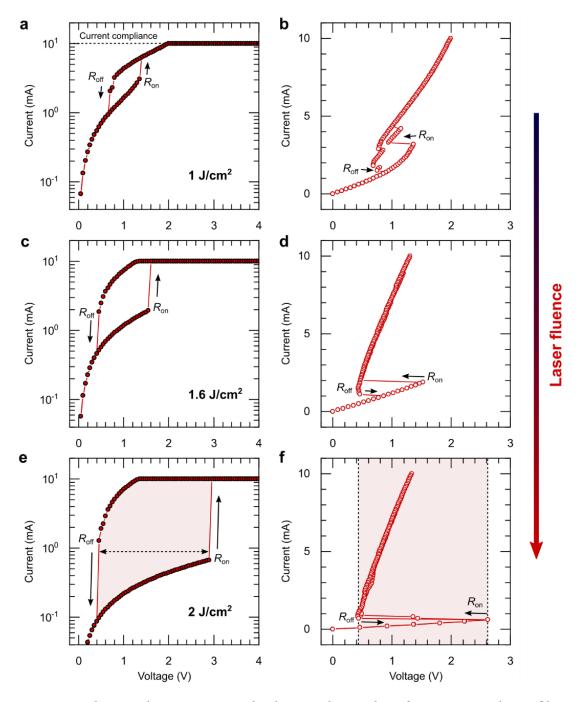

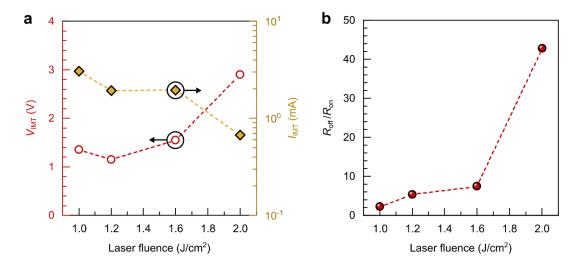

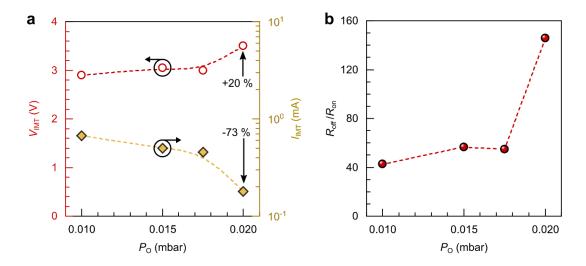

- 3.10 (a) The threshold voltage and current for the insulator-metal transition of the VO<sub>2</sub> devices as a function of laser fluence; (b) - The resistance switching ratios ( $R_{OFF}/R_{ON}$ ) of the devices as a function of laser fluence 58

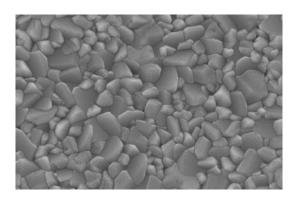

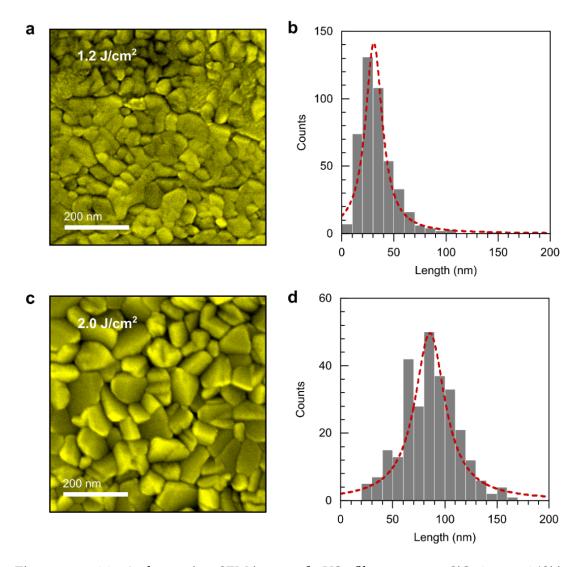

- 3.11 (a) A planar view SEM image of a VO<sub>2</sub> film grown on SiO<sub>2</sub>(200nm)/Si in  $P_O = 0.01 mbar$  with a relatively low laser fluence of 1.2  $J/cm^2$ ; (b) -The corresponding grain size distribution. The averaged grain size is 35 nm; (c) - An SEM image of a VO<sub>2</sub> film grown using a higher laser fluence of 2  $J/cm^2$ , while all other parameters were kept the same; (d) - The corresponding grain size distribution, with an average grain size of 86nm 59

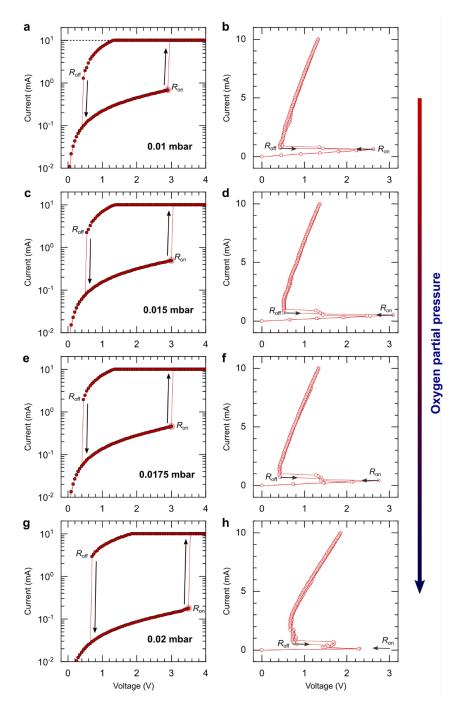

- 3.12 The I-V characteristics in both V- and I-modes of two-terminal VO<sub>2</sub> film devices as a function of PO. The left panels (a,c,e,g) show the current variations of the devices, measured by double voltage sweeping (0V 5V 0V). The right panels (b,d,f,h) show the voltage changes of the devices, measured by current injection (0A 10mA 0A) . . . . . . . . . . . 60

- 3.13 (a) The threshold voltage and current for the insulator-metal transition of the VO<sub>2</sub> devices as a function of  $P_{O_2}$ ; (b) - The resistance switching ratios ( $R_{OFF}/R_{ON}$ ) of the devices as a function of  $P_{O_2}$  . . . . . . . . . 61

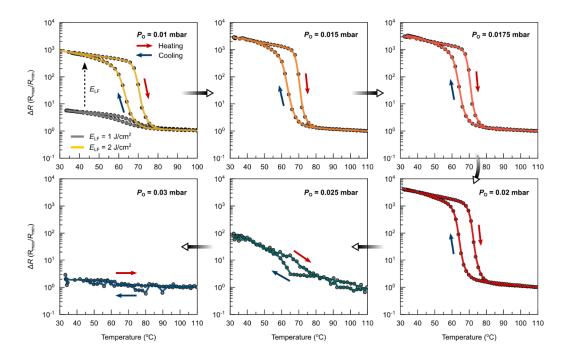

- 3.14 Temperature-dependent resistance variations of the VO<sub>2</sub> films as a function of P<sub>O2</sub>, grown by laser fluence  $E_{LF}$  of 2  $J/cm^2$ . The resistance variation of each sample was recorded by temperature sweeps (heating to cooling 30 °C  $\rightarrow$  110 °C  $\rightarrow$  30 °C). For comparison, the resistance variations of the films are determined by  $R_{MAX}/R_{MIN}$ . Only the upper left panel compares the thermally induced resistance changes of the films, grown at different laser fluence (1  $J/cm^2$  and 2  $J/cm^2$ ) in P<sub>O2</sub> (0.01 mbar). 62

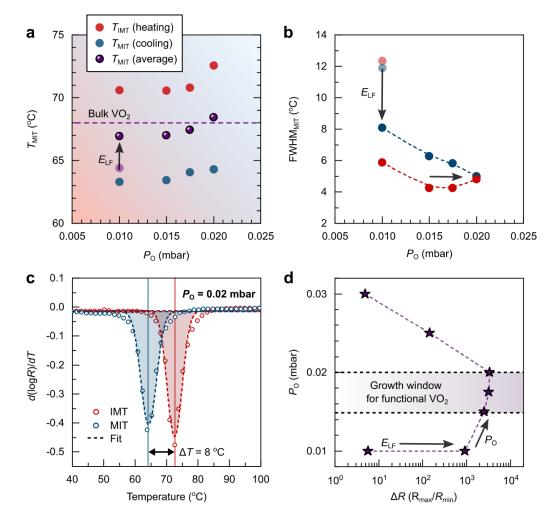

| 3.15 | (a) - Variations in the IMT, MIT, and averaged transition $[(T_{IMT}+T_{MIT})/2]$           |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | temperatures of the VO <sub>2</sub> films grown by different $P_{O_2}$ . When $P_{O_2}$ in- |    |

|      | creases up to $P_{O_2}$ = 0.02 mbar, the averaged phase transition temper-                  |    |

|      | atures reaches a typical MIT temperature (68 °C) of bulk VO <sub>2</sub> . (b) The          |    |

|      | FWHM values for $d(log R)/dT$ versus T plots of the IMT and MIT, which                      |    |

|      | reflect the abruptness of the phase transitions. (c) A $d(logR)/dT$ versus                  |    |

|      | T plot for a VO <sub>2</sub> film grown in $P_{O_2} = 0.02$ mbar which shows symmetrical    |    |

|      | IMT and MIT with a hysteresis width of $\Delta T = 8^{\circ}C$ . (d) The optimized          |    |

|      | growth window (0.015 mbar $\ge P_{O_2} \ge 0.02$ mbar, 2 $J/cm^2$ ) for the deposi-         |    |

|      | tion of high-quality functional VO <sub>2</sub> films with high resistance variations       |    |

|      | (>10 <sup>3</sup> )                                                                         | 63 |

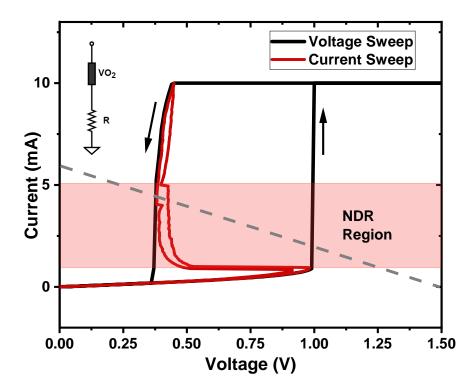

| 4.1  | VO <sub>2</sub> switching characteristic in the I-V space showing the region of             |    |

|      | negative differential resistance, along with the load line of an arbitrarily-               |    |

|      | valued resistor in series.                                                                  | 68 |

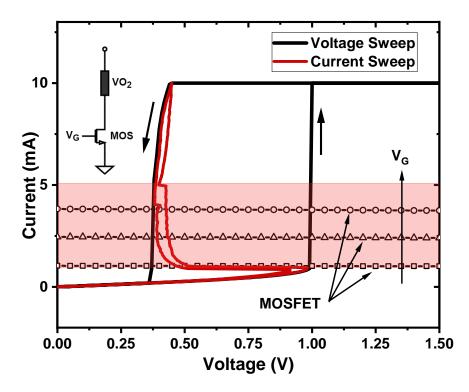

| 4.2  | VO <sub>2</sub> switching characteristic in the I-V space showing the region of nega-       |    |

|      | tive differential resistance, along with the load line of a series connected                |    |

|      | n-type MOSFET                                                                               | 69 |

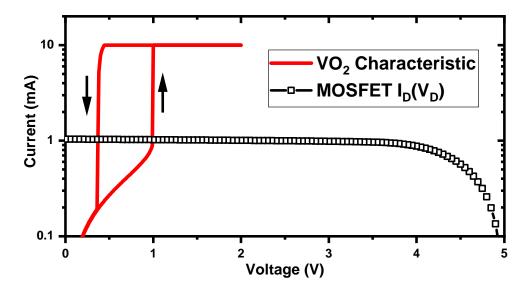

| 4.3  | VO <sub>2</sub> switching characteristic in the I-V space and the complete MOSFET           |    |

|      | load line, at a supply voltage of $V_S = 5V$ and gate voltage $V_G = 2.5V$                  | 70 |

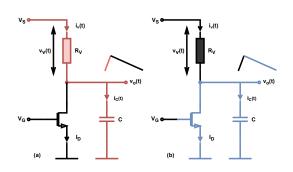

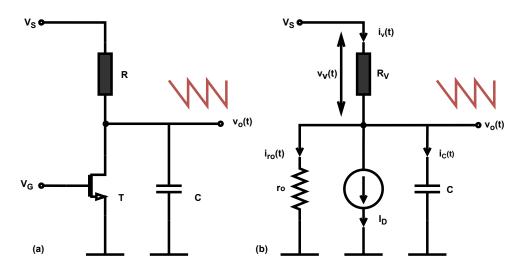

| 4.4  | (a) - Schematic of the VO <sub>2</sub> voltage controlled spiking oscillator alongside      |    |

|      | (b) - its small signal equivalent circuit                                                   | 71 |

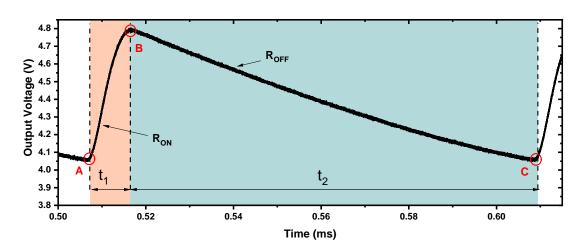

| 4.5  | One oscillation period, revealing the exponential transitions between                       |    |

|      | points A, B and C that define the limits of the linear charge and discharge                 |    |

|      | regimes, and the associated charging and discharging times $t_1$ and $t_2$ .                | 74 |

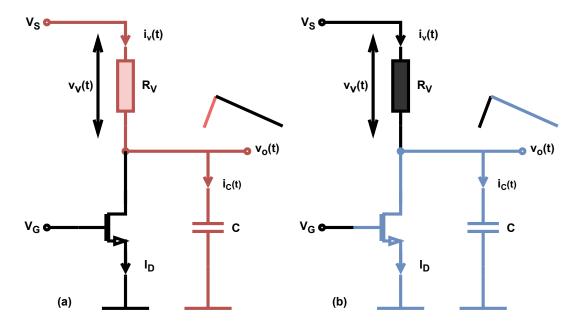

| 4.6  | Description of the "least resistance path" when (a) the VO <sub>2</sub> element is          |    |

|      | found in metallic state ( $R_V = R_{ON}$ ) and (b) when it is showing insulating            |    |

|      | behavior $(R_V = R_{OFF})$                                                                  | 75 |

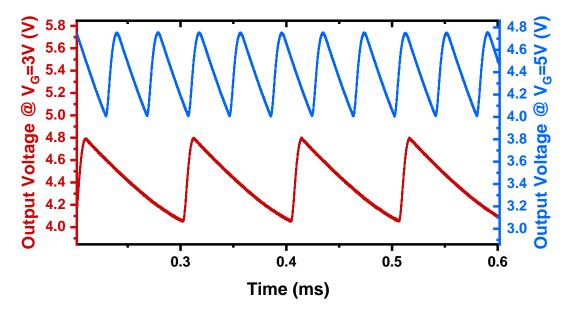

| 4.7  | Oscilloscope capture of the VCO output voltage under two distinct con-                      |    |

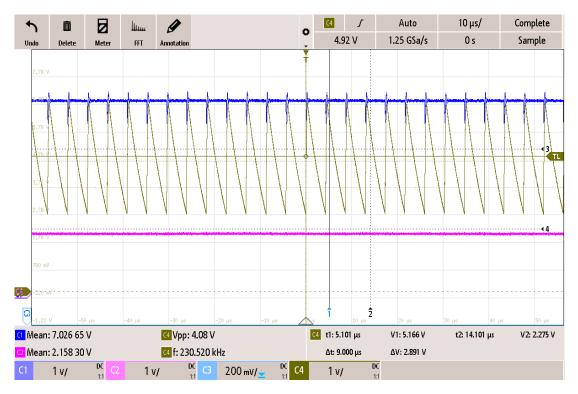

|      | trol voltages: $V_G = 3V$ and $V_G = 5V$                                                    | 76 |

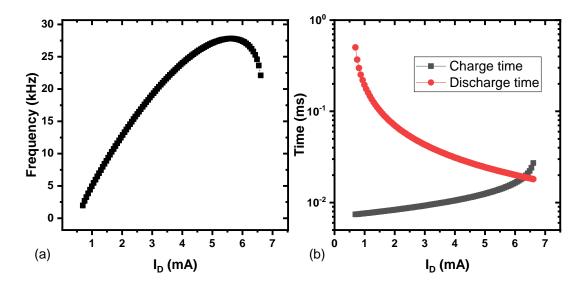

| 4.8  | (a) - The frequency range of the spiking oscillator, within the bounds set                  |    |

|      | by equation 4.10 showing a sudden decrease at high bias currents; (b) -                     |    |

|      | Simulation of the relaxation periods across the tuning range, crossing at                   |    |

|      | maximum frequency and causing decrease of frequency at high current                         |    |

|      | levels                                                                                      | 77 |

|      |                                                                                             |    |

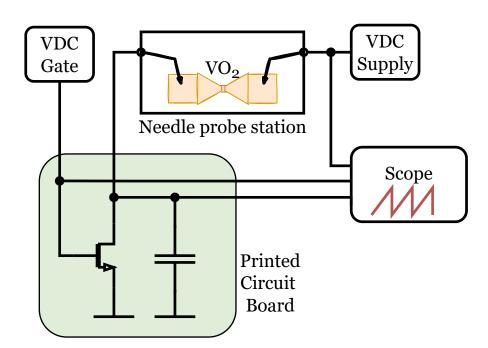

| 4.9 Oscillator measurement setup, outlining the connections between the                                                                                                                                                                                          |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| biasing supplies, the oscilloscope, the printed circuit board and the                                                                                                                                                                                            | 70        |

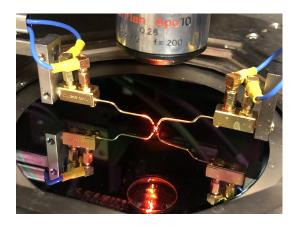

| needle probing station used for contacting $VO_2$ devices                                                                                                                                                                                                        | 79        |

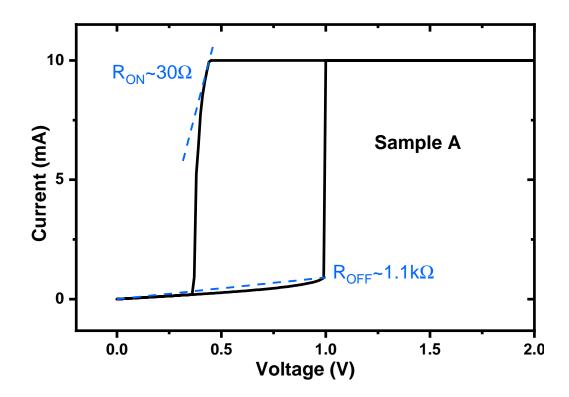

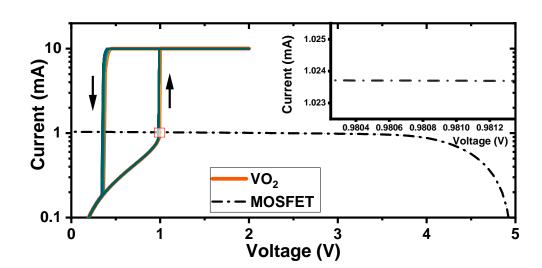

| 4.10 I-V Measurement used to extract the device parameters of Sample A                                                                                                                                                                                           | 80        |

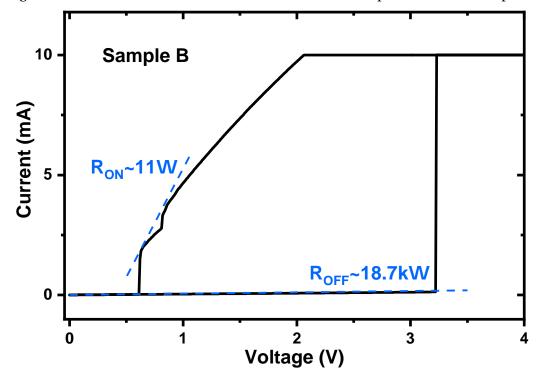

| 4.11 I-V Measurement used to extract the device parameters of Sample B                                                                                                                                                                                           | 80        |

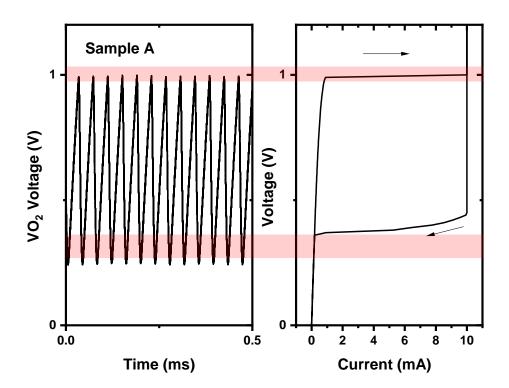

| 4.12 Right - The I-V characteristic of Sample A rotated such that the volt-<br>age axis is aligned with Left - the voltage drop across Sample A during<br>oscillation                                                                                            | 82        |

| 4.13 Right - The I-V characteristic of Sample B rotated such that the volt-<br>age axis is aligned with Left - the voltage drop across Sample B during<br>oscillation                                                                                            | 82        |

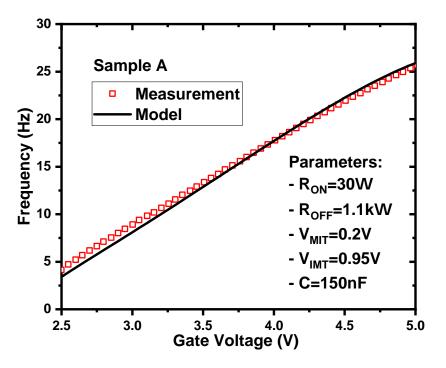

| 4.14 Comparison of the analytical prediction of oscillator frequency with re-<br>spect to experimental data gathered using Sample A. Model parameters<br>in inset                                                                                                | 84        |

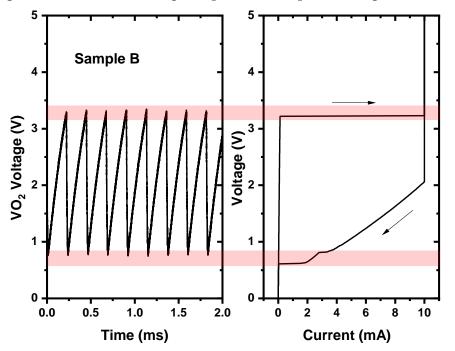

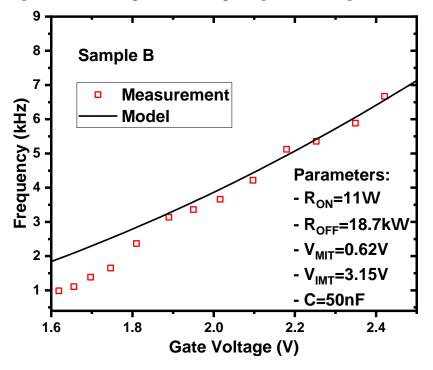

| <ul> <li>4.15 Comparison of the analytical prediction of oscillator frequency with respect to experimental data gathered using Sample B. Model parameters in inset</li> <li>4.16 Time-domain representation of the modeled oscillator output superim-</li> </ul> | 84        |

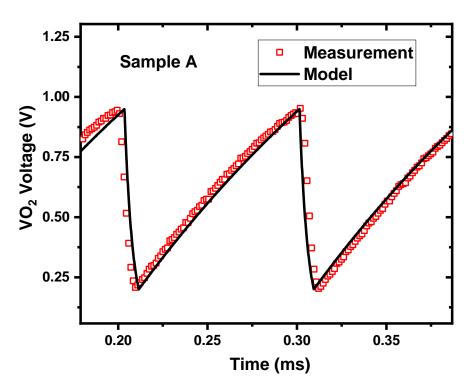

| posed over the experimental waveform capture - Sample A                                                                                                                                                                                                          | 85        |

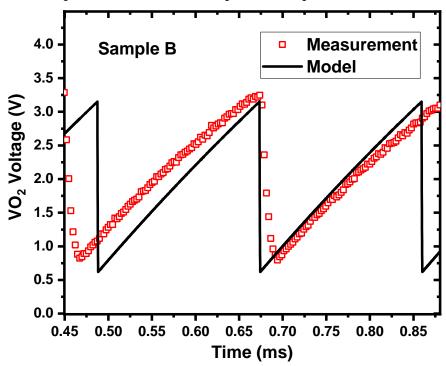

| 4.17 Time-domain representation of the modeled oscillator output superim-<br>posed over the experimental waveform capture - Sample B                                                                                                                             | 85        |

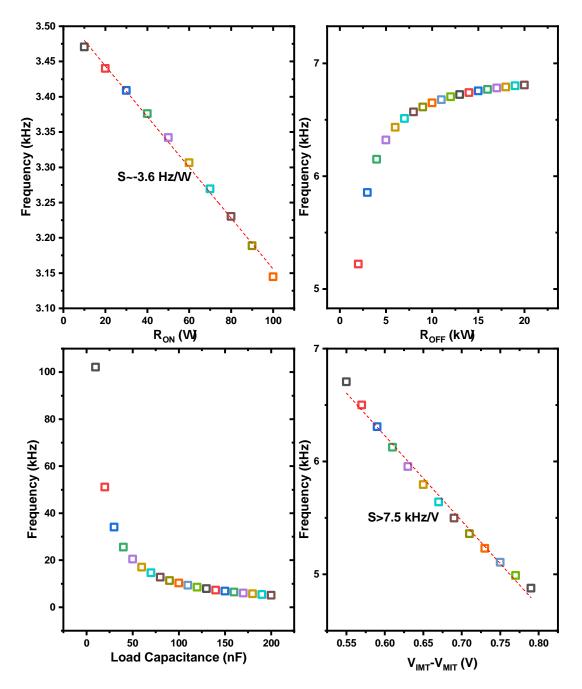

| 4.18 Sensitivity of oscillator frequency with respect to device and circuit parameters, in particular $R_{ON}$ , $R_{OFF}$ , load capacitance and VO <sub>2</sub> hysteresis window $V_{IMT} - V_{MIT}$                                                          |           |

| 4.19 Waveform capture of the VCO loaded only by the parasitic capacitance of the output node, showing oscillation frequencies higher than 200 kH                                                                                                                 | z 88      |

| 4.20 VO <sub>2</sub> static characteristic superimposed with the MOSFET loadline (V <sub>G</sub> =2. at supply bias of 5V. Inset shows random variation of the switching threshold across 50 switching cycles.                                                   | 5V)<br>90 |

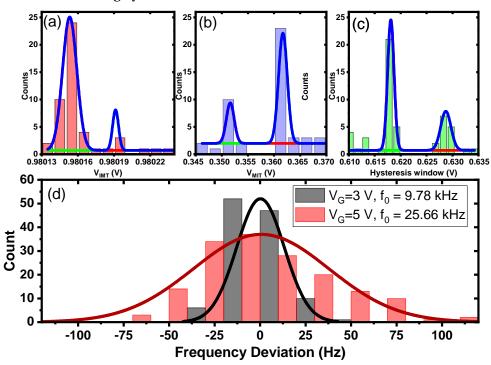

| 4.21 Threshold voltage histograms for a - $V_{IMT}$ , b - $V_{MIT}$ , c - hysteresis win-<br>dow; d - histogram showing the distribution of the frequency deviation<br>from the average value at $V_G = 3V$ and $V_G = 5V$ .                                     | 90        |

### LIST OF FIGURES

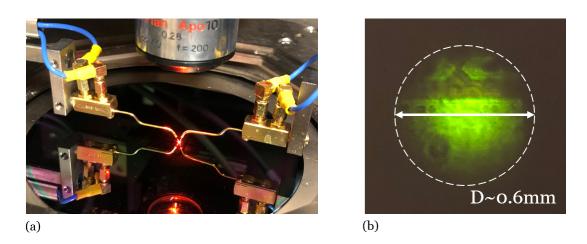

| 5.1 | (a) - The laser focusing setup on the wafer probing station, showing the needle probes used to contact the VO <sub>2</sub> devices and the laser spot focused by the microscope optics on the wafer surface; (b) - Low-resolution photograph of the illuminated device showing a beam diameter of approximately 0.6 mm. The dimension was estimated starting from the known dimensions of the contact pads visible in the picture.         | 94  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

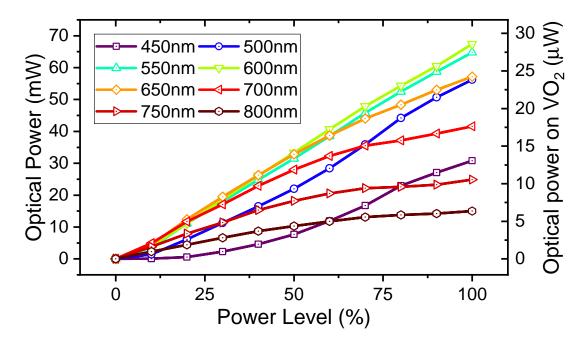

| 5.2 | Optical power measurement at the end of the optical chain at setpoints<br>between 0 and 100% and wavelengths between 450nm and 800nm. On<br>the left Y axis we represent the power levels recorded with the pow-<br>ermeter at the wafer level while on the right Y axis we represent the<br>calculated optical power incident on the active $VO_2$ device area. The<br>X-axis corresponds to the user-set percentage of the maximum laser | 94  |

|     | power                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95  |

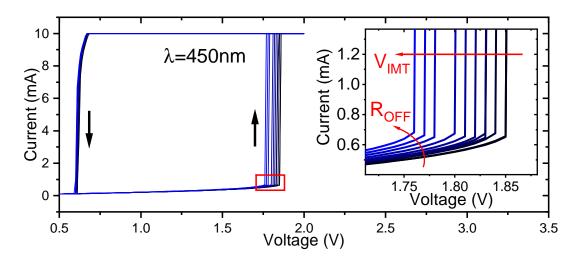

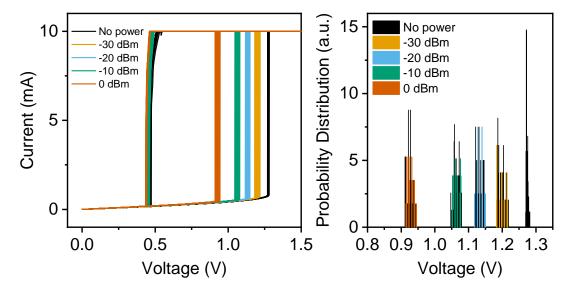

| 5.3 | Current-Voltage characteristic of the VO <sub>2</sub> device subjected to increasing optical power levels at $\lambda = 450 nm$ . Inset illustrates that as the incident power is increased, the IMT transition threshold $V_{IMT}$ decreases, accompanied by a slight increase in the off-state resistance $R_{OFF}$                                                                                                                      | 97  |

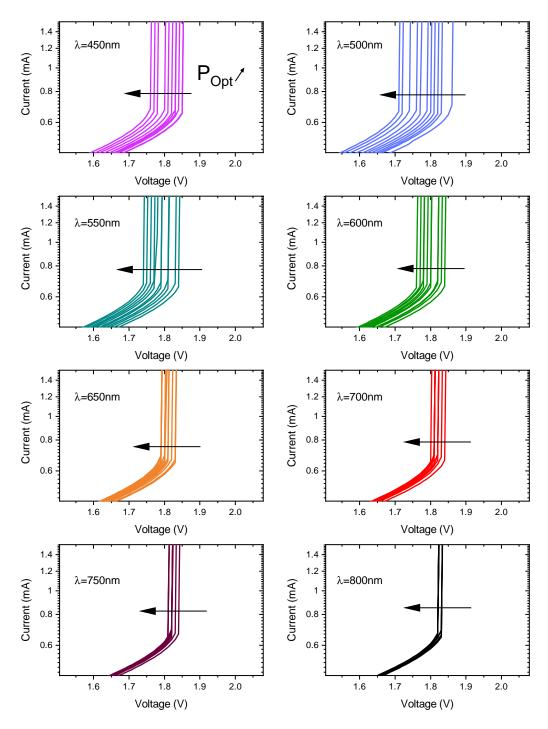

| 5.4 | Current-Voltage characteristic of the VO <sub>2</sub> device subjected to increasing optical power levels at eight key wavelengths across the visible spectrum. Arrows indicate a downward shift in the IMT threshold $V_{IMT}$ and the magnitude of the shift depends considerably on wavelength                                                                                                                                          | 98  |

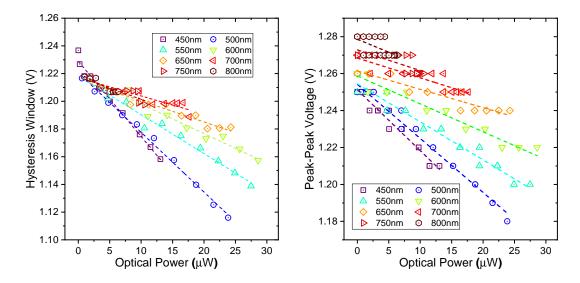

| 5.5 | Left: The VO <sub>2</sub> hysteresis window width, extracted from static I-V char-<br>acteristics under optical stimulation across the visible spectrum; Right:<br>Measurement of the peak-to-peak voltage of the oscillator output under<br>optical stimulation across the visible spectrum                                                                                                                                               | 99  |

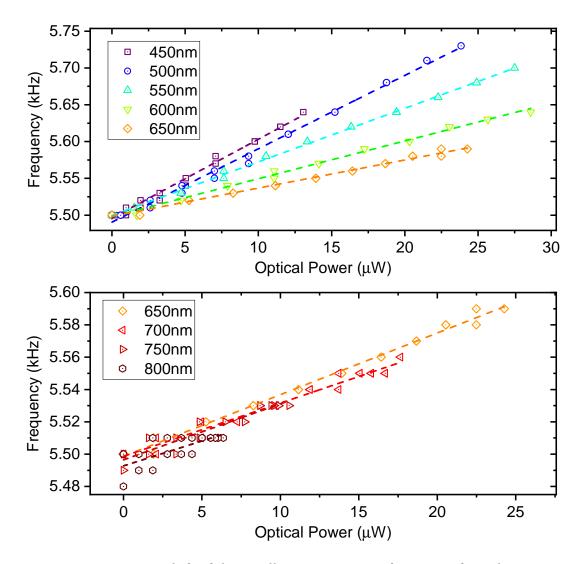

| 5.6 | Frequency shift of the oscillator output as a function of incident power<br>at different wavelength of the visible spectrum, with a drift correction of<br>-80 Hz/h applied. The curves were separated in order to improve clarity<br>of the long-wavelength plots.                                                                                                                                                                        | 100 |

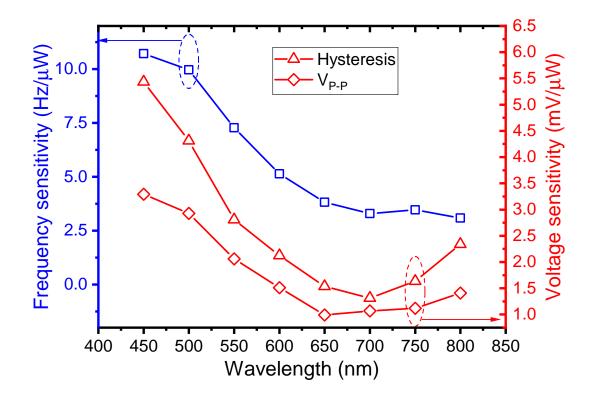

| 5.7 | Experimentally extracted sensitivities of oscillator output frequency,<br>hysteresis window width and peak-to-peak voltage to incident optical                                                                                                                                                                                                                                                                                             |     |

|     | power as a function of wavelength                                                                                                                                                                                                                                                                                                                                                                                                          | 101 |

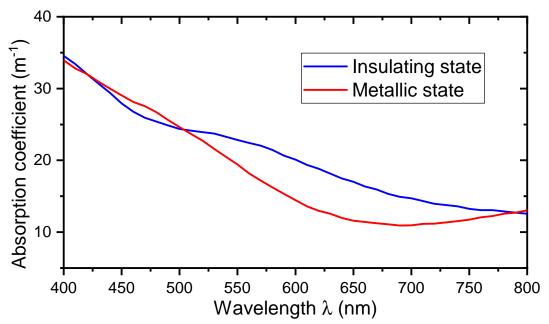

| 5.8 | The absorption coefficient of $VO_2$ in the insulating and metallic states                                                                                                                                                                                                                                                                                                                                                                 |     |

|     | as a function of wavelength. Data from [169]                                                                                                                                                                                                                                                                                                                                                                                               | 101 |

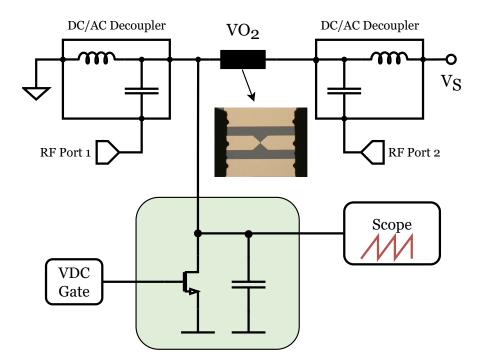

| 5.9 Measurement setup used to carry out experiments investigating effect of incident mmWave radiation on the switching dynamics of and output frequency of the VO <sub>2</sub> oscillator. Inset shows the microso capture of the interrupted co-planar waveguide (CPW) that contains VO <sub>2</sub> device.                                                                                                      | VO <sub>2</sub><br>cope<br>s the |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.10 (a) The effect of external RF excitation at multiple power levels or static I-V characteristics of the VO <sub>2</sub> device, indicating a strong influe of incident radiation on the IMT threshold voltage $V_{IMT}$ ; (b) The p ability distribution of the $V_{IMT}$ threshold voltages at different polevels confirming a considerable downwards shift as a consequent increasing incident power levels. | ence<br>prob-<br>ower<br>ce of   |

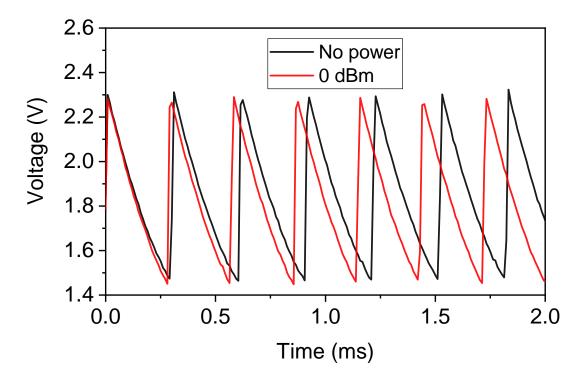

| 5.11 Oscilloscope capture of the oscillator output waveform under no app<br>power and at 0 dBm of applied RF power, outlining a clear increas<br>oscillation frequency as a consequence of external stimulation of<br>VO <sub>2</sub> device                                                                                                                                                                       | se in<br>f the                   |

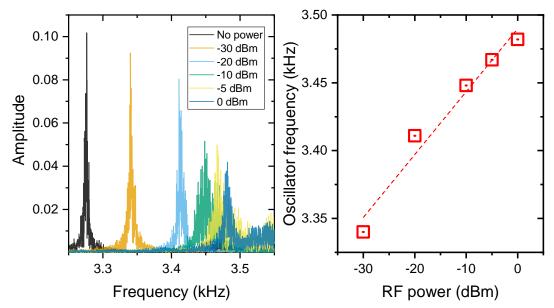

| 5.12 (a) - FFT spectra of the oscillator output voltage at RF power learning from -30 dBm up to 0 dBm, including the case where no powas applied; (b) - Oscillator output frequency represented as a function of incident RF power                                                                                                                                                                                 | ower                             |

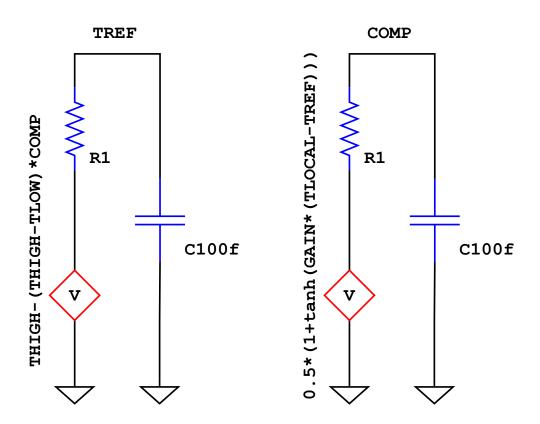

| 5.13 Schematic implementation of the Hysteretic comparator using two<br>havioral sources that implement the comparator equations. Resis<br>R1 and capacitors C100f are used as convergence aids                                                                                                                                                                                                                    | stors                            |

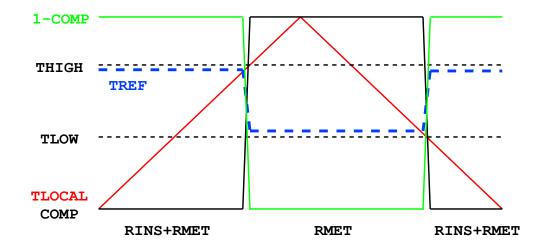

| 5.14 Qualitative depiction of the mechanism that enables hysteretic op<br>tion of the comparator, outlining the evolution of internal variables<br>function of local device temperature <i>TLOCAL</i>                                                                                                                                                                                                              | as a                             |

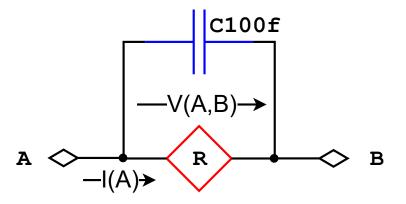

| 5.15 Schematic implementation of the behavioral resistor that models<br>electrical resistance of the VO <sub>2</sub> device controlled by the compar-<br>output. The capacitor C100f is used as convergence aid. Arrows indi-<br>the voltage drop across the VO <sub>2</sub> V(A,B) and the current flowing thro-<br>the device, measured at terminal A, I(A).                                                     | rator<br>icate<br>ough           |

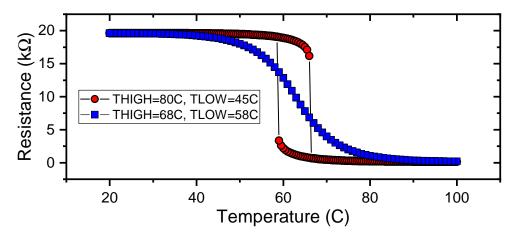

| 5.16 Simulation result of the temperature-dependent resistance of the device with $THIGH$ and $TLOW$ values that allow (red) or inhibit (be the formation of a hysteresis loop in the $R(T)$ characteristic.                                                                                                                                                                                                       | olue)                            |

### LIST OF FIGURES

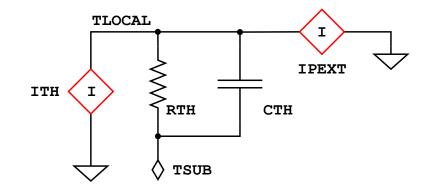

| 5.17 | Schematic implementation of the Joule heating thermal network, where                 |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | the thermal resistance and capacitance of the $VO_2$ device RTH and CTH              |     |

|      | are used to calculate the local temperature rise over ambient as a conse-            |     |

|      | quence of dissipated power - modeled by the behavioral current source                |     |

|      | ITH and external incident power - modeled by the behavioral current                  |     |

|      | source IPEXT.                                                                        | 113 |

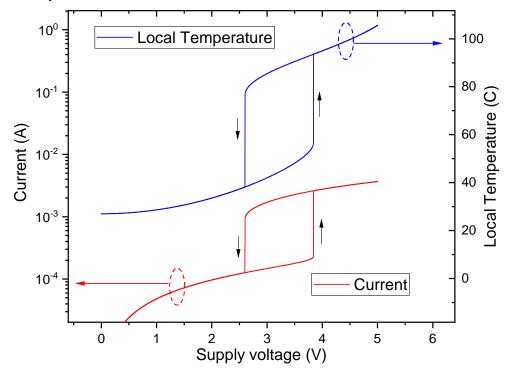

| 5.18 | Simulated voltage sweep of the modeled VO <sub>2</sub> device using a series re-     |     |

|      | sistor of $1.2k\Omega$ implemented for current limiting. With current levels         |     |

|      | limited to $\approx$ 5mA, the modeled local device temperature rises to just         |     |

|      | above 100C, comparable with reported values measured using Scanning                  |     |

|      | Thermal Microscopy [172]. Device current is represented on the left axis,            |     |

|      | while device temperature is represented on the right axis                            | 113 |

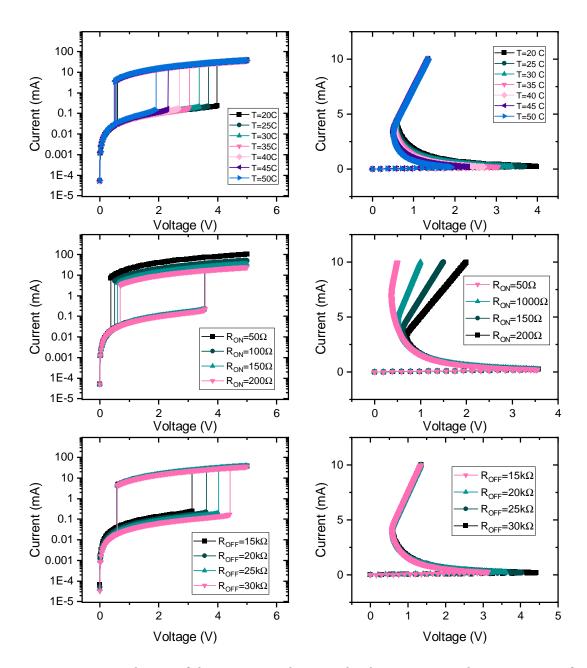

| 5.19 | Simulation of the current-voltage and voltage-current characteristics of             |     |

|      | the $VO_2$ model indicating the influence of model parameters on switch-             |     |

|      | ing dynamics: (a, c, e) - I-V curves at different temperatures, $R_{On}$ and         |     |

|      | $R_{Off}$ , respectively; (b, d, f) - V-I curves at different temperatures, $R_{On}$ |     |

|      | and $R_{Off}$ , respectively                                                         | 114 |

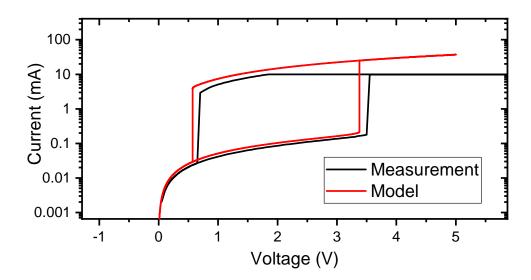

| 5.20 | Direct comparison between the measured device and the simulated                      |     |

|      | device model, using the parameters from table 5.1. The flattening of the             |     |

|      | measured curve is due to the current compliance limit set at 10mA. $\ . \ .$         | 115 |

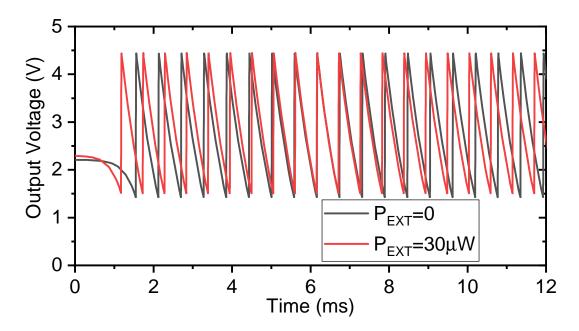

| 5.21 | Simulated oscillator waveforms with no applied power (black) and with                |     |

|      | $30 \mu W$ of external power applied (red)                                           | 117 |

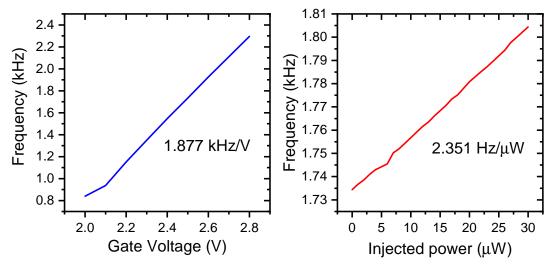

| 5.22 | (a) - Simulated frequency-voltage characteristic indicating a sensitivity            |     |

|      | of 1.877 kHz/W; (b) - Simulated frequency-injected power characteristic              |     |

|      | with a sensitivity of 2.351 Hz/ $\mu$ W                                              | 117 |

# List of Tables

| 2.1 | TFET figures of merit at key temperatures: 300K, 150K and 10K        | 23  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | Temperature variation of device parameters in Bulk CMOS processes .  | 25  |

| 2.3 | Temperature variation of device parameters in an FD-SOI CMOS process | 25  |

| 2.4 | TCAD Simulation parameters                                           | 29  |

|     |                                                                      |     |

| 4.1 | PLD recipes used for samples A and B                                 | 79  |

| 4.2 | Model parameters for samples A and B                                 | 81  |

|     |                                                                      |     |

| 5.1 | Simulation parameters                                                | 115 |

# 1 Introduction and rationale

The Internet-of-Things (IoT) represents an ecosystem of interconnected sensors and devices deployed at large scales that enables physical "things" such as computing devices, machines or objects to collect and transmit data continuously and communicate by leveraging network connectivity (internet or local networks). The IoT revolution is relevant today in a number of contexts, ranging from environment monitoring and agriculture, the automotive and manufacturing industry, all the way to personal healthcare and energy management in smart homes. As technology costs are lowering, increasing numbers of internet-capable devices and sensors such as smartphones or smart wearables are built and deployed, and contribute to the accelerated growth of the IoT ecosystem.

A direct consequence of the widespread nature of IoT "nodes" is the generation of vast amounts of data that is ever increasing [1] and that requires realtime, autonomous and secure information generation and processing, putting strain on the architecture of communication networks, standardization and, importantly, energy efficiency [2]. The emergence of IoT was accompanied by the development of Cloud and Edge-of-Cloud (EoC) technologies that enabled heavy computation and storage to be performed by networks of dedicated data centers while EoC devices handled data acquisition and interfacing with end-user devices (figure 1.1). Recently, however, focus is shifting towards performing smart computation at the EoC level, in order to circumvent possible limitations induced by the infrastructure or energy consumption and communication latency. For example, as the amounts of data that needs to be processed are growing, performing computation directly at the edge has a beneficial impact on energy efficiency and network throughput [3], saving energy and bandwidth associated with uploading/downloading raw and processed data to and from the Cloud. In addition, certain critical functionalities such as those enabled by intelligent sensors used for healthcare require fast, realtime processing, in addition to ensuring data privacy and security [4]. As the growing amounts of data that need to be handled worldwide have pushed today's technologies into the "Zettabyte era" [1], the improvement in energy efficiency of both Cloud and EoC technologies is becoming challenging, with a new role being played by moving more "intelligence" to the Edge (such as the so-called "tiny machine learning" [5]). Energy efficiency, realtime processing and local intelligence opened new opportunities for the role of bio-inspired neuromorphic computing architectures and new devices and materials beyond the exclusive use of traditional silicon CMOS.

The rapid growth of Information and Communication Technologies (ICT) was enabled and accelerated in the latter half of the past century by breakthrough discoveries and inventions in the field of electronics such as the first transistor, developed at Bell Labs in 1947 [6], the first integrated circuit developed by Kilby and Noyce in 1959 [7], the invention and first production of the nowadays ubiquitous metal-oxide-semiconductor field effect transistor (MOSFET) in 1960 [8] and the evolution step represented by the Complementary Metal-oxide-Semiconductor (CMOS) platform that allowed to drastically reduce cost and improve performance of the fundamental digital building blocks for computing technology. In the years that followed, the microelectronics industry focused its resources on MOSFET miniaturization towards the nanoscale (with transistor dimensions smaller than 100nm). By decreasing transistor sizes, device capacitances decreased allowing for higher maximum operating frequencies which led to an increased overall performance of integrated circuits. In 1965 Gordon Moore (co-founder of Intel) observed based on the data available at that time that the number of devices comprised in integrated circuits increased steadily over time and predicted that such an increase would continue, doubling the number of components every two years [9].

The establishment of silicon-based CMOS technology, along with the development of precise semiconductor doping processes enabled the beginning of the "happy scaling" era, closely following Moore's prediction through the implementation of geometrical device scaling principles set forth by Robert Dennard in 1974 [10]. By following the constant field scaling laws proposed by Dennard, the industry was able to keep up with Moore's Law mainly by means of geometric scaling of transistor

Figure 1.1: The Edge-to-Cloud information processing model for AI, suggesting unsustainable, inefficient and slow zettabyte data movement. Adapted from [1]

dimensions and the proportional increase in doping concentration and decrease in supply voltage necessary in order to satisfy the constant electric field guideline. As the trend continued, the introduction of technology boosters was necessary in order to overcome limitations that were not detectable in early, larger technology nodes. Notable examples include the adoption of high- $\kappa$  dielectrics and metal gates [11] and strain-engineered Si and SiGe channels with increased carrier mobility [12].

Based on all technological innovations, Moore's Law has been respected and followed by the industry for decades to reach device densities of more than 100 million transistors per  $mm^2$  but today it is facing a triple challenge: (i) limits of physics and principles, (ii) limits of energy efficiency, and (iii) limits of costs per transistor that started to slightly increase for technologies below 28nm.

In this complex context, the development of new materials and device concepts has an increasingly important role with two main trends that are recognized by the nanoelectronics community: (i) **scaling the operation voltage** (and consequently increase the energy efficiency) of digital and analog electronics, and (ii) **providing new functionalities** beyond the one of conventional MOSFET devices.

Within the first category, the classes of so-called steep slope switches emerged after

2010, among which Tunnel FETs [13–15], Negative Capacitance FETs [16–18] and Nano-Electro-Mechanical (NEM) switches [19–21]. Interestingly, in this quest, the phase change switches (based on the reversible metal-insulator transition in functional oxide materials) offer an interesting and promising combination of both steep-slope switching and new functionality, linked to their hysteretic behavior and to their high sensitivity to a large number of external stimuli like temperature, electromagnetic waves, light, strain, magnetic fields. [22].

Therefore, in this work we decided to focus on two classes of devices: (i) **Tunnel FETs for charge detection** (especially in the context of necessary alternative charge detectors to Single Electron Transistors (SETs) at deep cryogenic temperature) and (ii) **Phase-change switches to build new spiking sensors** architectures serving some of the challenges of IoT and Edge Artificial Intelligence (Edge AI) with innovations from materials to devices to circuit level. While for the first topic we established a cooperation with Lund University for providing some of the most advanced nanowire Tunnel FETs, on the second topic we have developed and optimized a technology based on Vanadium Dioxide (VO<sub>2</sub>) that can be co-integrated with CMOS in order to build new classes of spiking oscillators serving to develop multiple classes of sensors capable of detecting different types of stimuli. We particularly focused on this direction, from technology, to analytical modeling and experimental validations.

Therefore, the manuscript is organized in four chapters, dealing with the following topics: Chapter 2 - Charge sensing for Qubit readout using Tunnel FETs, Chapter 3 - Phase transition characteristics of  $VO_2$  thin films, Chapter 4 - A 1T-1R Spiking Voltage Controlled Oscillator based on  $VO_2$ , and Chapter 5 -  $VO_2$  Oscillators for sensing. Chapters 3, 4, and 5 are highly interconnected as they jointly deal with the field of  $VO_2$ -based spiking sensors, while Chapter 2 is a rather standalone work on the evaluation of an external technology.

This work has been carried out in the context of the Millitech ERC Advanced Grant, aiming at a novel technology platform that serves both computation and sensing using steep slope switches that exploit new device physics and concepts with the ultimate goal to achieve operation at voltages below 100 millivolts, which enabled collaborative work between a number of PhD students and post-doctoral fellows at EPFL.

### 1.1 Thesis Outline

This thesis is structured as follows:

### **Chapter 2: Charge Sensing for Qubit Readout using Tunnel FETs**

In this chapter we evaluate the functionality of Tunnel FETs at low temperatures with focus on liquid-helium temperatures as low as 10K. We perform an experimental study using state-of-the-art heterojunction nanowire TFET arrays and observe that their analog and digital figures of merit are quasi-insensitive to temperature variations when BTBT remains the dominant carrier transport mecha-

nism. Continuing, we propose that double-gate TFETs could harness the temperatureinsensitive steep subthreshold slope to provide enhanced sensitivity towards single or few elementary charges. To this end, we validate the sensing concept via TCAD simulations and propose an optimization strategy for increasing sensitivity to elementary charges. In closing, we perform an experimental proof-of-concept using Silicon-on Insulator SiGe/Si line tunneling TFETs.

### Chapter 3: Phase transition characteristics of VO<sub>2</sub> thin films

In chapter 3 we become familiar with Vanadium Dioxide ( $VO_2$ ), a functional oxide which represents a promising candidate towards achieving new and interesting functionalities in electronics. We provide an overview on the multitude of stimuli that  $VO_2$  is sensitive to, outlining its importance for novel sensing architectures. We continue by establishing an

optimized set of growth parameters by Pulsed Laser Deposition focusing on CMOS

compatibility. We study the influence of Laser fluence and Oxygen partial pressure during deposition and establish an optimal "growth window" - a set of growth parameters that ensure reproducible, high quality CMOS-compatible VO<sub>2</sub> depositions.

Chapter 4: A 1T-1R Voltage Controlled Spiking Oscillator based on VO<sub>2</sub>

In this chapter we explore the simple but interesting implementation of a 1Transistor-1Resistor (1T-1R) voltage controlled oscillator based on twoterminal VO<sub>2</sub> devices. We perform static and dynamic analyses of the circuit and find that key metrics of the oscillating output such as frequency and amplitude

are closely correlated to the intrinsic properties of the  $VO_2$  device, such as phase transition thresholds and electrical resistance, suggesting that the VCO can be used as a compact sensing unit that exploits the sensitivity of  $VO_2$  towards a wide variety of stimuli.

#### Chapter 5: VO<sub>2</sub> Oscillators for optical sensing (and beyond)

In the final chapter of this work, we continue the journey set forth at the end of chapter 4 and experimentally validate the functionality of the  $VO_2$  spiking oscillators as sensors. In the first study we investigate the sensitivity of  $VO_2$  intrinsic device parameters and oscillator output towards visible light radiation ranging from near UV to near infrared light in eight distinct wavelength bands. We find that oscillation frequency is strongly de-

pendent on incident power and wavelength, with higher sensitivities towards the shortwavelength end of the spectrum. We continue the exploration of sensing functionality by "illuminating" the VO<sub>2</sub> device with RF mmWave power via coplanar waveguides and we find that the sensitivity of the VCO circuit is preserved also in this region of the spectrum. The final chapter ends with the proposal of a SPICE-compatible device model that aims to capture key behaviors of  $VO_2$  such as its hysteretic resistance-temperature characteristic and effects of self heating and external power stimuli.

# 2 Charge Sensing for Qubit Readout using Tunnel FETs

# 2.1 Introduction

The aggressive geometric scaling of the feature size in the now ubiquitous CMOS technology has had an extraordinary impact on circuit performance, with considerable improvements being made in terms of switching speed, device density, functionality and cost [13]. A direct consequence of geometric scaling, however, is the proportional reduction of supply voltage required to maintain the constant electric field, as per Dennard's scaling laws [10]. However, supply voltage scaling needs to be accompanied by a corresponding decrease in threshold voltage  $V_T$ . Although not specifically required by Dennard rules, scaling of the  $V_T$  is necessary in order to ensure sufficient overdrive voltage  $V_{OV} = V_{DD} - V_T$ , as this directly influences the maximum achievable on-current  $I_{ON} \propto (V_{DD} - V_T)^2$ , which is required for high performance operation of digital circuits, particularly related to switching capacitive loads at high speeds thus ensuring high operating frequency.

In addition, the behavior of the MOSFET in the subthreshold regime (where the semiconductor channel is in weak inversion and the drain current is diffusion-dominated) is of fundamental importance for applications that require low-power operation, as it determines the MOSFET's behavior when switching between off- and on-state, indirectly affecting static power dissipation in logic circuits.

The steepness of the transition between off- and on- states in MOSFETs is dictated by the Subthreshold Slope (SS), a parameter that describes the relationship between gate voltage  $V_G$  and drain current  $I_D$  in weak inversion, and can be expressed as:

Figure 2.1: (a) - Qualitative representation of the exponential increase in  $I_{OFF}$  as a consequence of supply voltage reduction; (b) - A comparison of transfer characteristic for a bulk Si MOSFET alongside a Tunnel FET, a high-mobility channel MOSFET a multi-gate MOSFET and an ideal switch. The TFET can offer a steeper subthreshold slope at the cost of lower on-current. Adapted from [13]

$$S = \underbrace{\frac{\partial V_G}{\partial \Phi_S}}_{\text{m}} \underbrace{\frac{\partial \Phi_S}{\partial (\log_{10} I_D)}}_{\text{n}} = \left(1 + \frac{C_d}{C_{ox}}\right) ln 10 \frac{kT}{q}$$

where  $\Phi_S$  represents the surface potential, and its relationship to gate voltage is given by the gate to channel coupling, also known as the "body factor"  $m = 1 + C_d/C_{ox}$  and depends on the depletion layer capacitance  $C_d$  and the gate oxide capacitance  $C_{ox}$ . The second factor *n* represents the relationship between surface potential  $\Phi_S$  and drain current, and is determined by the charge injection mechanism. In MOSFETs, the mechanism is represented by the thermionic emission of carriers [23] and the *n* term is described by n = ln10(kT/q) where *k* represents the Boltzmann constant and *q* is the electron charge.