Scalable fabrication of functional nanostructures on stretchable substrates by capillary-assisted particle assembly and adhesion lithography

Présentée le 19 mai 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire de microsystèmes 1 Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Henry Shao-Chi YU

Acceptée sur proposition du jury

Prof. M. Gijs, président du jury Prof. J. Brugger, directeur de thèse

Dr H. Wolf, rapporteur

Prof. F. Perez-Murano, rapporteur

Prof. G. Villanueva Luis, rapporteur

## **Acknowledgements**

I am grateful to Prof. Jürgen Brugger for giving me the opportunity to do a PhD in his group and providing me with his time to help me keep moving on in my challenging research topics. This opportunity means a lot to my uncommon career path.

I am thankful for having kind support and discussions from Dr. Giovanni Boero. His advice in physics and electronics enlightened me whenever I was lost in figuring the puzzles out. I truly admire his passion for scientific research and education.

It is my pleasure to work with my inspiring colleagues in LMIS1. I would like to thank all current lab members for the help and the time we spent together. In particular, I would like to thank my lovely office mates, Dr. Thomas Walger and Dr. Ana Conde-Rubio, for their favor in correcting parts of my thesis manuscript and for those memorable moments we shared, as a colleague and as a sincere friend. I would also like to thank Dr. Mohammadmahdi Kiaee for the viscosity measurement of prebaked PDMS, Reza Farsi for his tutoring in electronic noise analysis, and Dr. Samuel T. Howell for reading parts of my thesis manuscript and giving me suggestions on the thesis writing.

Furthermore, I would like to thank Hsiang-Chu Wang and Prof. Olivier Martin from NAM lab of EPFL for our collaboration in optical measurements and simulations for the published work.

I would like to also express my respect and gratitude to the staff from the Center of MicroNanoTechnology (CMi) and the IPHYS cleanroom for their expertise and services.

Throughout my PhD life, I had a deep bonding with the Taiwanese community here in Lausanne, I would never forget those heart-warming cheerings during each of our gatherings. Without this community, my Swiss life would have been much less enjoyable.

Last but not least, I would like to thank my wife Yi-Fen Shih who sacrificed her career to come to Switzerland with me and takes good care of me and our home unconditionally. I would not have finished this journey without her.

Lausanne, February 22, 2022

Henry Shao-Chi Yu

## **Abstract**

The fabrication of metallic nanostructures on stretchable substrates enables specific applications that exploit the combination of the nano-scale phenomena and the mechanical tunability of the physical dimensions of the nanostructures. Due to the large difference in the thermal expansion coefficient between metals and polymer-based soft materials, patterning metallic nanostructures directly on a stretchable substrate is a known challenging task. In this thesis, scalable fabrications of metallic nanostructures on stretchable substrates by top-down and bottom-up methods are studied. Metallic nanostructures are first fabricated on Si substrates and subsequently transferred to stretchable substrates.

In the first part of this thesis, fabrication of nanogap electrodes (NGEs) on a polydimethylsiloxane (PDMS) substrate using adhesion lithography is reported. With wafer-level processes, the nanogap is created on an Al sacrificial layer by separating two Au electrodes with an Al<sub>2</sub>O<sub>3</sub> nanolayer. By etching the Al sacrificial layer, the NGEs are transferred to the PDMS substrate. Tunneling currents across the nanogap on PDMS are measured under various mechanical deformation statuses of the PDMS substrate. The electrical measurement results show that the nanogap distance is mechanically tunable in the quantum tunneling regime. The NGEs on PDMS might be eventually integrated with micro piezo-electric actuators to become miniaturized tunable NGEs, which could pave the way towards the application of an on-chip single-molecule detector. Apart from developing the fabrication process of the NGEs on PDMS, a yield study of the essential step of the adhesion lithography, e.g., the tape peeling process, is also conducted to understand the design principles of the NGEs. The yield of the wafer-level tape peeling process is larger than 80%.

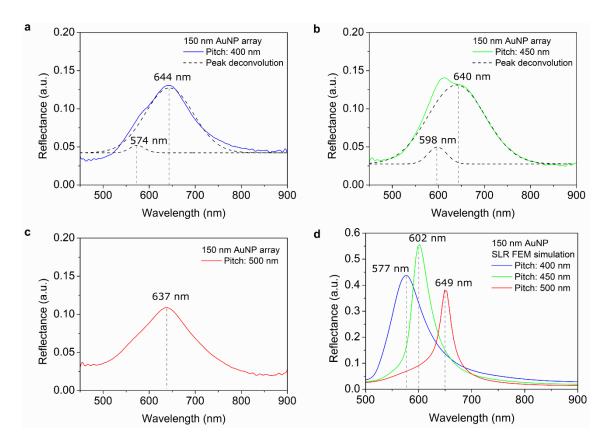

In the second part of this thesis, chip-level (~ 2 x 2 cm²) fabrication of ordered gold nanoparticles (AuNPs) on a PDMS substrate using capillary-assisted particle assembly (CAPA) technique is reported. AuNPs are first assembled on reusable Si templates with pre-defined topographical traps, and then transferred to the PDMS substrate by etching the Al sacrificial layer. The reusable assembly trap has the shape of the funnel which is designed for high assembly yield (> 90%) and precise particle placement (offset ~ 10 nm). The assembly yield, the particle position offset, the yield of the transfer process, and the reusability of the assembly template are systematically studied. Two functional AuNP structures are demonstrated using the reported fabrication process. The first structure is the plasmonic surface lattice resonance (SLR) arrays of 150 and 200 nm AuNP. The optical spectra of the AuNP arrays on PDMS are measured showing pitch-related SLR peaks that agree with the finite element method (FEM) simulation results. The second structure is the dimer of 200 nm AuNPs which has a nanogap between two AuNPs. By

assembling two AuNPs in the same funnel-shaped trap, a nanogap is formed between two AuNPs. Combining Au electrodes fabricated using electron beam lithography and the lift-off process, NGEs are fabricated and successfully transferred to a PDMS substrate.

#### Keywords

Nanogap electrodes, Adhesion lithography, Capillary-assisted particle assembly, CAPA, Surface lattice resonance, Stretchable substrate, Wet etching transfer, Tape peeling

## Résumé

La fabrication de nanostructures métalliques sur des substrats étirables permet des applications spécifiques qui exploitent la combinaison des phénomènes à l'échelle nanométrique et la possibilité de réglage mécanique des dimensions physiques des nanostructures. En raison de la grande différence de coefficient d'expansion thermique entre les métaux et les matériaux souples à base de polymères, la fabrication de nanostructures métalliques directement sur un substrat étirable est une tâche difficile. Dans cette thèse, les fabrications évolutives de nanostructures métalliques sur des substrats étirables par des méthodes descendants et ascendants sont étudiées. Des nanostructures métalliques sont d'abord fabriquées sur des substrats de Si et ensuite transférées sur des substrats étirables.

Dans la première partie de cette thèse, la fabrication d'électrodes à nano-espace (NGE) sur un substrat de polydiméthylsiloxane (PDMS) à l'aide de la lithographie par adhérence est rapportée. Le nano-espace est créé sur une couche sacrificielle d'Al en séparant deux électrodes d'Au avec une nano-couche d'Al<sub>2</sub>O<sub>3</sub>. En gravant la couche sacrificielle d'Al, les NGE sont transférées sur le substrat en PDMS. Les courants tunnels à travers le nanoespace sur le PDMS sont mesurés sous différents états de déformation mécanique du substrat PDMS. Les résultats des mesures électriques montrent que la distance du nanogap est mécaniquement réglable dans le régime de l'effet tunnel quantique. Les NGE sur PDMS pourraient éventuellement être intégrés à des micro-actionneurs piézoélectriques pour devenir des NGE miniaturisés et réglables, ce qui pourrait ouvrir la voie à l'application d'un détecteur de molécules uniques sur puce. Outre le développement du processus de fabrication des NGE sur PDMS, une étude de rendement de l'étape essentielle de la lithographie par adhésion, c'est-à-dire le processus de décollement du ruban, est également menée pour comprendre les principes de conception des NGE. Le rendement du processus de transfert par décollement de film adhésif effectué sur des plaquettes est supérieur à 80%.

Dans la deuxième partie de cette thèse, la fabrication au niveau des puces (~ 2 x 2 cm²) de nanoparticules d'or ordonnées (AuNPs) sur un substrat en PDMS en utilisant la technique d'assemblage de particules assistée par capillarité (CAPA) est rapportée. Les AuNPs sont d'abord assemblées sur des moules Si réutilisables avec des pièges topographiques prédéfinis, puis transférées sur le substrat PDMS en gravant la couche sacrificielle d'Al. Le piège d'assemblage réutilisable a une forme d'entonnoir qui est conçue pour un rendement d'assemblage élevé (> 90%) et un placement précis des particules (le décalage ~ 10 nm). Le rendement de l'assemblage, le décalage de la position des particules, le rendement du processus de transfert et la réutilisabilité du moule d'assemblage sont systématiquement étudiés. Deux structures d'AuNP fonctionnelles

sont démontrées en utilisant le procédé de fabrication rapporté. La première structure est un réseau de AuNPs (150 et 200 nm) plasmoniques à résonance de réseau (SLR). Les spectres optiques des réseaux d'AuNP sur PDMS sont mesurés et montrent des pics de SLR liés au pas et qui correspondent aux résultats de la simulation FEM. La deuxième structure est le dimère d'AuNPs (200 nm) qui présente un nano-espace entre deux AuNPs. En assemblant deux AuNPs dans le même piège en forme d'entonnoir, un nano-espace est formé entre deux AuNPs. En combinant des électrodes en Au fabriquées par lithographie par faisceau d'électrons et le processus de lift-off, les NGEs sont fabriquées et transférées avec succès sur un substrat en PDMS.

#### Mots-clés

Électrodes à nano-espace, lithographie par adhérence, assemblage de particules assisté par capillarité (CAPA), résonance de réseau, substrat extensible, transfert par gravure humide, décollement de bande.

## **Table of Content**

| Acknow    | ledgements                                                                    | V    |

|-----------|-------------------------------------------------------------------------------|------|

| Abstract  | t                                                                             | vi   |

| Résumé    |                                                                               | viii |

| Table of  | Content                                                                       | X    |

| List of F | igures                                                                        | xiii |

| List of T | ables                                                                         | xvii |

| List of E | quations                                                                      | xvii |

| Chapter   | 1 Introduction                                                                | 1    |

| 1.1       | Nanostructures on stretchable substrates                                      | 1    |

| 1.2       | Fabrication strategies                                                        | 2    |

| 1.3       | Thesis outline                                                                | 5    |

| -         | 2 Tunable nanogap electrodes on PDMS fabricated by adhesion                   | _    |

| lith      | nography                                                                      | 7    |

| 2.1       | Introduction                                                                  | 7    |

|           | 2.1.1 Nanogap electrodes                                                      | 7    |

|           | 2.1.2 Fabrication of nanogap electrodes                                       | 9    |

|           | 2.1.3 Aims and motivation                                                     | 10   |

| 2.2       | Fabrication process and design                                                | 11   |

| 2.3       | Gap distance tunability simulation                                            | 19   |

| 2.4       | Study of diffusion barrier layer                                              | 28   |

|           | 2.4.1 The effect of rapid thermal annealing to NGEs                           | 28   |

|           | 2.4.2 Sacrificial layer for the wet etching transfer process                  | 30   |

|           | 2.4.3 Using ALD Al <sub>2</sub> O <sub>3</sub> as the diffusion barrier layer | 31   |

|           | 2.4.4 Using TiW as the diffusion barrier layer                                | 35   |

| 2.5       | Yield study of the tape peeling process                                       | 40   |

|           | 2.5.1 Designs of test structures for yield study                              | 40   |

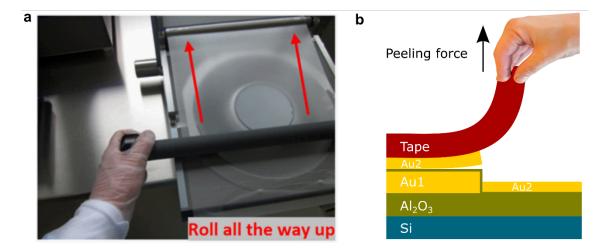

|           | 2.5.2 Tape bonding and peeling                                                | 43   |

|           | 2.5.3 Result and discussion                                                   | 44   |

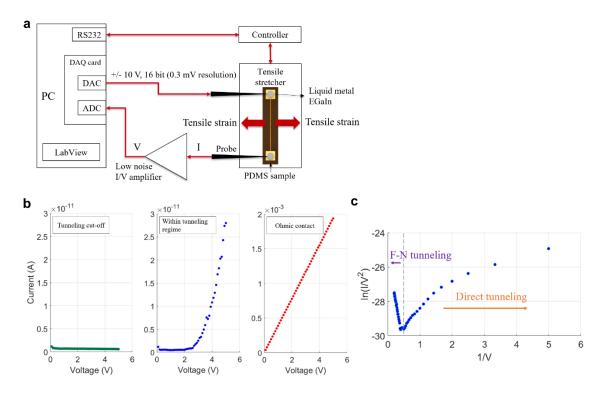

| 2.6       | Electrical characterization of the NGEs                                       | 50   |

|      |       | 2.6.1 Theory of metal-insulator-metal tunneling                       | .50 |

|------|-------|-----------------------------------------------------------------------|-----|

|      |       | 2.6.2 Mechanisms to change the nanogap distance                       | .51 |

|      |       | 2.6.3 Electrical measurement setup                                    | .51 |

|      |       | 2.6.4 Electrical measurement results of NGEs                          | .53 |

|      | 2.7   | Conclusion and outlook                                                | .60 |

| Chap | ter 3 | SLR arrays on PDMS fabricated by precise CAPA on reusable             |     |

|      | temp  | lates                                                                 | .63 |

|      | 3.1   | Introduction                                                          | .64 |

|      | 3.2   | Materials and methods                                                 | .65 |

|      |       | 3.2.1 Assembly template fabrication                                   | .65 |

|      |       | 3.2.2 Nanoparticle assembly                                           | .68 |

|      |       | 3.2.3 AuNP wet etching transfer and template recycle                  | .69 |

|      |       | 3.2.4 Assembly yield and position offset analysis                     | .70 |

|      |       | 3.2.5 Analysis of PDMS / OrmoComp substrates with transferred AuNPs   | 71  |

|      | 3.3   | Result and discussion                                                 | .71 |

|      |       | 3.3.1 AuNP assembly yield and position offset                         | .71 |

|      |       | 3.3.2 AuNP transfer                                                   | .75 |

|      |       | 3.3.3 The reusability of assembly templates                           | .78 |

|      |       | 3.3.4 Optical measurement of the SLR arrays on PDMS                   | .80 |

|      | 3.4   | Conclusion and outlook                                                | .83 |

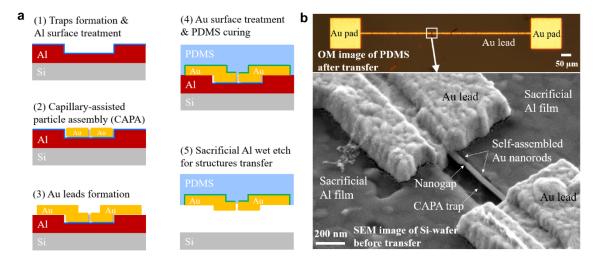

| Chap | ter 4 | NGEs on PDMS fabricated by CAPA                                       | .85 |

|      | 4.1   | Introduction                                                          | .85 |

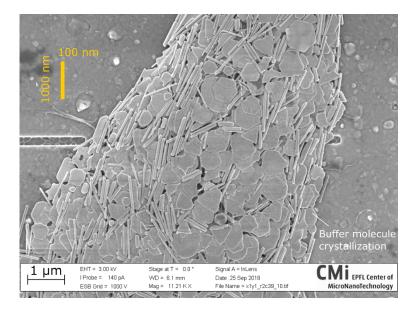

|      | 4.2   | NGEs fabricated by CAPA with Au nanorod                               | .86 |

|      |       | 4.2.1 High aspect ratio AuNR                                          | .86 |

|      |       | 4.2.2 NGEs fabrication                                                | .86 |

|      |       | 4.2.3 Electrical measurement                                          | .87 |

|      | 4.3   | NGEs fabricated by CAPA with AuNP in funnel traps                     | .90 |

|      | 4.4   | Conclusion and outlook                                                | .97 |

| Chap | ter 5 | Conclusion and outlook                                                | .99 |

|      | 5.1   | Tunable nanogap electrodes on PDMS fabricated by adhesion lithography |     |

|      | 5.2   | SLR arrays on PDMS fabricated by precise CAPA on reusable templates   | 100 |

|      | 5.3   | NGEs on PDMS fabricated by CAPA                                       | 100 |

| Bibliography     | 102 |

|------------------|-----|

| Curriculum Vitae | 109 |

# **List of Figures**

| <b>Figure 1.1.</b> Schematic working principle of transfer printing technique.                                                | 3  |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2. Schematic fabrication processes of dry peel-off and wet                                                           |    |

| etching transfer.                                                                                                             |    |

| <b>Figure 1.3.</b> Scheme of the research works in this thesis                                                                | 5  |

| Figure 2.1. Illustration of nanogap electrodes.                                                                               | 7  |

| Figure 2.2. NGEs applications on rigid substrates.                                                                            | 8  |

| Figure 2.3. Sub-2 nm NGEs applications on rigid substrates.                                                                   | 10 |

| <b>Figure 2.4.</b> Schematic illustration of the fabrication process of the tunable NGEs.                                     | 12 |

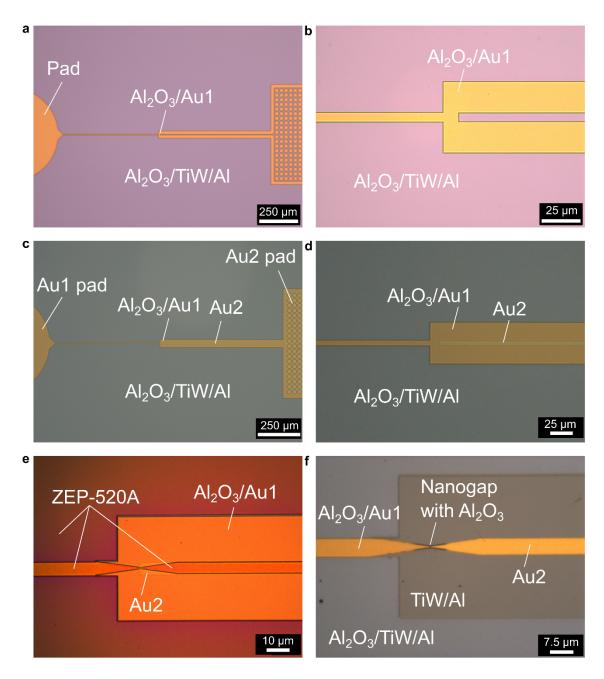

| <b>Figure 2.5.</b> OM images of the NGEs design after various process steps.                                                  | 13 |

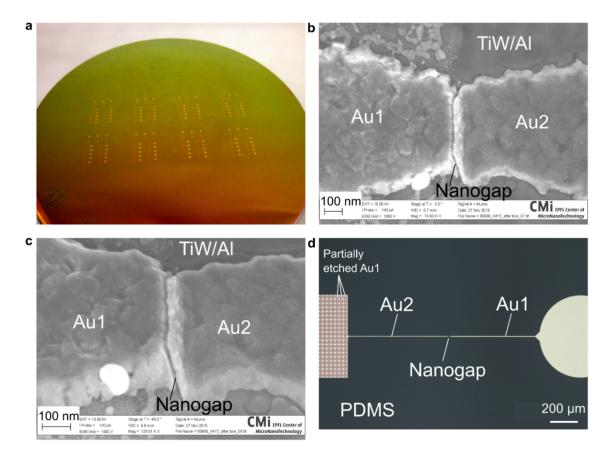

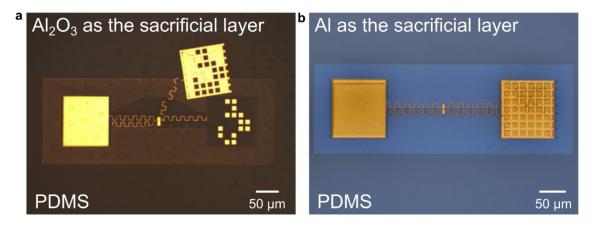

| <b>Figure 2.6.</b> Images of NGEs before and after the wet etching transfer process.                                          | 15 |

| Figure 2.7. Nanogap tunability study by COMSOL simulation                                                                     |    |

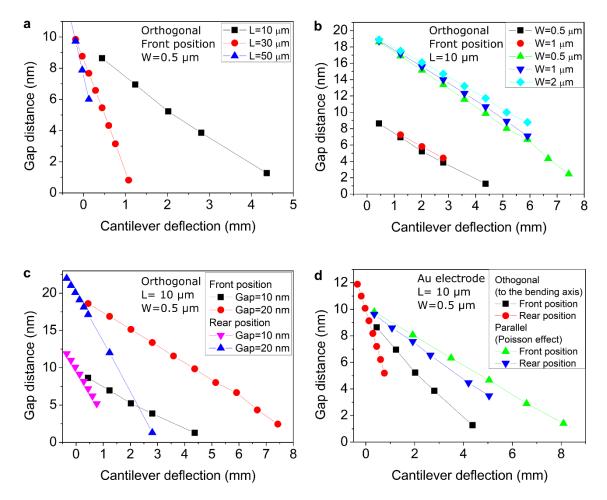

| Figure 2.8. COMSOL simulation results of the nanogap tunability                                                               | 22 |

| <b>Figure 2.9.</b> COMSOL simulation results of the sidewall profiles of the Au electrodes when the PDMS is strained.         | 23 |

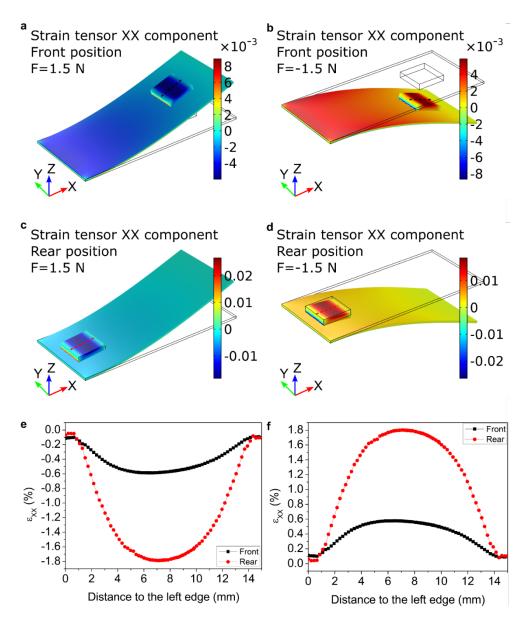

| <b>Figure 2.10.</b> COMSOL 3D surface plots of the strain tensor XX component of the bent PS cantilever.                      | 25 |

| <b>Figure 2.11.</b> COMSOL 3D surface plots of the strain tensor YY component of the bent PS cantilever                       | 26 |

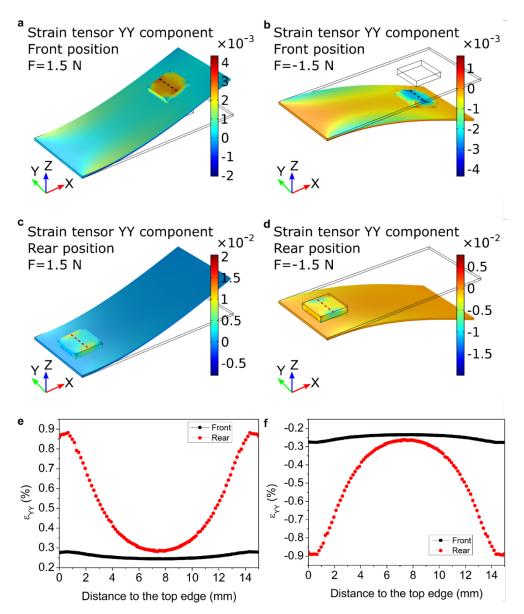

| <b>Figure 2.12.</b> COMSOL calculation results of the PDMS/cantilever bending.                                                | 27 |

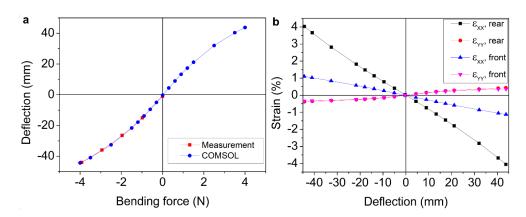

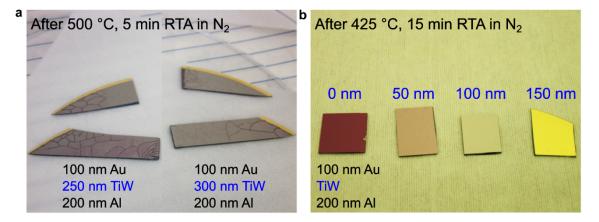

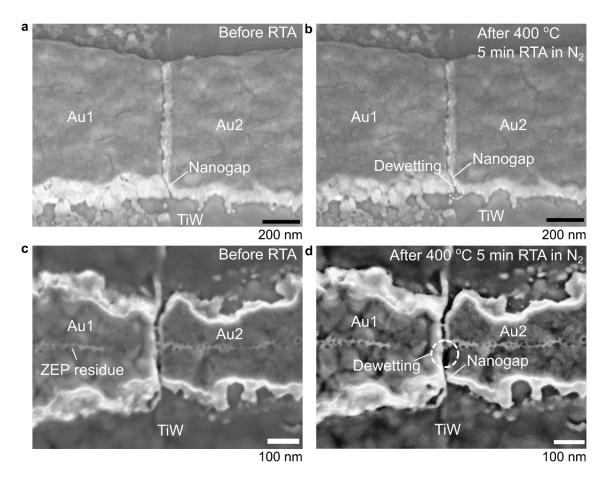

| Figure 2.13. Effect of 500 °C, 5 min RTA process to NGEs                                                                      | 29 |

| Figure 2.14. OM images of wet etching transfer results using different sacrificial layers                                     | 30 |

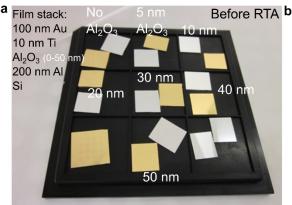

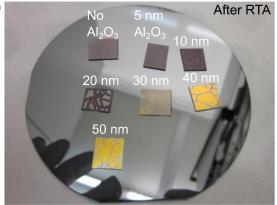

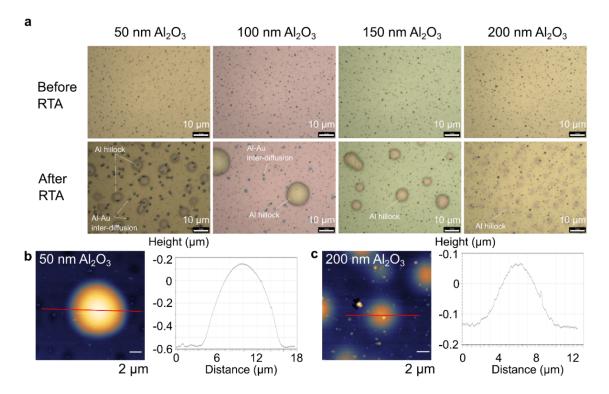

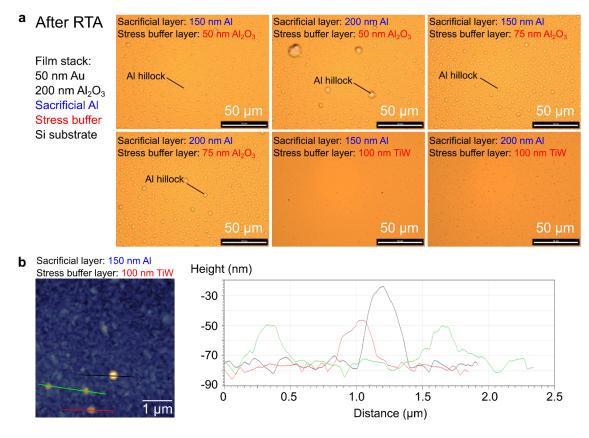

| <b>Figure 2.15.</b> Result of RTA experiment using Al <sub>2</sub> O <sub>3</sub> as the diffusion barrier layer up to 50 nm. | 31 |

| <b>Figure 2.16.</b> Result of RTA experiment using Al <sub>2</sub> O <sub>3</sub> as the diffusion barrier layer up to 200 nm | 32 |

| <b>Figure 2.17.</b> Result of RTA experiment with various stress buffer layers.                                                                                                                                            | 33 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

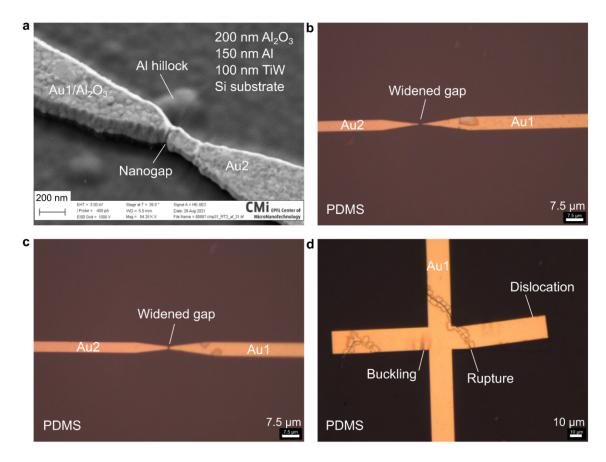

| <b>Figure 2.18.</b> Fabrication result of NGEs with 200 nm thick Al <sub>2</sub> O <sub>3</sub> as the diffusion barrier layer, 150 nm thick Al as the sacrificial layer, and 100 nm thick TiW as the stress buffer layer. | 35 |

| <b>Figure 2.19.</b> Results of RTA experiments with TiW as the diffusion barrier layer.                                                                                                                                    | 36 |

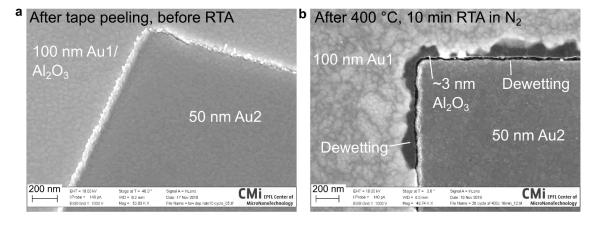

| <b>Figure 2.20.</b> Effect of 400 °C, 10 min RTA process to NGEs on test samples without Al/TiW layers.                                                                                                                    | 36 |

| Figure 2.21. Effect of 400 °C, 5 min RTA process to NGEs                                                                                                                                                                   | 37 |

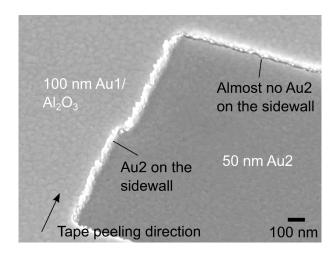

| <b>Figure 2.22.</b> 40° tilted-view SEM image of NGEs after the tape peeling process.                                                                                                                                      | 39 |

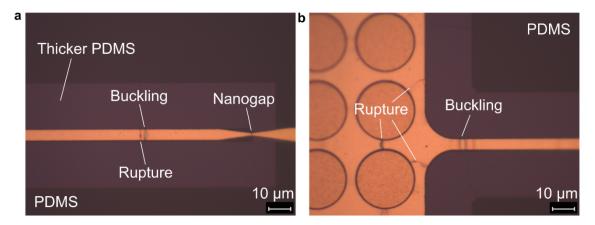

| <b>Figure 2.23.</b> OM images of NGEs on a PDMS substrate after the wet etching transfer process.                                                                                                                          | 39 |

| <b>Figure 2.24.</b> Illustrations of top and cross-sectional views of the tape peeling test structures.                                                                                                                    | 40 |

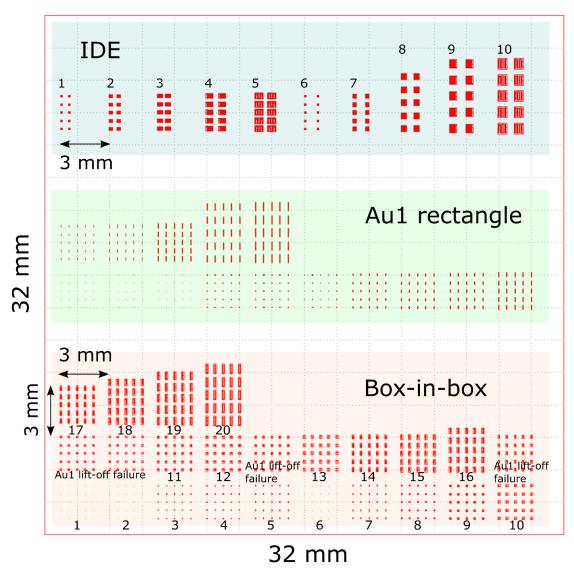

| <b>Figure 2.25.</b> Chip layout of test structures for the tape peeling experiment.                                                                                                                                        | 41 |

| <b>Figure 2.26.</b> Illustration of the wafer-level manual tape peeling process.                                                                                                                                           | 43 |

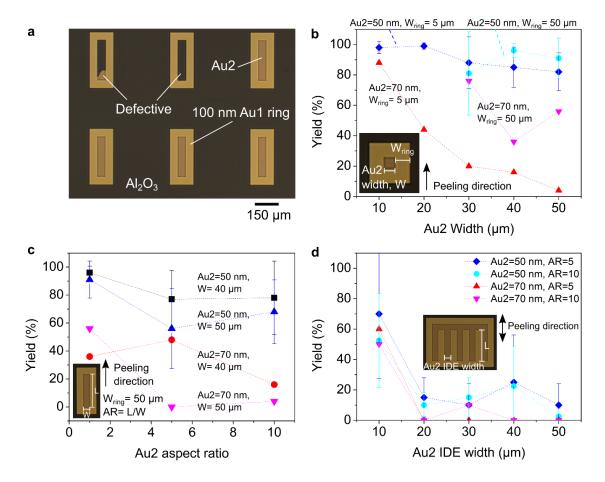

| Figure 2.27. The statistical results of the tape peeling yield study                                                                                                                                                       | 44 |

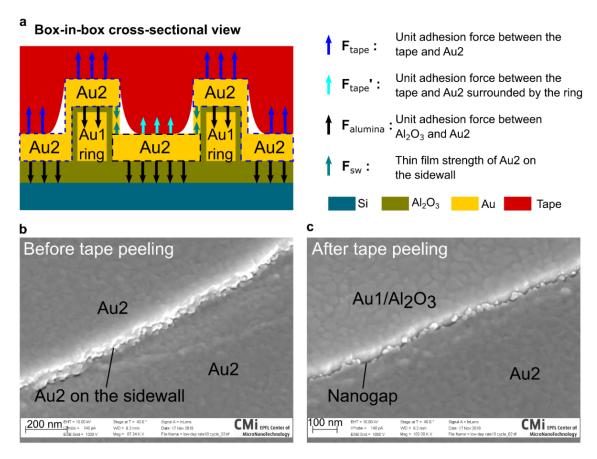

| <b>Figure 2.28.</b> (a) Illustration of the cross-sectional view of the box-in-box tape peeling test structure with the force diagram.                                                                                     | 45 |

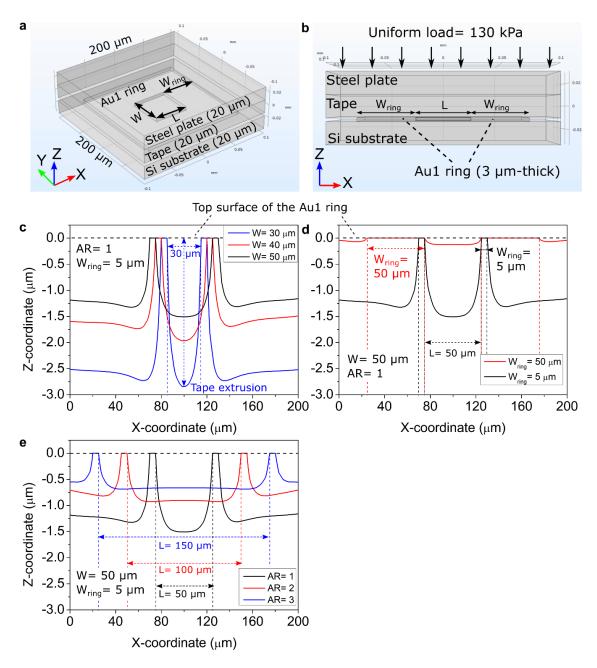

| <b>Figure 2.29.</b> COMSOL simulation study for the tape peeling experiments.                                                                                                                                              | 47 |

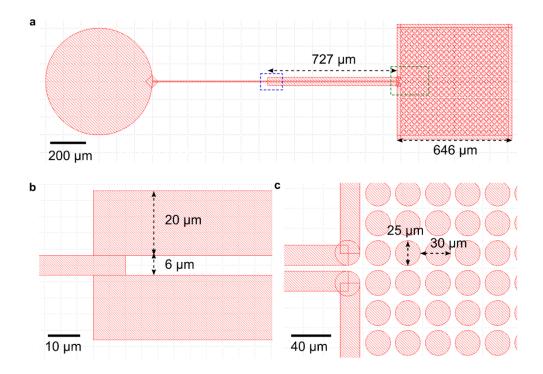

| Figure 2.30. The Au1 design of the NGEs in this work.                                                                                                                                                                      | 49 |

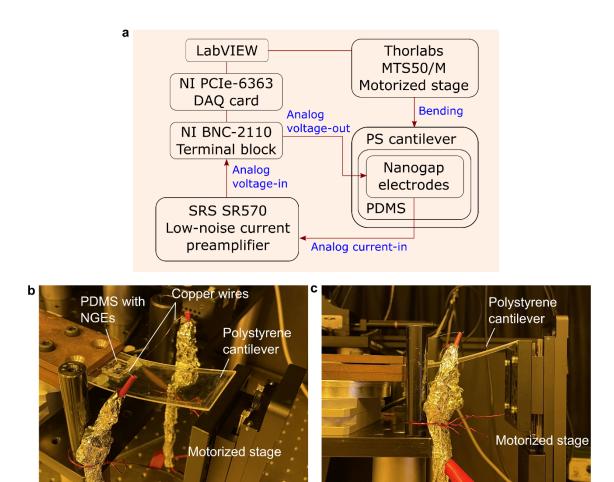

| Figure 2.31. Electrical measurement setup.                                                                                                                                                                                 | 52 |

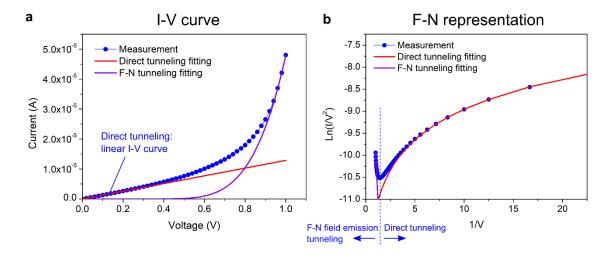

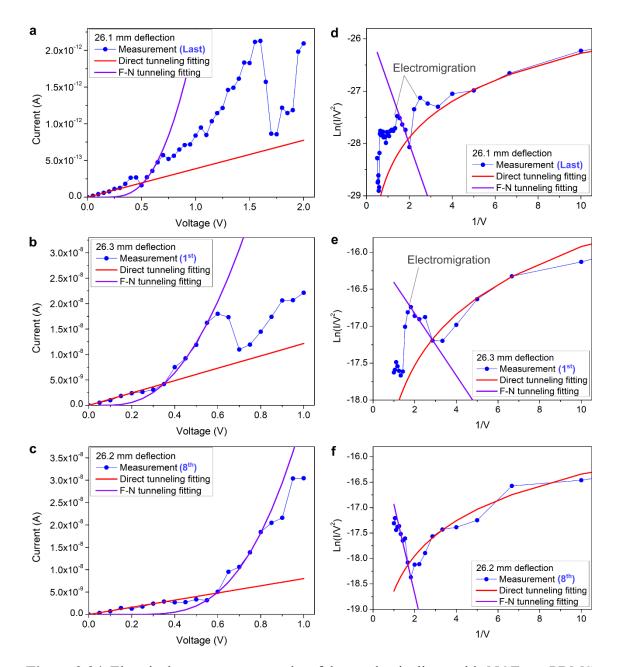

| <b>Figure 2.32.</b> Tunneling I-V curve measured from NGEs with ALD Al <sub>2</sub> O <sub>3</sub> filling in the gap.                                                                                                     | 53 |

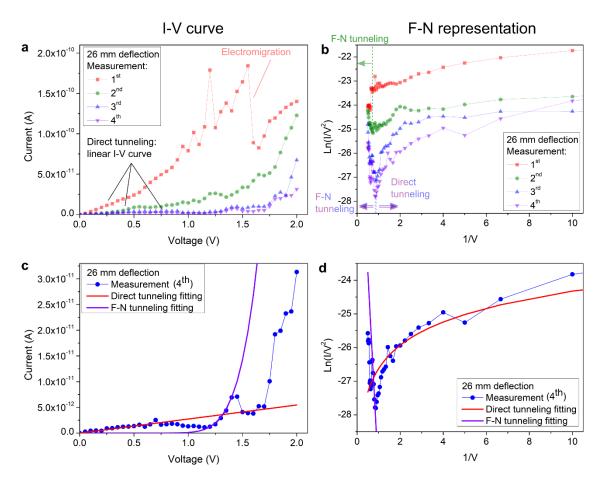

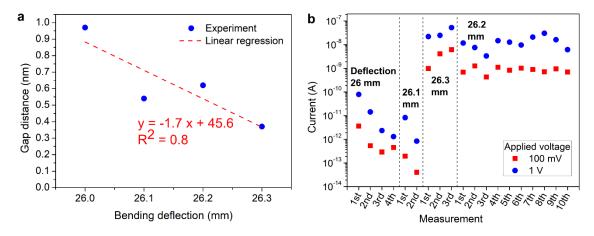

| <b>Figure 2.33.</b> Electrical measurement results of the mechanically tunable NGEs on PDMS under 26 mm bending deflections of the PS captilever.                                                                          | 55 |

| Figure 2.34. Electrical measurement results of the mechanically                                                                                                                                                            | 55 |

| tunable NGEs on PDMS under various bending deflections of the PS cantilever                                                                                                                                                | 56 |

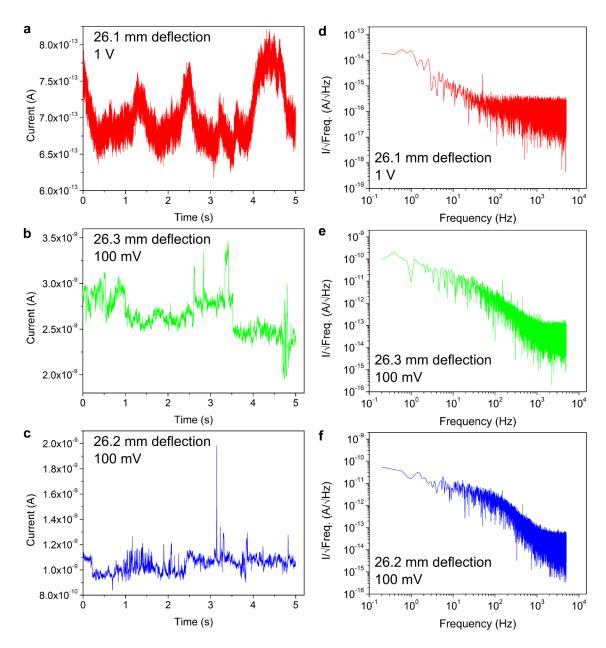

| Figure 2.35. Summary of the tunneling current measurement of the NGEs on PDMS.                                                                 | 57 |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.36. Tunneling currents in time and frequency domains under various bending deflections.                                               | 59 |

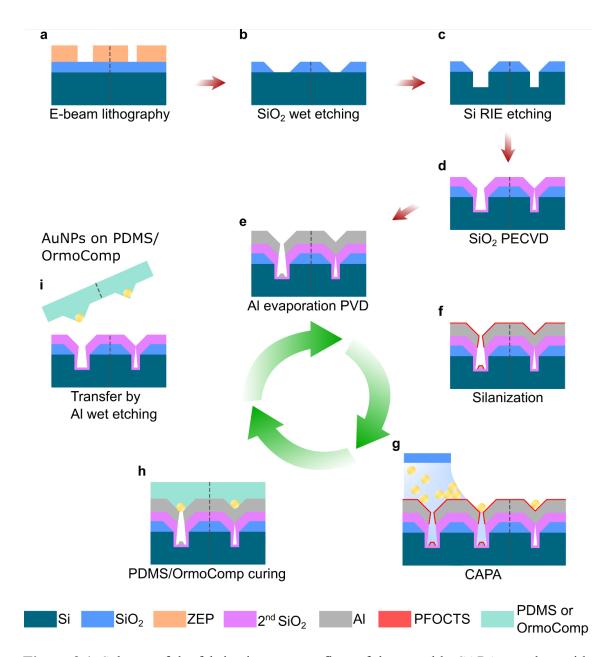

| Figure 3.1. Scheme of the fabrication process flow of the reusable CAPA template with funnel- (left-half) and cone- (right-half) shaped traps. | 66 |

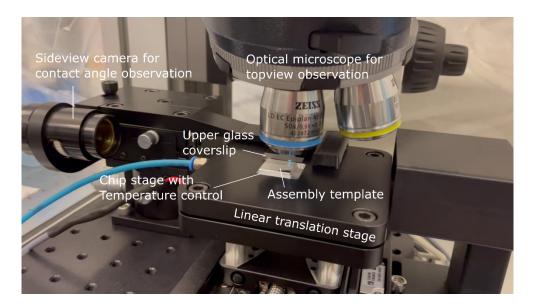

| Figure 3.2. The custom-made setup for capillary-assisted particle assembly (CAPA)                                                              | 68 |

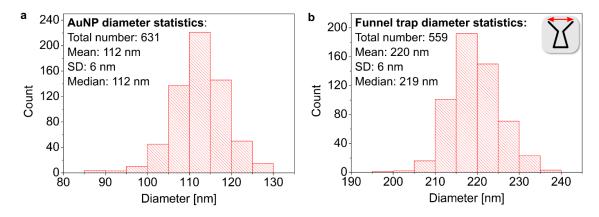

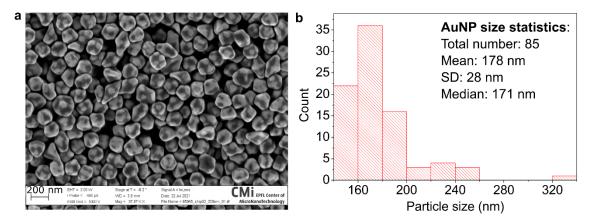

| Figure 3.3. The statistical analysis of the AuNPs and the funnel traps                                                                         | 69 |

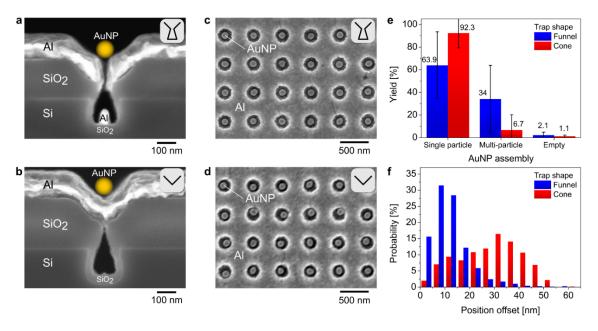

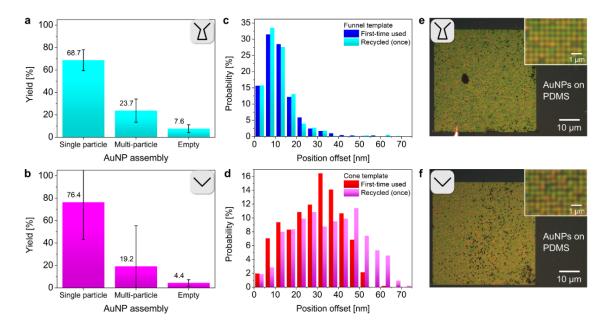

| Figure 3.4. CAPA assembly results with traps of different shapes                                                                               | 72 |

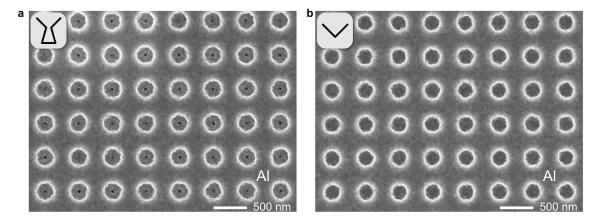

| Figure 3.5. SEM top-view images of assembly traps before CAPA processes                                                                        | 73 |

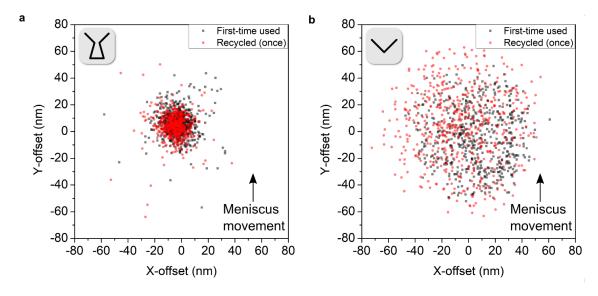

| Figure 3.6. Scatter plots of the AuNP position offset with respect to the centroid of the trap                                                 | 74 |

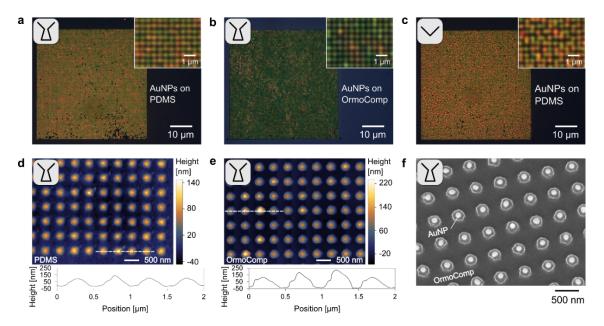

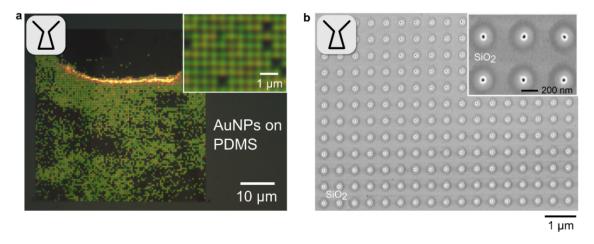

| Figure 3.7. Results of the wet etching transfer processes of AuNPs on PDMS and OrmoComp substrates.                                            | 76 |

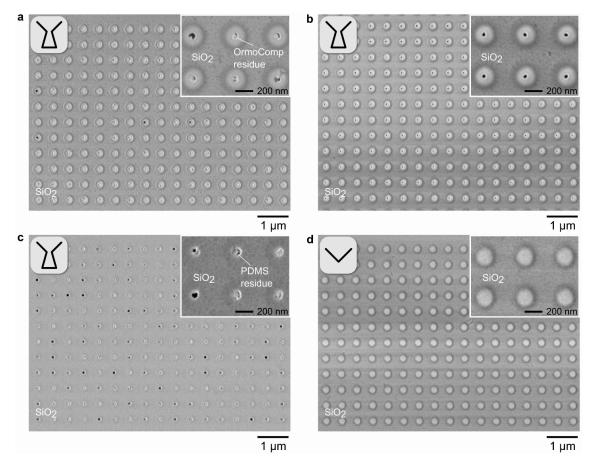

| Figure 3.8. SEM top-view images of assembly templates after wet etching transfer processes                                                     | 77 |

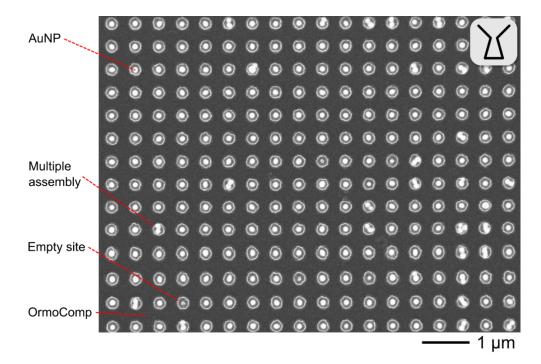

| Figure 3.9. SEM top-view image of an OrmoComp substrate with AuNPs transferred from a funnel template.                                         | 78 |

| Figure 3.10. CAPA assembly template reusability.                                                                                               | 79 |

| Figure 3.11. (a) Bright-field top-view optical microscope image (Leica DM800) of an AuNP array transferred from the reused funnel template     | 80 |

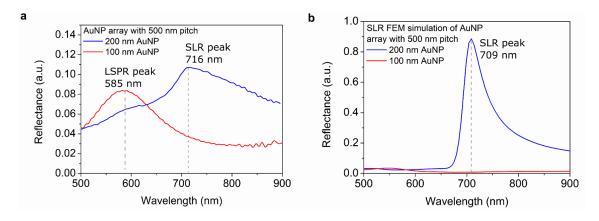

| Figure 3.12. Optical spectra of AuNP arrays.                                                                                                   |    |

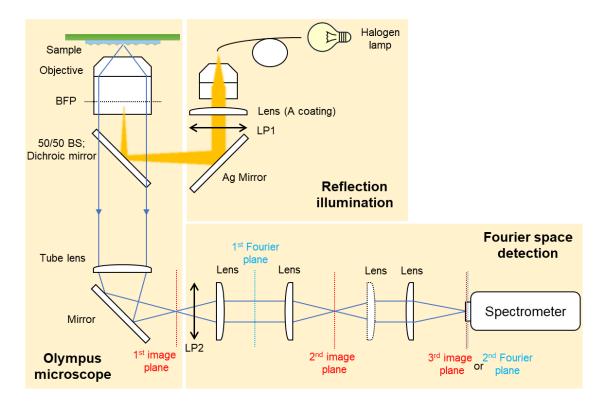

| Figure 3.13. Schematic diagram of the optical measurement setup in a reflection configuration.                                                 |    |

| Figure 3.14. Optical spectra of 150 nm AuNP arrays with various pitches                                                                        | 83 |

| Figure 4.1. Top-view SEM image of the nominally 100 nm x 100 nm x 1000 nm Au nanorods.                                                         | 86 |

| Figure 4.2. NGEs fabricated by CAPA with Au nanorods.                                                                                          | 87 |

| Figure 4.3. Electrical measurement results of the AuNR NGEs                                                                                    | 89 |

| Figure 4.4. 200 nm AuNPs for the NGEs fabricated by CAPA                                                                                       | 90 |

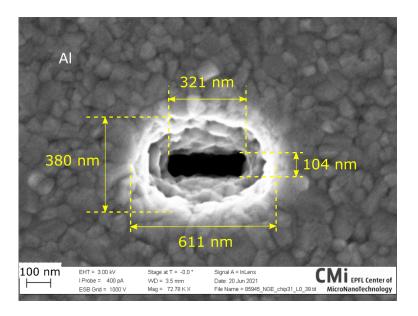

| <b>Figure 4.5.</b> Top-view SEM image of an anisotropic funnel trap for the |    |

|-----------------------------------------------------------------------------|----|

| assembly of 200 nm AuNP dimer                                               | 91 |

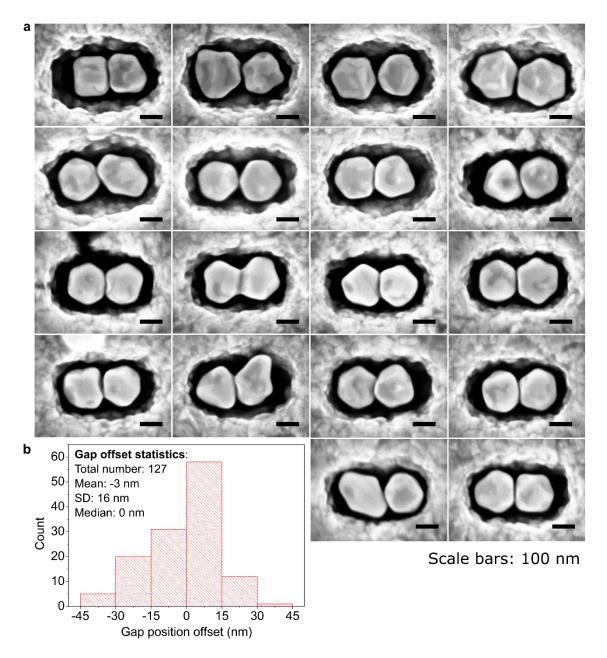

| Figure 4.6. CAPA results of 200 nm AuNP dimer.                              | 92 |

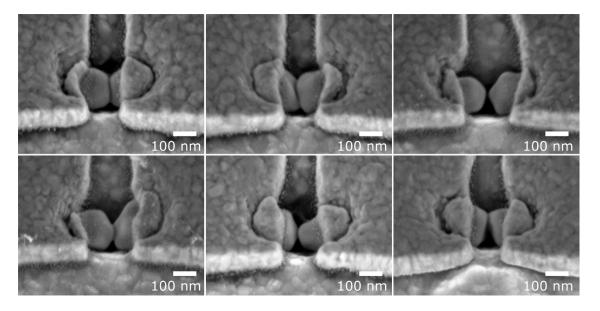

| Figure 4.7. NGEs fabricated by CAPA and EBL lift-off process                | 93 |

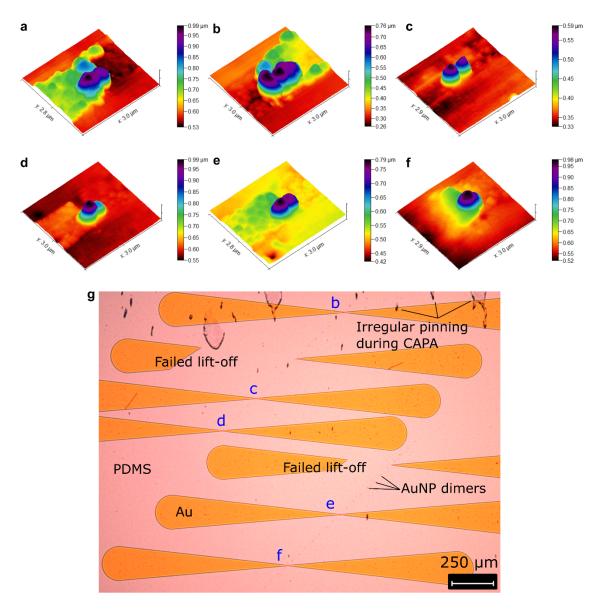

| Figure 4.8. NGEs on PDMS fabricated by CAPA                                 | 95 |

## **List of Tables**

| Table 2.1. Fabrication details of the tunable nanogap electrodes                               | 16  |

|------------------------------------------------------------------------------------------------|-----|

| <b>Table 2.2.</b> COMSOL parameters of the gap distance tunability simulation.                 | .21 |

| Table 2.3. Summary of attenuation factor.                                                      | 24  |

| Table 2.4. List of tape peeling test structures with various dimensions                        | 42  |

| <b>Table 2.5.</b> Deciding factors of the relevant parameters of the tape peeling process.     | .49 |

| Table 2.6. Results of the Simmons model fitting                                                | 57  |

| <b>Table 2.7.</b> Summary of the sampling rate of the current measurements                     | 58  |

| Table 3.1. Fabrication details of assembly templates                                           | 67  |

| Table 3.2. Fabrication details of AuNPs wet etching transfer                                   | 70  |

| <b>Table 3.3.</b> Statistics of AuNP position offset with respect to the centroid of the trap. | .74 |

| <b>Table 4.1.</b> Fabrication process of the NGEs on PDMS using the CAPA technique             | .96 |

# **List of Equations**

| Eq. 2.1 | 50 |

|---------|----|

| Eq. 2.2 | 50 |

## **Chapter 1** Introduction

#### 1.1 Nanostructures on stretchable substrates

Micro/Nanofabrication techniques have been developed since the mid of  $20^{\text{th}}$  century<sup>[1]</sup> to fabricate micro/nanoscale structures or devices on mechanically rigid substrates (Young's modulus, E > 10 GPa), e.g., Si and glass substrates. Miniaturized structures or devices such as electronic devices<sup>[1]</sup>, sensors,<sup>[2]</sup> actuators,<sup>[3]</sup> fluidic,<sup>[4]</sup> and optical<sup>[5]</sup> devices were fabricated monolithically to build various integrated systems on a single chip. These systems including integrated circuits (IC),<sup>[1]</sup> micro/nano-electromechanical systems (MEMS/NEMS),<sup>[3,6]</sup> lap-on-a-chip (LOC),<sup>[7,8]</sup> and micro/nano-optoelectromechanical systems (MOEMS/NOEMS)<sup>[9,10]</sup> are essential elements to the boost of cutting-edge technologies.

In the early 1990s, researches regarding the fabrication of polymer transistors on flexible plastic substrates were reported, [11,12] which are pioneers among others to explore the feasibility of fabricating micro-devices on mechanically unconventional substrates. [13] The primary motivations of fabricating micro-devices on non-rigid substrates can be summarized into the following two categories. On one hand, by fabricating well-developed micro-devices on flexible or stretchable substrates (E < 10 MPa), novel applications that are not feasible with the conventional rigid substrates can be achieved due to the flexibility or stretchability of the substrates. For example, the research field "stretchable electronics" [13–15] has been extensively developed to enable applications such as e-skin, [16,17] flexible/stretchable displays, [18–20] and wearable/implantable devices. [21–23] On the other hand, novel functional micro/nano structures or devices with working principles that are not compatible with rigid substrates can be realized on flexible/stretchable substrates. Strain sensors with high stretchability, [24,25] mechanically tunable plasmonic structures [26,27]/photonic crystals [28], and mechanically assembled 3D nanostructures [29,30] are remarkable examples in this category.

Among the above-mentioned research works, the optics-related applications particularly motivate the fabrication of nanostructures on stretchable substrates. Firstly, the working principle of plasmonics and photonics depends on physical features that are similar to or smaller than the wavelengths of interest, for example, from dozens to hundreds of

nanometers for visible light. Secondly, the tunability of the optical response of the nanostructures, such as reflectance or transmittance spectrum, is enabled by mechanical tuning of the physical dimensions of the nanostructures, e.g., the inter-structural gap size, thanks to the stretchability of the substrate. In particular, the integration of metallic nanostructures and stretchable substrates is by far the most promising methodology to realize such applications.

#### 1.2 Fabrication strategies

In practice, to pattern metallic nanostructures directly on a stretchable substrate is a known challenging task, which is mainly due to the large difference in the thermal expansion coefficient between metals and polymer-based soft materials. [31,32] As an alternative, a strategy to first deposit and pattern metallic thin film nanostructures on a silicon substrate using the conventional nanofabrication processes and subsequently transfer the metallic nanostructures onto a stretchable substrate is developed. Depending on the mechanism of structure transfer, three different methodologies are categorized and briefly described here: (1) Transfer printing, [33–35] (2) dry peel-off transfer, [29,36] and (3) wet etching transfer. [37,38]

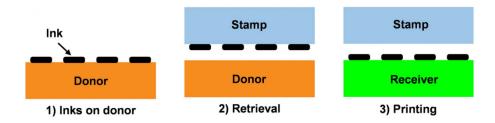

"Transfer printing is a materials assembly technique that uses elastomeric stamps for heterogeneous integration of various classes of micro- and nanostructured materials into two- and three-dimensionally organized layouts on virtually any type of substrate." As shown in Figure 1.1, nanostructures are transferred from a donor substrate onto a receiver substrate via an elastic stamp by manipulating the adhesion strength between the stamp/ink and the ink/substrate interfaces. The major advantage of the transfer printing technique is the variety of the receiver substrate.

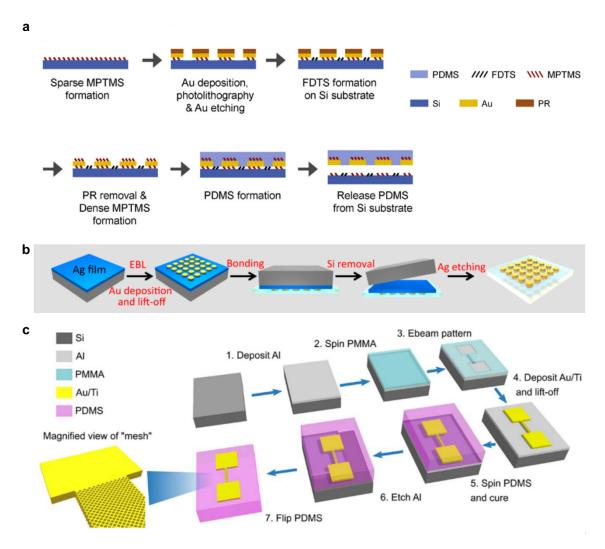

Similar to the transfer printing technique, the dry peel-off transfer is accomplished by creating an adhesion of the stretchable substrate/structures interface that is larger than the adhesion of the donor substrate/structures interface (see Figure 1.2a). Apart from using a solid-phase stretchable substrate to receive the transferred structures on top of the surface, embedded transferred structures can also be obtained using dry peel-off transfer. By pouring/coating uncured liquid-phase polymer materials such as polydimethylsiloxane (PDMS) on the donor substrate, the structures to be transferred are embedded in the stretchable substrate after the curing process, which is not straightforward to the transfer printing technique. The dry peel-off process is a simple method to transfer microstructures to stretchable substrates, however, this method does not work well to transfer the structures with the lateral dimension smaller than 10 µm. [29] To increase the transfer yield of nanostructures, a sacrificial metal film is introduced under the nanostructures, as shown in Figure 1.2b, to replace the interface between the stretchable substrate and the top surface of the donor substrate. The weak adhesion between the

**Figure 1.1.** Schematic working principle of transfer printing technique. (adapted from Figure 2 in ref. [35]). Micro/nanostructures are transferred from a donor substrate onto a receiver substrate via an elastic stamp by manipulating the adhesion strength between the stamp/ink and the ink/substrate interfaces.

sacrificial metal film and the donor substrate allows a high transfer yield of the nanostructures using the dry peel-off process.

A sacrificial layer is also introduced under the nanostructures when conducting the wet etching transfer as shown in Figure 1.2c. Instead of peeling off the sacrificial layer along with the nanostructures from the donor substrate, the sacrificial layer is etched in a chemical bath to eliminate the attachment of the nanostructures to the donor substrate. Compared to the transfer printing technique and the dry peel-off process, the mechanical stress induced by deforming the stretchable substrate during the process is avoided, and thereby the stress applied on the transferred nanostructures is reduced. To exploit this advantage, the research works reported in this thesis focus on using the wet etching transfer process to fabricate nanostructures on a stretchable substrate such as PDMS.

Figure 1.2. Schematic fabrication processes of dry peel-off and wet etching transfer. (a) Dry peel-off transfer process with transferred microstructures embedded in the PDMS substrate (adapted from Figure 1 in ref. [36]). (b) Metal-assisted dry peel-off transfer (adapted from Figure 1 in ref. [29]). By introducing a sacrificial layer (Ag film), Au nanostructures are transferred onto a PDMS substrate via the direct dry peeling process. (c) Wet etching transfer (Figure 1 in ref. [37]). By introducing a sacrificial layer (Al film), Au nanostructures are transferred and embedded in the PDMS after the Al wet etching process, avoiding the mechanical stress induced by deforming the PDMS substrate during the peel-off process.

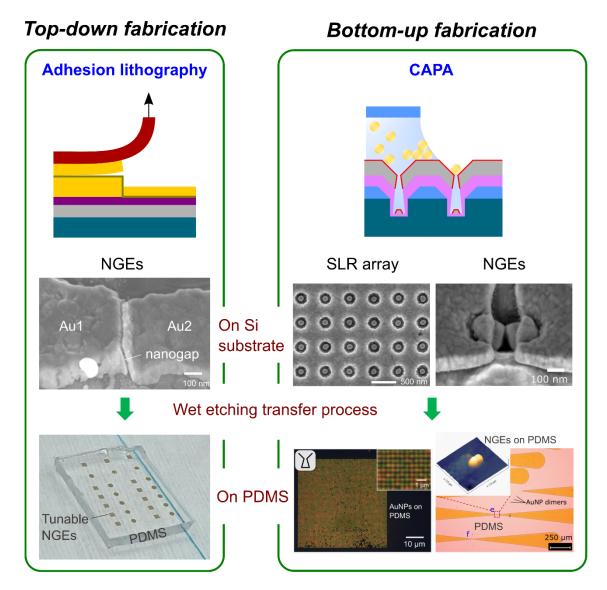

**Figure 1.3.** Scheme of the research works in this thesis. This thesis is composed of two parts regarding using adhesion lithography and capillary-assisted nanoparticle assembly (CAPA) technique, respectively, to fabricate functional nanostructures on PDMS. The nanostructures are first fabricated on Si substrates and subsequently transferred to PDMS substrates by the wet etching transfer process.

#### 1.3 Thesis outline

As shown in Figure 1.3, this thesis is composed of two parts regarding using adhesion lithography and capillary-assisted nanoparticle assembly (CAPA) technique, respectively, to fabricate functional nanostructures on PDMS. The nanostructures are first fabricated on Si substrates and subsequently transferred to PDMS substrates by the wet etching transfer process. Chapter 2 reports the work regarding the tunable nanogap electrodes (NGEs) on PDMS fabricated by adhesion lithography. Chapter 3 and chapter

4 report the works regarding the fabrication of plasmonic surface lattice resonance (SLR) nanoparticle arrays and NGEs, respectively, on PDMS by the CAPA technique. The introductions, motivations, conclusions, and outlooks of each work are given in the corresponding chapters. Finally, chapter 5 concludes the thesis and summarizes the outlooks for future works in scalable fabrications of NGEs towards the sensor and optical applications.

# Chapter 2 Tunable nanogap electrodes on PDMS fabricated by adhesion lithography

#### 2.1 Introduction

#### 2.1.1 Nanogap electrodes

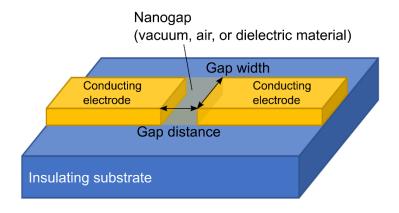

Nanogap electrodes (NGEs) comprise a pair (or more) of conducting electrodes on an insulating substrate.<sup>[39]</sup> The electrodes are separated by a gap distance ranging from several nm to dozens of nm. As shown in Figure 2.1, the gap can be in vacuum, air ,or filled by dielectric materials depending on the desired application. In the past decades, NGEs have been proposed as a unique nano-device in terms of interaction with electrons, photons, and molecules. Various applications have been studied and developed accordingly, such as resistive random access memory (RRAM),<sup>[40–42]</sup> nanoelectromechanical (NEM) switch,<sup>[43,44]</sup> and biosensing.<sup>[45–47]</sup> These applications are briefly described in Figure 2.2.

Figure 2.1. Illustration of nanogap electrodes.

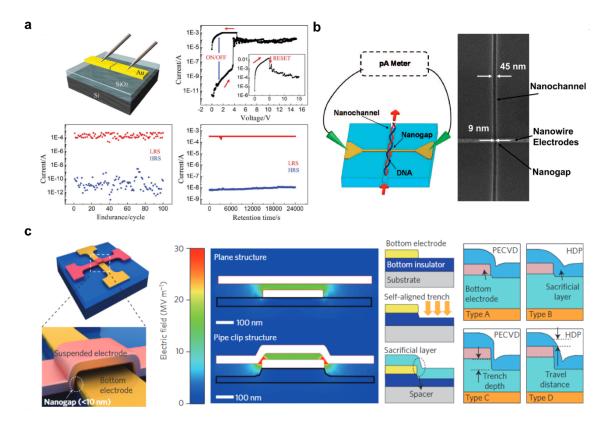

**Figure 2.2.** NGEs applications on rigid substrates. (a) Nonvolatile RRAM (adapted from Figure 3 in ref. <sup>[41]</sup>). The electrical conductance across the nanogap (~5 nm) can be "SET" to a low resistive state (LRS) and "RESET" to a high resistive state (HRS) by sweeping the applied voltage due to the formation and the dissolution of conducting filaments around the nanogap. (b) Label-free DNA detector (Figure 1, 3 in ref. <sup>[45]</sup>). A change in transverse current can be measured from the NGEs when a DNA molecule passes through the NGES in the nanochannel. (c) Sub-1-V NEM switch (adapted from Figure 1 in ref. <sup>[43]</sup>). The "ON" and "OFF" statuses can be switched by relative mechanical motion between the NGEs which is induced by electrostatic force and mechanical restoring force.

When the nanogap distance is smaller than 2 nm, more distinctive applications can be achieved as shown in Figure 2.3, including single-molecule discrimination, [48–50] electrical-driven nano-antenna, [51–54] molecular electronics. [55–57] These applications are enabled thanks to the enhanced phenomena in sub-2 nm nanogaps, i.e., significant quantum tunneling, highly concentrated electric field, and single-molecule bridging, respectively.

#### 2.1.2 Fabrication of nanogap electrodes

Apart from the applications of NGEs, various fabrication methods of NGEs have also been reported. In 2019, Y. Yang et al. summarized the fabrication methods for sub-5 nm metal nanogaps (with or without electrodes) in their review article. [58] Here, based on their summary table, the methods reported for the fabrication of NGEs are the following:

- Electrochemical deposition<sup>[59,60]</sup>

- Electromigration breakdown<sup>[61]</sup>

- Focus ion/electron beam lithography<sup>[62,63]</sup>

- Crack junction<sup>[64,65]</sup>

- Shadow deposition<sup>[66,67]</sup>

- Self-terminating electroless gold plating<sup>[68]</sup>

- Nano-imprinting lithography (NIL)<sup>[69]</sup>

- Adhesion lithography<sup>[70,71]</sup>

- Laser direct writing lithography<sup>[72]</sup>

- On-wire lithography<sup>[73]</sup>

Among the above-listed techniques, crack junction, shadow deposition, self-terminating gold plating, NIL, and adhesion lithography are parallel fabrication techniques, i.e., multiple NGEs in a large-area scale are fabricated simultaneously. The rest of the techniques in the list are often considered as not scalable. Although all of them are able to fabricate sub-5 nm NGEs effectively, the reliable fabrication of sub-2 nm NGEs remains a challenging task even with these approaches. Therefore, instead of fabricating a sub-2 nm nanogap directly, some groups proposed the fabrication of tunable NGEs. In this case, NGEs are first fabricated without any materials filling the nanogap, and then the gap distance is adjusted (e.g., mechanically) to the sub-2 nm range for the aforementioned specific applications. Up to now, the most promising technique to fabricate such tunable NGEs is the use of mechanically controllable break junctions (MCBJ).[74-76] To do so, first, a sub-um, free-standing metallic wire is defined. Then, the substrate is bent inducing a tensile strain to the metallic wire until the break junction is formed. The process is accompanied by real-time monitoring of the electrical conductance, enabling a precise bending deflection control and a configurable attenuation factor of the bent device. This in turn results in a tunable gap distance at the sub-nm scale. The only drawback of the MCBJ technique is that the bending device is typically a few centimeters large to achieve small attenuation factor for sub-nm gap distance control, which disallows monolithic integration with other devices.

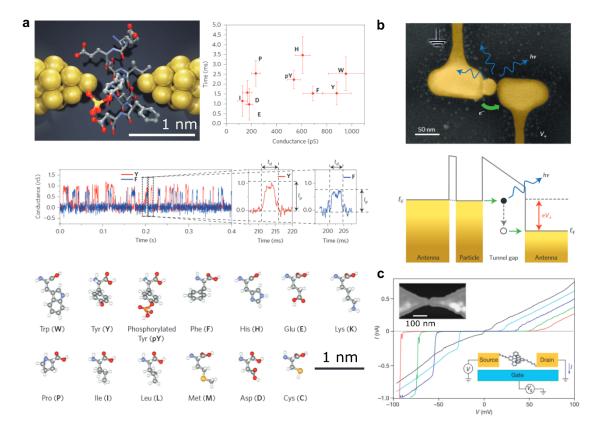

**Figure 2.3.** Sub-2 nm NGEs applications on rigid substrates. (a) Amino acid molecules discrimination (adapted from Figure 1, 2 in ref. <sup>[49]</sup>). The amplitude and the width of the tunneling current spikes induced when different amino acid molecules pass by the NGEs are statistically analyzed to discriminate the molecules. (b) Electrically-driven optical antennas (adapted from Figure 1 in ref. <sup>[54]</sup>). Photons are generated by inelastic tunneling across the NGEs and are resonating in the nano-antennas to radiate into the far field. (c) Molecular junctions (adapted from Figure 1 in ref. <sup>[57]</sup>). Single molecule bridges the NGEs with a back gate expressing the electronics properties as a single-electron transistor.

#### 2.1.3 Aims and motivation

In the past decade, Masateru Taniguchi and his group reported a series of research works regarding the use of tunable NGEs fabricated by the MCBJ technique in single-molecule detection/sequencing of DNA/RNA and peptides. [49,50,77-80] The results present a promising potential of such technology to realize a fast and low-cost de novo DNA/RNA/protein sequencing and quantitative analysis. Inspired by these results, the aim of this work is to develop a scalable fabrication process of tunable NGEs on a stretchable substrate such as PDMS. The motivation to fabricate NGEs on a soft substrate is twofold. On the one hand, a soft substrate could allow the integration of deformable nanofluidic channels and tunable NGEs. A deformable nanochannel is reported as one of the effective methods to reduce the molecule speed in a fluidic channel,

which is critical to the feasibility of single-molecule sequencing/analysis using NGEs.<sup>[81–83]</sup> On the other hand, similar to the on-chip MCBJ reported in 2020,<sup>[84]</sup> micromechanical actuators, e.g., piezoelectric actuators might be also integrated on a soft substrate<sup>[85,86]</sup> to tune the gap distance. An integrated system on a PDMS substrate could pave the way towards a miniaturized single-molecule analysis platform.

Here, we present the fabrication of tunable NGEs based on electron beam lithography (EBL) in combination with adhesion lithography. Atomic layer deposition (ALD) is used to deposit a sacrificial layer in the nanogap<sup>[70]</sup> for the ease and the accuracy of the initial gap distance configuration. A yield study of the essential step of the adhesion lithography, i.e. the tape peeling process, is also conducted in this work to understand the design principles of the NGEs. Finally, the electrical characterization of the NGEs is conducted in order to confirm whether the fabricated NGEs on PDMS are tunable in the tunneling regime.

#### 2.2 Fabrication process and design

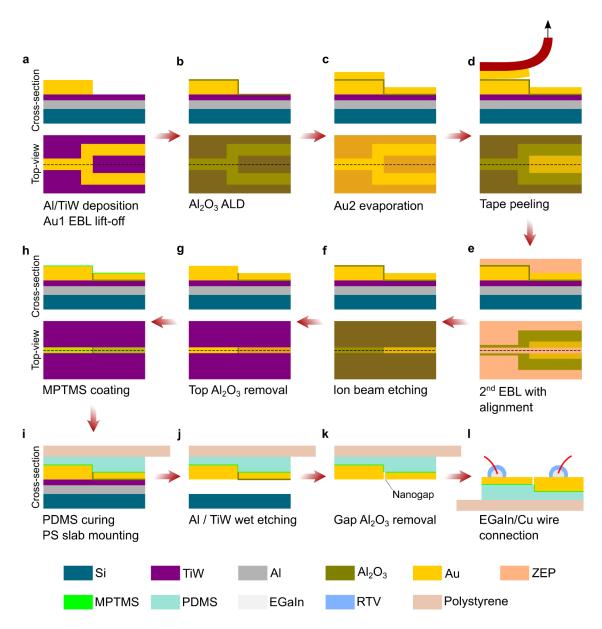

Figure 2.4 shows the fabrication process of the tunable nanogap electrodes on stretchable substrates demonstrated in this work, which is compatible with standard cleanroom processes. The first step is to pattern alignment marks for the EBL processes by typical direct laser writing photolithography and Si RIE etching. About 2  $\mu$ m deep Si etching into the Si wafer creates square holes for the electron beam to detect the topographical height difference and then align the wafer before the EBL process.

Following the alignment mark patterning, a 150 nm thick Al thin film serving as a sacrificial layer for the wet etching transfer process is deposited by e-beam evaporation. A 100 nm thick titanium tungsten (TiW) thin film is then deposited by DC sputtering on the Al layer. The TiW layer acts a diffusion barrier layer to prevent the inter-diffusion between the gold structures and the Al layer during the annealing process to be carried out afterward.<sup>[87]</sup> A MMA/PMMA positive resist bilayer is spin-coated on the TiW layer and then exposed to the electron beam writing with alignment control. The exposed bilayer is then developed. A metal thin film stack of Ti/Au/Ti (5/100/3 nm) is deposited for the lift-off process (Figure 2.4a). The patterned Ti/Au/Ti stack is hereafter referred to as the "Au1 layer".

After patterning the Au1 layer, a 4 nm thick Al<sub>2</sub>O<sub>3</sub> thin film is deposited by ALD (Figure 2.4b), serving as a sacrificial layer to separate the Au1 electrode and the following second Au electrode. OM images of the wafer after Au1 layer patterning and Al<sub>2</sub>O<sub>3</sub> deposition are shown in Figure 2.5a, b. A thin film stack of Au/Ti (50/3 nm) is deposited by e-beam evaporation (Figure 2.4c), which is hereafter referred to as the "Au2 layer".

**Figure 2.4.** Schematic illustration of the fabrication process of the tunable NGEs. The dimensions are not to scale to highlight the nano-scale structures.

The subsequent tape peeling process removes only the Au2 deposited on top of the Au1/Al<sub>2</sub>O<sub>3</sub>, thanks to the weak adhesion between Au and Al<sub>2</sub>O<sub>3</sub>. The Au2 layer deposited on TiW/Al<sub>2</sub>O<sub>3</sub> stays due to the height difference of the top surfaces (Figure 2.4d).<sup>[41]</sup> An experiment regarding the tape peeling process and the Au1 design is conducted and discussed in the following section. An OM image of the wafer after Au2 layer patterning is shown in Figure 2.5c, d.

**Figure 2.5.** OM images of the NGEs design after various process steps. (a) After the Au1 layer patterning and Al<sub>2</sub>O<sub>3</sub> deposition. (b) A magnified image of (a). (c) After using the tape peeling process to pattern the Au2 layer. (d) A magnified image of (c). (e) After the 2<sup>nd</sup> EBL to pattern ZEP-520A resist. (f) After the IBE process and resist removal, the NGEs are formed.

After the tape peeling process to pattern the Au2 layer, positive resist ZEP-520A is spin-coated on the wafer and the 2<sup>nd</sup> EBL is done (Figure 2.4e). The top Ti thin films on both Au1 and Au2 play the role of adhesion promoters to avoid poor coating of ZEP-520A at

this step. The patterned ZEP-520A is then subjected to a thermal reflow process to avoid the fence effect (re-sputtering deposition on the resist sidewall) during the later ion beam etching process (IBE). The IBE process etches unwanted Al<sub>2</sub>O<sub>3</sub>, Au1, and Au2 to form the NGEs structure (Figure 2.4f), and stops at the TiW layer by etching time control. OM images of the wafer after ZEP-520A patterning and IBE/resist removal processes are shown in Figure 2.5e, f, respectively.

After the IBE process, the NGEs are annealed at 400 °C in N<sub>2</sub> ambient for 5 min to smooth the edges and surfaces of the Au electrodes. The Al<sub>2</sub>O<sub>3</sub> on top of the Au1 layer is removed in a photoresist developer bath (AZ 726 MIF/MF CD 26) to reveal the Au1 top surface (Figure 2.4g) for the following (3-Mercaptopropyl)trimethoxysilane (MPTMS, Sigma Aldrich) coating process. MPTMS serves as an adhesion promoter to increase the adhesion between Au electrodes and the PDMS substrate that comes in the following process step (Figure 2.4h).<sup>[88]</sup> An OM image of the Si wafer and SEM images of the NGEs before the MPTMS coating process are shown in Figure 2.6.

Before pouring the PDMS, the processed Si wafer is manually cleaved into chips of  $\sim 17$  x 17 mm² PDMS (10:1) is then poured on the Si chip, degassed for 1 h, and cured at room temperature for a total time of 48 h in order to avoid thermal stress. After the curing, the PDMS is cut and trimmed to a substrate size of  $\sim 15$  x 15 mm² to increase the area of TiW/Al exposed to the chemical during the wet etching transfer process. Subsequently, a polystyrene (PS) slab (100 x 40 x 12 mm³) is manually aligned and brought into contact with the PDMS substrate. Thanks to the Van der Waals force, the PDMS sticks to the PS slab (Figure 2.4i), which serves not only as a handling substrate but also as a bending cantilever to apply strain to the PDMS and the NGEs to tune the nanogap distance during the electrical measurements.

**Figure 2.6.** Images of NGEs before and after the wet etching transfer process. (a) OM image of a 100-mm Si wafer with 8 NGEs chips on it before the top Al<sub>2</sub>O<sub>3</sub> removal process. (b) Top-view and (c) 40° tilted-view SEM images of NGEs before the wet etching transfer process. (d) OM image of NGEs on a PDMS substrate after the wet etching transfer process.

After the PS slab mounting, the Si chip, along with the PDMS/PS slab, are soaked in a diluted HCl bath for 6 to 12 h to etch the sacrificial Al layer. The NGEs structures are transferred onto the PDMS that is separated from the Si chip after this wet etching transfer process. TiW is etched in a H<sub>2</sub>O<sub>2</sub> bath (Figure 2.4j), followed by a deionized (DI) water rinse and a BHF wet etching to remove the Al<sub>2</sub>O<sub>3</sub> both on the Au2 layer and in the nanogap (Figure 2.4k). Thanks to the use of the PS slab as handling substrate, the mechanical stress applied on the soft PDMS and the NGEs on it is minimized after the wet etching transfer process. An OM image of the PDMS and the NGEs after the wet etching transfer process is shown in Figure 2.6d.

Since the typical wire bonding processes are not compatible with soft PDMS substrates, an alternative metal wire connection method is adopted here.<sup>[89]</sup> In order to connect the metal pads on the PDMS and the electrical measurement setups while minimizing the applied mechanical stress, copper wires are not in physical contact with the metal pads.

Instead, droplets of liquid metal (eutectic GaIn, EGaIn, Sigma-Aldrich) are used to bridge the copper wire and pads as shown in Figure 2.4i. The copper wires and the EGaIn droplets are fixed on the PDMS by a room-temperature-vulcanizing (RTV) silicone sealant (DC 732, Dow Corning) which is a rubber-like, soft material to reduce the mechanical stress applied to the PDMS and NGEs structures whenever the copper wires are moved.

The parameters and details of each process step are summarized in Table 2.1.

**Table 2.1.** Fabrication details of the tunable nanogap electrodes.

| Step | Process                                                        | Equipment                           | Parameters                                                                                                                                                              |

|------|----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PR coating for<br>alignment mark<br>patterning                 | Süss ACS200<br>GEN3                 | CMi tool recipe: 0123 Photoresist: AZ ECI 3007 HMDS priming/edge cleaning 2050 rpm, soft baking 90 s at 100 °C, thickness: 1 µm                                         |

| 2    | Exposure                                                       | Heidelberg<br>Instruments<br>VPG200 | i-line (355-365 nm), Dose: 120 mJ/cm <sup>2</sup>                                                                                                                       |

| 3    | Development                                                    | Süss ACS200<br>GEN3                 | CMi tool recipe: 0823<br>37s in AZ 726 MIF (or MF CD 26) at room<br>temperature and DI water rinse<br>Post-exposure baking: 1 min at 110 °C                             |

| 4    | Si RIE etching<br>for alignment<br>mark<br>patterning          | Alcatel AMS<br>200 SE               | CMi tool recipe: Si_Opto<br>RF 1500 W, DC 30 W, 40 / 55 sccm of<br>SF <sub>6</sub> / C <sub>4</sub> F <sub>8</sub> for 3 min                                            |

| 5    | PR ashing                                                      | TePla<br>GiGAbatch                  | 600 W, 400 seem O <sub>2</sub> , 5 min                                                                                                                                  |

| 6    | 150 or 200 nm<br>thick sacrificial<br>Al e-beam<br>evaporation | Leybold Optics<br>LAB 600H          | CMi tool recipe: 163 Room temperature, 1010 mm working distance, 1.8 x 10 <sup>-6</sup> mbar chamber pressure, 1 Å/s deposition rate                                    |

| 7    | 100 nm thick<br>diffusion<br>barrier layer<br>TiW deposition   | Alliance-<br>Concept DP<br>650      | CMi tool recipe: RTU_WTi10%  Room temperature, 80 mm working distance, 5 x 10 <sup>-3</sup> mbar chamber pressure, 30 sccm Ar, DC power: 250 W, 3.4 Å/s deposition rate |

| 8    | MMA/PMMA spin coating                                          | ATMsse<br>OPTIspin SB20             | 5 min dehydration baking at 180 °C                                                                                                                                      |

|    |                                                              |                            | 220 nm thick MMA EL6 coating: 500 rpm for 5 s and then 2000 rpm for 1 min 5 min soft baking at 180 °C 220 nm thick PMMA 495K A4 coating: 500 rpm for 5 s and then 2000 rpm for 1 min 5 min soft baking at 180 °C                                                 |

|----|--------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | E-beam exposure                                              | VISTEC<br>EBPG5000+        | 100 kV, 950 μc/cm <sup>2</sup>                                                                                                                                                                                                                                   |

| 10 | Development                                                  | Wet bench                  | 1 min in methyl isobutyl ketone (MIBK) / IPA (1:3) at room temperature, IPA rinse and N <sub>2</sub> drying                                                                                                                                                      |

| 11 | Aul e-beam evaporation                                       | Leybold Optics<br>LAB 600H | CMi tool recipe: 222 Room temperature, 1010 mm working distance, 1.5 x 10 <sup>-6</sup> mbar chamber pressure, 4 Å/s deposition rate, Ti/Au/Ti thickness: 5/100/3 nm                                                                                             |

| 12 | Aul lift-off                                                 | Wet bench                  | 4 h in acetone and 10 s sonication                                                                                                                                                                                                                               |

| 13 | Al <sub>2</sub> O <sub>3</sub> atomic<br>layer<br>deposition | BENEQ<br>TFS200            | CMi tool recipe: 01_Al2O3_50nm<br>Precursor: TMAl, H <sub>2</sub> O<br>50 cycles at 200 °C                                                                                                                                                                       |

| 14 | Au2 e-beam evaporation                                       | Leybold Optics<br>LAB 600H | CMi tool recipe: 732  Room temperature, 1010 mm working distance, 1.5 x 10 <sup>-6</sup> mbar chamber pressure, 0.5 Å/s deposition rate, Au/Ti thickness: 50/3 nm                                                                                                |

| 15 | Tape bonding and peeling                                     | POWATEC P-<br>200          | Tape bonding: Use a 1.65 kg weight roller rolling over the wafer (Adwill E series polyolefin UV-curable tape, LINTEC)  Tape peeling: Manual peeling with the force in the normal direction of the wafer, the overall peeling-off time ~ 10 s for a 100-mm wafer. |

| 16 | ZEP-520A spin coating                                        | ATMsse<br>OPTIspin SB20    | 500 rpm for 5 s and then 4000 rpm for 1 min, thickness: 400 nm                                                                                                                                                                                                   |

| 17 | E-beam exposure                                              | VISTEC<br>EBPG5000+        | $100 \text{ kV}, 260 \text{ μc/cm}^2$                                                                                                                                                                                                                            |

| 18 | Development                                                  | Wet bench                  | 1 min in n-amyl acetate, and 1 min rinsing in methyl isobutyl ketone (MIBK) / IPA (9:1) at room temperature, IPA rinse and N <sub>2</sub> drying                                                                                                                 |

| 19 | ZEP-520A<br>reflow                                           | Hotplate                   | 10 min at 145 °C                                                                                                                                                                                                                                                 |

| 20 | Ion beam etching                               | Veeco Nexus<br>IBE350           | CMi tool recipe: med_five_step<br>500 V, 800 mA, Ar ion beam at 10° to the<br>normal direction of the wafer<br>(12 s etching + 60 s cooling) x 4 + 12 s<br>etching |

|----|------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | ZEP-520A<br>removal                            | TePla<br>GiGAbatch<br>Wet bench | 600 W, 400 sccm O <sub>2</sub> , 1 min<br>10 min in NMP (Remover 1165), DI water<br>rinse and N <sub>2</sub> drying<br>600 W, 400 sccm O <sub>2</sub> , 5 min      |

| 22 | Rapid thermal<br>annealing<br>(RTA)            | Jipelec JetFirst 200            | 400 °C for 5 min in N <sub>2</sub> ambient, ramping time: 20 s                                                                                                     |

| 23 | Top Al <sub>2</sub> O <sub>3</sub> removal     | Wet bench                       | 3 min in AZ 726 MIF (or MF CD 26) at room temperature, 1 min in DI water, N <sub>2</sub> drying                                                                    |

| 24 | MPTMS priming                                  | Wet bench                       | 2 h in 60 mM MPTMS ethanol solution<br>2 min in IPA, N <sub>2</sub> drying                                                                                         |

| 25 | Wafer cutting                                  |                                 | Manual mechanical cleaving into chips                                                                                                                              |

| 26 | PDMS curing                                    |                                 | Dow Corning Sylgard 184, Base: curing agent = 10: 1, mixed and degassed PDMS pouring into a Petri dish with chips 1 h degassing Cured at room temperature for 48 h |

| 27 | Polystyrene slab mounting                      |                                 | PDMS manual cutting Manually bring polystyrene slab in contact with PDMS top surface with orientation alignment                                                    |

| 28 | Wet etching transfer                           | Wet bench                       | 6 to 12 h in diluted hydrochloric acid bath (37% HCl : DI water = 1:6, volume ratio)                                                                               |

| 29 | TiW removal                                    | Wet bench                       | 10 min in 30% H <sub>2</sub> O <sub>2</sub> at room temperature 2 min in DI water, N <sub>2</sub> drying                                                           |

| 30 | Nanogap Al <sub>2</sub> O <sub>3</sub> removal | Wet bench                       | 1 min in 7:1 BHF at room temperature 2 min in DI water*2, N <sub>2</sub> drying                                                                                    |

|    |                                                |                                 |                                                                                                                                                                    |

#### 2.3 Gap distance tunability simulation

In order to understand how precisely the fabricated nanogap can be tuned by the PS cantilever bending, a finite element method (FEM) simulation is conducted to study the gap distance tunability. As shown in Figure 2.7, a COMSOL model which comprises a PS cantilever, a PDMS substrate, and a pair of Au NGEs on the PDMS substrate is created for the simulation study. By fixing the PS cantilever at one end and uniformly applying a force in Z-direction at the other end (free end), the cantilever is bent with a deflection in Z-direction at the free end (see Figure 2.7a). Thus strain is applied to the PDMS substrate and the NGEs to change the nanogap distance. Depending on the distance of the PDMS substrate to the cantilever free end, there are two configurations: front position (Figure 2.7b) and rear position (Figure 2.7c), corresponding to lower and higher applied strain, respectively. During the electrical measurements, these two configurations can be switched by physically clamping the PS cantilever at the different sides. The Au NGEs in Figure 2.7d are modeled in an orientation that is orthogonal to the bending axis as shown in Figure 2.7a. With this orientation, the cantilever should be bent upwards to apply a compressive strain to the PDMS substrate in X-direction to reduce the nanogap distance. On the other hand, by rotating the NGEs by 90° with respect to the normal direction of the PDMS top surface, NGEs are also modeled in an orientation in parallel to the bending axis (Y-axis). In such a case, the cantilever should be bent downwards to apply a tensile strain to the PDMS substrate in X-direction, the nanogap distance is then reduced by a compressive strain in Y-direction due to the Poisson effect. The magnified nanogap model in Figure 2.7e shows that no PDMS is filling the nanogap and the PDMS around the nanogap is densely meshed for ease of convergence and correctness of the simulation results. The top surfaces of the Au electrodes and the PDMS substrate are in the same plane.

Due to difficulties in having convergence within a reasonable computation time, the NGEs in this simulation study are not modeled following the exact dimensions and shapes reported in the previous section of fabrication. Instead, both Au1 and Au2 electrodes are modeled as two cuboids with identical dimensions. By changing the length/width of the electrodes, as well as the PDMS position and the NGEs orientation, correlations between these factors and the nanogap tunability are studied. The nanogap tunability in this study is represented by the attenuation factor, which is defined as the ratio of the gap distance change,  $\Delta d$ , and the cantilever deflection,  $\delta$ . For example, if the attenuation factor is -10<sup>-6</sup>, this means the gap distance can be reduced by 1 nm when the cantilever is deflected by 1 mm. Table 2.2 lists COMSOL parameters and values that are used in this study, and the simulation results are shown in Figure 2.8.

**Figure 2.7.** Nanogap tunability study by COMSOL simulation. (a) Illustration of the bending simulation. (b) The meshed model with the PDMS at the front and (c) the rear position. (d) The magnified meshed model of the NGEs in the X-axis orthogonal to the bending axis (Y-axis). (e) The magnified meshed model of the tunable nanogap. No PDMS is filling the nanogap and the PDMS substrate around the nanogap is densely meshed.

Table 2.2. COMSOL parameters of the gap distance tunability simulation.

| Parameter                                  |                 | Value                   |  |  |

|--------------------------------------------|-----------------|-------------------------|--|--|

| PS cantilever                              | Length          | 90 mm                   |  |  |

|                                            | Width           | 40 mm                   |  |  |

|                                            | Thickness       | 1.18 mm                 |  |  |

|                                            | Density         | $1157 \text{ kg/m}^3$   |  |  |

|                                            | Young's modulus | 2.6 GPa                 |  |  |

|                                            | Poisson's ratio | 0.4                     |  |  |

| PDMS                                       | Length          | 15 mm                   |  |  |

|                                            | Width           | 15 mm                   |  |  |

|                                            | Thickness       | 3 mm                    |  |  |

|                                            | Density         | $970 \text{ kg/m}^3$    |  |  |

|                                            | Young's modulus | 1.2 MPa                 |  |  |

|                                            | Poisson's ratio | 0.49                    |  |  |

| Au electrode                               | Length          | 10-50 μm                |  |  |

|                                            | Width           | 0.5-2 μm                |  |  |

|                                            | Thickness       | 100 nm                  |  |  |

|                                            | Density         | $19300 \text{ kg/m}^3$  |  |  |

|                                            | Young's modulus | 83 GPa                  |  |  |

|                                            | Poisson's ratio | 0.44                    |  |  |

| Nanogap distance                           |                 | 10-20 nm                |  |  |

| Free end to PDMS distance (Front position) |                 | 15 mm                   |  |  |

| Free end to PDMS distance (Rear position)  |                 | 70 mm                   |  |  |

| COMSOL version                             |                 | 5.3                     |  |  |

| COMSOL Physics                             |                 | Solid mechanics (solid) |  |  |

| Include geometric nonlinearity             |                 | Yes                     |  |  |

| Solver                                     |                 | Direct solver (MUMPS)   |  |  |

| Nonlinear method                           |                 | Automatic (Newton)      |  |  |

| Gravity                                    |                 | On                      |  |  |

**Figure 2.8.** COMSOL simulation results of the nanogap tunability. The study of (a) the electrode length, (b) the electrode width, (c) the PDMS position, and (d) the NGEs orientation with respect to the nanogap tunability, respectively. The slope of each curve is defined as the attenuation factor to represent the nanogap tunability.

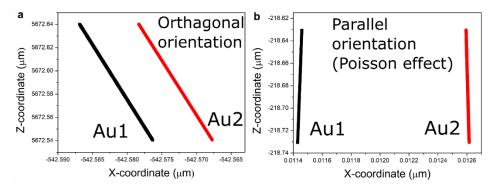

Figure 2.8a to c shows various curves of NGEs in the orthogonal orientation with different electrode lengths, widths, and PDMS positions, respectively. The significant difference in slopes in Figure 2.8a indicates that the electrode length plays an important role in the attenuation factor. Here, the electrode length is only modeled up to 50 µm to avoid a large amount of mesh and a long computation time. Within this length range, the absolute value of the attenuation factor increases with electrode length. On the other hand, from Figure 2.8b, the electrode width seems to be less relevant to the attenuation factor, regardless of the initial gap distance. Figure 2.8c shows that the attenuation factor with the PDMS at the rear position is higher compared to the case at the front position. As expected, this is due to the difference in the applied strain in both cases as shown in Figure 2.10e. Under the application of the same bending force, the strain applied to the PDMS at the rear position is almost 3 times higher than the strain applied to the PDMS at the front position.

**Figure 2.9.** COMSOL simulation results of the sidewall profiles of the Au electrodes when the PDMS is strained. (a) NGEs are in the orthogonal orientation to the bending axis, the sidewalls of Au1 and Au2 remain parallel to each other. (b) NGEs are in parallel to the bending axis, the top ends of Au1 and Au2 are closer than the bottom ends.

Figure 2.8d shows curves of NGEs in different orientations. In general, the attenuation factor of NGEs in parallel to the PDMS normal is smaller than that of NGEs in the orthogonal orientation. This is because the gap distance is reduced via the Poisson effect with a downward bending in the former case, and the Poisson's ratios of the materials involved here are all smaller than 0.5. The difference in NGEs orientation also results in differences in deformed sidewall profiles of the Au electrodes under strain. As shown in Figure 2.9, the sidewalls of the Au electrodes remain parallel to each other as the NGEs are orthogonal to the bending axis, whereas the Au electrodes become closer to each other at the top ends as the NGEs are parallel to the bending axis. This difference could lead to different effective tunneling areas when the nanogap is in the quantum tunneling regime (< 3 nm) and is subjected to a voltage bias across the nanogap.

Since all the curves in Figure 2.8 show good linearity, the attenuation factors are extracted from the linear regression curves, which are summarized in Table 2.3 for quantitative comparisons. In this study, attenuation factors range from about -1 x  $10^{-6}$  to -1.2 x  $10^{-5}$ , meaning the nanogap distance can be tuned at 1 nm or even sub-nm step sizes provided the deflection can be controlled at sub-mm step sizes.

**Table 2.3.** Summary of attenuation factor.

| NGEs            | PDMS     | Initial gap | Electrode | Electrode | Attenuation                |

|-----------------|----------|-------------|-----------|-----------|----------------------------|

| orientation     | position | distance    | length    | width     | factor = $\Delta d/\delta$ |

|                 |          | (nm)        | (µm)      | $(\mu m)$ | $(10^{-6})$                |

| Orthogonal      | Front    | 10          | 10        | 0.5       | -1.9                       |

| (to the bending |          | 10          | 10        | 1.0       | -1.8                       |

| axis)           |          | 10          | 30        | 0.5       | -7.1                       |

|                 |          | 10          | 50        | 0.5       | -11.7                      |

|                 |          | 20          | 10        | 0.5       | -2.3                       |

|                 |          | 20          | 10        | 1.0       | -2.1                       |

|                 |          | 20          | 10        | 2.0       | -1.9                       |

| Orthogonal      | Rear     | 10          | 10        | 0.5       | -6.1                       |

|                 |          | 20          | 10        | 0.5       | -6.6                       |

| Parallel        | Front    | 10          | 10        | 0.5       | -1.1                       |

|                 |          | 10          | 30        | 0.5       | -3.5                       |

| Parallel        | Rear     | 10          | 10        | 0.5       | -1.3                       |

|                 |          | 10          | 30        | 0.5       | -5.3                       |

**Figure 2.10.** COMSOL 3D surface plots of the strain tensor XX component of the bent PS cantilever. (a), (b) PDMS at the front position (15 mm from the free end to the PDMS edge) with (a) an upward and (b) a downward bending. (c), (d) PDMS at the rear position (70 mm from the free end to the PDMS edge) with (c) an upward and (d) a downward bending. A force of 1.5 N is uniformly applied to the free end to bend the cantilever. (e), (f) Profiles of strain tensor XX components across the PDMS top surface for the upper bending displayed in (a), (c) and the downward bending in (b) and (d), respectively.

**Figure 2.11.** COMSOL 3D surface plots of the strain tensor YY component of the bent PS cantilever. (a), (b) PDMS at the front position with (a) an upward and (b) a downward bending. (c), (d) PDMS at the rear position with (a) an upward and (d) a downward bending. A force of 1.5 N is uniformly applied to the free end to bend the cantilever. (e), (f) Profiles of strain tensor YY components across the PDMS top surface for the upper bending displayed in (a), (c) and the downward bending in (b) and (d), respectively.

**Figure 2.12.** COMSOL calculation results of the PDMS/cantilever bending. (a) Deflection as a function of applied bending force, simulated (in blue) and experimentally measured (in red) using a linear ruler to measure the deflection in the z-direction with a weight of 0 to 500 g attached to the free end of the PS cantilever. (b) Strain tensor components,  $\varepsilon_{XX}$  and  $\varepsilon_{YY}$ , at the center point of the PDMS top surface under various bending conditions and PDMS positions. The positive deflection corresponds to upward bending which causes compressive strain in X-direction, and tensile strain in Y-direction due to the Poisson effect.

Figure 2.10 and Figure 2.11 show COMSOL simulation results of the strain tensor XX ( $\epsilon_{XX}$ ), and YY ( $\epsilon_{YY}$ ) components of the studied model, respectively. The strain applied on the PDMS substrate by the cantilever bending is not uniform on the PDMS top surface, regardless of the strain direction. As shown in Figure 2.10e and f,  $\epsilon_{XX}$  has a maximum absolute value close to the center of the PDMS substrate, regardless of the PDMS position or bending direction. On the contrary,  $\epsilon_{YY}$  has a minimum absolute value close to the center of the PDMS substrate, regardless of the PDMS position or bending direction (see Figure 2.11e, f). Therefore, the difference in  $\epsilon_{YY}$  at the PDMS center between the front and the rear position is relatively small compared to the other sites on the PDMS substrate. This is the reason why the difference in slope (attenuation factor) between the two curves with parallel orientation is small (-1.1 and -1.3) in Figure 2.8d. These simulation results show the importance of the position of the NGEs on the PDMS in the attenuation factor.

Figure 2.12a shows a non-linear relationship between the bending force and the caused deflection with the given parameters listed in Table 2.2. Figure 2.12b displays the relationships between the deflection and the strain applied at the center point of the PDMS top surface. The linearity of each curve remains good up to 20 mm deflection, which corresponds to 1.7%  $\epsilon_{XX}$  and 0.3%  $\epsilon_{YY}$  for the PDMS at the rear position, and 0.6%  $\epsilon_{XX}$  and 0.3%  $\epsilon_{YY}$  for the PDMS at the front position.

# 2.4 Study of diffusion barrier layer

# 2.4.1 The effect of rapid thermal annealing to NGEs