## Hybrid Modular Multilevel Converter for Pumped Hydro Storage Applications

Présentée le 8 avril 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire d'électronique de puissance Programme doctoral en énergie

pour l'obtention du grade de Docteur ès Sciences

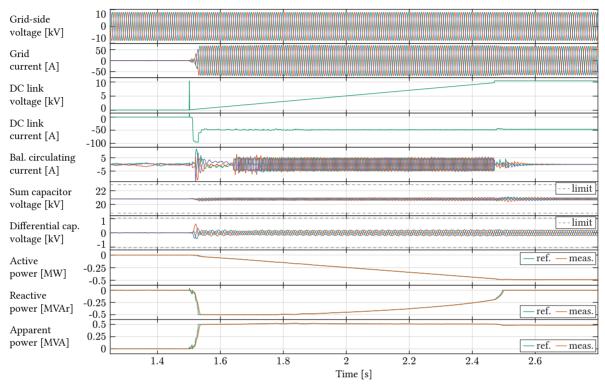

par

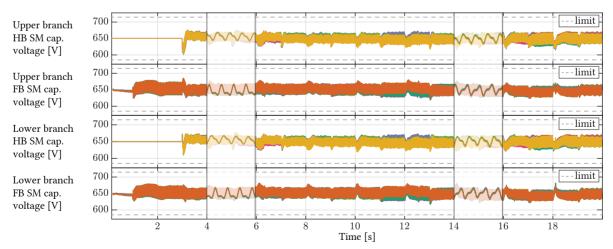

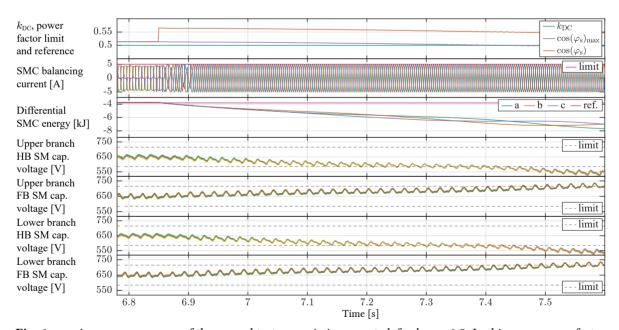

### **Miodrag BASIC**

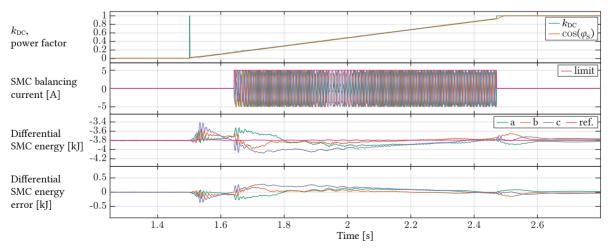

Acceptée sur proposition du jury

Prof. M. Paolone, président du jury

Prof. D. Dujic, directeur de thèse

Prof. H.-P. Nee, rapporteur

Dr C. Haederli, rapporteur

Dr C. Nicolet, rapporteur

École Polytechnique Fédérale de Lausanne Power Electronics Laboratory Station 11 1015 Lausanne, Switzerland

https://pel.epfl.ch

© 2021 by Miodrag Basić

#### **Abstract**

Energy balance in a power system must be maintained at all times, regardless of the variations in generation and consumption. Power systems have been historically developed to ensure such a balance, based on fairly good daily load curve prediction. Even today, the dominant share of electrical energy is generated by base generating units, large coal- or nuclear power plants, operated at constant power output for optimal efficiency. Daily profile of discrepancy between the consumption and the base generation varies with social and industrial activities. Large Pumped Hydro Storage Plants (PHSPs) are introduced to the power system to accumulate the excess of energy during the low demand (nighttime), and provide it back during the high demand (daytime).

As we are heading towards the Renewable Energy Sources (RES)-dominated power systems, their stochastic nature and ever-increasing share are altering the daily load curve of the system, increasing the need for highly-flexible energy storage capacities. Further, the PHSP strategy of accumulating the energy during the nighttime to provide it back during the daytime is not profitable anymore in the deregulated market, where high volumes of RES-generated energy can become available midday. Thus, from both engineering and commercial interests, PHSPs must be enabled to respond faster and provide a higher array of ancillary services to keep up the pace with the power system evolution. While we are witnessing scaling-up of alternative energy storage facilities, e.g. battery-based, PHSPs readily offer by far the highest share of energy storage capacity in the power system. High flexibility can be yielded through conversion of existing fixed-speed PHSPs to variable speed operation, by decoupling the machine from the grid by an AC-AC power electronics converter.

The Modular Multilevel Converter (MMC) is inherently scalable to the voltage and power levels of machines typically found in large PHSPs, i.e. 6 kV to 20 kV and 80 MVA to 400 MVA, and this thesis is based around its implementation in variable speed PHSP retrofitting scenario. To operate the machines originally designed for sine-wave grid power supply, at rated torque and over the entire frequency range for the highest flexibility, the MMC-specific internal energy balancing actions have to be performed in a machine-friendly way. Starting from the two extreme reference designs – a Half-Bridge (HB)-only Indirect MMC (I-MMC) requiring prohibitively high Common-Mode (CM)-voltage stress to the machine, and a Full-Bridge (FB)-Active Front-End (AFE)-based I-MMC providing CM-voltage-free operation at prohibitively high losses, the thesis introduces two novel control- and design methods based on Hybrid MMC (H-MMC) AFE, where hybrid refers to a mix of HB and FB Submodules (SMs) in each branch.

The first method offers reduced CM-voltage stress to the machine, at 56 % FB SM share in the AFE stage, while not compromising the grid-code compatibility. The CM-voltage reduction is achieved by reducing DC link voltage reference with machine speed down to 50 %, requiring less-severe balancing action in the Low Frequency (LF) operating region. The second method enables CM-voltage-free rated-torque machine operation over the full speed range, through down-to-zero DC link voltage reduction capability, requiring 62 % FB SM share in the AFE. DC link voltage reference variation with the machine speed in Variable Speed Drive (VSD) MMC eliminates the need for CM-voltage-based balancing intervention in the LF region. While this method cannot operate at unity grid-side power factor below rated machine speed, thus not offering full grid-code compatibility, a design trade-off is offered between the attainable power factor range and FB SM share. A comprehensive set of test scenarios has been performed for each of the newly introduced methods to verify the validity.

**Keywords** pumped hydro storage, hydroelectric power generation, hybrid modular multilevel converter, mixed cell converter, AC-DC converter, converter control, retrofit

#### Résumé

L'équilibre énergétique d'un système électrique doit être maintenu à tout instant, quelles que soient les variations de la production et de la consommation. Les systèmes électriques ont été historiquement développés pour assurer un tel équilibre, sur la base d'une assez bonne prévision de la courbe de charge quotidienne. Aujourd'hui encore, la part dominante de l'énergie électrique est produite par des unités de production de base, de grandes centrales à charbon ou nucléaires, exploitées à puissance constante pour une efficacité optimale. Le profil quotidien de l'écart entre la consommation et la production de base varie en fonction des activités sociales et industrielles. De grandes centrales hydroélectriques de pompage (PHSP) sont introduites dans le système électrique pour accumuler l'excès d'énergie pendant la faible demande (la nuit) et le restituer pendant la forte demande (le jour).

Alors que nous dirigeons vers des systèmes électriques dominés par les sources d'énergie renouvelables (SER), leur nature stochastique et leur part toujours croissante modifient la courbe de charge quotidienne du système, ce qui augmente le besoin de capacités de stockage d'énergie hautement flexibles. De plus, la stratégie PHSP consistant à accumuler l'énergie pendant la nuit pour la restituer pendant la journée n'est plus rentable sur le marché déréglementé, où de gros volumes d'énergie produite par les SER peuvent devenir disponibles en milieu de journée. Par conséquent, d'un point de vue technique et commercial, les PHSPs doivent être en mesure de réagir plus rapidement et de fournir un éventail plus large de services auxiliaires pour suivre le rythme de l'évolution du système électrique. Alors que nous assistons à la mise à l'échelle des installations de stockage d'énergie alternative, par exemple à base de batteries, les PHSP offrent de loin la plus grande part de capacité de stockage d'énergie dans le système électrique. Une grande flexibilité peut être obtenue en convertissant les PHSP à vitesse fixe existantes en un fonctionnement à vitesse variable, en découplant la machine du réseau par un convertisseur électronique de puissance AC-AC.

Le convertisseur modulaire multi-niveaux (MMC) est intrinsèquement adaptable aux niveaux de tension et de puissance des machines que l'on trouve généralement dans les grands PHSP, c'est-à-dire 6 kV to 20 kV et 80 MVA to 400 MVA, et cette thèse est fondée sur sa mise en œuvre dans un scénario de rétrofit de PHSP à vitesse variable. Pour faire fonctionner les machines conçues à l'origine pour l'alimentation sinusoïdale du réseau, au couple nominal et sur toute la plage de fréquence pour une flexibilité maximale, les actions d'équilibrage de l'énergie interne spécifiques à la MMC doivent être réalisées de manière adaptée pour la machine. En partant de deux conceptions de référence extrêmes - un MMC indirect (I-MMC) uniquement en demi-pont (HB) nécessitant une tension de mode commun (CM) prohibitive pour la machine, et un I-MMC fondé sur un front actif (AFE) en pont complet (FB) fournissant un fonctionnement sans tension de mode commun avec des pertes prohibitives, la thèse présente deux nouvelles méthodes de contrôle et de conception fondées sur l'AFE du MMC hybride (H-MMC), où hybride fait référence à un mélange de sous-modules (SMs) HB et FB dans chaque branche.

La première méthode permet de réduire la tension de la machine, avec une part de 56 % de SM FB dans l'étage AFE, sans compromettre la compatibilité avec le code de réseau. La réduction de tension CM est obtenue en réduisant la référence de tension de liaison CC avec une vitesse de machine réduite jusqu'à 50 %, ce qui nécessite une action d'équilibrage moins sévère dans la région de fonctionnement à basse fréquence (LF). La deuxième méthode permet un fonctionnement de la machine sans tension CM à couple nominal sur toute la plage de vitesse, grâce à une capacité de réduction de la tension de liaison CC jusqu'à zéro, nécessitant une part de 62 % de FB SM dans l'AFE. La variation de la référence de tension de liaison CC en fonction de la vitesse de la machine dans le MMC à entraînement à vitesse variable (VSD) élimine la nécessité d'une intervention d'équilibrage fondée sur la tension CM dans la

région LF. Bien que cette méthode ne puisse pas fonctionner à un facteur de puissance unitaire côté réseau en dessous de la vitesse nominale de la machine, n'offrant donc pas une compatibilité totale avec le code de réseau, un compromis de conception est offert entre la plage de facteur de puissance atteignable et la part de FB SM. Un ensemble complet de scénarios d'essai a été réalisé pour chacune des méthodes nouvellement introduite afin d'en vérifier la validité.

**Mots clés:** stockage hydroélectrique par pompage, production d'énergie hydroélectrique, convertisseur multiniveau modulaire hybride, convertisseur à cellules mixtes, convertisseur AC-DC, contrôle du convertisseur, rétrofit.

## Acknowledgments

A clear conscience is the sure sign of a bad memory.

Mark Twain

Four years ago, I was given an opportunity to leave the comfort of an engineering position in my hometown, join the Power Electronics Laboratory (PEL) of EPFL, and pursue the PhD degree. I am grateful to my thesis advisor, Prof. Dražen Dujić, for giving me this opportunity, and even more so for providing continuous support, technical and other discussions, and trying to provoke improvements in my personality beyond the "call of duty". The perception of our relationship was that of a friendly one since the first day.

My stay at EPFL was in good part supported by the Swiss Federal Office of Energy, and the Innosuisse – Swiss Innovation Agency, through the project number 25109.1 PFEN-IW, and for this I am thankful. The mutual project with GE Renewable Energy, located in Birr, Switzerland, brought important insights from the industrial experience. I would like to thank Dr. Alexander Schwery for the valuable discussions, technical inputs and advice throughout the work.

I am grateful to Prof. Hans-Peter Nee of KTH Royal Institute of Technology, Dr. Christoph Haederli of Hitachi ABB Power Grids, Dr. Christophe Nicolet of EPFL and PowerVision Engineering, and to Prof. Mario Paolone of EPFL, for accepting to take part in my PhD examination as the jury members. It is a significant commitment and responsibility that they have happily taken, and a valuable expert feedback that they will provide. I would also like to thank Yanick for meticulous proofreading of the thesis.

The overall perception of the PhD journey is to a good extent determined by the thesis advisor, but the everyday life at the lab is all about the people who make it, and those of PEL really made a difference. I would like to thank all of you for being such a good company, stress-relievers, sources of knowledge, fun, good- and not-so-good jokes. The array of backgrounds, interests and personalities of all of you made me grow as well.

Relocating from Belgrade to Lausanne and feeling "at home" again, having company for all sorts of good- and bad moments was only possible thanks to the friends I have made here. It all started through a small group of Serbian students, only to spread to those from around the world. Luckily, most of you are going to end up in Turgi anyway, but the rest will make me miss Lausanne greatly. I am also thankful to my friends from back home, and proud that our relationships endured the test of distance and time.

To my family, I am beyond grateful for continuous support since the first thought of starting this journey. They are to a good extent responsible for who I am today, and I couldn't have done this if they were different. I am lucky to have a family which does not always comply with anything I say, but rather does me a real favor by staying objective in their support, while unconditional in their love.

Lastly, my gratitude goes to my wife Aleksandra. For 10 years now, she has been a support, a voice of reason, a partner and a friend – and there are no indications this is going to change. I have had her unconditional support and understanding throughout this work, we have endured many challenges, and unsurprisingly we both ended up in Turgi. It is now the time for new challenges!

Lausanne, October 2021 Miodrag Basić

#### List of Abbreviations

3PH Three-Phase

AC Alternating Current

AC/AC Three-Phase to Three-Phase

AFE Active Front-End

CCC Circulating Current Control

CFSM Converter-Fed Synchronous Machine

CHB Cascaded H-Bridge

CM Common-Mode

D-MMC Direct MMC

DC Direct Current

DC/3-AC Direct to Three-Phase

DDSRF Double Decoupled Synchronous Reference Frame

DFIM Doubly-Fed Induction Machine

EMF Electromotive Force

FB Full-Bridge

FOC Field-Oriented Control

FVSC Flexible Voltage Support Control

GCC Grid Current Control

H-MMC Hybrid MMC HB Half-Bridge HF High Frequency HV High Voltage

HVDC High Voltage Direct Current

I-MMC Indirect MMC

IGBT Insulated Gate Bipolar Transistor

IGCT Integrated Gate-Commutated Thyristor

INU Inverter Unit

KVL Kirchhoff's voltage law

LF Low Frequency

LSC-PWM Level-Shifted Carrier PWM LVRT Low Voltage Ride-Through

MAS Maximum Area Saturator MMC Modular Multilevel Converter

MV Medium Voltage

NLM Nearest-Level Modulation

OPP Optimized Pulse Patterns

PEBB Power Electronic Building Block

PEL Power Electronics Laboratory

PHSP Pumped Hydro Storage Plant

PLL Phase-Locked Loop

PS Proportional Saturator

PSC Phase-Shifted Carrier

PSC-PWM Phase-Shifted Carrier PWM

PV Photo-Voltaic

RES Renewable Energy Sources

SFC Static Frequency Converter

SM Submodule

SMC Submodule Cluster

SRF Synchronous Reference Frame STATCOM Static Synchronous Compensator

TDD Total Demand DistortionTHD Total Harmonic DistortionTSO Transmission System Operator

VS Variable Speed

VSC Voltage Source Converter

VSD Variable Speed Drive

WRSM Wound-Rotor Synchronous Machine

## **List of Symbols**

$C_{\rm SM}$  SM capacitance  $C_{\rm br}$  Branch capacitance  $L_{\rm br}$  Branch inductance

$L_{\rm g}$  Grid equivalent inductance  $M_{\rm br}$  Branch mutual inductance

$N_{\rm SM}$  Number of submodules per branch

$P^*$  Active power reference

*P* Active power

$Q^*$  Reactive power reference

Q Reactive power

$R_{\rm SM}$  SM equivalent resistance

$R_{\rm br}$  Branch resistance

$R_{\rm g}$  Grid equivalent resistance

S Apparent power  $V_{

m DC}$  DC link voltage  $V_{

m SM}$  Submodule voltage

$\omega_{

m g}$  Fundamental grid angular frequency

$\omega_{\rm s}$  MMC AC-side electrical angular frequency

$\psi_{\rm g}$  Grid current-phasor angle

$\psi_{\rm s}$  MMC AC-side current-phasor angle

$\psi_{dq}$  dq angle

$\theta_{

m g}$  Grid voltage-phasor angle

$\theta_{\rm s}$  MMC AC-side voltage-phasor angle  $\phi_{\rm g}$  Grid voltage to current phase shift

$\varphi_s$  MMC AC-side voltage to current phase shift

$f_{\text{sw,app}}$  Apparent switching frequency

$f_{\rm sw}$  Switching frequency

$f_{\rm g}$  Fundamental grid frequency

*i*<sub>c</sub> Circulating current

$i_g$  Grid current

$k_{\rm br}$  Branch inductance coupling coefficient

$m_p, m_n$  Branch modulation indices  $m_s$  AC-side modulation index  $v_{g\{a,b,c\}}^*$  GCC voltage references

*v*<sub>CM</sub> Common Mode voltage

$v_c$  Summed phase-leg inserted voltage

$v_g$  AC grid voltage

$v_s$  Differential phase-leg voltage

$\begin{array}{ll} v_{C\Sigma p}, v_{C\Sigma n} & \text{Summed branch capacitor voltages} \\ v_{C\Sigma}^{\Delta} & \text{Differential phase-leg capacitor voltage} \\ v_{C\Sigma}^{\Sigma} & \text{Summed phase-leg capacitor voltage} \end{array}$

## Contents

| Al | ostra | et                                                           | i   |

|----|-------|--------------------------------------------------------------|-----|

| Ré | sum   | é                                                            | iii |

| Ac | knov  | wledgments                                                   | v   |

| Li | st of | Abbreviations                                                | vii |

| Li | st of | Symbols                                                      | xi  |

| 1  | Intr  | roduction                                                    | 1   |

|    | 1.1   | Background                                                   | 1   |

|    |       | 1.1.1 Fixed speed PHSPs                                      | 1   |

|    |       | 1.1.2 Power system evolution and deregulation                | 2   |

|    | 1.2   | Variable speed PHSPs                                         | 4   |

|    |       | 1.2.1 Doubly-fed induction machines                          | 4   |

|    |       | 1.2.2 Converter-fed synchronous machines                     | 5   |

|    |       | 1.2.3 Power range of interest                                | 6   |

|    | 1.3   | Motivations                                                  | 7   |

|    |       | 1.3.1 Monolithic multilevel converter technology limitations | 7   |

|    |       | 1.3.2 MMC perspectives for PHSP                              | 9   |

|    | 1.4   | MMC scaling for PHSP applications                            | 9   |

|    |       | 1.4.1 Indirect MMC for PHSP applications                     | 10  |

|    |       | 1.4.2 Direct MMC for PHSP applications                       | 11  |

|    |       | 1.4.3 Indirect MMC for PHSP retrofit                         | 11  |

|    | 1.5   | Objectives                                                   | 12  |

|    | 1.6   | Outline of the thesis                                        | 12  |

|    | 1.7   | List of publications                                         | 13  |

| 2  | Indi  | irect MMC Modeling                                           | 15  |

|    | 2.1   | MMC governing equations                                      | 15  |

|    | 2.2   | Converter control outline                                    | 18  |

|    | 2.3   | Internal MMC control                                         | 20  |

|    |       | 2.3.1 Branch-level energy ripple dynamics                    | 20  |

|    |       | 2.3.2 Energy measurement and filtering                       | 22  |

|    |       | 2.3.3 Horizontal energy balancing                            | 23  |

|    |       | 2.3.4 Vertical energy balancing                              | 24  |

|    |       | 2.3.5 Total energy control                                   | 25  |

|    |       | 2.3.6 MMC voltage references generation                      | 27  |

|    |       | 2.3.7 SM voltage balancing                                   | 27  |

|    |       | 2.3.8 Modulation                                             | 27  |

|    | 2.4   | Higher level control                                         | 28  |

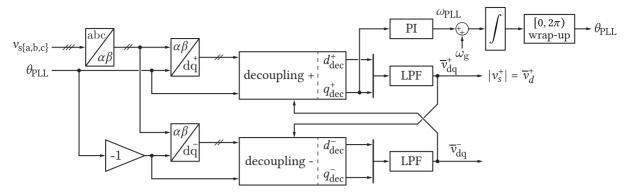

|    |       | 2.4.1 Grid synchronization                                   | 28  |

|   |      | 2.4.2 Grid current control                                    | 28 |

|---|------|---------------------------------------------------------------|----|

|   |      | 2.4.3 DC link voltage control                                 | 30 |

|   |      | 2.4.4 Active and reactive power control                       | 30 |

|   |      | 2.4.5 AC power grid                                           | 31 |

|   | 2.5  | SM modeling and ratings                                       | 32 |

|   |      | 2.5.1 PEL SM ratings                                          | 32 |

|   | 2.6  | Model output evaluation                                       | 34 |

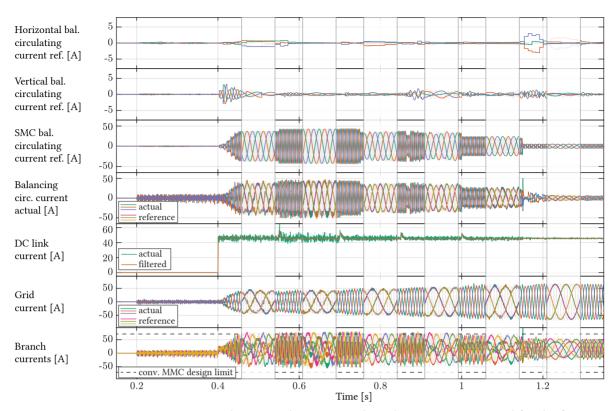

|   |      | 2.6.1 Internal MMC control                                    | 34 |

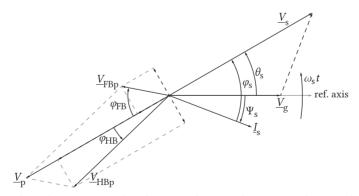

|   |      | 2.6.2 Higher level control                                    | 37 |

|   |      | 2.6.3 Back-to-back operation behavior                         | 42 |

|   | 2.7  | Summary                                                       | 42 |

| 3 | Indi | rect MMC Control for PHSP Application                         | 43 |

| • | 3.1  | Converter control outline                                     | 43 |

|   | 3.2  | Internal MMC control for LF operation                         | 44 |

|   | J    | 3.2.1 SM-level energy ripple in LF operation                  | 45 |

|   |      | 3.2.2 Common-mode voltage injection                           | 47 |

|   |      | 3.2.3 Horizontal energy balancing                             | 50 |

|   |      | 3.2.4 Vertical energy balancing                               | 50 |

|   |      | 3.2.5 Start-up and switch-over between LF and HF mode         | 50 |

|   | 3.3  | Machine-side control                                          | 55 |

|   | 0 0  | 3.3.1 Current control                                         | 55 |

|   |      | 3.3.2 Speed control                                           | 58 |

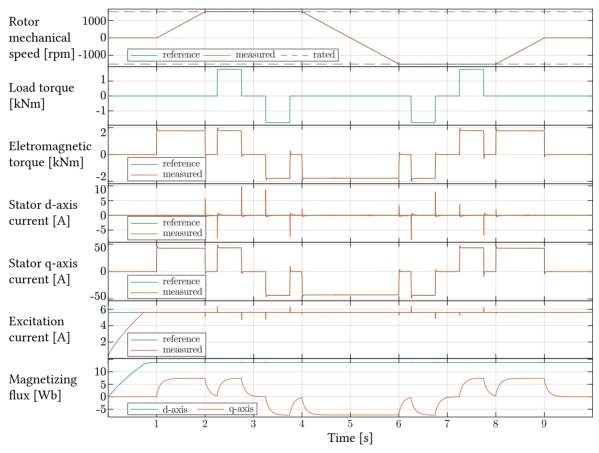

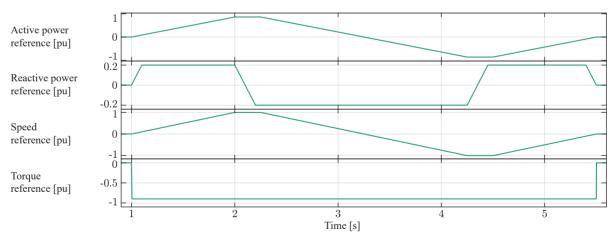

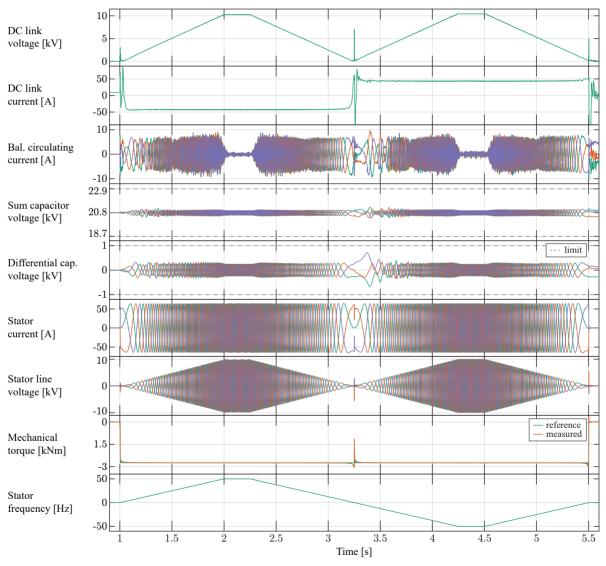

|   |      | 3.3.3 Test scenario model output                              | 61 |

|   | 3.4  | Grid-side control                                             | 63 |

|   |      | 3.4.1 Grid code requirements                                  | 63 |

|   |      | 3.4.2 Grid synchronization for unbalanced conditions          | 66 |

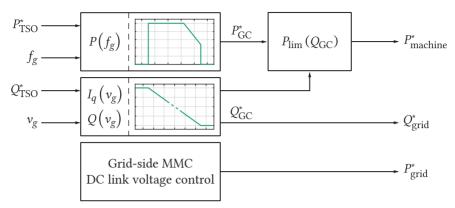

|   |      | 3.4.3 Power reference scaling for grid-code compliance        | 67 |

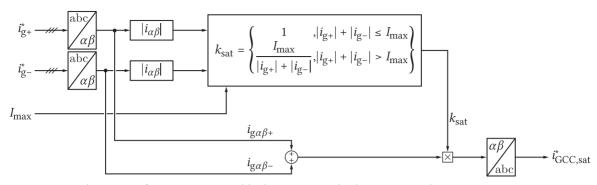

|   |      | 3.4.4 GCC reference saturation                                | 68 |

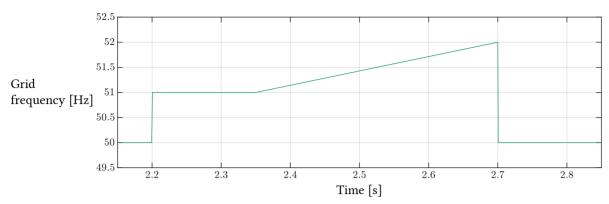

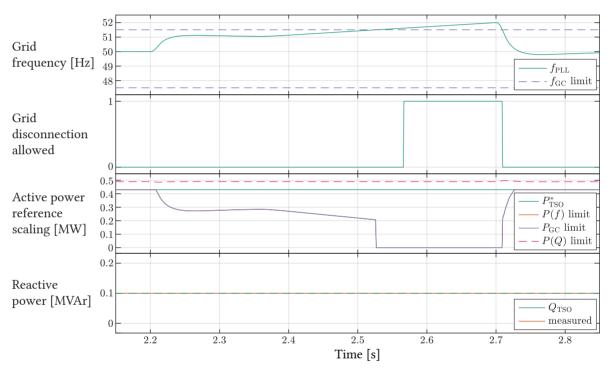

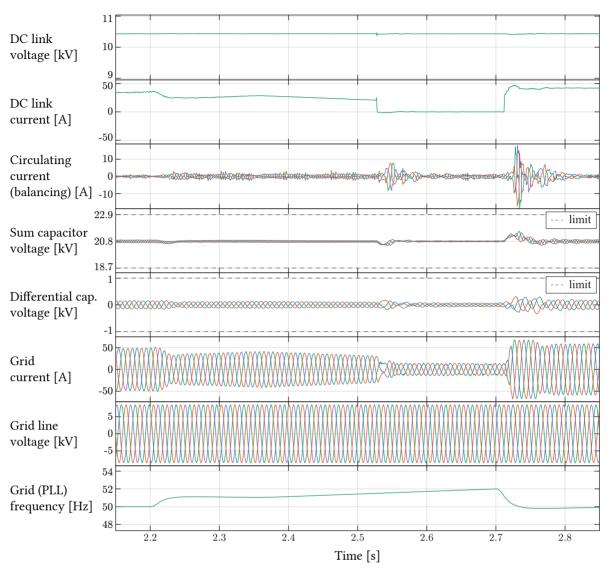

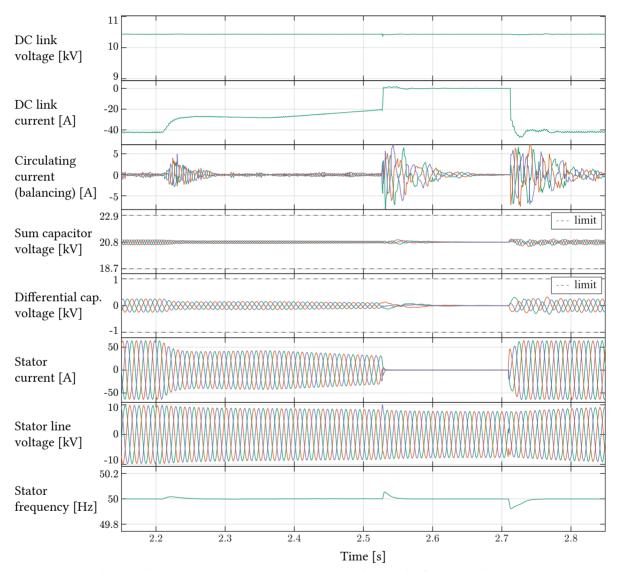

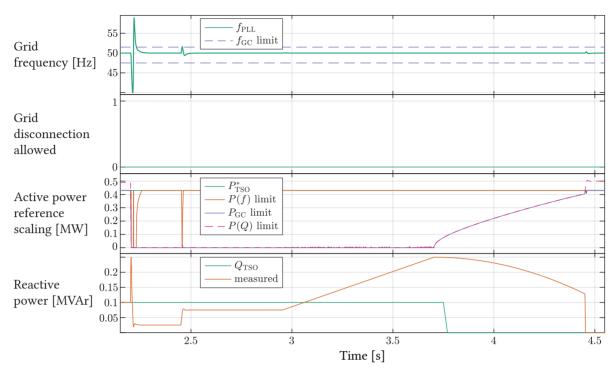

|   |      | 3.4.5 Test scenarios                                          | 69 |

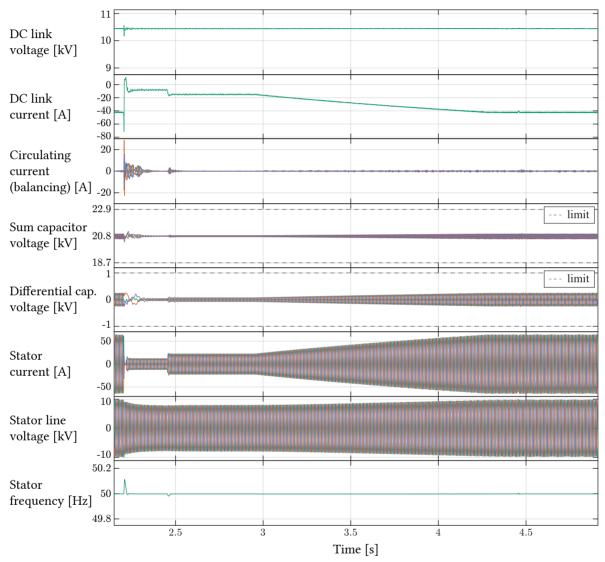

|   |      | 3.4.6 GCC reference calculation for unbalanced grid operation | 81 |

|   | 3.5  | Summary                                                       | 85 |

| 4 | Vari | table DC Link Voltage Operation for PHSP Retrofit             | 87 |

|   | 4.1  | Low frequency CM-voltage-free operation                       | 87 |

|   |      | 4.1.1 Machine-side stage                                      | 88 |

|   |      | 4.1.2 Grid-side stage                                         | 88 |

|   | 4.2  | Converter control                                             | 90 |

|   |      | 4.2.1 Grid-side higher-level control                          | 90 |

|   |      | 4.2.2 Machine-side higher-level control                       | 90 |

|   |      | 4.2.3 Internal MMC control                                    | 91 |

|   | 4.3  | Test scenario                                                 | 91 |

|   |      | 4.3.1 Variable Speed (VS) PHSP operation                      | 91 |

|   |      | 4.3.2 Low Voltage Ride-Through (LVRT) evaluation              | 91 |

|   | 4.4  | Simulation results                                            | 92 |

|   |      | 4.4.1 Machine-side VS PHSP operation                          | 03 |

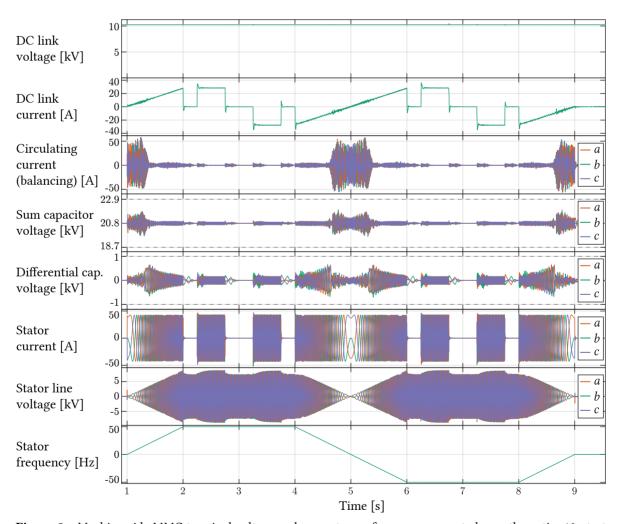

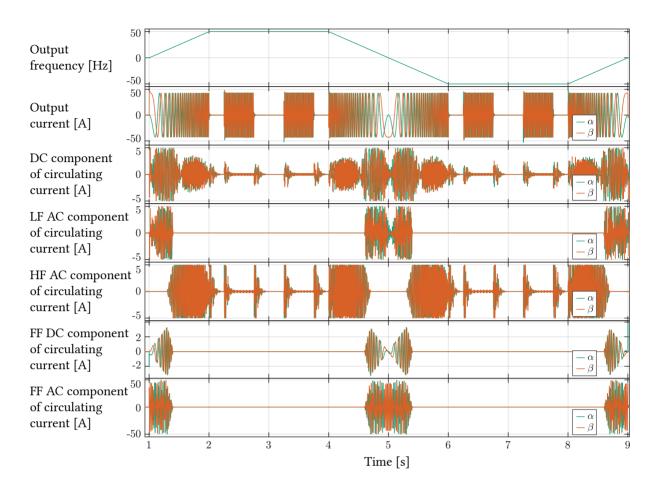

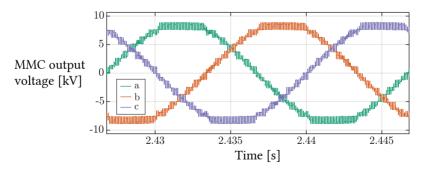

|   |     | 4.4.2 Zero-crossing capacitor ripple                          | 93  |

|---|-----|---------------------------------------------------------------|-----|

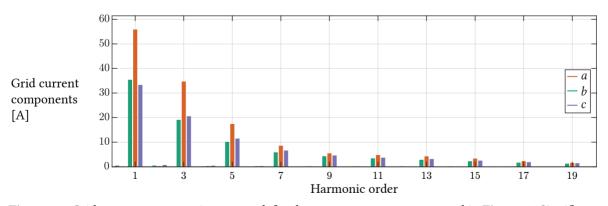

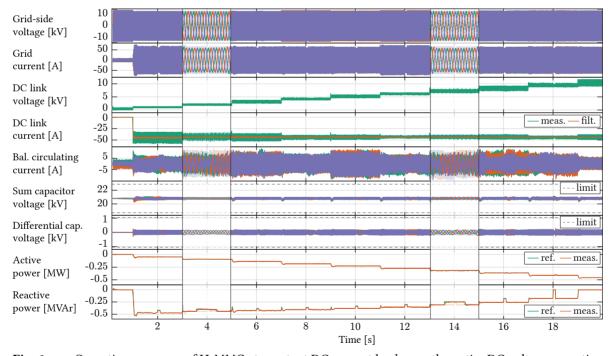

|   |     | 4.4.3 Grid-side variable-speed PHSP operation                 | 94  |

|   |     | 4.4.4 LVRT                                                    | 94  |

|   | 4.5 | Summary                                                       | 95  |

| 5 | Hyl | brid MMC With Reduced CM-Voltage-Stress for PHSP Retrofit     | 97  |

|   | 5.1 | Reduced DC link voltage operation                             | 97  |

|   |     | 5.1.1 Partial DC link voltage reduction                       | 99  |

|   | 5.2 | H-MMC equivalent circuit and energy dynamics                  | 100 |

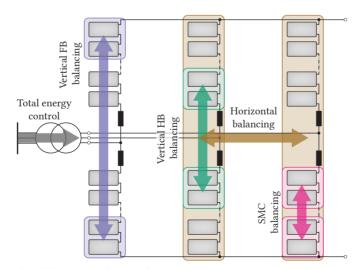

|   | 5.3 | H-MMC energy balancing                                        | 104 |

|   |     | 5.3.1 Branch-level energy balancing                           | 104 |

|   |     | 5.3.2 Inter-SMC energy balancing                              | 104 |

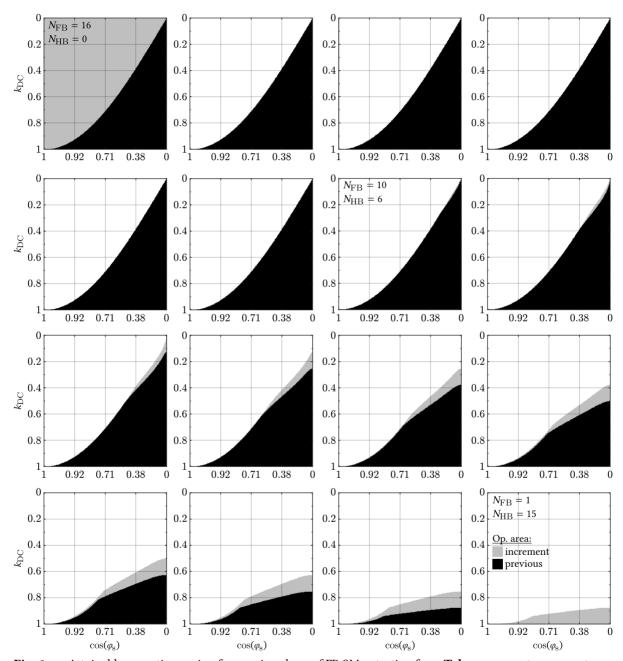

|   | 5.4 | H-MMC design                                                  | 106 |

|   |     | 5.4.1 SMC insertion voltage waveform                          | 107 |

|   |     | 5.4.2 Determination of the required FB/HB share               | 107 |

|   | 5.5 | Virtual SM at variable DC voltage operation                   | 108 |

|   |     | 5.5.1 Virtual SM concept                                      | 108 |

|   |     | 5.5.2 H-MMC modulation                                        | 109 |

|   | 5.6 |                                                               | 110 |

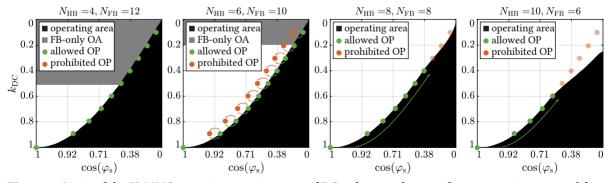

|   |     | 5.6.1 Unity power factor operation                            | 111 |

|   |     | 5.6.2 Variable power factor operation                         | 112 |

|   |     | 5.6.3 Constant-torque machine start-up                        | 112 |

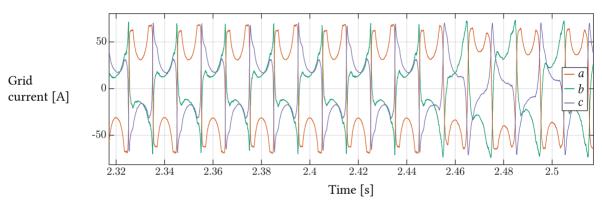

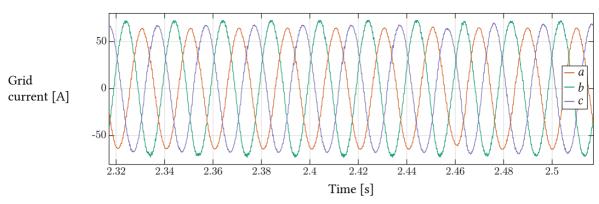

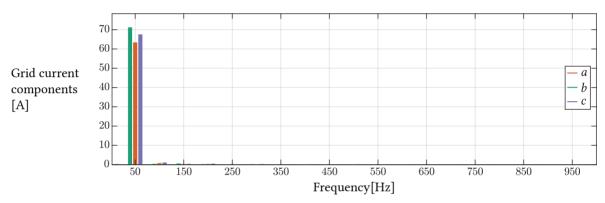

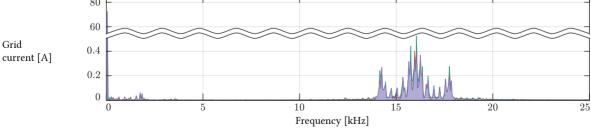

|   |     | 5.6.4 Spectral analysis of the grid-side current              | 113 |

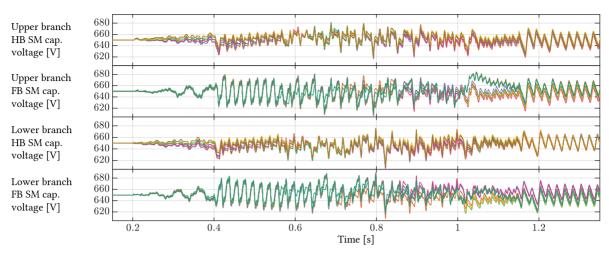

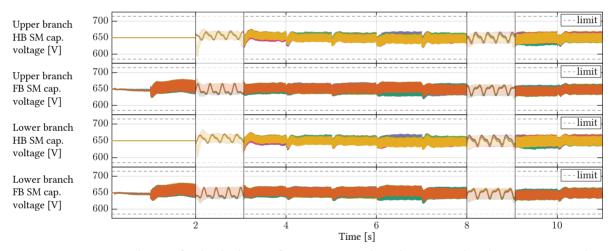

|   |     | 5.6.5 SMC energy control                                      | 114 |

|   |     | 5.6.6 Current capacity requirements of the H-MMC              | 115 |

|   | 5.7 |                                                               | 117 |

|   | 5.8 | Summary                                                       | 117 |

| 6 | Hyl | brid MMC With Zero CM-Voltage-Stress for PHSP Retrofit        | 119 |

|   | 6.1 |                                                               | 119 |

|   | 6.2 | 1 01 1 0                                                      | 119 |

|   |     | 6.2.1 Equivalent circuit                                      | 120 |

|   |     | 6.2.2 Operating constraints                                   | 121 |

|   |     | 6.2.3 Submodule Cluster (SMC) insertion voltage determination | 122 |

|   |     | 6.2.4 Power factor limitation                                 | 124 |

|   |     | 6.2.5 Design for an arbitrary DC voltage range                | 124 |

|   |     | 6.2.6 Design selection for PHSP application                   | 125 |

|   | 6.3 | <i>e.</i>                                                     | 126 |

|   |     | 6.3.1 Conventional energy balancing loops                     | 127 |

|   |     | 6.3.2 Vertical energy balancing                               | 127 |

|   |     | 6.3.3 Inter-SMC energy balancing                              | 128 |

|   |     | 6.3.4 Modulation                                              | 128 |

|   |     | 6.3.5 System-level control                                    | 129 |

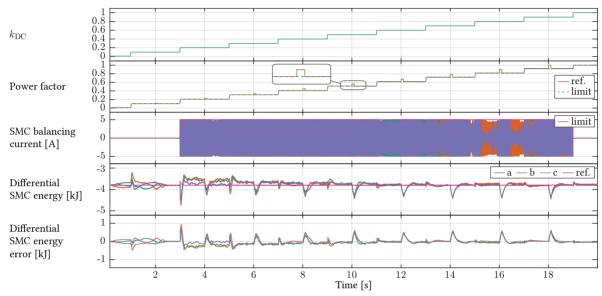

|   | 6.4 |                                                               | 130 |

|   |     | 6.4.1 H-MMC AFE supplying passive load                        | 130 |

|   |     | 6.4.2 H-MMC limit of operation                                | 132 |

|   |     | 6.4.3 Constant-torque machine start-up       | 135 |

|---|-----|----------------------------------------------|-----|

|   | 6.5 | Discussion of the results                    | 138 |

|   | 6.6 | Summary                                      | 138 |

| 7 | Sun | nmary, Overall Conclusions and Future Works  | 141 |

|   | 7.1 | Summary and contributions                    | 141 |

|   | 7.2 | Overall conclusions                          | 143 |

|   | 7.3 | Future works                                 | 144 |

|   |     | 7.3.1 Switching frequency reduction          | 144 |

|   |     | 7.3.2 Reduced SM reference voltage operation | 144 |

|   |     | 7.3.3 Real-life efficiency comparison        | 144 |

|   |     | 7.3.4 De-rated operation in case of SM loss  | 144 |

# 1 Introduction

#### 1.1 Background

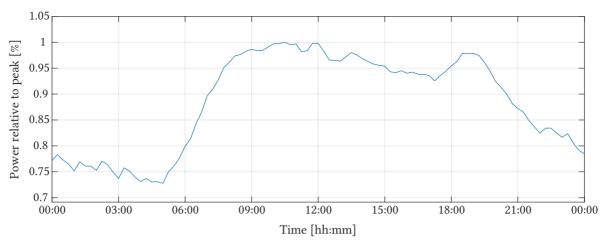

It is well known that, to maintain equilibrium in a classical power system, rate of electrical energy generation must equal rate of consumption at all times. Consumption is varying throughout the day, being significantly higher during daytime than during night (**Fig. 1.1**). On the other hand, big thermal power plants, e.g. coal and nuclear, that are globally still the dominant source of electrical energy [1], feature start-up times measured in hours or days and, once online, operate at highest efficiency while outputting constant power. Energy balancing is thus achieved by utilizing a number of such big thermal plants as base generation units of constant power output, a number of more flexible plants, e.g. gas powered and hydro, as balancing units of variable power output, and a number of reserve units for cases of big system-level disturbances.

One way to reduce the share of balancing and spinning reserve units in the overall installed generation capacity is to establish flexible grid-scale energy storage systems. By storing excess of energy from constant output plants at times of lower demand, typically throughout the night, these units can offer peaking power to the grid during high demands, typically during the daytime.

#### 1.1.1 Fixed speed Pumped Hydro Storage Plants (PHSPs)

PHSP is a grid-connected energy storage system, consisting of two water reservoirs at different elevations – an upper and a lower one. By pumping water from the lower to the upper reservoir, using a grid-supplied electrical machine and a hydraulic pump, the energy is stored in potential form. Delivery of energy is realized by reverting water back to the lower reservoir, through a turbine circuit. A turbine-coupled electrical generator provides electrical energy back to the grid. The reservoirs' volume and altitude difference determine the amount of stored energy. The first units were constructed during 1890s, in the mountain regions of Switzerland and Italy. A significant deployment of PHSPs, however, only began in 1960s to 1970s, when their flexibility was recognized as a good complement to base-load coal and nuclear power plants. [4]–[6].

Traditionally, PHSP units are used for pumping during off-peak hours, allowing the base-load plants to operate at constant, optimal power point, regardless of current consumption. During peak hours, PHSPs are operated in generation mode, to balance production-demand and provide "peak-shaving".

From today's perspective, PHSP represents a well-established and proven technology, having been in global use for decades. With an overall efficiency typically ranging between 70 and 85%, they offer the most efficient means of storing electrical energy at large scales [4], [5]. Featuring short start-up times and high flexibility, these have by far the highest share in installed capacity compared to all

1

**Fig. 1.1** Daily energy consumption profile in Switzerland, on a winter working day of 2018. The plot is based on aggregated energy data of the Swiss control block, and is accurate to 2 % [2], [3].

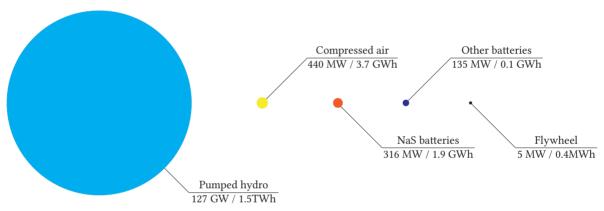

**Fig. 1.2** Global electrical energy storage share. Installed generating power and storage capacity are shown for dominant storage systems. *Other* batteries include: Li-ion, Ni-Cd, lead-acid and Redox.

energy storage techniques, reaching over 127 GW, or 3% of installed generating capacity worldwide (Fig. 1.2) [7], [8].

A fixed-speed PHSP is based on a grid-connected synchronous machine, and a specific hydraulic system. The synchronous machine is connected to transmission grid through a step-up transformer and thus operates at fixed frequency. The hydraulic system is most commonly realized utilizing a reversible pump-turbine unit of Francis type [5]. In this case, a change of operating regime (generation/pumping) requires a change of direction of rotation. Another option is a so-called ternary system, where turbine and pump are built as separate units and connected to a single synchronous machine. This approach enables independent optimization of both pump and turbine, along with faster switch-over between operating regimes, as direction of rotation can be the same.

#### 1.1.2 Power system evolution and deregulation

Supported by various government incentives from economical side and advances in power electronics from technological side, Renewable Energy Sources (RES) have gained a significant market share in recent years. The most dominant in terms of installed power, Photo-Voltaic (PV) and wind sources,

are however inherently stochastic, highly dependent on weather conditions, and thus challenging to predict over longer time horizons. With a total share in globally installed generation capacity currently being more than 1591 GW for wind, and 855 GW for PV plants [9], these intermittent sources require a counter-balance in form of a reliable and fast storage system, for production-load balancing. Regarding Transmission System Operators (TSOs) scheduling models, it has been shown that the share of installed wind plants has a direct impact on the amount and type of the required operation reserves [10], [11].

An additional challenge to traditional operation of PHSPs has been set by gradual deregulation of once centralized electrical energy markets. This change has, in general, introduced wholesale markets for exchange of electrical energy and services:

- Spot market, for day-ahead exchange.

- *Intraday* market, compensating for deviations in planned day-ahead production and consumption schedules [12].

- Futures market, managing energy exchange over longer time horizons.

- *Ancillary* markets, organized for various services, e.g. frequency regulation, reactive power control, voltage support during Low Voltage Ride-Through (LVRT), power reserves.

Nowadays, as a consequence of the aforementioned penetration of volatile RES, considerable peaks and dips in production and demand can occur throughout the day (PV, wind) and night (wind). With prices being formed based on demand and offer on the market, the once fairly estimable daily cost curve of electrical energy can now be significantly deviated. Profitability of traditional operation of PHSPs is directly proportional to the ratio of peak and off-peak cost of electrical energy on the spot markets. On the other hand, ancillary services markets are considerably enlarged due to the aforementioned effects of RES uncertainties.

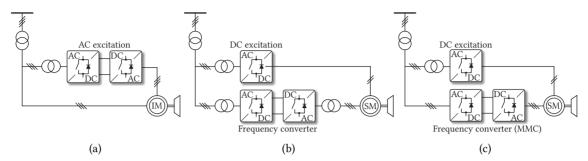

In this sense, the introduction of power electronic converters to PHSPs can provide higher control flexibility, increasing their presence and making them more competitive in ancillary markets. Advances in power electronics, in both switching devices blocking capabilities and topologies, have enabled converter power ratings that match some PHSP machines' ratings [13]. Implementation of such converters to PHSPs is possible for both Converter-Fed Synchronous Machines (CFSMs), and Doubly-Fed Induction Machines (DFIMs) (**Fig. 1.3**). In both cases, they offer decoupling of machine's mechanical speed from the grid frequency.

In practice, this means a machine can be controlled in a way to operate at variable mechanical speed, while maintaining fixed electrical frequency at grid terminals, which offers multiple benefits:

- Expansion of power-frequency regulation to both pumping and turbine mode.

- Higher overall efficiency, through operation at the optimal speed from the hydraulic system perspective, for a given head level.

- Extension of operating range, in terms of maximal to minimal head ratio, compared to fixed-speed PHSPs 1,45 compared to 1,25 is claimed in [5].

- Instantaneous injection of considerable power spikes to the grid in case of disturbances, by exploiting rotor as a flywheel. The use of this feature effectively allows for reduction of grid spinning reserve [14].

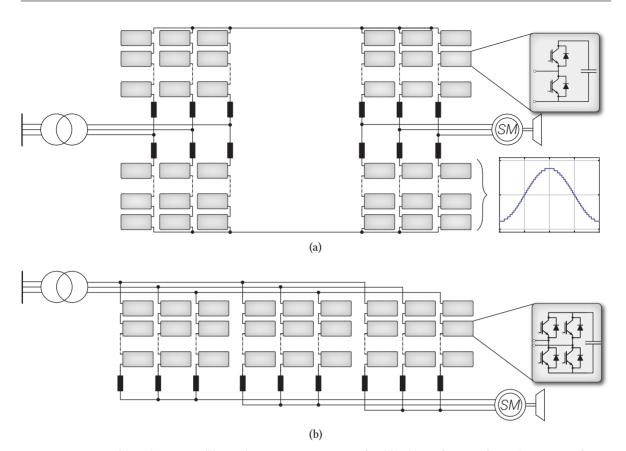

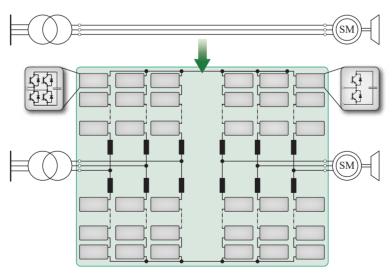

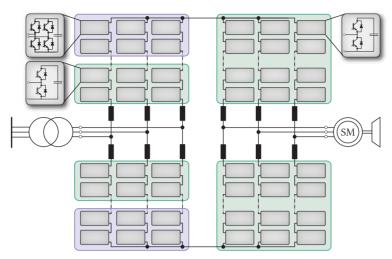

**Fig. 1.3** Variable speed PHSP configurations: (a) DFIM; (b) CFSM; (c) CFSM realized with Modular Multilevel Converter (MMC). The main advantage of the MMC is the scalability to machine- and grid-side voltage level without the need for additional transformers.

• Reduced hydraulic stress and, consequently, expected increase in hydraulic machines' lifetime.

By offering both energy at the spot market and ancillary services like power-frequency regulation, a PHSP could increase overall profitability. Some researchers suggest that this strategy could potentially double the daily income of a PHSP, utilizing certain heuristic algorithms to decide on capacity placement between the markets [10], [15]. In a real-world example of the Portuguese power system, secondary regulation reserve is shown to be the most important source of revenue for a PHSP [16].

#### 1.2 Variable speed PHSPs

#### 1.2.1 Doubly-fed induction machines

The DFIM configuration (**Fig. 1.3**) is the most consolidated technology used for variable speed PHSPs, especially for machines of high power ratings, exceeding 100 MW. The advantage of this configuration is the fact that the converter has to be rated at only a fraction of the nominal power of the machine to achieve usually  $\pm 10\%$  of speed variation [14]. This, in turn, provides roughly  $\pm 30\%$  of pumping power variation [14]. Converters of these power levels are technologically available, making DFIM an already established technology. A list of variable speed units over 100 MW known to the author, currently in operation or under construction, is given in **Tab. 1.1**, based on [4], [17]–[20].

However, in contrast to the aforementioned variable speed operation benefits, several drawbacks exist for the DFIM configuration.

- The wound rotor is complex in design, introduces slip rings as an additional maintenance issue, and has a limited power rating according to cooling capabilities of the machine, limiting the available speed range and starting torque.

- Limited starting torque, in return, may be insufficient when switching between generation and pumping, requiring a dewatering procedure, a time- and resource-consuming task.

- During grid faults resulting in short circuit, low voltage ride-through (LVRT) proves to be challenging for DFIM. High rotor currents in short circuit conditions reach values well above rated, overloading the converter. In case rotor supply converter enters protected mode, rotor windings are short-circuited, and DFIM acts as a consumer of reactive power, negatively contributing to LVRT situation.

| Tab. 1.1  | Variable speed PHSP units above 100 MW currently in operation or under construction, arranged by    |

|-----------|-----------------------------------------------------------------------------------------------------|

| individua | al power rating. Only two installations are based on CFSM: Grimsel being a retrofit and Galgenbichl |

| comprisi  | ng new machines and converters.                                                                     |

| Name           | Country              | Type | Turbine power [MW] | No. of units | Total power [MW] |

|----------------|----------------------|------|--------------------|--------------|------------------|

| Kazunogawa     | Japan                | DFIM | 460                | 2            | 920              |

| Okawachi       | Japan                | DFIM | 395                | 2            | 790              |

| Frades 2       | Portugal             | DFIM | 390                | 2            | 780              |

| Venda Nova 3   | Portugal             | DFIM | 380                | 2            | 760              |

| Okukiyotsu 2   | Japan                | DFIM | 340                | 1            | 340              |

| Omarugawa      | Japan                | DFIM | 330                | 3            | 990              |

| Okutataragi    | Japan                | DFIM | 320                | 2            | 640              |

| Omarugawa      | Japan                | DFIM | 310                | 1            | 310              |

| Shiobara       | Japan                | DFIM | 309                | 1            | 309              |

| Fengning       | China                | DFIM | 300                | 2            | 600              |

| Goldisthal     | Germany              | DFIM | 265                | 2            | 530              |

| Linth-Limmern  | Switzerland          | DFIM | 250                | 4            | 1000             |

| Tehri          | India                | DFIM | 250                | 4            | 1000             |

| Kyogoku        | Japan                | DFIM | 230                | 2            | 460              |

| Avče           | Slovenia             | DFIM | 180                | 1            | 180              |

| Nant de Drance | Switzerland          | DFIM | 150                | 6            | 900              |

| Takami 2       | Japan                | DFIM | 103                | 1            | 103              |

| Hatta          | United Arab Emirates | DFIM | 125                | 2            | 250              |

| Grimsel 2      | Switzerland          | CFSM | 100                | 1            | 100              |

| Galgenbichl    | Austria              | CFSM | 80                 | 2            | 160              |

- Special requirements for DFIM during LVRT thus require the machine to be controlled for some time during the fault. In practice, this means that converter must be oversized to withstand the requirement.

- If an existing PHSP is considered for conversion to DFIM variable speed unit, one must account for additional mechanical requirements imposed by the more complex and heavier rotor.

#### 1.2.2 Converter-fed synchronous machines

Recent advances in power electronics semiconductors and topologies have enabled full-size converter between machine and grid to be considered [13], in what is called CFSM configuration (**Fig. 1.3**). The use of a standard synchronous machine decoupled from the grid through the converter offers considerable benefits compared to DFIM solution.

- Retrofit of an existing fixed-speed PHSP, if available cavern space permits, is possible without replacement of the machine itself.

- Higher rotational speeds can be achieved, thanks to a less complex rotor design.

- Rated torque is available from zero speed.

- · No need for additional pole-reversing installation, as a change in rotating magnetic field

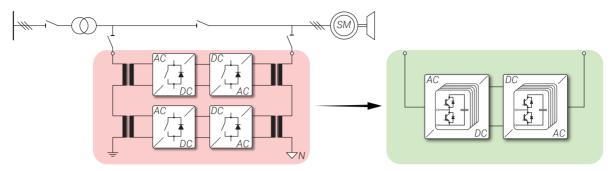

**Fig. 1.4** CFSM layout in Grimsel 2 PHSP, including converter bypass switch for turbine regime and interleaved converters (red); equivalent prospective MMC solution is depicted to the right (green).

direction of the machine can be achieved through appropriate change in converter output voltage references.

- Better short-circuit handling, as converter current limit can be freely parametrized and, for instance, limited to 1 p.u. Plant behavior is not defined by the nature of the machine.

- Considerable reactive power can be delivered to the grid in support of LVRT situations.

- Static Synchronous Compensator (STATCOM) functionality reactive power is supplied from the converter, and available even when the machine is at standstill. In case of new installations, machine can be designed for higher power factor, i.e. more compact size.

#### 1.2.3 Power range of interest

The field of interest of this thesis falls into the large-PHSP power range, as in **Tab. 1.2**. The absolute majority of installed variable speed units in this range of power ratings are DFIM, with only two CFSM unit sets on the list (**Tab. 1.1**). Lower-power CFSM units, of up to 50 MW, for heads up to 250 m and flow rates of 40 m<sup>3</sup>/h, have been proposed as a means of local balancing, to be placed in the vicinity of stochastic RES plants [18]. These power levels can be processed through readily available power electronic converter technologies.

Regarding higher-power-rated converters for CFSM units in the order of 100 MW and up, which can be found in existing PHSP installations, and are the focus of this research, there are only two installations based on CFSM currently in operation. The first is a 100 MW unit installed in Grimsel 2 power plant, located in Switzerland. The plant comprises four 90 MW/13.5 kV ternary machine units [13]. One of the machine sets has been retrofitted with a full size power electronic converter supply. The second represents a new installation in Galgenbichl power plant in Austria. The project comprises two new 80 MW/18 kV machine sets and matching converters [19], [21].

In case of Grimsel 2 retrofit project, where the original machine set has been kept, due to technical limitations in available technology, the required power has been achieved through the parallel operation of two 50 MW back-to-back monolithic multilevel converters, developed by ABB, and based on Integrated Gate-Commutated Thyristors (IGCTs). Currently available semiconductor devices in this power range do not enable both high enough voltage and current levels to match typical machine ratings, implying the use of both grid- and machine-side converter transformers. The converter layout in presented in **Fig. 1.4**. It should be noted that this form of converter stacking produces beneficial multilevel output voltage waveforms. The achieved pumping power range is 60 MW to 100 MW [13].

**Tab. 1.2** Typical synchronous machine ratings in PHSP applications.

| Stator voltage (line-to-line) | $V_{LL} = 6 \text{ kV to } 30 \text{ kV}$  |

|-------------------------------|--------------------------------------------|

| Stator current (RMS)          | $I_{RMS} = 2 \text{ kA to } 8 \text{ kA}$  |

| Apparent power                | $S_n = 80 \text{ MVA to } 400 \text{ MVA}$ |

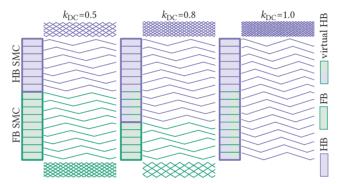

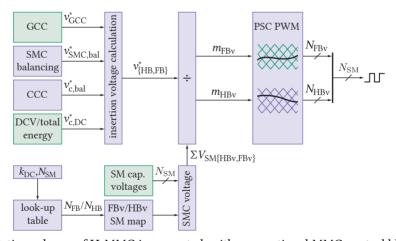

Regarding the Galgenbichl plant project, both new machines and matching converters are delivered. Thus, freedom of machine-converter group optimization is available, which has led to the 30 Hz rated machine frequency design and the world's first use of Direct MMC (D-MMC) in PHSP applications [19], [22]. As it will be shown in the following section, retrofit of existing PHSPs to the variable speed operation is the focus of this thesis, where no freedom in machine design exists. In such applications, where nominal machine- and grid-frequency are equal, Indirect MMC (I-MMC) is preferable over D-MMC [23]. However, due to topology-specific control requirements, Half-Bridge (HB)-based I-MMC imposes prohibitively high Common-Mode (CM)-voltage-stress to the machine, originally designed for sine-wave grid voltage supply. Overcoming this retrofit shortcoming of I-MMC, through PHSP-oriented design and specific control of Hybrid MMC (H-MMC)-based Active Front-End (AFE), comprising a mix of HB and Full-Bridge (FB) Submodules (SMs) in each branch, is the contribution space and the motivation of this work.

#### 1.3 Motivations

#### 1.3.1 Monolithic multilevel converter technology limitations

Voltage levels of 3.3 kV to 6.6 kV line-to-line are at limits of reach for majority of today's Medium Voltage (MV) converters, not considering topologies that require specific transformers and can thus achieve higher voltages, e.g. Robicon Cascaded H-Bridge (CHB) [24]. The rating can be multiplied through series connection of converter units, by means of interleaving transformers as in **Fig. 1.4**. A higher voltage rating can alternatively be achieved by stacking semiconductors within a single converter arm, as in [25]. Further increase in current rating is possible through parallel operation of such units. **Tab. 1.3** provides an overview of maximum ratings for MV monolithic Voltage Source Converters (VSCs), as advertised by some of the major manufacturers [25]–[27].

It should be noted that GE MV7's higher voltage rating is achieved through stacking of eight low voltage Insulated Gate Bipolar Transistor (IGBT) modules. The manufacturer also advertises possibility of up to 300 MW output power through parallel operation of listed units. Similarly, Siemens utilizes three three-level neutral-point-clamped converters in parallel for listed rating.

**Tab. 1.3** Maximum achievable monolithic converters power ratings, as advertised by some of the major manufacturers.

| Manufacturer | Model           | Technology | Voltage           | Power |

|--------------|-----------------|------------|-------------------|-------|

| ABB          | ACS 6000        | 3-L IGCT   | $3.3\mathrm{kV}$  | 36 MW |

| GE           | MV 7            | 5-L IGBT   | $13.8\mathrm{kV}$ | 37 MW |

| Siemens      | SINAMICS SM 150 | 3-L IGCT   | $3.3\mathrm{kV}$  | 30 MW |

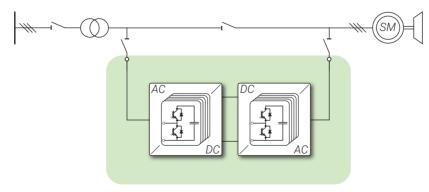

**Fig. 1.5** I-MMC (a) and D-MMC (b) topologies. I-MMC is a preferable choice for retrofit applications, offering arbitrary frequency selection for grid and machine side, output voltage waveform beneficial for old machines without insulation reinforcement for converter operation; half-bridge submodules can be used. D-MMC can be considered for new installations, requiring different grid and machine side frequencies. This topology requires full-bridge submodules, and features single-stage conversion. Converter bypass has not been drawn for simplicity.

The scalability, however, is limited. As in **Fig. 1.4**, each additional series-connected converter requires a set of grid- and machine-side interleaving transformers. In case of limited number of levels, high dv/dt values can be putting extra stress to machine windings' insulation. PHSP units that are candidates for conversion from fixed- to variable speed are based on older synchronous machines designed for grid voltage waveforms. The insulation of these machines, subjected to high dv/dt stresses of VSC output, could age significantly faster and deteriorate. This limitation introduces the need for filtering, which directly translates to additional space, losses and financial requirements, with first two being critical in limited cavern spaces. Looking at the equipment displacement in [28], it can be seen that passive components, i.e. transformers and filters, take up roughly half of the total volume. Limited voltage levels require higher current ratings to achieve desired power levels. This, in turn, leads to problems with handling high short circuit currents in case of converter faults. Issues with harmonic distortions could, depending on power system regulations, require additional filtering on grid side.

#### 1.3.2 MMC perspectives for PHSP

To achieve very high power levels implied by the PHSP application, independently of current semiconductor technology limitations, a topology with better scalability is required. The MMC is a promising alternative to monolithic converters. In scenarios where two Alternating Current (AC) systems are to be interconnected, there are two possible topologies – I-MMC and D-MMC, both depicted in **Fig. 1.5**. Indirect, or back-to-back MMC is well established in point-to-point High Voltage Direct Current (HVDC) bulk energy transmission systems. D-MMC found its use in Static Frequency Converters (SFCs) for railway interties, as an interface between three-phase 50 Hz public grid and single-phase 16.7 Hz railway supply; a reference to a recent  $2 \times 40$  MW unit in Geneva, Switzerland can be found in [29]. In these established applications, MMC is interfacing two grids of fixed frequencies, while in case of PHSP, electric machine side of the installation operates at variable frequency. Variable frequency drive operation of MMC, including Low Frequency (LF) regimes, has been studied. It is shown that MMC driven machine can output significant levels of torque from zero speed onward [30]-[32].

On the other hand, the concept of MMC [33] overcomes voltage scaling limitations through simple stacking of unrestricted number of SMs in converter arms Fig. 1.5. The SMs can be realized as unipolar HB or bipolar FB units, using well-established semiconductor components. This strategy makes PHSP machine voltage levels reachable within a single converter, while dismissing the need for interleaving transformers. The potential use of I-MMC in hydro applications has been firstly discussed to a certain level in [24]. Further, IGCT-based D-MMC for PHSP has been proposed in [23]. The first, and so far the only, application of MMC in PHSP has been realized recently in the Galgenbichl project (Tab. 1.1). In this application, the machine has been designed along with the converter, and eventually rated at 30 Hz for optimization purposes [22]. D-MMC topology used in Galgenbichl project is, however, not a preferable solution when it comes to retrofit applications, where exclusively grid-frequency machines are found, as it will be discussed later [23].

#### 1.4 MMC scaling for PHSP applications

Based on technological constraints in winding insulation and thermal management, synchronous machines currently in operation, and those expected in new installations, could roughly be fitted in the ratings displayed in **Tab. 1.2**. This is the range of interest for the converter design.

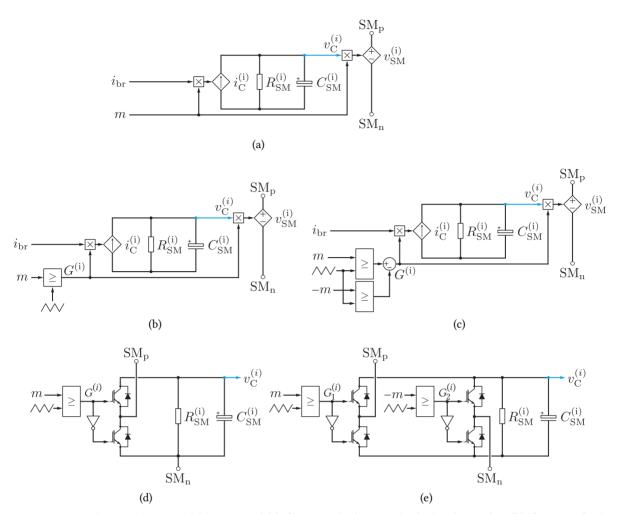

The building block of an MMC is a SM, comprising standard switching elements (IGBT or IGCT) predominantly either in HB or FB configuration, and a capacitor bank. Converter arms are realized as strings of these SMs, making very high voltage levels achievable with available semiconductor technologies.

Multilevel converter scalability depends on the choice of basic building blocks. In very high power applications, it is preferable to design a converter using the so-called Power Electronic Building Blocks (PEBBs), as for instance introduced in [34], [35]. A PEBB comprises power switches, accompanying control, communication and protection circuits, thus making for complete subsystem for easy scaling.

Regarding semiconductor technology at high power levels, the use of "presspack" housing could be beneficial, as in case of component fault, it safely fails to short-circuit state. The converter can continue the operation utilizing redundant SMs, providing high availability. Both IGBT and thyristor-based IGCT presspacks are available for kV voltage levels. While an advantage of IGBT may be higher

**Tab. 1.4** Estimated rated DC link voltage and current, based on ABB proposal [35].

| Cell variant | DC link voltage  | Current rating |

|--------------|------------------|----------------|

| a            | 5.0 kV           | 420 A          |

| b            | $3.6\mathrm{kV}$ | 583 A          |

| c            | $2.5\mathrm{kV}$ | 840 A          |

| d            | $1.8\mathrm{kV}$ | 1167 A         |

attainable switching frequency, IGCT offers superiorly low on-state losses, with a limitation of lower switching frequencies. As can be shown, apparent switching frequency of an HB-based MMC arm, for Phase-Shifted Carrier PWM (PSC-PWM) modulation, equals:

$$f_{\rm sw,app} = N_{\rm SM} \cdot f_{\rm sw} \tag{1.1}$$

where  $N_{\rm SM}$  represents number of SMs per converter arm, and  $f_{\rm sw}$  equals SM switching frequency. While (1.1) holds true for many forms of multilevel converters, an MMC has a considerably higher number of levels  $N_{\rm SM}$ . This means a satisfactory apparent frequency can be achieved with reduced SM level  $f_{\rm sw}$ . Yet, in high-power applications high switching frequencies are prohibitive due to thermal and efficiency constraints, and the use of Optimized Pulse Patterns (OPP) or other fundamental switching methods is more likely [36]. A high-power IGCT-based PEBB has been introduced by ABB in [34], containing two FB-type SMs, of ratings "b" from **Tab. 1.4**, in a single cabinet assembly. Three more alternatives have been given, favoring either higher voltage or higher current capability, while at fixed power rating. Based on data from [34], estimated rated Direct Current (DC) link voltage and current rating of the cells are given in **Tab. 1.4**.

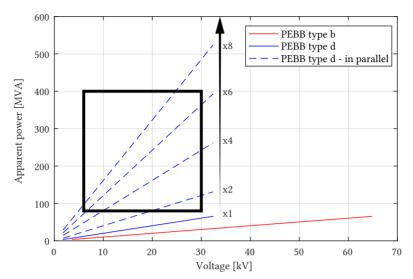

MMC can be scaled up in voltage to meet machine rated voltage by stacking SMs in series, and scaled up in current rating by connecting SMs within a branch or entire branches in parallel. Considering the aforementioned PEBBs, variants b and d can be considered for MMC PHSP application. Ratings "b" were chosen as a solution already implemented by ABB. With voltage being easily scalable in MMC in contrast to the current rating, PEBB type d proves interesting as the modification option with highest current rating. **Fig. 1.6** displays achievable power-voltage range for PEBB b and PEBB d, as well as PHSP range of interest.

Since majority of the area of interest cannot be covered through the use of considered cells, parallel connection has also been investigated [37], [38]. Paralleling PEBBs or branches steepens P(V) curve, bringing MMC solution to the desired application range. It can be noted that PEBB units aiming future PHSP applications should favor higher current ratings, as this enables operation with less PEBBs or converter branches in parallel.

#### 1.4.1 Indirect MMC for PHSP applications

As shown, MMC arm strings can be scaled to real-world PHSP ratings. I-MMC enables use of either HB or FB SMs, with a total of 12 arms due to back-to-back configuration. Due to decentralized energy storage and rather different energy management compared to monolithic VSCs, some limitations are imposed on LF operation of these converters with variable speed drives [30]. It has been shown that I-MMC can be implemented in control of drives with quadratic load, such is a pump, with very little additional control action. However, operation at constant machine torque over the complete

**Fig. 1.6** Achievable power-voltage range of I-MMC using PEBB b, PEBB d and parallel PEBB d building blocks. The square represents PHSP range of interest.

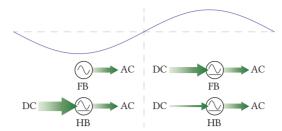

frequency range, which would enable PHSP pumping/turbine changeover without de-watering, is only possible when SM balancing is ensured. This can be performed through additional CM voltage and balancing current injection [30], [31], at the price of high CM voltage stress to the machine and higher converter current requirements. Alternatively, CM-voltage-free operation, beneficial to the old machines designed for sine-wave supply voltage, can be enabled through variable DC link voltage operation, at the expense of utilizing lossier FB SMs within the grid-side converter stage [39]–[41].

#### 1.4.2 Direct MMC for PHSP applications

On the other hand, D-MMC is regarded as suitable for low-speed high-torque applications, owing to output current overload capability in low-frequency range, which can be in range of 200% of nominal. This feature enables high torque to be achieved at low speeds, starting from standstill [42]. In contrast to I-MMC, D-MMC topology requires FB cells to be used, while comprising lower arm count of nine for the whole converter.

#### 1.4.3 Indirect MMC for PHSP retrofit

The above stated makes both converter layouts suitable candidates for PHSP applications. I-MMC is, however, advantageous when it comes to retrofit applications. As opposed to D-MMC, I-MMC is the preferred topology when synchronous machine and grid rated frequencies are equal, which is the case in existing fixed-speed plants [23]. The research work thus focuses on I-MMC solution for PHSP, and in particular on the utilization of H-MMC, comprising a mix of HB and FB SMs within each branch.

The motivation for research work in this domain is to exploit the possibility of qualitative leap in PHSP performance through the implementation of MMC solution. The use of MMC technology is expected to lead towards numerous advantages:

• Increase of PHSP flexibility towards the grid side, to support further integration of RES in

power system.

- Freely scalable, transformer-less and filter-less CFSM PHSP design, as depicted in Fig. 1.4.

- High converter availability through SM redundancy.

- Increase in efficiency of hydraulic side, i.e. better use of storage resources.

#### 1.5 Objectives

Principal research outcomes of the thesis are as follows:

- Development of a novel control methods for H-MMC, minimizing impact on machine insulation. Apart from being the enabling factor for retrofit of existing PHSP units to variable speed operation, this is also beneficial regarding design constraints of machines for new plants.

- Development of a novel design method for H-MMC AFE operated over an arbitrary, down-to-zero, DC link voltage range. The method offers a trade-off between attainable DC link voltage range, power factor and minimal FB SM share.

- Development of a novel design methods of H-MMC for CFSM PHSP applications, enabling a trade-off between grid support capabilities, allowable machine CM-voltage stress and minimization of FB SM share.

#### 1.6 Outline of the thesis

Following *Chapter 1*, the thesis is structured in the following manner.

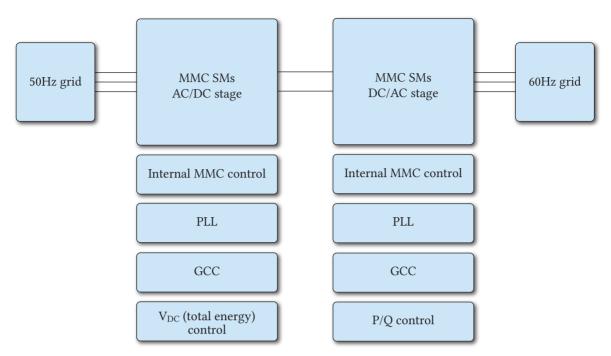

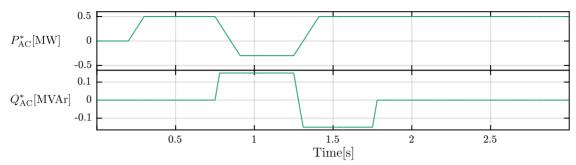

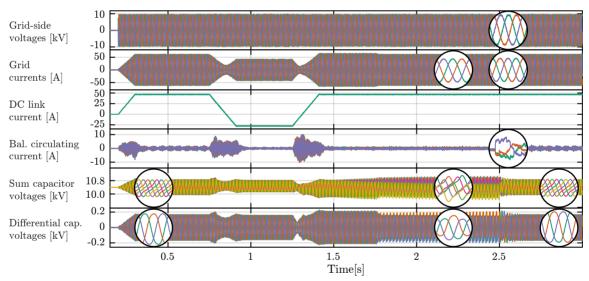

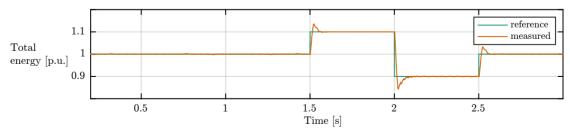

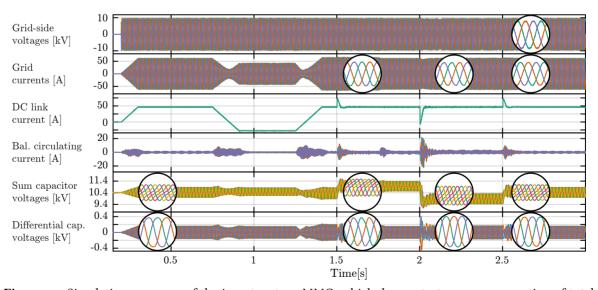

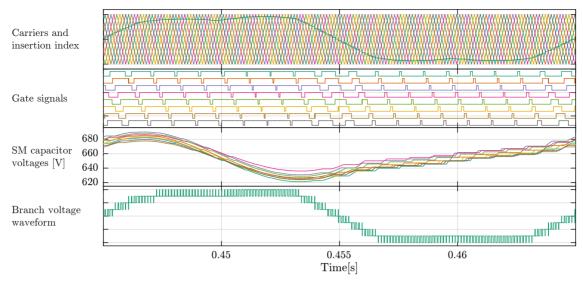

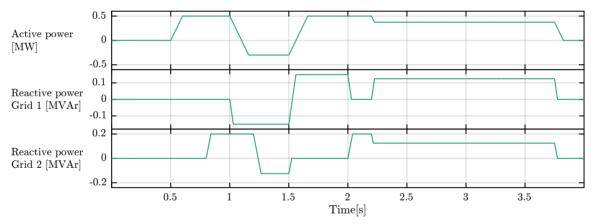

Chapter 2 introduces modeling approach to an individual Direct to Three-Phase (DC/3-AC) MMC. Derivation of governing equations is presented, converter-specific energy balancing methods are implemented, control loops are identified. Based on the results, back-to-back operation of two Three-Phase (3PH) MMCs, forming an I-MMC, is thoroughly analyzed. At this point, the converter operation is analyzed for an intertie application between two fixed AC grids of different fundamental frequencies, namely 50 Hz and 60 Hz. Control actions of individual converters are defined – rectifier MMC controls common DC link voltage, dictating active power exchange with grid 1; inverter MMC controls power exchange with grid 2, to meet the desired *P-Q* profile. This diversification leads to modifications of control loops of the two stages, which is described and implemented. Finally, switched model of an I-MMC is developed in *PLECS* software package.

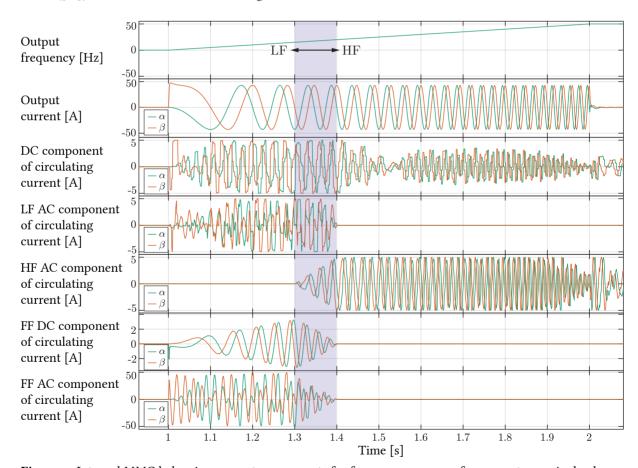

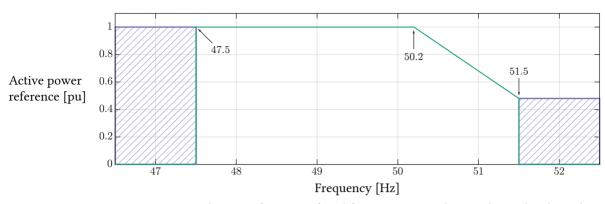

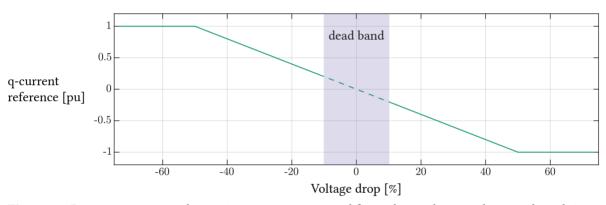

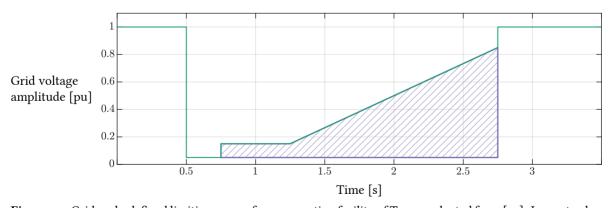

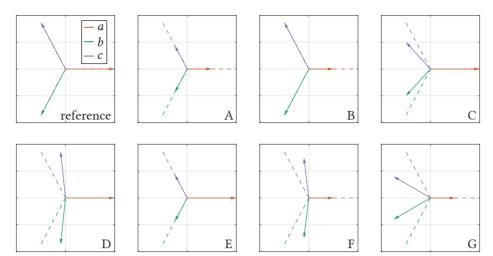

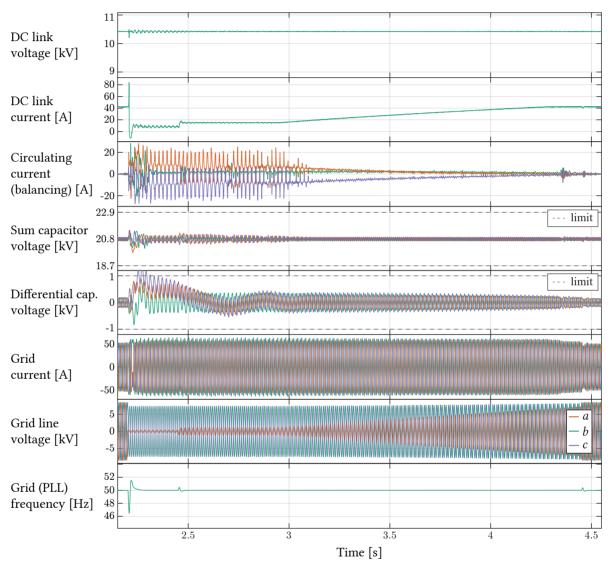

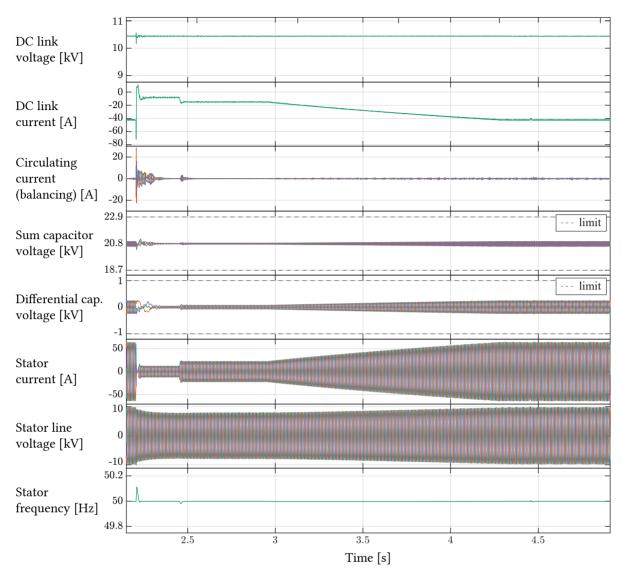

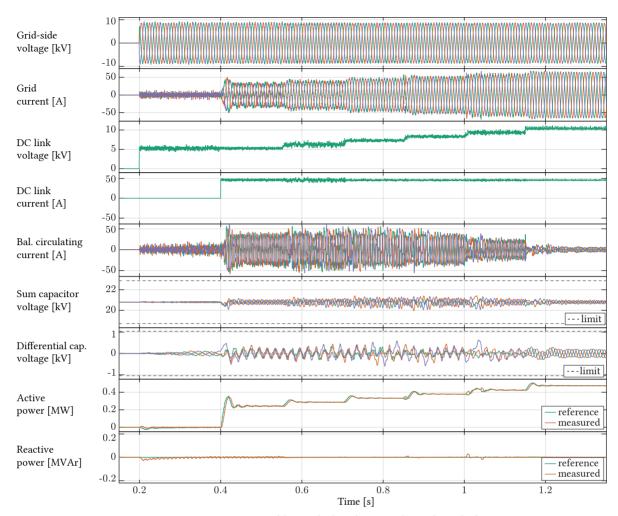

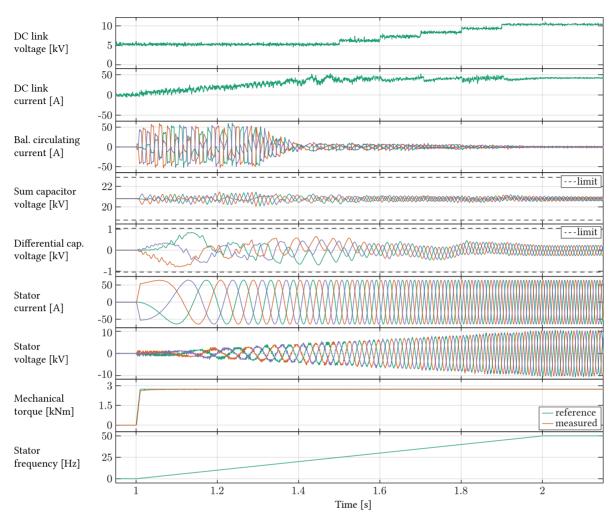

Chapter 3 focuses on synchronous machine modeling, as the next step in analysis of PHSP MMC solution. Machine ratings matching Power Electronics Laboratory (PEL) medium voltage research platform prototype are analyzed. Vector control for CFSM is implemented to inverter MMC stage of the previously developed I-MMC model. Machine operation in the the zero-to-rated frequency region, is investigated. CM-voltage-based machine-side stage energy balancing is implemented, enabling operation at rated torque over the entire frequency range. PHSP-specific operating regimes are tested on the model. Start-stop sequences and operation mode switch-over between pumping and generating are considered. Grid-side control is extended for grid code compatibility. Upon detection of grid voltage or frequency deviation, converter response complies with the grid code requirements. Grid support capabilities of PHSP in such events has been analyzed and supported by in-depth simulation

results. An essential drawback of HB-based MMC in Variable Speed Drive (VSD) retrofit applications is identified: prohibitively high CM voltage machine stress at low-frequency operation.

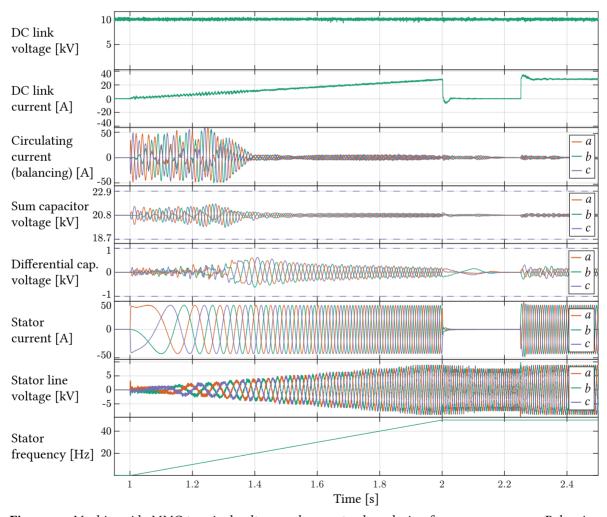

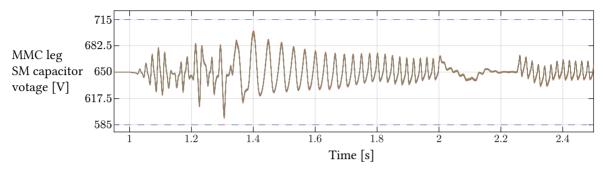

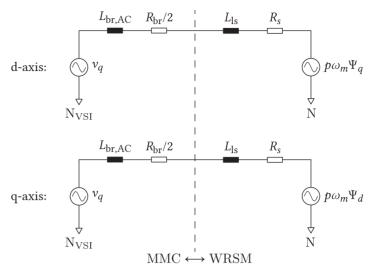

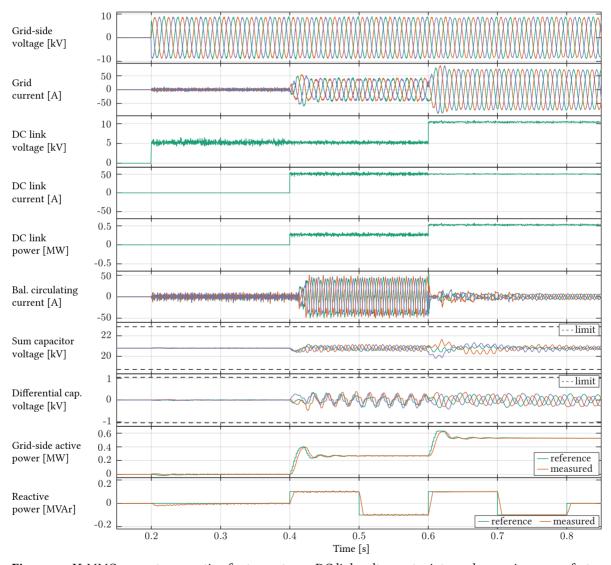

Chapter 4 addresses the nature of MMC SM energy oscillations and their dependence on output frequency, output current and DC link voltage level. It is shown that machine-friendly CM-voltage-free MMC operation over the entire frequency range, and at rated machine torque, can be performed through variable DC link voltage control, without additional balancing control action compared to rated-frequency converter operation. Grid-side stage of the I-MMC is replaced by a FB-based design. DC link voltage control is implemented to allow for the CM-voltage-free operation. Machine start-up operating sequence, pumping/turbine change-over and LVRT sequence are demonstrated. The reference design comprising FB-based AFE stage is the starting point for H-MMC AFE development, leading to reduced CM-voltage machine stress at reduced FB SM share in the AFE converter stage.

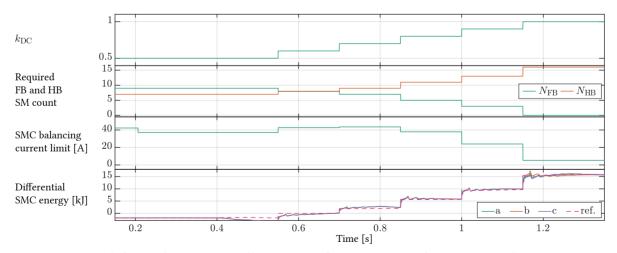

Chapter 5 proposes a reduced CM-voltage-stress operation of PHSP at reduced FB count in the grid-side stage compared to Chapter 4. A novel control and appropriate design approach for H-MMC topology, as a grid-side stage of an I-MMC, enabling operation at variable DC link voltage and arbitrary power factor has been introduced. Insertion voltage sharing between HB and FB SMs is presented. An additional internal energy balancing loop for balancing between HB and FB SM clusters of each branch has been developed. Sizing and operation at typical operating points are compared to equally-rated I-MMC with FB-based grid-side stage of Chapter 4. Performance is compared to other existing H-MMC solutions. Converter design, in terms of required FB share, for arbitrary DC link voltage reduction at unity grid-side power factor, has been presented.

Chapter 6 proposes a novel H-MMC control and design method for further reduction of FB SM share in the grid-side stage of a PHSP I-MMC, while offering CM-voltage-free operation over the entire machine speed range. Starting from branch insertion voltage references, FB and HB insertion voltage sharing and reference alteration has been performed in such a way to ensure inherently balanced converter without additional control actions. An additional, corrective balancing control action is introduced for transient stability. While reduced FB SM share comes at the price of reduced power factor towards the grid at reduced machine speeds, a H-MMC design method for the proposed control approach has been presented, enabling a trade-off between attainable DC link voltage reduction range, available power factor range and minimal FB SM share. Operation limits of the presented control method have been verified. Machine start-up control sequence has been demonstrated.

Chapter 7 summarizes the thesis results and provides an outlook for future work.

#### 1.7 List of publications

Journal papers:

- J1. M. Basić, M. Utvić, and D. Dujić, "Hybrid modular multilevel converter design and control for variable speed pumped hydro storage plants," *IEEE Access*, vol. 9, pp. 140 050–140 065, 2021

- J2. M. Basić and D. Dujić, "Hybrid modular multilevel converter for variable dc link voltage operation," *CPSS Transactions on Power Electronics and Applications*, vol. 6, no. 2, pp. 178–190, 2021

Conference papers:

- C1. M. Basić, A. Schwery, and D. Dujić, "Highly Flexible Indirect Modular Multilevel Converter for High Power Pumped Hydro Storage Plants," in *IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society*, IEEE, Oct. 2020, pp. 5290–5295

- C2. M. Basić, S. Milovanović, and D. Dujić, "Comparison of two Modular Multilevel Converter Internal Energy Balancing Methods," in *2019 20th International Symposium on Power Electronics (Ee)*, IEEE, Oct. 2019, pp. 1–8

- C3. M. Basić, P. C. O. Silva, and D. Dujić, "High Power Electronics Innovation Perspectives for Pumped Storage Power Plants," 2018

## 2

## **Indirect MMC Modeling**

This chapter presents I-MMC modeling approach. Single converter stage dynamics is derived. MMC-specific internal energy balancing controllers are implemented. Higher level grid-side control structures are added, respecting differences in rectifier and inverter stage operation. Individual control loops, as well as back-to-back operation of the I-MMC have been validated.

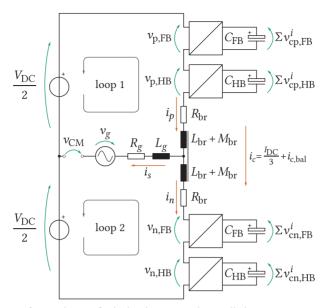

#### 2.1 MMC governing equations

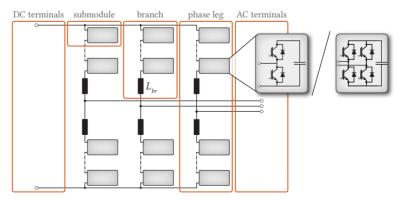

Within the thesis, common MMC nomenclature is used, as depicted in **Fig. 2.1**. Basic building element of the converter is a SM. Each branch comprises a string of  $N_{\rm SM}$  series connected SMs, and a branch inductance, denoted  $L_{\rm br}$ , for protection and branch current control capability. Each of the three phase legs incorporates an upper (positive) and a lower (negative) branch.

Per-phase equivalent circuit of a DC/3-AC MMC, for the purpose of converter dynamics analysis, is displayed in **Fig. 2.2**. MMC branches comprise two-terminal SMs, as previously illustrated in **Fig. 2.1**. Energy storage is distributed, so that each SM comprises capacitor bank of  $C_{\rm SM}$ . As there is no external fixed voltage power supply to individual SMs, number of levels can be freely chosen and scaled to application. Consequently, however, capacitor voltage levels are not defined, but rather floating. To ensure equal voltage distribution among SMs and proper operation of the converter, level of charge, i.e. energy, of each  $C_{\rm SM}$  has to be controlled.

Individual SMs' capacitor voltage levels are denoted  $v_{cpx}^i$  and  $v_{cnx}^i$  for positive and negative branches, respectively, where x denotes phase and i index of the SM within the branch string. For simplicity, the entire string of branch SMs is presented through an equivalent capacitance  $C_{br} = C_{SM}/N_{SM}$ , charged

**Fig. 2.1** Basic structure and nomenclature of a DC/3-AC MMC.

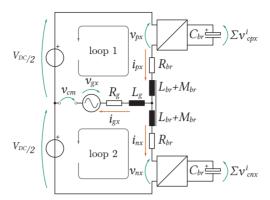

Fig. 2.2 Equivalent circuit of one phase leg of MMC.

to the sum of all capacitor voltages within the branch. If SM capacitor voltages are measured, it is straight-forward to determine modulation index of each branch for required instantaneous output voltage [43]. In MMC, modulation index is referred to as *insertion index*, as it essentially determines which portion of available distributed capacitor voltage is to be "inserted" in branch circuit. There are various switching strategies developed to achieve this; to reveal converter controllability, one can neglect switching behavior of SMs and assume branch-level voltage at terminals of the equivalent SM,  $v_{\text{fp,n}}$ , is equal to insertion index portion of total available capacitor voltage:

$$v_{\{p,n\}x} = m_{\{p,n\}x} \cdot \sum_{i=1}^{N} v_{c\{p,n\}x}^{i}$$

(2.1)

where  $m_{\{p,n\}} \in [0,1]$  denotes SM insertion index. In case SM-level switching action is taken into consideration, instantaneous voltage  $v_{\{p,n\}_X}$  is defined as:

$$v_{\{p,n\}x} = \sum_{i=1}^{N} \left( s_{\{p,n\}x}^{i} \cdot v_{c\{p,n\}x}^{i} \right)$$

(2.2)

where  $s_{\{p,n\}_X}^i$  is a binary insertion function, that determines state of switches for each of the SMs.

Branch inductors are coupled with a factor  $k_{\rm br}$ , mutual inductance being defined as  $M_{br} = k_{br}L_{br}$ . Converter losses are modeled through branch resistances  $R_{\rm br}$ . In this case, grid is modeled as star-connected 3PH voltage source behind impedance. Grid impedance is represented by  $R_{\rm g}$  and  $L_{\rm g}$ , grid-side voltage by  $v_{\rm g}$  and CM voltage component by  $v_{\rm CM}$ .

Grid currents are defined through upper and lower branch currents as:

$$i_{gx} = i_{px} - i_{nx} \tag{2.3}$$

Kirchhoff's voltage law (KVL) equations can be written from two loops in Fig. 2.2:

$$\frac{V_{dc}}{2} = v_{CM} + v_{gx} + v_{px} + R_g \left( i_{px} - i_{nx} \right) + L_g \frac{d \left( i_{px} - i_{nx} \right)}{dt} + L_{br} \frac{d i_{px}}{dt} - M_{br} \frac{d i_{nx}}{dt} + R_{br} i_{px}$$

(2.4)

$$\frac{V_{dc}}{2} = -v_{CM} - v_{gx} + v_{nx} - R_g \left( i_{px} - i_{nx} \right) - L_g \frac{d \left( i_{px} - i_{nx} \right)}{dt} + L_{br} \frac{d i_{nx}}{dt} - M_{br} \frac{d i_{px}}{dt} + R_{br} i_{nx}$$

(2.5)

Further addition and subtraction of (2.4) and (2.5) leads to:

$$V_{dc} = v_{px} + v_{nx} + (L_{br} - M_{br}) \frac{d(i_{px} + i_{nx})}{dt} + R_{br}(i_{px} + i_{nx})$$

(2.6)

$$0 = v_{px} - v_{nx} + 2v_{CM} + 2v_g + \left(L_{br} + M_{br} + 2L_g\right) \frac{d(i_{px} - i_{nx})}{dt} + \left(2R_g + R_{br}\right)(i_{px} - i_{nx})$$

(2.7)

If we define the following quantities:

$$v_{cx} = \frac{v_{nx} + v_{px}}{2}$$

total inserted leg voltage (2.8)

$$v_{sx} = \frac{v_{nx} - v_{px}}{2}$$

differential phase-leg voltage (2.9)

$$i_{cx} = \frac{i_{px} + i_{nx}}{2}$$

circulating current (2.10)

$$i_{\{p,n\}x} = i_{cx} \pm \frac{i_{gx}}{2}$$

positive- and negative-branch currents (2.11)

Equations (2.6) and (2.7) can be rewritten as:

$$V_{dc} - v_{cx} = 2\left(L_{br} - M_{br}\right) \frac{di_c}{dt} + 2R_{br}i_c$$

(2.12)

$$v_{sx} - v_{gx} - v_{CM} = \left(L_g + \frac{L_{br} + M_{br}}{2}\right) \frac{di_{gx}}{dt} + \left(R_g + \frac{R_{br}}{2}\right) i_{gx}$$

(2.13)

By observing (2.12) and (2.13), it can be seen that grid current  $i_g$  and MMC-specific circulating current  $i_c$  are controllable through  $v_s$  and  $v_c$ , respectively. Power at which the energy is exchanged through AC and DC terminals can thus be independently controlled. Another conclusion is that freedom in design of branch inductors, more specifically freedom in choice of coupling coefficient  $k_{\rm br}$ , means either grid- or circulating current filtering can be preferred:

$$k_{br}$$

$\begin{cases} > 0 & i_g \text{ filtering preferred} \\ < 0 & i_c \text{ filtering preferred} \end{cases}$

In PHSP applications, with grid-code requirements on one AC side and synchronous machine stress on the other, filtering of AC-side current  $i_g$  is preferred. Thus, positive coupling coefficient has been chosen.

As aforementioned, MMC structure requires control of energy distribution among the SMs' capacitor banks, i.e. energy balancing. Capacitor dynamics is determined by the rate of charge or discharge. In case of an averaged model, being on the SM level and starting from (2.1), the following is true:

$$C_{\text{SM}} \frac{dv_{c\{p,n\}x}^{i}}{dt} = m_{\{p,n\}x} i_{\{p,n\}x}$$

(2.14)

Different modulation techniques can be applied, resulting in different energy balancing of SMs within a converter branch. At the higher level, capacitor voltage dynamics and energy distribution between upper and lower branches within a phase-leg, as well as between phase-legs, can be observed in

the same fashion, regardless of modulation approach and, consequently, insertion index calculation strategy. Starting from (2.14), capacitor voltage dynamics at branch level is determined:

$$v_{c\Sigma\{p,n\}x} = \sum_{i}^{N_{SM}} v_{c\{p,n\}x}^{i}$$

(2.15)

$$C_{\text{br}} \frac{dv_{c\Sigma\{p,n\}x}}{dt} = m_{\{p,n\}x} i_{\{p,n\}x}$$

(2.16)

which leads to sum (2.17) and differential (2.18) phase-leg voltage values:

$$v_{c\Sigma\Sigma x} = v_{c\Sigma px} + v_{c\Sigma nx} \tag{2.17}$$

$$v_{c\Sigma\Delta x} = \frac{v_{c\Sigma nx} - v_{c\Sigma px}}{2} \tag{2.18}$$

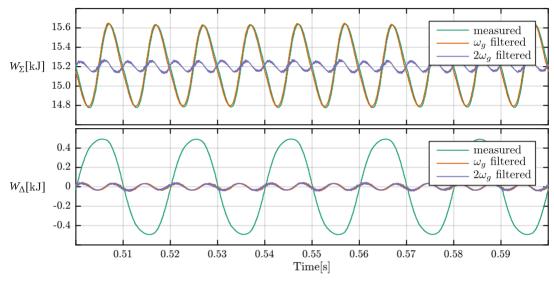

The aim of branch-level energy controller is to manage energy distribution among MMC branches. It is achieved by equalizing sum voltage levels of all three phases (2.17), at the same time driving differential voltage levels of upper and lower phase-leg's branches to zero (2.18).

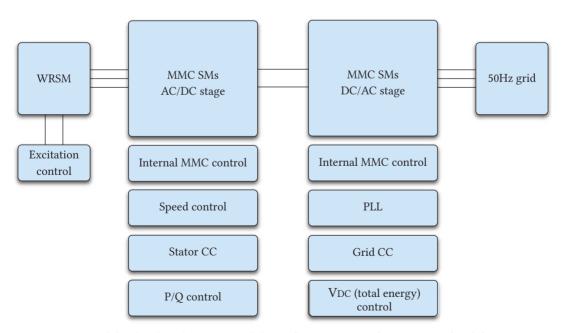

# 2.2 Converter control outline

I-MMC model has been developed, as presented in **Fig. 2.3**. Looking at a single conversion stage, one can diversify:

- MMC SMs power stage and appropriate voltage and current measurements

- *Internal MMC control* topology-specific control loops:

- Energy balancing: control of horizontal and vertical energy distribution among SMs, and of total energy stored in the converter

- Circulating current control used for energy balancing actions

- Individual SM insertion commands

- *Higher-level control* structures, used regardless of the selected topology:

- Phase-Locked Loop (PLL) for synchronization with the grid

- Grid Current Control (GCC) to achieve desired power of energy exchange towards the grid

- DC link voltage control, indirectly through total energy control, handled by the rectifier stage

- *P/Q* control towards the 60 Hz grid, handled by the inverter stage

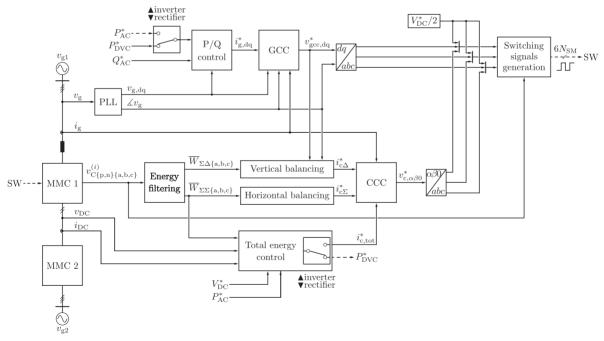

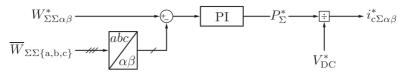

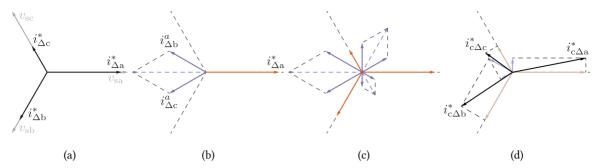

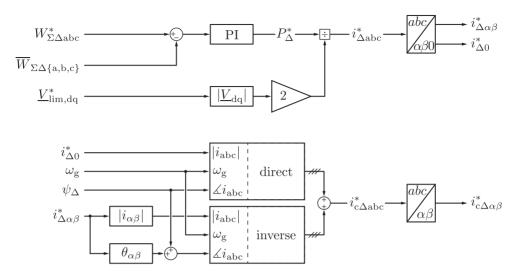

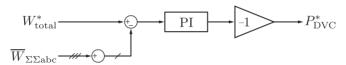

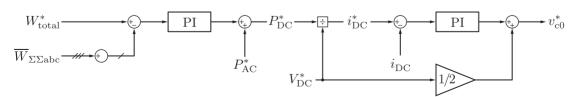

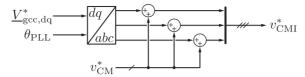

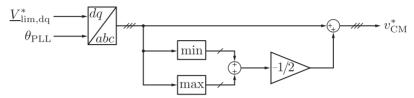

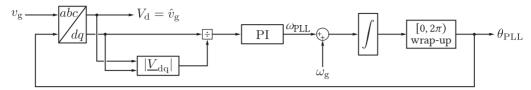

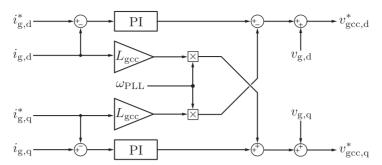

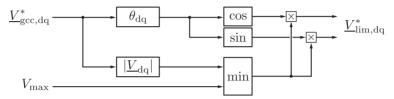

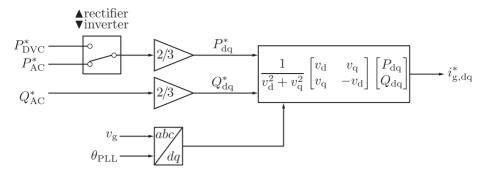

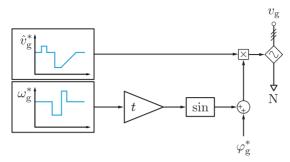

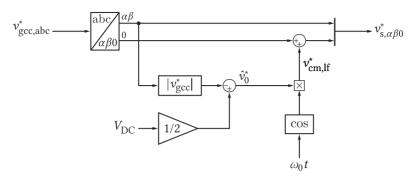

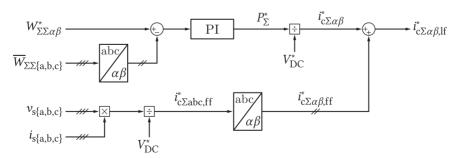

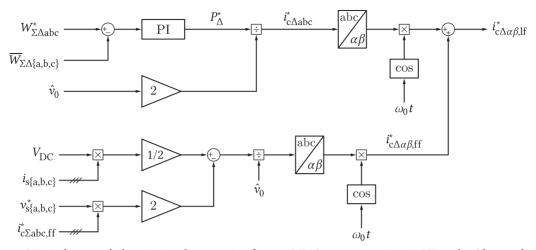

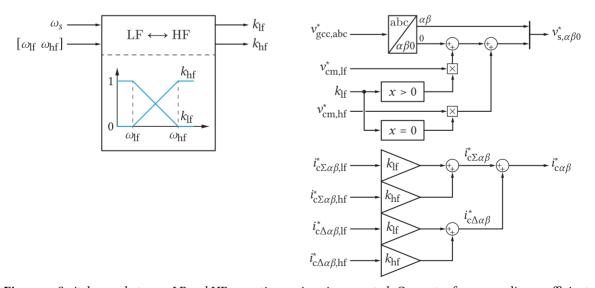

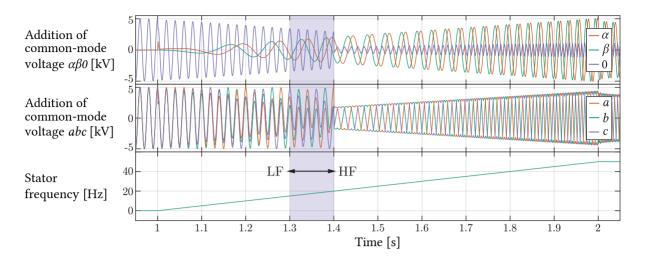

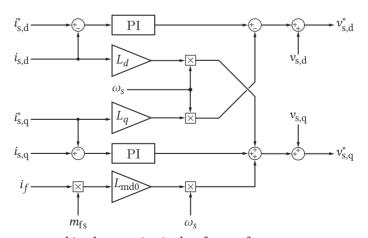

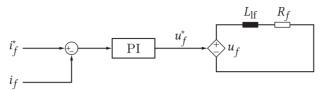

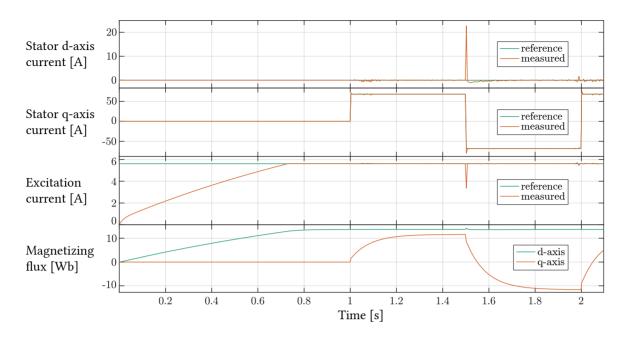

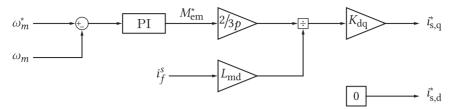

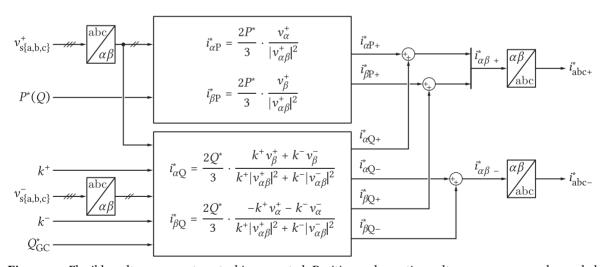

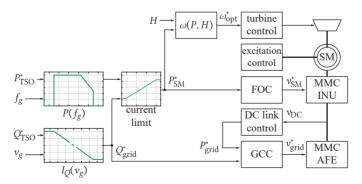

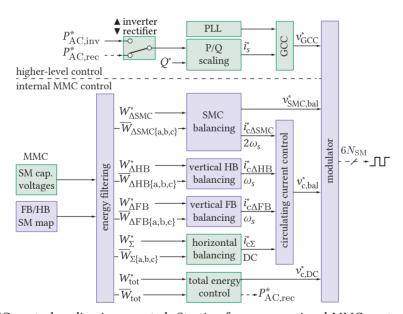

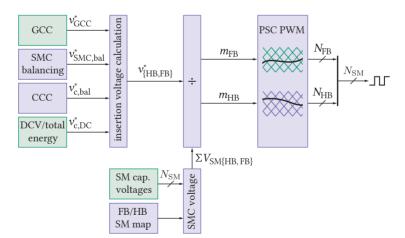

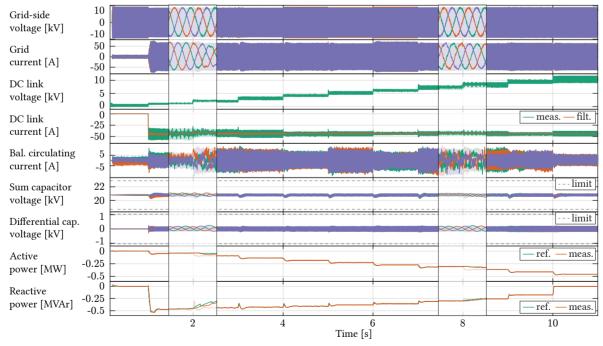

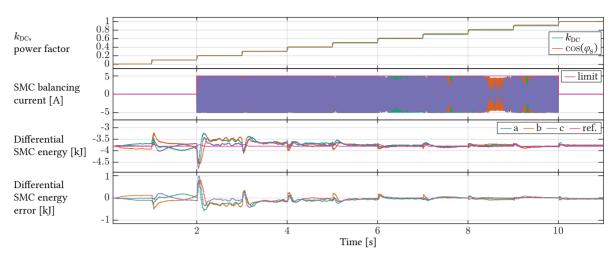

Converter control structure is shown in more detail in **Fig. 2.4**. Apart from well-known higher level control blocks, topology-specific energy balancing structures can be identified. The differences in realization of certain control blocks for rectifier and inverter stages are stressed in the figure, and explained further within the chapter.

**Fig. 2.3** Overview of the developed I-MMC model, interfacing two AC grids of different frequencies. Rectifier and inverter stages are connected to 50 Hz and 60 Hz grids, respectively.

**Fig. 2.4** DC/3-AC MMC control structure is presented, including the most important signals. Difference between rectifier and inverter MMC application can be seen in the way total energy is controlled, output voltages generated, and power references calculated. Reference values are marked by an asterisk. The following sections describe each block in detail.

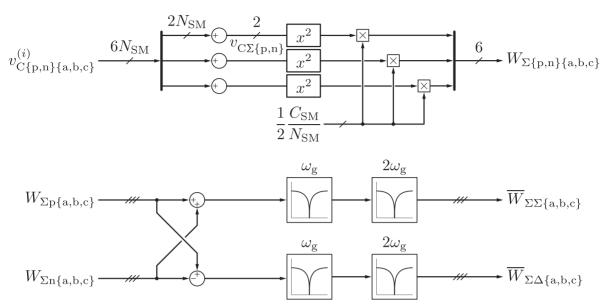

# 2.3 Internal MMC control

Distributed energy storage, the enabling element of MMC scalability and redundancy, requires special attention from control perspective. Converter branches are realized as strings of two-terminal SMs, with each SM acting as a voltage source. Voltage amplitude is naturally not fixed but rather determined by the state of charge of SM's capacitor bank,  $C_{\rm SM}$ . Thus, equal average voltage level of each SM capacitor bank within the MMC must be ensured, regardless of the slight differences in actual SM capacitances due to manufacturing tolerances, or unequal loading due to transient operating events. Utilizing three sets of branch-level controllers, and one SM-level controller, energy storage can be balanced:

- Total level of stored energy in MMC corresponds to nominal charge of all SMs

- Horizontal all three phase-legs store equal amounts of energies

- Vertical within each phase-leg, upper and lower arm evenly share energy storage

- Local SM equal capacitor voltage level for each SM within a converter branch

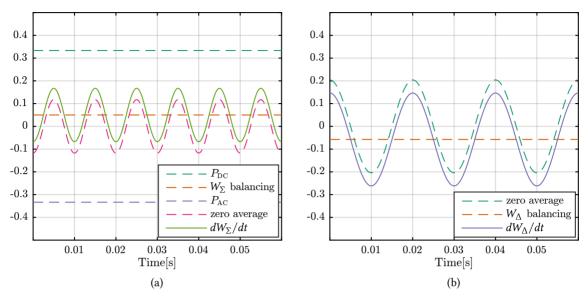

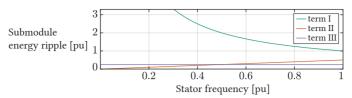

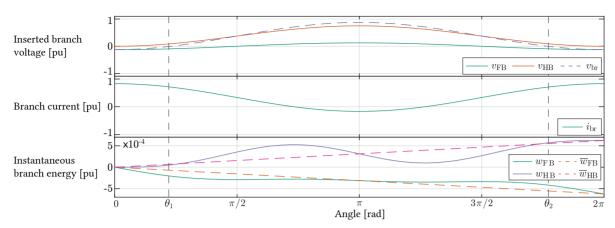

## 2.3.1 Branch-level energy ripple dynamics

Expanding (2.16) with (2.11), the following is obtained:

$$C_{br}\frac{dv_{c\Sigma px}}{dt} = m_{px}\left(i_{cx} + \frac{i_{gx}}{2}\right) \tag{2.19}$$

$$C_{br}\frac{dv_{c\Sigma nx}}{dt} = m_{nx}\left(i_{cx} - \frac{i_{gx}}{2}\right) \tag{2.20}$$

where ideal insertion indexes can be defined from (2.8) and (2.9):

$$v_{cx} = \frac{m_{px}v_{c\Sigma px} + m_{nx}v_{c\Sigma nx}}{2} \tag{2.21}$$

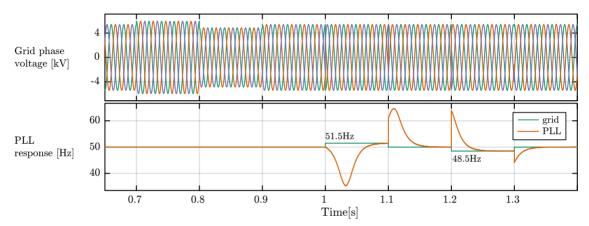

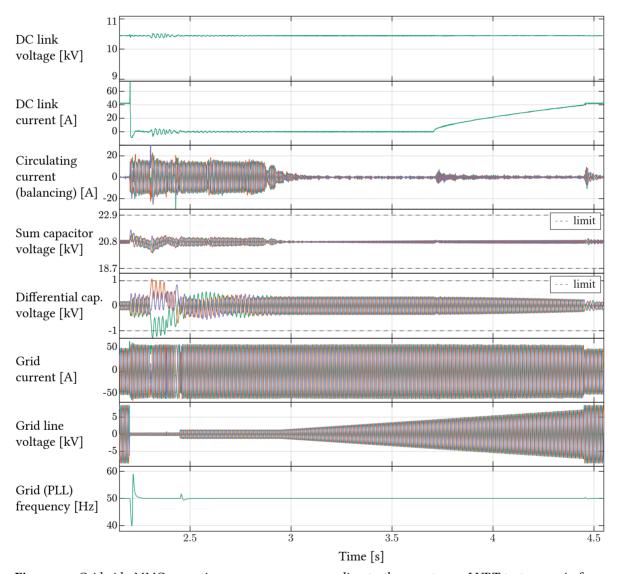

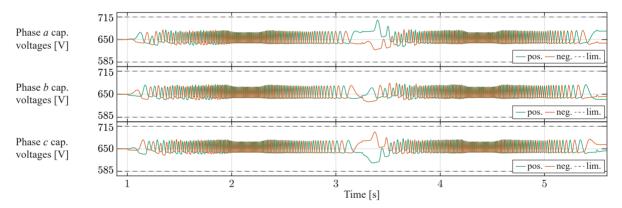

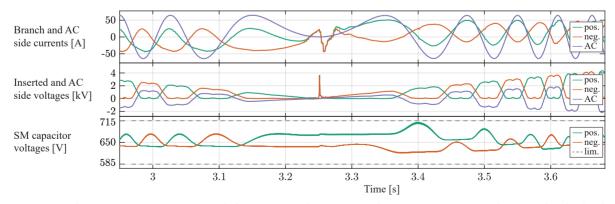

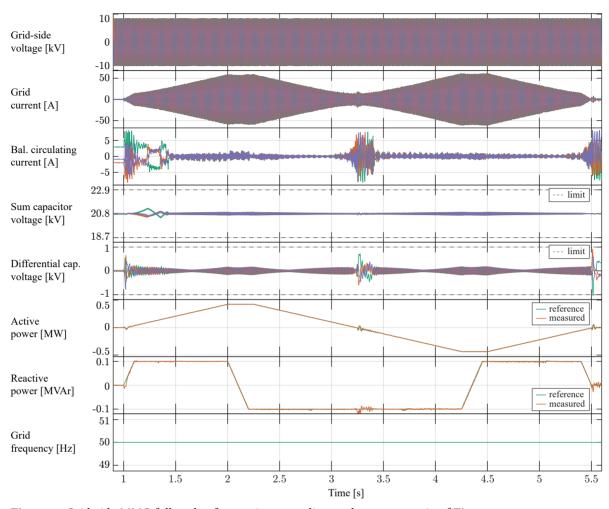

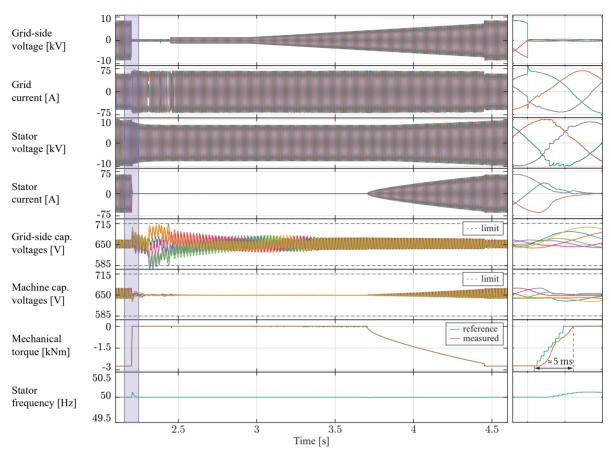

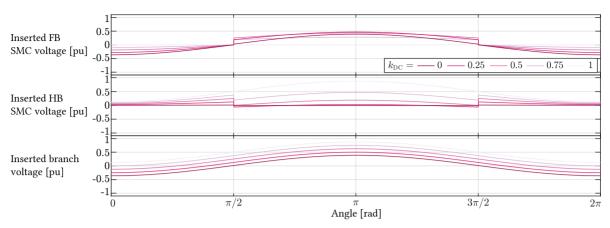

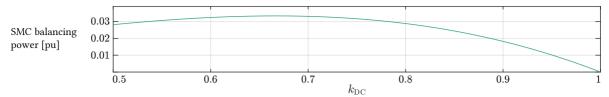

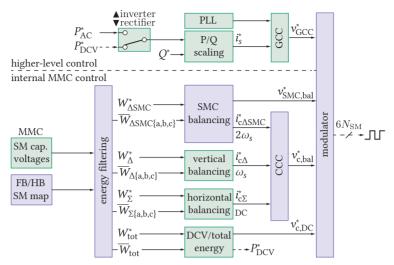

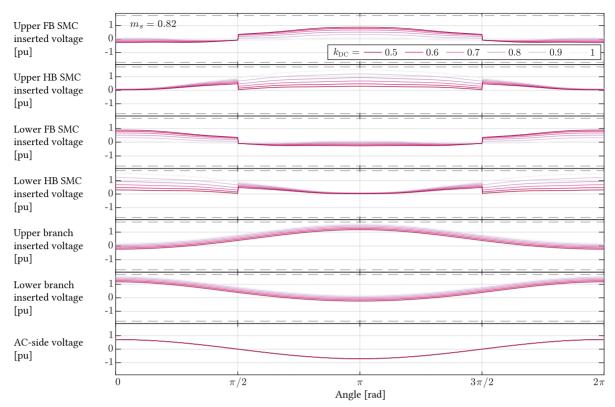

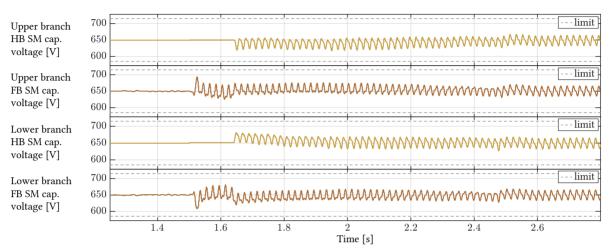

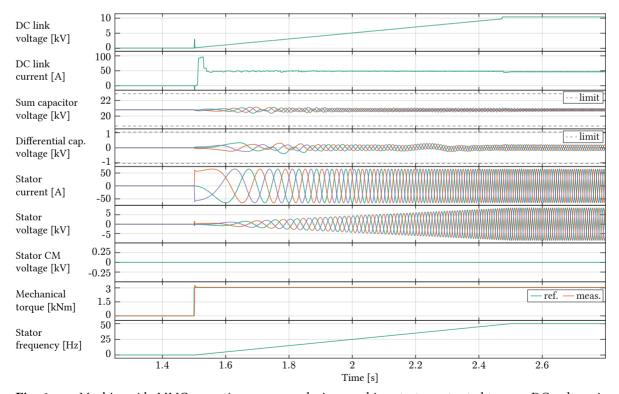

$$v_{sx} = \frac{-m_{px}v_{c\Sigma px} + m_{nx}v_{c\Sigma nx}}{2} \tag{2.22}$$