Thèse n° 9042

# EPFL

### Hard and Soft Switching Losses in Power Converters: Role of Transistor Output Capacitance

Présentée le 28 mars 2022

Faculté des sciences et techniques de l'ingénieur Laboratoire de dispositifs semiconducteurs de puissance Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### Palliyage Srilak Nirmana PERERA

Acceptée sur proposition du jury

Prof. F. Rachidi-Haeri, président du jury Prof. E. D. N. Matioli, directeur de thèse Prof. M. Kazimierczuk, rapporteur Dr T. Wijekoon, rapporteur Prof. D. Dujic, rapporteur

École polytechnique fédérale de Lausanne

2022

Truth is the daughter of time.

To my mother...

## Acknowledgements

My journey towards getting a PhD degree has not been an easy task. It has been challenging, both mentally and physically. The five years at EPFL has taught me that the journey, ultimately, is a test of your willpower and the support you get along the way, nothing else.

First, I would like to thank my thesis supervisor, Professor Elison Matioli, for giving me the opportunity to carry out my doctoral studies at EPFL and putting his trust in me. Thank you for your support and guidance throughout my studies. I'm grateful to the jury members of my doctoral examination for their time in assessing my doctoral work, and their valuable insights and recommendations. The appreciation I received for my thesis from you is very important to me, and I regard it very highly. I thank the president of the jury, Professor Farhad Rachidi-Haeri from EPFL, the external experts Professor Marian Kazimierczuk from Wright State University, Ohio, U.S.A, and Dr Thiwanka Wijekoon from Huawei Technologies, Germany, and the internal expert Professor Drazen Dujic. I'm thankful to EPFL for supporting me throughout my studies and financing my research work. I also thank the Swiss Office of Energy (SFOE) for providing important financial support for my research work as well as for the betterment of our research lab.

Muriel, I'm deeply indebted to you for all the support you gave me during my initial settlement in Switzerland; and your support did not stop there. You helped me with matters even outside of EPFL till the very end. I thank all the Powerlab members for their support during various stages of my studies.

I must mention a few additional words about the jury members of my doctoral examination. I'm grateful to Professor Drazen Dujic for his support during my stay at EPFL. Every time I had a question, whether technical or about my career, you were very quick to meet with me and provide guidance. I'm also lucky to get to know Professor Farhad Rachidi-Haeri. Not only you were the president of my doctoral examination but you also helped me with several technical questions I had during my third year of studies. Prof. Kazimierczuk, I'm grateful to you for the detailed comments and corrections on my thesis; they helped me to improve my thesis before its final publication. And Dr Wijekoon, thank you for the encouragement and all the advice.

I'm also grateful to Professor Mario Paolone for being the president of my candidacy exam as well as for his wonderful and cheerful engagement as the advisor of the EPFL hyperloop team.

I'm thankful to Dr André Hodder, Sylvain Robert, and Dr Stéphane Burri for their kind technical advice and support during various stages of my studies. I especially thank Pietro Bianco for his invaluable technical support. Pietro, your level of service and kindness are such a rarity. I would also like to thank my students Jessy Ançay, Linda Ösmon, Nicolas Bollier, Enea Figini, Bruno Kola, and Simon Aquarone. Thank you all for giving me a chance to work on my teaching and supervising skills.

I'm forever grateful to my colleague and friend Georgios Kampitsis. You helped me through a

### Acknowledgements

very challenging time when I was doubting myself. You believed in me and your moral support was instrumental to pass those hurdles. The same goes for my friend Armin Jafari. Your company was invaluable to me to get through the final stages of my PhD. I would also like to thank my friends Giovani and Ilaria for all the good times we had together and for always getting us exceptionally good food. Luca, thank you for all the technical and non-technical discussions we had together. I'm also thankful to Remco, Katya, and Jun for their cheerful support during various stages of my work.

One of the best things that happened to me during my stay at EPFL was being part of the EPFL Hyperloop team (2017–2018). I will never forget the time we spent together, both in Lausanne and Los Angeles. I would like to thank the whole team, with special thanks to Simone, Milena, Linda, and João. Simone, whenever I needed help, you were there; your friendship made my life in Switzerland much easier. Milena, thank you for being a really good friend and helping me to preserve my sanity. Linda and João, thank you for all the good memories and your support.

I would also like to acknowledge my lifelong friends Kasun, Hiranya, and Amali. Your constant communication, although you live in three different countries, has helped me more than you can imagine. I'm grateful to my good friends Kamalaruban Parameswaran and Nuwan Liyanage for their continuous support and advice, especially during the final year of my studies.

I'm also grateful to my first power electronics teacher Professor Sunil Abeyratne and my second power electronics teacher Professor John Salmon.

Finally, I would like to thank my mother, my father, my sister, and my brother-in-law. I cannot thank you enough for everything you have done for me.

Lausanne, 21.03.2022

Nirmana Perera

## Preface

Since the industrial revolution, a myriad of machines were invented, commercialized, and then used to do one task, which can be put under the following umbrella ideology: the betterment of human society and creation of solutions that make everyday life easier. Electric power, and consequently, modern-day power processing has been an integral part of this ideology, shaping the technical advancements in many fields.

At the time of writing this thesis (the year 2022), the world has faced a far bigger challenge than this ideology. The EU-wide existing ambition for 'The 2030 climate and energy framework' is the following [1] (verbatim from the source):

- At least 40% cuts in greenhouse gas emissions (from 1990 levels)

- · At least 32% share for renewable energy

- At least 32.5% improvement in energy efficiency

To make this a reality, power processing now has a very timely task ahead. Consequently, *power electronic converters* need to see a significant increase in their performance within a very short amount of time.

This thesis work was not initially undertaken with this as an ideology. The work was undertaken purely on its scientific merit. But I hope it aids, in some way, to achieve this important goal as the thesis presents important insights on the energy losses in power converters.

Nirmana Perera,

Lausanne, Switzerland.

(March 2022)

## Abstract

### Hard and Soft Switching Losses in Power Converters:

### **Role of Transistor Output Capacitance**

by

Nirmana Perera

To best utilize power converters, a sound understanding of the relationship between the circuit topology and the power-semiconductor-device characteristics is required. This is especially important in high-frequency switching, where device parasitics start to largely interfere with the circuit. In this regard, the parasitic-output-capacitance of power devices plays a vital role in the losses of the system, which affect both the efficiency of the circuit and the system volume. This thesis studies the characterization of output capacitance as well as its interaction with power electronic topologies at a fundamental level and presents important insights, underlining limitations in the conventional knowledge on the subject.

The thesis shows that the analysis of output-capacitance-related losses should be treated based on the type of switching employed, as the circuit-level effect of the output capacitance is different in soft- and hard-switching topologies. For both cases, it is highlighted that the charge-versus-voltage curve of device output capacitance provides the most complete information of its behaviour. First, the correct measurement methods to identify output capacitance losses for soft-switching operations are analysed and validated. Then, it is shown how a fundamentally different charge–discharge mechanism in device output capacitance takes place in hard-switching operation (in contrast to soft-switching), and a new measurement approach is devised to quantify the related loss. These measurement methods are then used to evaluate output-capacitance losses of commercially available Si, SiC, and GaN power transistors. The developed concepts are taken a step further and utilized to separately evaluate gateand driver-related losses in driving a transistor undergoing zero-voltage-switching. The technique is then used to identify the performance limitations of HF and VHF gate-driver ICs. Finally, consolidating the ideas developed throughout the thesis, an experimental case study is provided for a soft-switching converter.

We conclude that output capacitance is a critical device feature that should be considered in high-frequency converter design and be given the same level of attention as device on-resistance in the design stage of a device. We believe this is instrumental to the progress of modern power converters—especially, ones based on emerging wide-bandgap devices—towards their fullest potential.

**Keywords:** calorimetry, charging, class-E inverter, co-energy, discharging, energy loss, electrical measurements, gallium nitride (GaN), gate driving, gate loss, hard switching, hysteresis, no-load circuit, no-load loss, output capacitance, silicon (Si), silicon carbide (SiC), soft switching, power converters, power loss, resonant converters, switching, switching energy, switching loss, wide-bandgap (WBG) devices.

## Résumé

### Pertes de commutation dure et douce dans les convertisseurs de puissance:

### Rôle de la capacité de sortie du transistor

par

Nirmana Perera

Afin de mieux utiliser les convertisseurs de puissance, une compréhension approfondie de la relation entre la topologie du circuit et les caractéristiques de composant à semi-conducteur de puissance est nécessaire. Celle-ci est particulièrement pertinente dans les cas de commutation à haute fréquence, où les effets parasites provenant du composant commencent à interférer de manière conséquente avec le circuit. A cet égard, la capacité de sortie parasite des composants de puissance joue un rôle crucial dans les pertes du système, en affectant à la fois l'efficacité et le volume du circuit. Cette thèse étudie la caractérisation de la capacité de sortie aussi bien que son interaction avec les topologies d'électronique de puissance à un niveau fondamental et présente des informations importantes mettant en avant les limites des connaissances conventionnelles sur le sujet.

Cette étude montre que l'analyse des pertes liées à la capacité de sortie doit être traitée en fonction du type de commutation utilisé, car l'effet de la capacité de sortir au niveau du circuit est différent dans les topologies à commutation douce et dure. Dans les deux cas, il est mis en évidence que la courbe charge-tension de la capacité de sortie du composant fournit les informations les plus complètes sur son comportement. Tout d'abord, les méthodes de mesure correctes pour identifier les pertes de capacité de sortie pour les opérations de commutation douce sont analysées et validées. Ensuite, il est montré comment un mécanisme de charge-décharge fondamentalement différent dans la capacité de sortie du composant se présente lors d'une opération de commutation dure (contrairement à la commutation douce), et une nouvelle approche de mesure est conçue pour quantifier la perte associée. Ces méthodes de mesure sont ensuite utilisées pour évaluer les pertes de capacité de sortie des transistors de puissance Si, SiC et GaN disponibles dans le commerce. Les concepts développés sont ensuite approfondis et utilisés pour évaluer séparément les pertes liées à la grille et au driver lors du fonctionnement d'un transistor subissant une commutation à tension nulle. La technique est également utilisée pour identifier les limitations de performances des circuits intégrés de driver pour la grille à HF et VHF. Enfin, consolidant les idées développées tout au long de la thèse, une étude de cas expérimentale est fournie pour un convertisseur à commutation douce.

Nous concluons que la capacité de sortie est une caractéristique essentielle du composant qui doit être prise en compte dans la conception du convertisseur de haute fréquence et doit recevoir le même niveau d'attention que la résistance à l'état passant du composant lors de la phase de conception. Nous pensons que cela joue un rôle déterminant dans la progression des convertisseurs de puissance modernes, en particulier ceux basés sur des composants émergents à large bande interdite, vers leur plein potentiel.

## Contents

| Ac | knov  | wledge | ments                                                 | i   |

|----|-------|--------|-------------------------------------------------------|-----|

| Pr | eface | e      |                                                       | iii |

| Ał | ostra | ct     |                                                       | v   |

| I  | PA    | RT 1   |                                                       | 1   |

| 1  | Intr  | oducti | on                                                    | 3   |

|    | 1.1   | New (  | Challenges in Power Conversion                        | 3   |

|    | 1.2   | Power  | r Electronic Circuits and Power Semiconductor Devices | 4   |

|    | 1.3   | Motiv  | ations                                                | 7   |

|    | 1.4   | Thesi  | s Contributions                                       | 9   |

|    | 1.5   | Thesi  | s Organization                                        | 10  |

| 2  | The   | matic  | Overview: Output Capacitance, Charge, and Energy      | 11  |

|    | 2.1   | Basic  | Concepts and Terminology                              | 11  |

|    |       | 2.1.1  | Device Parasitic Capacitances                         | 11  |

|    |       | 2.1.2  | Input, Output, and Reverse-Transfer Capacitances      | 12  |

|    |       | 2.1.3  | Output Capacitance and CV Curves                      | 13  |

|    |       | 2.1.4  | Output Charge and QV Curves                           | 13  |

|    |       | 2.1.5  | Drain–Source Voltage                                  | 13  |

|    |       | 2.1.6  | Stored Energy and co-Energy                           | 14  |

|    |       | 2.1.7  | Hysteresis Energy Loss                                | 15  |

|    | 2.2   |        | - versus Large-Signal Excitation                      | 15  |

|    |       | 2.2.1  | Notation of Output Capacitance                        | 16  |

|    |       | 2.2.2  | Small-Signal CV and QV Characteristics                | 17  |

|    | 2.3   |        | d QV Measurements                                     | 18  |

|    |       | 2.3.1  | Small-Signal CV Measurements                          | 18  |

|    | o (   |        | Large-Signal QV Measurements                          | 18  |

|    | 2.4   | -      | ge- and Energy-Equivalent Parameters                  | 20  |

|    | 2.5   |        | Linear Nature of Device Output Capacitance            | 21  |

|    | 2.6   | Outpu  | It Capacitance and Circuit Topology                   | 22  |

| 3  | The | matic  | Overview: Switching Circuits and Switching Process                        | 25 |

|----|-----|--------|---------------------------------------------------------------------------|----|

|    | 3.1 | Basic  | Concepts                                                                  | 25 |

|    |     | 3.1.1  | ON Resistance and Channel Resistance                                      | 26 |

|    |     | 3.1.2  | Operating modes in a Hard-Switching Circuit                               | 26 |

|    |     | 3.1.3  | Operating modes in a Soft-Switching Circuit                               | 27 |

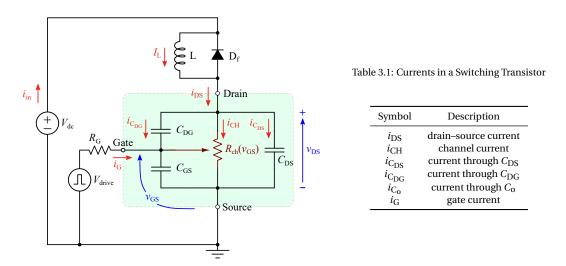

|    |     | 3.1.4  | Currents in a Switching Transistor                                        | 28 |

|    |     | 3.1.5  | Switching Energy                                                          | 29 |

|    | 3.2 | Soft-S | Switching Operation                                                       | 30 |

|    |     |        |                                                                           |    |

| II | PA  | ART 2  |                                                                           | 33 |

|    |     |        |                                                                           |    |

| 4  |     | -      | pacitance and Soft-Switching Circuits                                     | 35 |

|    | 4.1 |        | ground: Output-Capacitance Hysteresis Loss                                | 36 |

|    |     | 4.1.1  |                                                                           | 37 |

|    |     |        | Adaption of the Sawyer–Tower Technique                                    | 38 |

|    | 4.2 | Analy  | sis of the Sawyer–Tower Technique                                         | 40 |

|    |     | 4.2.1  | Basic Steady-State Operation                                              | 40 |

|    |     | 4.2.2  | Start-up of the Circuit                                                   | 41 |

|    |     | 4.2.3  | Measurements                                                              | 41 |

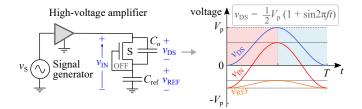

|    |     | 4.2.4  | High-Voltage Amplifier and Equivalent Load                                | 42 |

|    |     |        | 4.2.4.1 Effects of $C_{oss}$ and $C_{ref}$                                | 45 |

|    |     |        | 4.2.4.2 Voltage Amplifier Selection and Slew-Rate Limitations             | 47 |

|    |     | 4.2.5  | Reference Capacitor, <i>C</i> <sub>ref</sub>                              | 47 |

|    |     |        | 4.2.5.1 Selecting the Type of $C_{\text{ref}}$                            | 48 |

|    |     |        | 4.2.5.2 Frequency Dependence of $C_{ref}$                                 | 49 |

|    |     |        | 4.2.5.3 Selecting the Value of $C_{\text{ref}}$                           | 50 |

|    |     | 4.2.6  | Experimental Evaluation of the Effects of C <sub>ref</sub>                | 51 |

|    |     | 4.2.7  | The Reverse Conduction of the DUT                                         | 53 |

|    |     |        | 4.2.7.1 Experimental Observation of Reverse Conduction                    | 54 |

|    |     |        | 4.2.7.2 Identification of Underlying Reasons                              | 54 |

|    |     |        | 4.2.7.3 Minimizing Steady-State Reverse Conduction of the DUT             | 56 |

|    | 4.3 | Outpu  | ut-Capacitance Loss in Soft-Switching Circuits                            | 57 |

|    |     | 4.3.1  | Measurement Approach and Basic QV Patterns                                | 58 |

|    |     | 4.3.2  | Hysteresis Losses Observed with the Sawyer–Tower Circuit                  | 60 |

|    |     | 4.3.3  | Voltage Dependence of QV Patterns                                         | 61 |

|    |     | 4.3.4  | Frequency Dependence of Hysteresis Loss and QV Patterns                   | 64 |

|    |     | 4.3.5  | Hysteresis Losses versus Hard-Switching Losses                            | 67 |

|    |     | 4.3.6  | Family Comparison                                                         | 67 |

|    | 4.4 | Possil | pilities of Small-Signal Measurements                                     | 70 |

|    |     | 4.4.1  | Background                                                                | 70 |

|    |     | 4.4.2  | Measurements on the Output-Capacitance Branch                             | 72 |

|    |     | 4.4.3  | Results for Commercial Power FETs                                         | 74 |

|    |     | 4.4.4  | Implications of <i>R</i> <sub>oss</sub> on Large-Signal Hysteresis Losses | 76 |

|    |     |        | 4.4.4.1 The Practicality of Eq. (4.45)                                    | 78 |

|    |     |        | 4.4.4.2 Use of a Loss Tangent                                             | 79 |

|    |     | 4.4.5  | Qualitative Results                                                       | 80 |

|    |     | 4.4.6  | Discussion                                                                | 82 |

|    |     | 1. 1.0 |                                                                           | 02 |

|   |      | 4.4.7   | Recent Research and Limitations of the Approach                | 83  |

|---|------|---------|----------------------------------------------------------------|-----|

|   | 4.5  | Origir  | ns of Output-Capacitance Hysteresis Losses                     | 85  |

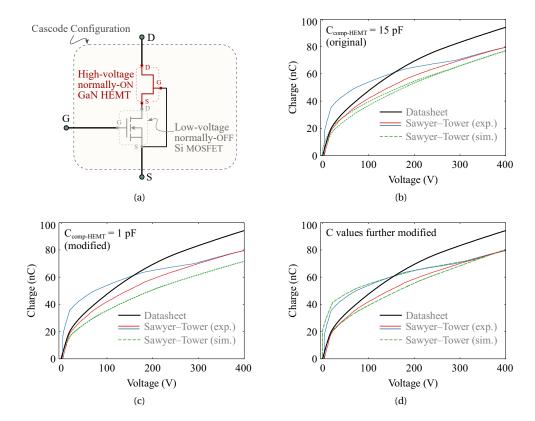

|   |      | 4.5.1   | On the Cascode Configuration and $C_0$ -Hysteresis Losses      | 86  |

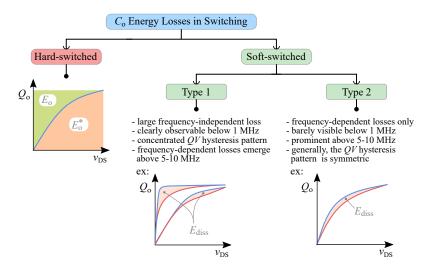

|   | 4.6  | Categ   | orization of Hysteresis Losses                                 | 88  |

|   |      | 4.6.1   | Output-Capacitance Hysteresis Losses Beyond 1 MHz              | 88  |

|   |      | 4.6.2   | Categorization based on QV Patterns                            | 89  |

|   | 4.7  | Sumn    | nary                                                           | 90  |

| 5 | Out  | nut Ca  | pacitance and Hard-Switching Circuits                          | 91  |

|   | 5.1  | -       | ground and Motivation.                                         | 92  |

|   | 5.2  | -       | Concepts                                                       | 92  |

|   |      |         | Hard-Switching versus Soft-Switching: Current Scenario         | 93  |

|   |      |         | Importance of Topological Distinction                          | 93  |

|   |      |         | Hard-Switching-Transitions and Related Losses                  | 94  |

|   | 5.3  |         | y Components Related to Charging and Discharging of Capacitors | 96  |

|   |      | -       | ept of co-energy in a Capacitor                                | 97  |

|   | 0.1  |         | Mathematical Analysis                                          | 97  |

|   |      | 5.4.2   | Simulation Results                                             | 98  |

|   |      |         | Historical Background on co-energy and $Q_0 V_{dc}$ Loss       | 100 |

|   |      |         | co-energy Component in Switching Circuits                      | 100 |

|   | 5.5  |         | lated Turn-ON Energy Loss in Hard Switching                    | 101 |

|   | 5.6  |         | Io-Load Concept                                                | 102 |

|   | 5.0  | 5.6.1   | Operation of the No-load Circuit                               | 105 |

|   |      |         | •                                                              | 105 |

|   |      | 5.6.2   | Experimental Demonstration of the co-energy Component          |     |

|   |      |         | 5.6.2.1 Concept                                                | 108 |

|   |      | 0       | 5.6.2.2 Design and Results                                     | 109 |

|   | 5.7  |         | ration of QV Curves for Hard Switching                         | 112 |

|   |      | 5.7.1   | Use of Asymmetrical Gate-Driving                               | 113 |

|   | 5.8  | -       | at-Capacitance Losses in Hard-Switching Circuits               | 114 |

|   |      | 5.8.1   | 1                                                              | 116 |

|   |      | 5.8.2   |                                                                | 118 |

|   |      | 5.8.3   | 0                                                              | 118 |

|   |      | 5.8.4   | Implications of the Loaded Operation                           |     |

|   |      |         | Effects from the Large-Signal Hysteresis of $C_0$              |     |

|   | 5.9  | Impo    | rtant Technical Considerations                                 | 122 |

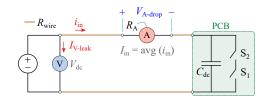

|   |      | 5.9.1   | Average Current and Voltage Measurements                       | 123 |

|   |      | 5.9.2   | Loading Effects of DMMs                                        | 123 |

|   |      | 5.9.3   | Probing of the Switch Node                                     | 123 |

|   |      | 5.9.4   | Drain–Source Leakage Current ( $I_{DSS}$ )                     | 124 |

|   |      | 5.9.5   | Selection of dc-link Capacitance                               | 124 |

|   | 5.10 | ) Sumn  | nary                                                           | 124 |

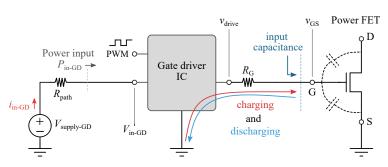

| 6 | Gate | e-Drivi | ing Losses                                                     | 127 |

|   | 6.1  |         | ration                                                         | 127 |

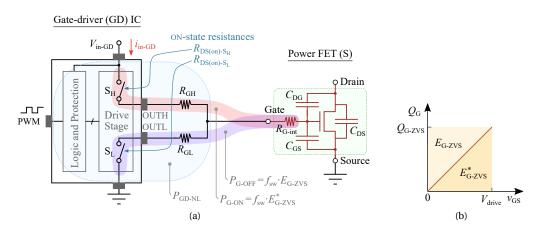

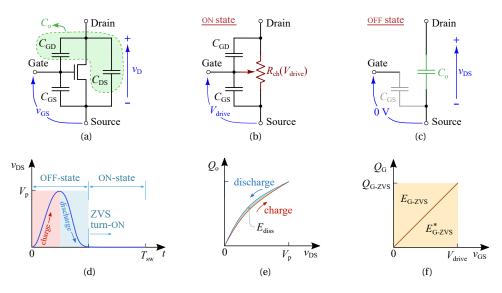

|   | 6.2  |         | Concepts                                                       | 129 |

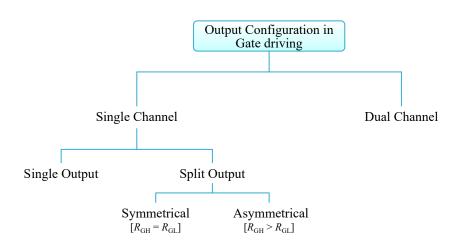

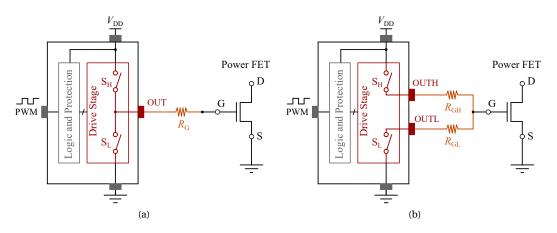

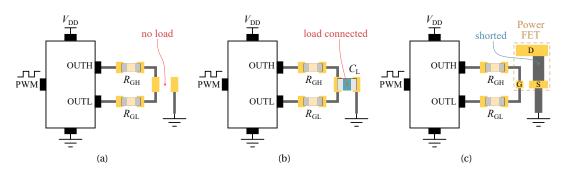

|   |      | 6.2.1   | Output Configuration in Gate Driving                           | 129 |

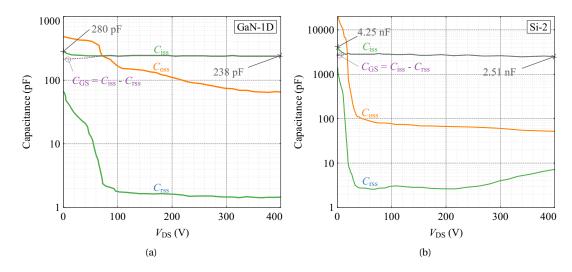

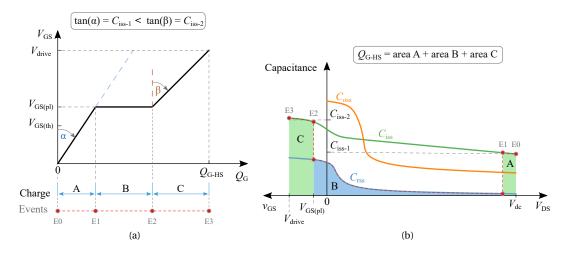

|   |      | 6.2.2   | Input Capacitance, and Charge Stored in Input Capacitance      | 130 |

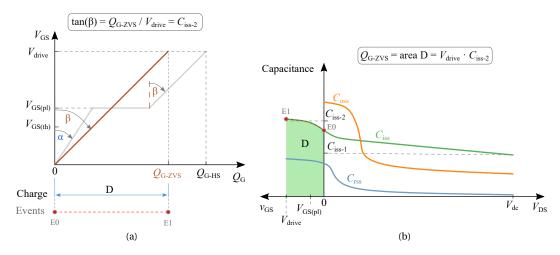

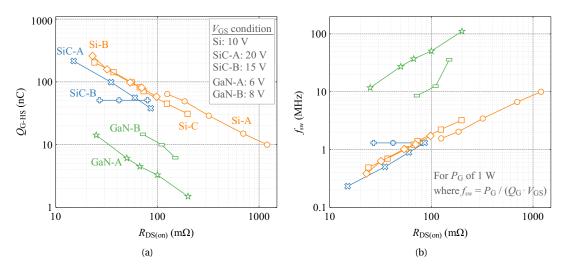

|   |      | 6.2.3   | $Q_{\text{G-HS}}$ and $Q_{\text{ZVS}}$                         |     |

|   |      |         |                                                                |     |

|   |     | graphy                                                                                        | 175 |

|---|-----|-----------------------------------------------------------------------------------------------|-----|

| A | Ack | nowledgements: Technical                                                                      | 173 |

|   | 8.3 | Additional Future Directions                                                                  | 170 |

|   |     | Conclusions and Outlook                                                                       | 169 |

|   | 8.1 | Summary                                                                                       | 169 |

| 8 |     | nclusion and Future Directions                                                                | 169 |

|   | 7.8 | Summary                                                                                       | 168 |

|   |     | 7.7.5 Overlook                                                                                | 168 |

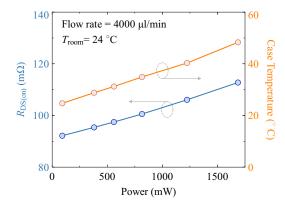

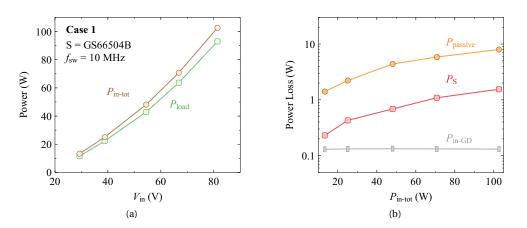

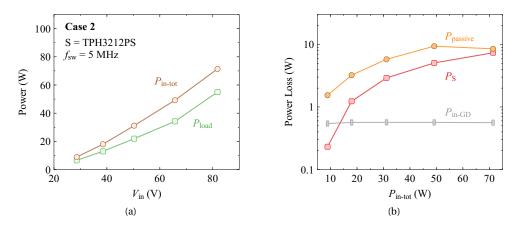

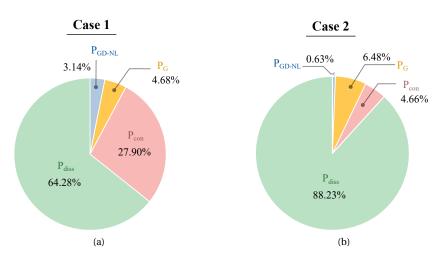

|   |     | 7.7.4 Complete Loss Breakdown of Active Devices                                               | 167 |

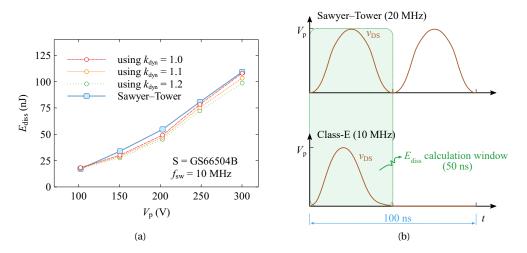

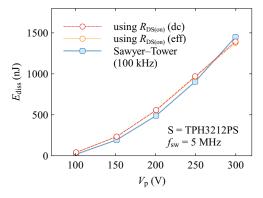

|   |     | 7.7.3 Output-Capacitance Losses                                                               | 165 |

|   |     | 7.7.2 Transistor Conduction Losses                                                            | 165 |

|   |     | 7.7.1 Gate-driving Losses                                                                     | 164 |

|   | 7.7 | Results and Discussion                                                                        | 163 |

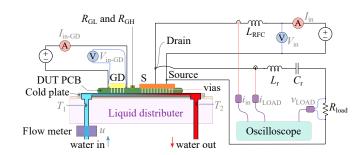

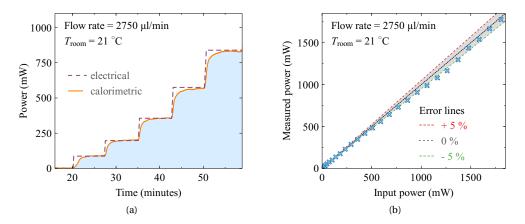

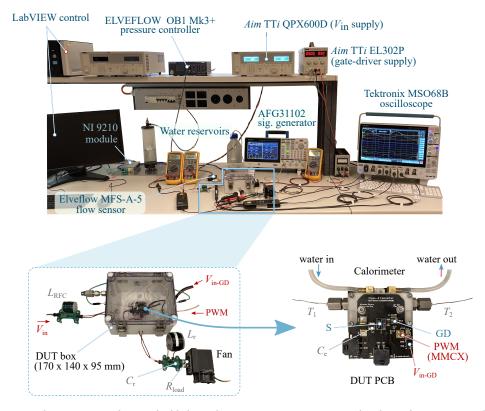

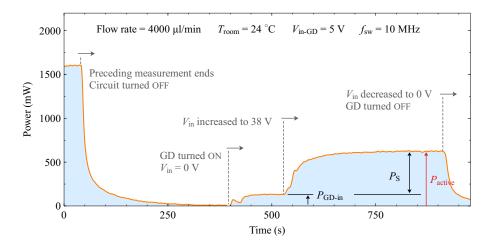

|   | 7.6 | Experimental System and Procedure                                                             | 161 |

|   | 7.5 | Loss Breakdown Approach                                                                       | 160 |

|   |     | 7.4.2 Electrical Measurements                                                                 | 158 |

|   |     | 7.4.1 Design of a Compact Calorimeter                                                         | 157 |

|   | 7.4 | Design of the Measurement System                                                              | 156 |

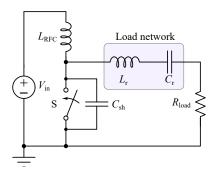

|   | 7.3 | Class-E Inverter                                                                              | 155 |

|   | 7.2 | Basic Concepts and Analysis                                                                   | 153 |

|   | 7.1 | Introduction to the Case Study                                                                | 152 |

| 7 | Cas | e Study with a Class-E Inverter                                                               | 151 |

|   | 6.7 | Summary                                                                                       | 150 |

|   | 6.6 | Evaluation of $Q_{G-ZVS}$                                                                     | 149 |

|   |     | 6.5.4 Discussion                                                                              | 147 |

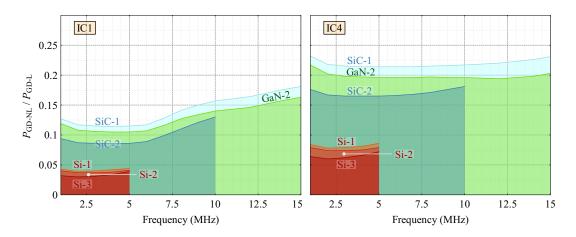

|   |     | 6.5.3 Power Loss in Driving Commercial Power FETs                                             | 146 |

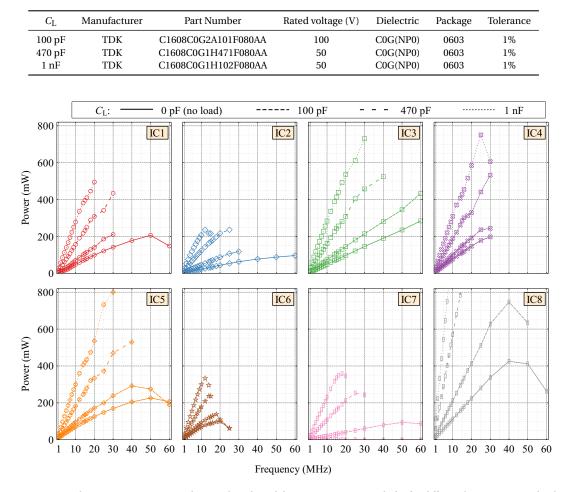

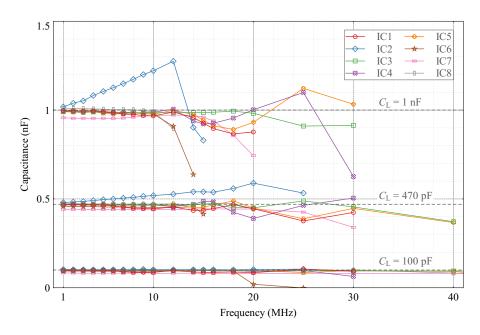

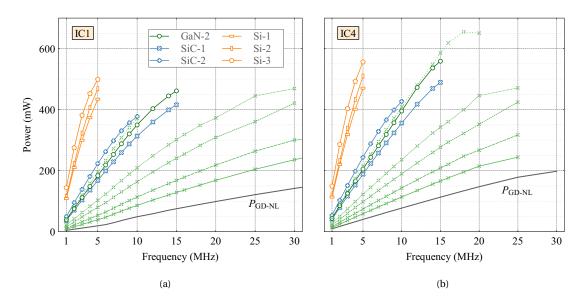

|   |     | 6.5.2 Power Loss in Driving Linear Capacitors                                                 | 143 |

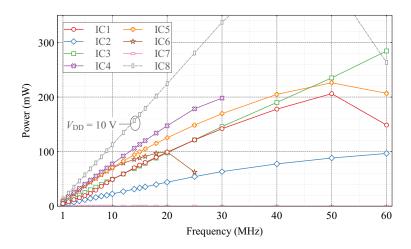

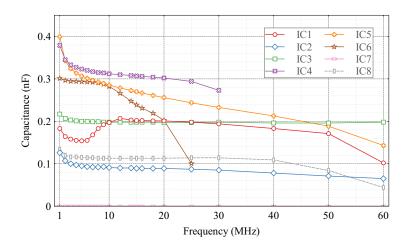

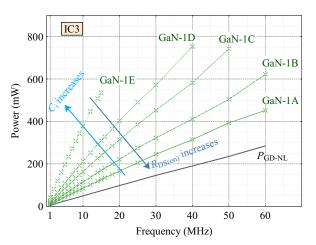

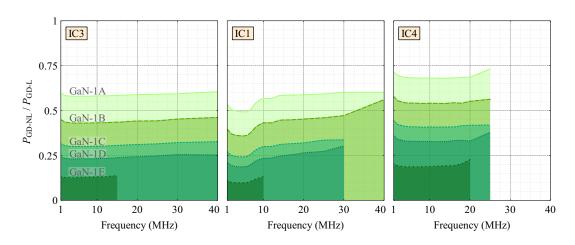

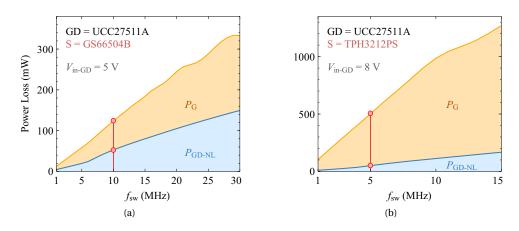

|   |     | 6.5.1 Power Loss in No-load Operation                                                         | 142 |

|   | 6.5 | Performance Comparison of Commercial Gate Drivers for MHz-Range Switching                     | 141 |

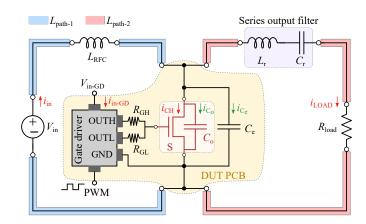

|   |     | 6.4.2 Details of the Experiments                                                              | 140 |

|   |     | 6.4.1 Important Measurement Considerations                                                    | 138 |

|   | 6.4 | Experimental Technique                                                                        | 137 |

|   |     | 6.3.3 Total Gate-Driving Loss                                                                 | 137 |

|   |     | 6.3.2 Losses in the Gate-Driver IC                                                            | 136 |

|   |     | 6.3.1 Gate Loss ( <i>P</i> <sub>G</sub> )                                                     | 135 |

|   | 6.3 | Analysis of the Loss Mechanisms in Gate Driving                                               | 135 |

|   |     | 6.2.5 Hard-Gating versus Resonant Gate-Driving                                                | 134 |

|   |     | 6.2.4 $Q_{\text{G-HS}}$ values: a Practical View                                              | 134 |

|   |     | $6.2.3.2  Q_{G-ZVS}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $         | 133 |

|   |     | $6.2.3.1  Q_{G-HS}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 132 |

# List of Figures

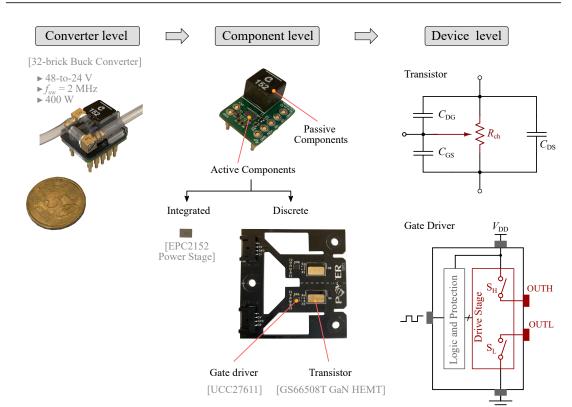

| 1.1  | A power electronics system can be described from three different levels: converter level,                 |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | component level and device level.                                                                         | 5  |

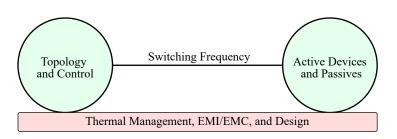

| 1.2  | Constituents of a power electronic converter.                                                             | 6  |

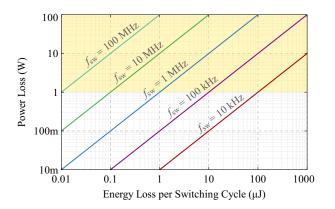

| 1.3  | How an energy loss related to a single switching cycle translates to a power loss at different            |    |

|      | switching frequencies.                                                                                    | 6  |

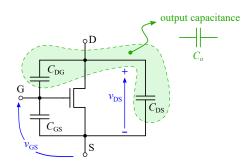

| 2.1  | A model of a field-effect transistor (FET) with its parasitic capacitances: gate-source                   |    |

|      | capacitance ( $C_{GS}$ ), drain–gate capacitance ( $C_{DG}$ ), and drain–source capacitance ( $C_{DS}$ ). | 12 |

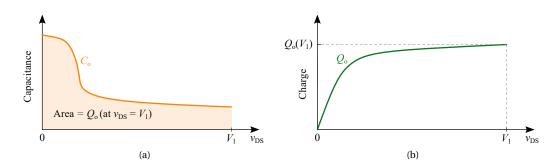

| 2.2  | The main features of device output capacitance are characterized by its <i>CV</i> and <i>QV</i> curves.   | 13 |

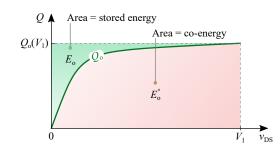

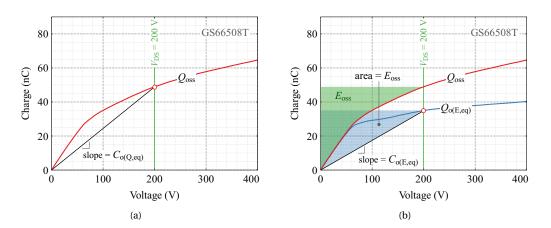

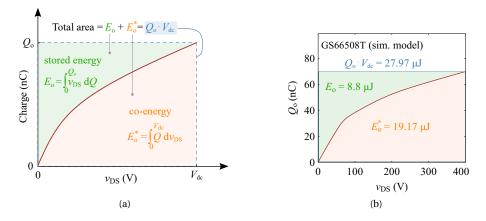

| 2.3  | Definition of energy components related to output capacitance on a <i>QV</i> curve                        | 14 |

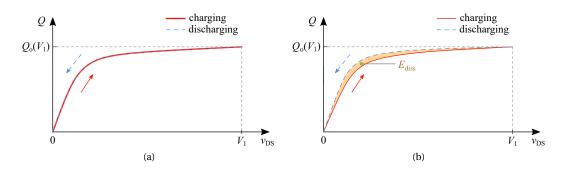

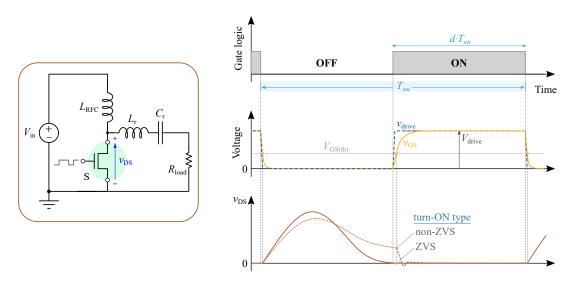

| 2.4  | Charge and discharge paths in a <i>QV</i> plot: without and with hysteresis.                              | 15 |

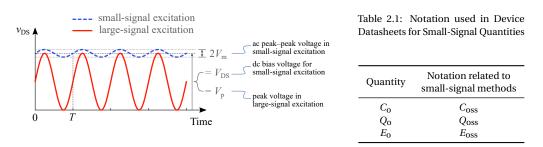

| 2.5  | Small-signal versus large-signal excitations.                                                             | 16 |

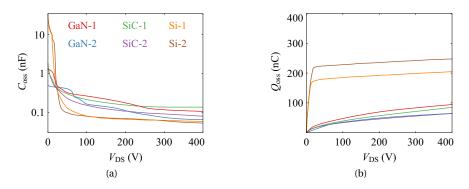

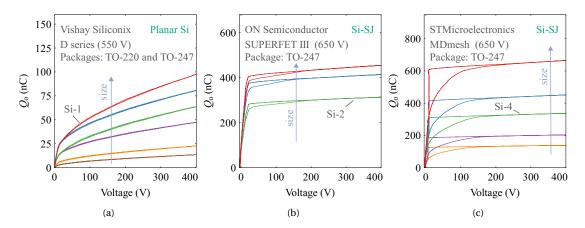

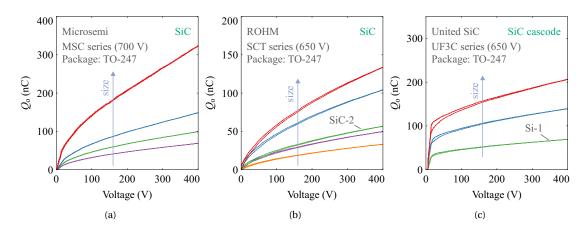

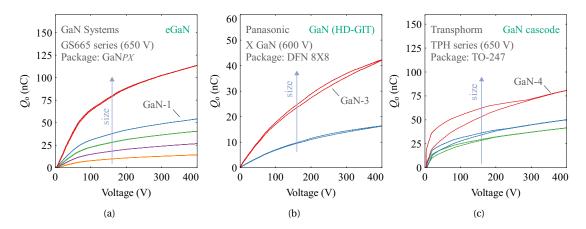

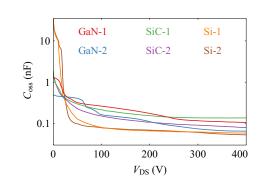

| 2.6  | $C_{\rm oss}$ and $Q_{\rm oss}$ curves of several commercial power FETs                                   | 17 |

| 2.7  | Calculation of the small-signal parameters $Q_{oss}$ and $E_{oss}$ from datasheet $C_{oss}$ curves        | 18 |

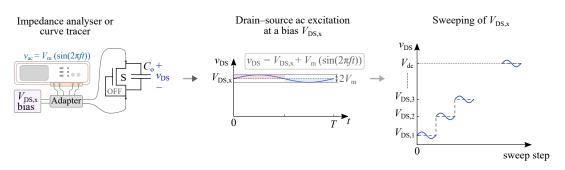

| 2.8  | Performing <i>small-signal CV</i> measurements with an impedance analyser or a power device               |    |

|      | curve tracer.                                                                                             | 19 |

| 2.9  | Large-signal excitation with the Sawyer–Tower circuit.                                                    | 19 |

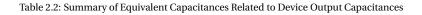

| 2.10 | Definition of charge- and energy-equivalent capacitances based on $C_{oss}$                               | 20 |

|      | A summary of different representations of $C_{oss}$ found on device datasheets                            | 21 |

| 2.12 | <i>CV</i> curves obtained using Eq. (2.19) for $m = 1/2$ , and $C_0 = 400$ pF and 100 pF. Four            |    |

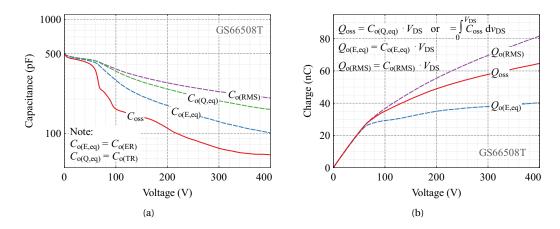

| 0.10 | different values for $V_0$ are considered for the two cases of $C_0$                                      | 22 |

| 2.13 | The relationship between the output capacitance of a power FET and a power electronics                    | 00 |

|      | circuit: two examples are considered.                                                                     | 23 |

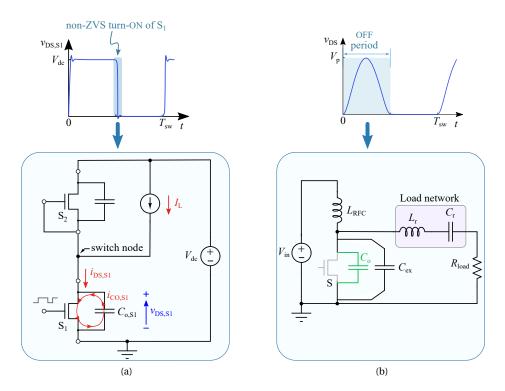

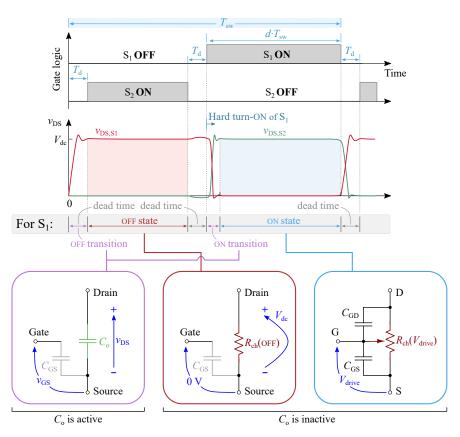

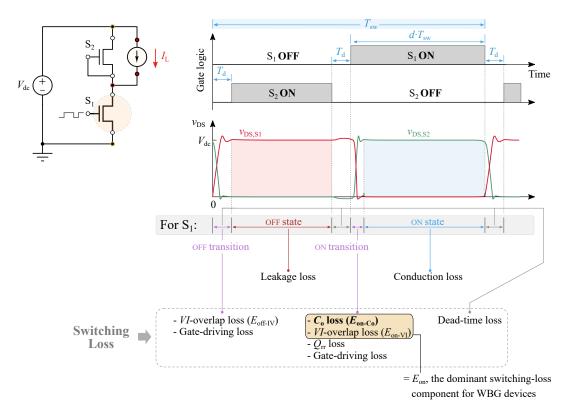

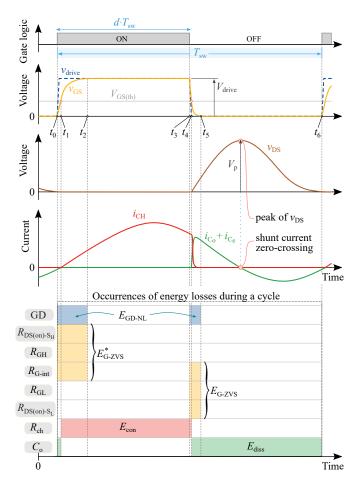

| 3.1  | Operating modes in a standard hard-switching circuit. The device under test is $S_1$                      | 27 |

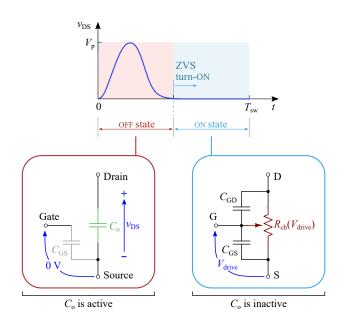

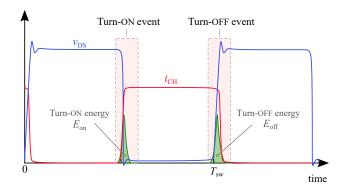

| 3.2  | Operating modes in a standard class-E circuit.                                                            | 28 |

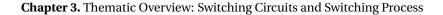

| 3.3  | Currents in a switching transistor.                                                                       | 29 |

| 3.4  | Representation of switching energy.                                                                       | 30 |

| 3.5  | ZVS and non-ZVS turn-ON events of the switching device in a class-E inverter                              | 31 |

| 3.6  | ZVS, partial-ZVS, and hard turn-on events of the synchronous device in a buck converter.                  | 32 |

| 4.1  | Qualitative overview on the charging-discharging process of the output capacitance of a                   |    |

| 1.1  | transistor in a resonant converter and related QV curves.                                                 | 36 |

|      |                                                                                                           | 00 |

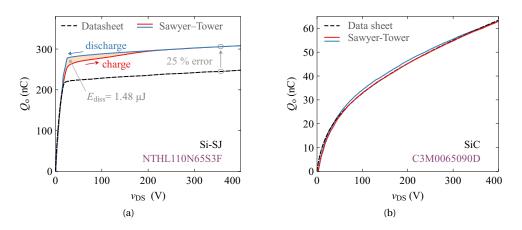

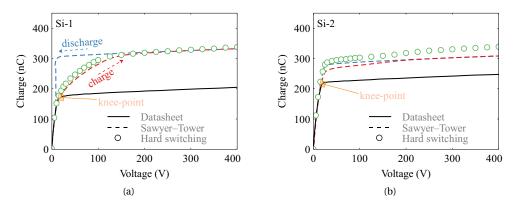

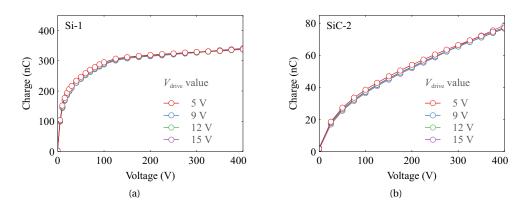

| 4.2   | Large-signal $Q_0$ vs $v_{DS}$ curves of two power FETs (obtained using the Sawyer–Tower circuit).                                                                                                                                                                                                                                                                 | 37 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

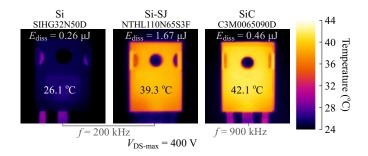

| 4.3   | Thermal images showing the temperature rise of three devices (Si, Si-SJ and SiC) with different $E_{\text{diss}}$ values (estimated using the Sawyer–Tower circuit). The devices (with $v_{\text{GS}} = 0$ V) have the same hardware package (TO-247) and were excited sinusoidally in the Sawyer–Tower circuit arrangement at 400 V.                              | 20 |

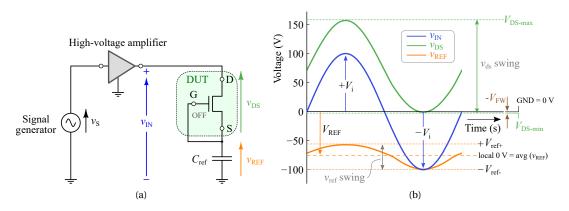

| 4.4   | Sawyer–Tower circuit arrangement at 400 V                                                                                                                                                                                                                                                                                                                          | 38 |

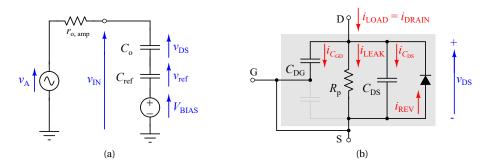

|       | operation.                                                                                                                                                                                                                                                                                                                                                         | 40 |

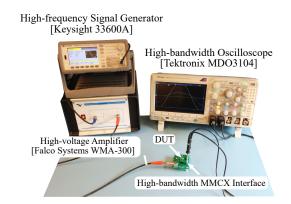

| 4.5   | Experimental test setup of the Sawyer–Tower measurement technique used to analyse large-signal output capacitance.                                                                                                                                                                                                                                                 | 42 |

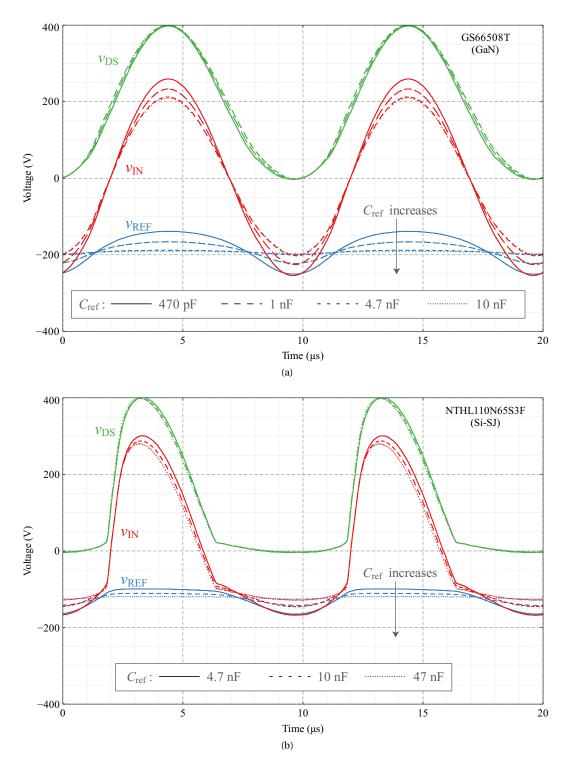

| 4.6   | Experimental waveforms showing the variation of the voltages $v_{IN}$ , $v_{REF}$ and $v_{DS}$ for different $C_{ref}$ values in the Sawyer–Tower circuit, where the DUT is (a) GS66508T GaN HEMT (650-V and 30-A) and (b) an NTHL110N65S3F Si-SJ MOSFET (650-V and 30-A). All reference capacitors were of COG type. Conditions: $V_{DS-max} = 400$ V and 100 kHz | 43 |

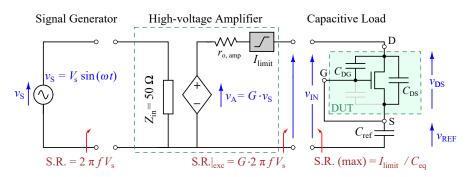

| 4.7   | Detailed Sawyer–Tower circuit. The following are highlighted: slew-rates at each interface; amplifier output resistance, $r_{0, amp}$ and current limit, $I_{limit}$ ; and DUT, where $C_0 = C_{DG}$ +                                                                                                                                                             |    |

|       | <i>C</i> <sub>DS</sub>                                                                                                                                                                                                                                                                                                                                             | 44 |

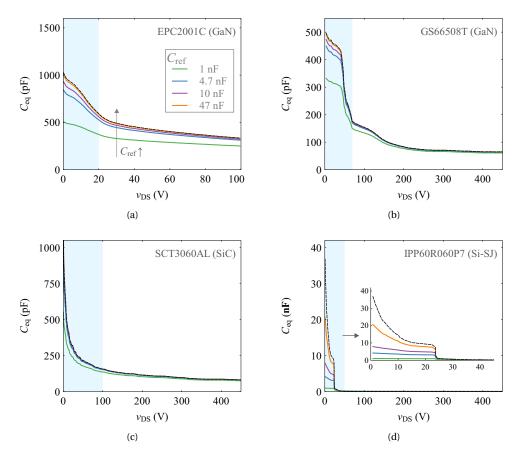

| 4.8   | $C_{\rm eq}$ versus $v_{\rm DS}$ for (a) EPC2001C(GaN), (b) GS66508T(GaN), (c) SCT3060AL(SiC), and (d) IPP60R060P7(Si-SJ) transistors, for different $C_{\rm ref}$ values.                                                                                                                                                                                         | 45 |

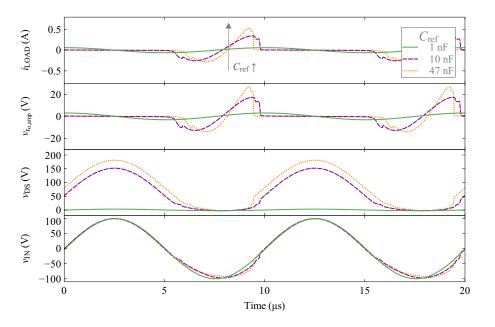

| 4.9   | LTspice simulation results showing the effects of having a large $C_{\text{oss}}$ value in the low $v_{\text{DS}}$ range, for $f = 100$ kHz. The DUT is a Si-SJ MOSFET (IPP60R060P7)                                                                                                                                                                               | 46 |

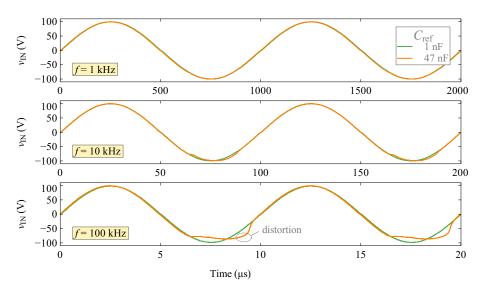

| 4.10  | Experimental waveforms of $v_{\rm IN}$ for the IPP60R060P7 Si-SJ MOSFET for different excitation                                                                                                                                                                                                                                                                   |    |

| 4 1 1 | frequencies. $v_{\text{IN}}$ distorts when $C_{\text{ref}}$ is large                                                                                                                                                                                                                                                                                               | 46 |

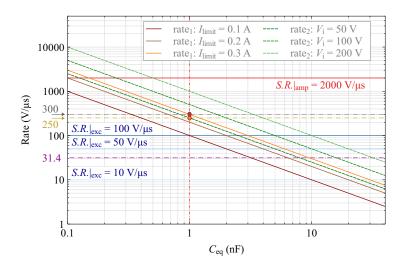

| 4.11  | Variation of rate <sub>1</sub> (in solid diagonal lines for different $I_{\text{limit}}$ ), and rate <sub>2</sub> (in dashed diagonal lines for different $V_{\text{i}}$ with $r_{\text{o}, \text{ amp}}$ fixed at 50 $\Omega$ ) with $C_{\text{eq}}$ . Solid blue lines show practical                                                                            | 47 |

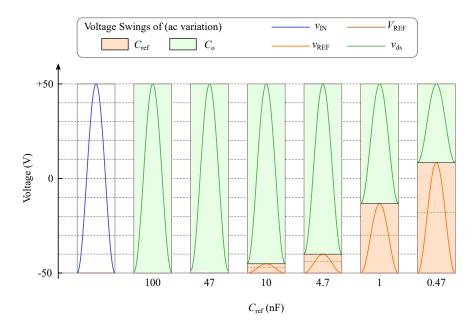

| 4.12  | $S.R. _{exc}$ values while the solid red line shows $S.R. _{amp}$ for the WMA-300 amplifier The distribution of the available voltage swing for the DUT (shaded area in green) and                                                                                                                                                                                 | 47 |

|       | the reference capacitor (shaded area in orange) upon the selection of <i>C</i> <sub>ref</sub> values of 100, 47, 10, 4.7, 1, and 0.47 in nF.                                                                                                                                                                                                                       | 49 |

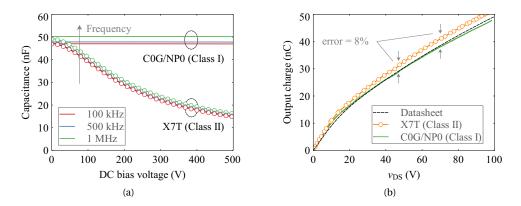

| 4.13  | (a) Capacitance <i>vs</i> bias-voltage of $C_{ref}$ , and (b) experimental $Q_o$ curves for an EPC2001C transistor at $f = 100$ kHz using the same $C_{ref}$ . A Class I NPO/COG capacitor and a Class II                                                                                                                                                          |    |

|       | X7T capacitor with nominal values of 47 nF are compared.                                                                                                                                                                                                                                                                                                           | 49 |

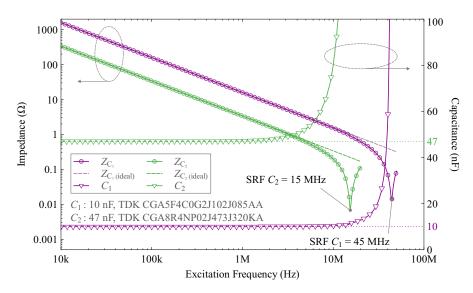

| 4.14  | Variation of impedance and capacitance of two C0G/NP0 capacitors ( $C_1$ of 10 nF and $C_2$ of 47 nF) measured with a Keysight E4990A Impedance Analyser                                                                                                                                                                                                           | 50 |

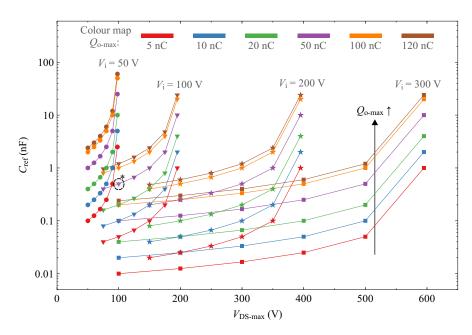

| 4.15  | Selection chart of $C_{\text{ref}}$ value for a required $V_{\text{DS-max}}$ based on the input voltage range $V_i$<br>and device's $Q_{0-\text{max}}$ . $Q_{0-\text{min}} \approx 0$ for practical cases.                                                                                                                                                         | 51 |

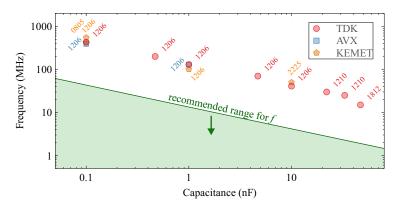

| 4.16  | Self-resonant frequency versus capacitance for commercial C0G/NP0 MLC capacitors (500/630 V): marked by three different symbols for three different manufacturers. The labels indicate the package.                                                                                                                                                                | 51 |

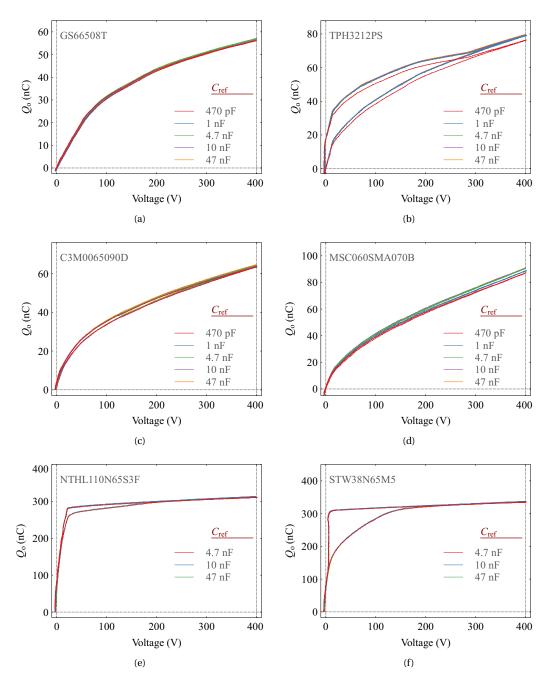

| 4.17  | $QV$ patterns obtained using the Sawyer–Tower circuit for different $C_{ref}$ values. Six different devices are considered as the DUTs: (a)–(b) GaN devices; (c)–(d) SiC devices; and (e)–(f)                                                                                                                                                                      |    |

| 1 10  | Si-SJ devices. Conditions: $V_{\text{DS-max}} = 400 \text{ V}$ and 100 kHz                                                                                                                                                                                                                                                                                         | 52 |

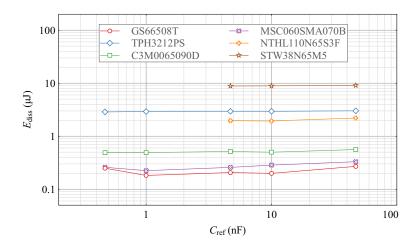

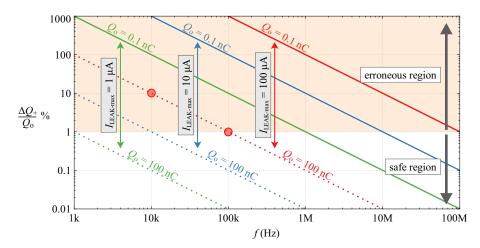

|       | Variation of $E_{diss}$ with $C_{ref}$ for the devices considered in Figure 4.17. Conditions: 400 V and 100 kHz.                                                                                                                                                                                                                                                   | 53 |

| 4.19  | (a) Sawyer–Tower circuit under steady-state operation where $v_{\text{REF}} = v_{\text{ref}} + V_{\text{BIAS}}$ , and (b) a model of the DUT showing the leakage current $i_{\text{LEAK}}$ .                                                                                                                                                                       | 54 |

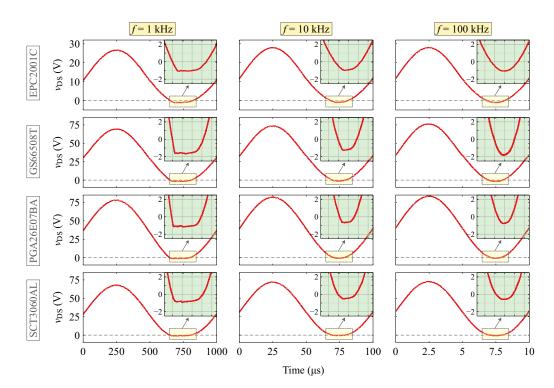

| 4.20 | Experimental waveforms of $v_{DS}$ showing steady-state reverse conduction for DUTs: GaN HEMTs; EPC2001C, GS66508T, PGA26E07BA; and SiC device SCT3060AL. Negative clip-                                                                                                                                                                                                                                                                                                  |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ping of $v_{\text{DS}}$ is seen in all the cases for $f = 1$ kHz and 10 kHz                                                                                                                                                                                                                                                                                                                                                                                               | 55 |

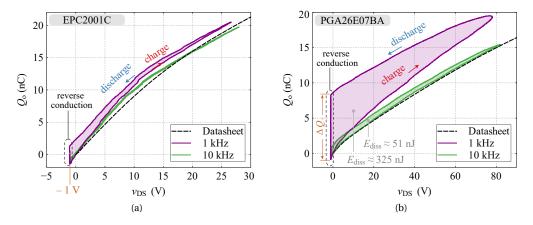

| 4.21 | Experimental $v_{DS}$ vs $Q_o$ curves for (a) EPC 2001C, and (b) PGA26E07BA transistors, showing hysteresis paths and $E_{diss}$ losses that are not due to $C_o$ , but due to an artefact of the steady-state reverse conduction of the DUT.                                                                                                                                                                                                                             | 55 |

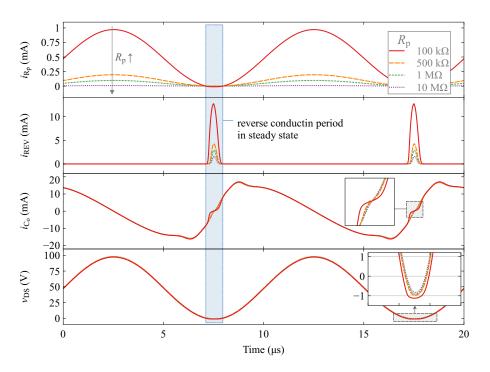

| 4.22 | LTspice simulation results showing the effect of device leakage (by changing $R_p$ ), in creating a reverse conduction period during the steady-state operation of the Sawyer–Tower circuit. $v_{\rm DS}$ clipping at -1.2 V shows clear reverse conduction                                                                                                                                                                                                               | 56 |

| 4.23 | The variation of the ratio between $\Delta Q_+$ and device $Q_0$ values, with $f_1$                                                                                                                                                                                                                                                                                                                                                                                       | 57 |

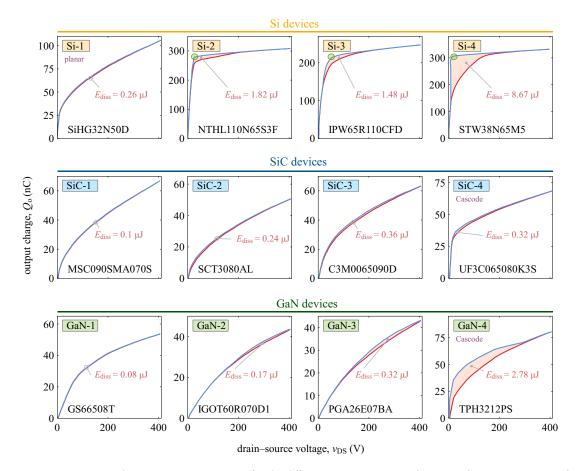

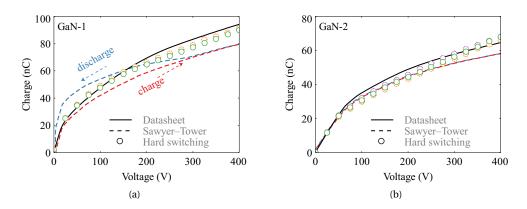

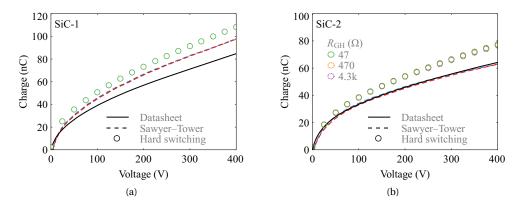

| 4.24 | Experimental <i>QV</i> curves of twelve different high-voltage transistors (voltage rating between 500–900 V and current rating around 30 A): planar/conventional Si device Si-1, Si-SJ devices Si-2 to Si-4, SiC devices SiC-1 to SiC-4 and GaN devices GaN-1 to GaN-4. The Sawyer–Tower technique was utilized at $V_p = 400$ V and $f = 100$ kHz. A $C_{ref}$ of 1 nF was used for all the measurements, except for the Si devices 2–4, where a $C_{ref}$ of 47 nF was |    |

|      | used                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60 |

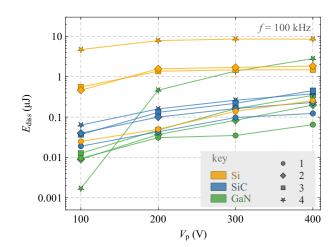

| 4.25 | Variation of $E_{\text{diss}}$ with different $V_{\text{p}}$ values for the twelve tested devices. $V_{\text{p}}$ is varied between 100 and 400 V at 100 V steps.                                                                                                                                                                                                                                                                                                         | 61 |

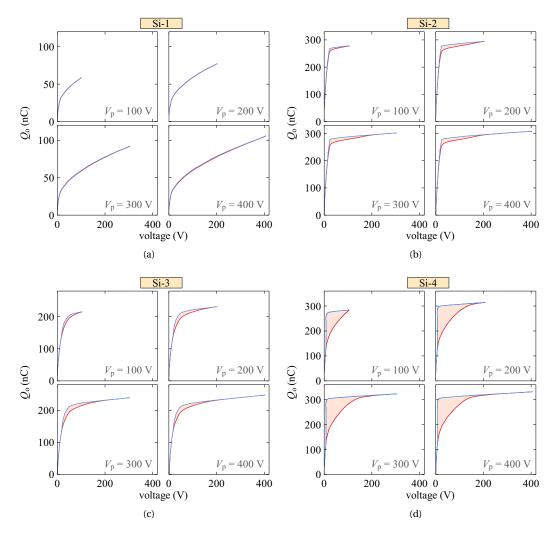

| 4.26 | Experimental results showing how the $QV$ hysteresis patterns vary with $V_p$ (100, 200, 300 and 400 V) for the tested Si devices. The excitation frequency was set at 100 kHz.                                                                                                                                                                                                                                                                                           | 62 |

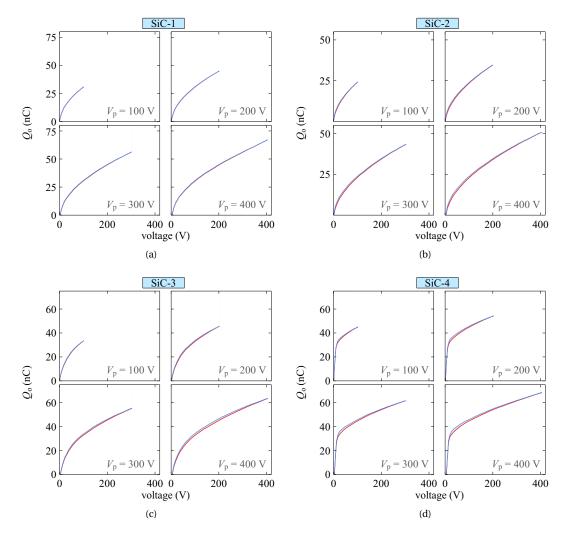

| 4.27 | Experimental results showing how the $QV$ hysteresis patterns vary with $V_p$ (100, 200, 300 and 400 V) for the tested SiC devices. The excitation frequency was set at 100 kHz                                                                                                                                                                                                                                                                                           | 63 |

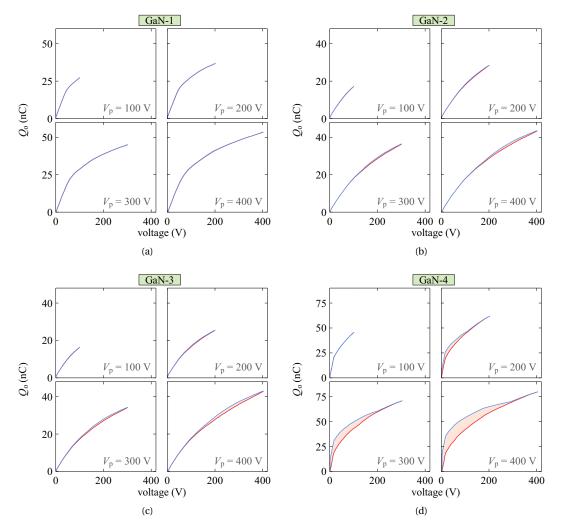

| 4.28 | Experimental results showing how the $QV$ hysteresis patterns vary with $V_p$ (100, 200, 300 and 400 V) for the tested GaN devices. The excitation frequency was set at 100 kHz.                                                                                                                                                                                                                                                                                          | 64 |

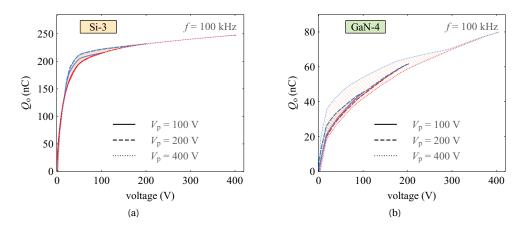

| 4.29 | Superimposition of <i>QV</i> hysteresis patterns of the devices (a) Si-3 and (b) GaN-4. The hysteresis pattern of device Si-3 at 400 V is a clear extension of the pattern at 100 V, with coincidental charging paths at each voltage. Device GaN-4 shows no hysteresis at 100 V; at 200 and 400 V, it shows hysteresis, but unlike device Si-3, the charging paths for each                                                                                              |    |

|      | case of peak voltage are non-coincidental.                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

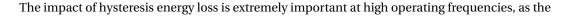

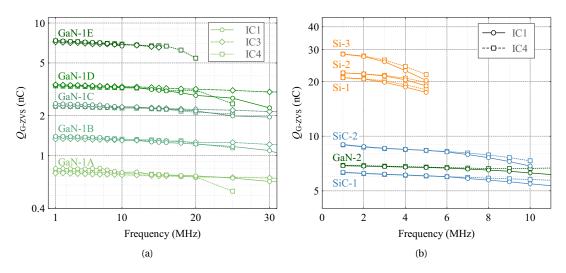

| 4.30 | Variation of $E_{\text{diss}}$ versus $f$ for selected devices. The results are obtained using the Sawyer–<br>Tower circuit with a variable frequency sinusoidal excitation signal                                                                                                                                                                                                                                                                                        | 65 |

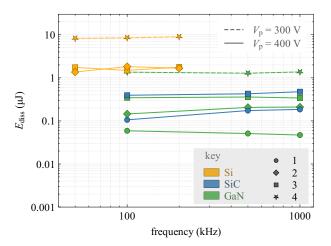

| 4.31 | Experimental $QV$ patterns for different $f$ values. The considered devices, in general, maintain a $QV$ pattern that is independent of the considered frequency range.                                                                                                                                                                                                                                                                                                   | 66 |

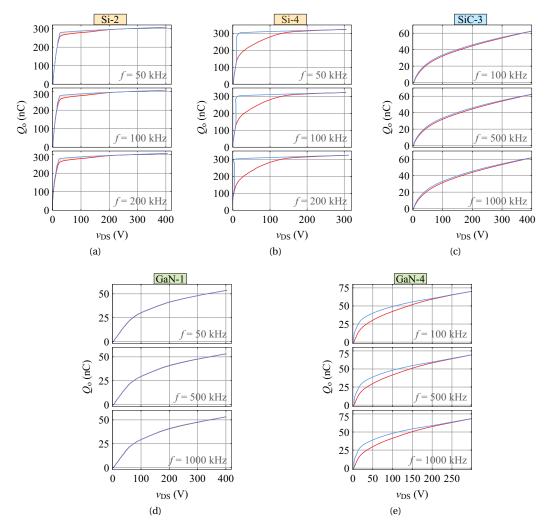

| 4.32 | $E_{\text{diss}}$ values of the devices listed in Table 4.3 plotted as a percentage loss of their $E_{\text{oss}}$ values. The $E_{\text{diss}}$ values are evaluated at 400 V and 100 kHz, while the $E_{\text{oss}}$ values are                                                                                                                                                                                                                                         |    |

| 1 33 | calculated using datasheet-provided $C_{oss}$ curves for 400 V                                                                                                                                                                                                                                                                                                                                                                                                            | 67 |

|      | Three families/manufacturers are considered                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 |

| 4.34 | Variation of <i>QV</i> patterns within a particular SiC-device-family of a given rated voltage.<br>Three families/manufacturers are considered                                                                                                                                                                                                                                                                                                                            | 69 |

| 4.35 | Variation of <i>QV</i> patterns within a particular GaN-device-family of a given rated voltage.<br>Three families/manufacturers are considered                                                                                                                                                                                                                                                                                                                            | 69 |

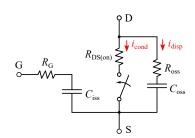

| 4.36 | Device model that was presented in the work by Perreault et al. [63]. The output-<br>capacitance branch consists of a capacitance $C_{oss}$ and a resistance $R_{oss}$ .                                                                                                                                                                                                                                                                                                  | 71 |

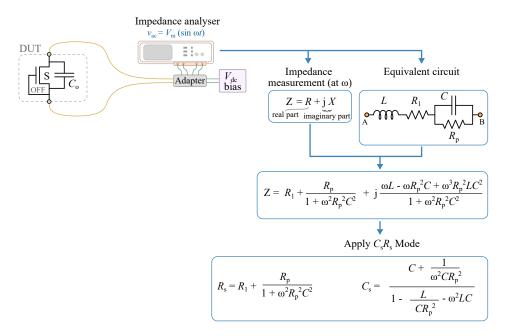

| 4.37 | The process of getting $C_s$ and $R_s$ values from impedance measurements using an imped-                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | ance analyser.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73 |

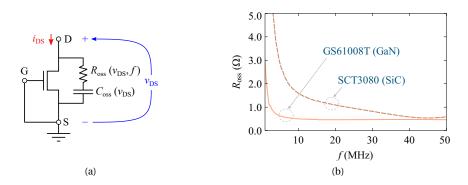

| 4.38 | (a) The output capacitance of a FET modelled as a branch consisting of the series combin-<br>ation of a capacitance $C_{oss}$ and a resistance $R_{oss}$ , which are evaluated with small-signal<br>measurements. (b) Variation of $R_{oss}$ with excitation frequency for a 100-V GaN device                                                                                                                                                                 |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | and a 650-V SiC device                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74  |

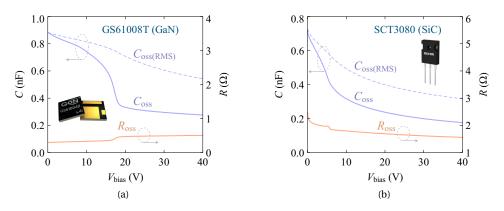

| 4.39 | Variation of $C_{oss}$ , $C_{oss(RMS)}$ and $R_{oss}$ with bias voltage for the same devices considered in                                                                                                                                                                                                                                                                                                                                                    |     |

|      | Figure 4.38(b). An excitation voltage of 100 mV at a frequency of 10 MHz was used                                                                                                                                                                                                                                                                                                                                                                             | 74  |

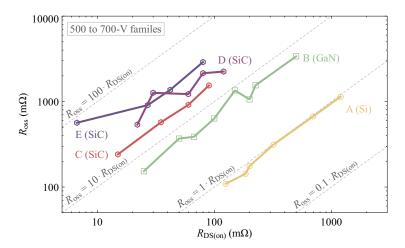

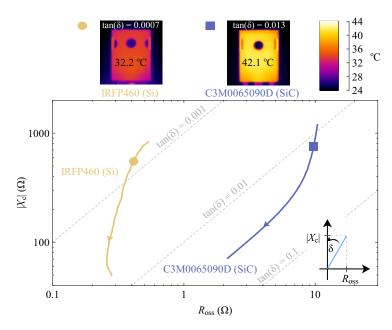

| 4.40 | Variation of $R_{\text{oss}}$ (at $v_{\text{DS}} = 40$ V and $v_{\text{GS}} = 0$ V) with $R_{\text{DS(on)}}$ for 500-700 V normally-off                                                                                                                                                                                                                                                                                                                       |     |

|      | device families. The excitation signal has $f = 10$ MHz and a peak of 100 mV                                                                                                                                                                                                                                                                                                                                                                                  | 75  |

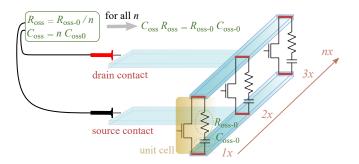

| 4.41 | Sizing of a large device of a current rating $I_{D(rated)}$ can be imagined by a distribution of $n$ unit cells, where each has a current rating of $I_{D0}$ .                                                                                                                                                                                                                                                                                                | 76  |

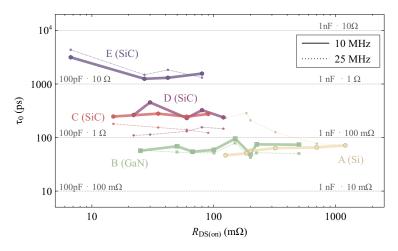

| 4.42 | Variation of $\tau_0 = C_{oss(RMS)} \cdot R_{oss}$ (at $v_{DS} = 40$ V and $v_{GS} = 0$ V) with $R_{DS(on)}$ for the device families considered in Figure 4.40 and Table 4.4.                                                                                                                                                                                                                                                                                 | 76  |

| 4.43 | A simple <i>RC</i> circuit                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77  |

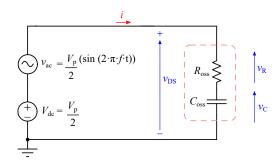

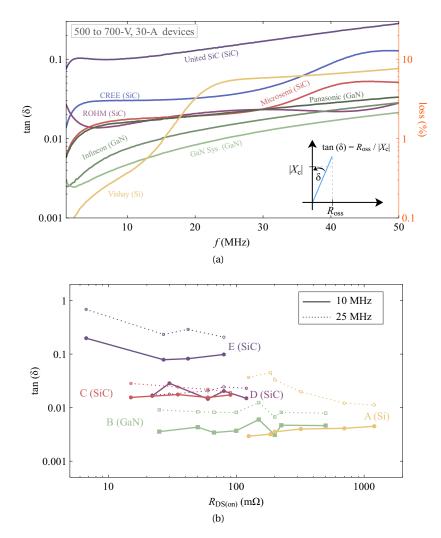

| 4.44 | (a) Variation of tan ( $\delta$ ) <i>vs f</i> for 30-A 500–900-V devices from different manufacturers.<br>The percentage losses are also given with respect to their effective stored energies. (b) Variation of tan( $\delta$ ) with $R_{\text{DS}(\text{on})}$ for the device families A-E, measured at <i>f</i> = 10 MHz (solid lines) and <i>f</i> = 25 MHz (dotted lines), with $C_{\text{oss}(\text{RMS})}$ values estimated at $v_{\text{DS}} = 400$ V | 81  |

| 4.45 | Temperature rise observed in two devices that have approximately equal $E_{oss}$ values ( $\approx 10 \ \mu$ J) at 400V, but different tan( $\delta$ ) values. The devices are excited using the Sawyer–Tower                                                                                                                                                                                                                                                 | 01  |

|      | circuit with a $v_{\text{DS}}$ swing of 0–400 V and $f = 900$ kHz.                                                                                                                                                                                                                                                                                                                                                                                            | 82  |

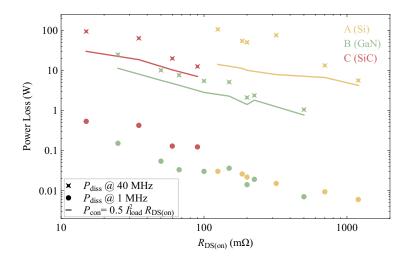

|      | Comparison of soft-switching power-loss levels with $R_{\text{DS(on)}}$ for three device families.                                                                                                                                                                                                                                                                                                                                                            | 83  |

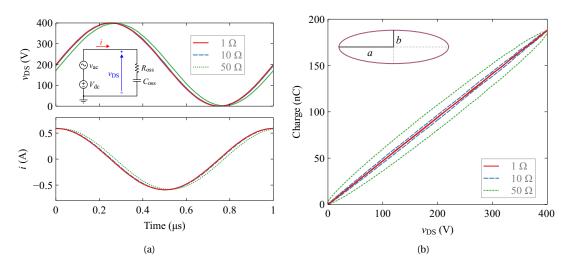

| 4.47 | Large-signal excitation of the output-capacitance branch, which is modelled with the small-signal quantities $C_{oss}$ and $R_{oss}$ . A linear capacitance of value 470 pF is used for $C_{oss}$ and three fixed values are considered for $R_{oss}$ : 1, 10 and 50 $\Omega$ . (a) voltage and current                                                                                                                                                       | 0.4 |

| 4 40 | waveforms. (b) QV curves.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84  |

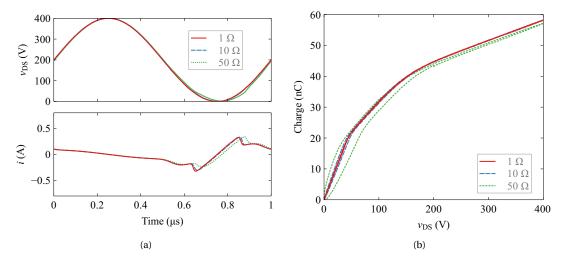

| 4.48 | Large-signal excitation of the output-capacitance branch. The non-linear output capacit-<br>ance of a GaN HEMT (GS66508T) is used for $C_{oss}$ . Three fixed values are considered for $R_{oss}$ : 1, 10 and 50 $\Omega$ . (a) voltage and current waveforms. (b) $QV$ curves                                                                                                                                                                                | 84  |

| 4 49 | GaN-cascode configuration and investigation on its SPICE models and related $C_0$ hyster-                                                                                                                                                                                                                                                                                                                                                                     | 01  |

| 1110 | esis.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87  |

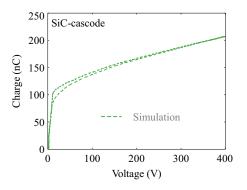

| 4.50 | Simulation results of the <i>QV</i> curves of the SiC cascode device UJC1210K obtained using the Sawyer–Tower circuit.                                                                                                                                                                                                                                                                                                                                        | 88  |

| 4.51 | Categorization of $C_0$ -related energy losses in hard-switching and soft-switching power                                                                                                                                                                                                                                                                                                                                                                     | 00  |

|      | electronic topologies.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

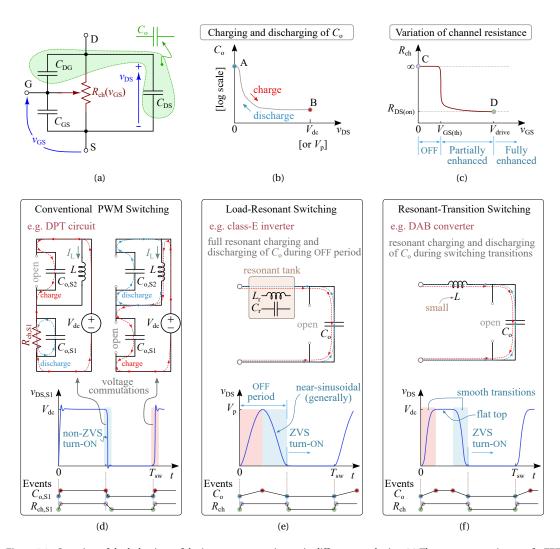

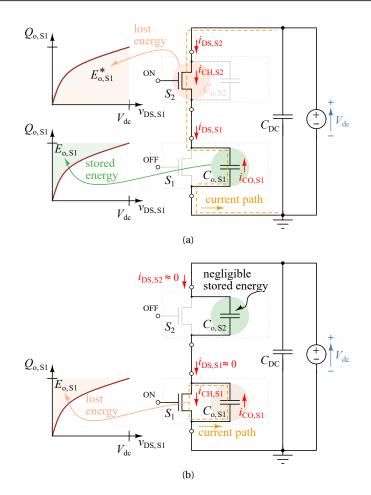

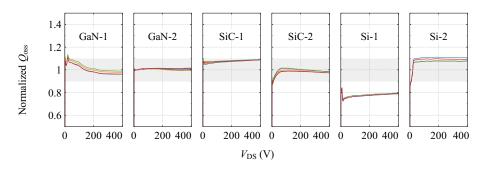

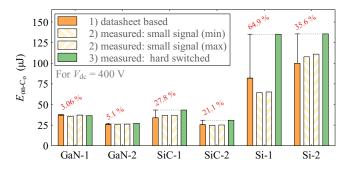

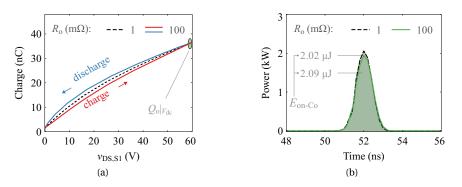

| 5.1  | Overview of the behaviour of device output capacitance in different topologies                                                                                                                                                                                                                                                                                                                                                                                | 94  |

| 5.2  | Qualitative representation detailing how hard-switching losses occur in a DPT circuit.                                                                                                                                                                                                                                                                                                                                                                        | 95  |

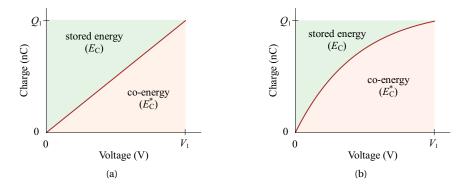

| 5.3  | The distribution of stored energy $(E_{\rm C})$ and co-energy $(E_{\rm C}^*)$ components in a charge versus voltage $(QV)$ plot related to (a) a linear capacitor, and (b) a nonlinear capacitance                                                                                                                                                                                                                                                            | 96  |

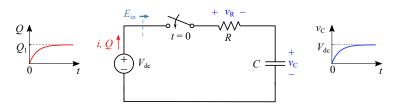

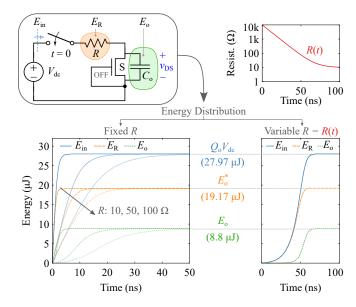

| 5.4  | An ideal dc voltage source, $V_{dc}$ , charges a capacitance C in series with a resistance R. The                                                                                                                                                                                                                                                                                                                                                             |     |

|      | circuit is turned ON at $t = 0$ . At $t \gg RC$ , the charging process is completed with $v_C = V_{dc}$ ,                                                                                                                                                                                                                                                                                                                                                     |     |

|      | and a total charge equal to $Q_1$ has been supplied by the source that is stored in $C$                                                                                                                                                                                                                                                                                                                                                                       | 97  |

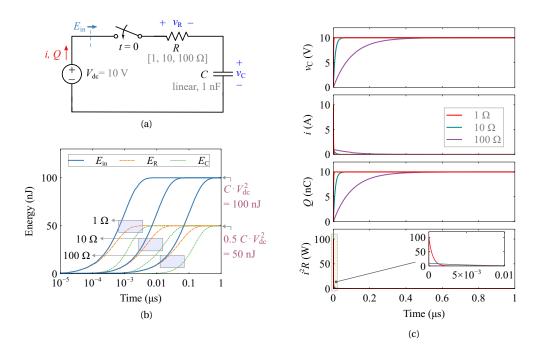

| 5.5  | (a) Linear capacitor of 1 nF (in series with a resistor, <i>R</i> ) is charged by an ideal dc voltage source of 10 V. The circuit is simulated in LTspice. (b) Related energy distributions with                                                                                                                                                                                                                                                              |     |

|      | time for three different values of $R$                                                                                                                                                                                                                                                                                                                                                                                                                        | 98  |

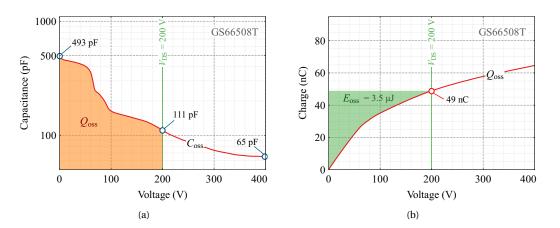

| 5.6  | (a) Stored energy and co-energy components related to the output capacitance of a FET                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | (b) QV curve of a GaN HEMT (GS66508T)                                                                                                                                                                                                                                                                                                                                                                                                                         | 99  |

| 5.7  | Energy distributions when a GaN HEMT (GS66508T) model, with $v_{GS}$ = 0 V, is put in series                                                                                                                                      |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | with a resistor, <i>R</i> , and an ideal dc voltage source $V_{dc} = 400$ V                                                                                                                                                       | 100 |

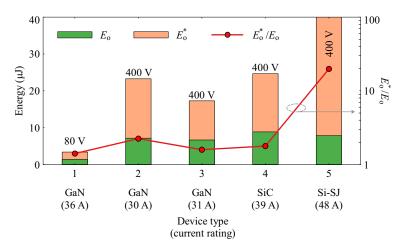

| 5.8  | Variation of $E_0$ , $E_0^*$ , and the ratio $n_{co} = E_0^*/E_0$ evaluated at the marked voltages, for different commercial field-effect transistors.                                                                            | 102 |

| 5.9  | (a) In a double-pulse-test (DPT) circuit, switch $S_1$ (the DUT) experiences a fully hard-                                                                                                                                        | 102 |

| 5.9  | switched operation, while the complementary switch $S_2$ is kept OFF. $S_2$ is of the same                                                                                                                                        |     |

|      | device type as $S_1$ . (b) <i>LTspice</i> simulation results of voltage, channel current and power                                                                                                                                |     |

|      | waveforms of $S_1$ during its turn-ON transient, where $S_1$ and $S_2$ are EPC2001C devices.                                                                                                                                      | 102 |

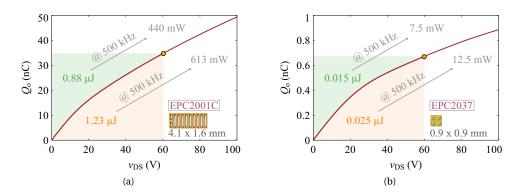

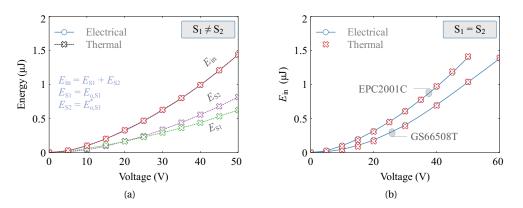

| 5 10 | $QV$ curves of the GaN HEMTs (a) EPC2001C and (b) EPC2037, where $E_0$ and $E_0^*$ values are                                                                                                                                     | 102 |

| 5.10 | evaluated at a voltage of $V_{dc} = 60$ V, using datasheet-provided $C_{oss}$ curves                                                                                                                                              | 102 |

| 5 11 |                                                                                                                                                                                                                                   | 103 |

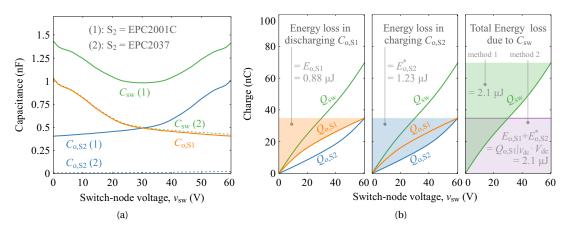

| 5.11 | Variation of (a) switch-node capacitance, $C_{sw}$ , and (b) switch-node charge, $Q_{sw}$ , during the turn ON process of a fully hard quitched better quite $S_{sw}$ of an inverter log with                                     |     |

|      | the turn-ON process of a fully hard-switched bottom switch $S_1$ of an inverter leg with $V_1 = 60 V_2$                                                                                                                           | 104 |

| F 10 | $V_{\rm dc} = 60$ V                                                                                                                                                                                                               | 104 |

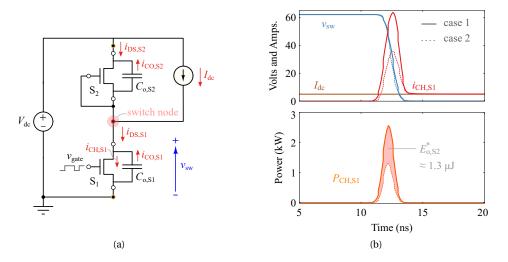

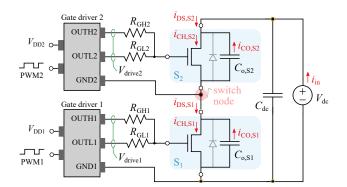

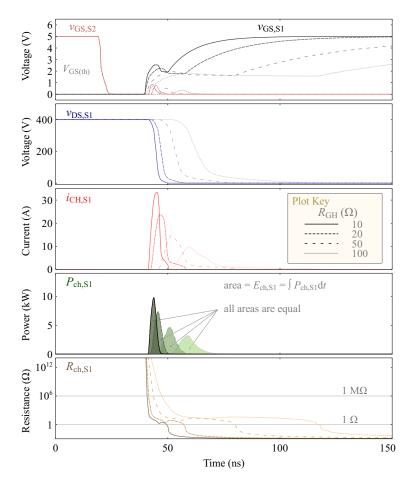

| 5.12 |                                                                                                                                                                                                                                   |     |

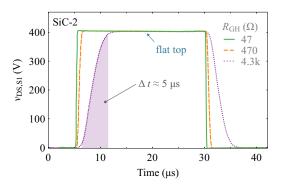

|      | $(S_1 \text{ and } S_2)$ are switched complementarily using an asymmetrical gate-driving configuration.                                                                                                                           | 106 |

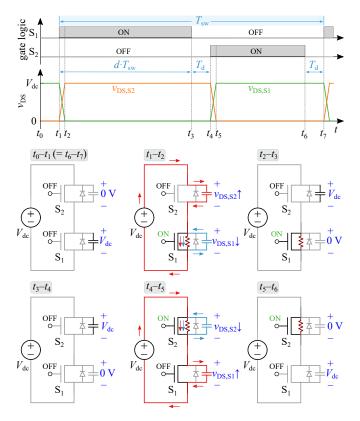

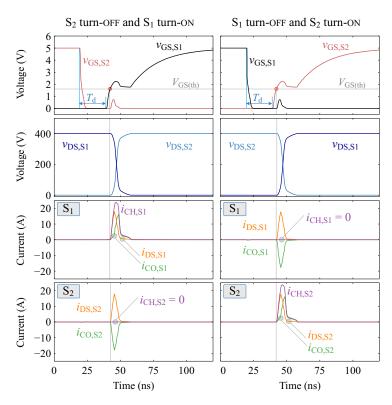

| 5 12 | Six modes of operation in the no-load circuit.                                                                                                                                                                                    | 100 |

|      | LTspice simulation results showing the turn-ON and turn-OFF transitions of $S_1$ and $S_2$ in                                                                                                                                     | 100 |

| 5.14 | the no-load circuit, where $V_{dc} = 400$ V, $f_{sw} = 100$ kHz, $d = 0.5$ , $T_d = 20$ ns, $R_{GH} = 20 \Omega$ and                                                                                                              |     |

|      | $R_{\rm GL} = 0.1 \ \Omega$ . S <sub>1</sub> and S <sub>2</sub> are GS66508T GaN HEMT models                                                                                                                                      | 108 |

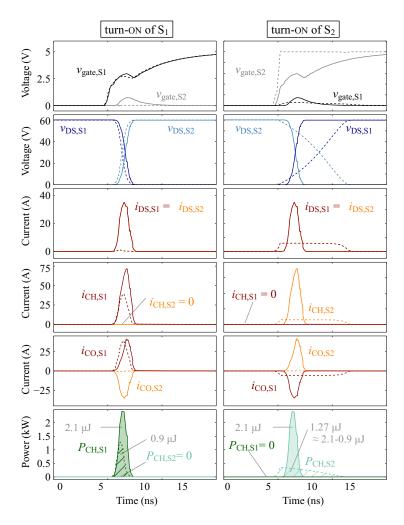

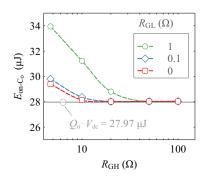

| 5 15 | $M_{GL} = 0.122$ . S <sub>1</sub> and S <sub>2</sub> are GS005001 GaV HEWT models                                                                                                                                                 | 100 |

| 5.15 | transient of $S_1$ , in the special no-load configuration used to verify the co-energy concept.                                                                                                                                   | 100 |

| 5 16 | Element of S <sub>1</sub> , in the special no-load configuration used to verify the co-energy concept.<br>LTspice simulation results showing the turn-ON transients of S <sub>1</sub> and S <sub>2</sub> , where $V_{dc} = 60$ V, | 105 |

| 5.10 | $f_{sw} = 500 \text{ kHz}$ , duty = 0.5, $T_{dead} = 50 \text{ ns}$ , $R_{G1H} = R_{G2H} = 1 \Omega$ . The solid lines show Case 1,                                                                                               |     |

|      | $J_{sw} = 500$ kHz, duty = 0.5, $T_{dead} = 50$ Hs, $R_{G1H} = R_{G2H} = 122$ . The solid lines show Case 1, where both S <sub>1</sub> and S <sub>2</sub> are EPC2001C devices, while the dashed curves show Case 2, where        |     |

|      | $S_2$ is an EPC2037 device that has a negligible $C_0$ value compared to an EPC2001C device.                                                                                                                                      | 110 |

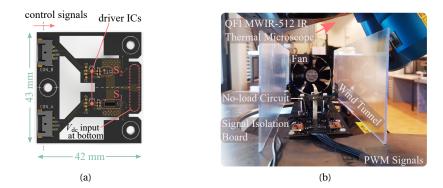

| 5 17 | $G_{2}$ is an El C2007 device that has a negligible $G_{0}$ value compared to an El C2007C device.                                                                                                                                | 110 |

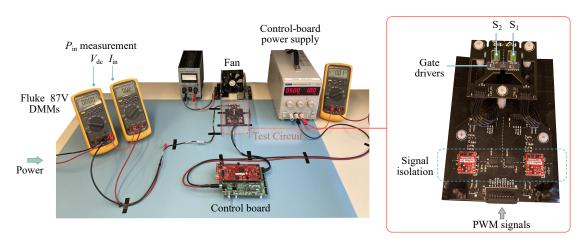

| 5.17 | imental test setup showing the test circuit, wind tunnel and Quantum Focus Instrument                                                                                                                                             |     |

|      | (QFI) IR microscope.                                                                                                                                                                                                              | 111 |

| 5 18 | Experimental results showing (a) the dissipated power versus dc-link voltage, and (b) the                                                                                                                                         |     |

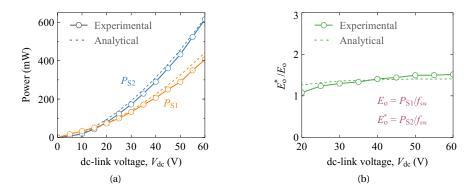

| 0.10 | ratio $n_{co} = E_0^* / E_0$ . The analytical results are based on datasheet-provided small-signal                                                                                                                                |     |

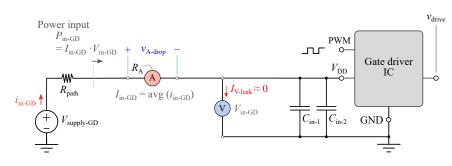

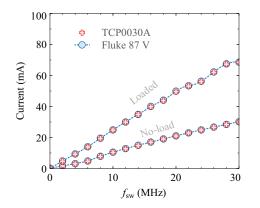

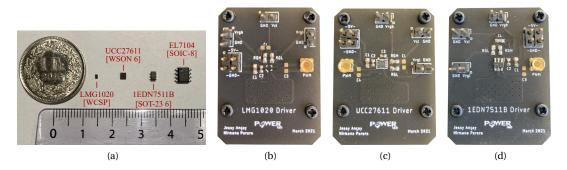

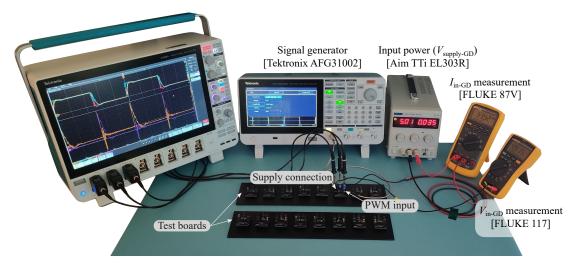

|      | $C_{\text{oss}}$ curves. $P_{\text{S1}}$ and $P_{\text{S2}}$ are power dissipations in the switches $S_1$ and $S_2$ , respectively.                                                                                               |     |