# Active-Device Losses in Resonant Power Converters: A Case Study with Class-E Inverters

Nirmana Perera, Remco van Erp, Jessy Ançay, Armin Jafari and Elison Matioli

Power and Wide-Band-Gap Electronics Research Laboratory

École Polytechnique Fédérale de Lausanne (EPFL)

Lausanne, Switzerland

nirmana.perera@epfl.ch and elison.matioli@epfl.ch

Abstract-Recent research has reported an undesirable OFFstate loss in high-frequency soft-switching power converters, such as resonant converters. This loss is attributed to a hysteresis loss related to the charging-discharging process of the output capacitance of the power transistor. However, precise estimation of transistor power loss and its breakdown into ON-state and OFF-state losses is challenging in the MHz-range operation due to the small circuit size, parasitic effects, and limited accuracy in existing methods to measure low-loss systems. We present a measurement concept to perform a complete loss breakdown of MHz-range resonant converters, as well, directly determine the OFF-state losses in transistors, which is demonstrated for a GaNbased class-E inverter operating at 10 MHz. A novel and compact calorimeter was designed to measure the converter active-device losses down to 20 mW within a 5 % error. This measured loss is then separated into four components using a combination of average and instantaneous electrical measurements: transistor ON-state loss, transistor OFF-state loss, gate-driver internal loss and gate loss. A simple no-load technique was devised to evaluate the gate-driver internal loss. The proposed approach directly determines output-capacitance hysteresis losses during the actual converter operation, which is not possible with existing measurement methods. The presented knowledge of individual loss components permits better optimization of MHz-range power converters.

Index Terms—Active devices, calorimeter, class-E inverter, gate-driver losses, hysteresis losses, electrical measurements, output capacitance  $(C_0)$ , soft switching, switching losses.

#### I. INTRODUCTION

The use of GaN devices in resonant power converters, such as in the class-E topology [1]–[4], has gained recent popularity due to high-efficiency operation at MHz-range frequencies [5], [6]. Precise determination of all the power losses in these converters is paramount for their optimization. Such a task necessitates accurate measurement techniques to breakdown converter losses down to milliwatt level, and a clear understanding of transistor and gate-driver loss distributions. And it has never been more important as a notable OFF-state power loss in GaN transistors has been reported [7], [8], compromising the converter efficiency. This loss cannot be predicted by device datasheets and is related to a hysteresis energy loss ( $E_{diss}$ ) in the transistor output-capacitance,  $C_o$  [9]; and it is a function of device drain–source voltage,  $v_{DS}$ .

Exclusive measurement of  $C_0$ -hysteresis loss in an actual resonant power converter is challenging. This is due to the requirement of small circuit-size in high-frequency operation that in turn creates measurement issues: for example, probing difficulties in electrical measurements and loss quantification issues in thermal/calorimetric methods [8] (due to thermal cross-coupling when several devices are involved). Therefore, indirect electrical methods such as the Sawyer-Tower technique [7], [8], [10] or calorimetric methods [11], [12] have been used to predict  $C_0$ -hysteresis losses in a working converter. However, they offer difficulties in certain aspects. On the one hand, although an excellent technique [7], the Sawyer–Tower method cannot always replicate the actual  $v_{DS}$ waveform, and in some cases, the subsequent estimations could not fully explain the difference between measured versus predicted efficiencies in certain converters [6], [8]. Thus, a direct and accurate method to measure hysteresis losses during actual circuit operation is required. On the other hand, existing calorimetric methods involve relatively slow systems that are also limited in accuracy, especially in mW-range power levels [13]. Furthermore, they often determine system-level losses, and therefore, lack the ability to perform a complete loss break-down of a real converter in operation.

Moreover, the losses in gate driving become non-negligible in MHz-range switching frequencies. In this regard, the conventional approach used to calculate gate-driving losses accounts only for the gate loss,  $P_G$ , which is related to the turn-ON and turn-OFF processes of the power transistor [14], [15], with some works separating  $P_G$  into driver and transistor losses based on the physical location of gate-loop path resistances [16]. But this approach leaves the switching loss inside the gate driver itself unaccounted for [17]. The distinction between these two components is essential for a correct breakdown of active-device losses and to make an informed decision on the gate-driver selection for high-frequency converters.

In this research work, we demonstrate a complete and accurate loss breakdown of a class-E inverter operating at 10 MHz. A high-precision and compact flow-calorimeter is developed to accurately measure active-device losses at mW-level. This loss is then separated into transistor and gate-driving losses, using a combination of average current and voltage measurements. The transistor power loss is divided into ON-state (or the conduction loss,  $P_{\rm con}$ ) and OFF-state losses. A no-load concept

This work was supported in part by the Swiss Office of Energy (SFOE) Grant Numbers SI501887-01 (MEPCO) and SI/502100-01, and in part by the European Research Council (ERC Starting Grant) under the European Union's H2020 program (ERC grant agreement number 679425).

is utilized to separate the gate-driving loss into gate loss and driver internal-loss. We have chosen the class-E topology, especially as a platform to measure the OFF-state loss of a transistor, as it offers several practical advantages:

- 1) The existence of only a single transistor eliminates the issue of thermal cross-coupling between two devices [8].

- 2) The path inductances between the input, the devicebranch, and the output can be incorporated into circuit inductances, thus permitting direct electrical measurements, without complicating the circuit operation.

- 3) All the parasitic shunt capacitances can be lumped together to a single shunt capacitance [18].

This paper aims to serve as a practical point of reference for high-frequency losses in transistors and gate drivers, their relative contributions and practical measurement. Section II introduces the important concepts on active-device losses, with special focus on  $C_0$ -hysteresis losses and gate-driving losses. Section III discusses the class-E topology. Section IV details the measurement concept and the development of the test system. Experimental results are presented in Section V. Section VI concludes the paper.

## II. ACTIVE-DEVICE LOSSES IN RESONANT POWER CONVERTERS

In our analysis, we consider only field-effect transistors (FETs)—such as Si and SiC MOSFETS, and GaN HEMTs as the switching device, which is denoted as S and undergoes zero-voltage-switching (ZVS). All the expressions and abbreviations for power refer to their average values, unless otherwise stated. The power losses generated in S and the gatedriving sub-circuit constitute the active-device losses,  $P_{active}$ . The total power loss in a converter,  $P_{loss-tot}$ , consists of  $P_{active}$ and passive-device losses,  $P_{passive}$ :

$$P_{\text{loss-tot}} = P_{\text{active}} + P_{\text{passive}} \tag{1}$$

The total input power,  $P_{\text{in-tot}}$ , of the converter is described as

$$P_{\text{in-tot}} = P_{\text{loss-tot}} + P_{\text{load}},\tag{2}$$

where  $P_{\text{load}}$  is the useful output power. In terms of average input power measurements,  $P_{\text{in-tot}}$  can be expressed as the addition of the power-circuit input power (or the dc-link power),  $P_{\text{in}}$ , and gate-driver IC input power,  $P_{\text{in-GD}}$ :

$$P_{\text{in-tot}} = P_{\text{in}} + P_{\text{in-GD}}.$$

(3)

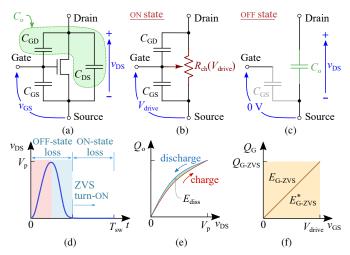

A FET model with its parasitic capacitances is shown in Fig. 1(a), highlighting the output capacitance. When the device is in ON state [Fig. 1(b)], a conduction loss,  $P_{\rm con}$ , occurs which is a function of the ON-state resistance of the device channel,  $R_{\rm ch}(V_{\rm drive}) = R_{\rm DS(on)}$ , and the channel current,  $i_{\rm CH}$ . Here,  $V_{\rm drive}$  is the voltage across the gate–source terminals of S,  $v_{\rm GS}$ , in fully-ON state. In the class-E inverter, which is a load-resonant soft-switching converter [19],  $C_{\rm o}$  gets charged and discharged during the OFF state [Fig. 1(c)] of the device. The corresponding  $v_{\rm DS}$  waveform is shown in Fig. 1(d). This charge–discharge process of  $C_{\rm o}$  results in a non-ideal hysteretic

Fig. 1. (a) Model of a FET showing its parasitic capacitances, where  $C_0 = C_{\rm GD} + C_{\rm DS}$  is defined as the output capacitance.  $C_0$  is inactive during (b) the ON state of the device; and gets charged and discharged during (c) the OFF state of the device for a class-E inverter, where (d) the drain-source voltage,  $v_{\rm DS}$ , shows a large-signal variation that generally occupies 50 % of the switching period,  $T_{\rm sw}$ . (e) Related variation of the output charge ( $Q_0$ ) with  $v_{\rm DS}$  is represented by a QV curve; different charging (red line) and discharging (blue line) paths result in a hysteresis energy loss,  $E_{\rm diss}$ , which is specified for a given maximum voltage  $V_p$  of  $v_{\rm DS}$ . (f) Gate of the device gets charged up to  $Q_{\rm G-ZVS}$  during the turn-ON transient and then gets discharged at the device turn-OFF, resulting in a total gate-energy-loss  $Q_{\rm G-ZVS} \cdot V_{\rm drive}$ .

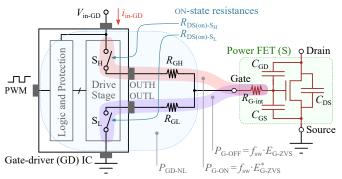

Fig. 2. An asymmetrical gate-driver IC has split outputs to control the turn-ON (through OUTH pin and  $R_{GH}$ ) and turn-OFF (through OUTL pin and  $R_{GL}$ ) processes of the power FET, S. In hard gating, the input power to the gatedriver IC,  $P_{in-GD}$ , is totally lost. This loss has two components: 1) losses inside the gate-driver IC, dominated by the switching losses of the drive-stage transistors S<sub>L</sub> and S<sub>H</sub>, and denoted as  $P_{GD-NL}$ ; 2) a gate loss  $P_{G-ON} + P_{G-OFF}$ in charging–discharging of the input capacitance of S.

energy loss,<sup>1</sup>  $E_{\text{diss}}$ , and can be calculated using a charge versus voltage (QV) curve as Fig. 1(e) indicates [7], [10]. The OFF-state losses related to the leakage current through the device channel are generally negligible, especially in comparison to  $E_{\text{diss}}$  losses for MHz-range frequencies [10]. Therefore, the total power loss is in S, at a switching frequency of  $f_{\text{sw}}$ , is given by (4), where  $P_{\text{diss}} = f_{\text{sw}} \cdot E_{\text{diss}}$ . Any loss related to gate driving is treated separately as shown next.

$$P_{\rm S} = P_{\rm con} + P_{\rm diss} \tag{4}$$

A typical gate-driver circuit consists of the gate-driver IC

$^{1}$ A similar phenomenon can be observed [20] for resonant-transition [21] converters; however, in that case, the charge and discharge processes occur during switching transitions (OFF-state  $v_{DS}$  is fixed at dc-link voltage).

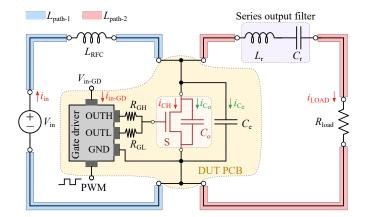

Fig. 3. Class-E inverter circuit. The transistor S and gate driver can be placed in a separate PCB, allowing the physical separation of the activeand passive-device losses in the circuit. The extra inductances ( $L_{\text{path}1}$  and  $L_{\text{path}2}$ ) of connecting wires introduced by this separation are simply added to the inductances of the RF choke  $L_{\text{RFC}}$  and the series output filter inductor  $L_{\tau}$ ; these inductors and the capacitor  $C_{\text{r}}$  account for  $P_{\text{passive}}$ . Important currents (total instantaneous) in the circuit are also marked.

(denoted as GD) and external resistances  $R_{GH}$  and  $R_{GL}$ , as Fig. 2 illustrates. From the perspective of the power transistor, the traditional gate-driving is hard-gated, i.e., the gate-driving path is an *RC* circuit and involves no inductive components to achieve resonant gate-driving [17]. For ZVS conditions, the total gate charge in S is denoted by  $Q_{G-ZVS}$  as Fig. 1(f) shows [22]. During the turn-ON transient of S, a power  $P_{G-ON} = f_{sw} \cdot E^*_{G-ZVS}$  is dissipated in the resistances  $R_{DS(on)-SH} + R_{GH} + R_{G-int}$  as marked by the area shaded in red in Fig. 2; and during the turn-OFF transient, a power  $P_{G-OFF} = f_{sw} \cdot E_{G-ZVS}$  is dissipated in the resistances are independent of the resistance values and are determined by  $Q_{G-ZVS}$ ,  $V_{drive}$  and  $f_{sw}$ . The complete gate loss ( $P_G$ ) is therefore given as

$$P_{\rm G} = P_{\rm G-ON} + P_{\rm G-OFF} = f_{\rm sw} (E_{\rm G-ZVS}^* + E_{\rm G-ZVS})$$

(5)

There exists another loss (marked by the area shaded in light blue in Fig. 2) that is often overlooked in the gate-driving process, which is related to the drive stage of the IC; the two transistors  $S_L$  and  $S_H$  are hard switched and thus create their own output-capacitance-related losses and gate losses [17]. It should be emphasized that this loss cannot be calculated from the power device characteristics as it is an attribute of the chosen gate-driver IC. In this work, we present a simple no-load method to measure this power loss, which is denoted here as  $P_{\text{GD-NL}}$ . Finally, the total power loss in gate driving is

$$P_{\text{in-GD}} = P_{\text{G}} + P_{\text{GD-NL}}.$$

(6)

## III. CLASS-E INVERTER AND LOSS DISTRIBUTION

In this section, the loss components introduced in Section II are identified with a class-E inverter circuit. The fundamental operation principles of this circuit are widely available in technical literature [2], [3], [6], [19], and hence, are not discussed here. Fig. 3 shows a detailed schematic of the circuit: the transistor S and the gate driver constitute  $P_{\text{active}}$ ; the input choke  $L_{\text{RFC}}$  and the series output filter consisting of  $L_{\text{r}}$  and  $C_{\text{r}}$

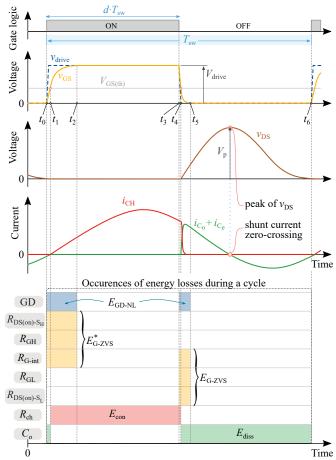

Fig. 4. Class-E circuit basic waveforms and time distributions of active-device energy losses during a switching cycle  $T_{sw} = 1/f_{sw}$ . Generally, the duty ratio *d* is kept at 0.5. The gate-driver output terminals OUTH and OUTL (see Fig. 2) determine the effective drive voltage  $v_{drive}$ . At  $t_0$ , OUTH is activated and  $v_{GS}$ rises. At  $t_1$ ,  $v_{GS}$  equals gate-source threshold voltage  $V_{GS(th)}$ : the device channel turns ON and  $i_{CH}$  starts to rise at ZVS conditions. At  $t_2$ , the charging process of device input capacitance ceases and the channel is fully enhanced. At  $t_3$ , OUTH is turned OFF and OUTL is activated:  $v_{GS}$  starts to decrease. At  $t_4$ ,  $v_{GS} = V_{GS(th)}$ : device channel is cut off,  $i_{CH}$  decreases rapidly, and  $v_{DS}$  rises charging  $C_0$ . At  $t_5$ ,  $v_{GS}$  approaches 0 V. The discharge of  $C_0$  ideally ceases at the next  $v_{GS} = V_{GS(th)}$  condition after  $t_6$ . The period  $t_1-t_4$  is considered as the effective conduction period of the device channel (energy loss =  $E_{con}$ ).

are responsible for  $P_{\text{passive}}$ . The total shunt capacitance consists of the transistor output-capacitance  $C_{\text{o}}$  and any external linear capacitance  $C_{\text{e}}$  added for optimum class-E operation.

The operation of the circuit is summarised in Fig. 4, highlighting how the energy losses related to the active devices in the circuit are distributed within a single switching cycle in steady state. The circuit is always operated in ZVS conditions ( $v_{DS} = 0$  V at  $t_1$  where  $v_{GS} = V_{GS(th)}$ ). The gate-driving losses occur during the turn-ON and turn-OFF switching transients. For the duration ( $t_1$ - $t_4$ ) of the conduction loss, it is assumed that the channel is fully enhanced with  $R_{ch} = R_{DS(on)}$ . The hysteresis energy loss  $E_{diss}$  in  $C_o$  occurs during the OFF state (ideally extends up to some part of the switching transient).

## IV. MEASUREMENT CONCEPT AND DESIGN

Referring to Fig. 3, it can be noticed that a physical separation of the heat generated due to  $P_{\text{active}}$  and  $P_{\text{passive}}$  is

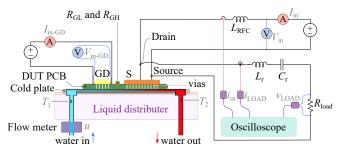

Fig. 5. Simplified block diagram of the presented measurement system showing the class-E inverter, the DUT PCB, and the application of calorimetric and electrical measurements. Two thermocouples (type K) measure the inlet and outlet temperatures,  $T_1$  and  $T_2$ , respectively. An Elveflow MFS-A-5 flow meter accurately measures the flow rate *u*.  $I_{in}$ ,  $V_{in}$ ,  $I_{in-GD}$  and  $V_{in-GD}$  are average electrical measurements carried out with Fluke 87V DMMs.  $i_{in}$  and  $i_{LOAD}$  are total instantaneous current measurements carried out with Tektronix TCP0030A current probes and a MSO68B oscilloscope.  $v_{LOAD}$  is measured with a Tektronix THDP0200A differential voltage probe.

possible with the class-E topology. This is the underlying principle of the proposed measurement approach for the accurate breakdown of losses. The device under test (DUT) and the gate driver can be placed in a single PCB that is separated from the rest of the circuit. This requires longer connecting cables as marked by  $path_1$  and  $path_2$ . The advantage of the class-E circuit is that  $L_{path_1}$  (and its related losses) is easily incorporated into  $L_{RFC}$ , and requires no further compensation. Similarly,  $L_{path_2}$  is added to  $L_r$ ; but as  $L_{path_2}$  alters the circuit operating conditions in this case, the circuit should be tuned to achieve optimum class-E operation.<sup>2</sup> The use of calorimetric and electrical measurements, together with the approach for the full-breakdown of losses are discussed in the following subsections with reference to the block diagram of the measurement system depicted in Fig. 5.

#### A. Calorimetric Measurements and Calorimeter Design

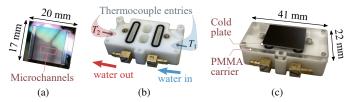

A novel and compact calorimetric unit [see Figs. 6(a) to 6(c) was designed to evaluate the active-device losses in the circuit. The heat generated in S and in GD (including the heat generated in  $R_{GL}$  and  $R_{GH}$ ) are extracted by a microchannelbased cold plate fabricated on a piece of silicon [see Fig. 6(a)], which is attached to the bottom of the PCB as Fig. 5 illustrates. A pressure controller is used to pass deionized water through the microchannels embedded in the cold plate [23]. The cold plate is brought in to good thermal contact with the circuit using thermal grease, which enables a high level of heat extraction in a small form factor [24]. This provides an additional benefit of cooling the active devices, permitting higher power dissipations without approaching critical temperatures. Due to its small size, the cold plate has a small heat capacity, resulting in short measurement times. The calorimeter evaluates the power dissipated on the PCB as

$$P_{\text{calori}} = \rho \, C_{\text{p}} \, u \, \Delta T. \tag{7}$$

Here,  $\rho$  is the density of the liquid with a specific heat of  $C_p$ ; and u is the flow rate of the liquid. The temperature difference

<sup>2</sup>This is achieved by adjusting one or a combination of the components  $C_e$ ,  $L_r$ ,  $C_r$  and  $R_{\text{load}}$  for a given  $f_{\text{sw}}$  [3].

Fig. 6. (a) A silicon microchannel-based cold plate and (b) a 3d-printed liquid distributor, with entries for water and thermocouples, are assembled as (c) a compact calorimeter and an efficient cooler.

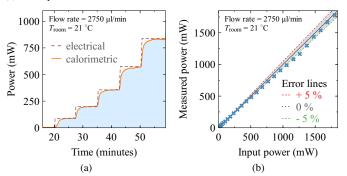

Fig. 7. (a) Example showing that the power loss measured with the developed calorimeter (solid line) approaches the dc input power  $V_{DS} \cdot I_{DS}$  (dashed lines) quite fast, allowing 6–7 measurements within an hour at the given flow rate; the calorimeter tracks power levels as low as 100 mW with very good accuracy. Here, the transistor S is in ON state and a dc current  $I_{DS}$  was passed through it, while measuring the dc drain–source voltage  $V_{DS}$  (a 4-point measurement was used) (b) Calorimeter measurements exhibit good agreement with the dc input power, keeping the error  $\approx 5 \%$ .

$(\Delta T = T_2 - T_1)$  between the outlet and inlet water is measured using two thermocouples [see Fig. 6(b)].

The accuracy of the calorimetric system was verified with a dc calibration as Fig. 7(a) shows. The power measured with the calorimeter approaches the value of the dc input power within a few minutes, where the error in measurement [Fig. 7(b)] is kept around 5 % for the whole power range, indicating very good accuracy. The system can measure a wide power range of 20 mW to 10 W; this is especially beneficial as  $E_{\text{diss}}$  vary quite significantly between different device structures and with  $f_{\text{sw}}$  [7]. A complete discussion on the design, operation and performance of the calorimeter is presented in a companion paper [23].

#### **B.** Electrical Measurements

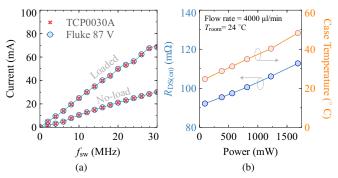

The power inputs to the gate-driver IC and the power circuit are measured with Fluke 87V digital multimeters (DMMs), whose average-mode specifications are listed in Table I [25]. The gate-driving loss is calculated as  $P_{\text{in-GD}} = V_{\text{in-GD}} \cdot I_{\text{in-GD}}$ , where  $V_{\text{in-GD}}$  is a dc quantity and is measured very accurately. The input current to the gate driver,  $i_{\text{in-GD}}$ , contains highfrequency components at  $f_{\text{sw}}$  and above. Fluke DMMs can measure the average value of this current,  $I_{\text{in-GD}}$ , with  $\mu$ Alevel accuracy, owing to an analogue 2-pole filter implemented before the ADC. The results from the DMM were verified by measuring  $I_{\text{in-GD}}$  using a Tektronix TCP0030A current probe. The two measurements exhibit very good agreement and are compared in Fig. 8(a).

The input power of the power circuit,  $P_{in} = V_{in} \cdot I_{in}$ , is evaluated using the same method of average electrical measure-

TABLE I

Specifications of Average Measurements with FLUKE 87V DMM

| Measurement                                                                              | Туре                                     | Used Range                           | Resolution                             | Accuracy <sup>1</sup>                                                                                         |

|------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|

| $\begin{matrix} V_{\rm in} \\ V_{\rm in-GD} \\ I_{\rm in} \\ I_{\rm in-GD} \end{matrix}$ | Average<br>Average<br>Average<br>Average | 0–600 V<br>0–6 V<br>0–6 A<br>0–60 mA | 0.1 V<br>0.001 V<br>0.001 A<br>0.01 mA | $\begin{array}{c} \pm (0.05 \% + 1) \\ \pm (0.05 \% + 1) \\ \pm (0.2 \% + 4) \\ \pm (0.2 \% + 4) \end{array}$ |

<sup>1</sup> For a measured value M, a  $\pm$  (X % + Y) accuracy means an absolute error of  $\pm$  [0.01MX + ( $Y \cdot$  Resolution)]. Note: resolution depends on the selected range.

ments (also see Fig. 5), where  $I_{in}$  is the average value of  $i_{in}$ . The load power is calculated as  $P_{load} = V_{LOAD(rms)} \cdot I_{LOAD(rms)}$ , where the instantaneous load voltage ( $v_{LOAD}$ ) and current ( $i_{LOAD}$ ) are measured using a Tektronix THDP0200 voltage probe and a TCP0030A current probe, respectively.<sup>3</sup> The specifications of the current and voltage probes are tabulated in Table II. For amplitude measurements, the probes and the oscilloscope system retain an error < 3 %, up to 30 % of its specified bandwidth [26].

#### C. Approach for Full Breakdown of Converter Losses

First, the total power loss in the system and the passivedevice loss is evaluated. With  $P_{in}$ ,  $P_{in-GD}$  and  $P_{load}$  available, using (2) and (3) the total power loss in the system is

$$P_{\text{loss-tot}} = P_{\text{in}} + P_{\text{in-GD}} - P_{\text{load}}.$$

(8)

As  $P_{\text{active}}$  is directly measured with the calorimeter, the passive-device loss can be calculated according to (1):

$$P_{\text{passive}} = P_{\text{loss-tot}} - P_{\text{active}}.$$

(9)

The active-device losses are further separated to the four components detailed in (4) and (6) as follows. First the total power loss in the transistor is calculated as

$$P_{\rm S} = P_{\rm active} - P_{\rm in-GD}.$$

(10)

The transistor conduction loss is then separately calculated as

$$P_{\rm con} = f_{\rm sw} \cdot R_{\rm DS(on)} \int^{T_{\rm ON}} i_{\rm CH}^2 dt, \qquad (11)$$

where  $T_{ON}$  is the ON period of S, which is experimentally measured by observing the  $v_{DS}$  waveform (a TPP1000 passive probe was used). The value of  $R_{DS(on)}$  is experimentally evaluated using dc electrical measurements as shown in Fig. 8(b). For the device ON resistance of GaN devices, dynamic  $R_{DS(on)}$ degradation should be considered when (11) is evaluated [27], [28]. The specific application of this effect to the class-E circuit is discussed in Section V.

For the ON state of S, the channel current is calculated as  $i_{\text{CH}} = i_{\text{in}} - i_{\text{LOAD}}$  (no current passes through  $C_{\text{o}}$  or  $C_{\text{e}}$  as  $v_{\text{DS}} = 0$  V). Using (4), hysteresis energy loss of  $C_{\text{o}}$  is calculated as

$$E_{\rm diss} = \frac{P_{\rm S} - P_{\rm con}}{f_{\rm sw}}.$$

(12)

<sup>3</sup>We have verified the accuracy of current and voltage measurements by calculating  $P_{\text{load}}$  using  $V_{\text{LOAD}(\text{rms})}^2/R_{\text{load}}$  and  $I_{\text{LOAD}(\text{rms})}^2 \cdot R_{\text{load}}$ , where an impedance analyser was used to measure  $R_{\text{load}}$ . This testing shows that as the load voltage is near-sinusoidal in class-E inverters, both current and voltage probes perform well even at high frequencies such as 10 MHz.

Fig. 8. (a) Variation of average input current  $I_{\rm in-GD}$  going into the gatedriver IC (a UCC27511A IC is used) with  $f_{\rm sw}$ . Measurements with a Fluke DMM and a Tektronix TCP0030A current probe are compared. Both noload (no S is soldered to the PCB) and loaded conditions (S is a GS66504B device) are shown. (b) Device dc ON-state resistance ( $R_{\rm DS(on)} = V_{\rm DS}/I_{\rm DS}$ ) is experimentally determined using 4-point dc measurements to calculate the conduction loss in S—see (11). The case temperature of S, measured with an IR camera, is also indicated.

One could consider using the multiplication of instantaneous shunt-capacitance current ( $i_{C_o} + i_{C_e} = i_{in} - i_{LOAD}$  in OFF state) and voltage ( $v_{DS}$ ) waveforms for the duration of the OFF period to evaluate  $E_{diss}$ . As this approach takes the difference of two similar values (as  $v_{DS}$  is always positive and the current crosses zero at  $V_p$ —see Fig. 4), it could result in a large error,<sup>4</sup> especially at high  $f_{sw}$ , for which the switching periods are in the range of probe propagation-delay times.

To separate the gate-driving losses according to (6),  $P_{\text{GD-NL}}$  is individually evaluated by measuring the gate-driving loss on an exact replica of the DUT PCB, but without soldering the transistor S. Then, when the gate-driver is switched at  $f_{\text{sw}}$ , its measured input power solely represents  $P_{\text{GD-NL}}$ . Consequently, the device gate-loss is evaluated as

$$P_{\rm G} = P_{\rm in-GD} - P_{\rm GD-NL}.$$

(13)

#### V. EXPERIMENTAL SYSTEM, RESULTS, AND DISCUSSION

In this section, the developed measurement concept is applied to identify individual loss components in a class-E inverter circuit operating at 10 MHz.

#### A. Experimental Procedure

A GaN Systems GS66504B GaN HEMT was used as the transistor and a Texas Instruments UCC27511A IC was used as the gate driver (details are listed in Table III). The passive components were calculated using the design equations derived by Sokal [3] and the final tuned-values are tabulated in Table IV. The external shunt-capacitance  $C_e$  and series-filter capacitance  $C_r$  are multi-layer-ceramic (MLC) capacitors with a COG (NP0) dielectric and have high quality-factors. The load resistance has a temperature coefficient of resistance (TCR) of 100 ppm/K, and thus, its variation within the operating temperatures here is negligible. The implementation of the

© 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

$<sup>^{4}</sup>$ The significance of the error is dependent on  $f_{sw}$ , and voltage and current probe characteristics. The input impedance (frequency dependent) of the voltage probe is an important factor here as a certain level of device-branch-current could pass through it. These factors require further investigations.

| TABLE II                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------|

| $Specifications \ of \ Measurements \ Carried \ out \ with \ Tektronix \ MSO68B-Oscilloscope \ and \ Probe \ System$ |

| Probe                           | Bandwidth                   | Measurement                                                                 | Туре                                                              | Used Range                  | Sensitivity     | Gain Accuracy                      | @ 10 MHz <sup>1</sup>                                                  |                                                                                        |

|---------------------------------|-----------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|-----------------|------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                 |                             |                                                                             |                                                                   |                             |                 |                                    | Input Impedance                                                        | Derating Starts at                                                                     |

| TCP0030A<br>THDP0200<br>TPP1000 | 120 MHz<br>200 MHz<br>1 GHz | i <sub>in</sub> , i <sub>LOAD</sub><br><sup>v</sup> LOAD<br>v <sub>DS</sub> | Total instantaneous<br>Total instantaneous<br>Total instantaneous | 0–5 A<br>0–150 V<br>0–300 V | 1 mA<br>_2<br>- | 1 % (dc typ.)<br>2 % (dc)<br>2.2 % | $\approx 0.1 \ \Omega$ $\approx 4.8 \ k\Omega$ $\approx 4.1 \ k\Omega$ | 4 A <sub>peak</sub><br>80 V <sub>rms</sub><br>160–200 V <sub>ac-rms</sub> <sup>3</sup> |

<sup>1</sup> Values approximated from the specification-sheet curves; <sup>2</sup> A vertical resolution can be considered, Resolution = Full-Scale Range / No. of Bits;  ${}^{3}v_{DS}$  measurement is carried out for a very short duration of time.

TABLE III LIST OF ACTIVE COMPONENTS

| Component                          | Part No.              | Specifications                                                                             |

|------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|

| Transistor (S)<br>Gate driver (GD) | GS66504B<br>UCC27511A | 650 V, 15 A, 100 mΩ<br>Split output, 4.5–18 V, 4-A source,<br>8-A sink, SOT-23 (6) package |

| TABLE IV                   |

|----------------------------|

| LIST OF PASSIVE COMPONENTS |

| Component       | Value  | Unit    | Remarks                                     |

|-----------------|--------|---------|---------------------------------------------|

| R <sub>GH</sub> | 4.7    | Ω       | 0402 package, 1/5 W, 1%                     |

| R <sub>GL</sub> | 1      | Ω       | 0402 package, 1/5 W, 1%                     |

| Rload           | 25     | Ω       | Ohmite TGHMV25R0JE, ±100 ppm/K,             |

|                 |        |         | 0.23 °C/W, #187 tab terminals               |

| $L_{\rm RFC}$   | 10.8   | $\mu H$ | Air core, at 10 MHz, quality factor = 300   |

| $L_{\rm r}$     | 4.44   | μH      | Air core, at 10 MHz, quality factor = $343$ |

| $C_{\rm r}$     | 56.9   | pF      | NP0 MLC capacitors, 1111 package            |

| C <sub>e</sub>  | 0-40.5 | pF      | NP0 MLC capacitors, 1111 package            |

Notes:  $C_e$  and  $C_r$  are high-Q / low-ESR non-magnetic multi-layer ceramic (MLC) capacitors with a COG (NP0) dielectric, from Johanson Technology (E-series).  $L_{RFC}$  and  $L_r$  are made with 20-AWG and 14-AWG magnet wires, respectively. Inductance and quality factor values are measured with a Keysight 4990A impedance analyser and a 16047E test fixture.  $L_{path-2}$  (Fig. 3) was measured to be around 410–420 nH at 10 MHz.

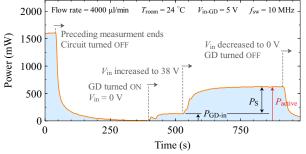

circuit and the complete measurement system is shown in Fig. 9. An example of using the calorimeter to measure  $P_{\text{active}}$  is presented in Fig. 10: after the DUT board cools down from a preceding measurement, first the gate-driver circuit is turned ON and PWM is applied while  $V_{\text{in}} = 0$  V; then  $V_{\text{in}}$  is gradually increased to the target operating mode. Once the thermal steady state is reached,  $P_{\text{active}}$  value is recorded.

One major aim of this work is to evaluate  $E_{\rm diss}$  as a function of  $V_{\rm p}$  for a given transistor, which is achieved by varying the input voltage of the circuit.  $V_{\rm p}$  values of 100 to 300 V, at 50 V steps, were considered. The ZVS conditions were maintained by changing the value of  $C_{\rm e}$  for  $V_{\rm p} \ge 200$  V, while d = 0.5was maintained. For  $V_{\rm p} \le 200$  V,  $C_{\rm e}$  was 0 and d was slightly adjusted from 0.5 to achieve ZVS conditions.

#### B. Experimental Results and Discussion

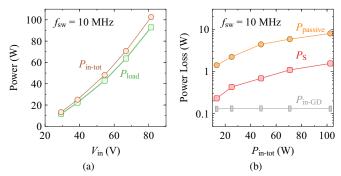

Fig. 11(a) shows the total input power and the load power for different  $V_{in}$  values (at  $f_{sw} = 10$  MHz). An input power of 102.6 W is reached for  $V_{in} = 81.4$  V, which corresponds to a  $V_p$  of 300 V. Fig. 11(b) shows the breakdown of the corresponding power losses in the converter into passivedevice, transistor, and gate-driving losses. The passive-device losses are predominant and increase with the input power due to the increased average current in  $L_{RFC}$  and RMS current in  $L_r$ . The latter is responsible for the largest contribution as it is

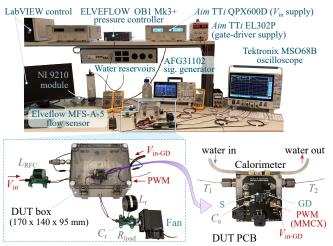

Fig. 9. Complete experimental system highlighting the measurement equipment and probes, calorimeter control system, class-E inverter circuit components, and the PCBs. The two active devices in the circuit (S and GD) and  $C_e$  are built into a separate DUT PCB. A Tektronix AFG31102 signal generator is used to generate the PWM signals. For  $P_{active}$  measurement, a LabVIEW-based control system is utilized: set the flow rate using a pressure controller, read the actual flow-rate using flow sensor; record the thermocouple readings  $T_1$  and  $T_2$ ; calculate  $P_{active}$  in real time.

Fig. 10. Example showing the application of the developed calorimeter to measure  $P_{\text{active}}$  of the designed class-E inverter: the distinction between the gate-driving loss and the transistor losses is also observed.

subjected to a large ac current, hence increasing its ac winding losses; on the other hand,  $L_{RFC}$  experiences a relatively small ac ripple as the input current is nearly dc in the topology.

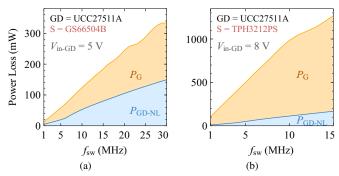

The gate-driving loss  $P_{in-GD}$  stays constant, approximately around 120 mW [see Fig. 11(b)]; this result is expected as  $f_{sw}$ was fixed and ZVS conditions were maintained at each power level. Based on the measurement concepts presented in Section IV, this loss is divided into  $P_{GD-NL}$  and  $P_G$  in Fig. 12(a), where a wide switching-frequency is investigated. At 10 MHz, the loss distribution is such that  $P_{GD-NL} = 52.7$  mW and  $P_G =$ 71.1 mW, i.e., for this combination of S and GD,  $P_{GD-NL}$ amounts for 40 % of total gate-driving loss. For comparison,

Fig. 11. Experimental results for the designed class-E inverter (see Table III and Table IV) operating at f = 10 MHz. (a) Variation of the total input power,  $P_{\text{in-tot}}$ , and the load power,  $P_{\text{load}}$ , with input voltage. (b) Breakdown of the losses with  $P_{\text{in-tot}}$ : the gate-driving loss  $P_{\text{in-GD}}$ , transistor loss  $P_{\text{S}}$  and passive-device losses  $P_{\text{passive}}$ . The presented method is capable of measuring mW-range power levels, enabling accurate loss and efficiency calculations.

Fig. 12. Distribution of gate-driving loss components (hard-gating) with  $f_{sw}$  for two different transistors. In MHz-range and high-efficiency resonant power converters, the gate-driver loss cannot be neglected. For the GS66504B device,  $P_{GD-NL}$  is around 40 % of  $P_{in-GD}$ . Relevant equations are:  $P_{in-GD} = P_G + P_{GD-NL}$  and  $P_G = P_{G-OFF}$ .

results for a Transphorm TPH3212PS GaN HEMT, which is a cascode structure, is shown in Fig. 12(b). Here,  $P_{\text{GD-NL}}$ amounts for only 10–12 % of total gate-driving loss as the power transistor has a much higher input capacitance.

Referring to Fig. 11(b), it is observed that the losses in the transistor also increase with  $P_{\text{in-tot}}$ . This is due to two reasons. On the one hand, the conduction loss increases with  $V_{\text{in}}$  (or  $P_{\text{in-tot}}$ ) because of the increased RMS current through S—note that  $R_{\text{DS-on}}$  of S does not vary significantly (stays around 100 m $\Omega$ ) for the considered power-dissipation range [see Fig. 8(b)]. On the other hand, the OFF-state loss increases with  $V_{\text{in}}$ , or more specifically with  $V_{\text{p}}$ , due to the hysteresis loss that occurs in  $C_{\text{o}}$  while it is being charged and discharged during the OFF-state in each cycle.

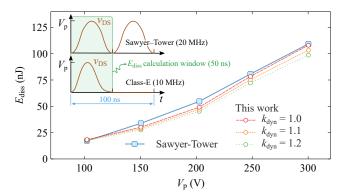

Recent works have reported that for soft-switching circuits, dynamic  $R_{DS(on)}$  shows a smaller degradation in contrast to hard-switching circuits [27], [29]. However, such studies do not consider the particular OFF-state conditions imposed on the switch by the class-E circuit. To investigate this, we have considered the effect of an increase up to 20 % in the measured dc  $R_{DS(on)}$  value, based on recent works [29]. Fig. 13 plots the corresponding  $E_{diss}$  values, where  $R_{DS(on)}$  in (11) is multiplied by a positive factor  $k_{dyn}$  to evaluate  $P_{con}$ . The corresponding Sawyer–Tower results, reported by Zulauf et al. [8], are also marked (in solid blue). The comparison reveals that, as the

Fig. 13. Variation of output-capacitance hysteresis losses with  $V_p$  for the GS66504B transistor in actual converter operation at 10 MHz.  $k_{dyn} = 1.0, 1.1$  and 1.2 correspond to 0, 10, and 20 % increase in the  $R_{DS(on)}$  value (measured in dc conditions) to investigate dynamic  $R_{DS(on)}$  effects. The corresponding Sawyer–Tower results are marked in solid blue (from Zulauf et al. [8]). Note that the  $v_{DS}$  waveform of a class-E inverter at 10 MHz with d = 0.5 has a 50 ns of charge–discharge time for  $C_0$ ; this corresponds to a Sawyer–Tower excitation at 20 MHz.

value of  $k_{dyn}$  increases, the measured  $E_{diss}$  value deviates from the Sawyer-Tower results, suggesting that dynamic  $R_{DS(on)}$ degradation is much smaller in class-E circuit compared to other circuits [27], [28]. This could be explained by the short duration of the peak OFF-state-voltage in class-E circuit, which can create different charging dynamics during the OFF state; however more studies are needed to understand such effects.

Note that although the circuit operates at  $f_{sw}$  of 10 MHz ( $T_{sw} = 100$  ns), the actual charging–discharging event of  $C_o$  corresponds to a duration of 50 ns (for d = 0.5), or an effective frequency of 20 MHz (see Fig. 13). Therefore, the Sawyer–Tower results at 20 MHz should be used for comparison to get a similar charge–discharge frequency, as most GaN devices show a frequency dependence for  $E_{diss}$  [7], [8]. In addition,  $C_e$  is subjected to the same voltage swing as  $C_o$ . Since  $C_e$  was chosen to have a low equivalent-series-resistance (ESR), any ESR losses can be assumed negligible for the considered RMS current through the device branch; this assumption was validated by the observation of insignificant temperature rise in  $C_e$  during the circuit operation for all power levels.

Fig. 14 breaks down the active-device losses at  $f_{sw} = 10$  MHz into the four main components described in (4) and (6) for the case of  $V_{in} = 81.4$  V (or equivalently  $V_p = 300$  V). The results reveal that  $P_{diss}$  dominates active-device losses with a contribution of 64.28 %, which amounts to 1.08 W. This observation demonstrates the major implication of output-capacitance hysteresis losses in MHz-range operation, inhibiting the ideal advantages of zero switching-losses (or OFF-state losses) offered by soft-switching operation. It is also important to note that the gate-driving losses in total amount to 7.82 % of  $P_{active}$ , which is not negligible.

This comprehensive breakdown of active-device losses aids the power electronic circuit designer to identify the causes for losses and choose the best transistor and gate-driver IC combination for the most favourable design. The measurement approach can be extended to other resonant converter circuits, but the complexity depends on the topology. For example, in an LLC half-bridge resonant converter [30], the PCB heats

Fig. 14. Complete breakdown of the active-device average power losses in the tested class-E inverter at 10 MHz. Here, total active-device loss  $P_{\text{active}} = 1.68$  W, total input power  $P_{\text{in-tot}} = 102.6$  W and  $V_{\text{in}} = 81.4$  V. S is a GS66504B GaN HEMT and GD is a Texas instrument UCC27511A IC.  $C_{\text{o}}$ -hysteresis loss is the major contributor accounting for 64.28 % of losses. These results are based on in-circuit measurements (without using any estimation based on indirect measurements) and therefore represent actual operating losses.

up due two transistors. A single gate-driver can be used by employing a bootstrap method for direct  $P_{\text{in-GD}}$  measurement. And dead-time should not extend much beyond the required minimum value to avoid errors in conduction loss calculations.

#### VI. CONCLUSIONS

We have demonstrated a complete loss-breakdown concept for a class-E inverter. The presented ideas allow to compare and separate the active-device losses into transistor ON- and OFF-state losses, as well as gate and internal-gate-driver losses. An experimental method with mW-level precision is presented and utilized to measure these losses at 10 MHz. The approach provides an accurate and in-converter evaluation of the hysteresis losses related to the output-capacitance of transistors. It was shown that the distinction between transistor-related gate loss and the driver-related internal loss is important for the loss characterization of MHz-range converters.

### ACKNOWLEDGMENT

The first author would like to thank Pietro Bianco from Linktronix and Gilles Clermont from Tektronix for their technical advice and support.

#### References

- [1] G. D. Ewing, "High-efficiency radio-frequency power amplifiers," Ph.D. dissertation, Oregon State University, 1964.

- [2] N. Sokal and A. Sokal, "Class E-A new class of high-efficiency tuned single-ended switching power amplifiers," *IEEE Journal of Solid-State Circuits*, vol. 10, no. 3, pp. 168–176, Jun. 1975.

- [3] N. O. Sokal, "Class-E RF Power Amplifiers," *Qex 204.1 (2001)*, pp. 9–20., 2001.

- [4] A. Grebennikov and F. H. Raab, "A History of Switching-Mode Class-E Techniques: The Development of Switching-Mode Class-E Techniques for High-Efficiency Power Amplification," *IEEE Microwave*, vol. 19, no. 5, pp. 26–41, Jul. 2018.

- [5] A. Lidow, J. Strydom, M. de Rooij, and D. Reusch, GaN Transistors for Efficient Power Conversion, 2nd ed. Wiley, Sep. 2014.

- [6] K. N. Surakitbovorn and J. M. Rivas-Davila, "On the Optimization of a Class-E Power Amplifier With GaN HEMTs at Megahertz Operation," *IEEE Trans. Power Electron.*, vol. 35, no. 4, pp. 4009–4023, Apr. 2020.

- [7] N. Perera, A. Jafari, L. Nela, G. Kampitsis, M. S. Nikoo, and E. Matioli, "Output-Capacitance Hysteresis Losses of Field-Effect Transistors," in 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Nov. 2020, pp. 1–8.

- [8] G. Zulauf, S. Park, W. Liang, K. N. Surakitbovorn, and J. Rivas-Davila, "Coss Losses in 600 V GaN Power Semiconductors in Soft-Switched, High- and Very-High-Frequency Power Converters," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10748–10763, Dec. 2018.

- [9] J. B. Fedison and M. J. Harrison, "Coss hysteresis in advanced superjunction MOSFETs," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2016, pp. 247–252.

- [10] N. Perera, G. Kampitsis, R. van Erp et al., "Analysis of Large-Signal Output Capacitance of Transistors Using Sawyer–Tower Circuit," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 3, pp. 3647–3656, Jun. 2021.

- [11] D. Koch, S. Araujo, and I. Kallfass, "Accuracy Analysis of Calorimetric Loss Measurement for Benchmarking Wide Bandgap Power Transistors under Soft-Switching Operation," in 2019 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), May 2019, pp. 1–6.

- [12] D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10-kV SiC mosfets and Diodes," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5240–5250, Jun. 2018.

- [13] A. Jafari, M. Heijnemans, R. Soleimanzadeh *et al.*, "High-Accuracy Calibration-Free Calorimeter for the Measurement of Low Power Losses," *IEEE Transactions on Power Electronics*, vol. 36, no. 1, pp. 23–28, Jan. 2021.

- [14] B. Sun, Z. Zhang, and M. A. E. Andersen, "A Comparison Review of the Resonant Gate Driver in the Silicon MOSFET and the GaN Transistor Application," *IEEE Trans. on Ind. Applicat.*, vol. 55, no. 6, pp. 7776– 7786, Nov. 2019.

- [15] Y. Chen, F. Lee, L. Amoroso, and H.-P. Wu, "A resonant MOSFET gate driver with efficient energy recovery," *IEEE Transactions on Power Electronics*, vol. 19, no. 2, pp. 470–477, Mar. 2004.

- [16] A. Jafari, M. S. Nikoo, N. Perera, F. Karakaya, R. Soleimanzadeh, and E. Matioli, "Small-Signal Approach for Precise Evaluation of Gate Losses in Soft-Switched Wide-Band-Gap Transistors," in 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Nov. 2020, pp. 1–5.

- [17] T. Lopez, G. Sauerlaender, T. Duerbaum, and T. Tolle, "A detailed analysis of a resonant gate driver for PWM applications," in *Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition*, 2003. APEC '03., vol. 2, Feb. 2003, pp. 873–878 vol.2.

- [18] M. Kazimierczuk and K. Puczko, "Exact analysis of class E tuned power amplifier at any Q and switch duty cycle," *IEEE Trans. Circuits Syst.*, vol. 34, no. 2, pp. 149–159, Feb. 1987.

- [19] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Converters, Applications, and Design*, 3rd ed. Hoboken, NJ: John Wiley & Sons, 2003.

- [20] M. Kasper, R. M. Burkart, G. Deboy, and J. W. Kolar, "ZVS of Power MOSFETs Revisited," *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp. 8063–8067, Dec. 2016.

- [21] M. Bellar, T. Wu, A. Tchamdjou, J. Mahdavi, and M. Ehsani, "A review of soft-switched DC-AC converters," *IEEE Transactions on Industry Applications*, vol. 34, no. 4, pp. 847–860, Jul. 1998.

- [22] W. Zhang, "Gate Driver Design from Basics to Details," Texas Instruments, https://training.ti.com/gate-driver-design-basics-details, 2018.

- [23] R. van Erp, N. Perera, and E. Matioli, "Microchannel-based Calorimeter for Rapid and Accurate Loss Measurements on High-efficiency Power Converters," in 13th Annual IEEE Energy Conversion Congress and Exposition (ECCE 2021), October 2021, in press.

- [24] R. van Erp, G. Kampitsis, and E. Matioli, "Efficient Microchannel Cooling of Multiple Power Devices With Compact Flow Distribution for High Power-Density Converters," *IEEE Transactions on Power Electronics*, vol. 35, no. 7, pp. 7235–7245, Jul. 2020.

- [25] "Fluke 83V and 87V Digital Multimeters," Fluke, https://damassets.fluke.com/s3fs-public/2161164\_6116\_ENG\_B\_W.PDF.

- [26] "ABCs of Probes-Primer," Tektronix, 2016.

- [27] G. Zulauf, M. Guacci, and J. W. Kolar, "Dynamic on-Resistance in GaN-on-Si HEMTs: Origins, Dependencies, and Future Characterization Frameworks," *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 5581–5588, Jun. 2020.

- [28] A. Jafari, M. S. Nikoo, N. Perera *et al.*, "Comparison of Wide-Band-Gap Technologies for Soft-Switching Losses at High Frequencies," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 12595–12600, Dec. 2020.

- [29] O. C. Spro, D. Peftitsis, O.-M. Midtgard, and T. Undeland, "Modelling and quantification of power losses due to dynamic on-state resistance of GaN E-mode HEMT," in 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Jul. 2017, pp. 1–6.

- [30] H. Huang, "Designing an LLC Resonant Half-Bridge Power Converter," Texas Instruments Power Supply Design Seminar SEM1900, 2010.