Deep-UV approaches and printing of indium zinc oxide thin-film transistors targeting their processing on thermosensitive substrates

Présentée le 10 décembre 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire des microsystèmes pour les technologies spatiales Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Alessio MANCINELLI

Acceptée sur proposition du jury

Prof. J. Brugger, président du jury

Dr D. Briand, directeur de thèse

Dr N. Marjanovic, rapporteur

Dr E. Smits, rapporteur

Prof. G. Villanueva, rapporteur

Omnia quae nunc vetustissima creduntur, nova fuere.

– Publio Cornelio Tacito

# Acknowledgements

I would like to express my most sincere gratitude to Dr. Danick Briand, who gave me the precious opportunity to be a member of his research group and to be involved in this challenging yet stimulating topic. I really appreciated your passion for science, your suggestions for improvement, and the scientific discussion we had in these four years. Thank you for your availability, your guidance throughout my doctoral study, and your continued support.

I am grateful to the members of my Ph.D. jury, Prof. Jürgen Brugger, Prof. Guillermo Villanueva, Dr. Edsger Smits, and Dr. Nenad Marjanovic, for having accepted to read and evaluate this thesis.

I would like to thank all the colleagues of the FOxIP project, especially Dr. Sami Bolat and Dr. Yaroslav Romanyuk, for their collaboration and the proficient talks we had these years.

Special thanks go to Saleem Khan and Alexis Marette, who helped me at the beginning of this journey with their guidance and their friendship.

A mention for my office mates Ryan van Dommelen and Silvia Demuru, it was great to spend the time in the office between scientific discussions and laugh, it really made this journey easier and noisier.

A huge thanks go to Jaemin Kim, a great colleague, always available and ready to help. I'm really grateful for our scientific discussions and your support, it really allowed me to reach this goal.

Working at LMTS, Microcity, EPFL has been a great experience, mainly thanks to the lab's people and their spirit. I would like to thank Juan Zarate, Christine de Saint-Aubin, Samuel Schlatter, Xiaobin Ji, Francesca Sorba, Mathias Imboden, Alexandre Poulin, Ulas Adiyan, Rubaiyet Haque, Vito Cacucciolo, Edouard Leroy, Jean-Baptiste Chossat, Krishna Manaswi Digumarti, Robert Marius Hennig, Ronan Julien Hinchet, Djen Timo Kühnel, Brince Paul Kunnel, Michael James Henry Smith, Fabio Beco Albuquerque, Valentin Py, Sylvain Thomas Schaller, Giulio Grasso, James Alec Pierce Bourely, Nicolas Francis Fumeaux, Min Gao and Morgan Monroe. (I hope I didn't forget anyone)

I would also like to thank Prof. Herbert Shea that made such an ideal working environment possible. Moreover, a special thank goes to the best-secretary-ever Myriam Poliero, for her kindness and availability.

Thanks to all my friends, scattered all over Italy and the globe, Matteo, Luca, Andrea, Tommaso, Flavio, Giuseppe, Gianmarco, Paolo, Giovanni, Ilario, Marco....(I would never finish) Thanks to Leandro for the long talks and the support during these years. Grazie Champ.

I'm really grateful to my family, my parents Fabrizio and Michelina, that always supported me, and my sisters, Giulia and Barbara. Thanks also to my grandma, my grandpa, all my uncles, cousins, to Papzzoland... Thank you all for your love.

Last but not least, my wife Elena, thank you. I feel really blessed to have you always on my side.

| Grazie | а | tutti, |

|--------|---|--------|

|        |   |        |

Alessio

Neuchâtel, 24 September 2021

## **Abstract**

Novel metal-oxides (MO<sub>x</sub>) semiconductors for thin-film transistors (TFTs) are being developed as they can offer superior electric performances over organic-based counterparts. MO<sub>x</sub> TFTs processed on foil could be exploited in smart labels as RFID and NFC tags, flexible wearable devices, interfaced with or like sensors for personalized healthcare, fulfilling the demand for device integration in daily life products. However, their current processing conditions do not enable large-area manufacturing on commonly used substrates in printed electronics, such as thermosensitive polyethylene-based foils, preventing their cost-effective diffusion in consumer and logistic products. This thesis addresses the solution processing at low temperature (<200°C), via deep-UV enhanced synthesis, of metal-oxide-based TFTs and their additive manufacturing, including ink development and printing, and TFT fabrication and characterization.

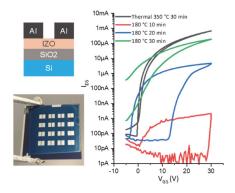

First, we present bottom gated TFTs made from a novel, fully solution-processed IZO/AlO<sub>x</sub>-based stack. On silicon, we studied how thermally annealed IZO (200–450°C) interacts with high-k AlO<sub>x</sub>-based spin-coated and vacuum-deposited dielectrics by evaluating TFT performances and IZO chemical composition. The optimal material match in the sol-gel-based stack processed at 450°C resulted in superior interface and TFTs overperforming their ALD counterparts,  $\mu$ ~26cm²/Vs,  $I_{on}/I_{off}$ ~10<sup>6</sup> versus  $\mu$ ~4cm²/Vs,  $I_{on}/I_{off}$ ~10<sup>4</sup>. Finally, fully solution-processed metal-oxide TFTs at high temperature were achieved by implementing photolithography, resulting in high-performance devices with  $\mu$ ~68cm²/Vs and  $I_{on}/I_{off}$  ratio>10<sup>9</sup>, comparable with state-of-the-art sputtered devices.

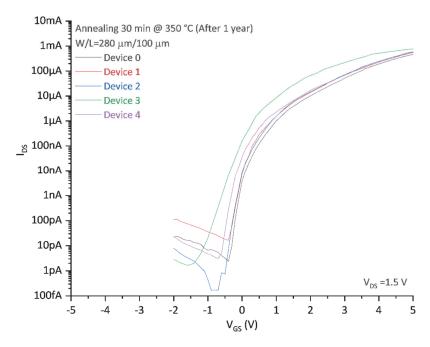

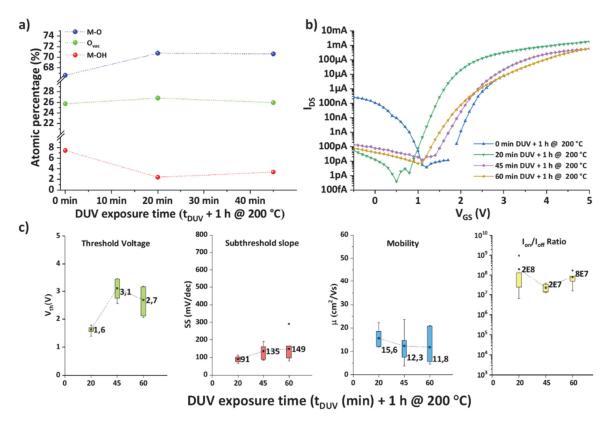

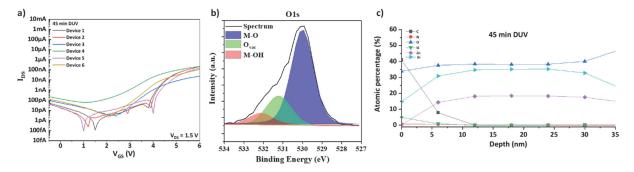

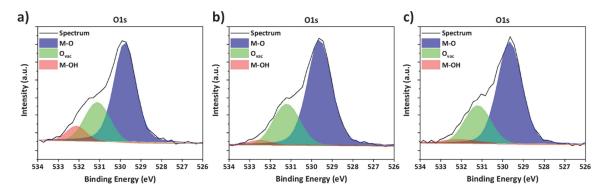

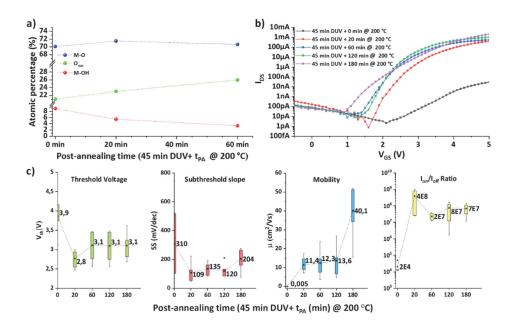

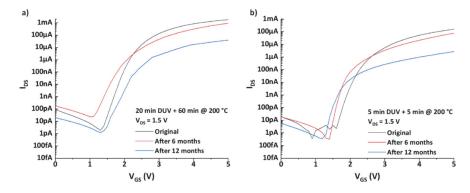

Then, we implemented a DUV-enhanced protocol for the synthesis of spin-coated IZO semiconductor and printed  $AlO_x/YAlO_x$  dielectric at a low temperature of 200°C. Prolonged DUV exposure (1h) and thermal annealing (3h) yielded TFTs with  $\mu$  as high as ~40cm²/Vs. By studying the effects of the process parameters on IZO chemical composition and TFTs characteristics, the IZO synthesis time was shortened to ~1h while maintaining excellent performances such as  $\mu$ ~16cm²/Vs,  $l_{on}/l_{off}>10^8$ , and SS<100mV/dec. Ultimately, we demonstrated a protocol as short as 10min at 200°C capable of yielding TFTs with mobility of ~3cm²/Vs,  $l_{on}/l_{off}>10^8$ , and SS<100mV/dec, stable after one year without passivation.

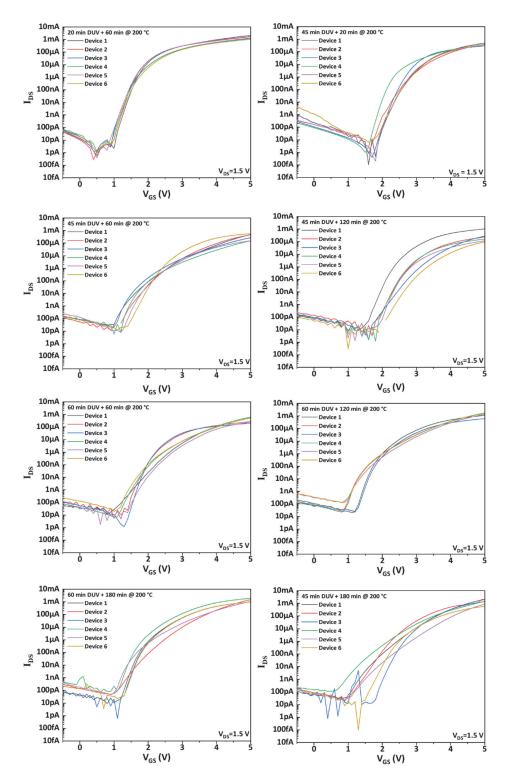

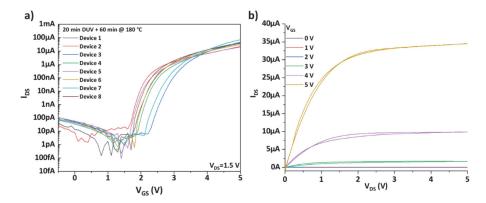

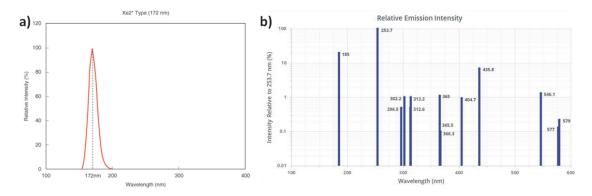

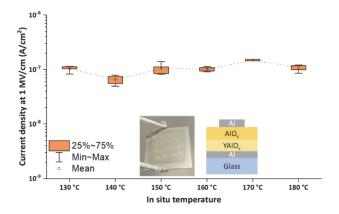

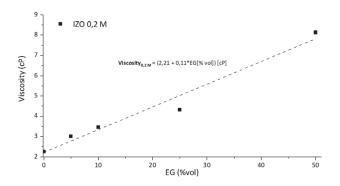

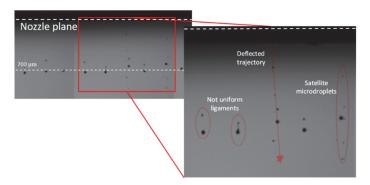

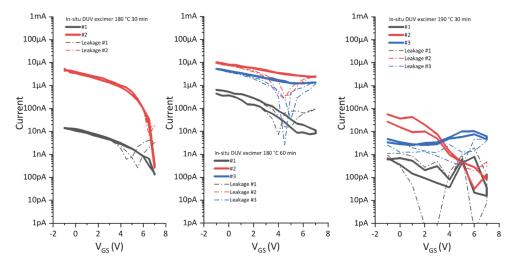

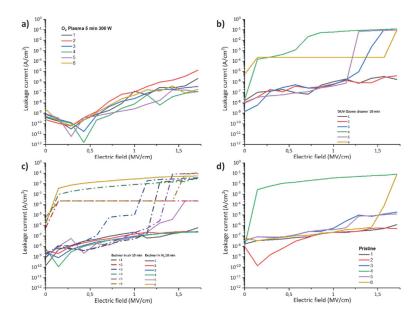

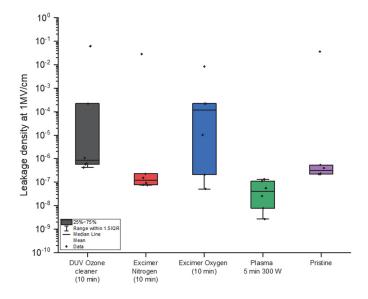

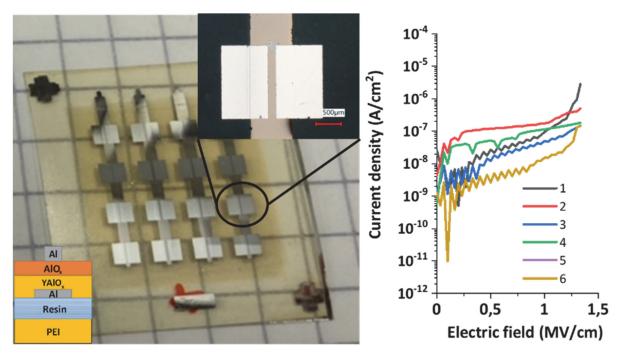

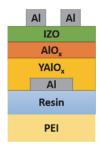

Aiming at further reducing the thermal budget, we explored an in-situ DUV excimer synthesis approach and inkjet printing of the  $MO_x$  functional layers. First, DUV excimer was implemented on the  $AlO_x/YAlO_x$  dielectric, demonstrating at a very low processing temperature of 130°C, capacitors (MIM) exhibiting leakage currents of about  $10^{-7}A/cm$  at 1MV/cm. We proposed and validated a process flow to integrate these MIMs on flexible foil, resulting in operative MIMs with a printed  $AlO_x/YAlO_x$  dielectric on PEI foil. We developed an IZO ink and studied composition influences on printability and TFT performance when synthesized at temperatures below 200°C. The combination of DUV excimer treatment at 180°C with an optimized IZO ink formulation and printing process resulted in TFTs with  $\mu$ >1cm²/Vs. Finally, thermally annealed TFTs with printed  $MO_x$  functional stack exhibiting  $\mu$ >4cm²/Vs were proven. Process tuning is still required to achieve fully printed IZO-AlO<sub>x</sub>/YAlO<sub>x</sub> TFTs on foil, but the preliminary results proved the suitability of both printing and synthesis approaches with cost-effective polymeric substrates.

### Keywords

deep-UV, indium zinc oxide, low temperature, metal oxide, printing, solution processing, thin-film transistor, flexible substrate

### Sommario

Nuovi semiconduttori a ossidi metallici ( $MO_x$ ) per transistor a film sottile (TFT),vengono oggigiorno sviluppati grazie alle superiori prestazioni elettriche rispetto alle controparti a base organica. I  $MO_x$  TFT fabricati su pellicola potrebbero essere sfruttati in etichette intelligenti come tag RFID e NFC, in dispositivi indossabili flessibili, come sensori personalizzati, soddisfacendo la domanda di funzionalità extra nei prodotti della vita quotidiana. Tuttavia, le loro attuali condizioni di fabbricazione non consentono la produzione in grande scala e a basso costo su substrati comunemente usati nell'elettronica stampata, come le plastiche termosensibili a base di polietilene, impedendone la diffusione nei prodotti di consumo e logistici. Questa tesi tratta la fabbricazione di TFT a base di ossido di metallo con tecniche additive a bassa temperatura (<200°C) tramite sintesi basata su UV profondo (DUV), compreso lo sviluppo di inchiostro e la stampa, fabbricazione e caratterizzazione dei dispositivi.

In primo luogo, presentiamo i TFT realizzati, basati su strati di IZO/AlO<sub>x</sub> processati in soluzione. Su silicio, abbiamo studiato come IZO trattato termicamente (200-450°C) interagisce con dielectrico ad alto k basato su alumina, depositato con spin-coating e con tecniche sotto vuoto (ALD), valutando le prestazioni dei TFT e composizione chimica dell'IZO. Rispetto alle controparti con dielectrico ALD, l'abbinamento ottimale dei materiali nello stack basato su sol-gel ha portato a un'interfaccia superiore e a TFT piu performanti,  $\mu^26cm^2/Vs$ ,  $I_{on}/I_{off}^10^6$  rispetto a  $\mu^4cm^2/Vs$ ,  $I_{on}/I_{off}^10^4$ . Infine, aplplicando fotolitografia, i TFT ad ossido di metallo completamente lavorati in soluzione ad alta temperatura hanno raggiunto alte prestazioni con  $\mu^68cm^2/Vs$  e  $I_{on}/I_{off}^10^9$ , paragonabili allo stato dell'arte di dispositivi standard.

Poi, abbiamo realizzato un protocollo per la sintesi dell' IZO rivestito per rotazione e del dielettrico  $AlO_x/YAlO_x$  stampato, ad una bassa temperatura di 200°C grazie alla sintesi con DUV a bassa temperatura. Prolungate esposizione DUV (1h) e ricottura termica (3h) hanno ottenuto TFT con  $\mu$  fino a ~40cm²/Vs. Studiando gli effetti dei parametri di processo sulla composizione chimica IZO e le caratteristiche TFTs, il tempo di sintesi IZO è stato ridotto a ~1h mantenendo eccellenti prestazioni come  $\mu$ ~16cm²/Vs,  $l_{on}/l_{off}$ >108, e SS<100mV/dec. In definitiva, abbiamo dimostrato un protocollo breve come 10min a 200°C in grado di produrre TFT, stabili oltre un anno anche senza passivazione, con mobilità di ~3cm²/Vs,  $l_{on}/l_{off}$ >108, e SS<100mV/dec.

Al fine di ridurre ulteriormente l'impatto termico della sintesi, abbiamo implementato un approccio di sintesi con DUV excimer e temperature applicate simultanemente ("in-situ"), con  $MO_x$  stampati ad inchiostro. In primo luogo, DUV in-situ è stato applicato sul dielettrico  $AIO_x/YAIO_x$ , realizzando a bassa temperature (130°C), condensatori (MIM) con basse correnti di perdita, circa  $10^{-7}A/cm$  a 1MV/cm. Abbiamo proposto e convalidato un processo produttivo per integrare questi MIM su un foglio flessibile, ottenendo MIM operativi con un dielettrico  $AIO_x/YAIO_x$  stampato su foglio di PEI. Abbiamo sviluppato un inchiostro IZO e studiato come la sua composizione influisce sulla stampabilità e sullele prestazioni dei transitor quando sintetizzati a temperature inferiori a  $200^{\circ}$ C. La combinazione del trattamento DUV excimer a  $180^{\circ}$ C con una formulazione ottimizzata di inchiostro IZO ha portato a TFT stampati con  $\mu$ >1cm²/Vs. Infine, sono stati dimostrati TFT con ossidi metallici entrambi stampati, trattati termicamente, con  $\mu$ >4cm²/Vs. Una messa a punto del processo è ancora necessaria per ottenere TFT IZO-AIO $_x/YAIO_x$  completamente stampati su lamina, ma i risultati preliminari hanno dimostrato l'idoneità di entrambi gli approcci di stampa e di sintesi con i convenienti substrati polimerici.

### Parole chiave

UV profondo, transistor a film sottile, processi a bassa temperatura, stampa, ossido di indio e zinco, substrati flessibili

### Résumé

De nouveaux semi-conducteurs à oxyde métallique ( $MO_x$ ) pour les transistors à couche mince (TFT) sont actuellement développés en raison de leurs performances électriques supérieures à celles de leurs homologues à base organique. Les TFTs  $MO_x$  fabriqués sur substrats souples pourraient être exploités dans des étiquettes intelligentes comme les tags RFID et NFC, ou interfacés avec ou comme capteur appliqués aux soins de santé personalisés, répondant ainsi une demande pour une intégration de fonctionnalités supplémentaires dans les produits quotidiens. Toutefois, leurs conditions de fabrication actuelles ne permettent pas leur production à grande échelle et à faible coût sur des substrats couramment utilisés en électronique imprimée, tels que les plastiques thermosensibles à base de polyéthylène, ce qui empêche leur utilisation généralisée dans les produits de consommation et dans la logistique. Cette thèse traite de la fabrication et de la caractérisation de TFTs à base d'oxydes métalliques à basse température (<200°C) en employant des techniques additives de mise en forme et une synthèse des basée sur une exposition à des UV profonds (DUV).

Premièrement, nous présentons des TFTs fabriqués à partir d'un empilement original de couches d'IZO/AlO<sub>x</sub> synthétisés par un procédé sol-gel. Sur silicium, nous avons étudié comment le semiconducteur IZO traité thermiquement (200-450°C) interagit avec des diélectriques de grille à base d'alumine à constante diélectrique élevée, déposés par dépôt à la tournette et en phase vapeur sous vide (ALD). Par rapport au diélectrique formé par ALD, l'empilement des oxydes fonctionnels synthétisés que par sol-gel à 450°C a induit une qualité d'interface résultant en des TFT plus performants,  $\mu$ ~26cm²/Vs,  $I_{on}/I_{off}$ ~106 par rapport à  $\mu$ ~4cm²/Vs,  $I_{on}/I_{off}$ ~104. Enfin, avec une structuration par photolithographie, les TFTs composés de ces mêmes oxydes métalliques synthétisés à haute température ont présenté des performances élevées avec une mobilité ~68cm²/Vs et un ratio  $I_{on}/I_{off}$ >109, comparables à l'état de l'art.

Ensuite, nous avons développé un protocole pour la synthèse à une température minimale de 200°C par exposition aux UV profonds du semiconducteur IZO et des diélectriques AlO<sub>x</sub>/YAlO<sub>x</sub>. Une exposition aux DUV (1h) et un traitement thermique (3h) prolongés ont permis d'obtenir des TFTs avec une mobilité atteignant ~ $40\text{cm}^2$ /Vs. Suite à une étude de l'effet des différents paramètres sur la composition chimique de l'IZO et les caractéristiques des TFTs, le temps de synthèse de l'IZO a été réduit à ~1h tout en maintenant d'excellentes performances telles que  $\mu$  ~ $16\text{cm}^2$ /Vs,  $I_{\text{on}}/I_{\text{off}}>10^8$ , et SS <100mV/dec. Finalement, nous avons démontré un protocole réduit à 10min permettant la production à  $200^\circ$ C de TFTs stables sur une année, cela même sans passivation, présentant une mobilité de ~ $3\text{cm}^2$ /Vs, un ratio  $I_{\text{on}}/I_{\text{off}}>10^8$ , et un SS<100mV/dec.

Afin de réduire davantage le budget thermique de la synthèse, nous avons mis en œuvre une approche in-situ, combinant DUV excimère et chauffage, appliquées à des couches MO<sub>x</sub> imprimées par jet d'encre. Tout d'abord, ce procédé a été appliqué sur le diélectrique AlO<sub>x</sub>/YAlO<sub>x</sub>, permettant la fabrication à basse température (130°C) de condensateurs (MIM) ayant de faibles courants de fuite, environ 10<sup>-7</sup>A/cm à 1MV/cm. Nous avons proposé et validé un procédé de fabrication de ces MIMs sur un substrate souple (PEI), avec la réalisation de MIMs composés d'un empilement AlO<sub>x</sub>/YAlO<sub>x</sub> imprimé. Nous avons développé une encre IZO et étudié comment sa composition affecte son impression et les performances du transistor pour une synthèse d'IZO à des températures inférieures à 200°C. La combinaison du traitement DUV excimère avec une formulation d'encre IZO optimisée a permis d'imprimer des TFTs présentant une mobilité >1cm²/Vs. Enfin, des TFTs à base d'IZO imprimé et traité thermiquement à 180°C ont été démontrés avec une mobilité >4cm²/Vs. Une optimization du procédé est encore nécessaire pour obtenir des TFTs faits d'IZO-AlO<sub>x</sub>/YAlO<sub>x</sub> entièrement imprimés sur feuille, mais les résultats préliminaires ont démontré l'adéquation de l'approche avec les substrats polymèriques.

### Mots-clés

UV profond, oxyde d'indium et de zinc, oxyde métallique, impression, procédés en solution à basse température, transistor à couche mince, substrat flexible

# Contents

| Acknowledge    | ements  |                                                             | i    |

|----------------|---------|-------------------------------------------------------------|------|

| Abstract       |         |                                                             | iii  |

| Keywords       |         |                                                             | iii  |

| Sommario       |         |                                                             | v    |

| Parole chiave  | e       |                                                             | v    |

| Résumé         |         |                                                             | vii  |

| Mots-clés      |         |                                                             | vii  |

| List of Figure | s       |                                                             | xiii |

| List of Tables | s       |                                                             | xxi  |

| List of Equati | ions    |                                                             | xxii |

| Chapter 1      | Introd  | duction                                                     | 1    |

| 1.1            | Backg   | round and motivation                                        | 1    |

| 1.2            | Object  | tives and challenges                                        | 2    |

| 1.3            | Contri  | ibutions and thesis outline                                 | 4    |

| Chapter 2      | Metal   | l-oxide thin-film transistors: fundamentals and technology  | 7    |

| 2.1            | Introd  | duction to TFT technology                                   | 8    |

|                | 2.1.1   | TFTs and MOSFET: working principle and comparison           | 8    |

|                | 2.1.2   | Configurations and characteristics of TFTs                  | 9    |

|                | 2.1.3   | Figures of merit                                            | 10   |

|                | 2.1.4   | Comparison between semiconducting channels                  | 13   |

| 2.2            | Solutio | on processing of MO <sub>x</sub> based TFTs                 | 14   |

|                | 2.2.1   | Process fundamentals and comparison with standard methods   | 14   |

|                | 2.2.2   | Sol-gel chemistry                                           | 15   |

| 2.3            | Depos   | sition methods for solution-processed metal-oxide TFTs      | 16   |

|                | 2.3.1   | Coating techniques                                          | 16   |

|                | 2.3.2   | Printing methods                                            | 17   |

| 2.4            | Reduc   | ction of the synthesis temperature for sol-gel metal-oxides | 19   |

|                | 2.4.1   | Chemical process optimization                               | 20   |

|                | 2.4.2   | Alternative curing approaches                               | 21   |

|                | 2.4.3   | Photoactivation via deep-ultraviolet (DUV) treatment        | 23   |

| 2.5       | Comb    | ining solution-processed MO <sub>x</sub> dielectric and semiconductor                                    | 26 |

|-----------|---------|----------------------------------------------------------------------------------------------------------|----|

|           | 2.5.1   | Basics of MO <sub>x</sub> dielectric                                                                     | 26 |

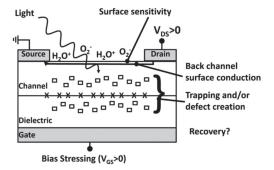

|           | 2.5.2   | Semiconductor-Dielectric interactions in MO <sub>x</sub> TFTs                                            | 27 |

| 2.6       | Printir | ng MO <sub>x</sub> TFTs on flexible and temperature-sensitive substrates                                 | 31 |

|           | 2.6.1   | Flexible and thermosensitive substrates characteristics                                                  | 31 |

|           | 2.6.2   | Printing MO <sub>x</sub> TFTs on flexible and thermosensitive substrates                                 | 32 |

| 2.7       | State-  | of-the-art summary on low-temperature processed and printed $MO_x$ TFT: status and challenges            | 33 |

|           | 2.7.1   | Status on low-temperature processed and printed MO <sub>x</sub> TFTs                                     | 33 |

|           | 2.7.2   | Challenges and research approaches addressed in this thesis                                              | 35 |

| 2.8       | Concl   | usions                                                                                                   | 36 |

| Chapter 3 | Conce   | pt and design of solution-processed MO <sub>x</sub> semiconductor                                        | 37 |

| 3.1       | Mater   | rial design towards performing amorphous oxide semiconductor channel                                     | 38 |

|           | 3.1.1   | Amorphous metal oxide semiconductors                                                                     | 38 |

|           | 3.1.2   | ZnO-based multi-component oxides semiconductors                                                          | 39 |

|           | 3.1.3   | InO <sub>x</sub> -based multi-component oxides semiconductors                                            | 40 |

|           | 3.1.4   | The selected sol-gel based IZO semiconductor for low-temperature processing                              | 42 |

| 3.2       | Ink de  | sign for the IZO solution                                                                                | 42 |

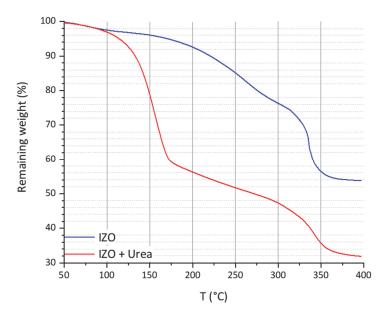

|           | 3.2.1   | Characterization of the sol-gel reaction by TGA                                                          | 43 |

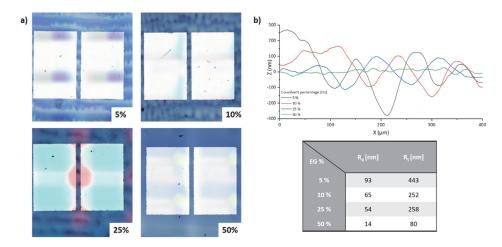

|           | 3.2.2   | Variation of In:Zn ratio in the IZO semiconductor                                                        | 44 |

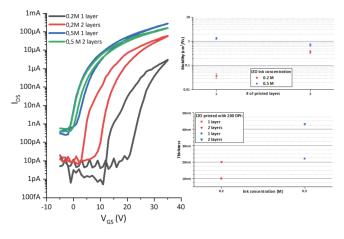

|           | 3.2.3   | Electrical characterization                                                                              | 45 |

|           | 3.2.4   | Characterization of film morphology by optical microscopy and XRD analysis                               | 46 |

|           | 3.2.5   | Conclusions on the formulation of IZO solutions                                                          | 47 |

| 3.3       | Doped   | d-IZO as semiconductor                                                                                   | 47 |

|           | 3.3.1   | Al as doping element for MO <sub>x</sub> semiconductor                                                   | 48 |

|           | 3.3.2   | Effect of Al doping in the IZO system                                                                    | 48 |

|           | 3.3.3   | Electrical characterization                                                                              | 49 |

|           | 3.3.4   | Al-doped IZO: discussion                                                                                 | 51 |

| 3.4       | Concl   | usions                                                                                                   | 51 |

| Chapter 4 | Therm   | nal synthesis of solution-processed IZO-based TFTs                                                       | 53 |

| 4.1       | Therm   | nal annealing of indium zinc oxide-based MO <sub>x</sub> TFTs                                            | 54 |

|           | 4.1.1   | Thermally annealed sol-gel IZO: comparison between solution-processed and ALD metal-oxid gate dielectric |    |

|           | 4.1.2   | Characterization methodology                                                                             | 57 |

|           | 4.1.3   | Results for IZO on spin-coated AIO <sub>x</sub> /YAIO <sub>x</sub> dielectric                            | 58 |

|           | 4.1.4   | Results for IZO on ALD Al <sub>2</sub> O <sub>3</sub> dielectric                                         | 61 |

|           | 4.1.5   | Comparison and discussion                                                                                | 63 |

| 4.2       | Manu    | facturing of TFTs with fully solution-processed MO <sub>x</sub> active stack at high temperature         | 65 |

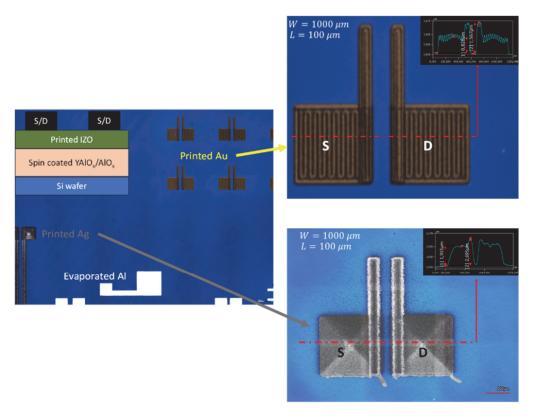

| 4.2.2 Process flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70             |

| 4.2.4 TFT characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75             |

| 4.2.5 Dielectric characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77             |

| 4.2.6 Characterization of TFTs stability and reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80             |

| 4.2.7 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82             |

| 4.3 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83             |

| Chapter 5 Low thermal budget synthesis of IZO semiconductor through DUV-enhanced appro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oach 85        |

| 5.1 Lowering the IZO synthesis temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86             |

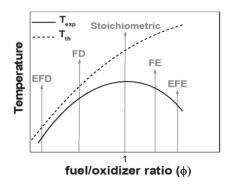

| 5.1.1 Combustion process with urea as fuel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86             |

| 5.1.2 IZO synthesis via DUV annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88             |

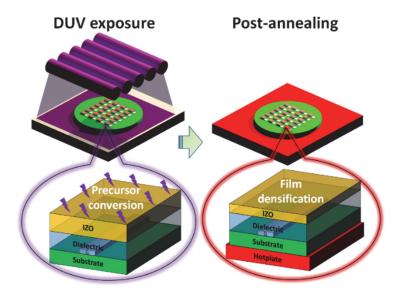

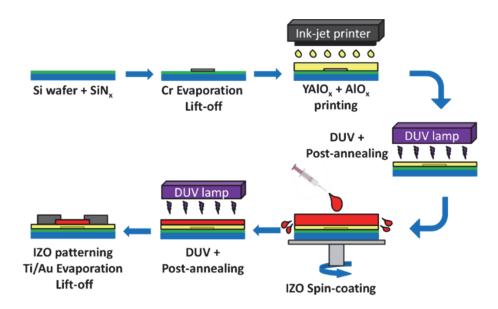

| 5.2 DUV-enhanced approach for low-temperature synthesis of IZO based TFTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90             |

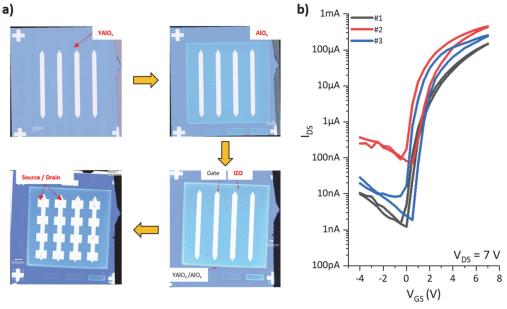

| 5.2.1 Designs and process flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91             |

| 5.2.2 Characterization methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 93             |

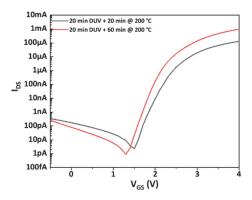

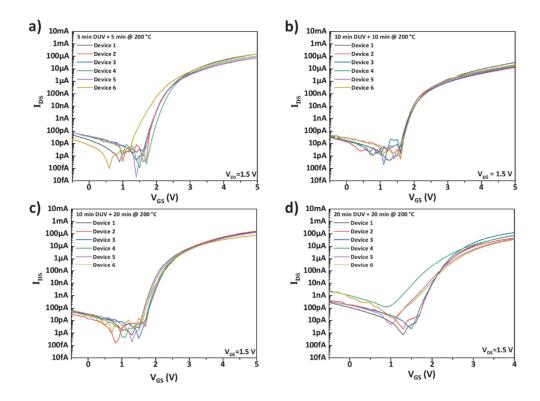

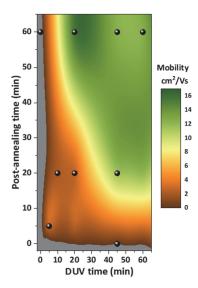

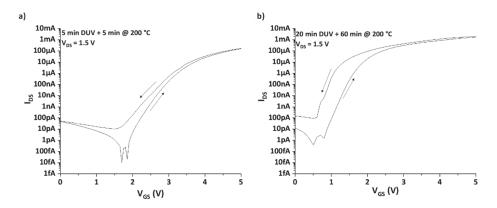

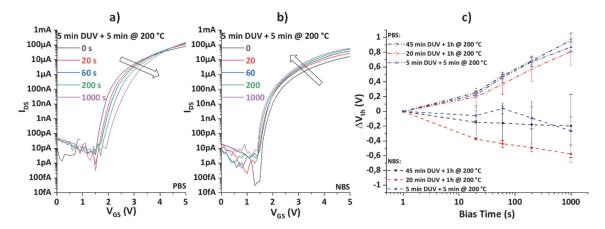

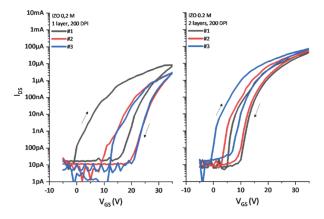

| 5.2.3 Influence of DUV exposure and post-annealing time on TFT characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93             |

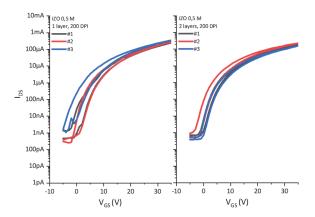

| 5.2.4 Shortening of the protocol duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98             |

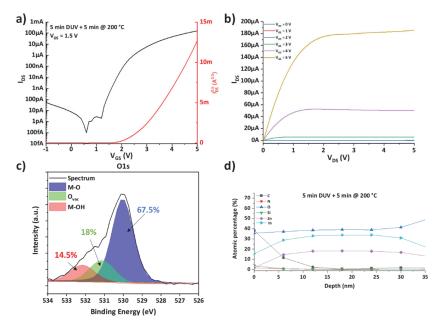

| 5.2.5 Complementary characterizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101            |

| 5.2.6 Lowering the maximum process temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 107            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| 5.2.7 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 108            |

| 5.2.7 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 109            |

| 5.3 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 109            |

| 5.3 Conclusions  Chapter 6 Towards fully printed MO <sub>x</sub> TFTs at low temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109111 stem113 |

| 5.3 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 109111 stem113 |

| 5.3 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 109111 stem114 |

| 5.3 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Chapter 6 Towards fully printed MO <sub>x</sub> TFTs at low temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Towards fully printed MO <sub>x</sub> TFTs at low temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

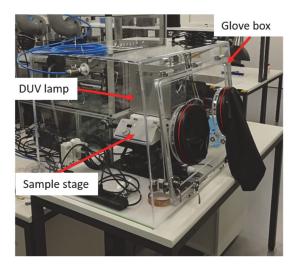

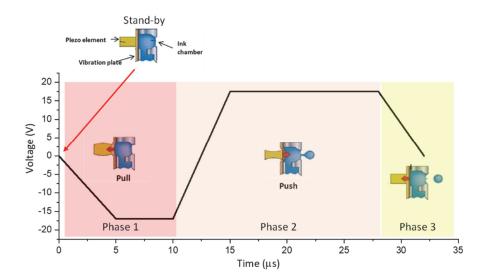

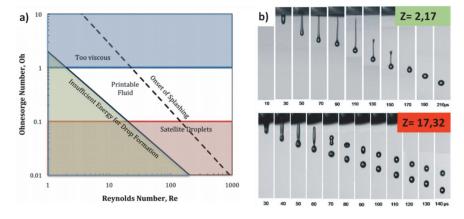

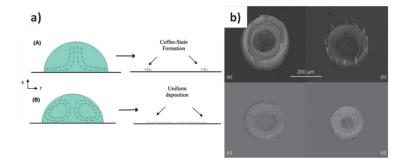

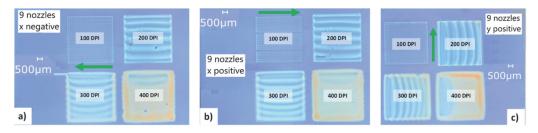

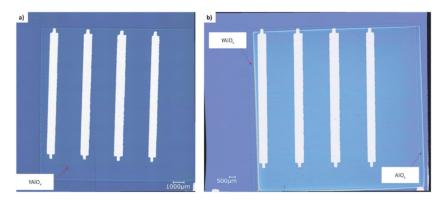

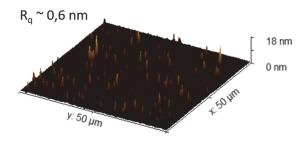

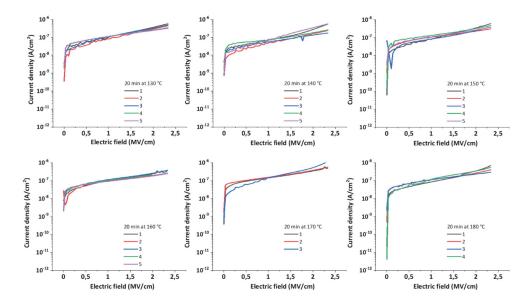

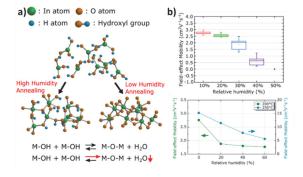

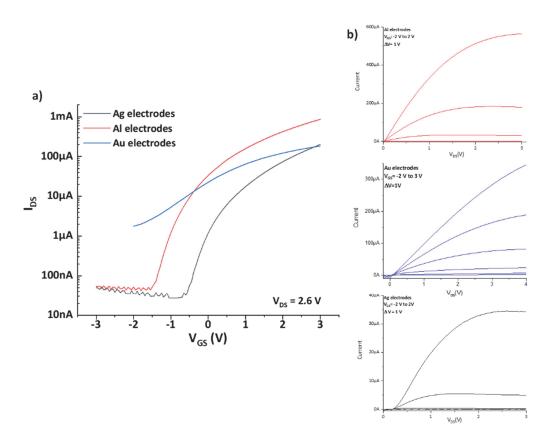

| Chapter 6 Towards fully printed MO <sub>x</sub> TFTs at low temperature  6.1 Synthesis of metal-oxide dielectric and semiconductor films via an excimer DUV system  6.2 Inkjet printing of the metal-oxide functional layers  6.2.1 Inkjet printing fundamentals  6.2.2 Low-temperature processing of printed MO <sub>x</sub> layers: challenges and requirem  6.2.3 Approach to the solvent formulation for MO <sub>x</sub> inkjet ink  6.3 Printing of active layers for MO <sub>x</sub> TFTs  6.3.1 Printing system: Ceraprinter F-serie  6.3.2 Printing of AlO <sub>x</sub> /YAlO <sub>x</sub> dielectric stack  6.3.3 IZO semiconductor printing  6.3.4 Effect of humidity during processing on the TFTs electrical characteristics  6.3.5 Discussion. |                |

| Chapter 6 Towards fully printed MO <sub>x</sub> TFTs at low temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

### Contents

| Chapter 7   | Concl | usion and outlook                                                                   | 149 |

|-------------|-------|-------------------------------------------------------------------------------------|-----|

| 7.1         | Concl | usion                                                                               | 149 |

|             | 7.1.1 | Solution-processed IZO-based TFTs                                                   | 149 |

|             | 7.1.2 | Low-temperature processing of MO <sub>x</sub> TFTs via DUV                          | 149 |

|             | 7.1.3 | MO <sub>x</sub> printing towards fully printed TFTs onto thermosensitive substrates | 150 |

| 7.2         | Outlo | ok                                                                                  | 151 |

| References. |       |                                                                                     | 153 |

| Curriculum  | vitae |                                                                                     | 167 |

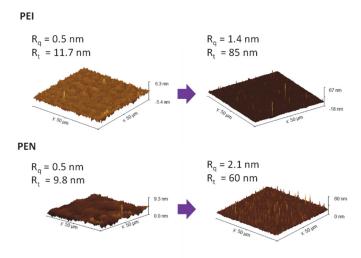

# List of Figures

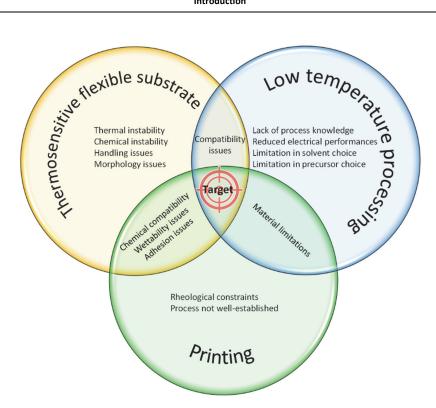

| Figure 1.1 Challenges & constraints related to the selected processing methods and their interactions                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

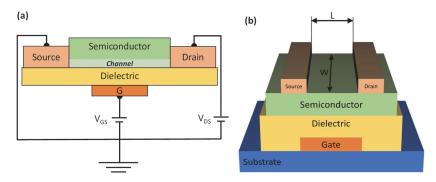

| Figure 2.1 Schematic representation of a three-terminal field-effect transistor. (a) Shows the biases applied to the electrodes and (b) represents a TFT architecture with the relevant geometrical dimensions                                                                                                                                   |

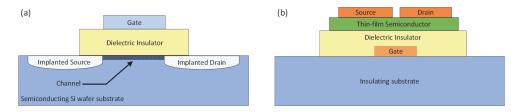

| Figure 2.2 Cross-section and structure comparison between (a) MOSFET and (b) TFT.                                                                                                                                                                                                                                                                |

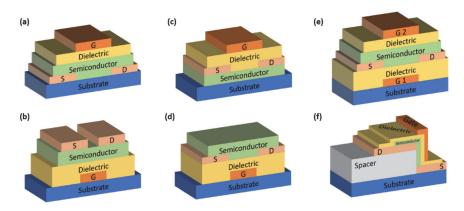

| Figure 2.3 The most common TFT configurations: (a) top gate (TG) staggered TFT, (b) bottom gate (BG) staggered TFT, (c) TG coplanar TFT, (d) BG coplanar TFT, (e) double gate (DG) TFT, and (f) vertical TFT (VTFT)9                                                                                                                             |

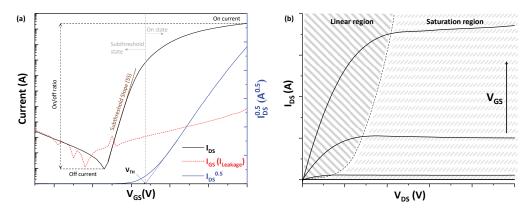

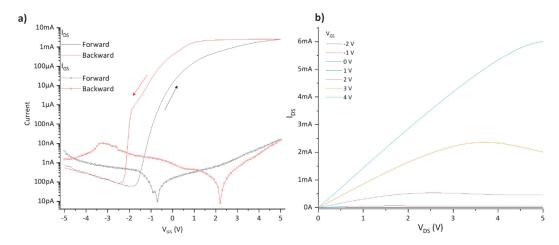

| Figure 2.4 Typical I-V characteristics of a TFT: the transfer (a), obtained at varying $V_{GS}$ and fixed $V_{DS}$ , and the output (b), extracted by varying $V_{DS}$ at determined $V_{GS}$ values                                                                                                                                             |

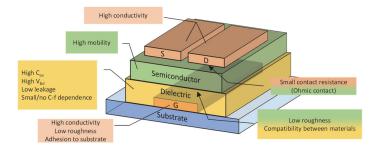

| Figure 2.5 General requirements for each TFT component and their interfaces                                                                                                                                                                                                                                                                      |

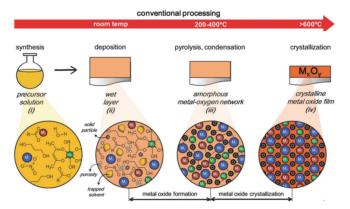

| Figure 2.6 Representation of the chemical steps occurring during the heat treatment of a sol-gel processed $MO_x$ layer. Adapted from [35]                                                                                                                                                                                                       |

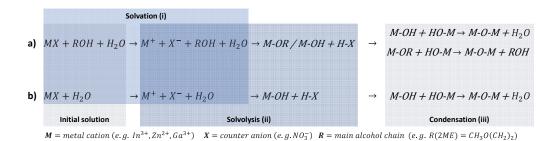

| Figure 2.7 The chemical reactions occurring during the sol-gel process. Depending on the solvents involved: a) represents the alcohol route while b) represents the water route. As an example, are reported the elements involved in the sol-gel process of IGZO using nitrate precursors and 2-methoxyethanol as solvent                       |

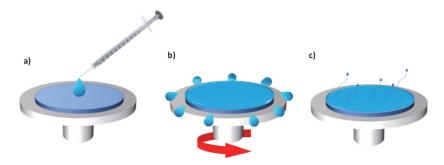

| Figure 2.8 Schematic working principle of spin-coating deposition. a) Solution deposition, b) solution spreading to form a uniform thin layer, and c) solvent evaporation                                                                                                                                                                        |

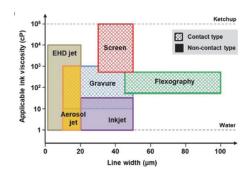

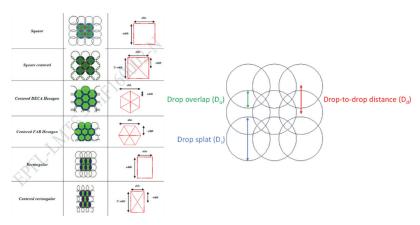

| Figure 2.9 Feature resolution and viscosity operational windows of the different printing methodologies.[54] . 18                                                                                                                                                                                                                                |

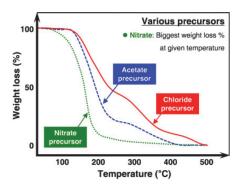

| Figure 2.10 Thermal gravimetric analysis (TGA) obtained from solutions composed by different initial precursors.[89]                                                                                                                                                                                                                             |

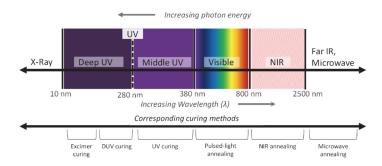

| Figure 2.11 Electromagnetic spectrum and the correlated curing techniques described in the literature, applied to solution-processed $MO_x$ films                                                                                                                                                                                                |

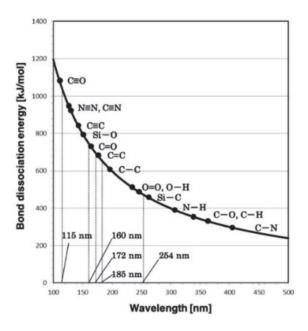

| Figure 2.12 Energy level, and correspondent wavelength, required to break the typical chemical bonds present in the various molecules.[114]23                                                                                                                                                                                                    |

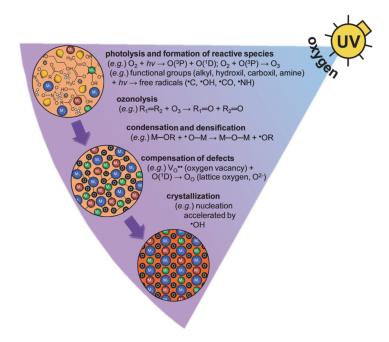

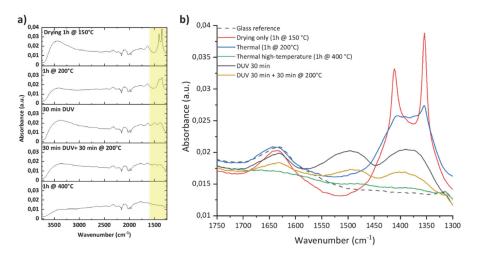

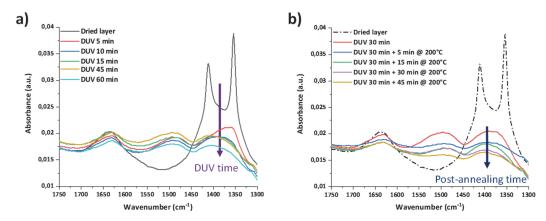

| Figure 2.13 Summary of the chemical reactions triggered from exposure to a DUV light in an O <sub>2</sub> -rich environment.[35]                                                                                                                                                                                                                 |

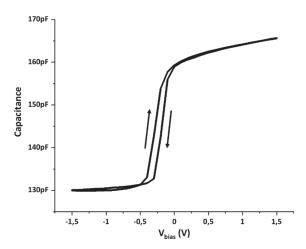

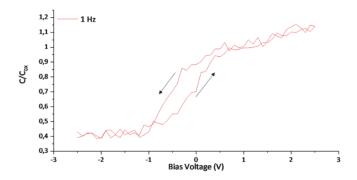

| Figure 2.14 Example of C-V characteristic extracted from a MOS structure made of the typical material stack employed in this thesis: Au/Ti/IZO/AIO <sub>x</sub> /YAIO <sub>x</sub> /Cr. (frequency= 1 kHz)                                                                                                                                       |

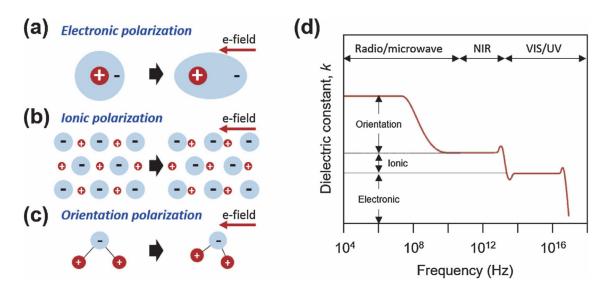

| Figure 2.15 The basic mechanisms of dielectric polarization. Schematics of (a) electronic polarization, (b) ionic polarization, (c) orientation polarization. (d) Electronic, ionic, and orientation polarization contribute to the overall dielectric constant as a function of the frequency applied.[146]                                     |

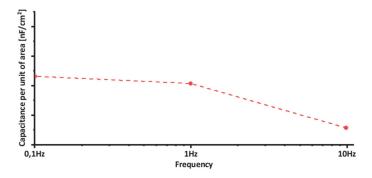

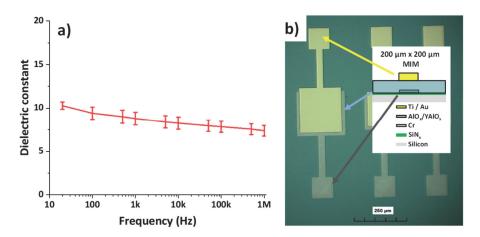

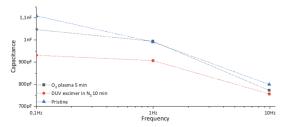

| Figure 2.16 Example of C-f characteristic at low frequency, extracted from a MIM structure made of the typical material stack employed in this thesis: Al/AlO <sub>x</sub> /YAlO <sub>x</sub> /Cr                                                                                                                                                |

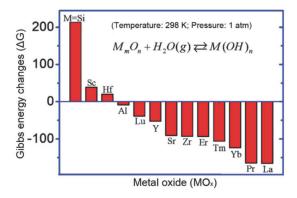

| Figure 2.17 Gibbs energy changes required for moisture adsorption, under standard conditions, for some high-k oxide dielectrics.[149]                                                                                                                                                                                                            |

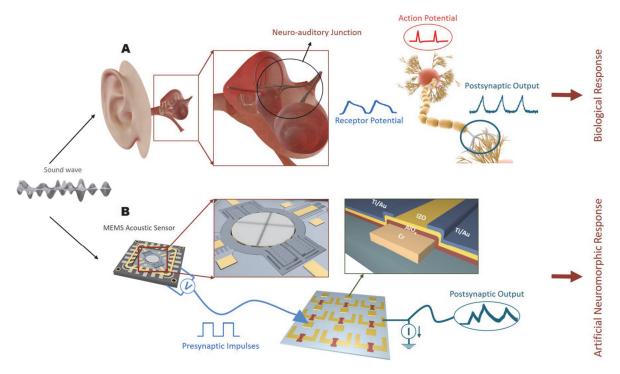

| Figure 2.18 Example of solution-processed MO <sub>x</sub> TFTs acting as synaptic transistors in neuromorphic applications.[157]                                                                                                                                                                                                                 |

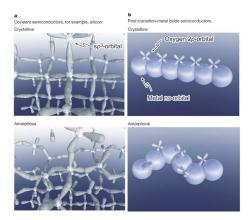

| Figure 3.1 Charge transport in covalent semiconductors and post-transition metal-oxide semiconductors.[26]                                                                                                                                                                                                                                       |

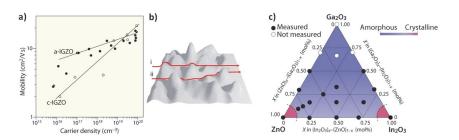

| Figure 3.2 Comparison between crystalline and amorphous MO <sub>x</sub> . a) Relationship between Hall mobility and carrier density for c-IGZO and a-IGZO. b) Illustration of percolation conduction showing examples of (i) a shorter and (ii) a longer path. c) Relation between film morphology and chemical composition. (Adapted from[167]) |

| Figure 3.3 Morphological and electrical characteristics of ZTO-based transistors with different Zn:Sn ratios.[169]                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.4 Example of sputtered IZO films exploited as conductors and as a semiconductor in the same TFT. (Adapted from [176])                                                                                                                                                                                              |

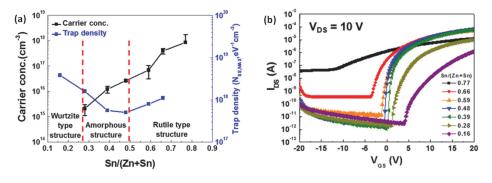

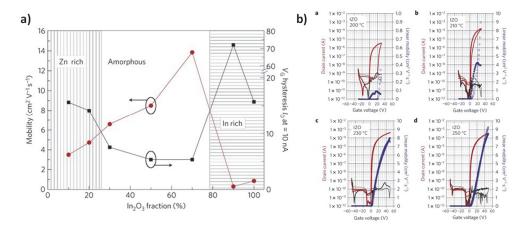

| Figure 3.5 Structural and electrical characteristics of IZO TFTs. a) Plot of mobility and hysteresis of IZO TFTs as a function of the stoichiometry. b) Transfer curves obtained from TFTs cured at various temperatures. (Adapted from [91])                                                                               |

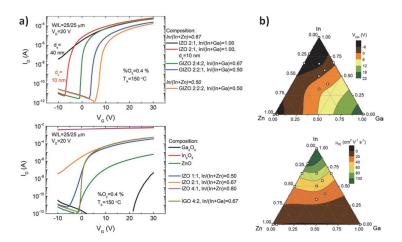

| Figure 3.6 Effect of cation tuning on sputtered IGZO TFTs. a) IGZO transfer characteristics for different cation stoichiometry. b) Effect of cation stoichiometry on mobility and threshold voltage. (Adapted from [5])                                                                                                     |

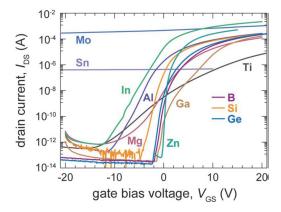

| Figure 3.7 Transfer characteristics obtained from various sputtered In-X-O TFTs.[176]                                                                                                                                                                                                                                       |

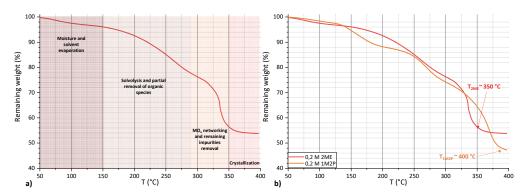

| Figure 3.8 Thermogravimetric analysis of nitrate-based IZO solutions. a) Depicts the typical curve obtained from a 2ME-based solution where we can identify the different moments of the sol-gel reaction. b) Shows the comparison between two IZO solutions employing different solvents                                   |

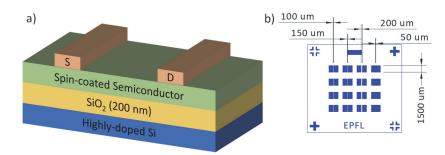

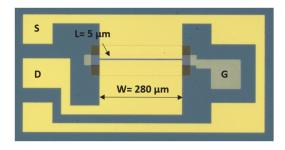

| Figure 3.9 TFT cross-section and electrodes dimensions. a) shows the TFT cross-section while b) depicts the four different W/L present on the mask. Each device for a given W/L is repeated four times to ensure statistical results.                                                                                       |

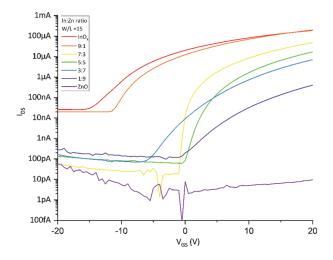

| Figure 3.10 Comparison between typical transfer curves obtained from TFTs with a variable indium-zinc ratio in the active channel                                                                                                                                                                                           |

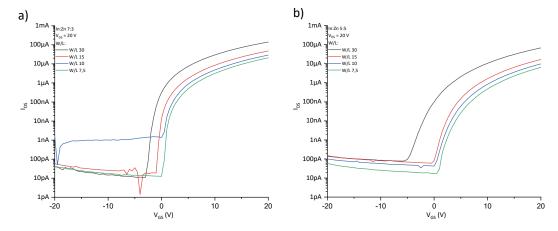

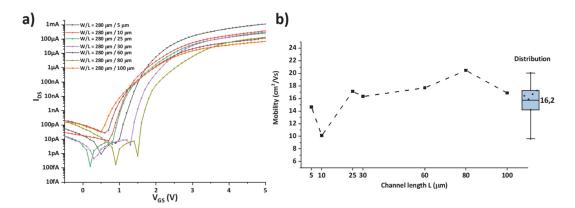

| Figure 3.11 Comparison between transfer characteristics of TFTs with different active channel composition: a) 7:3 IZO and b) 5:5 IZO. The curves were obtained from TFTs with various W/L                                                                                                                                   |

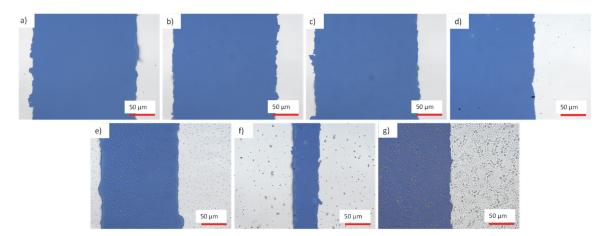

| Figure 3.12 Optical images of the deposited films with variable In:Zn. The indium percentage in the film increases from a) to g). Respectively a) InO <sub>x</sub> , b) 9:1 IZO, c) 7:3 IZO, d) 5:5 IZO, e) 3:7 IZO, f) 1:9 IZO, and g) ZnO.                                                                                |

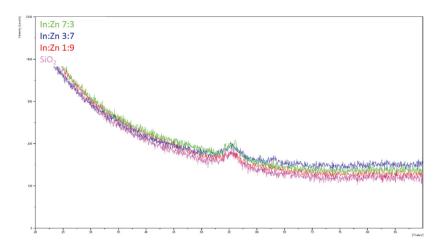

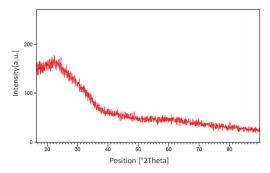

| Figure 3.13 GIXRD patterns obtained from the IZO films with different chemical compositions (In:Zn= 7:3, 3:7, and 1:9, plus SiO <sub>2</sub> reference)                                                                                                                                                                     |

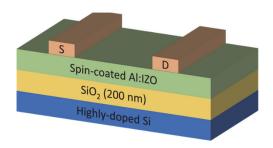

| Figure 3.14 Cross-section schematic of the fabricated TFTs with Al-doped IZO                                                                                                                                                                                                                                                |

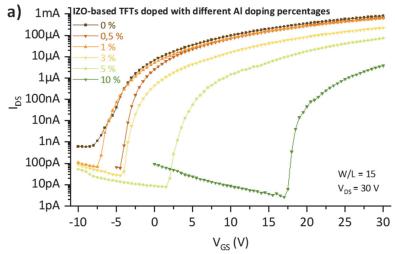

| Figure 3.15 Typical a) transfer and b) output curves obtained from IZO TFTs with different Al %                                                                                                                                                                                                                             |

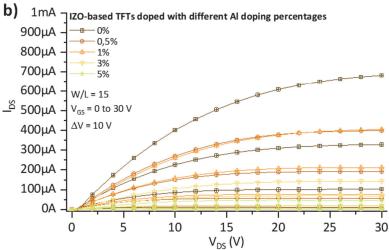

| Figure 3.16 Electrical characteristics of the Al-doped IZO-based TFTs. a) Saturation mobility and threshold voltage versus Al % and b) on- and off-currents on the right axis, left axis depicts the ratio between the average measured mobility over the mobility value of the undoped IZO film versus Al %                |

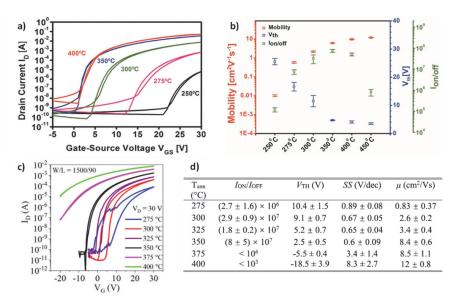

| Figure 4.1 Effect of annealing temperatures on IZO based TFTs: a) transfer characteristics comparison and b) comparative statistics. Adapted from [189]. c) Transfer curves and d) electrical performances reported by Cai et al Adapted from [190]                                                                         |

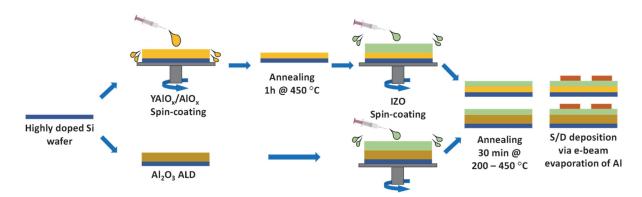

| Figure 4.2 Schematic of the manufacturing process flow employed to realize the IZO/AlO <sub>x</sub> -based TFTs                                                                                                                                                                                                             |

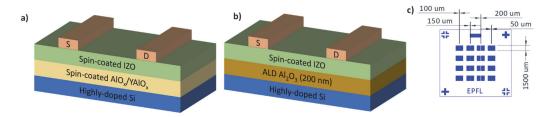

| Figure 4.3 Devices cross-section. a) and b) Depict the TFT cross-sections while c) the layout of the shadow mask for the source and drain electrodes illustrating the four different W/L are present in the mask                                                                                                            |

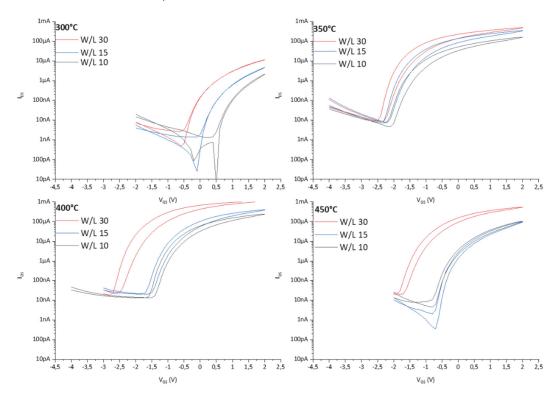

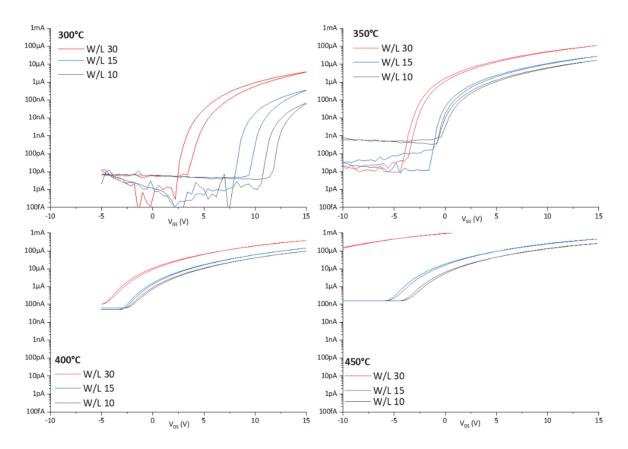

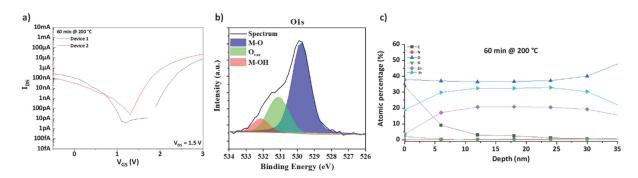

| Figure 4.4 TFTs with spin-coated IZO and spin-coated $AIO_x/YAIO_x$ dielectric. Representative transfer curves extracted from TFTs cured with different annealing temperatures from devices with different W/L. The drain voltage $V_{DS}$ for all the curves was 2 V. The devices cured at 200°C and 250°C were not active |

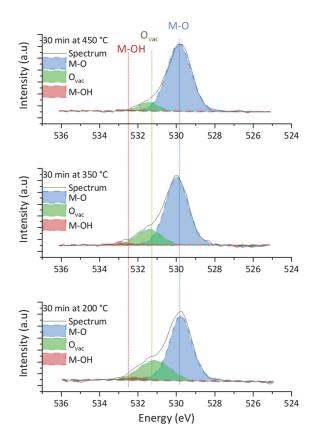

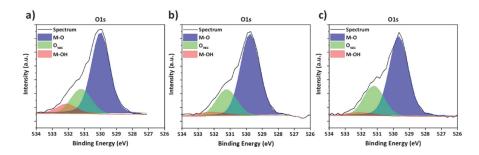

| Figure 4.5 Comparison of the O1s peaks extracted from the IZO layers cured with different annealing protocols with relative deconvolution.                                                                                                                                                                                  |

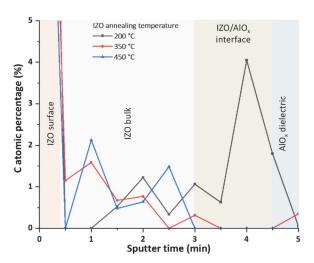

| Figure 4.6 Carbon atomic distribution over semiconductor thickness in the TFTs with spin-coated                                                                                                                                                                                                                             |

| $IZO/AIO_x/YAIO_x$ stack as a function of the IZO annealing temperature, obtained from the in-depth XPS analysis.                                                                                                                                                                                                           |

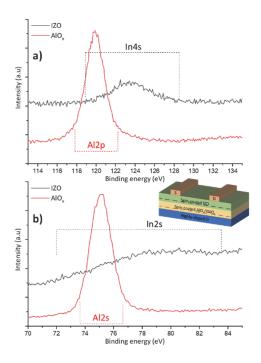

| Figure 4.7 XPS signal overlap from Al and In. The curves obtained from the semiconductor layer (in black) and the dielectric layer (in red) show the spectra analysis in the two emission windows a) $^{\sim}120$ eV and b) $^{\sim}74$ eV.                                                                                                                                                                                                                                        | 61 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.8 XPS spectra from the samples with spin-coated dielectric registered at ~74 eV. We can see an overlap between the In4p peak and the Al2p peak: as the percentages possibly involved are minimal, the Al peak is not visible in the IZO films cured at the various temperatures. Instead, it becomes more evident when the same analysis is performed at the semiconductor/dielectric interface where the Al fractions are higher, and the In signal is less predominant. | 61 |

| Figure 4.9 TFTs with spin-coated IZO and ALD dielectric. Representative transfer curves extracted from TFTs cured at different annealing temperatures from devices with variable W/L. The drain voltage $V_{DS}$ used during the measurements was 15 V. The devices cured at 200°C and 250°C were not active                                                                                                                                                                       | 62 |

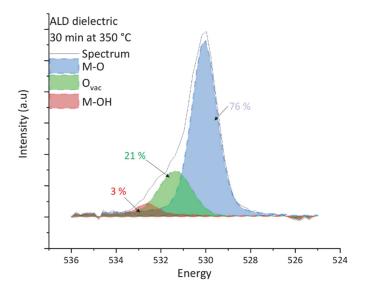

| Figure 4.10 O1s curve of the IZO deposited on ALD Al2O3 with the relative deconvolution and the atomic fractions calculated, with a fitting parameter ( $\chi^2$ ) equal to 0.61. The values 76 %, 21 %, and 3 %, respectively M-O, O <sub>vac</sub> , and M-OH, are comparable to those obtained from the IZO on spin-coated dielectric, cured with the same protocol: 78.3 %, 18.6 %, and 3.1 %                                                                                  | 63 |

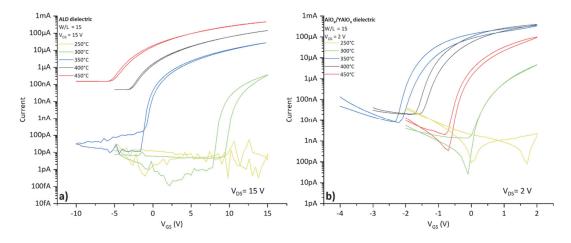

| Figure 4.11 Comparison of transfer curves from devices cured at different temperatures: a) ALD dielectric and b) solution-processed dielectric                                                                                                                                                                                                                                                                                                                                     | 63 |

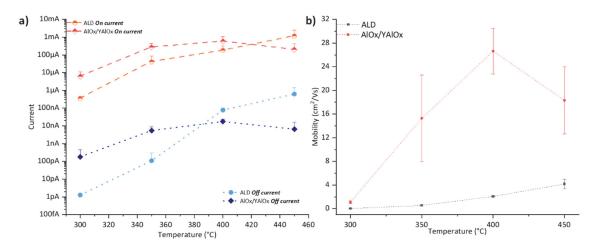

| Figure 4.12 Comparison of the electrical characteristic between the two types of TFT. a) Depicts the tendency for on-current and off-current as a function of the annealing temperature. b) Shows the calculated mobility as a function of the temperature.                                                                                                                                                                                                                        | 64 |

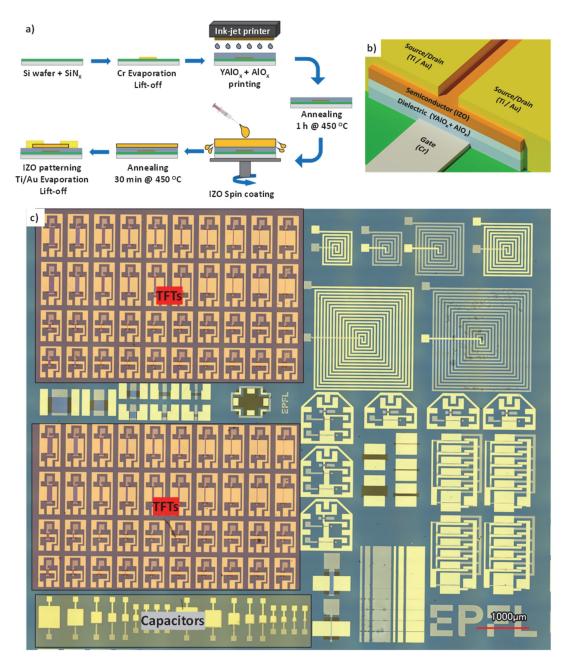

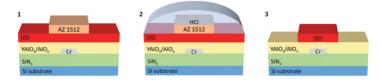

| Figure 4.13 Layout and process flow of the photolithographically patterned structures. a) Schematic process flow and b) cross-section of the final stack. c) Optical image of the layout of a unit cell after fabrication                                                                                                                                                                                                                                                          | 66 |

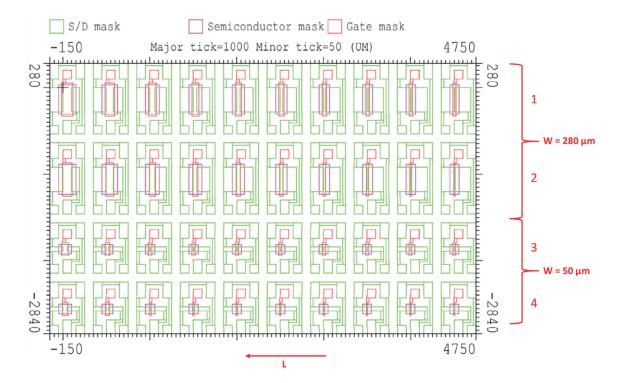

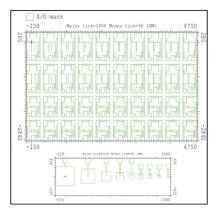

| Figure 4.14 Digital file representing all the 40 different TFT types available in a unit cell. Here are reported all the designs contained in the layout of the three masks necessary to fabricate the TFTs                                                                                                                                                                                                                                                                        | 67 |

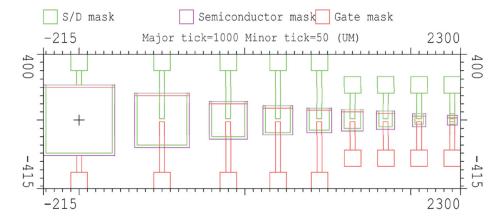

| Figure 4.15 Digital file representing the dimensions of the different capacitors. Here are reported all the designs contained in the masks to fabricate the capacitors. The image depicts the MOS capacitors                                                                                                                                                                                                                                                                       | 67 |

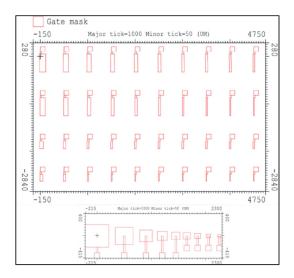

| Figure 4.16 Section of a digital file, referred to the TFT and capacitive structures, exploited to fabricate the gate mask                                                                                                                                                                                                                                                                                                                                                         | 68 |

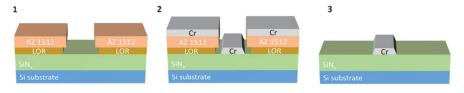

| Figure 4.17 Schematic of the double layer lift-off process used to pattern the chromium gate electrodes                                                                                                                                                                                                                                                                                                                                                                            | 68 |

| Figure 4.18 Schematic description of the wet etching process necessary to pattern the IZO structures.1) Photoresist deposition and patterning, followed in 2) by the wet etching in HCl and resist stripping in 3), which releases the patterned IZO structures.                                                                                                                                                                                                                   | 69 |

| Figure 4.19 Section of the digital mask file, referred to the TFT and MOS structures, exploited to pattern the semiconductor channel.                                                                                                                                                                                                                                                                                                                                              | 69 |

| Figure 4.20 Section of a digital file, referred to the TFT and capacitive structures, exploited to pattern the source/drain and top electrodes.                                                                                                                                                                                                                                                                                                                                    | 70 |

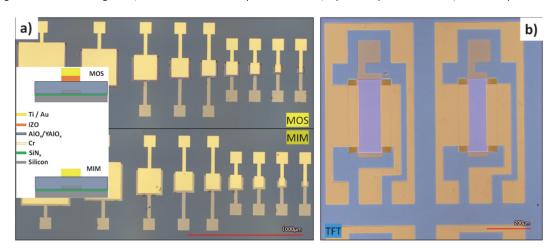

| Figure 4.21 Optical image of the a) MIM and MOS capacitors and relative cross-sections, and b) TFTs                                                                                                                                                                                                                                                                                                                                                                                | 70 |

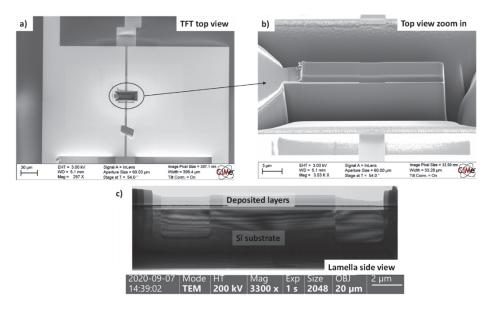

| Figure 4.22 Lamella preparation. a) Location selected for the lamella and b) a close-up image of the process. c) Depicts the final lamella already fixed to the holder.                                                                                                                                                                                                                                                                                                            | 71 |

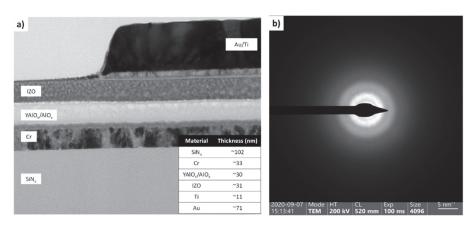

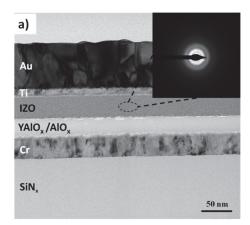

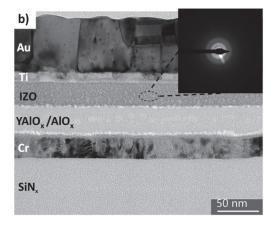

| Figure 4.23 a) High-resolution TEM image of the TFT cross-section. b) Diffraction pattern of the IZO film, which does not show signs of crystalline orientation.                                                                                                                                                                                                                                                                                                                   | 71 |

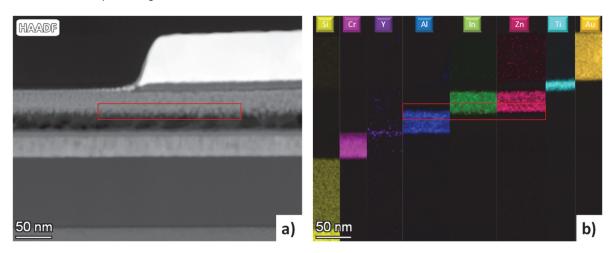

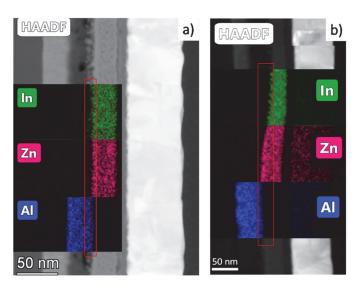

| Figure 4.24 STEM pictures of the cross-section. a) High-resolution HAADF image of the cross-section. b) Chemical elements distribution in the layers obtained via EDX.                                                                                                                                                                                                                                                                                                             | 72 |

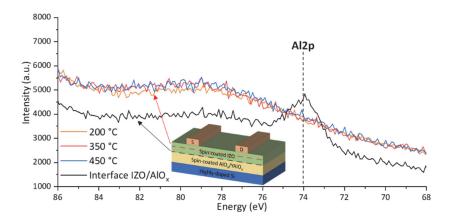

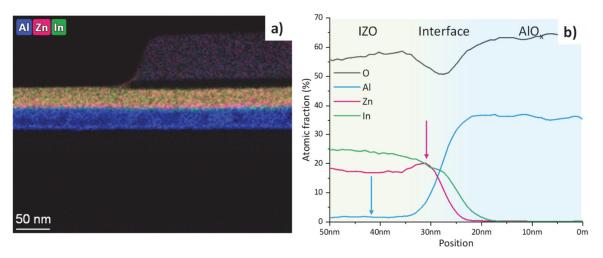

| Figure 4.25 Chemical analysis of the active layers with a) HAADF image and b) relative atomic fraction profile.                                                                                                                                                                                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

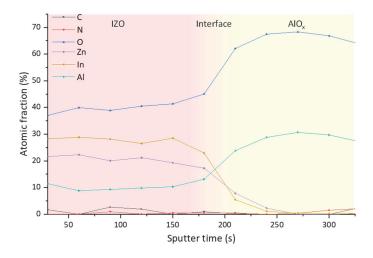

| Figure 4.26 Profile of the chemical composition extracted from the in-depth XPS measurements                                                                                                                                                                                                                                                                                                                                                                                       | /3 |

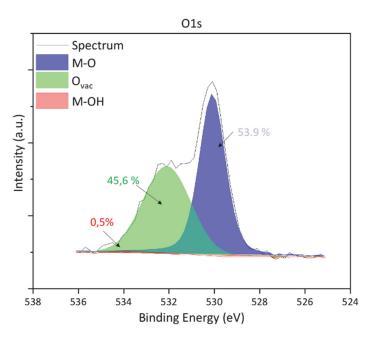

| Figure 4.27 O1s deconvolution obtained from the bulk of the IZO layer, with a fitting parameter ( $\chi^2$ ) equal to 0.65                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

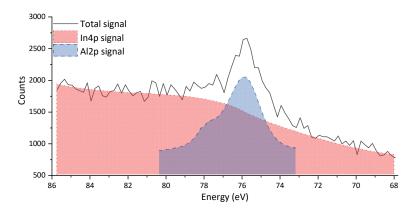

| Figure 4.28 The total signal registered around 75 eV. The signal can be deconvoluted in two contributions related to the In4p located at 78 eV characterized from a large FWHM and the Al2p located at ~75 eV                                                                                           |

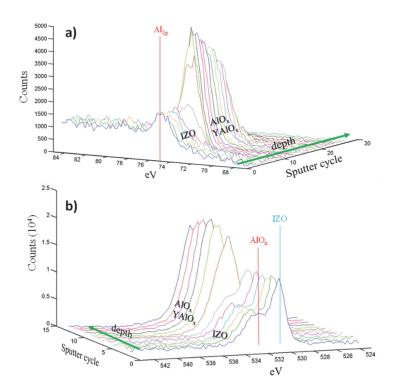

| Figure 4.29 Profile distribution of a) Al and b) O1s over the whole active layers thicknesses                                                                                                                                                                                                           |

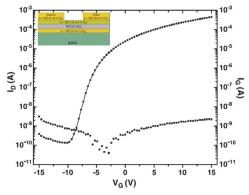

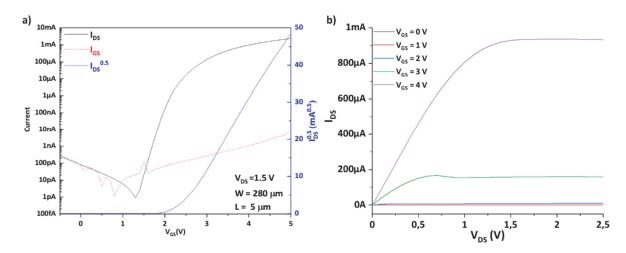

| Figure 4.30 Typical a) transfer and b) output characteristics measured from the TFTs. The voltage applied during the measurement of the transfer characteristics was $V_{DS} = 1.5 \text{ V}$                                                                                                           |

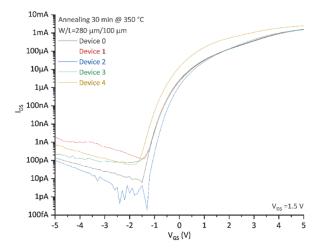

| Figure 4.31 Transfer curves obtained from several devices. (n=5)                                                                                                                                                                                                                                        |

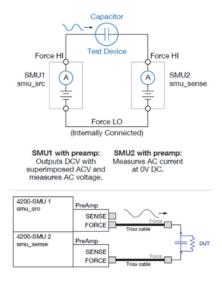

| Figure 4.32 VLF C-V measurement working principle. Adapted from [204]                                                                                                                                                                                                                                   |

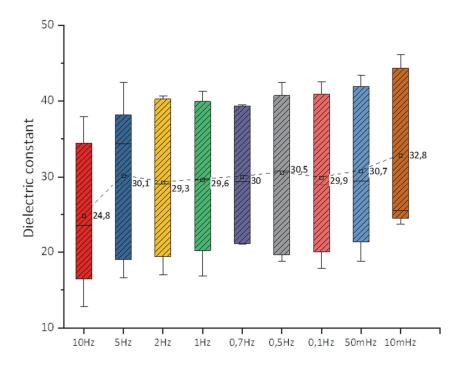

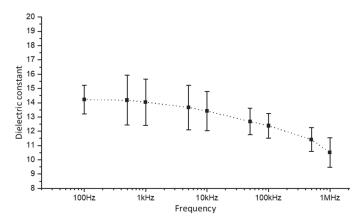

| Figure 4.33 Box plot of the dielectric constant values calculated from VLF C-V measurements at 0 V. The dotted line connects the mean values, also numerically reported on the right of the relative bar. We obtained the statistics from a minimum of n>5 devices                                      |

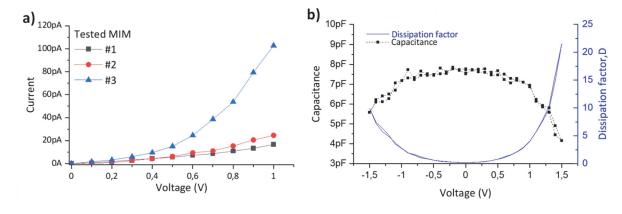

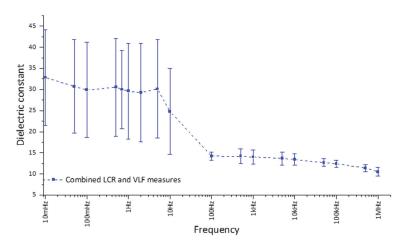

| Figure 4.34 VLF analysis limits. a) typical I-V leakage curves obtained from 30x40 $\mu m$ MIM. b) Capacitance measure at 0.1 Hz: the dissipation factor grows as a function of the applied voltage due to the increase of leakage currents                                                             |

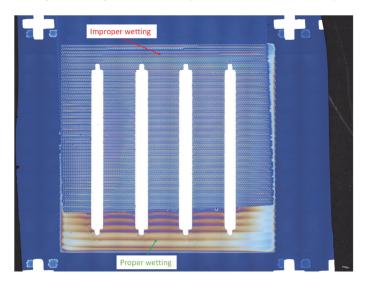

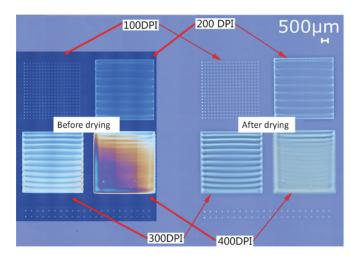

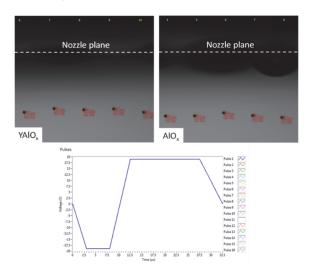

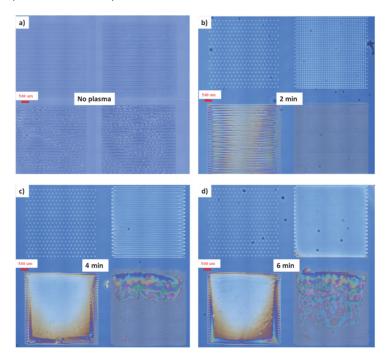

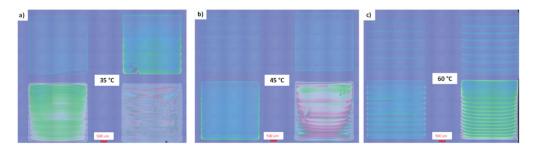

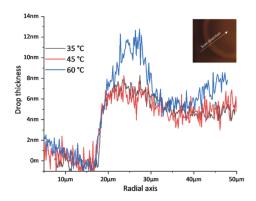

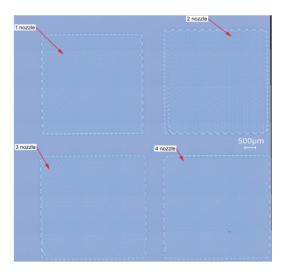

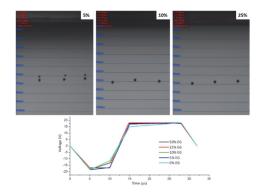

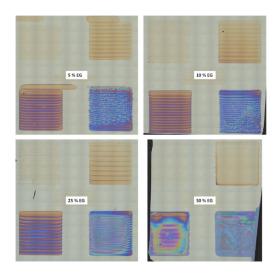

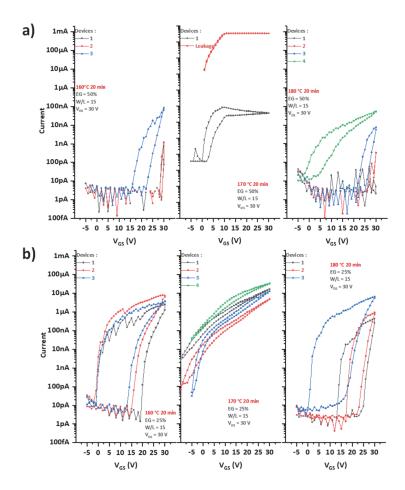

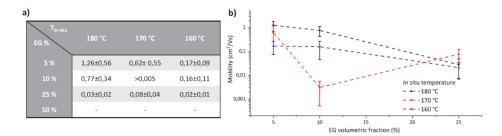

| Figure 4.35 Dielectric constant variation at medium-high frequencies                                                                                                                                                                                                                                    |