# Figures-of-Merit of Lateral GaN Power Devices: modeling and comparison of HEMTs and PSJs

Luca Nela, Catherine Erine, Maria Vittoria Oropallo, and Elison Matioli

Abstract—In this work, we propose a simple and yet accurate physical model to describe the figures-of-merit (FOMs) of lateral GaN power devices. While the performance limit of vertical devices is well understood, the FOMs of lateral devices are not properly described by current models. This work investigates the specific characteristics of the depletion in lateral devices, particularly focusing on the substantial potential of Polarization Super Junctions (PSJs) compared to conventional **High-Electron-Mobility** Transistors (HEMTs). Our results show that PSJs can result in more than a 10-fold decrease in specific on-resistance for the same breakdown voltage compared to HEMTs, which can be further improved by the use of multi-channel heterostructures. In addition, we demonstrate that PSJs lead to a significant reduction of the Ron x Eoss figure-ofmerit, both in the case of negligible and dominating parasitic contributions. This model enables a proper evaluation of the main figures-of-merit of lateral GaN power devices and shows the potential of PSJs to reduce both the DC and switching losses in power devices.

*Index Terms*— Gallium Nitride, Polarization Super Junction, HEMT, off-state modeling.

### I. INTRODUCTION

GaN-on-Si lateral devices have shown outstanding potential for power conversion applications and a substantial improvement in their performance has been achieved in recent years [1], [2]. Yet, the performance of current GaN High-Electron-Mobility Transistors (HEMTs) is still far below what is thought to be the limit for such devices [3]. In particular, their lateral architecture combined with the large density of the twodimensional electron gas (2DEG) results in a peaked off-state electric field at the gate edge, which severely reduces the maximum achievable breakdown voltage ( $V_{BR}$ ). To address this limitation, polarization super junctions (PSJs) have been proposed [4]–[9], which take advantage of the polarization fields naturally formed in GaN heterostructures to achieve charge balance. This approach enables to overcome the challenging GaN *p*-doping, which is necessary to achieve

This work was supported in part by the Swiss National Science Foundation through Assistant Professor (AP) Energy under Grant PYAPP2\_166901 and in part by the ECSEL Joint Undertaking (JU) under grant agreement No 826392. The JU receives support from the European Union's Horizon 2020 research and innovation program and Austria, Belgium, Germany, Italy, Norway, Slovakia, Spain, Sweden, Switzerland''. L. Nela, C. Erine, M. V. Oropallo and E. Matioli are with the Power and Wide-band-gap Electronics Research Laboratory (POWERLAB), École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland (e-mail: luca.nela@epfl.ch; elison.matioli@epfl.ch).

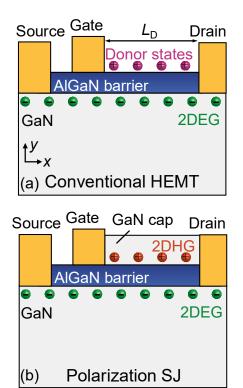

Fig. 1. (a) Schematic of conventional HEMT device and (b) of a Polarization Super Junction HEMT.

charge matching in conventional doping-based super junctions, by relying instead on polarization charges to induce a twodimensional hole gas (2DHG). In PSJ devices, the charge compensation between electrons in the 2DEG and holes in the 2DHG (Fig. 1) results in an overall neutral drift region and thus in a flat off-state electric field profile.

Although PSJ devices have been experimentally demonstrated [10]-[14] and a flat electric field profile intuitively results in improved blocking capabilities, a quantitative analysis of the performance improvement enabled by PSJs with respect to conventional HEMTs is lacking, with current comparisons limited to the case of uniformly doped power devices [4]. This is due to two main reasons. On the one hand, while the on-resistance versus  $V_{BR}$  material limit is often used to show the potential of GaN compared to Si or SiC, such an approach cannot be used to accurately compare GaN HEMT and PSJ devices. In particular, while a uniform off-state field profile is typically assumed to extract the material limit [3], this assumption is not valid for HEMTs which, similarly to doped devices, present fixed charges in the depleted drift region (Fig. 1) [15], [16]. On the other hand, the lack of simple analytical models describing the off-state of PSJs and HEMTs does not allow easily comparing the performance of these devices and

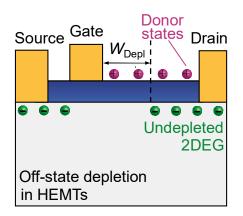

Fig. 2. Carrier depletion during the off-state in a HEMT device.

thus show the potential of polarization super junctions. In addition, an accurate investigation of PSJ switching performance is yet to be reported and some concerns are present due to the large charge depletion that is achieved in such devices, which could hinder their high-frequency operation.

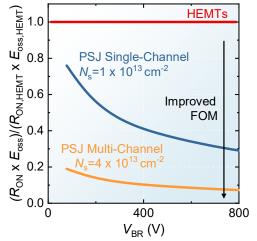

In this work, we provide a detailed analysis and comparison of the main figures-of-merit describing the DC and switching performance of HEMT and PSJ devices. We propose a simple analytical model to describe the off-state behavior of HEMTs and PSJs based on the different carrier depletion mechanisms involved in such devices. From these results, we compare the  $R_{ON,sp}$  vs  $V_{BR}$  performance of PSJs and HEMTs and show that a more than 10-time decrease in  $R_{ON,sp}$  for the same  $V_{BR}$  can be achieved by PSJs with sheet resistance ( $R_{\rm sh}$ ) of 300  $\Omega$ /sq, which can be further improved by the use of multi-channel heterostructures to reduce  $R_{\rm sh}$  down to ~ 80  $\Omega/\text{sq}$  [17]–[22]. In addition, we compare the switching losses of PSJs and HEMTs showing that a significant improvement in the  $R_{\text{ON}} \ge E_{\text{oss}}$  figureof-merit, where  $E_{oss}$  is the energy stored in the device output capacitance, is achieved by PSJ devices both in the case of negligible and dominating parasitic contributions. This model enables a proper evaluation of the main figures-of-merit of lateral GaN power devices and shows the potential of PSJs to reduce both the DC and switching losses in power devices.

### II. MODELING

The main difference in the off-state behavior between PSJs and HEMTs comes from the origin of the 2DEG. In conventional GaN HEMTs, in which no GaN cap (or at most a thin cap of a few nanometers) is present on top of the AlGaN barrier, the source of electrons in the 2DEG are donor states at the interface [15], [16] (Fig. 1 (a)). These states are ionized by the polarization field, donating their electrons to the 2DEG and being left with a positive fixed charge with the same magnitude of 2DEG carrier concentration  $(N_s)$ , similarly to what occurs in usual *n*-type doped semiconductors. On the contrary, in the case of PSJs, the thick GaN cap enables the formation of a 2DHG at the top AlGaN barrier interface having the same carrier concentration of the 2DEG [23], [24] (Fig. 1 (b)). The 2DHG provides the electrons to the 2DEG, without requiring the ionization of the donor states at the top interface. The key difference with respect to conventional HEMTs lies in the fact that the holes in the 2DHG are mobile and thus can be depleted in the off-state (if a proper ohmic contact between the

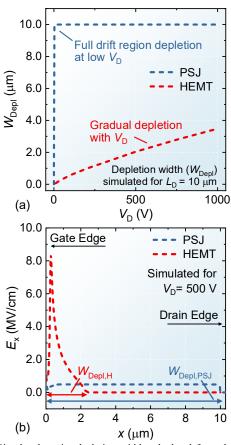

Fig. 3. (a) Simulated carrier depletion width calculated from the gate edge  $(W_{\text{Depl}})$  as a function of the off-state voltage for PSJs and HEMTs having the same drift region length. (b) Simulated off-state electric field profile in the 2DEG region along  $L_D$  for a PSJ and a HEMT device. All the simulation results presented in this work were obtained by employing the Atlas Silvaco software and using its built-in material parameters [52]. The polarization scale has been set to 0.92.

gate/anode and the 2DHG is provided), while ionized donors are fixed charges that affect the off-state electric field profile according to the Poisson equation. This results in a neutral drift region in the off-state for PSJs, while positive fixed charges still remain in the case of HEMTs (Fig. 2).

To model such behaviors, the carrier depletion mechanisms for the two kinds of devices need to be investigated. Figure 3 (a) shows the simulated carrier depletion width ( $W_{\text{Depl}}$ ) (see Fig. 2) as a function of the off-state voltage ( $V_{\text{D}}$ ) for the drift region of a PSJ and HEMT device. It should be noted that the off-state depletion of the drift region of a diode and a transistor are equivalent, which enables employing the same general model for both devices. An intrinsic, 4 µm-thick buffer on an insulating substrate was considered to avoid any early breakdown through the buffer layer and provide a fair comparison between the two architectures. Throughout the manuscript, dashed lines represent simulated results while solid lines are used for the analytical model. Blue lines are employed for PSJs while red is used for HEMTs.

PSJ devices show a complete carrier depletion of the whole drift region length  $(L_D)$  for  $V_D$  of only a few volts (Fig. 3 (a)). Such a depletion occurs for both electrons and holes, resulting in a neutral drift region. HEMTs present, instead, a smaller  $W_{\text{Depl}}$ , which requires much larger  $V_D$  values to grow and more closely resembles the case of doped semiconductors. The two different depletion mechanisms are directly linked to the offThis article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2021.3125742, IEEE Journal of the Electron Devices Society

### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) < 3

state electric field profile in such devices. The efficient carrier depletion and the neutral drift region of PSJs result in a flat electric field profile in the whole  $L_D$  while the smaller  $W_{Depl}$ along with the presence of fixed positive charges in the depletion region lead to a non-uniform electric field profile with a peaked shape for HEMTs (Fig. 3 (b)). While based on these results PSJ devices intuitively should present improved offstate performance, an analytical model describing these devices is necessary to draw more quantitative conclusions while maintaining a detailed understanding of the physical mechanisms involved. In addition, this would enable determining the upper-performance limit of HEMTs and PSJs and properly estimating their potential and figures-of-merit for power conversion applications.

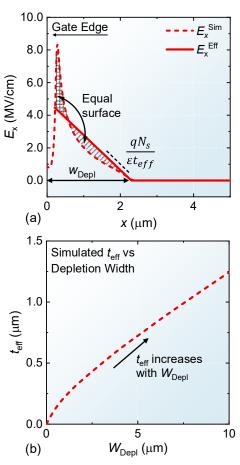

The off-state electric field profile for a HEMT is in general a complicated function due to the device's two-dimensional architecture (Fig. 2). Indeed, while a uniformly-doped semiconductor can be considered as a 1D problem, the presence of a sheet charge requires a two-dimensional treatment. Typical mathematical methods to address this problem are based on conformal mapping methods [25]-[29], which however result in very complicated and non-analytical solutions. Here, we propose a simplified approach that results in an analytical solution enabling direct comparison with PSJs, while still accurately describing the physical mechanisms that determine the device operation. In particular, the HEMT off-state electric field ( $E_{x,HEMT}$ ) along the drift region direction (x) in the 2DEG region is approximated by a linear function having  $W_{\text{Depl}}$  as xaxis intercept and a slope such that the voltage drop in the depleted region is conserved (Fig. 4 (a)). The resulting expression is:

$$E_{\rm x, HEMT} = \frac{q_{N_{\rm s, HEMT}}}{\varepsilon t_{\rm eff}} \left( x - W_{\rm Depl} \right)$$

(1)

where q is the magnitude of the electronic charge,  $N_{s,HEMT}$  is the 2DEG concentration in the HEMT device and  $\varepsilon$  is GaN dielectric constant.  $t_{eff}$  is a geometrical parameter (in cm) which accounts for the electric field extension in the vertical direction due to its 2D distribution between the gate electrode and the undepleted 2DEG. This model enables us to treat a HEMT similarly to a conventional 1D doped device, greatly simplifying the mathematical expressions. It should be noted that the assumption of a linear field overestimates the breakdown voltage of HEMT devices, which in reality presents a more peaked electric field profile. However, since the goal of this work is to present the potential of PSJs with respect to conventional HEMT structures, this assumption only results in an underestimation of the performance improvement brought by PSJ. Besides, this model represents an improvement compared to previous works, in which the  $E_x$  profile of HEMTs is assumed to be flat in the whole drift region [3]. Such a hypothesis is not physically accurate due to the presence of ionized donor states with a positive charge and actually describes the case of PSJ devices, preventing a fair comparison between the two device architectures. The geometrical parameter t<sub>eff</sub> accounts for the 2D distribution of the electric field between the gate electrode and the edge of the undepleted 2DEG. For this reason, it only depends on the device's geometrical parameters, such as the gate metal thickness and the dielectric constant of the passivation layer, and the depletion

Fig. 4. (a) Simulated off-state electric field  $(E_x^{Sim})$  along  $L_D$  in the 2DEG region for a HEMT device and corresponding approximated linear field profile  $(E_x^{Eff})$ assumed in the model (b)  $t_{eff}$  as a function of the depletion width extracted from the device simulation.

width, i.e. the separation between the gate electrode and the undepleted 2DEG. In particular,  $t_{\rm eff}$  increases as  $W_{\rm Depl}$  grows due to the more 2D shape of the electric field (Fig. 4 (b)).  $t_{\rm eff}$  is instead independent of the specific combination of  $N_{\rm s}$  and  $V_{\rm D}$  that was required to achieve a certain depletion width. Indeed, such a combination only influences the magnitude of the electric field but not its distribution. While a mathematical formula for  $t_{\rm eff}$  is challenging to obtain, its value can be determined from simulation by extracting the  $W_{\rm Depl}$  for a certain off-state voltage  $V_{\rm D}$  (Fig. 3 (a)) and using the expression:

$$t_{\rm eff} = \frac{q N_{\rm s, \rm HEMT} W_{\rm Depl}^2}{2 \varepsilon V_{\rm D}} \tag{2}$$

which is derived from eq. (1). Figure 4 (b) shows  $t_{\rm eff}$  as a function of the depletion width for a HEMT with a 30 nm-thick Al<sub>0.25</sub>GaN barrier, 100 nm-thick gate contact, and 200 nm-thick Si<sub>3</sub>N<sub>4</sub> passivation layer. Since the field distribution, and thus  $t_{\rm eff}$ , depends on the exact device structure, slight adjustments to  $t_{\rm eff}$  may be required in case a very different device architecture is used. However, for conventional device architectures, variations of  $t_{\rm eff}$  well below 10 % are expected.

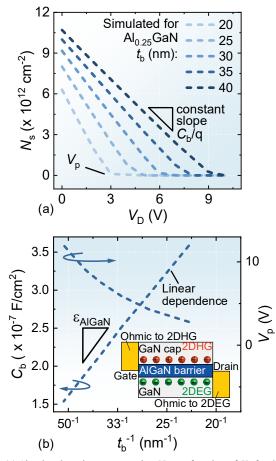

To model the off-state behavior of PSJs, the carrier depletion in these devices needs to be properly described. Figure 5 (a) shows the  $N_s$  as a function of the off-state voltage for different Al<sub>0.25</sub>GaN barrier thicknesses ( $t_b$ ). While the  $N_s$  value at equilibrium ( $V_D = 0$  V) increases for larger  $t_b$ , the carrier depletion varies linearly with the off-state voltage for all barrier

Fig. 5. (a) Simulated carrier concentration  $N_s$  as a function of  $V_D$  for different Al<sub>0.25</sub>GaN barrier thicknesses.  $N_s$  was extracted by integrating the electron concentration in the 2DEG region along the vertical direction. A cut in the middle of the device's drift region was taken to avoid any possible carrier depletion from the contacts. (b) Barrier capacitance ( $C_b$ ) and PSJ pinch off-voltage ( $V_p$ ), extracted from Figure 5 (a), as a function of the barrier thickness. The bottom-right inset shows a schematic of the simplified parallel plate capacitor model used to describe carrier depletion in PSJ devices.

thicknesses, which can be described by introducing an effective barrier capacitance ( $C_b$ ) from the linear fit of the  $N_s$  vs  $V_D$  curve. Figure 5 (b) shows that  $C_b$ , extracted from Fig. 5 (a), increases linearly with the inverse of the barrier thickness  $(t_b^{-1})$ , with a slope equal to the dielectric constant of the AlGaN barrier. This behavior allows us to model the carrier depletion in PSJs with a simple parallel plate capacitor having the barrier as the insulator between the sheet charges of the 2DHG and 2DEG, with the gate providing an ohmic contact to the 2DHG and the drain to the 2DEG (Fig. 5 (b) inset). The 2DHG can be seen as acting similarly to a usual gate that forms a parallel-plate capacitor and uniformly depletes the 2DEG over the whole drift region, with a threshold voltage comparable to that of a typical Schottky gate. It should be noted that such a model is valid because of the small pinch-off voltage  $(V_p)$  required to completely deplete PSJ devices (Fig. 5 (b)) and the large Schottky barrier present between the drain metal and the 2DHG. In this condition, the conventional lateral depletion at the edges of the electrodes is negligible with respect to the drift region length and no significant leakage is present through the Schottky barrier. Besides, the barrier thickness is much smaller than  $L_{\rm D}$ , which allows neglecting the parasitic capacitance between the two electrodes. The pinch-off voltage is only a few

Volts for any realistic value of AlGaN barrier thickness (Fig. 5 (b)) and could be further reduced by employing higher polarization materials in the barrier, such as InAlN or AlN, which enable reducing  $t_b$  for a given  $N_s$ . Thanks to the small value of  $V_p$  compared to the breakdown voltage values considered in this work, the off-state electric field profile can be considered approximately flat in the whole PSJ drift region ( $L_{D,PSJ}$ ) and be given by:

$$E_{\rm x,PSJ} = -\frac{V_{\rm D}}{L_{\rm D,PSJ}} \tag{3}$$

### III. STATIC FIGURE-OF-MERIT COMPARISON

Based on the electric field profiles for HEMTs and PSJs described in eqs. (1) and (3), we can compare the DC performance of the devices. It should be noticed that TCAD simulation was only employed to extract the  $t_{eff}$  parameter and to show the different physical mechanisms involved. The following analysis on the device figure-of-merit is entirely based on an analytical treatment. The breakdown voltage is typically obtained by considering the onset of avalanche breakdown by impact ionization, with the ionization integral being simplified by using Fulop's power law [3], [30]. Solving the resulting ionization integral using eqs. (1) and (3) and considering a complete depletion of the drift region, as in the case of a well-designed power device, one obtains a relation between  $V_{BR}$  and the drift region length for both device types, as described in [3]:

$$V_{\rm BR,PSJ}$$

[V] = 0.94 x 10<sup>6</sup>  $L_{\rm D,PSI}^{6/7}$  [cm] (4)

$$V_{\rm BR,HEMT}$$

[V] = 0.63 x 10<sup>6</sup>  $L_{\rm D,HEMT}^{6/7}$  [cm] (5)

These expressions, which depend only on the  $E_x$  profile and not on the carrier concentration, set an important link between the drift region length of PSJs and HEMTs. In particular, for a given  $V_{BR}$ ,  $L_{D,PSJ} = 0.67 \times L_{D,HEMT}$ , which means that PSJ devices can have a shorter drift region to hold the same voltage thanks to the improved off-state electric field profile. Besides, one obtains also a relation between  $V_{BR}$  and  $N_s$  for HEMTs

$$V_{\rm BR, HEMT}[V] = 2.5 \ge 10^{15} \ge (N_{\rm s, HEMT}[\rm cm^{-2}]/t_{eff}[\rm cm])^{-3/4}(6)$$

while, thanks to the very small value of  $V_p$  for any realistic carrier concentration, in a first approximation  $V_{BR}$  does not depend on  $N_s$  in PSJs.

For a lateral device, the specific on-resistance  $(R_{ON,SP})$  is given by:

$$R_{\rm ON,SP} = \frac{L_{\rm D}^2}{q\mu N_{\rm s}} \tag{7}$$

with  $\mu$  the electron mobility. By inserting eq. (4) (for a PSJ) and eq. (5-6) (for a HEMT) in eq. (7), one can extract the expression of the device minimum  $R_{ON,SP}$  achievable for a certain  $V_{BR}$ , which represents the main figure-of-merit to assess the upper-performance limit of power devices:

$$R_{\rm ON,sp,HEMT} \left[\Omega \, \mathrm{x} \, \mathrm{cm}^2\right] = \frac{5.2 \, \mathrm{x} \, \mathrm{10^{-16}}}{\mu [\mathrm{cm}^2/\mathrm{Vs}] t_{\mathrm{eff}} [\mathrm{cm}]} V_{\mathrm{BR}}^{11/3} [\mathrm{V}] \quad (8)$$

$$R_{\rm ON,sp,PSJ} \left[\Omega \ge cm^2\right] = 1.15 \ge 10^{-14} \ge R_{\rm sh} \left[\Omega\right] V_{\rm BR}^{7/3} [\rm V] \ (9)$$

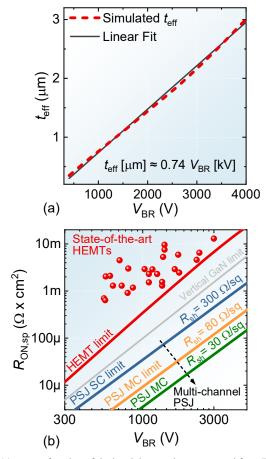

Fig. 6. (a)  $t_{\rm eff}$  as a function of the breakdown voltage extracted from Fig. 4 (b) and eq. (5), and corresponding linear fit (in black). (b)  $R_{\rm ON,SP}$  vs  $V_{\rm BR}$  benchmark for HEMTs and PSJs with single and multiple channel heterostructures (SC and MC respectively) calculated from eqs. (8) and (9). Electron mobility of 2000 cm<sup>2</sup>/Vs was used. The solid lines represent the calculated theoretical limits for each architecture while the performance of state-of-the-art HEMTs devices in literature is reported in red dots.

where  $R_{\rm sh}$  is the heterostructure sheet resistance  $(R_{\rm sh} = 1/q\mu N_{\rm s})$ . To obtain  $t_{\rm eff}$  as a function of  $V_{\rm BR}$ , one can apply eq. (5) to Fig. 4 (b) in order to link  $W_{\rm Depl}$  to  $V_{\rm BR}$  since, for a well-designed power HEMT,  $W_{\rm Depl}$  corresponds to  $L_{\rm D}$  at the breakdown. Fig 6 (a) shows the dependence of  $t_{\rm eff}$  on  $V_{\rm BR}$ , which can be inserted in eq. (8) to plot HEMTs' specific on-resistance (Fig. 6 (b)). To further simplify eq. (8) and obtain a more general expression, one can approximate  $t_{\rm eff}$  as a linear function of  $V_{\rm BR}$  (Fig. 6 (a)). In addition, eq. (9) can be expressed as a function of  $N_{\rm s}$  to offer a direct comparison between  $R_{\rm ON,sp,HEMT}$  and  $R_{\rm ON,sp,PSJ}$ :

$$\left(R_{\rm ON,sp,HEMT}[\Omega \, \mathrm{x} \, \mathrm{cm}^2] = \frac{7 \, x \, 10^{-9}}{\mu \left[\frac{\mathrm{cm}^2}{\mathrm{Vs}}\right]} V_{\rm BR}^{8/3}[\mathrm{V}]$$

(10)

$$R_{\rm ON,sp,PSJ} \left[ \Omega \ge cm^2 \right] = \frac{0.72 \ge 10^5}{\mu \left[ \frac{cm^2}{\rm Vs} \right] N_{\rm S} \left[ cm^{-2} \right]} V_{\rm BR}^{7/3} [\rm V] \qquad (11)$$

Finally, the reduction in the specific on-resistance for PSJs compared to HEMTs can be derived considering the ratio between eqs. (11) and (10) and assuming the same mobility for the two devices:

$$\frac{R_{\rm ON,sp,PSJ}}{R_{\rm ON,sp,HEMT}} = \frac{1}{N_{\rm s} [x \, 10^{13} \rm cm^{-2}] V_{\rm BR}^{1/3} [V]}$$

(12)

A significant improvement in the  $R_{ON,SP}$  vs  $V_{BR}$  limit can be achieved by PSJs using conventional AlGaN/GaN singlechannel heterostructures. For instance,  $R_{ON,SP,PSJ}$  can be reduced up to 10 times compared to RON, SP, HEMT for typical heterostructures having  $R_{\rm sh} \sim 300 \ \Omega/{\rm sq}$  (or  $N_{\rm s} \sim 1 \ {\rm x} \ 10^{13} \ {\rm cm}^{-2}$ ) for a breakdown voltage of 1000 V (Fig. 6 (b)), with a further reduction when devices with larger  $V_{BR}$  are considered (eq. (12)). It should be noted that often the electric field profile of HEMT devices is approximated to be flat in the whole  $L_{\rm D}$ , which however erroneously results in the same  $R_{ON,SP}$  vs  $V_{BR}$ limit as for PSJ devices. Nevertheless, as previously explained, such an assumption is not physically accurate and leads to an overestimation of the potential of HEMT devices. This explains why real HEMTs present performance very far from this limit, which is instead properly described by the proposed model (Fig. 6 (b)).

In addition, we observe that for HEMTs, the  $V_{\rm BR}$  depends on  $N_{\rm s}$  (see eq. (6)) and thus the carrier concentration does not appear in eqs. (8) and (10). This is the usual situation for conventional semiconductor devices for which there is a tradeoff between the carrier concentration and the blocking capabilities. On the contrary,  $R_{\rm sh}$  (and thus  $N_{\rm s}$ ) does not affect the off-state electric field (eq. (3)) and the breakdown voltage for PSJs (eqs. (9) and (11)), which allows increasing the device conductivity without degrading its blocking performance. While, one could achieve a low sheet resistance in conventional single-channel heterostructures by proper design of an AlN or AllnN barrier, a more effective way to significantly reduce the heterostructure  $R_{\rm sh}$  is by using multiple parallel channels, which enable to increase the carrier concentration without degrading the mobility [17], [18], [31]. Besides, the growth of the multichannel structure typically requires only a small increase in the growth time compared to the rest of the heterostructure, thus providing a cost-effective solution to significantly reduce the on-resistance in power devices. Following this approach, AlGaN/GaN multi-channel heterostructures with  $R_{\rm sh} \sim 80 \ \Omega/{\rm sq}$ have been shown experimentally, both with doped and undoped barrier layers, and power devices based on these structures have been demonstrated [17]-[21], revealing the feasibility in achieving high voltages in such high conductivity structures. Further increase in the number of channels and higher polarization barrier materials (such as lattice-matched InAlN [32] and AlN [33]) have resulted in structures with  $R_{\rm sh}$  value down to ~ 30  $\Omega$ /sq. As shown in Fig. 6 (b), the reduced sheet resistance of multi-channel PSJ devices would enable a considerable improvement in the  $R_{ON,SP}$  vs  $V_{BR}$  trade-off, resulting in a decrease of the device resistance without affecting its off-state behavior.

## IV. SWITCHING LOSSES COMPARISON

The different carrier depletion mechanisms in HEMTs and PSJs directly affect the device output capacitance ( $C_{oss}$ ), which largely determines its switching losses. In particular, during hard switching, the energy stored in  $C_{oss}$  ( $E_{oss}$ ) is dissipated at each switching cycle, resulting in the following expression for the hard-switching losses [34]–[36] (where losses during the

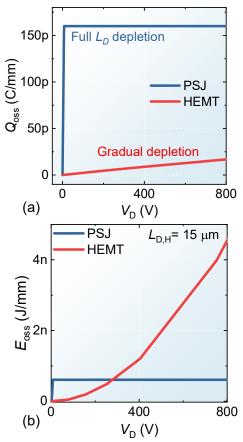

Fig. 7. (a)  $Q_{\text{oss}}$  and (b)  $E_{\text{oss}}$  as a function of  $V_{\text{D}}$  for HEMT and PSJ devices in the case of negligible  $C_{\text{p}}$  calculated from eqs. (16) and (17).

turn-off are typically negligible for GaN devices and thus not considered [37], [38]):

$$P_{\rm SW} = f E_{\rm oss} + P_{\rm IV} \tag{13}$$

where f is the operating frequency and  $P_{IV}$  is a term related to the current-voltage overlap during the switching transition.

The device  $C_{oss}$  can be modeled as the sum of a first term describing the carrier depletion in the drift region [25], [39], [40] (which depends on  $V_D$ ), and a second contribution ( $C_p$ ) related to the device geometry and the parasitic capacitance terms (which is independent on voltage) [25], [41]. According to the previous analysis on the carrier depletion (Fig. (4-5)), we can approximate  $C_{oss}$  as a step function for PSJs and as an increasing function  $\sim 1/\sqrt{V_D}$  for HEMTs:

$$C_{\text{oss,PSJ}} = \begin{cases} C_{\text{b}}L_{\text{D,PSJ}} + C_{\text{p}} & \text{for } V_{\text{D}} \le V_{\text{p}} \\ C_{\text{p}} & \text{for } V_{\text{D}} > V_{\text{p}} \end{cases}$$

(14)

$$C_{\rm oss, HEMT} = \sqrt{\frac{q\varepsilon t_{\rm eff} N_{\rm s, HEMT}}{2V_{\rm D}}} + C_{\rm p}$$

(15)

By integrating eqs. (14) and (15) with respect to  $V_{\rm D}$ , the device output charge  $Q_{\rm oss}$  is obtained, and a second integration results in  $E_{\rm oss}$ :

$$E_{\text{oss,PSJ}} = \begin{cases} \frac{1}{2} C_{\text{b}} V_{\text{D}}^{2} L_{\text{D,PSJ}} + \frac{1}{2} C_{\text{p}} V_{\text{D}}^{2} & \text{for } V_{\text{D}} \le V_{\text{p}} \\ \frac{1}{2} C_{\text{b}} V_{\text{p}}^{2} L_{\text{D,PSJ}} + \frac{1}{2} C_{\text{p}} V_{\text{D}}^{2} & \text{for } V_{\text{D}} > V_{\text{p}} \end{cases}$$

(16)

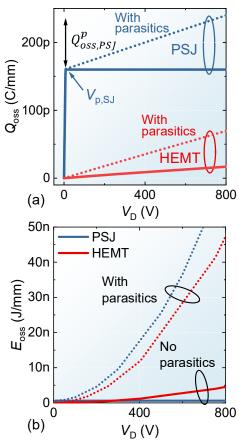

Fig. 8. (a)  $Q_{oss}$  and (b)  $E_{oss}$  as a function of  $V_D$  for HEMT and PSJ devices for a negligible (solid lines) and non-negligible (dotted lines) parasitic capacitance contribution calculated from eqs. (16) and (17).  $C_p$  was set to 1 pF/cm for PSJs and 0.66 pF/cm for HEMTs, which reflects the different  $L_D$  required by the two devices to achieve the same  $V_{BR}$ .

$$E_{\text{oss,HEMT}} \ge \frac{\sqrt{2\epsilon q N_{\text{s,HEMT}} t_{\text{eff}}}}{3} V_{\text{D}}^{3/2} + \frac{1}{2} C_{\text{p}} V_{\text{D}}^2$$

(17)

where the  $\geq$  sign in eq. (17) results from assuming  $t_{\text{eff}}$  to be an increasing function with  $V_{\text{D}}$ , which is verified in Fig. 4 (b) and Fig. 6 (a). In order to analyze this result, two different cases will be considered, i.e. the situation in which the carrier depletion is the main term in  $C_{\text{oss}}$  ( $C_{\text{p}}$  negligible) and the case in which  $C_{\text{p}}$  is instead the dominant term. The relative magnitude of the two terms can strongly depend on the device structure and its packaging strategy, making it useful to consider both cases. Besides, to compare devices having the same  $V_{\text{BR}}$ , eqs. (4), (5) and (6) will be considered, which impose  $L_{\text{D,PSJ}} = 0.67 \times L_{\text{D,HEMT}}$  and set a relation between the HEMT carrier density and its  $V_{\text{BR}}$ .

The output charge for a negligible  $C_p$  is shown in Fig. 7 (a). Since  $Q_{oss}$  directly depends on the depletion width, a similar behavior as in Fig. 3 (a) is observed, with the PSJ output charge increasing sharply with  $V_D$  until the full drift region depletion at  $V_D = V_p$  and with the HEMT  $Q_{oss}$  gradually rising over the whole  $V_D$  range. These differences in the  $Q_{oss}$  vs  $V_D$  profile result in an  $E_{oss}$  value that is larger for PSJs at low operating voltages but becomes much smaller than that of HEMTs when large  $V_D$  values are considered (Fig. 7 (b)). In particular, comparing the important switching figure-of-merit (FOM)  $R_{ON}$

Fig. 9. Ratio between the  $R_{\rm ON}$  x  $E_{\rm oss}$  figure-of-merit for PSJs and HEMTs in the case of non-negligible parasitic capacitance contributions calculated from eq. (19).

x  $E_{oss}$  at the device rated voltage for PSJs and HEMTs, an important relationship is obtained:

$$\frac{R_{\rm ON,PSJ} \times E_{\rm oss,PSJ}}{R_{\rm ON,HEMT} \times E_{\rm oss,HEMT}} = 0.67 \frac{V_{\rm p}}{V_{\rm BR}} \quad \text{for} \quad C_{\rm p} = 0 \quad (18)$$

Since the PSJs pinch-off voltage  $V_p$  is much smaller than the breakdown voltage of typical power devices (Fig. 5 (b)), PSJs enable to achieve a significant reduction in the  $R_{ON} \ge E_{OSS}$  FOM, which increases as devices with larger voltage ratings are considered.

In real power devices, parasitic capacitance contributions to  $C_{\text{oss}}$  related to the device geometry rather than the drift region depletion can become significant depending on the device architecture. While an exact estimation requires the precise knowledge of the device structure, here a  $C_p$  of 1 pF/cm for  $L_{\text{D,PSJ}}$  of 10 µm is assumed, which is a typical value for multifinger scaled-up devices [25], [27]. Besides, we consider  $C_p \sim 1/L_D$ , resulting in a  $C_p$  value of 0.66 pF/cm for  $L_{\text{D,HEMT}}$  of 15 µm. This assumption is favorable for HEMTs as parasitic terms usually have a weaker dependence on  $L_D$  for typical device dimensions [25], [27], [42].

Figure 8 (a) presents  $Q_{oss}$  as a function of  $V_D$  for nonnegligible  $C_p$ . As a result of the parasitic contributions, an increase of  $Q_{oss}$  is observed, which is larger for PSJs due to the shorter drift region length. The corresponding  $E_{oss}$  vs  $V_D$  curves are presented in Fig. 8 (b), which shows a dominant contribution from the  $C_p$  term with respect to the depletion contribution. In this situation, PSJs present a larger  $E_{oss}$  value, due to their shorter  $L_D$ . However, a fair comparison between the two devices requires considering the  $R_{ON} \times E_{oss}$  FOM:

$$\frac{R_{\rm ON,PSJ} \times E_{\rm oss,PSJ}}{R_{\rm ON,HEMT} \times E_{\rm oss,HEMT}} = \frac{3.4 \times 10^{20} \times t_{\rm eff}[\rm cm]}{N_{\rm s,PSJ}[\rm cm^{-2}] V_{\rm BR}^{4/3}[\rm V]}$$

(19)

which can be further simplified in case the linear fit of  $t_{\text{eff}}$  vs  $V_{\text{BR}}$  (Fig. 6 (a)) is used:

$$\frac{R_{\rm ON,PSJ} \ge E_{\rm oss,PSJ}}{R_{\rm ON,HEMT} \ge E_{\rm oss,HEMT}} = \frac{2.5}{N_{\rm s,PSJ}[\ge 10^{13} \rm cm^{-2}] V_{\rm BR}^{1/3}[V]}$$

(20)

The decoupling of  $N_s$  from the off-state performance for PSJ devices results in a better  $R_{ON} \ge E_{OSS}$  FOM, which improves as

the device  $V_{\rm BR}$  increases (Fig. 9). Besides, by employing multichannel structures with larger  $N_{\rm s}$  it is possible to further reduce  $R_{\rm ON} \ge R_{\rm oss}$  to values 10 times lower than for HEMT devices.

Finally, for what concerns the  $P_{IV}$  contribution in eq. (13), this term is proportional to the external load current and is linked to the time required to discharge  $C_{oss}$  through the device channel. This time is usually determined by the circuit operation and by the addition of an external gate resistor to control the dV/dt. In these conditions, HEMTs and PSJs would exhibit similar  $P_{\rm IV}$  as this term is entirely controlled by the external circuit. However, in the absence of a gate resistor or in the case of very low gate-path resistance, the transition speed depends only on the device properties. In this case, the strong non-linearity of  $C_{oss}$  for PSJ devices (see eq. (14)) results in a reduced overlap term at high voltages with respect to HEMTs. This is due to the efficient carrier depletion in PSJs, which leads to a very low  $C_{oss}$  value for off-state voltages above the pinchoff and translates in a reduction of the  $P_{\rm IV}$  overlap term compared to HEMTs, similarly to what has been reported for Si devices [43]. Thus, since for PSJ devices the  $P_{IV}$  term is smaller or equal than for HEMTs while the  $E_{oss}$  contribution is muchreduced for any condition, we can conclude that PSJs result in a significant decrease of the overall switching losses.

### V. MODEL BOUNDARIES

GaN lateral devices typically present a large density of traps at the heterostructure top interface. Electrons trapped in these surface states during the off-state partly deplete the 2DEG close to the gate edge and alleviate the electric field peak, resulting in an improvement of the device breakdown voltage [44]-[47] through a virtual gate effect. Yet, this mechanism is highly undesirable as it degrades the device resistance in the on-state, resulting in current collapse phenomena [48], [49]. A similar reasoning can also be applied to trap states in the buffer layer, which are often introduced to increase its resistivity but can act as trapping centers for electrons in the 2DEG. Thus, a more meaningful indicator of the device performance is represented by the dynamic on-resistance rather than the DC  $R_{ON}$ , which does not take into account trapping effects. In this work, the presence of trap states has not been considered as the exact estimation of their density and energy level is highly dependent on the device design and passivation strategy. However, all the analyses here reported remain valid by simply replacing  $R_{ON}$ with the dynamic on-resistance (R<sub>ON,dyn</sub>) measured for experimental devices.

GaN layers also present a certain concentration of unintentional impurities (e.g. Si or O) due to contaminations during the growth, which can act as fixed net charges and affect the electric field profile. Nevertheless, recent advances in MOCVD growth have enabled impurity concentrations as low as  $3 \times 10^{15}$  cm<sup>-3</sup> [50], [51], preventing significant effects on the device's off-state behavior. In this work, the role of impurities has not been included since their concentration can vary significantly depending on the growth technique and parameters, which prevents drawing any general conclusion. However, in the case of a significant presence of impurities, this can be readily accounted for in the presented equations by including an additional fixed net charge term.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2021.3125742, IEEE Journal of the Electron Devices Society

# > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) < 8

Finally, GaN HEMTs usually also have few field plate (FP) structures. While the analytical treatment of field plates is rather straightforward [25], [28], their design varies significantly from device to device making it difficult to provide a general model. Yet, some considerations can be drawn. One of the main goals of FPs is to reduce the electric field peak at the gate edge. While the field profile in the FPs region differs from the one here presented, FPs typically extend only for a few microns and the majority of the off-state voltage falls on the portion of the drift region without FP. This situation is well described by the proposed model, which can be extended to include the presence of FPs [25], [28] once the precise device structure under investigation is known. Finally, the use of FPs results in an increased  $C_{oss}$  parasitic contribution ( $C_p$ ) due to the reduced distance between electrodes, which increases the switching losses and poses an additional trade-off between  $E_{oss}$  and the blocking performance. The proposed model and analysis offer precious general insights into the operation mechanisms of two investigated devices and can be easily adapted to a specific device architecture, once its precise structure is known.

### VI. CONCLUSIONS

In this work, we provided a detailed analysis and comparison of the main figures-of-merit describing the DC and switching performance of HEMT and PSJ devices. We proposed a simple analytical model to describe the off-state behavior of HEMTs and PSJs based on the different carrier depletion mechanisms involved in such devices. Based on these results, we showed that a 10-time decrease in  $R_{ON,sp}$  for the same  $V_{BR}$  can be achieved by single-channel PSJs, which can be further improved by the use of multi-channel heterostructures to reduce the sheet resistance. In addition, we compared the switching losses of PSJs and HEMTs showing that PSJ devices result in a significant improvement in the  $R_{ON} \ge E_{oss}$  figure-of-merit both in the case of negligible and dominating parasitic contributions. This model enables a proper evaluation of the main figures-ofmerit of lateral GaN power devices and shows the potential of PSJs to reduce both the DC and switching losses in power devices.

### REFERENCES

- K. J. Chen, O. Haberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si power technology: Devices and applications," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 779– 795, 2017, doi: 10.1109/TED.2017.2657579.

- [2] H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, R. Chu, C. De Santi, and M. M. De Souza, "The 2018 GaN power electronics roadmap," J. Phys. D. Appl. Phys., vol. 51, p. 163001, 2018.

- [3] B. J. Baliga, "Gallium nitride devices for power electronic applications," *Semicond. Sci. Technol.*, vol. 28, no. 7, 2013, doi: 10.1088/0268-1242/28/7/074011.

- [4] A. Nakajima, K. Adachi, M. Shimizu, and H. Okumura, "Improvement of unipolar power device performance using a polarization junction," *Appl. Phys. Lett.*, vol. 89, no. 19, pp. 87–90, 2006, doi: 10.1063/1.2372758.

- [5] H. Ishida, D. Shibata, M. Yanagihara, Y. Uemoto, H. Matsuo, T. Ueda, T. Tanaka, and D. Ueda, "Unlimited high breakdown voltage by natural super junction of polarized semiconductor," *IEEE Electron Device Lett.*, vol. 29, no. 10, pp. 1087–1089, 2008, doi: 10.1109/LED.2008.2002753.

- [6] S. Han, J. Song, and R. Chu, "Design of GaN/AlGaN/GaN Super-Heterojunction Schottky Diode," *IEEE Trans. Electron Devices*, vol. 67, no. 1, pp. 69–74, 2020, doi: 10.1109/TED.2019.2953843.

- [7] B. Song, M. Zhu, Z. Hu, K. Nomoto, D. Jena, and H. Xing, "Design and optimization of GaN lateral polarization-doped super-junction (LPSJ): An analytical study," *Proc. Int. Symp. Power Semicond. Devices ICs*, vol. 2015-June, pp. 273–276, 2015, doi: 10.1109/ISPSD.2015.7123442.

- [8] H. Huang, J. Cheng, B. Yi, W. Zhang, and W. T. Ng, "A unified model for vertical doped and polarized superjunction GaN devices," *Appl. Phys. Lett.*, vol. 116, no. 10, 2020, doi: 10.1063/1.5142855.

- [9] X. Zhou, J. R. Howell-Clark, Z. Guo, C. W. Hitchcock, and T. P. Chow, "Performance limits of vertical GaN of conventional doped pn and natural polarization superjunction devices," *Appl. Phys. Lett.*, vol. 115, no. 11, 2019, doi: 10.1063/1.5109389.

- [10] A. Nakajima, Y. Sumida, M. H. Dhyani, H. Kawai, and E. M. Narayanan, "GaN-based super heterojunction field effect transistors using the polarization junction concept," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 542–544, 2011, doi: 10.1109/LED.2011.2105242.

- [11] H. Kawai, S. Yagi, S. Hirata, F. Nakamura, T. Saito, Y. Kamiyama, M. Yamamoto, H. Amano, V. Unni, and E. M. S. Narayanan, "Low cost high voltage GaN polarization superjunction field effect transistors," *Phys. Status Solidi Appl. Mater. Sci.*, vol. 214, no. 8, 2017, doi: 10.1002/pssa.201600834.

- [12] B. Shankar and M. Shrivastava, "Safe Operating Area of Polarization Super-junction GaN HEMTs and Diodes," *IEEE Trans. Electron Devices*, vol. 66, no. 10, pp. 4140–4147, 2019, doi: 10.1109/TED.2019.2933362.

- [13] S. W. Han, J. Song, S. H. Yoo, Z. Ma, R. M. Lavelle, D. W. Snyder, J. M. Redwing, T. N. Jackson, and R. Chu, "Experimental Demonstration of Charge- Balanced GaN Super-Heterojunction Schottky Barrier Diode Capable of 2.8 kV Switching," *IEEE Electron Device Lett.*, vol. 41, no. 12, pp. 1758–1761, 2020, doi: 10.1109/LED.2020.3029619.

- [14] V. Unni, H. Long, M. Sweet, A. Balachandran, E. M. S. Narayanan, A. Nakajima, and H. Kawai, "2.4kV GaN Polarization Superjunction Schottky Barrier Diodes on semi-insulating 6H-SiC substrate," *Proc. Int. Symp. Power Semicond. Devices ICs*, pp. 245–248, 2014, doi: 10.1109/ISPSD.2014.6856022.

- [15] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors," *Appl. Phys. Lett.*, vol. 77, no. 2, 2000, doi: 10.1063/1.126940.

- [16] S. Heikman, S. Keller, Y. Wu, J. S. Speck, S. P. DenBaars, and U. K. Mishra, "Polarization effects in AlGaN/GaN and GaN/AlGaN/GaN heterostructures," *J. Appl. Phys.*, vol. 93, no. 12, pp. 10114–10118, 2003, doi: 10.1063/1.1577222.

- [17] L. Nela, C. Erine, P. Xiang, V. Tileli, T. Wang, K. Cheng, and E. Matioli, "Multi-channel nanowire devices for efficient power conversion," *Nat. Electron.*, 2021, doi: 10.1038/s41928-021-00550-8.

- [18] J. Ma, C. Erine, M. Zhu, L. Nela, P. Xiang, K. Cheng, and E. Matioli, "1200 V Multi-Channel Power Devices with 2.8 Ω·mm ON-Resistance," 2019 IEEE Int. Electron Devices Meet., 2019, doi: 10.1109/IEDM19573.2019.8993536.

- [19] L. Nela, H. K. Yildirim, C. Erine, R. Van Erp, P. Xiang, K. Cheng, and E. Matioli, "Conformal passivation of Multi-Channel GaN power transistors for reduced current collapse," *IEEE Electron Device Lett.*, vol. 42, no. 1, pp. 1–1, 2020, doi: 10.1109/led.2020.3038808.

- [20] J. Ma, C. Erine, P. Xiang, K. Cheng, and E. Matioli, "Multi-channel tri-gate normally-on / off AlGaN / GaN MOSHEMTs on Si substrate with high breakdown voltage and low ON-resistance," *Appl. Phys. Lett.*, vol. 113, no. 242102, pp. 1–5, 2018, doi: 10.1063/1.5064407.

- [21] J. Ma, G. Kampitsis, P. Xiang, K. Cheng, and E. Matioli, "Multi-Channel Tri-gate GaN Power Schottky Diodes with Low ON-Resistance," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 275–278, 2018, doi: 10.1109/LED.2018.2887199.

- [22] M. Xiao, Y. Ma, K. Cheng, K. Liu, A. Xie, E. Beam, Y. Cao, and Y. Zhang, "3.3 kV Multi-Channel AlGaN/GaN Schottky Barrier Diodes With P-GaN Termination," *IEEE Electron Device Lett.*, vol. 41, no. 8, pp. 1177–1180, 2020, doi: 10.1109/LED.2020.3005934.

- [23] A. Nakajima, P. Liu, M. Ogura, T. Makino, K. Kakushima, S. I. Nishizawa, H. Ohashi, S. Yamasaki, and H. Iwai, "Generation and transportation mechanisms for two-dimensional hole gases in GaN/AlGaN/GaN double heterostructures," *J. Appl. Phys.*, vol. 115, no. 15, 2014, doi: 10.1063/1.4872242.

- [24] P. Liu, K. Kakushima, H. Iwai, A. Nakajima, T. Makino, M. Ogura, S. Nishizawa, and H. Ohashi, "Characterization of two-dimensional

hole gas at GaN/AlGaN heterointerface," *1st IEEE Work. Wide Bandgap Power Devices Appl. WiPDA 2013 - Proc.*, pp. 155–158, 2013, doi: 10.1109/WiPDA.2013.6695585.

- [25] D. Čučak, M. Vasić, O. García, J. A. Oliver, P. Alou, J. A. Cobos, A. Wang, S. Martín-Horcajo, M. F. Romero, and F. Calle, "Physics-Based Analytical Model for Input, Output, and Reverse Capacitance of a GaN HEMT With the Field-Plate Structure," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2189–2202, 2017, doi: 10.1109/TPEL.2016.2569404.

- [26] D. Cucak, M. Vasic, O. Garcia, Y. Bouvier, J. Oliver, P. Alou, J. A. Cobos, A. Wang, S. Martin-Horcajo, F. Romero, and F. Calle, "Physical model for GaN HEMT design optimization in high frequency switching applications," *Eur. Solid-State Device Res. Conf.*, pp. 393–396, 2014, doi: 10.1109/ESSDERC.2014.6948843.

- [27] D. Čučak, "Physics-based Analytical Modelling and Optimization of the GaN HEMT with the Field-Plate Structure for Application in High-Frequency Switching Converters," 2017.

- [28] J. Liu, Y. Guo, J. Zhang, J. Yao, X. Huang, C. Huang, Z. Huang, and K. Yang, "Analytical model for the potential and electric field distributions of AlGaN/GaN HEMTs with gate-connected FP based on Equivalent Potential Method," *Superlattices Microstruct.*, vol. 138, no. July 2019, p. 106327, 2020, doi: 10.1016/j.spmi.2019.106327.

- [29] J. Si, J. Wei, W. Chen, and B. Zhang, "Electric field distribution around drain-side gate edge in algan/gan hemts: Analytical approach," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3223– 3229, 2013, doi: 10.1109/TED.2013.2272055.

- [30] W. Fulop, "Calculation of avalanche breakdown voltages of silicon p-n junctions," *Solid State Electron.*, vol. 10, no. 1, pp. 39–43, 1967, doi: 10.1016/0038-1101(67)90111-6.

- [31] C. Erine, J. Ma, G. Santoruvo, and E. Matioli, "Multi-Channel AlGaN/GaN In-Plane-Gate Field-Effect Transistors," *IEEE Electron Device Lett.*, vol. 41, no. 3, pp. 321–324, 2020, doi: 10.1109/LED.2020.2967458.

- [32] P. Sohi, J.-F. Carlin, M. D. Rossel, R. Erni, N. Grandjean, and E. Matioli, "High conductivity InAlN/GaN multi-channel two-dimensional electron gases," *Semicond. Sci. Technol.*, 2021, doi: 10.1088/1361-6641/abf3a7.

- [33] Y. Cao, K. Wang, G. Li, T. Kosel, H. Xing, and D. Jena, "MBE growth of high conductivity single and multiple AlN/GaN heterojunctions," *J. Cryst. Growth*, vol. 323, no. 1, pp. 529–533, 2011, doi: 10.1016/j.jcrysgro.2010.12.047.

- [34] L. Nela, N. Perera, C. Erine, and E. Matioli, "Performance of GaN Power Devices for Cryogenic Applications down to 4.2 K," *IEEE Trans. Power Electron.*, vol. 36, no. 7, pp. 7412–7416, 2020, doi: 10.1109/TPEL.2020.3047466.

- [35] E. A. Jones, F. Wang, D. Costinett, Z. Zhang, and B. Guo, "Temperature-dependent turn-on loss analysis for GaN HFETs," *Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. - APEC*, vol. 2016-May, pp. 1010–1017, 2016, doi: 10.1109/APEC.2016.7467994.

- [36] R. Hou, J. Lu, and D. Chen, "Parasitic capacitance Eqoss loss mechanism, calculation, and measurement in hard-switching for GaN HEMTs," Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. -APEC, vol. 2018-March, pp. 919–924, 2018, doi: 10.1109/APEC.2018.8341124.

- [37] G. Deboy, O. Haeberlen, and M. Treu, "Perspective of Loss Mechanisms for Silicon and Wide Band-Gap Power Devices," CPSS Trans. Power Electron. Appl., vol. 2, no. 2, pp. 89–100, 2017, doi: 10.24295/cpsstpea.2017.00010.

- [38] X. Li, L. Zhang, S. Guo, Y. Lei, A. Q. Huang, and B. Zhang, "Understanding Switching Losses in SiC MOSFET: Toward Lossless Switching," *IEEE 3rd Work. Wide Bandgap Power Devices Appl.*, 2015.

- [39] L. Nela, G. Kampitsis, J. Ma, and E. Matioli, "Fast-Switching Tri-Anode Schottky Barrier Diodes for Monolithically Integrated GaNon-Si Power Circuits," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 99–102, 2020, doi: 10.1109/LED.2019.2957700.

- [40] L. Nela, R. Van Erp, G. Kampitsis, H. K. Yildirim, J. Ma, and E. Matioli, "Ultra-compact, high-frequency power integrated circuits based on GaN-on-Si Schottky Barrier Diodes," *IEEE Trans. Power Electron.*, pp. 1–1, 2020, doi: 10.1109/tpel.2020.3008226.

- [41] C. Yin, Y. Li, and Y. Pei, "AlGaN/GaN HEMTs Large Signal Model Considering Nonlinear Cds," Int. Appl. Comput. Electromagn. Soc. Symp., 2017.

- [42] F. R. Zypman, "Mathematical expression for the capacitance of

coplanar strips," J. Electrostat., vol. 101, no. August, p. 103371, 2019, doi: 10.1016/j.elstat.2019.103371.

- [43] Infineon Technologies AG, "Superjunction MOSFET for charger applications Application note," 2016.

- [44] A. Nakajima, S. Yagi, M. Shimizu, and H. Okumura, "Effect of deep trap on breakdown voltage in AlGaN/GaN HEMTs," *Mater. Sci. Forum*, vol. 600–603, no. Keithley 4200, pp. 1345–1348, 2009, doi: 10.4028/www.scientific.net/msf.600-603.1345.

- [45] L. Zhu, J. Wang, H. Jiang, H. Wang, W. Wu, Y. Zhou, and G. Dai, "Theoretical analysis of buffer trapping effects on off-state breakdown between gate and drain in AlGaN/GaN HEMTs," *Proc.* 2016 IEEE Int. Conf. Integr. Circuits Microsystems, ICICM 2016, pp. 33–36, 2017, doi: 10.1109/ICAM.2016.7813558.

- [46] A. M. Wells, M. J. Uren, R. S. Balmer, K. P. Hilton, T. Martin, and M. Missous, "Direct demonstration of the 'virtual gate' mechanism for current collapse in AlGaN/GaN HFETs," *Solid. State. Electron.*, vol. 49, no. 2, pp. 279–282, 2005, doi: 10.1016/j.sse.2004.10.003.

- [47] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Misha, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 560–566, 2001, doi: 10.1109/16.906451.

- [48] T. Hashizume, K. Nishiguchi, S. Kaneki, J. Kuzmik, and Z. Yatabe, "State of the art on gate insulation and surface passivation for GaNbased power HEMTs," *Mater. Sci. Semicond. Process.*, vol. 78, no. July 2017, pp. 85–95, 2018, doi: 10.1016/j.mssp.2017.09.028.

- [49] Z. Yatabe, J. T. Asubar, and T. Hashizume, "Insulated gate and surface passivation structures for GaN-based power transistors," J. Phys. D. Appl. Phys., vol. 49, no. 39, 2016, doi: 10.1088/0022-3727/49/39/393001.

- [50] T. Ciarkowski, "Low Impurity Content GaN Prepared via OMVPE for Use in Power Electronic Devices: Connection Between Growth Rate, Ammonia Flow, and Impurity Incorporation," 2019.

- [51] T. Ciarkowski, N. Allen, E. Carlson, R. McCarthy, C. Youtsey, J. Wang, P. Fay, J. Xie, and L. Guido, "Connection between carbon incorporation and growth rate for GaN epitaxial layers prepared by OMVPE," *Materials (Basel).*, vol. 12, no. 15, 2019, doi: 10.3390/ma12152455.

- [52] Joachim Piprek, Nitride Semiconductor Devices -Principles and Simulation. 2007.