# Engineering Breakdown Probability Profile for PDP and DCR Optimization in a SPAD Fabricated in a Standard 55nm BCD Process

Francesco Gramuglia, *Student Member, IEEE*, Pouyan Keshavarzian, *Student Member, IEEE*, Ekin Kizilkan, *Student Member, IEEE*, Claudio Bruschini, *Senior Member, IEEE*, Shyue Seng Tan, Michelle Tng, Elgin Quek, *Member, IEEE*, Myung-Jae Lee, *Member, IEEE*, and Edoardo Charbon, *Fellow, IEEE*

Abstract—CMOS single-photon avalanche diodes (SPADs) have broken into the mainstream by enabling the adoption of imaging, timing, and security technologies in a variety of applications within the consumer, medical and industrial domains. The continued scaling of technology nodes creates many benefits but also obstacles for SPAD-based systems. Maintaining and/or improving upon the high-sensitivity, low-noise, and timing performance of demonstrated SPADs in custom technologies or well-established CMOS image sensor processes remains a challenge. In this paper, we present SPADs based on DPW/BNW junctions in a standard Bipolar-CMOS-DMOS (BCD) technology with results comparable to the state-of-the-art in terms of sensitivity and noise in a deep sub-micron process. Technology CAD (TCAD) simulations demonstrate the improved PDP with the simple addition of a single existing implant, which allows for an engineered performance without modifications to the process. The result is an 8.8  $\mu$ m diameter SPAD exhibiting  $\sim$ 2.6 cps/ $\mu$ m<sup>2</sup> DCR at 20°C with 7 V excess bias. The improved structure obtains a PDP of 62 % and  $\sim$ 4.2 % at 530 nm and 940 nm, respectively. Afterpulsing probability is  ${\sim}0.97~\%$  and the timing response is 52 ps FWHM when measured with integrated passive quench/active recharge circuitry at 3V excess bias.

Index Terms—Single-photon avalanche diodes (SPADs), Photon counting, depth-sensing, BCD, time-correlated single-photon counting(TCSPC), LIDAR, three-dimensional (3-D) ranging, FLIM, QRNG

### I. INTRODUCTION

ARGE-FORMAT single-photon avalanche diode (SPAD) arrays [1]–[3] are becoming ubiquitous in the time-resolved imaging domain for their utility in applications such as fluorescence lifetime imaging microscopy (FLIM),

Francesco Gramuglia, Pouyan Keshavarzian and Ekin Kizilkan contributed equally to this work. Corresponding Author: Myung-Jae Lee and Edoardo Charbon

Francesco Gramuglia Pouyan Keshavarzian, Ekin Kizilkan, Claudio Bruschini, and Edoardo Charbon are with the Advanced Quantum Architecture Laboratory (AQUA), École Polytechnique Fédérale de Lausanne (EPFL), 2000 Neuchâtel, Switzerland e-mail: (francesco.gramuglia@epfl.ch; pouyan.keshavarzian@epfl.ch; ekin.kizilkan@epfl.ch; claudio.bruschini@epfl.ch; edoardo.charbon@epfl.ch).

Shyue Seng Tan, Michelle Tng, and Elgin Quek are with GLOBALFOUNDRIES Singapore Pte. Ltd., 60 Woodlands Industrial Park D Street 2, Singapore 738406 e-mail: (jason.tan@globalfoundries.com; jinghuamichelle.tng@globalfoundries.com; elgin.quek@globalfoundries.com).

M.-J. Lee is with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul 02792, South Korea (e-mail:fodlmj@gmail.com)

Manuscript received May 31, 2021; revised August 10, 2021; accepted September 15, 2021.

LiDAR/Time-of-flight (ToF), and also emerging domains, such as quantum random number generation (QRNG). Technology scaling allows for an increased number of pixels, resulting in higher spatial resolution, more data, and further enabling the integration of complex logic functionality [4]. However, on the detector side, the higher relative doping levels, along with reduced annealing, cause a much higher order defect concentration in SPADs, which results in high noise and reduced sensitivity. The advent of 3D-stacking in IC design has provided a potential remedy, as a custom process for the detector can be bonded to a separate CMOS IC that contains the core circuitry [5]. These system-on-chip designs [6]– [12] provide a best-of-both-worlds outlet. However, this can result in high cost and additional design complexity. A good compromise between the benefits of older standard processes with reliable SPAD performance and the 3D approach is to develop high-performing SPADs in a standard deep submicron node.

In [13], the concept of exploiting the process flow and high power design aspects of smart power technologies, such as Bipolar-CMOS-DMOS (BCD), was demonstrated. In that work, SPADs with excellent performance in terms of timing and noise characteristics were experimentally verified in a 160 nm ST BCD technology. In this work, we push the bounds on scaling with SPAD designs by exploiting the highly commutable GF 55 nm BCDL process. Moreover, through analytical modeling and TCAD simulation of the implant concentration and depth, we iterate through two versions of the deep-junction SPAD by only adding already available masks in order to improve overall performance. This simple-tounderstand approach, grounded in device physics, can be used by designers to improve sensitivity. Experimental validation of the devices shows comparable noise and sensitivity to the published state-of-the-art.

# II. DESIGN BACKGROUND

# A. Fundamentals of Deep-Junction SPADs

The fundamental operation of SPADs, process methods, and inherent design trade-offs are well described in the literature [14]–[16]. A general description of the operating behavior can be understood by analyzing the device cross-section, which consists of the neutral/quasi-neutral and multiplication (space charge) regions [17]. Furthermore, the relative geometries of

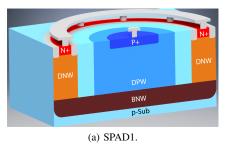

Fig. 1. Cross-sections of proposed 55 nm BCD SPADs. A single implant (PW) highlights the difference between structures.

these regions are used to distinguish between 'deep' and 'shallow' SPADs. While shallow junctions can be advantageous for their typically lower breakdown voltages, they suffer from lower photon detection probability (PDP), particularly at the longer wavelengths which are used for applications such as LiDAR. Moreover, detectors can be discriminated between whether they provide substrate isolation, which is desirable when integrating circuits on the same silicon.

For monolithic-based systems, i.e. where the SPADs and circuits co-exist on the same substrate, a way of isolating the circuits from the SPADs can be designed using 'deep' or 'buried' n-well layers [18]. The physical construction of this buried layer has direct consequences for the timing response. Considering the light absorption length of the silicon, the thickness of the n-well region contributes to the diffusion tail while the overall resistivity of the path to the cathode contact and avalanche spreading dynamics determines the full-width at half-maximum (FWHM) of the timing jitter [19], [20]. Furthermore, the buried n-well, which can be designed with retrograde doping, aids in the design of the multiplication and space-charge regions which is key for low-noise operation [21].

The PDP is defined by the product of the breakdown probability and quantum efficiency, as shown in (1).

Fig. 2. Doping comparison showing decrease of hole concentration for SPAD2 in contrast with increase shown for SPAD1 level. Net relative doping levels after all implants are placed is displayed at 5  $V_{\rm EX}$ .

$$PDP(\lambda) = P_b(\lambda) \cdot QE(\lambda) \tag{1}$$

Quantum efficiency is a function of the surface transmission, relative depth, and width of the space charge region. In any given process, it may be difficult for a designer to improve the quantum efficiency of a SPAD structure, particularly for deep junctions, as it can substantially be limited by the capabilities of the foundry. Nevertheless, it is possible to improve PDP across the spectrum by engineering the photo-collector regions for higher breakdown probability [22].

Owing to the fact that electrons have higher ionization coefficients than holes for silicon, it is desirable to have electrons drift from the depletion region to the multiplication region [23]. The premier and intuitive step for enabling this principle is to bury the junction deep inside the silicon, allowing for the minority electrons to be swept into the high-electric field where an avalanche can be initiated. A well-established design technique allowing for practical realization of this deep junction is to implant high energy Boron ions, [13], [24], [25]. This ensures that low-energy red/NIR photons are detected with higher efficiency. However, while the junction depth plays an essential role in SPAD performance, small differences in the design of the quasi-neutral (photo-collector) region i.e. the net implant profile approaching the junction can produce considerably varied results in terms of PDP. In an ideal structure,

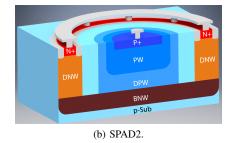

Fig. 3. Simulated conduction band diagram of SPADs. Inset illustrates the drift barrier resulting from the net concentration difference between the proposed SPADs.

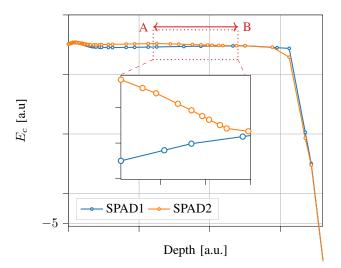

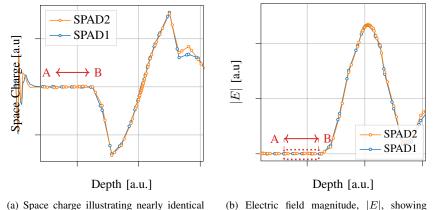

- (a) Space charge illustrating nearly identical multiplication regions.

- (b) Electric field magnitude, |E|, showing depth range of interest is outside the multiplication region.

- Bepth [a.u.]

(c) Simulated breakdown probability for each SPAD which culminates in the dramatic difference in performance between the two devices.

Fig. 4. Comparison between the simulated junction parameters of SPAD1 and SPAD2 at breakdown. Space charge and E-field highlight nearly-identical junction parameters. Normalized values are shown at 5  $V_{\rm EX}$ .

a designer would engineer the net doping in order to fully deplete the depth range where photons are absorbed, allowing for the drift of generated charge carriers to the multiplication region. This increases the breakdown probability and allows for maximum PDP. However, in a standard process, there are only a limited, number of masks available, which create variations in net doping when combined. A method through which the effect these variations have on detection efficiency can be examined by observing the band diagram in a TCAD simulation and, by extension, simulation of the corresponding breakdown probability.

# B. Device Physics and TCAD Simulation

The general structure of the proposed SPADs is shown in Fig. 1. The only difference between the variants is the additional p-well (PW) implant in SPAD2. Modelling of the junction in a single dimension enables quick evaluation of a SPADs detection efficiency [22], [26]. Oldham *et al.* described the voltage-dependent triggering probability with (2), (3) [23], where  $P_e$  and  $P_h$  are the probabilities that an electron and hole initiate an avalanche, respectively. The ionization coefficients are denoted by  $\alpha$  and  $\beta$ , respectively.

$$\frac{dP_e}{dP_x} = -(1 - P_e)\alpha(P_e + P_h - P_e \cdot P_h) \tag{2}$$

$$\frac{dP_h}{dP_x} = (1 - P_h)\beta(P_e + P_h - P_e \cdot P_h) \tag{3}$$

McIntyre extended the analysis by formulating a history-dependent ionization coefficient [27]. In TCAD, the McIntyre model is used to simulate these quantities along with the band diagram and doping profile.

The relative concentration of majority carriers (holes) in two demonstrated deep SPADs for a section close to the surface, which corresponds to the transition from the P+ to PW implants, is plotted in Fig. 2 with the corresponding conduction band diagram illustrated by Fig. 3. It can be seen that for SPAD2, the hole concentration monotonically

decreases towards the junction after a certain depth (highlighted by point A) while there is a region of increased concentration in SPAD1. The increase in holes is a result of the net concentration caused by the profile from all the implants used. We note that this depth range of interest (A-B), is outside the high-field multiplication region, which can be observed in Fig. 4a and Fig. 4b. There are multiple analytical manifestations that can help elucidate the consequence of this doping variation. From the energy band diagram in Fig. 3, there is an evident barrier created, which inhibits electron diffusion towards the multiplication region caused by photons absorbed close to the surface. This is in contrast to SPAD2, where the effective photo-collector region becomes much wider, enabling the photo-generated electrons in the charge-neutral region to transit to the multiplication region. The result is a greatly improved breakdown probability. In simulation, the combined breakdown probability of holes and electrons confirms this principle with the results displayed in Fig. 4c. Carriers that are injected into SPAD2 possess a higher probability of igniting an avalanche breakdown within a wider range of depths, which corresponds to a wider spectral response.

It is clearly shown by simulation that the space charge regions and electric field magnitude of the two devices are nearly identical in the multiplication region. Therefore, it is reasonable to conclude that differences in measured PDP would, to a great extent, arise from the doping variation in the photo-collector region.

### III. MEASUREMENT RESULTS

# A. I-V Characteristics

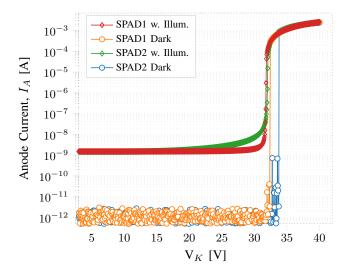

The diode I-V curves were measured using the Keysight B1500A semiconductor analyzer with the resulting dark currents and breakdown voltages (~32 V) matching well the simulation carried out in TCAD and are displayed in Fig. 5. It is clearly shown that SPAD2 achieves higher photo-current near the breakdown voltage, as predicted by TCAD. Light emission testing was performed as an initial qualitative measure to ensure the absence of edge breakdown from either

Fig. 5. I-V curves for proposed SPADs in dark and illuminated conditions at room temperature.

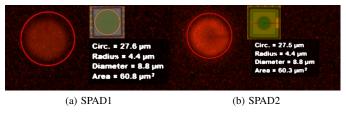

Fig. 6. Light emission test images with micrographs of SPAD1 (left) and SPAD2 (right) taken at  $V_{\rm EX}=3\ V$

of the two devices. Micrographs of SPAD1 and SPAD2 along with the LET image showing good uniformity around an active diameter of  $\sim 4.4~\mu m$  are shown in Fig. 6.

# B. Photon Detection Probability

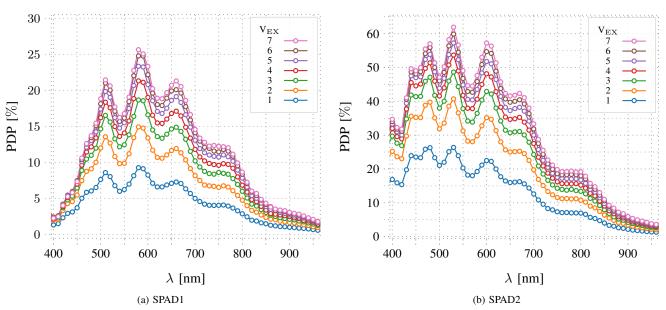

PDP measurement results for the two proposed SPADs at excess bias voltages of 1-7 V are displayed in Fig. 7a and Fig. 7b. These measurements were taken at room temperature with 10 nm intervals using the continuous light technique [28]. In our setup, a monochromator and integrating sphere are used to select a temporally coherent and uniform spatial distribution. A reference photodiode (PD) (Hamamatsu s2281) along with the device under test (DUT) are placed at a calibrated distance from the light output. The output is monitored with a universal counter (Keysight 53230A) and by an oscilloscope to verify the proper response of the SPAD.

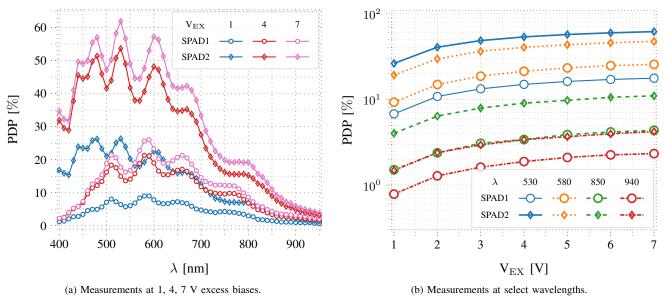

A distinct performance difference, as initially postulated by simulation, is outlined by the overall improved sensitivity of SPAD2 along with the very low detection efficiency of blue wavelength photons in SPAD1, which has a peak PDP of 26 % (580 nm). Conversely, SPAD2 is capable of an enhanced performance of 62 % (530 nm) at 7 V excess bias and maintains > 19 % PDP up to 800 nm.

A more direct comparison of the relationship between the two SPADs' performance across excess bias and wavelength can be drawn by observing Fig. 8a and Fig. 8b, which show the results of the devices on the same plot for sample excess biases and wavelengths. These graphs clearly illustrate how the performance of the two SPADs trends towards similarity at longer wavelengths, as lower energy photons, which are absorbed deeper inside the silicon, ignite avalanches with a similar probability. The standing wave pattern across the visible spectrum is a result of a non-optimized optical stack designed on top of the silicon.

# C. Noise Performance

1) DCR: The noise of a single-photon avalanche diode is characterized by its primary and secondary pulses, which combined constitute the dark count rate (DCR) in the absence

Fig. 7. PDP measurements for several excess bias voltages, measured with a 220 kΩ ballast resistor at 20°C for both SPAD designs presented in this work.

Fig. 8. PDP comparison between the two proposed SPADs highlighting variation across wavelength and excess bias.

of impinging photons. Thermally generated carriers and bandto-band tunneling are the main contributors to primary pulses. When there is either an initiated avalanche or thermal generation, carriers become trapped in 'deep' levels caused by defects in the silicon process. The release of and subsequent avalanche caused by these carriers are the secondary pulses known as afterpulses.

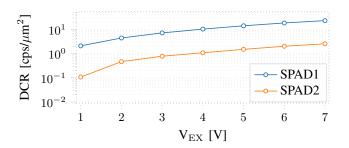

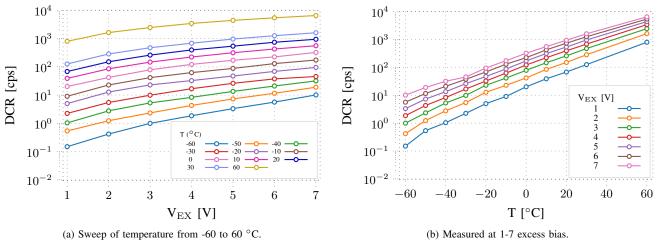

An oscilloscope (Teledyne LeCroy WaveMaster 813 Zi-B) was used to analyze the DCR. The median result for both SPADs across 10 dies at an excess bias voltage range of 1-7 V are plotted in Fig. 9. The SPAD2 results demonstrate  $\sim\!\!1$  cps/ $\mu m^2$  at 4 V excess bias and  $\sim\!\!2.6$  cps/ $\mu m^2$  at 7 V excess bias. As both SPADs show relatively low DCR, the remainder of the focus was the characterization of SPAD2 because of its superior PDP. Measurements were taken for a single SPAD2 die from -60°C to 60°C and the results are displayed in Fig. 10. The data demonstrates excellent performance even at high temperature and excess bias with a value of <10 kcps at @ 60°C and  $V_{\rm EX}=7$  V. Trap-assisted thermal generation is the main source of noise, as the DCR shows a strong temperature dependence.

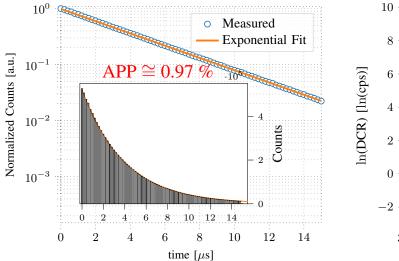

2) Afterpulsing: Characterization of the afterpulsing for silicon SPADs is typically conducted by histogramming the

Fig. 9. Normalized DCR comparison at room temperature across excess bias values. Median value shown for 10 dies of each SPAD

inter-arrival time between dark counts, although it can also be indirectly obtained by estimating the lifetime and density of traps using the time-correlated carriers counting (TCCC) technique [29], which is typically more useful for III-V SPADs where the afterpulsing probability can be relatively high.

The inter-arrival histogramming technique was employed using a passive quench active recharge (PQAR) circuit, similar in design to the work presented in [30], [31], which is integrated on the same die at 3  $V_{\rm EX}$  and 50 % level of the signal swing, and is displayed in Fig. 11. The excess bias is limited to 3 V by the chosen high-voltage transistor inside of the pixel circuit. In this setup, the dead time at the 50 % level was  $\sim 4.5$  ns. Data are binned at 200 ns intervals, with a total of  $\sim 10.6$  million counts observed. The multiexponential behavior arising from afterpulsing is typically fitted using 3 deep-level traps [32]. The afterpulsing probability is calculated by fitting the arrival data points after 10  $\mu$ s, which typically exceeds the maximum trap lifetime in silicon [32], and then dividing the secondary pulses (above the fit) by the primary pulse count (below the fit). The calculated afterpulsing probability is  $\sim 0.97$  %. This low afterpulsing probability is consistent with the overall low DCR rate, suggesting that there is a relatively low defect concentration.

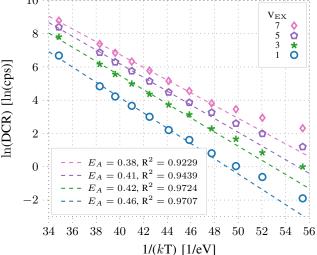

Assuming that thermal generation is the main component of DCR, activation energies can be extracted from their temperature dependence [33]. In our case, this is a justified premise because of the low relative doping of the deep junction, which results in a lower electric field at the breakdown (< 1 MV/cm) along with the strong dependence of the DCR on temperature previously outlined in Fig. 10. The Arrhenius plot is shown in Fig. 12. At high temperature and low excess bias, where SRH effects are more dominant, this qualitative analysis is used to extract the activation energies of traps. The 0.46 eV value displayed at 1  $V_{\rm EX}$  can likely be explained by phosphorusvacancy defects [34], with the change in slope illustrating

Fig. 10. Temperature dependence of DCR for a single randomly selected SPAD2 die illustrating strong temperature dependence of DCR.

Fig. 11. Inter-arrival histogram of SPAD2 with fitted exponential measured at 50 % level and room temperature at 3 V excess bias with integrated PQAR circuit and a dead time of  $\sim$ 4.5 ns.

Fig. 12. Arrhenius plot of the DCR for SPAD2 at the excess bias voltages of 1, 3, 5, and 7  $\rm V$ .

how at higher excess bias the tunneling effects become more prevalent.

# D. Timing Jitter

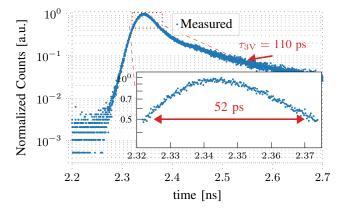

The timing performance of SPADs can be a critical parameter for applications requiring precise sensing. The results for the jitter of SPAD2 are displayed in Fig. 13. The time-correlated single-photon counting (TCSPC) acquisition technique was utilized to obtain data using the same oscilloscope used for the afterpulsing measurement, operating as a time-to-digital converter (TDC). The setup used for characterization is analogous to the one reported in [31]. A 1560 nm laser (NKT Onefive ORIGAMI-08) with second harmonic generation was used to output pulses at a wavelength of 780 nm containing a pulse-width of 150 fs pulsed at a repetition rate of 50 MHz. A 45 GHz optical receiver was inserted as a trigger on the 1560 nm branch. Moreover, neutral density filters were

Fig. 13. Jitter measurement of SPAD2 performed with a 780 nm pulsed laser. FWHM is 52 ps and a diffusion tail time constant of 110 ps at  $V_{\rm EX}$  = 3 V using integrated PQAR circuitry.

| TABLE I                                                    |

|------------------------------------------------------------|

| PERFORMANCE SUMMARY AND COMPARISON TO ESI STATE-OF-THE-ART |

| Reference                   |                   | Year | Tech.            | Junc.                            | Guard<br>Ring     | Active<br>Diam.<br>[μ] | V <sub>EX</sub> /<br>V <sub>BD</sub><br>[V] | Peak<br>PDP<br>[%] @\(\lambda\)<br>[nm] | PDP<br>[%]<br>@940<br>[nm] | DCR / area [cps / | DCR<br>@V <sub>EX</sub> f<br>[V] | AP<br>[%]                 | Jitter<br>[ps] | Jitter<br>λ[nm] | Jitter<br>V <sub>EX</sub><br>[V] |

|-----------------------------|-------------------|------|------------------|----------------------------------|-------------------|------------------------|---------------------------------------------|-----------------------------------------|----------------------------|-------------------|----------------------------------|---------------------------|----------------|-----------------|----------------------------------|

| Niclass et al.              | [35]              | 2007 | 130              | p+/n                             | pw                | 10                     | 1-2.7<br>/10                                | 31-41<br>@450                           | 1                          | 1300              | 100k<br>@1.7                     | N.A.                      | 144            | 637             | 1.7                              |

| Gersbach et al.             | [36]              | 2008 | 130              | p+/nw                            | $\mathrm{STI}^m$  | 8.6                    | 1-2 /9                                      | 18-30<br>@480                           | 2                          | 1.5k -<br>11.5k   | 670k<br>@2                       | <1 <sup>g</sup>           | 125            | 637             | 1                                |

| Richardson et al.           | [37]              | 2009 | 130              | pw/<br>DNW                       | $N.A.^c$          | 8                      | 0.6-1.4<br>/14                              | 18-28<br>@500                           | 2                          | 0.24 -<br>0.6     | 30<br>@1.4                       | $0.02^{h}$                | 200            | 815             | N.A                              |

| Richardson et al.           | <sup>9</sup> [25] | 2011 | 130              | pw/<br>DNW <sup>v</sup><br>p+/nw | N.A. <sup>c</sup> | $8^x$                  | 0.2-1.2<br>/12-18                           | 18-33<br>@450-<br>560                   | 2-3                        | 0.5-<br>0.97      | 40-47<br>@0.8                    | $0.02^{i}$                | 183 -<br>237   | 470             | 1.2                              |

| Webster et al.              | [38]              | 2012 | 90               | DNW/<br>p-epi <sup>k</sup>       | N.A. <sup>c</sup> | 6.4                    | 2.46<br>/14.9                               | 44<br>@690                              | 12                         | ~ 4.6             | ~150<br>@1                       | $0.38^{l}$                | 51             | 470             | 2.46                             |

| Webster et al.              | [39]              | 2012 | 130              | p-epi <sup>k</sup>               | N.A. <sup>c</sup> | 8                      | 2-12<br>/20                                 | 72<br>@560                              | 12                         | 0.36              | 18.0<br>@2                       | <4                        | 60             | 654             | 12                               |

| Leitner et al.              | [40]              | 2013 | 180              | p+/nw                            | N.A. <sup>c</sup> | 10                     | 1-3.3<br>/21                                | 35-47<br>@450                           | N.A.                       | 0.3-1.8           | ~180<br>@4                       | N.A.                      | N.A.           | N.A.            | N.A.                             |

| Charbon et al.              | [41]              | 2013 | 65               | n+/pw                            | nw                | 8                      | 0.05-<br>0.4<br>/9                          | 2-5.5<br>@420                           | 0.2                        | 340-<br>15.6k     | 105<br>@.05                      | 1 <sup>n</sup>            | 235            | 637             | 0.4                              |

| Villa et al.                | [42]              | 2014 | 350              | p+/nw                            | pw                | 10-500                 | 2-6 /25                                     | 37-55<br>@420                           | 2                          | 0.05              | 1.0<br>@4                        | 10                        | 56-<br>4470    | 780             | 6                                |

| Veerappan et al.            | [18]              | 2014 | 180              | p+/nw                            | pw                | 12                     | 2-10<br>/23.5                               | 24-48<br>@480                           | N.A.                       | 0.16-<br>12.8     | 20 @2                            | 0.03-<br>0.3 <sup>p</sup> | 86             | 637             | 10                               |

| Lee et al.                  | [43]              | 2015 | $140^d$          | p+/nw                            | pw                | 12                     | 0.5-3<br>/11                                | 10-25<br>@500                           | 1-3                        | 0.9-<br>244       | 30k<br>@3                        | $1.7^{p}$                 | 65             | 405             | 3                                |

| Veerappan et al.            | [44]              | 2015 | 180              | p+/nw                            | pw                | 12                     | 1-4 /14                                     | 23-47<br>@480                           | N.A.                       | 16                | 2k @4                            | $0.2^q$                   | 95             | 405             | 4                                |

| Veerappan et al.            | [24]              | 2016 | 180              | p-epi/<br>DNW                    | ${\sf N.A.}^c$    | 12                     | 1-12<br>/25                                 | 18-47<br>@520                           | N.A.                       | 1.5               | 200<br>@11                       | $7.2^{q}$                 | 97             | 637             | 11                               |

| Takai et al.                | [45]              | 2016 | 180              | $n/p^r$                          | N.A. <sup>c</sup> | 16                     | 1.5-5<br>/20.5                              | 62<br>@210                              | 8                          | 0.5               | 100<br>@5                        | 0.35                      | 161            | 635             | 5                                |

| Pellegrini et al.           | [46]              | 2017 | 130              | pw/<br>DNW                       | $\mathrm{N.A.}^c$ | 8                      | 0.5<br>/14.2                                | 43<br>@480                              | 1.4                        | 1.6               | 80<br>@0.5                       | 0.08                      | 100            | N.A.            | 2.4                              |

| Xu et al.                   | [47]              | 2017 | 150              | p+/nw                            | N.A. <sup>c</sup> | 10                     | 5 /<br>18.0                                 | 31<br>@450                              | 2                          | 0.4               | 200<br>@5                        | 0.85                      | 42             | 831             | 4                                |

| Pellegrini et al.           | [48]              | 2017 | 40               | pw/<br>DNW                       | N.A. <sup>c</sup> | N.A.                   | 1.0<br>/15.5                                | 45 <sup>s</sup><br>@500                 | 3                          | N.A.              | 50<br>@1.0                       | 0.1                       | 140            | 850             | 1                                |

| Sanzaro et al. <sup>y</sup> | [13]              | 2018 | 160 <sup>e</sup> | p+/n<br>p/<br>DNW                | N.A. <sup>c</sup> | 10-80                  | 3-9/<br>25-36                               | 58-71<br>@450-<br>490                   | 3                          | 0.1-0.2           | 100<br>@5                        | 0.02-<br>1.59             | 28-41          | 820             | 5                                |

| This Work (SPA              | D2)               | -    | 55 <sup>e</sup>  | DPW/<br>BNW                      | N.A. <sup>c</sup> | 8.8                    | 1-7/<br>31.5                                | 26-62<br>@530                           | 4.2                        | 0.1-2.6           | 6.1-<br>156<br>@1-7              | $\sim 0.97^t$             | 52             | 780             | 3                                |

<sup>&</sup>lt;sup>a</sup>Taken at max excess bias if not range of excess bias values not specified. <sup>c</sup>Virtual guard ring structure. <sup>d</sup>Silicon-on-insulator. <sup>e</sup>BCD. <sup>f</sup> At 20°C. <sup>g</sup>180 ns dead time. <sup>h</sup>200 ns dead time. <sup>t</sup>50 ns dead time. <sup>k</sup>Not substrate isolated. <sup>l</sup>15 ns dead time. <sup>m</sup>Shallow trench isolation with passivation implants to create p-type glove structure. <sup>n</sup>At 1 μs dead time. <sup>o</sup>30 μm diameter. <sup>p</sup>200 ns dead time. <sup>q</sup>300 ns dead time. <sup>r</sup>Surface-isolated n-spad/p-spad junction. <sup>s</sup>With microlens. <sup>t</sup>4.5 ns dead time with 50 % level @ 3 V<sub>EX</sub>. <sup>v</sup>Two different deep structures presented one with an epi layer and one with a pw implant. <sup>x</sup>Multiple diameters demonstrated. <sup>y</sup>3 SPAD structures proposed.

placed for attenuating the light intensity in order to avoid pile-up and ensure operation in the single-photon detection regime. Utilizing the same PQAR circuitry at 3  $V_{\rm EX}$  we achieved a full width at half-maximum of 52 ps, which is commensurate to other CMOS SPADs in the literature that performed this measurement using integrated pixel circuits. The exponential time constant of the diffusion tail is 110 ps. Further improvements by adding active quench/recharge circuitry and optimizing the measurement setup are ongoing.

# IV. DISCUSSION AND COMPARISON WITH THE STATE-OF-THE-ART

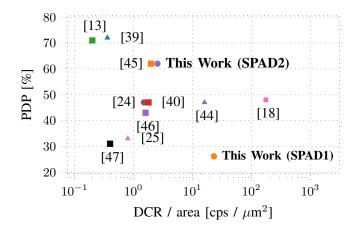

A summary table outlining the relevant front-side illuminated (FSI) SPADs demonstrated in literature is shown in Table I. The literature is organized in chronological order to achieve a visualization of the advancements over the course of time. In general, the research and development focus has been to try and achieve improved PDP and lower noise while experimenting with a number of junction and guard

Fig. 14. State-of-the-art comparison of noise and sensitivity performance. DCR taken at max excess bias reported.

ring structures. Although it can be difficult to draw a direct comparison, given that there are many figures of merit and technologies, some key conclusions can be drawn from this work

It can be seen that there have been few published designs in process nodes lower than 100 nm. Industrial SPADs in a 40nm process have been developed [48], although with lower PDP than this work. SPADs in a standard 28nm FDSOI [49], were presented recently, however, the results do not achieve comparable levels of performance to those displayed by Table I. Our SPADs demonstrate the highest peak sensitivity and lowest noise for SPADs in an advanced technology (< 65 nm). A visual comparison of the DCR and PDP for relevant works is depicted in Fig. 14. Finally, a key exposition from our work was that performance could be dramatically improved with only a single additional implant close to the surface of the SPAD. TCAD was used to explain the reasoning behind this, and the principle was then subsequently validated in silicon.

Engineering of the dopant profiles, improving the optical stack, and the addition of circuitry are our main focus going forward, which is required to improve performance. Overall, the excellent figures achieved in our work demonstrate the possibility of designing high-performance SPAD-based systems in a modern MPW technology without the need for 3D-stacking.

### V. CONCLUSION

This work has reported SPADs in a 55nm process which demonstrates comparable noise and sensitivity characteristics to the state-of-the-art. The SPAD photocollector region was optimized with the addition of a single implant, resulting in greatly improved performance. Furthermore, these SPADs are highly amenable to the design of fully integrated SPAD-based system-on-chips in a standard process.

# ACKNOWLEDGMENT

This research was supported, in part, by the Swiss National Science Foundation under grant 200021-169465. The authors would also like to thank GlobalFoundries for access to and assistance with the technology.

# REFERENCES

- [1] T. Okino, S. Yamada, Y. Sakata, S. Kasuga, M. Takemoto, Y. Nose, H. Koshida, M. Tamaru, Y. Sugiura, S. Saito, S. Koyama, M. Mori, Y. Hirose, M. Sawada, A. Odagawa, and T. Tanaka, "A 1200×900 6μm 450fps Geiger-mode vertical avalanche photodiodes CMOS image sensor for a 250m time-of-flight ranging system using direct-indirect-mixed frame synthesis with configurable-depth-resolution down to 10cm," in Proc. Intern. Solid-State Circuits Conf. (ISSCC) 2020, Feb. 2020, pp. 96–98

- [2] A. C. Ulku, C. Bruschini, I. M. Antolović, Y. Kuo, R. Ankri, S. Weiss, X. Michalet, and E. Charbon, "A 512 × 512 SPAD image sensor with integrated gating for widefield FLIM," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 1, pp. 1–12, Jan. 2019.

- [3] K. Morimoto, A. Ardelean, M.-L. Wu, A. C. Ulku, I. M. Antolovic, C. Bruschini, and E. Charbon, "Megapixel time-gated SPAD image sensor for 2D and 3D imaging applications," *Optica*, vol. 7, no. 4, pp. 346–354, Apr. 2020.

- [4] K. Morimoto and E. Charbon, "A scaling law for SPAD pixel miniaturization," *Sensors*, vol. 21, no. 10, May 2021.

- [5] M. Lee, A. R. Ximenes, P. Padmanabhan, T. Wang, K. Huang, Y. Yamashita, D. Yaung, and E. Charbon, "High-performance backilluminated three-dimensional stacked single-photon avalanche diode implemented in 45-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 6, pp. 1–9, Nov. 2018.

- [6] S. W. Hutchings, N. Johnston, I. Gyongy, T. Al Abbas, N. A. W. Dutton, M. Tyler, S. Chan, J. Leach, and R. K. Henderson, "A reconfigurable 3-D-stacked SPAD imager with in-pixel histogramming for flash LIDAR or high-speed time-of-flight imaging," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 2947–2956, Sep. 2019.

- [7] A. Ronchini Ximenes, P. Padmanabhan, M. Lee, Y. Yamashita, D. Yaung, and E. Charbon, "A modular, direct time-of-flight depth sensor in 45/65-nm 3-D-stacked CMOS technology," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3203–3214, Sep. 2019.

- [8] P. Padmanabhan, C. Zhang, M. Cazzaniga, B. Efe, A. R. Ximenes, M.-J. Lee, and E. Charbon, "A 256×128 3D-stacked (45nm) SPAD flash liDAR with 7-level coincidence detection and progressive gating for 100m range and 10klux background light," in *Proc. Intern. Solid-State Circuits Conf. (ISSCC)* 2021, Feb. 2021, pp. 111–113.

- [9] O. Kumagai, J. Ohmachi, M. Matsumura, S. Yagi, K. Tayu, K. Amagawa, T. Matsukawa, O. Ozawa, D. Hirono, Y. Shinozuka, R. Homma, K. Mahara, T. Ohyama, Y. Morita, S. Shimada, T. Ueno, A. Matsumoto, Y. Otake, T. Wakano, and T. Izawa, "A 189×600 back-illuminated stacked SPAD direct time-of-flight depth sensor for automotive LiDAR systems," in *Proc. Intern. Solid-State Circuits Conf. (ISSCC)* 2021, Feb. 2021, pp. 110–112.

- [10] S. Parent, M. Côté, F. Vachon, R. Groulx, S. Martel, H. Dautet, S. A. Charlebois, and J.-F. Pratte, "Single photon avalanche diodes and vertical integration process for a 3D digital SiPM using industrial semiconductor technologies," in 2018 IEEE Nuclear Science Symposium and Medical Imaging Conference Proceedings (NSS/MIC), 2018, pp. 1–4.

- [11] F. Gramuglia, A. Muntean, E. Venialgo, M.-J. Lee, S. Lindner, M. Motoyoshi, A. Ardelean, C. Bruschini, and E. Charbon, "CMOS 3D-stacked FSI multi-channel digital SiPM for time-of-flight PET applications," in 2020 IEEE Nuclear Science Symposium and Medical Imaging Conference Proceedings (NSS/MIC), 2020.

- [12] F. Nolet, V.-P. Rhéaume, S. Parent, S. A. Charlebois, R. Fontaine, and J.-F. Pratte, "A 2D proof of principle towards a 3D digital SiPM in HV CMOS with low output capacitance," *IEEE Trans. Nucl. Sci.*, vol. 63, no. 4, pp. 2293–2299, Aug. 2016.

- [13] M. Sanzaro, P. Gattari, F. Villa, A. Tosi, G. Croce, and F. Zappa, "Single-photon avalanche diodes in a 0.16 μm BCD technology with sharp timing response and red-enhanced sensitivity," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 2, pp. 1–9, Mar. 2018.

- [14] S. Cova, M. Ghioni, A. Lacaita, C. Samori, and F. Zappa, "Avalanche photodiodes and quenching circuits for single-photon detection," *OSA Appl. Opt. J.*, vol. 35, no. 12, pp. 1956–1976, Apr. 1996.

- [15] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2028–2035, Jul. 2011.

- [16] D. P. Palubiak and M. J. Deen, "CMOS SPADs: Design issues and research challenges for detectors, circuits, and arrays," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 409–426, Nov. 2014.

- [17] A. Gulinatti, I. Rech, M. Assanelli, M. Ghioni, and S. Cova, "A physically based model for evaluating the photon detection efficiency and the temporal response of SPAD detectors," *Journal of Modern Optics*, vol. 58, no. 3-4, pp. 210–224, 2011.

- [18] C. Veerappan and E. Charbon, "A substrate isolated CMOS SPAD enabling wide spectral response and low electrical crosstalk," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 299–305, Nov. 2014.

- [19] M. Assanelli, A. Ingargiola, I. Rech, A. Gulinatti, and M. Ghioni, "Photon-timing jitter dependence on injection position in single-photon avalanche diodes," *IEEE J. Quantum Electron.*, vol. 47, no. 2, pp. 151– 159, Jan. 2011.

- [20] C. H. Tan, J. S. Ng, G. J. Rees, and J. P. R. David, "Statistics of avalanche current buildup time in single-photon avalanche diodes particle detection," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 903–910, Sep. 2007.

- [21] A. Schenk, "An improved approach to the Shockley-Read-Hall recombination in inhomogeneous fields of space-charge regions," *Journ. Appl. Phys.*, vol. 71, no. 7, pp. 3339–3349, 1992.

- [22] L. Pancheri, D. Stoppa, and G. Dalla Betta, "Characterization and modeling of breakdown probability in sub-micrometer CMOS SPADs," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 328–335, 2014.

- [23] W. G. Oldham, R. R. Samuelson, and P. Antognetti, "Triggering phenomena in avalanche diodes," *IEEE Trans. Electron Devices*, vol. 19, no. 9, pp. 1056–1060, Sep. 1972.

- [24] C. Veerappan and E. Charbon, "A low dark count p-i-n diode based SPAD in CMOS technology," *IEEE Trans. Electron Devices*, vol. 63, no. 1, pp. 65–71, Jan. 2016.

- [25] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer cmos technology," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2028– 2035, Jul. 2011.

- [26] A. Spinelli and A. L. Lacaita, "Physics and numerical simulation of single photon avalanche diodes," *IEEE J. Electron Devices Soc.*, vol. 44, no. 11, pp. 1931–1943, Nov. 1997.

- [27] R. J. McIntyre, "A new look at impact ionization-Part I: A theory of gain, noise, breakdown probability, and frequency response," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1623–1631, Aug. 1999.

- [28] G. Zappalà, F. Acerbi, A. Ferri, A. Gola, G. Paternoster, N. Zorzi, and C. Piemonte, "Set-up and methods for SiPM photo-detection efficiency measurements," *Journal of Instrumentation*, vol. 11, no. 08, pp. P08 014– P08 014, aug 2016.

- [29] S. Cova, A. Lacaita, and G. Ripamonti, "Trapping phenomena in avalanche photodiodes on nanosecond scale," *IEEE Electron Device Lett.*, vol. 12, no. 12, pp. 685–687, Dec. 1991.

- [30] S. Lindner, S. Pellegrini, Y. Henrion, B. Rae, M. Wolf, and E. Charbon, "A high-PDE, backside-illuminated SPAD in 65/40-nm 3D IC CMOS pixel with cascoded passive quenching and active recharge," *IEEE Photon. Technol. Lett.*, vol. 38, no. 11, pp. 1547–1550, Nov. 2017.

- [31] F. Gramuglia, M.-L. Wu, C. Bruschini, M.-J. Lee, and E. Charbon, "A low-noise CMOS SPAD pixel with 12.1 ps SPTR and 3 ns dead time," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. X, p. X, Sep. X.

- [32] Z. Cheng, X. Zheng, D. Palubiak, M. J. Deen, and H. Peng, "A comprehensive and accurate analytical SPAD model for circuit simulation," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 1940–1948, May 2016.

- [33] M. Liu, C. Hu, X. Bai, X. Guo, J. C. Campbell, Z. Pan, and M. M. Tashima, "High-performance InGaAs/InP single-photon avalanche photodiode," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 887–894, Sep. 2007.

- [34] E. A. G. Webster, R. L. Nicol, L. Grant, and D. Renshaw, "Per-pixel dark current spectroscopy measurement and analysis in CMOS image sensors," *IEEE Trans. Electron Devices*, vol. 57, no. 9, pp. 2176–2182, Sep. 2010.

- [35] C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 863–869, Jul. 2007.

- [36] M. Gersbach, C. Niclass, E. Charbon, J. Richardson, R. Henderson, and L. Grant, "A single photon detector implemented in a 130nm CMOS imaging process," in *Proc. 38th Eur. Solid-State Device Res. Conf.*, Nov. 2008, p. 270–273.

- [37] J. A. Richardson, L. A. Grant, and R. K. Henderson, "Low dark count single-photon avalanche diode structure compatible with standard nanometer scale CMOS technology," *IEEE Photon. Technol. Lett.*, vol. 21, no. 14, pp. 1020–1022, Jul. 2009.

- [38] E. A. G. Webster, J. A. Richardson, L. A. Grant, D. Renshaw, and R. K. Henderson, "A single-photon avalanche diode in 90-nm cmos imaging technology with 44% photon detection efficiency at 690 nm," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 694–696, May 2012.

- [39] E. A. G. Webster, L. A. Grant, and R. K. Henderson, "A high-performance single-photon avalanche diode in 130-nm CMOS imaging technology," *IEEE Electron Device Lett.*, vol. 33, no. 11, pp. 1589–1591, Nov. 2012.

- [40] T. Leitner, A. Feiningstein, R. Turchetta, R. Coath, S. Chick, G. Visokolov, V. Savuskan, M. Javitt, L. Gal, I. Brouk, S. Bar-Lev, and Y. Nemirovsky, "Measurements and simulations of low dark count rate single photon avalanche diode device in a low voltage 180-nm CMOS image sensor technology," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1982–1988, Jun. 2013.

- [41] E. Charbon, H. Yoon, and Y. Maruyama, "A Geiger mode APD fabricated in standard 65nm CMOS technology," in *Proc. 2013 IEEE Int. Electron Devices Meeting*, 2013, p. 27.5.1–27.5.4.

- [42] F. Villa, D. Bronzi, Y. Zou, C. Scarcella, G. Boso, S. Tisa, A. Tosi, F. Zappa, D. Durini, S. Weyers, U. Paschen, and W. Brockherde, "CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm," *J. Mod. Opt.*, vol. 61, no. 2, pp. 102–115, Jun. 2014.

- [43] M.-J. Lee, P. Sun, and E. Charbon, "A first single-photon avalanche diode fabricated in standard SOI CMOS technology with a full characterization

- of the device," *Opt. Express*, vol. 23, no. 10, pp. 13 200–13 209, May 2015.

- [44] C. Veerappan and E. Charbon, "CMOS SPAD based on photo-carrier diffusion achieving PDP >40% from 440 to 580 nm at 4 v excess bias," *IEEE Photon. Technol. Lett.*, vol. 27, no. 23, pp. 2445–2448, Dec. 2015.

- [45] I. Takai, H. Matsubara, M. Soga, M. Ohta, M. Ogawa, and T. Yamashita, "Single-photon avalanche diode with enhanced NIR-sensitivity for automotive LIDAR systems," *Sensors*, vol. 16, no. 4, Mar. 2016.

- [46] S. Pellegrini and B. Rae, "Fully industrialised single photon avalanche diodes," in *Proc. Adv. Photon Count. Techniq. XI*, vol. 10212, 2017, pp. 16.5.1–16.5.4.

- [47] H. Xu, L. Pancheri, G.-F. D. Betta, and D. Stoppa, "Design and characterization of a p+/n-well SPAD array in 150nm CMOS process," *Opt. Express*, vol. 25, no. 11, pp. 12765–12778, May 2017.

- [48] S. Pellegrini, B. Rae, A. Pingault, D. Golanski, S. Jouan, C. Lapeyre, and B. Mamdy, "Industrialised SPAD in 40 nm technology," in *Proc.* 2017 IEEE Int. Electron Devices Meeting, 2017, pp. 16.5.1–16.5.4.

- [49] T. C. de Albuquerque, F. Calmon, R. Clerc, P. Pittet, Y. Benhammou, D. Golanski, S. Jouan, D. Rideau, and A. Cathelin, "Integration of SPAD in 28nm FDSOI CMOS technology," in *Proc. 2018 Europ. Solid-State Device Research Conf. (ESSDERC)*, 2018, pp. 82–85.

Francesco Gramuglia (S'17) major in electronics, received the B.S. degree in Biomedical Engineering from Politecnico di Milano, Milan, Italy, in 2013 and the M.S. degree in Electronics Engineering from Politecnico di Milano, Milan, Italy in 2016. From 2015 to 2016, he was a trainee in the STORMlab of Vanderbilt University, Nashville, Tennessee, where he collaborated on the development of robotic endoscope platforms. In 2016, he received the Best Application Prize and Overall Winner at Surgical Robot Challenge during the Hamlyn Symposium on

Medical Robotics at Imperial College, London, 2016. Since 2017, he has been pursuing a Ph.D. degree at the EPFL in the Advanced Quantum Architecture laboratory (AQUA). In 2021 he received the First Place Nuclear Science Symposium (NSS) Student Paper Award. His research interests focus on the design of deep-submicron Si-SPAD and SPAD-based detectors in saveral CMOS and BCD technologies, and system development for use in several applications based on single photon detection, e.g. Time-of-flight Positron emission tomography (TOFPET).

Pouyan Keshavarzian (S'14) received the B.Sc. and M.Sc. degrees in Electrical Engineering from the University of Calgary, Calgary, AB, Canada, in 2015 and 2019, respectively. From 2013 to 2016, he had various roles in hardware engineering within Garmin Canada, Cochrane, AB, Canada, where he was involved in the design of low-power wireless sensors for sport and health monitoring applications. For his M.Sc. research, he focused on developing microwave backscattering circuits and systems for radar applications. He is currently pursuing the Ph.D.

degree at the AQUA Laboratory, École Polytechnique Fédérale de Lausanne, Neuchâtel, Switzerland. His current research interests include the statistical modelling and development of circuits and detectors for SPAD-based quantum random number generators.

Ekin Kizilkan received his B.S. degree in Electrical and Electronics Engineering and in Physics from Middle East Technical University (METU), Turkey in 2016 and 2017, respectively. From 2016 to 2017, he worked as a full-time research assistant in Quantum Devices and Nanophotonics Research Laboratory on the design and fabrication of SWIR Cameras based on III/V compound semiconductors. In 2019, he earned degree of M.S. from École Polytechnique Fédérale de Lausanne (EPFL). Since 2019, he is a Ph. D. student in Advanced Quantum

Architecture Laboratory (AQUA). He has been conducting research on Single-Photon Avalanche Diodes (SPAD) based on various technologies (CMOS, Germanium on Silicon PIC, III/V) to enhance SPADs performance in NIR wavelengths as part of his Ph.D. work.

Elgin Quek (M'88) obtained his B. Eng. with First Class Honors from National University of Singapore and his M.S. from Stanford University, both in Electrical Engineering. From 1988 to 2009, he was with Chartered Semiconductor, Singapore, where he worked on process integration, yield enhancement, device engineering and SPICE modeling for CMOS and floating gate memories. Since 2009, he has been with GLOBALFOUNDRIES Singapore, where he is a GF Senior Fellow in Technology Development responsible for device design for CMOS-based logic,

SRAM, non-volatile memory, display-driver and sensor technologies. He has co-authored more than 40 technical papers and holds more than 150 U.S. patents.

Claudio Bruschini (M'12 SM'17) received the Laurea degree in physics from the University of Genova, Italy, in 1992, and the Ph.D. degree in applied sciences from Vrije Universiteit Brussel, Brussels, Belgium, in 2002. He is currently a Scientist and Lab Deputy with EPFL's Advanced Quantum Architecture Laboratory. His scientific interests have spanned from high energy physics and parallel computing in the early days, to challenging sensor applications in humanitarian demining, concentrating since 2003 on quantum photonic devices, high-speed and time-

resolved 2D/3D optical sensing, as well as applications thereof (biophotonics, nuclear medicine, basic sciences, security, ranging). He has authored or co-authored over 130 articles and conference proceedings and one book; he was the co-recipient of the 2012 European Photonics Innovation Award and of the Image Sensors Europe 2019 Award in the category "Best Academic Research Team", as well as Swiss Medtech Award 2016 finalist. He is an IEEE and SPIE Senior Member and co-founder of a start-up commercialising selected AQUA lab SPAD designs.

Myung-Jae Lee (S'08–M'13) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Postdoctoral Researcher with the faculty of electrical engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applica-

tions based on single-photon avalanche diodes. In 2017, he joined the school of engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Senior Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests have spanned from photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof (e.g., LiDAR, D-ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, optical interconnects, etc.).

Shyue Seng (Jason) Tan received his B. Eng (with First-class Honors) and PhD degrees in Electrical & Electronics Engineering from Nanyang Technological University, Singapore, in 2001 and 2004, respectively. He is now a PMTS (Deputy Director) working in Technology Development Department of Globalfoundries Singapore Pte Limited, where he is leading a group of engineers working on the CMOS logic, HV, NVM, HBT device design and development. His research interests include semiconductor device physics and reliability physics; as well as

biosensor, CIS and SPAD development. He has authored or coauthored more than 30 journal and conference papers include one invited paper. He is the holder of 123 US patents and more are in the progress of filing/searching. In addition, he served as peer reviewer for International Journal paper eg IEEE Transaction of Electron Devices (T-ED), Electron Device Letters (EDL), Journal of Electrochemical Society (JES), Applied Physics Letter (APL) and Journal of Applied Physics (JAP).

Edoardo Charbon (SM'00 F'17) received the Diploma from ETH Zurich, the M.S. from the University of California at San Diego, and the Ph.D. from the University of California at Berkeley in 1988, 1991, and 1995, respectively, all in electrical engineering and EECS. He has consulted with numerous organizations, including Bosch, X-Fab, Texas Instruments, Maxim, Sony, Agilent, and the Carlyle Group. He was with Cadence Design Systems from 1995 to 2000, where he was the Architect of the company's initiative on information hiding

for intellectual property protection. In 2000, he joined Canesta Inc., as the Chief Architect, where he led the development of wireless 3-D CMOS image sensors. Since 2002 he has been a member of the faculty of EPFL. From 2008 to 2016 he was with Delft University of Technology's as Chair of VLSI design. He has been the driving force behind the creation of deepsubmicron CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. His interests span from 3-D vision, LiDAR, FLIM, FCS, NIROT to superresolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for the control of qubit arrays in quantum computers. He has authored or co-authored over 400 papers and two books, and he holds 23 patents. Dr. Charbon is a distinguished visiting scholar of the W. M. Keck Institute for Space at Caltech, a fellow of the Kavli Institute of Nanoscience Delft, a distinguished lecturer of the IEEE Photonics Society, and a fellow of the IEEE.

Michelle Tng received the B.Eng. degree in electrical and electronic engineering from the Nanyang Technological University, Singapore, in 2012. Since then, she has been with GLOBALFOUNDRIES, where she is a part of the Global TCAD team. Her research interests include semiconductor device modeling and single photon avalanche diodes.