# A Low-noise CMOS SPAD Pixel with 12.1 ps SPTR and 3 ns Dead Time

Francesco Gramuglia, *Student Member, IEEE*, Ming-Lo Wu, Claudio Bruschini, *Senior Member, IEEE*, Myung-Jae Lee, *Member, IEEE*, and Edoardo Charbon, *Fellow, IEEE*

Abstract-Single-photon avalanche diodes (SPADs) have become the sensor of choice in many applications whenever high sensitivity, low noise, and sharp timing performance are required, simultaneously. Recently, SPADs designed in CMOS technology, have vielded moderately good performance in these parameters, but never equaling their counterparts fabricated in highly customized, non-standard technologies. The arguments in favor of CMOS-compatible SPADs were miniaturization, cost and scalability. In this paper, we present the first CMOS SPAD with performance comparable or better than that of the best custom SPADs, to date. The SPAD-based design, fully integrated in 180 nm CMOS technology, achieves a peak photon detection probability (PDP) of 55% at 480 nm with a very broad spectrum spanning from near ultraviolet (NUV) to near infrared (NIR) and a normalized dark count rate (DCR) of 0.2 cps/ $\mu$ m<sup>2</sup>, both at 6 V of excess bias. Thanks to a dedicated CMOS pixel circuit front-end, an afterpulsing probability of about 0.1% at a dead time of  $\sim$ 3 ns were achieved. We designed three SPADs with a diameter of 25, 50, and 100  $\mu$ m to study the impact of size on the timing jitter and to create a scaling law for SPADs. For these SPADs, a single-photon time resolution (SPTR) of 12.1 ps, 16 ps, and 27 ps (FWHM) was achieved at 6 V of excess bias, respectively. The SPADs operate in a wide range of temperatures, from -65°C to 40°C, reaching a normalized DCR of 1.6 mcps/ $\mu$ m<sup>2</sup> at 6 V of excess bias for the 25  $\mu$ m at -65°C. The proposed SPADs are ideal for a wide range of applications, including (quantum) LiDAR, super-resolution microscopy, quantum random number generators, quantum key distribution, fluorescence lifetime imaging, time-resolved Raman spectroscopy, to name a few. All these applications can take advantage of the vastly improved performance of our detectors, while enjoying the opportunities of megapixel resolutions promised by the economy of scale that is offered by CMOS technologies.

Index Terms—Active reset, cascode, jitter, low noise, low power, photon detection probability (PDP), pixel, quantum key distribution (QKD), single-photon avalanche diode (SPAD), timing.

#### I. Introduction

SILICON-BASED Single-photon avalanche diodes (SPADs) attracted increasing interest in the last decades thanks to their interesting performance [1], [2]. These devices

Francesco Gramuglia, Ming-Lo Wu, Claudio Bruschini and Edoardo Charbon are with the Advanced Quantum Architecture Laboratory (AQUA), École polytechnique fédérale de Lausanne (EPFL), 2002 Neuchâtel, Switzerland. e-mail: (francesco.gramuglia@epfl.ch; minglo.wu@epfl.ch; claudio.bruschini@epfl.ch; edoardo.charbon@epfl.ch).

M.-J. Lee is with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul 02792, South Korea (e-mail:mj.lee@kist.re.kr)

Manuscript received MONTH DAY, YEAR; revised MONTH DAY, YEAR.

(Myung-Jae Lee and Edoardo Charbon contributed equally to this work.) (Corresponding authors: Francesco Gramuglia, Myung-Jae Lee and Edoardo Charbon.)

showed relatively low noise, high photon detection probability (PDP), and very good timing performance [3]–[5]. Initially, SPADs were fabricated in custom epitaxial technology [6]. The use of a custom technology guarantees freedom in design optimization, in order to obtain the best performance in terms of sensitivity and noise [7], [8]. Recently, important efforts have been devoted to implement SPADs in commercial CMOS platforms [9]-[25]. Although CMOS SPADs are generally less performing in terms of PDP and noise, the benefit of integrating them side-by-side with electronic circuits is quite obvious. Indeed, this approach leads to reduced parasitics and more sophisticated ancillary circuits, larger application spectrum through more extensive functionality, and cost reduction thanks to mass production. Moreover, the circuits used for the SPAD front-end interface have been substantially improved over time, allowing the implementation of much more complex systems that fit a wider spectrum of applications [26]-[30]. In this context, very large array sizes, up to 1Mpixel have been achieved [31], [32].

In this work, we present three SPAD pixel detectors, based on high-performance SPAD pixels implemented in 180 nm CMOS technology. This device is specifically designed to achieve high performance in terms of count rate, sensitivity, timing precision, noise, and power consumption. The latter is very important if the same architecture is implemented in large arrays. The paper is organized as follows. After a description of the SPAD structure and corresponding TCAD simulations, along with the electronic front-end in Section II, the device characterization is presented, covering noise performance (Section III), sensitivity (Section IV), and timing (Section V). The setup for each of the parameters is added to the results. Section VI presents a discussion of the results followed by perspectives opened up by this work. Section VII closes the paper.

#### II. SPAD DESIGN

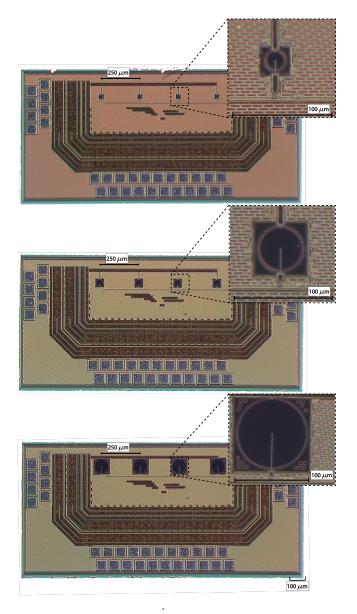

We designed three devices in separate dies. Each device comprises four independent SPADs with a dedicated pixel circuit, placed at a distance of 250  $\mu$ m. Fig. 1 shows the micrograph of the three implementations, whereas the inset on the *top-right* of each micrograph, shows three different SPAD diameters (25  $\mu$ m, 50  $\mu$ m and 100  $\mu$ m, respectively). To achieve the maximum of controllability and observability of the system, each chip has a large padring. Several pads were added in this prototyping phase to ensure the possibility of fine tuning the several control voltages of the pixel circuit,

Fig. 1. Micrograph of the implemented *chip 1 (top)*, *chip 2 (middle)*, and *chip 3 (bottom)* with a zoom-in on the SPAD pixel (*top-right* of each image). These devices embed four SPADs of 25  $\mu m$ , 50  $\mu m$ , and 100  $\mu m$  for chip 1, 2, and 3 respectively. Each SPAD has a dedicated pixel and a pixel pitch of 250  $\mu m$ .

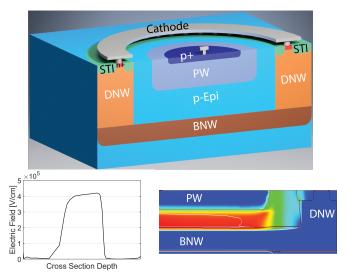

together with the high voltage to bias the SPAD, digital VDD, ground, and ESD supplies. The SPADs, implemented in 180 nm CMOS technology, rely on a p-i-n structure, similar to [21]. Fig. 2 shows the cross-section of the SPAD (top) and a TCAD simulation of the electric field in 2D, as well as a quantitative plot of the field along the vertical axis. The SPAD is a substrate-isolated type, where a p-well (PW) layer forms the anode of the SPAD and a buried n-well (BNW) layer creates the cathode contact. The latter is connected to the high voltage through a deep-n-well (DNW). An epi layer between anode and cathode allows a fairly large high-field region (Fig. 2, bottom), thus achieving a large sensitivity spectrum. The simulation results correspond to the SPAD operation at an excess bias voltage of 6 V.

Fig. 2. SPAD cross-section (top) and TCAD simulation of the electric field (bottom). A quantification of the electric field along the vertical axis is also shown (left-side).

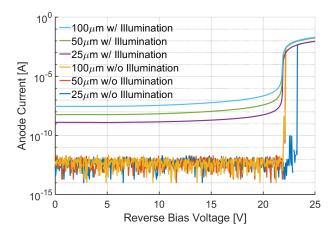

The SPAD breakdown voltage was measured to be about 22 V at room temperature. The corresponding I-V curve is shown in Fig. 3 under both dark and illuminated conditions.

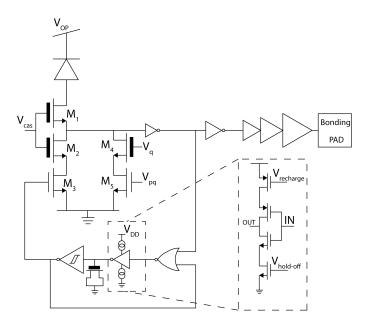

The SPAD front-end circuit, shown in Fig. 4, was inspired by [33], whereas cascode transistor  $M_1$  is used as a resistive divider, along with  $M_2$  to enable high excess bias (up to 11 V) [34] in combination with thin-oxide MOS transistors in the remainder of the front-end.

The gate of  $M_1$  is fixed at  $V_{CAS}$ , supplied externally. When an avalanche is triggered in the SPAD, the voltage at the source of  $M_1$  rises, thus decreasing the transistor overdrive. When the voltage reaches  $V_{CAS} - V_{th}$ ,  $M_1$  turns off boosting the impedance seen at the SPAD's anode. Thanks to the *body effect* acting on these transistors, the overdrive of  $M_1$  is dynamically reduced, thus making it turn off faster.

Both passive and active recharge strategies are available in the

Fig. 3. IV curve measured on isolated SPAD samples with the same cross section and size. The measurements were performed both with and without illumination. The breakdown voltage is about 22 V. As it possible to see in the measurements without illumination the breakdown results overestimated. This is an indication of the low noise of the device.

Fig. 4. Simplified schematic of the SPAD pixel. A cascode structure is used to allow high excess bias voltage (up to 11 V). An active reset feedback guarantees the fine control of the SPAD deadtime. A buffering chain is implemented to output the signal on an analog pad.

pixel and can be used independently.  $M_5$ , controlled by  $V_{pq}$ , is used to disable the passive quenching/recharge branch, represented by  $M_4$ . Active recharge is formed by  $M_2$  and  $M_3$ , the latter being turned on by the feedback loop represented by the OR gate, Schmitt trigger, and tunable delay element. The loop acts as a programmable-length monostable. The delay element is implemented using a current starved inverter (CSI) with a series voltage controlled transistor for both pMOS and nMOS branches (Fig. 4 right). Controlling this delay, and thus the hold-off time is important to control afterpulsing, especially in relatively large SPADs. This mechanism determines both the pulse width at the output and, in large part, the dead time. To guarantee the stability of the monostable and to get sharp edges at the output, an inverting Schmitt trigger was added, while, to improve the linearity of the CSI controls, a current mirror was included [35]. The slew rate of the output was maximized, unlike in [34], using a custom buffering chain to the bonding pad. This solution ensured an output slew rate of approximately 1 V/ns.

#### III. Noise Performance

#### A. Dark Count Rate

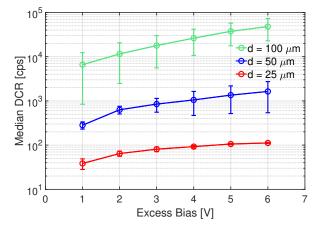

Dark count rate (DCR) was measured at different excess bias voltages for all three SPAD structures (Fig. 5). The measurement was performed at room temperature using an oscilloscope (Teledyne LeCroy WaveMaster 813 Zi-B). To a first approximation, DCR is linear in the area of the active region. However, a super-linear behavior is generally observed in the normalized median DCR due to the increased probability of traps in larger SPADs, thus causing trap-assisted dark counts. The results are shown in Fig. 5, where the median DCR is  $0.2 \text{ cps}/\mu\text{m}^2$  at 6 V excess bias and room temperature for the  $25 \mu\text{m}$  diameter SPAD. The DCR of the devices was

Fig. 5. DCR median value measured at several excess bias voltages for the different SPAD sizes. The results are obtained measuring 15 devices for each size.

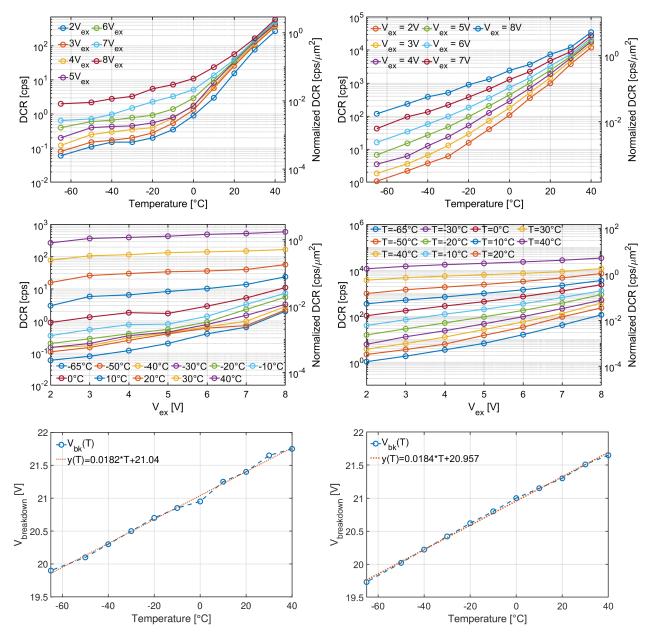

also measured as a function of temperature in the -65°C to 40°C range using a climate chamber operated in a closed loop. Fig. 6 shows DCR in cps as a function of temperature for a range of excess bias voltages for the smaller (25  $\mu$ m) and the larger (100  $\mu$ m) SPADs. The figure also shows the breakdown voltage behavior over temperature for the same devices. These values were used to apply a precise excess bias. By decreasing the temperature, DCR decreases by about three orders of magnitude, reaching a value of 1.6 mcps/ $\mu$ m<sup>2</sup> at 6 V<sub>ex</sub> for a diameter of 25  $\mu$ m, operating at -65°C. The normalized DCR on the active area reaches a value of 4 mcps/ $\mu$ m<sup>2</sup> at 8 V<sub>ex</sub> at -65°C.

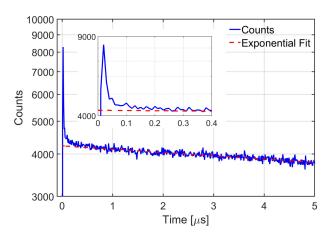

# B. Afterpulsing

Afterpulsing probability is another very important parameter, especially when one wants to minimize dead time through active recharge, so as to increase the maximum count rate in SPADs. This effect is due to some carriers, generated during the avalanche process, that may be captured by deep-level traps [36]–[38]. These carriers are then released after a statistical delay that depends on the lifetime of the traps [37], [38]. If a free carrier is released in a region where the electric field is sufficiently high it can ignite another avalanche. In general, the probability that this event occurs is more frequent with short dead times. Afterpulsing characterization for silicon SPADs is performed by histogramming the pulse inter-arrival time. This can be measured in the dark or under dim and uniform illumination. It can also be indirectly obtained by estimating the lifetime and density of traps using the time-correlated carriers counting (TCCC) technique [38], [39], which is typically more useful for III-V SPADs where the afterpulsing probability is significantly higher. In the presented work, the afterpulsing probability was obtained through inter-arrival histogramming under controlled dim illumination. Fig. 7 shows the measured inter-arrival time between pulses generated by the  $25-\mu m$ SPAD at 6  $V_{ex}$ . The SPAD dead time was set at about 11 ns using the integrated active recharge circuit described earlier.

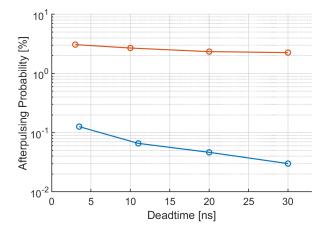

In Fig. 8 it is possible to see the measured afterpulsing

Fig. 6. Top: DCR measured at different temperatures; Middle: DCR shown as a function of the excess bias voltage; Bottom: Breakdown voltage as a function of temperature. The results refer to a SPAD diameter of  $25 \ \mu m$  (left side) and  $100 \ \mu m$  (right side), respectively.

probability on the same SPAD, as a function of the pulse width. The afterpulsing probability remains as low as 0.1% for a pulse width of about 5 ns. With the current architecture, the minimum achievable SPAD dead time is 3 ns.

#### IV. SENSITIVITY PERFORMANCE

# A. PDP Setup

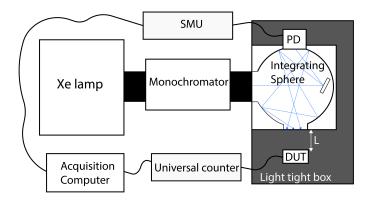

The most common method of measuring the PDP is to create an area with uniform photon flux of a particular wavelength and compare the responsivity of the SPAD under test to a calibrated reference device (usually a photodiode). The setup used to measure PDP is based on the continuous light technique [40], schematically shown in Fig. 9. The setup comprises a wide-spectrum Xenon lamp that generates wide spectrum light,

a monochromator, an integrating sphere, a calibrated reference photodiode (PD) with a precision source and measurement unit (SMU) to measure the photocurrent generated by the PD, and a universal counter connected to the device under test (DUT). The integrating sphere and the DUT are enclosed in a light tight box to eliminate any source of background noise that would affect the measurement. A custom software was developed to automate the scan at a very fine wavelength resolution. The DUT has been placed at distance L from the output window of the integrating sphere, so as to ensure lower light level and high uniformity [41]. The reason to have a lower light level is that the SPAD (sensible to single photons) can be saturated if exposed to high light level, thus causing pile-up, which distorts the SPAD's sensitivity curve,

Fig. 7. Inter arrival time distribution measured with the pulse width of 11 ns on the SPAD of 25  $\mu m$  size. The measurement is taken at a temperature of 25°C.

Fig. 8. Afterpulsing probability as a function of the pulse width on the  $25~\mu m$  diameter and  $100~\mu m$  diameter SPADs at 6 V excess bias. All the measurements are taken at a temperature of  $25^{\circ}$ C.

causing an underestimation of PDP. Moreover, a stronger light impinging on the reference photodiode can improve its SNR. A 45 s integration time was used for each step. For each value of excess bias, the DCR is measured before starting the acquisition under the light. This value is then used to compute the PDP as shown in [40]:

$$PDP(\lambda) = \eta \frac{S - DCR}{A_{SPAD}F_{PD}(\lambda)} = \eta \frac{F_{SPAD}(\lambda)}{F_{PD}(\lambda)}$$

(1)

Where  $\eta$  is a light ratio computed during the calibration phase measuring the light power at the integrating sphere output port and at the location of the DUT with a calibrated reference photodiode; S is the number of pulses at the SPAD output when exposed to light;  $A_{SPAD}$  is the active area of the SPAD;  $F_{PD}(\lambda)$  is the photon flux detected by the reference photodiode.

#### B. PDP Results

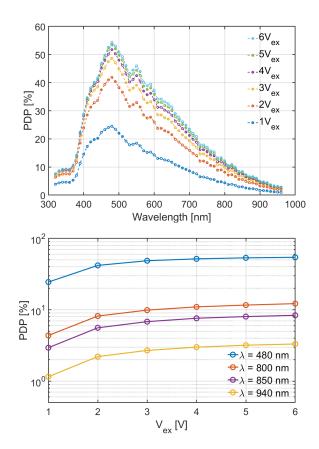

The PDP is plotted in Fig. 10 as a function of wavelength (top) and excess bias voltage (bottom). All the measurements

Fig. 9. PDP setup used for device characterization. A Xenon lamp generates a wide spectrum photon flux. Narrow band of wavelengths are selected with the monochromator and the integrating sphere diffuses the photons equally to the DUT and the reference PD, while the PD (Hamamatsu S2281) and the DUT are placed at a calibrated distance *L*. The setup is enclosed in a light tight box and an universal counter (Keysight 53230A) is used to evaluate the SPAD output.

Fig. 10. *Top*: PDP measurements for several excess bias voltages (from 1 V to 6 V excess bias). The measurement is performed with a wavelength step of 10 nm in a wavelength range between 320 nm and 960 nm. *Bottom*: saturation effect of PDP over bias voltage for four selected wavelengths.

were performed at room temperature. The wavelength scan was performed with a step of 10 nm. The sensitivity peak is 55% at 480 nm at 6  $V_{ex}$ . These results are consistent with [21], [34] for similar SPAD cross-sections. The relatively large sensitivity spectrum is also in line with the structure used (Fig. 2). Note the typical PDP saturation above 5  $V_{ex}$ . At and above this voltage, the PDP becomes increasingly

Fig. 11. Optical setup used for the single-photon timing resolution measurement. A femtosecond laser generates a 150 fs pulse at 1030 nm, which is then upconverted to 515 nm after SHG. A fast PD is used as a reference to the oscilloscope, while the upconverted beam (515 nm) is filtered by neutral density filters (NDFs). The output of the DUT is sampled through a 4 GHz, 0.6 pF active probe by a 40 GS/s, 13 GHz oscilloscope to generate a histogram using time-correlated single-photon counting (TCSPC) acquisition.

insensitive to variations of breakdown voltage, which makes this SPAD amenable to integration in large arrays, where the breakdown voltage could vary significantly across the chip, thereby causing unwanted PDP variability.

#### V. TIMING JITTER

## A. Jitter Setup

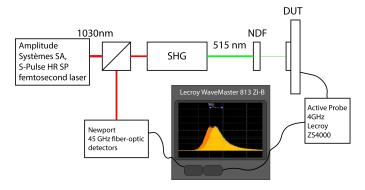

The setup used to evaluate timing jitter in the DUT shown in Fig. 11 is based on [42]. The setup comprises a femtosecond laser (Amplitude Systèmes SA, S-Pulse HR SP), capable of generating 150 fs pulses at a wavelength of 1030 nm and 515 nm after second-harmonic generation (SHG). A fast photodiode (Newport InGaAs Photodetector, 45 GHz bandwidth) is used as a timing reference, while the upconverted beam is attenuated by a bank of neutral density filters (NDFs), so as to achieve single-photon detection regime. The DUT has a high-impedance output and thus an active probe is used to capture the output. An oscilloscope (LeCroy WaveMaster 813 Zi-B) is used to capture both the waveform from the DUT and the reference PD.

#### B. Jitter Results

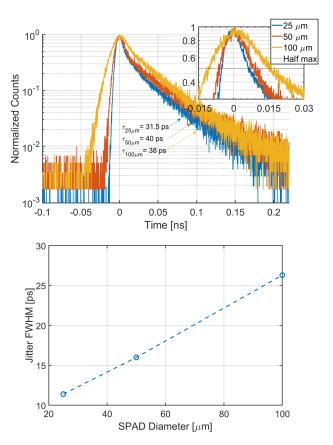

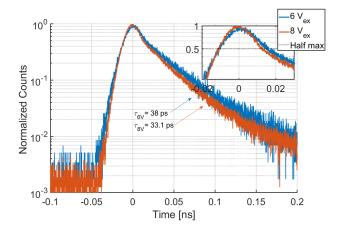

Timing jitter measurements for the 3 device sizes are shown in Fig. 12. The plot shows the histograms of the response of the SPADs when biased at an excess bias voltage of 6 V and at room temperature. The oscilloscope trigger threshold was set at 400 mV for the SPAD pulse and 300 mV for the PD. The laser repetition rate is 100 MHz and the light was reduced in order to detect less than a laser pulse every 100. The jitter value (FWHM) of the response distribution was measured at 12.1 ps for a diameter of 25  $\mu$ m, 16 ps for 50  $\mu$ m, and 27.2 ps for 100  $\mu$ m. To capture the diffusion tails, the full width at tenth of maximum (FWTM) was extracted as well; it results in 55.7 ps for a diameter of 25  $\mu$ m, 66.8 ps for 50  $\mu$ m, and 91.7 ps for 100  $\mu$ m. The exponential time constant for the diffusion tails was also extracted from the plot to be 31.5 ps, 40.7 ps and 36 ps for the 25  $\mu$ m, 50  $\mu$ m and 100  $\mu$ m SPAD, respectively. The plots in Fig. 13 show the response of a 100

Fig. 12. Jitter measurements performed with a 515 nm femtosecond pulsed laser. Histogram results (top) and extracted jitter value as a function of the area (bottom) are visible in the graphs. The jitter results to be around 12.1 ps, 16 ps and 27.2 ps FWHM for the 25  $\mu m$ , 50  $\mu m$ , 100  $\mu m$  diameter SPADs, respectively. The measurement is performed at  $V_{ex}$  = 6V excess bias for the three samples.

Fig. 13. Jitter measurements comparison at two excess bias voltages (6 V and 8 V) performed on the 100  $\mu m$  diameter SPAD. The jitter results to be 27.2 ps and 23.5 ps FWHM, respectively.

$\mu$ m SPAD with two excess bias voltages of 6 and 8 V, with an improvement of the jitter from 27.2 to 23.5 ps FWHM. Also in this case the exponential time constant of the diffusion tail was extracted and it is 38 ps for 6 V excess bias and 33.1 ps for 8 V excess bias. It is important to note that these results were obtained without the need for low threshold comparators, thus a simplified circuit can be used in each pixel, thereby ensuring

7

scalability to large arrays of pixels.

#### VI. DISCUSSION

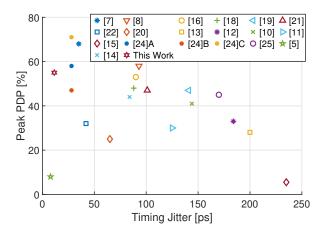

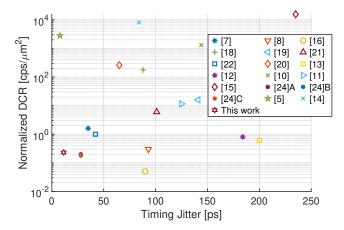

Table I and Fig. 14 summarize the performance of several state-of-the-art devices found in the literature in comparison to the SPADs presented in this work. Many of the SPADs listed here were developed in standard technologies. SPADs implemented in older technology nodes (between 0.35  $\mu$ m and 0.16  $\mu$ m) exhibit the best sensitivity performance [16]–[19], [21], [24]. Instead, in more recent nodes, where higher doping and shallower standard layers are used, peak PDP does not usually exceed 32% and noise is higher [10]-[13], [15], [20], [22]. In [43] it is shown how very high PDPs can be achieved in the red in a 180 nm CMOS node using custom layers. However, this SPAD is not isolated, and thus the integration of front-end circuits is not straightforward. In addition, the achieved timing jitter is high because of its large drift region. The PDP performance of the devices presented in this work is among the best ever reported in the literature for substrate isolated SPADs. The peak value of  $\sim$ 54% at 480 nm with 5 V excess bias is quite close to that reported in [24], device (C), for the same bias. The noise performance reported in this work is also among the best shown in the literature (Fig. 14 right).

To the best of our knowledge, the timing jitter achieved in this work is superior to any other CMOS SPAD-based device reported in literature, except for [5], which reports a peak PDP of 8% and a DCR of 2800 cps/ $\mu$ m<sup>2</sup>, while our device achieves a peak PDP of 55% and worst-case DCR of 0.23 cps/ $\mu$ m<sup>2</sup> (Fig. 14 *left*). Moreover, in our solution, we have shown the performance of the SPAD with a low-power digital front-end and without the need for any circuit that could affect power consumption, such as a low threshold comparators. Thus, we believe that the proposed SPAD is an example of a new generation of devices with similar or better performance than custom SPADs but allowing scalable architectures with little to no power budget restrictions. Finally, we believe that the reduction of the front-end circuit threshold could improve timing performance and power consumption even further.

# VII. CONCLUSIONS

We report on the design and characterization of a new SPAD fabricated in 180 nm CMOS technology, exhibiting a performance comparable or better than that of the most advanced custom SPADs, to date. The devices have a peak PDP of 55% at 480 nm and DCR is as low as 0.2 cps/ $\mu$ m<sup>2</sup> at room temperature, both at 6 V excess bias. The DCR is as low as 1.6 mcps/ $\mu$ m<sup>2</sup> at -65°C, while the SPAD operated normally at 40°C. The pixel circuit used allows the fine tuning of the SPAD dead time to control the maximum achievable count rate up to 300 Mcps, while afterpulsing remains in the order of 0.1%.

Three SPAD families were designed with 25, 50, and 100  $\mu$ m. The SPTR reached 12.1 ps (FWHM) in the smallest SPAD and did not exceed 27 ps in the largest, all at 6 V of excess bias and room temperature. Low static power consumption is compatible with large arrays of SPADs, which

makes this technology amenable to scalable Mpixel sensor architectures, suitable for a variety of applications demanding high sensitivity, low noise, and sharp timing performance.

### VIII. FUNDING

This research was supported, in part, by the Swiss National Science Foundation under grant 200021-169465.

#### IX. ACKNOWLEDGMENTS

The Authors would like to thank Simone Frasca and Olivier Bernard for the fruitfull discussions and the technical support on the laser setup. EPFL also gratefully acknowledges the generous support of the Swiss National Science Foundation.

#### REFERENCES

- S. Cova, M. Ghioni, A. Lacaita, C. Samori, and F. Zappa, "Avalanche photodiodes and quenching circuits for single-photon detection," *Applied Optics*, vol. 35, no. 12, pp. 1956–1976, 1996.

- [2] F. Ceccarelli, G. Acconcia, A. Gulinatti, M. Ghioni, I. Rech, and R. Osellame, "Recent advances and future perspectives of singlephoton avalanche diodes for quantum photonics applications," *Advanced Quantum Technologies*, p. 2000102, 2020.

- [3] S. Cova, A. Lacaita, M. Ghioni, G. Ripamonti, and T. Louis, "20-ps timing resolution with single-photon avalanche diodes," *Review of Scientific Instruments*, vol. 60, no. 6, pp. 1104–1110, 1989.

- [4] A. Spinelli, M. A. Ghioni, S. D. Cova, and L. M. Davis, "Avalanche detector with ultraclean response for time-resolved photon counting," *IEEE Journal of Quantum Electronics*, vol. 34, no. 5, pp. 817–821, 1998.

- [5] F. Nolet, S. Parent, N. Roy, M.-O. Mercier, S. Charlebois, R. Fontaine, and J.-F. Pratte, "Quenching circuit and SPAD integrated in CMOS 65 nm with 7.8 ps FWHM single photon timing resolution," *Instruments*, vol. 2, p. 19, 9 2018.

- [6] M. Ghioni, S. Cova, A. Lacaita, and G. Ripamonti, "New silicon epitaxial avalanche diode for single-photon timing at room temperature," *Electronics Letters*, vol. 24, no. 24, pp. 1476–1477, 1988.

- [7] M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, and S. Cova, "Progress in silicon single-photon avalanche diodes," *IEEE Journal of Selected Topics* in *Quantum Electronics*, vol. 13, no. 4, pp. 852–862, 2007.

- [8] A. Gulinatti, I. Rech, F. Panzeri, C. Cammi, P. Maccagnani, M. Ghioni, and S. Cova, "New silicon SPAD technology for enhanced redsensitivity, high-resolution timing and system integration," *Journal of Modern Optics*, vol. 59, no. 17, pp. 1489–1499, 2012.

- [9] A. Rochas, M. Gani, B. Furrer, P. Besse, R. Popovic, G. Ribordy, and N. Gisin, "Single photon detector fabricated in a complementary metaloxide-semiconductor high-voltage technology," *Review of Scientific In*struments, vol. 74, no. 7, pp. 3263–3270, 2003.

- [10] C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 13, no. 4, pp. 863–869, 2007.

- [11] M. Gersbach, C. Niclass, E. Charbon, J. Richardson, R. Henderson, and L. Grant, "A single photon detector implemented in a 130nm CMOS imaging process," in ESSDERC 2008-38th European Solid-State Device Research Conference. IEEE, 2008, pp. 270–273.

- [12] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2028–2035, Jul. 2011.

- [13] J. A. Richardson, L. A. Grant, and R. K. Henderson, "Low dark count single-photon avalanche diode structure compatible with standard nanometer scale CMOS technology," *IEEE Photonics Technology Let*ters, vol. 21, no. 14, pp. 1020–1022, 2009.

- [14] E. A. G. Webster, J. A. Richardson, L. A. Grant, D. Renshaw, and R. K. Henderson, "A single-photon avalanche diode in 90-nm CMOS imaging technology with 44% photon detection efficiency at 690 nm," *IEEE Electron Device Letters*, vol. 33, no. 5, pp. 694–696, 2012.

- [15] E. Charbon, H. Yoon, and Y. Maruyama, "A Geiger mode APD fabricated in standard 65nm CMOS technology," in 2013 IEEE International Electron Devices Meeting, 2013, pp. 27.5.1–27.5.4.

| TABLE I                     |  |  |  |  |  |  |  |  |

|-----------------------------|--|--|--|--|--|--|--|--|

| SUMMARY OF SDAD REDEORMANCE |  |  |  |  |  |  |  |  |

| Comparative Table |             |          |                 |                         |                    |                          |                        |                        |              |

|-------------------|-------------|----------|-----------------|-------------------------|--------------------|--------------------------|------------------------|------------------------|--------------|

|                   | Technology  | Diameter | $V_{EX}/V_{BD}$ | Peak PDP                | PDP (%)            | DCR/unit area            | AP (%)                 | Jitter (ps)            | $FoM_T$ [44] |

|                   | (nm)        | $\mu m$  | (V)             | $(\%)$ @ $\lambda$ (nm) | @850 nm            | $(cps/\mu m^2)$          |                        |                        |              |

| Ghioni [7]        | Custom Thin | 50-200   | 5-10/30-35      | 52-68 @550              | 12-15              | $0.4 \text{-} 1.6^a$     | $2^b$                  | 35 <sup>c</sup>        | 1.88E+11     |

| Gulinatti [8]     | Custom RE   | 50       | 20/45-55        | 58 @650                 | 28                 | $0.3^{d}$                | N/A                    | 93°                    | N/A          |

| Villa [16]        | 350         | 10-500   | 2-6/25          | 37-53 @450              | 2-4.5              | $0.05^{a}$               | 1 e                    | $90^f$                 | 6.52E+11     |

| Leitner [17]      | 180         | 10       | 1-3.3/21        | 35-47 @450              | $N/A^g$            | $0.3 \text{-} 1.8^a$     | N/A                    | N/A                    | N/A          |

| Veerappan [18]    | 180         | 12       | 2-10/23.5       | 24-48 @480              | 3-8                | $0.16 - 176^a$           | $0.03 - 0.3^h$         | 112-88 <sup>i</sup>    | 1.37E+9      |

| Veerappan [19]    | 180         | 12       | 1-4/14          | 23-47 @480              | 4-7                | $0.28 \text{-} 16^d$     | $0.2^{j}$              | $161-141^{i}$          | 2.78E+9      |

| Veerappan [21]    | 180         | 12       | 1-12/25         | 18-47 @520              | 2-8                | $0.2 - 6^d$              | $7.2^{k}$              | $139 \text{-} 101^{i}$ | 5.88E+9      |

| Xu [22]           | 150         | 10       | 2-5/19          | 24-32 @450              | 2-3.5              | 0.1-1                    | $1-13^{l}$             | $42^{m}$               | 1.33E+11     |

| Lee [20]          | 140(SOI)    | 12       | 0.5-3/11        | 12-25 @500              | 2.5-7              | 0.9-260                  | 1.7 <sup>n</sup>       | 65°                    | 1.17E+9      |

| Richardson [13]   | 130         | 8        | 0.6-1.4/14      | 18-28 @500              | 3-5                | $0.24 - 0.6^a$           | $0.02^{p}$             | $200^{q}$              | 9.04E+9      |

| Richardson [12]   | 130         | 8        | 0.2-1.2/12-18   | 18-33 @450              | 2-5                | 0.4-0.8                  | $0.02^{r}$             | 237-184 <sup>s</sup>   | 4.01E+10     |

| Niclass [10]      | 130         | 10       | 1-3.5/10        | 31-41 @450              | 3                  | $120 - 1300^d$           | N/A                    | $144^{i}$              | N/A          |

| Niclass [43]      | 180         | 25       | 5/20.5          | 64.8 @610 <sup>ii</sup> | 24                 | 0.6                      | $0.49^{dd}$            | 190                    | 1.83E+11     |

| Gersbach [11]     | 130         | 4.3      | 1-2/9           | 18-30 @480              | 3.5-5              | 1.5-11.5                 | <1 <sup>t</sup>        | $125^{i}$              | 3.89E+9      |

| Charbon [15]      | 65          | 8        | 0.05-0.4/9      | 2-5.5 @420              | 0.2-0.4            | 340-15.6k <sup>a</sup>   | <1 <sup>u</sup>        | $235^{i}$              | 3.71E+5      |

| Sanzaro(A) [24]   | 160(BCD)    | 10-80    | 3-9/36          | 31-58 @450              | 2.5-6.5            | $0.12 \text{-} 0.2^{v}$  | $0.43 - 1.59^w$        | 39-28 <sup>c</sup>     | 9.12E+11     |

| Sanzaro(B) [24]   | 160(BCD)    | 10-80    | 3-9/25          | 2-47 @450               | 2.5-6.5            | $0.1 \text{-} 0.18^{v}$  | $0.02 \text{-} 0.14^w$ | 36-28 <sup>c</sup>     | 7.9E+11      |

| Sanzaro(C) [24]   | 160(BCD)    | 10-80    | 3-9/26          | 55-71 @490              | 6-9                | $0.13 \text{-} 0.19^{v}$ | $0.41 \text{-} 1.26^w$ | $41-28^{c}$            | 1.15E+12     |

| Pellegrini [25]   | 40          | 18.36    | 1/15.5          | 45 @460 <sup>+</sup>    | 5                  | N/A <sup>†</sup>         | 0.1                    | 170*                   | N/A          |

| Nolet [5]         | 65          | 20       | 1.75/9.9        | 8 @470                  | N/A                | 2.8k                     | <10                    | 7.8♯                   | N/A          |

| Webster [14]      | 90          | 6.4      | 14.9/2.4        | 44 @700                 | 22                 | 8.1k                     | 0.375                  | 84                     | N/A          |

| This Work         | 180         | 25-100   | 1-11/22         | 25-55@480 <sup>2</sup>  | 3-8.4 <sup>x</sup> | 0.06-0.23 <sup>y</sup>   | $\sim$ 0.12-3 $^z$     | 12.1 <sup>1</sup>      | 2.78E+13     |

$^a$ At 20°C. $^b$ 200 $\mu$ m-diameter, at 25°C, 80 ns dead time, $V_{EX}$ =5V. $^c$ 820 nm wavelength.  $^d$ At 25°C. $^d$ 24 ns dead time.  $^e$ 30  $\mu$ m-diameter, at 25°C, 40 ns dead time, $V_{EX}$ =5 V, integrated AQC.  $^f$ A time resolution of 28-37 ps FWHM and a diffusion tail of 160-340 ps were demonstrated in Ref. [45] using the substrate bias as a trade-off parameter between jitter and diffusion tail.  $^g$ PDE=10-13% at 800 nm.  $^h$ 300 ns dead time,  $V_{EX}$ =2-10 V. $^t$ 637 nm wavelength.  $^i$ 8 Substrate not isolated SPAD.  $^j$ 300 ns dead time,  $V_{EX}$ =4V. $^k$ 300 ns dead time,  $V_{EX}$ =11 V. $^t$ 50 ns dead time,  $V_{EX}$ =11.5-5 V. $^m$ 831 nm wavelength.  $^n$ 200 ns dead time,  $V_{EX}$ =2V. $^o$ 405 nm wavelength.  $^p$ 200 ns dead time,  $V_{EX}$ =2V. $^q$ 815 nm wavelength.  $^r$ 50 ns dead time.  $^s$ 470 nmwavelength.  $^t$ 180 ns dead time.  $^s$ 470 nmwavelength.  $^t$ 180 ns dead time.  $^s$ 470 nmwavelength.  $^t$ 80 ns dead time.  $^s$ 470 nmwavelength.  $^t$ 90 ns dead time.  $^t$ 91 nm wavelength.  $^t$ 91 nm wavelength.  $^t$ 920 ns dead time.  $^t$ 920 ns dead time.  $^t$ 93 ns on the 25°C on the

Fig. 14. Left: visualization of state-of-the-art performance in terms of PDP and timing jitter. The best solutions are located toward the top-left corner of the graph. Right: Performance comparison in terms of normalized DCR and timing jitter. The best performance is found at the bottom-left corner of the graph.

- [16] F. Villa, D. Bronzi, Y. Zou, C. Scarcella, G. Boso, S. Tisa, A. Tosi, F. Zappa, D. Durini, S. Weyers, U. Paschen, and W. Brockherde, "CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm," *Journal of Modern Optics*, vol. 61, no. 2, pp. 102–115, 2014.

- [17] T. Leitner, A. Feiningstein, R. Turchetta, R. Coath, S. Chick, G. Visokolov, V. Savuskan, M. Javitt, L. Gal, I. Brouk, S. Bar-Lev, and Y. Nemirovsky, "Measurements and simulations of low dark count rate single photon avalanche diode device in a low voltage 180-nm CMOS image sensor technology," *IEEE Transactions on Electron Devices*, vol. 60, no. 6, pp. 1982–1988, 2013.

- [18] C. Veerappan and E. Charbon, "A substrate isolated CMOS SPAD enabling wide spectral response and low electrical crosstalk," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, no. 6, pp. 299–305, 2014.

- [19] C. Veerappan and E. Charbon, "CMOS SPAD based on photo-carrier diffusion achieving PDP >40% from 440 to 580 nm at 4 V excess bias,"

- IEEE Photonics Technology Letters, vol. 27, pp. 2445-2448, 2015.

- [20] M.-J. Lee, P. Sun, and E. Charbon, "A first single-photon avalanche diode fabricated in standard SOI CMOS technology with a full characterization of the device," *Optics Express*, vol. 23, no. 10, pp. 13 200–13 209, May 2015.

- [21] C. Veerappan and E. Charbon, "A low dark count p-i-n diode based SPAD in CMOS technology," *IEEE Transactions on Electron Devices*, vol. 63, pp. 65–71, 2016.

- [22] H. Xu, L. Pancheri, G.-F. D. Betta, and D. Stoppa, "Design and characterization of a p+/n-well SPAD array in 150nm CMOS process," *Optics Express*, vol. 25, no. 11, pp. 12765–12778, May 2017.

- [23] C. Veerappan, "Single-photon avalanche diodes for cancer diagnosis," Ph.D. dissertation, Delft University of Technology, Delft, Netherlands, March. 2016.

- [24] M. Sanzaro, P. Gattari, F. Villa, A. Tosi, G. Croce, and F. Zappa, "Single-photon avalanche diodes in a 0.16 μm BCD technology with sharp

- timing response and red-enhanced sensitivity," *IEEE Journal of Selected Topics in Quantum Electronics*, pp. 1–1, 10 2017.

- [25] S. Pellegrini, B. Rae, A. Pingault, D. Golanski, S. Jouan, C. Lapeyre, and B. Mamdy, "Industrialised SPAD in 40 nm technology," in *IEEE International Electron Devices Meeting (IEDM)*, 12 2017, pp. 16.5.1–16.5.4.

- [26] C. Bruschini, H. Homulle, I. M. Antolovic, S. Burri, and E. Charbon, "Single-photon avalanche diode imagers in biophotonics: review and outlook," *Light: Science & Applications*, vol. 8, no. 1, p. 87, 2019.

- [27] X. Michalet, A. Ingargiola, R. A. Colyer, G. Scalia, S. Weiss, P. Maccagnani, A. Gulinatti, I. Rech, and M. Ghioni, "Silicon photoncounting avalanche diodes for single-molecule fluorescence spectroscopy," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, no. 6, pp. 248–267, 2014.

- [28] G. Buller and A. Wallace, "Ranging and three-dimensional imaging using time-correlated single-photon counting and point-by-point acquisition," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 13, no. 4, pp. 1006–1015, 2007.

- [29] M. A. Karami and M. Ansarian, "Neural imaging using single-photon avalanche diodes," *Basic and Clinical Neuroscience Journal*, vol. 8, no. 1, 2017.

- [30] H. Takesue, E. Diamanti, C. Langrock, M. Fejer, and Y. Yamamoto, "10-GHz clock differential phase shift quantum key distribution experiment," Optics Express, vol. 14, no. 20, pp. 9522–9530, 2006.

- [31] A. C. Ulku, C. Bruschini, I. M. Antolović, Y. Kuo, R. Ankri, S. Weiss, X. Michalet, and E. Charbon, "A 512 × 512 SPAD image sensor with integrated gating for widefield flim," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 25, no. 1, pp. 1–12, 2019.

- [32] K. Morimoto, A. Ardelean, M.-L. Wu, A. C. Ulku, I. M. Antolovic, C. Bruschini, and E. Charbon, "Megapixel time-gated SPAD image sensor for 2D and 3D imaging applications," *Optica*, vol. 7, no. 4, pp. 346–354, Apr. 2020.

- [33] S. Lindner, S. Pellegrini, Y. Henrion, B. Rae, M. Wolf, and E. Charbon, "A high-PDE, backside-illuminated SPAD in 65/40-nm 3D IC CMOS pixel with cascoded passive quenching and active recharge," *IEEE Electron Device Letters*, vol. 38, no. 11, pp. 1547–1550, 2017.

- [34] I. M. Antolovic, C. Bruschini, and E. Charbon, "Dynamic range extension for photon counting arrays," *Optics Express*, vol. 26, no. 17, pp. 22 234–22 248, Aug 2018.

- [35] P. Mroszczyk and P. Dudek, "Tunable CMOS delay gate with improved matching properties," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 9, pp. 2586–2595, 2014.

- [36] B. Korzh, T. Lunghi, K. Kuzmenko, G. Boso, and H. Zbinden, "Afterpulsing studies of low-noise ingaas/inp single-photon negative-feedback avalanche diodes," *Journal of Modern Optics*, vol. 62, no. 14, pp. 1151–1157, 2015. [Online]. Available: https://doi.org/10.1080/09500340.2015.1024294

- [37] Z. Cheng, X. Zheng, D. Palubiak, M. J. Deen, and H. Peng, "A comprehensive and accurate analytical spad model for circuit simulation," *IEEE Transactions on Electron Devices*, vol. 63, no. 5, pp. 1940–1948, 2016.

- [38] M. Anti, A. Tosi, F. Acerbi, and F. Zappa, "Modeling of afterpulsing in single-photon avalanche diodes," in *Physics and Simulation* of Optoelectronic Devices XIX, B. Witzigmann, F. Henneberger, Y. Arakawa, and A. Freundlich, Eds., vol. 7933, International Society for Optics and Photonics. SPIE, 2011, pp. 371 – 378. [Online]. Available: https://doi.org/10.1117/12.875143

- [39] S. Cova, A. Lacaita, and G. Ripamonti, "Trapping phenomena in avalanche photodiodes on nanosecond scale," *IEEE Electron Device Lett.*, vol. 12, no. 12, pp. 685–687, Dec. 1991.

- [40] G. Zappalà, F. Acerbi, A. Ferri, A. Gola, G. Paternoster, N. Zorzi, and C. Piemonte, "Set-up and methods for sipm photo-detection efficiency measurements," *Journal of Instrumentation*, vol. 11, no. 08, p. P08014, 2016.

- [41] S. K. Yang, J. Lee, S.-W. Kim, H.-Y. Lee, J.-A. Jeon, I. H. Park, J.-R. Yoon, and Y.-S. Baek, "Precision measurement of the photon detection efficiency of silicon photomultipliers using two integrating spheres," *Optics Express*, vol. 22, no. 1, pp. 716–726, 1 2014.

- [42] R. H. Hadfield, "Single-photon detectors for optical quantum information applications," *Nature Photonics*, vol. 3, no. 12, pp. 696–705, 2009.

- [43] C. Niclass, H. Matsubara, M. Soga, M. Ohta, M. Ogawa, and T. Yamashita, "A NIR-sensitivity-enhanced single-photon avalanche diode in 0.18

µm CMOS," in Proceedings of the International Image Sensor Workshop, Vaals, The Netherlands, 2015, pp. 8–11.

- [44] D. Bronzi, F. Villa, S. Tisa, A. Tosi, and F. Zappa, "Spad figures of merit for photon-counting, photon-timing, and imaging applications: A review," *IEEE Sensors Journal*, vol. 16, no. 1, pp. 3–12, 2016.

[45] M. Buttafava, G. Boso, A. Ruggeri, A. Dalla Mora, and A. Tosi, "Time-gated single-photon detection module with 110 ps transition time and up to 80 MHz repetition rate," *Review of Scientific Instruments*, vol. 85, no. 8, p. 083114, 2014.

Francesco Gramuglia (S'17) major in electronics, received the B.S. degree in Biomedical Engineering from Politecnico di Milano, Milan, Italy, in 2013 and the M.S. degree in Electronics Engineering from Politecnico di Milano, Milan, Italy in 2016. From 2015 to 2016, he was a trainee in the STORMlab of Vanderbilt University, Nashville, Tennessee, where he collaborated on the development of robotic endoscope platforms. In 2016, he received the Best Application Prize and Overall Winner at Surgical Robot Challenge during the Hamlyn Symposium on

Medical Robotics at Imperial College, London, 2016. Since 2017, he has been pursuing a Ph.D. degree at the EPFL in the Advanced Quantum Architecture laboratory (AQUA). In 2021 he received the First Place Nuclear Science Symposium (NSS) Student Paper Award. His research interests focus on the design of deep-submicron Si-SPAD and SPAD-based detectors in standard CMOS and BCD technologies, and system development for use in several applications based on single photon detection, e.g. Time-of-flight Positron emission tomography (TOFPET).

Ming-Lo Wu major in physics and electronics, received the B.S. degree in nano-science and nanoengineering from National Chiao Tung University, Hsinchu, Taiwan, in 2017 and the M.S. degree in nano-engineering from KU Leuven, Belgium, in 2018. Between 2018 and 2019, he served in the military in Taiwan. He then proceeded to continue his study in microsystems and microelectronics. He is currently pursuing the Ph.D. degree at EPFL, Neuchâtel, Switzerland. His research interest includes physics on the device level and system level

applications of advanced electronic components.

Claudio Bruschini (M'12 SM'17) received the Laurea degree in physics from the University of Genova, Italy, in 1992, and the Ph.D. degree in applied sciences from Vrije Universiteit Brussel, Brussels, Belgium, in 2002. He is currently a Scientist and Lab Deputy with EPFL's Advanced Quantum Architecture Laboratory. His scientific interests have spanned from high energy physics and parallel computing in the early days, to challenging sensor applications in humanitarian demining, concentrating since 2003 on quantum photonic devices, high-speed and time-

resolved 2D/3D optical sensing, as well as applications thereof (biophotonics, nuclear medicine, basic sciences, security, ranging). He has authored or co-authored over 130 articles and conference proceedings and one book; he was the co-recipient of the 2012 European Photonics Innovation Award and of the Image Sensors Europe 2019 Award in the category "Best Academic Research Team", as well as Swiss Medtech Award 2016 finalist. He is an IEEE and SPIE Senior Member and co-founder of a start-up commercialising selected AQUA lab SPAD designs.

Myung-Jae Lee (S'08–M'13) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Postdoctoral Researcher with the faculty of electrical engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applica-

tions based on single-photon avalanche diodes. In 2017, he joined the school of engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Senior Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests have spanned from photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof (e.g., LiDAR, D-ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, optical interconnects, etc.).

Edoardo Charbon (SM'00 F'17) received the Diploma from ETH Zurich, the M.S. from the University of California at San Diego, and the Ph.D. from the University of California at Berkeley in 1988, 1991, and 1995, respectively, all in electrical engineering and EECS. He has consulted with numerous organizations, including Bosch, X-Fab, Texas Instruments, Maxim, Sony, Agilent, and the Carlyle Group. He was with Cadence Design Systems from 1995 to 2000, where he was the Architect of the company's initiative on information hiding

for intellectual property protection. In 2000, he joined Canesta Inc., as the Chief Architect, where he led the development of wireless 3-D CMOS image sensors. Since 2002 he has been a member of the faculty of EPFL. From 2008 to 2016 he was with Delft University of Technology's as Chair of VLSI design. He has been the driving force behind the creation of deepsubmicron CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. His interests span from 3-D vision, LiDAR, FLIM, FCS, NIROT to superresolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for the control of qubit arrays in quantum computers. He has authored or co-authored over 400 papers and two books, and he holds 23 patents. Dr. Charbon is a distinguished visiting scholar of the W. M. Keck Institute for Space at Caltech, a fellow of the Kavli Institute of Nanoscience Delft, a distinguished lecturer of the IEEE Photonics Society, and a fellow of the IEEE.