Thèse n°7949

# EPFL

### Architecture Exploration and Optimization of Heterogeneous Many-Core Compute and Memory Architectures with Architectural Extensions

Présentée le 10 septembre 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire des systèmes embarqués Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### Yasir Mahmood QURESHI

Acceptée sur proposition du jury

Prof. A. M. Alahi, président du jury Prof. D. Atienza Alonso, directeur de thèse Prof. A. Coskun, rapporteuse Dr J. Picorel , rapporteur Prof. A. Burg, rapporteur

École polytechnique fédérale de Lausanne

2021

There is only one thing that makes a dream impossible to achieve: the fear of failure — Paulo Coelho

To my loving parents; To my amazing and wonderful wife; And to my beautiful lively kids.

### Acknowledgements

To being with, first and fore-most, I will to thank and express my deepest gratitude to my thesis director **Prof. David Atienza** for not only giving me the opportunity to pursue my Ph.D. at the Embedded Systems Laboratory (ESL), but also supervising and guiding me throughout this journey. This Ph.D. thesis would not have been possible without his continuous support and advise. I will also like to thank him for helping me grow professionally and enabling me to gain a wide range of skills not just from research perspective, but as a person as well. I am also grateful to him for creating a conformable and amiable environment at work and taking care of our needs in the lab. Additionally, I will like to thank him for all the ESL activities including annual Christmas dinners, summer BBQs and ESL team building activities, which is something that is very unique to ESL. Finally, I appreciate and am grateful to him for being compassionate, considerate and always listening to my personnel circumstances and accommodating them accordingly.

I will like take this opportunity to thank and and express my gratitude to the jury members comprising of **Prof. Alexandre Alahi, Prof. Andreas Burg, Prof. Ayse Coskun,** and **Dr. Javier Picorel**, for taking out time from their busy schedules to evaluate this thesis and providing valuable feedback.

Then, I will like to thank **Prof. Marina Zapater**, who was my supervising post-doc and go to person throughout my Ph.D. I am grateful to her for helping and guiding me whenever I was stuck in something, encouraging and supporting me whenever there was a rejected paper and finally, reviewing and helping me with different publications, which would not have been possible without her valuable feedback. I will like to thank **Prof. Katzalin Olcoz, Prof. Sonia Gonzalez-Navarro** and **Prof. Oscar Plata**, with whom I have various publications in different collaborations. I am also particularly grateful to **Miguel Peon Quiros** and **Luis Costero** for reviewing and proof-reading this thesis and providing valuable feedback on it.

Furthermore, I will like thank ESL's administrative assistant **Homeira Salimi** taking care of all the administrative matters, from booking hotels and flights abroad for conferences to organization of Ski trips, ESL dinners and birthdays. I will like to appreciate and thank the IT administrators at ESL, including **Rodolphe Buret**, **Mikael Doche** and **Thomas Christoph** for resolving my day-to-day IT related problems, and enabling me to carry out my research seamlessly. I will also like to thank the post-doctoral researchers in the lab, including **Ruben Braojos, Amir Aminifar, Leila Cammoun, Giovanni Ansaloni, Adriana Arza, Alexandre Levisse, Dennis Majoe** and **Tomas Teijeiro**, with whom I worked directly or indirectly, either for work, research or just a chat in the kitchen. Moreover, I will like to express my gratitude to my office mates, **Loris, Gregoire**,

#### Acknowledgements

Josh and Nacho, for sharing the nice ELG-132 office with me and having good conversations on a range of topics. I will like to extend my gratitude to all the past and present ESL Ph.D. students, including Ali Pahlevan, Arman Iranfar, Soumya Basu, Benoît Denkinger, Dionisije Sopic, Elisabetta De Giovanni, Artem Andreev, Halima Najibi, Farnaz Forooghifar, Flavio Ponzina, Renato Zanetti, William Simon, Marco Rios, Darong Huang, Alireza Amirshahi, Saleh Baghersalimi, Simone Machetti, Giulio Masinelli, Rafael Morillas, Una Pale, Hossein Taji, Pengbo Yu and Silvio Zanoli, for the great moments and wonderful time spent with them. It is these colleagues that make ESL international and multi-cultural.

This journey would not have been possible without all the new friends that I made during my stay in Lausanne. I will like to thank the **Pakistani-Students Society Lausanne** and all my Pakistani friends here in Switzerland, who were there for me whenever I needed them and for arranging the wonderful Eid BBQ's. I will also grateful to all my friends at **GMU** for arranging the amazing Ramadan Iftars every year. I will take this opportunity to give a shout-out and express my gratitude to my friend **Anas**, who was always there for me and my family, since our arrival in Switzerland.

Furthermore, I will to thank all my family for their continuous support. In particular, I will like to start by expressing my deepest gratitude to my **father Nasir Mahmood Qureshi**, who always wished and dreamed for me to be become a Ph.D. scholar. A dream that he narrowly missed himself, and wished for one of his children to complete. It was he who convinced and motivated me to pursue this journey. I am proud and glad that I could fulfil his dream, and he could see the start of this journey, however, I feel sad and grieved at the same time, as he is no longer with us to witness the completion my Ph.D., one of the most important milestones in my life. Next, I will like to thank my **mother Tallat Nasir**, for all her support and prayers for my success, and taking time to talk to me every single day trying to keep me motivated and going. I will also like thank my brothers **Waqas** and **Haris**, for being very supportive and taking care of the matters back home in Pakistan on my behalf. I also want to thank my **father-in-law Dr. Qamar Mubashir** and **mother-in-law Kulsoom Mubashir** for believing in me and being very encouraging and supportive throughout the journey.

Last but not the least, I will like to say special thanks to my wonderful and amazing wife **Ramsha**, who was very supportive throughout this journey from the very start of making the decision to pursue a Ph.D. I really appreciate her for being very understanding during the course of my Ph.D. It was her who motivated me daily, kept me focused on my research by taking care of our beautiful kids and all the house-hold stuff, and prepared delicious meals and dinners everyday. The effort and contributions she did in enabling me to be focused on my research are beyond words. Moreover, I will to say a big thanks to my two little cute sons, **Arham** and **Affan**, who are the joy of my life, and relieved me of all the work and research related stress everyday, whenever I returned back home. They made this journey really wonderful. It would not have been the same experience without the joyful moments I had with them, and to which I looked forward everyday when coming back home.

Lausanne, August 22, 2021

Yasir Mahmood Qureshi

### Abstract

The expeditious proliferation of Internet connectivity and the growing adoption of digital products have transformed various spheres of our everyday lives. This increased digitization of society has led to the emergence of new applications, which are deployed all the way from High Performance Computing (HPC) systems and cloud servers to mobile devices. These new emerging applications like video analytics, autonomous driving, natural language processing, content recommendation, bioinformatics, and genome sequencing, have different performance/energy requirements, and are deployed on a variety of different platforms. To meet the performance and Quality-of-Service (QoS) constraints, cloud servers, and HPC platforms are comprised of many-core processors. Even the processors in today's mobile and edge devices are multi-core. To optimize energy efficiency and performance, a system-level simulator is required. This simulator must be capable of simultaneously executing multi-threaded applications in a full-system environment with a complete operating system (OS), on a heterogeneous many-core system.

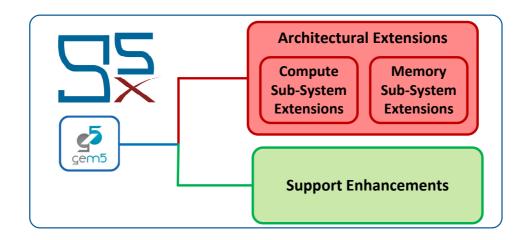

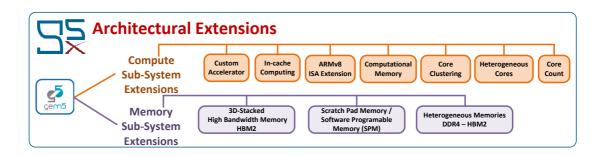

In this thesis, I present gem5-X, a system-level simulation platform to optimize many-core heterogeneous compute and memory architectures. Gem5-X exploration and optimization methodology is also proposed to optimize both the compute and memory sub-system for multi-thread applications. Gem5-X extends gem5 with architectural extensions for the compute and memory sub-systems, including in-caching computing accelerator, clustered heterogeneous cores, inmemory computing engine, and 3D stacked High Bandwidth Memory v2 (HBM2). It also adds support enhancements to gem5, including, Virtual Machine (VM) support, profiling support in the simulator using gperf profiler, enhanced checkpointing, and file sharing between the simulated and the host system. Finally, all the extensions and enhancements are fully supported in Full System (FS) mode of gem5-X, enabling booting and running a full Linux stack on top of the simulator, allowing almost any application running in a Linux system to be executed using gem5-X.

To demonstrate the capabilities of gem5-X, various compute-dominated and memory-dominated applications are used as case studies. These state-of-the-art applications include video encoding, video analytics, VMs in the cloud, Binary Neural Networks (BNNs) and Recurrent Neural Networks (RNNs) as compute-intensive workloads. In addition to compute-dominated workloads, memory-dominated applications, including genome sequence alignment based on Next Generation Sequencing (NGS) techniques, and Convolutional Neural Networks (CNNs) are presented as case studies to demonstrate the memory sub-system extensions of gem5-X. Gem5-X exploration

methodology is used to optimize architectures for these applications, achieving both performance and energy benefits. All the applications and workloads used in this thesis are case studies to showcase the capabilities of gem5-X. Gem5-X is generic and can be used to optimize and explore architectures for any multi-threaded (or single-threaded) application that can run on a Linux-based OS.

**Keywords:** Many-core, multi-core, heterogeneous architectures, architecture exploration, simulator, gem5, gem5-X, in-cache computing, in-memory computing, HBM, 3D ICs, SPM, 3D stacked memory, CNN, NGS, genome sequencing, High Performing Computing (HPC), Cloud Computing

### Résumé

L'augmentation de la connectivité internet et de l'utilisation de produits digitaux ont transformé différentes facettes de notre vie quotidienne. La digitalisation de notre société a fait apparaître de nouvelles applications qui sont déployées sur tout l'éventail de l'infrastructure informatique, des serveurs cloud et centre de Calcul Haute Performance (HPC) jusqu'aux appareils mobiles. Ces applications, telles que l'analyse vidéo, la conduite autonome, le traitement du langage naturel, ou le séquençage du génome, ont des exigences différentes en matière de performances/-énergie et sont déployées sur une large gamme d'appareils. Pour répondre aux contraintes de performances et de qualité de service, les serveurs cloud et les plateformes HPC sont composés de processeurs multicœurs. Même les processeurs des téléphones mobiles et des dispositifs périphériques d'aujourd'hui sont multicœurs. Pour optimiser leur efficacité énergétique et leurs performances, un simulateur du système complet est nécessaire. Ce dernier doit être capable d'exécuter simultanément des applications multithread dans un environnement système complet avec un système d'exploitation (OS) complet, sur un système multicœurs hétérogène.

Dans cette thèse, je présente gem5-X, une plateforme de simulation au niveau système pour optimiser les architectures de calculs et de mémoire hétérogènes à plusieurs cœurs. Gem5-X propose aussi une méthodologie pour l'exploration et l'optimisation à la fois du sous-système de calcul et de la mémoire, pour les applications multithread. Gem5-X étend gem5 avec des extensions architecturales, notamment un accélérateur de calcul en cache, des cœurs hétérogènes groupés, un moteur de calcul en mémoire et une mémoire à bande passante élevée (HBM2) empilée en 3D. Gem5-X apporte également plus de support à gem5, y compris, mais sans s'y limiter, la prise en charge du profilage dans le simulateur à l'aide du profileur gperf. Toutes les extensions et améliorations sont entièrement prises en charge en mode Système complet de gem5-X, permettant de démarrer et d'exécuter une couche Linux complète sur le simulateur et ainsi d'exécuter presque toutes les applications fonctionnant sur un système Linux.

Pour démontrer les capacités de gem5-X, diverses applications dominées par leur demande en calculs et en mémoire sont utilisées comme études de cas. Ces applications de pointes incluent l'encodage vidéo, l'analyse vidéo, les machines virtuelles dans le cloud, les réseaux de neurones binaires (BNN) et les réseaux de neurones récurrents (RNN), l'alignement de séquences génomiques basé sur les techniques de séquençage de nouvelle génération (NGS) et les réseaux de neurones à convolution (CNN). La méthodologie d'exploration Gem5-X est utilisée pour optimiser les architectures pour ces applications, permettant à la fois des avantages en termes de performances et d'énergie.

**Mots-clés :** Architectures multicœurs, architectures hétérogènes, exploration d'architecture, simulateur, gem5, gem5-X, calcul en cache, calcul en mémoire, HBM, circuits intégrés 3D, SPM, mémoire 3D empilé, CNN, NGS, séquençage du génome, Calcul Haute Performance (HPC), calcul dans le cloud

## Contents

| Ac | know    | ledgem        | ents        |                                                             | i    |

|----|---------|---------------|-------------|-------------------------------------------------------------|------|

| Ał | ostrac  | t (Engli      | sh)         |                                                             | iii  |

| Ré | ésumé   | (França       | is)         |                                                             | v    |

| Li | st of l | igures        |             |                                                             | xiii |

| Li | st of ] | <b>Fables</b> |             |                                                             | xix  |

| Ac | rony    | ms            |             |                                                             | xxi  |

| 1  | Intr    | oductior      | 1           |                                                             | 1    |

|    | 1.1     | The Po        | wer Wall    | Problem                                                     | 2    |

|    | 1.2     | The Me        | emory Wa    | ll Problem                                                  | 3    |

|    | 1.3     | Thesis        | Contribut   | ion                                                         | 3    |

|    |         | 1.3.1         | The Gem     | 15-X Simulator                                              | 4    |

|    |         |               | 1.3.1.1     | Architectural Extensions                                    | 4    |

|    |         |               | 1.3.1.2     | Support Enhancements                                        | 5    |

|    |         | 1.3.2         | Compute     | -Dominated Architecture Exploration                         | 6    |

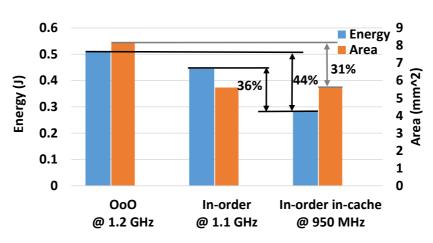

|    |         |               | 1.3.2.1     | Architecture Optimization for Video Encoding                | 6    |

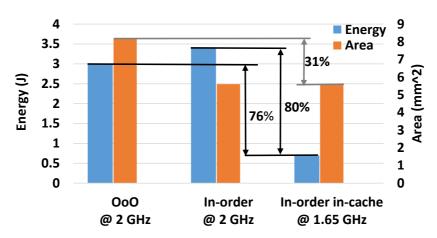

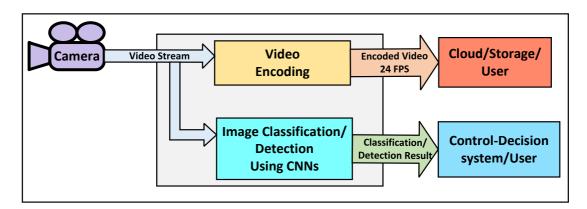

|    |         |               | 1.3.2.2     | Heterogeneous Architecture for Video Analytics              | 7    |

|    |         |               | 1.3.2.3     | Near-Threshold-Computing (NTC) Servers for VMs in the       |      |

|    |         |               |             | Cloud                                                       | 8    |

|    |         |               | 1.3.2.4     | In-Memory Computation of Artificial Intelligence (AI) Work- | _    |

|    |         |               |             | loads                                                       | 9    |

|    |         | 1.3.3         | •           | Dominated Architecture Exploration                          | 10   |

|    |         |               | 1.3.3.1     | Genome Sequence Alignment                                   | 10   |

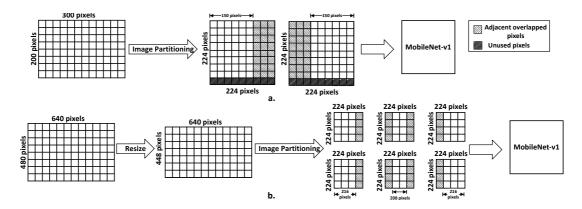

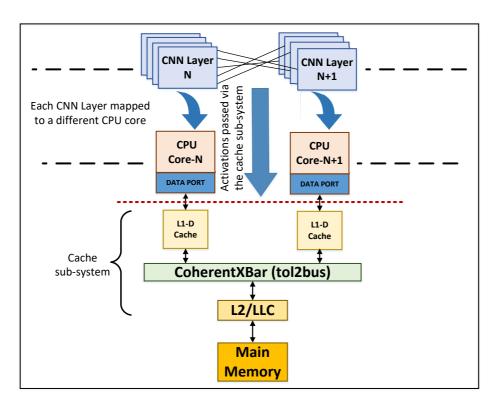

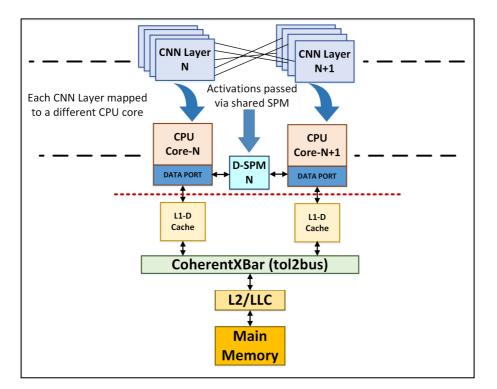

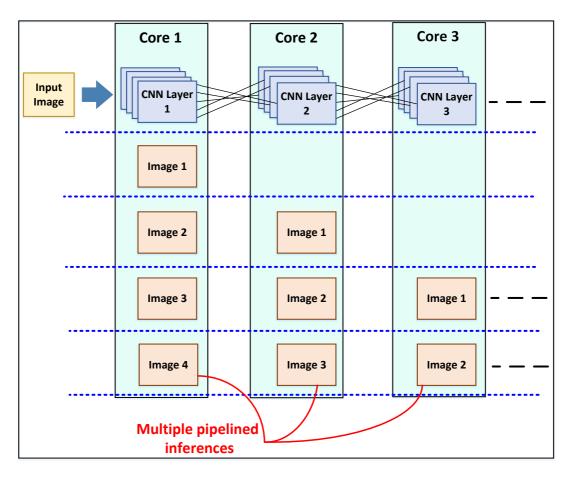

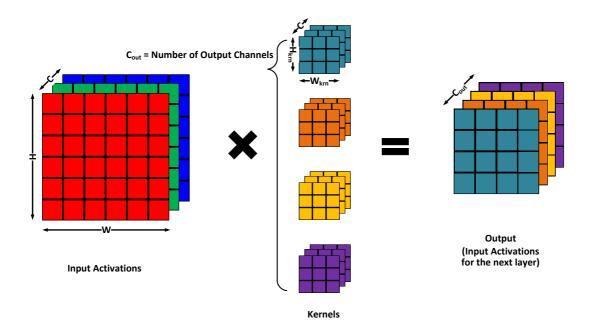

|    |         |               | 1.3.3.2     | Scratchpad Memories (SPMs) for CNNs                         | 11   |

| 2  | The     | Gem5-X        | K Simulat   | or                                                          | 13   |

|    | 2.1     | Introdu       | ction       |                                                             | 13   |

|    | 2.2     | Related       | l work .    |                                                             | 15   |

|    | 2.3     | Archite       | ectural Ext | tensions                                                    | 16   |

|     | 2.3.1                                                                                                 | Compute Sub-System                                                                                                                                                                                                                                                        | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     |                                                                                                       | 2.3.1.1 ISA Extension                                                                                                                                                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.2 Custom Accelerator                                                                                                                                                                                                                                                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.2.1 Memory Mapped Accelerator                                                                                                                                                                                                                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.2.2 Custom Instruction Accelerator                                                                                                                                                                                                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

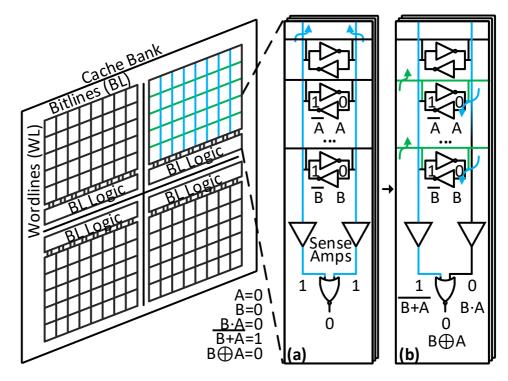

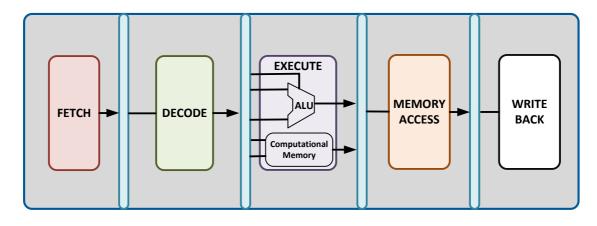

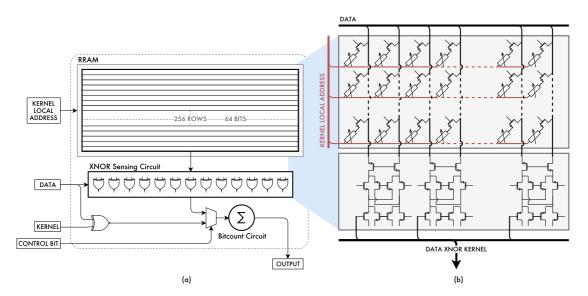

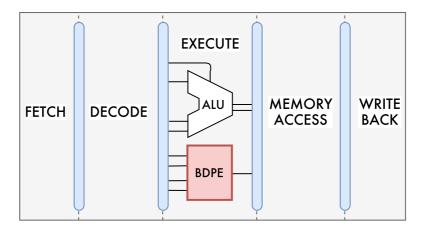

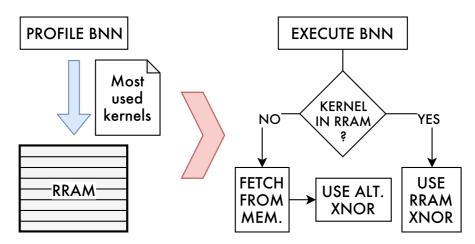

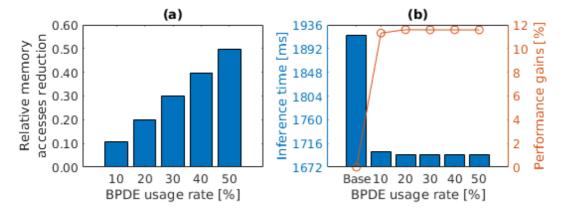

|     |                                                                                                       | 2.3.1.3 BLADE In-cache Computing Engine                                                                                                                                                                                                                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.4 Computational Memory                                                                                                                                                                                                                                              | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

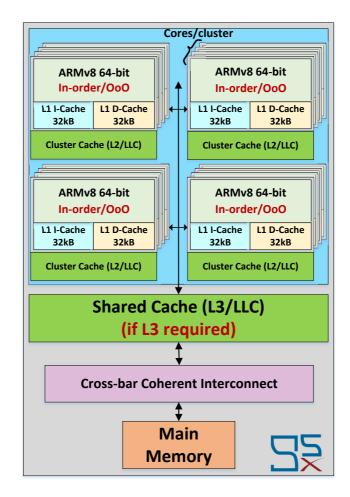

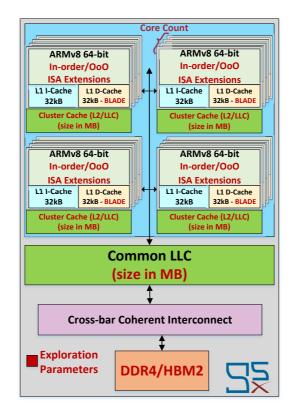

|     |                                                                                                       | 2.3.1.5 Core Clustering                                                                                                                                                                                                                                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.6 Heterogeneous Cores                                                                                                                                                                                                                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.1.7 Core Count                                                                                                                                                                                                                                                        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.3.2                                                                                                 | Memory Sub-System                                                                                                                                                                                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

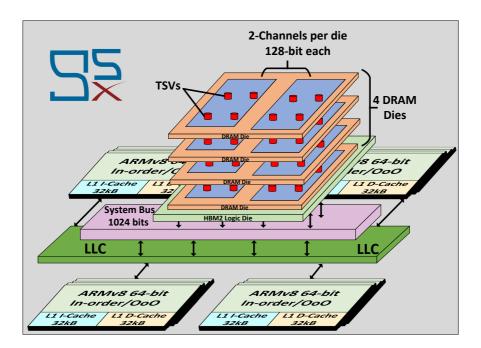

|     |                                                                                                       | 2.3.2.1 High Bandwidth Memory v2 (HBM2)                                                                                                                                                                                                                                   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

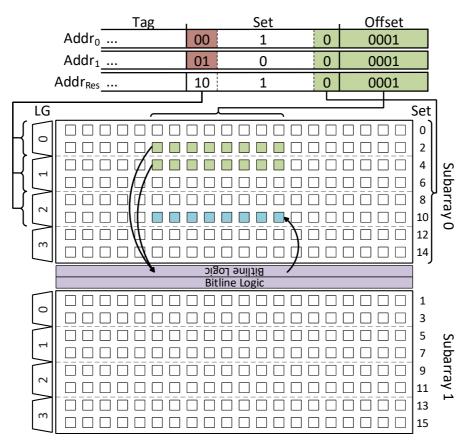

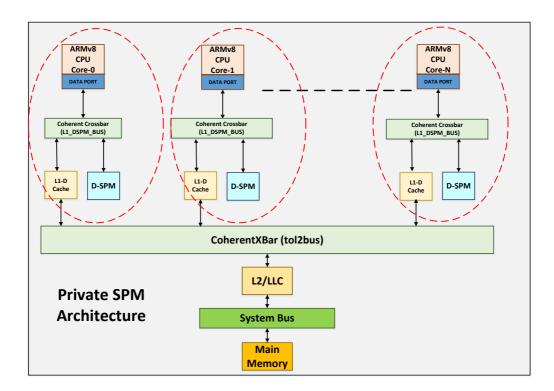

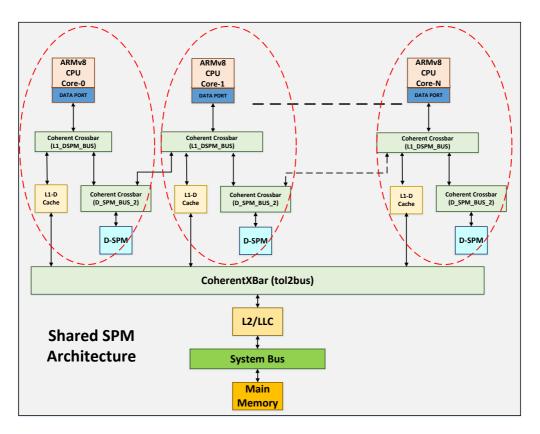

|     |                                                                                                       | 2.3.2.2 ScratchPad Memory (SPM)                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.3.2.3 Heterogeneous Memories                                                                                                                                                                                                                                            | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.3.3                                                                                                 | Gem5-X Parameters                                                                                                                                                                                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

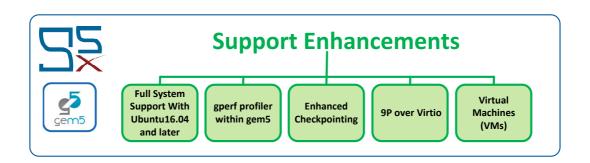

| 2.4 | Suppor                                                                                                | rt Enhancements                                                                                                                                                                                                                                                           | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.4.1                                                                                                 | ARMv8 64-bit Full System (FS) Support                                                                                                                                                                                                                                     | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.4.2                                                                                                 | Gperf Profiler                                                                                                                                                                                                                                                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.4.3                                                                                                 | 1 8                                                                                                                                                                                                                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.4.4                                                                                                 | 9P over Virtio                                                                                                                                                                                                                                                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.4.5                                                                                                 | Virtual Machines (VMs)                                                                                                                                                                                                                                                    | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

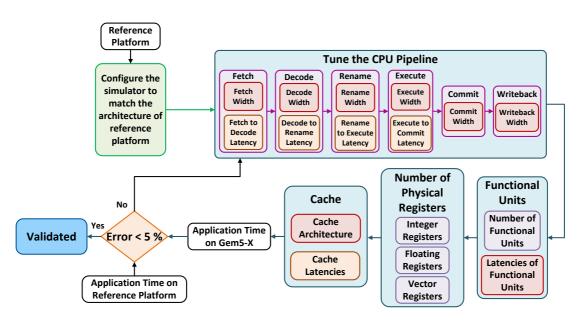

| 2.5 | Validat                                                                                               | tion                                                                                                                                                                                                                                                                      | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

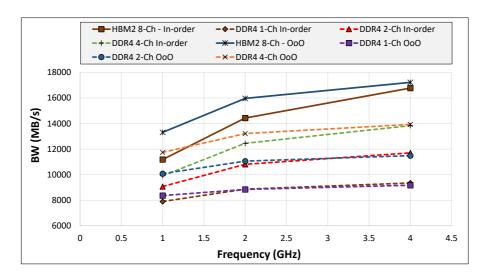

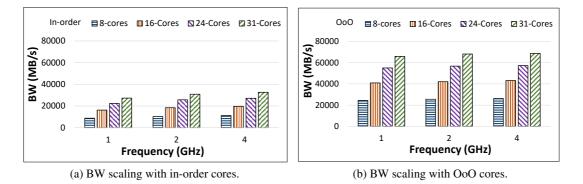

| 2.6 | HBM2                                                                                                  | 2 Model Bandwidth Analysis                                                                                                                                                                                                                                                | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

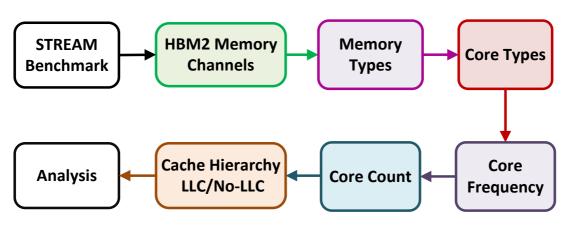

|     | 2.6.1                                                                                                 | BW Analysis Methodology                                                                                                                                                                                                                                                   | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

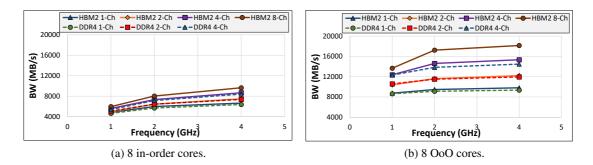

|     | 2.6.2                                                                                                 | Bandwidth Analysis Results                                                                                                                                                                                                                                                | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 2.7 | Power Models and Area                                                                                 |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

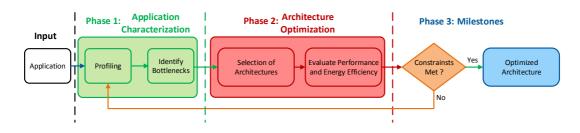

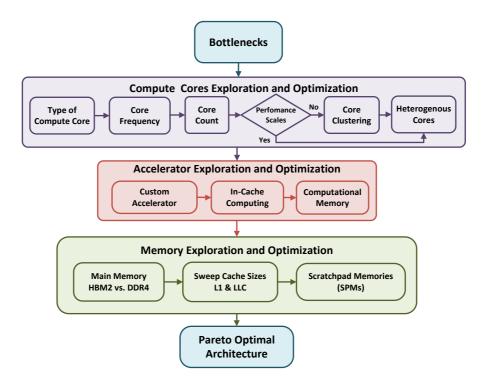

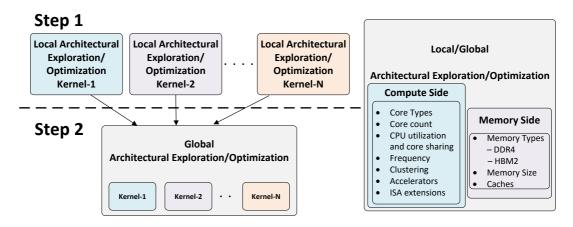

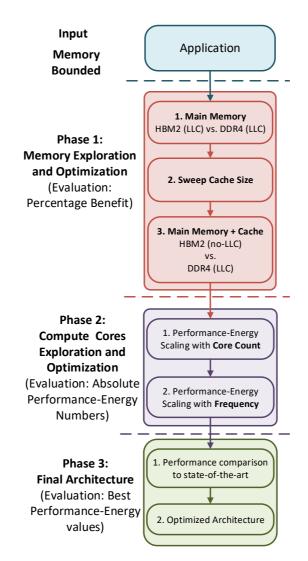

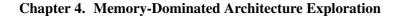

| 2.8 | Architecture Exploration and Optimization Methodology                                                 |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|     | 2.8.1                                                                                                 | Single-Step Architecture Exploration and Optimization Methodology .                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.8.1.1 Phase 1: Application Characterization                                                                                                                                                                                                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       | 2.8.1.2 Phase 2: Architecture Optimization                                                                                                                                                                                                                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                                                                                       |                                                                                                                                                                                                                                                                           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 2.8.2                                                                                                 |                                                                                                                                                                                                                                                                           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 2.9 | Summ                                                                                                  | ary                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

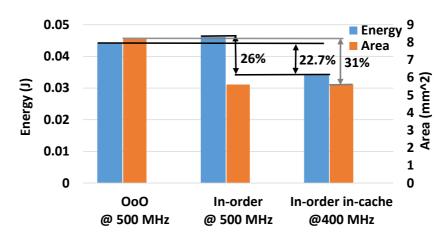

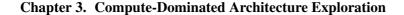

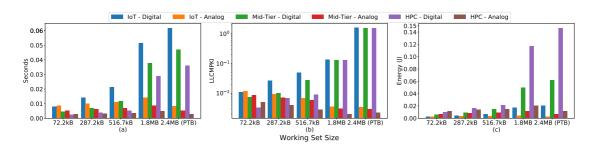

| Com | pute-D                                                                                                | -                                                                                                                                                                                                                                                                         | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3.1 |                                                                                                       |                                                                                                                                                                                                                                                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3.2 |                                                                                                       |                                                                                                                                                                                                                                                                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

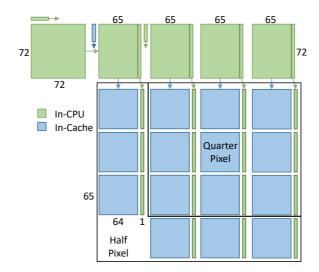

|     | 3.2.1                                                                                                 | 6                                                                                                                                                                                                                                                                         | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 3.2.2                                                                                                 | •                                                                                                                                                                                                                                                                         | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | 3.2.3                                                                                                 |                                                                                                                                                                                                                                                                           | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |