Thèse n° 9082

# EPFL

# Resource Trade-Offs in Circuits and Systems: from Neurotechnology to Communications

Présentée le 30 août 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de systèmes d'information et d'inférence Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

## Arda URAN

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury Prof. V. Cevher, Prof. Y. Leblebici, directeurs de thèse Prof. A. Emami, rapporteuse Dr P. Muller, rapporteur Prof. A. P. Burg, rapporteur

École polytechnique fédérale de Lausanne

2021

The struggle to free myself of restraints becomes my very shackles. — Meshuggah, *Disenchantment*, Catch 33

To my family...

## Acknowledgments

First and foremost, I would like to express my gratitude to my advisors Prof. Volkan Cevher and Prof. Yusuf Leblebici. I had the privilege of conducting diverse and exciting research projects under their patient guidance throughout my time at EPFL. They always supported my ideas and gave me the freedom to explore them, which influenced my professional and personal development as a researcher and as an engineer. I cannot thank them enough for giving me this unique opportunity.

I would like to extend my sincere thanks to Prof. Azita Emami, Dr. Paul Muller, Prof. Andreas Burg, and Prof. Giovanni De Micheli for serving in my thesis committee and reviewing the work presented here. I am grateful to Prof. Azita Emami also for hosting me at her laboratory in Caltech with great hospitality for three wonderful months. I also wish to thank Prof. Catherine Dehollain and Prof. Stéphanie Lacour for our fruitful collaboration, and Prof. Andreas Burg for generously sharing the test facilities of his laboratory.

I must mention Prof. Armin Tajalli as a *de facto* co-advisor of the second part of this thesis, and thank him for his close involvement. I have learned so much as a designer from his rigorous and systematic approach to high-speed circuits.

This thesis was made possible by the valuable contributions of many collaborators. I would like to begin with thanking Dr. Cosimo Aprile for his strong support during my first year and introducing me to the learning-based compression concepts. Special thanks to Dr. Kerim Türe for boosting the value of the neural recording chip project by adding the wireless capabilities, and also for helping me with my measurements. Many thanks to Dr. Florian Fallegger and Dr. Alix Trouillet for providing the electrodes and performing the surgery for *in vivo* validation.

It was a great pleasure working with Dr. Alain Vachoux since my first year at EPFL as his student, assistant, and colleague. I gratefully acknowledge his timely support for the design tools and the server infrastructure, which were essential for meeting the strict tapeout deadlines. I also thank Dr. Alexandre Schmid for his help with the laboratory organization.

I received invaluable assistance from our electronics technician Sylvain Hauser, who helped me get my PCBs running with countless reworks, and has always been ready to help when I needed. I had the chance to benefit from the experience of Peter Brühlmeier, who designed an excellent RF PCB. I very much appreciate the help of my colleagues Thomas Sanchez and Igor Krawczuk for setting up the machine learning experiments. I would also like to recognize the support of Gosia Baltaian and Patricia Vonlanthen for all administrative matters.

#### Acknowledgments

The journey towards this thesis has been inherently full of hurdles, and a global pandemic or the departure of an advisor certainly did not make it any easier. Therefore, my biggest thanks are to my wife, friends and family, from whom I found the strength to persevere.

The fun we had with my officemates and true friends, Dr. Cosimo Aprile and Dr. Jonathan Narinx, inside and outside ELD 335, will always remain as the fondest memories of my time at EPFL. I will miss Jonathan saving me from mountain tops on multiple occasions, and I will never forget Cosimo's greatest advice: "it is better to regret, than not to [sic]". Special thanks to Valentine, Rachele, and Victor for joining us occasionally.

I would also like to thank my colleagues at LSM: Dr. Kiarash Gharibdoust, Dr. Can Baltacı, Dr. Jury Sandrini, Dr. Elmira Shahrabi, Dr. Reza Navid Ranjandish, Dr. Cecilia Giovinazzo, Dr. Mustafa Kilic, Dr. Duygu Kostak, Dr. Bilal Demir, and Dr. Gain Kim; and my colleagues at LIONS: Thomas Sanchez, Igor Krawczuk, Dr. Baran Gözcü, Thomas Pethick, Paul Rolland, Fabian Latorre, Leello Dadi, Ahmet Alacaoğlu, Ali Kavis, Fatih Sahin, and Pedro Abranches, for the good times we shared throughout the years.

The work presented here was conducted in three cities: Lausanne, Sion, and Pasadena, where I had the chance to meet awesome people. I would like to thank Dr. Mish Ebrahim, Dr. Giovanni Resta, Dr. Bardiya Valizadeh, and Özge Kadıoğlu for being amazing chefs; Dr. Chris Ireland, Dr. Samantha Anderson, Dr. Kyriakos Stylianou, Dr. Alina Kampouri, Dr. Arunraj Chidambaram, and Dr. Andrzej Gladysiak for treating me as one of their officemates; Peanut, Lila, and Luna for being good dogs; Nancy McGuire for being such a lovely host and flatmate; Benyamin Haghi for our productive gym sessions, and counteracting lunch breaks at Ernie's; and finally, the SBB train crew for welcoming me on the InterRegio 90 every morning and evening, frequently at nights as well.

I do not always have luck, but when I do, I am the luckiest. The biggest luck I had during these years, and in my life in general, has been having my wife Dr. Pelin Kınık ( $\pi$ ) always by my side. I could not have reached the end without her helping me to rise back to my feet every time I fell. I am also proud in the sense that our exchange of love notes in high school has evolved into exchanging love notes in our thesis acknowledgments.

I dedicate this thesis to my mother Sevda and grandmother Bingül, from whom I inherited the determination to endure this tough but rewarding journey. Sevgili annem ve anneannem, bu tezi tamamlamak için ihtiyacım olan azmi ve kararlılığı size borçluyum. Tüm özveriniz ve sınırsız desteğiniz için sonsuz teşekkürler. Sizi seviyorum.

Sion, June 22, 2021

Arda Uran

This work was supported by Hasler Foundation Program: Cyber Human Systems (project number 16066), and the Department of the Navy, Office of Naval Research (ONR) under the grant number N62909-17-1-2111.

## Abstract

This thesis aims to explore and exploit trade-offs in integrated circuits and systems to overcome the fundamental bottlenecks faced by future data acquisition and communication systems. Specifically, we target the emerging implantable neurotechnology and the advancing high-speed communication domains as case studies.

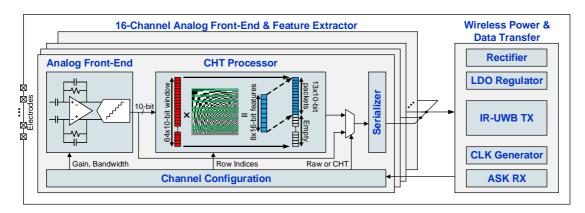

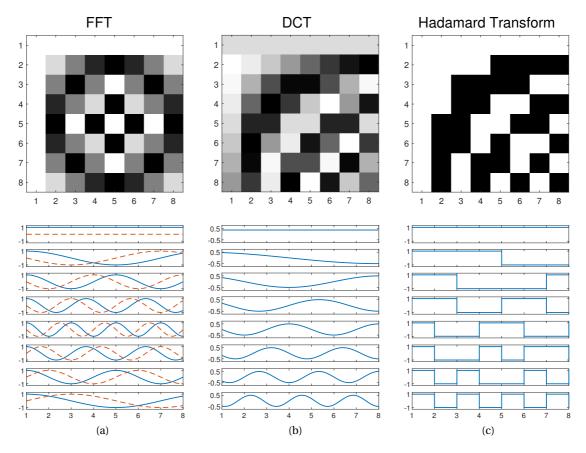

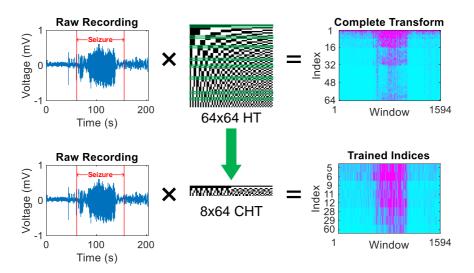

The first part of the thesis addresses the extreme resource constraints of implantable neurotechnology. As the number of electrodes for neural recording reaches towards thousands, a single-chip solution is rendered infeasible in terms of both energy and area. To tackle this problem, we present an analog front-end architecture that applies various energy- and areasaving techniques to reduce the hardware resource demand of neural recording. The second challenge has been transferring the massive data throughput over a wireless link to allow neural recording in independent environments. Inspired by the previous ideas for compression and the emerging machine learning applications in neuroscience, we introduce an on-chip adaptive feature extraction framework to reduce the overall data rate to the feasible range.

The second part of the thesis focuses on the timing uncertainty problem in high-speed communication systems. The increasing data rates in wireline and wireless transceivers, and the emerging need for multitransceiver architectures necessitate the lowest energy and area for the frequency synthesis, which contradicts the current jitter-cost trade-off paradigm. To allow the use of area-efficient ring oscillators for jitter-sensitive applications under low-power constraints, we introduce a multiphase feedback phase-locked loop architecture, which suppresses the oscillator phase noise over a larger bandwidth.

### Keywords:

Implantable neurotechnology, high-density neural recording, analog front-end (AFE), AC coupling, inverter-based low-noise amplifier (LNA), analog-to-digital converter (ADC), successive approximation register (SAR), monotonic switching, unit-length capacitor (ULC), on-chip compression, compressed Hadamard transform (CHT), wireless power and data transfer, machine learning, seizure detection, joint training, frequency synthesizer, phase-locked loop (PLL), loop bandwidth, Gardner's limit, multiphase feedback (MPF), voltage controlled ring oscillator, matrix phase detector (MPD).

## Résumé

Cette thèse vise à explorer et exploiter des compromis dans les circuits et systèmes intégrés pour surmonter les goulots d'étranglement fondamentaux auxquels sont confrontés les futurs systèmes d'acquisition de données et de communication. Plus précisément, nous ciblons les applications émergentes dans les domaines de la neurotechnologie implantable et celui des communications à haut débit comme études de cas.

La première partie de la thèse aborde les contraintes de ressources extrêmes de la neurotechnologie implantable. Comme le nombre d'électrodes pour l'enregistrement neuronal atteint des milliers, une solution à puce électronique unique est rendue irréalisable en termes d'énergie et de surface. Pour résoudre ce problème, nous présentons une architecture frontale analogique qui applique diverses techniques d'économie d'énergie et de surface pour réduire la demande en ressources matérielles de l'enregistrement neuronal. Le deuxième défi a été de transférer l'énorme débit de données sur une liaison sans fil pour permettre l'enregistrement neuronal dans des environnements indépendants. Inspiré par les idées précédentes pour la compression et les applications émergentes d'apprentissage automatique en neuroscience, nous introduisons un cadre d'extraction de caractéristiques sur puce pour réduire le débit de données global à la plage possible.

La deuxième partie de la thèse se concentre sur le problème de l'incertitude temporelle dans les systèmes de communication à haut débit. L'augmentation des débits de données dans les émetteurs-récepteurs filaires et sans fil, ainsi que le besoin émergent d'architectures multi-émetteurs-récepteurs nécessitent l'énergie et la surface les plus basses possibles pour la synthèse de fréquences, ce qui contredit le paradigme actuel de compromis gigue versus coût. Pour permettre l'utilisation d'oscillateurs en anneau de faible surface pour les applications sensibles à la gigue sous des contraintes de faible puissance, nous introduisons une architecture de boucle à verrouillage de phase à rétroaction multiphase et implémentons un synthétiseur de fréquence à large bande.

Mots clés : Neurotechnologie implantable, enregistrement neuronal haute densité, circuit frontal analogique, couplage AC, amplificateur à faible bruit, convertisseur analogique-numérique, registre d'approximation successive, commutation monotone , condensateur de longueur unitaire, compression sur puce, transformée de Hadamard compressée, puissance sans fil et transfert de données, apprentissage automatique, détection de crise, entraînement conjoint, synthétiseur de fréquence, boucle à verrouillage de phase, bande passante de boucle, Limite de Gardner, rétroaction multiphase, oscillateur en anneau commandé en tension, détecteur de phase à matrice.

# Contents

| Ac | Acknowledgments                                                  |                                                          |    |  |  |

|----|------------------------------------------------------------------|----------------------------------------------------------|----|--|--|

| Ał | Abstract (English/Français) ii                                   |                                                          |    |  |  |

| Li | List of Figures xi<br>List of Tables xv<br>List of Acronyms xvii |                                                          |    |  |  |

| Li |                                                                  |                                                          |    |  |  |

| Li |                                                                  |                                                          |    |  |  |

| In | trod                                                             | ction                                                    | 1  |  |  |

| I  | Imj                                                              | antable Neurotechnology                                  | 3  |  |  |

| 1  | Neu                                                              | al Recording Implants: A Review                          | 5  |  |  |

|    | 1.1                                                              | Introduction                                             | 6  |  |  |

|    |                                                                  | 1.1.1 Probing the Electrical Activity of the Brain       | 6  |  |  |

|    |                                                                  | 1.1.2 Applications of Invasive Neural Recording          | 8  |  |  |

|    | 1.2                                                              | Analog Front-Ends for Sensing Neural Potentials          | 11 |  |  |

|    |                                                                  | 1.2.1 Specifications                                     | 12 |  |  |

|    |                                                                  | 1.2.2 Amplification                                      | 14 |  |  |

|    |                                                                  | 1.2.3 Digitization                                       | 16 |  |  |

|    | 1.3                                                              | Wireless Telemetry                                       | 17 |  |  |

|    |                                                                  | 1.3.1 Powering the Implant                               | 17 |  |  |

|    |                                                                  | 1.3.2 Communication                                      | 19 |  |  |

|    | 1.4                                                              | Data Rate Reduction Techniques                           | 21 |  |  |

|    |                                                                  | 1.4.1 On-Chip Compression                                | 21 |  |  |

|    |                                                                  | 1.4.2 On-Chip Classification                             | 26 |  |  |

|    | 1.5                                                              | Summary                                                  | 28 |  |  |

| 2  | An ]                                                             | nergy-Area Efficient Wideband Neural Recording Front-End | 29 |  |  |

|    | 2.1                                                              | ULC-Based Asynchronous SAR ADC                           | 30 |  |  |

|    |                                                                  | 2.1.1 Unit-Length Capacitor Array DAC (ULCDAC)           | 31 |  |  |

|    |                                                                  | 2.1.2 Track-and-Hold Switches                            | 33 |  |  |

|    |                                                                  | 2.1.3 Asynchronous Logic                                 | 36 |  |  |

### Contents

|    |                                                                              | 2.1.4 Dynamic Double-Tail Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37                                                                                                                                                                                                         |

|----|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 2.2                                                                          | Capacitively-Coupled Low-Noise Amplifier (CC-LNA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                                                                                         |

|    |                                                                              | 2.2.1 Gain Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                                                                         |

|    |                                                                              | 2.2.2 Operational Transconductance Amplifier (OTA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39                                                                                                                                                                                                         |

|    | 2.3                                                                          | Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                                                                                                                                                         |

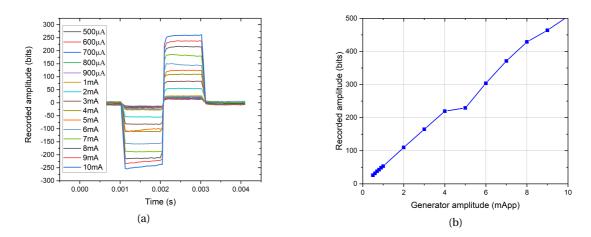

|    |                                                                              | 2.3.1 Bench Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                                                                                                                         |

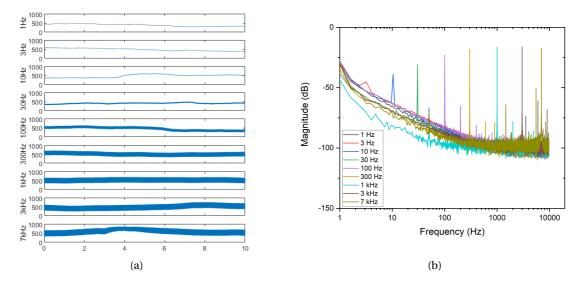

|    |                                                                              | 2.3.2 In Vitro Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                                                                                                         |

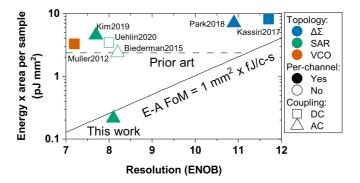

|    |                                                                              | 2.3.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                                                                                                                         |

| 3  | AW                                                                           | ireless Neural Recording SoC for Machine Learning Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                                                                                                         |

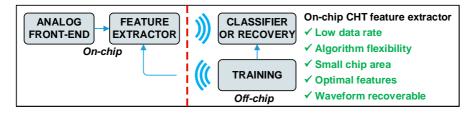

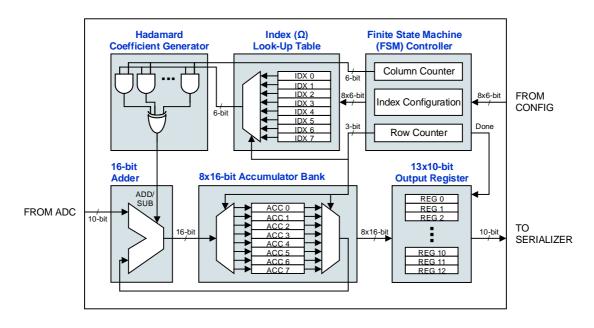

|    | 3.1                                                                          | On-Chip Feature Extractor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                                                                                                         |

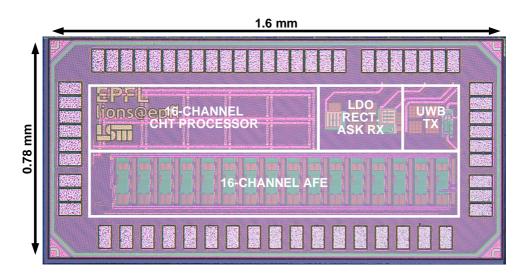

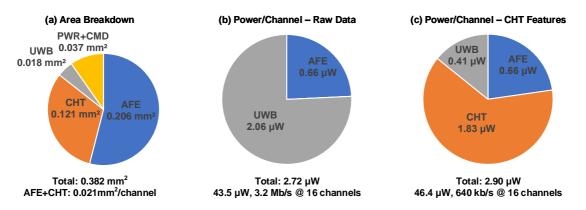

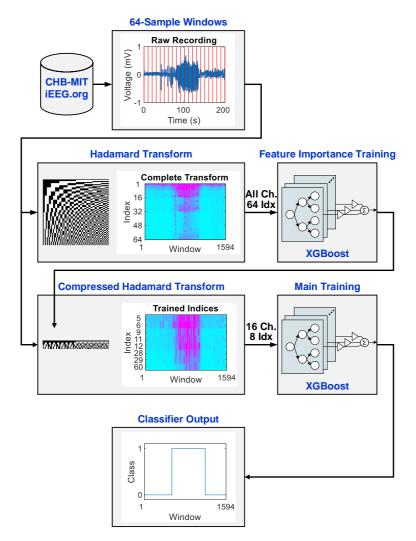

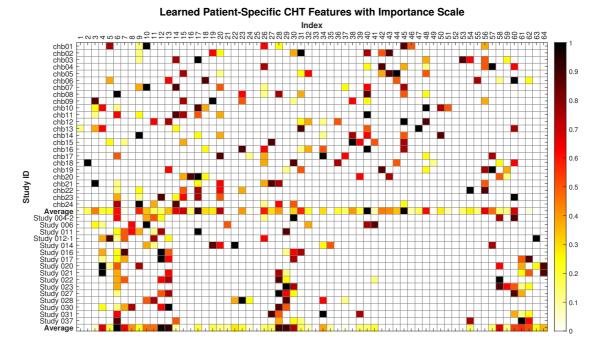

|    |                                                                              | 3.1.1 Compressed Hadamard Transform (CHT) Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |

|    | 3.2                                                                          | Wireless Power and Data Transfer (WPDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49                                                                                                                                                                                                         |

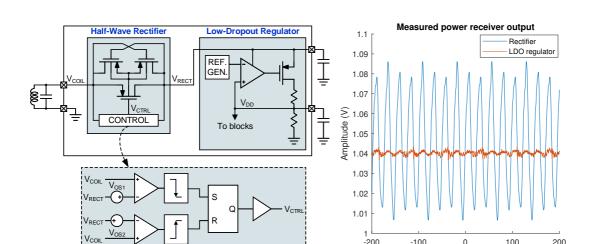

|    |                                                                              | 3.2.1 Half-Wave Rectifier and Low-Dropout (LDO) Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                                         |

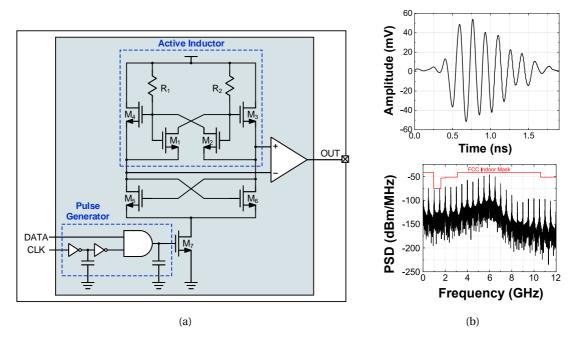

|    |                                                                              | 3.2.2 Impulse-Radio Ultra-Wideband (IR-UWB) Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                                                                                                                         |

|    | 3.3                                                                          | Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51                                                                                                                                                                                                         |

|    |                                                                              | 3.3.1 Offline Seizure Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                                                                                                                                                                         |

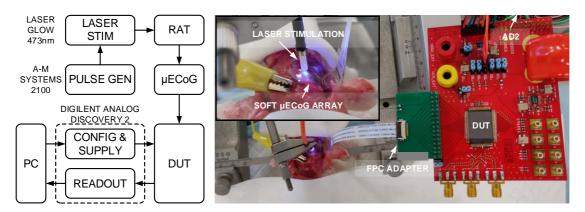

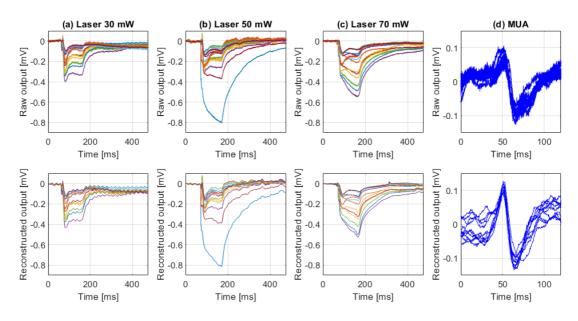

|    |                                                                              | 3.3.2 In Vivo Waveform Reconstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                                                                                                                         |

|    |                                                                              | 3.3.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58                                                                                                                                                                                                         |

| II | Hi                                                                           | gh-Speed Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59                                                                                                                                                                                                         |

|    |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                            |

| 4  | AW                                                                           | ideband Phase-Locked Loop Technique for Mitigating VCO Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                                         |

| 4  | <b>A W</b><br>4.1                                                            | ideband Phase-Locked Loop Technique for Mitigating VCO Noise Phase-Locked Loop Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>61</b><br>63                                                                                                                                                                                            |

| 4  |                                                                              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>61</b><br>63<br>63                                                                                                                                                                                      |

| 4  |                                                                              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators         4.1.2         Loop Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>61</b><br>63<br>63<br>64                                                                                                                                                                                |

| 4  |                                                                              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>61</b><br>63<br>63<br>64                                                                                                                                                                                |

| 4  | 4.1                                                                          | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators         4.1.2         Loop Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>61</b><br>63<br>63<br>64<br>65                                                                                                                                                                          |

| 4  | 4.1                                                                          | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators         4.1.2         Loop Bandwidth         Multiphase Feedback Phase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>61</b><br>63<br>63<br>64<br>65<br>66                                                                                                                                                                    |

| 4  | 4.1                                                                          | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1         Voltage-Controlled Oscillators         4.1.2         Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1         XOR Matrix Phase Detector                                                                                                                                                                                                                                                                                                                                                                                      | <b>61</b><br>63<br>63<br>64<br>65<br>66<br>66                                                                                                                                                              |

| 4  | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         25 GHz Integer-N Ring PLL with 0.92f <sub>REF</sub> Bandwidth                                                                                                                                                                                                                                                                    | <b>61</b><br>63<br>63<br>64<br>65<br>66<br>66                                                                                                                                                              |

|    | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         Architecture Details                                                                                                                                                                                                                                                                                                             | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> </ul>                                                                                     |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         5.1.1 Matrix Phase Detector and Loop Filter                                                                                                                                                                                                                                                                                      | <ul> <li>61</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> </ul>                                                                         |

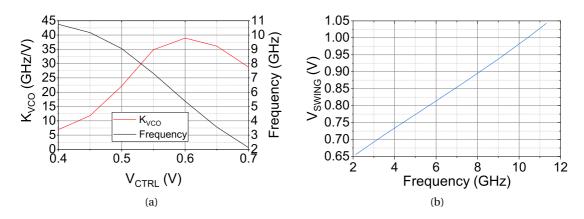

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         5.1.1 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator                                                                                                                                                                                                                                     | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>72</li> </ul>                                                 |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         5.1.1 Matrix Phase Detector and Loop Filter                                                                                                                                                                                                                                                                                      | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>72</li> </ul>                                                 |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         5.1.1 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator                                                                                                                                                                                                                                     | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> </ul>                                     |

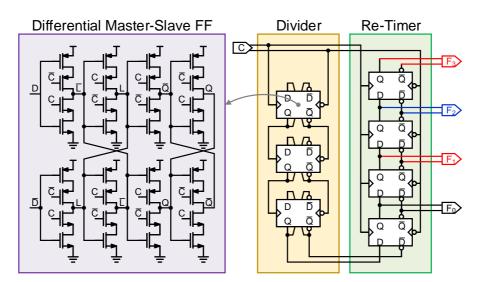

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         Summary         5.1.1 Matrix Phase Detector and Loop Filter         5.1.3 Feedback Divider                                                                                                                                                                                                                                                       | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> </ul>                         |

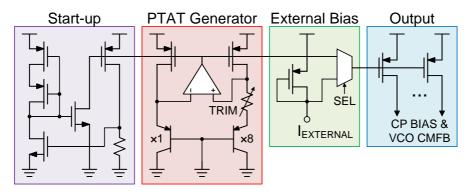

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         5.11 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator         5.1.4 Bandgap Reference                                                                                                                                                                                                                      | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> </ul>                         |

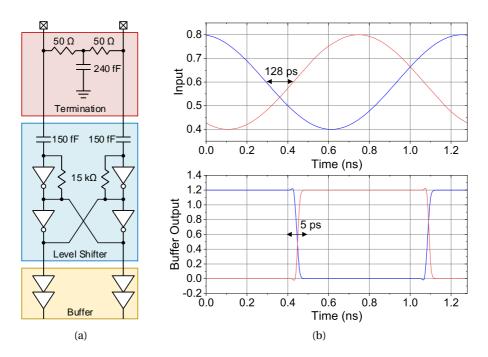

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> </ul>              | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         5.11 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator         5.1.3 Feedback Divider         5.1.4 Bandgap Reference         5.1.5 Input Buffer                                                                                                                                                            | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>75</li> </ul>             |

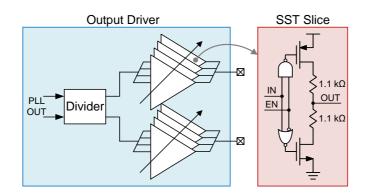

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> <li>5.1</li> </ul> | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         25 GHz Integer-N Ring PLL with 0.92f <sub>REF</sub> Bandwidth         Architecture Details         5.1.1 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator         5.1.3 Feedback Divider         5.1.4 Bandgap Reference         5.1.5 Input Buffer         5.1.6 Output Driver                            | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>75</li> <li>76</li> </ul> |

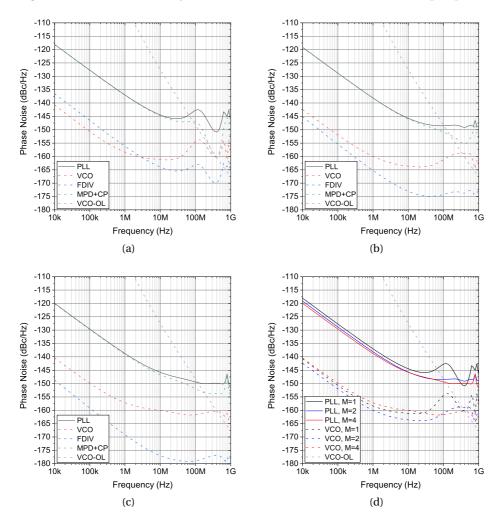

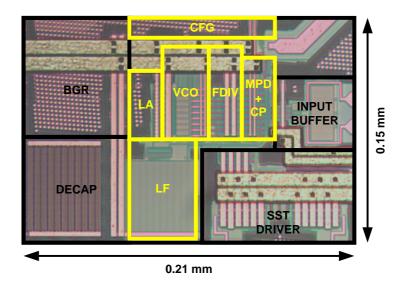

|    | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>A 6.</li> <li>5.1</li> </ul> | ideband Phase-Locked Loop Technique for Mitigating VCO Noise         Phase-Locked Loop Considerations         4.1.1 Voltage-Controlled Oscillators         4.1.2 Loop Bandwidth         Multiphase Feedback Phase-Locked Loop         4.2.1 XOR Matrix Phase Detector         4.2.2 Behavioral Simulation         Summary         25 GHz Integer-N Ring PLL with 0.92f <sub>REF</sub> Bandwidth         Architecture Details         5.1.1 Matrix Phase Detector and Loop Filter         5.1.2 Voltage-Controlled Ring Oscillator         5.1.3 Feedback Divider         5.1.4 Bandgap Reference         5.1.5 Input Buffer         5.1.6 Output Driver         Simulation Results | <ul> <li>61</li> <li>63</li> <li>63</li> <li>64</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>76</li> </ul> |

### Contents

107

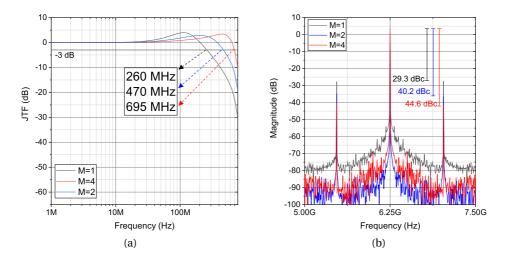

| 5.3.1        | Bandwidth Measurements   | 77  |

|--------------|--------------------------|-----|

| 5.3.2        | Phase Noise Measurements | 80  |

| 5.3.3        | Discussion               | 81  |

| Conclusion   |                          | 83  |

| Part I: Imp  | lantable Neurotechnology | 83  |

| Summ         | nary                     | 83  |

| Futur        | e Work                   | 84  |

| Part II: Hig | h-Speed Communications   | 85  |

| Sumn         | nary                     | 85  |

| Futur        | e Work                   | 85  |

| Bibliography |                          | 105 |

**Curriculum Vitae**

# List of Figures

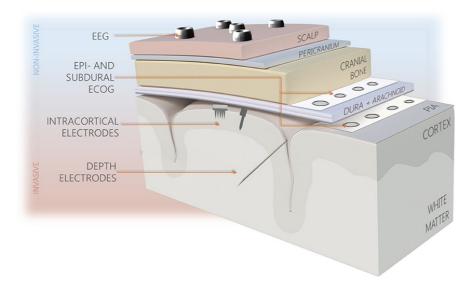

| 1.1                                                                                                                   | Types of neural probes for sensing electrical activity.                                                                                                                                                                                                                                                                                                                      | 7                                           |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

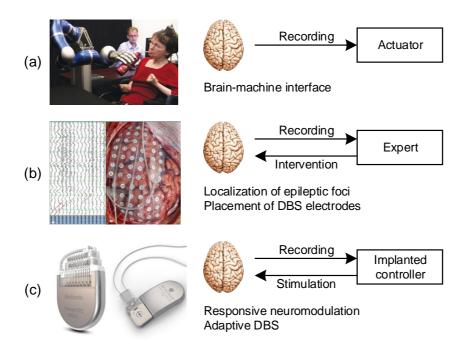

| 1.2                                                                                                                   | Application examples for invasive neural recording.                                                                                                                                                                                                                                                                                                                          | 8                                           |

| 1.3                                                                                                                   | A generic analog front-end.                                                                                                                                                                                                                                                                                                                                                  | 11                                          |

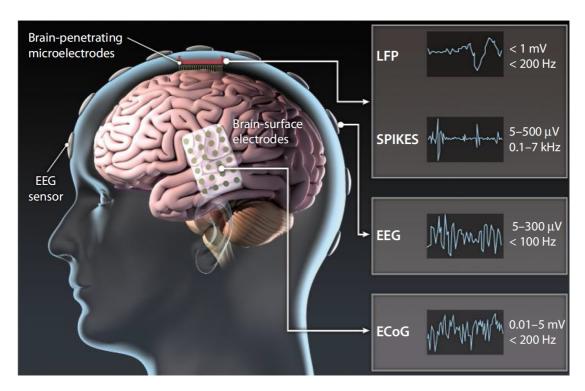

| 1.4                                                                                                                   | Bandwidth and amplitude of different types of neural signals                                                                                                                                                                                                                                                                                                                 | 12                                          |

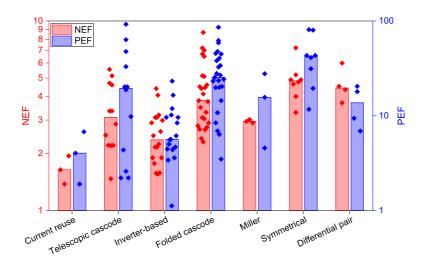

| 1.5                                                                                                                   | Comparison of published NEF and PEF values for various amplifier topologies.                                                                                                                                                                                                                                                                                                 | 15                                          |

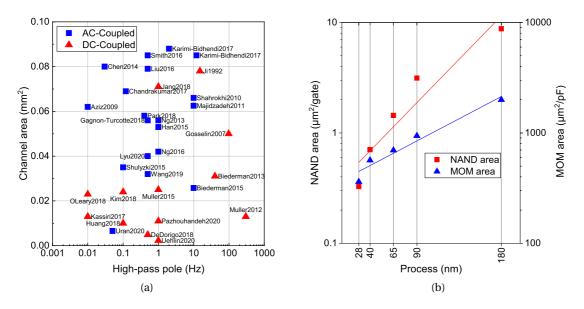

| 1.6                                                                                                                   | (a) Area and high-pass pole location trade-off. (b) Rate of progress for NAND                                                                                                                                                                                                                                                                                                |                                             |

|                                                                                                                       | gate and metal-oxide-metal (MOM) capacitor area efficiencies                                                                                                                                                                                                                                                                                                                 | 16                                          |

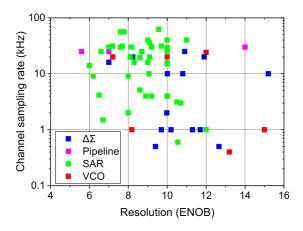

| 1.7                                                                                                                   | Sampling rate and resolution choices in the literature.                                                                                                                                                                                                                                                                                                                      | 18                                          |

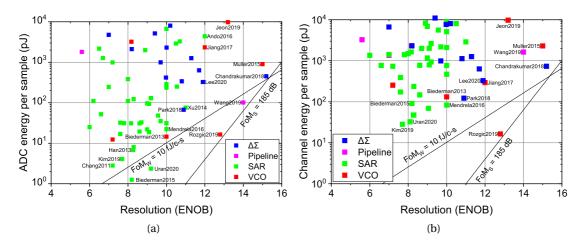

| 1.8                                                                                                                   | Energy efficiencies of published (a) ADCs and (b) AFEs.                                                                                                                                                                                                                                                                                                                      | 18                                          |

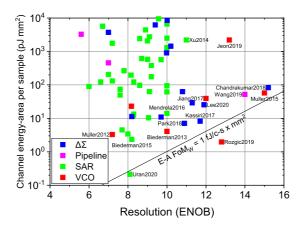

| 1.9                                                                                                                   | Energy-area efficiencies of published AFEs                                                                                                                                                                                                                                                                                                                                   | 18                                          |

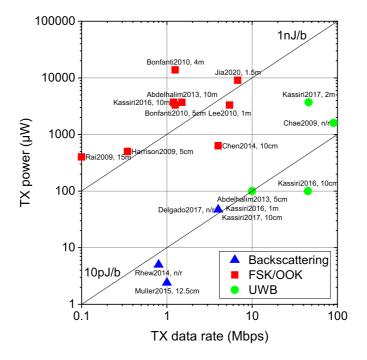

| 1.10                                                                                                                  | Comparison of data rate and transmitter power for various strategies                                                                                                                                                                                                                                                                                                         | 20                                          |

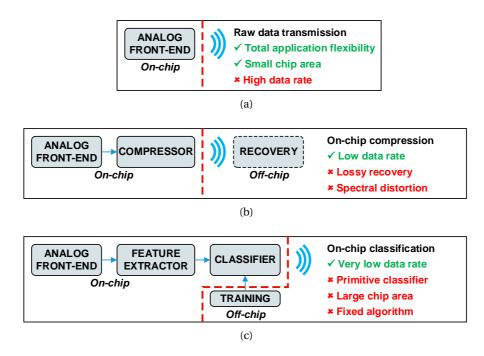

| 1.11                                                                                                                  | Advantages and disadvantages of data rate reduction techniques.                                                                                                                                                                                                                                                                                                              | 21                                          |

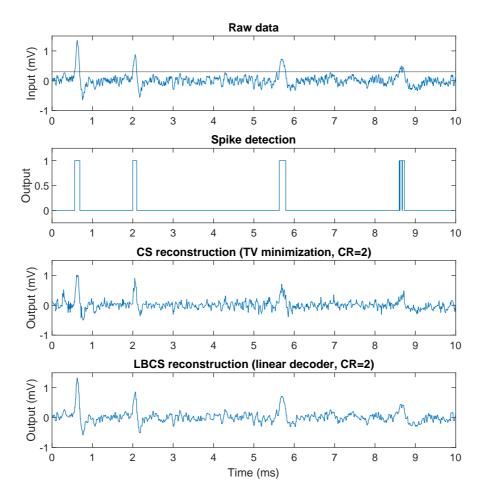

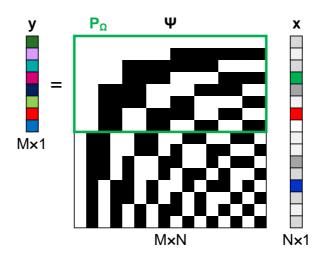

| 1.12                                                                                                                  | Three on-chip compression approaches: spike detection, CS, and LBCS                                                                                                                                                                                                                                                                                                          | 22                                          |

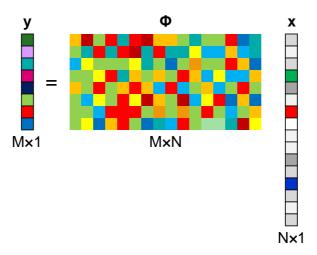

| 1.13                                                                                                                  | Illustration of a generic CS measurement.                                                                                                                                                                                                                                                                                                                                    | 24                                          |

| 1.14                                                                                                                  | Illustration of the LBCS concept with a subsampled Hadamard measurement                                                                                                                                                                                                                                                                                                      |                                             |

|                                                                                                                       | matrix                                                                                                                                                                                                                                                                                                                                                                       | 25                                          |

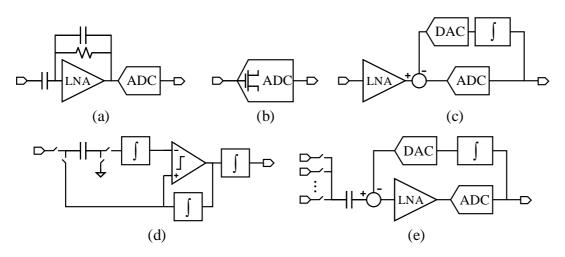

| 2.1                                                                                                                   | AC and DC-coupled front-end architectures                                                                                                                                                                                                                                                                                                                                    | 30                                          |

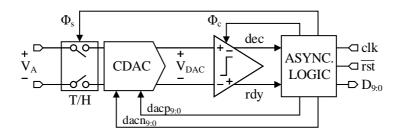

| 2.2                                                                                                                   | Top level schematic of the SAR ADC highlighting the main components.                                                                                                                                                                                                                                                                                                         | 30                                          |

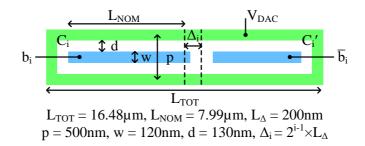

| 2.3                                                                                                                   | Layout of a unit-length capacitor and the dimensions used in this work                                                                                                                                                                                                                                                                                                       | 31                                          |

| 2.4                                                                                                                   | (a) Conventional switching scheme (b) Monotonic switching scheme                                                                                                                                                                                                                                                                                                             |                                             |

| 2.4                                                                                                                   | (a) Conventional switching scheme. (b) Monotonic switching scheme                                                                                                                                                                                                                                                                                                            | 32                                          |

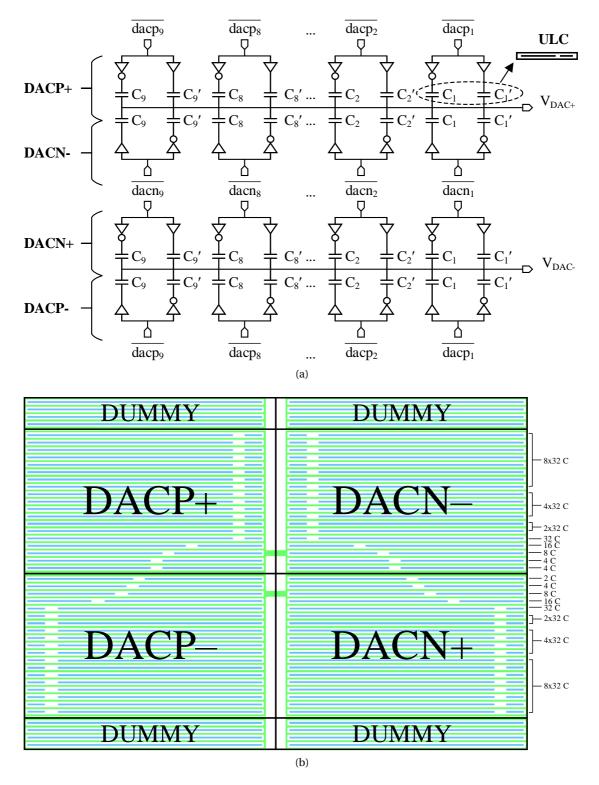

| 2.4<br>2.5                                                                                                            | (a) Schematic and (b) layout of the constant common-mode ULCDAC                                                                                                                                                                                                                                                                                                              | 32<br>34                                    |

|                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| 2.5                                                                                                                   | (a) Schematic and (b) layout of the constant common-mode ULCDAC                                                                                                                                                                                                                                                                                                              | 34                                          |

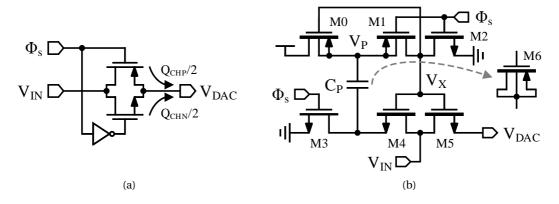

| 2.5<br>2.6                                                                                                            | <ul><li>(a) Schematic and (b) layout of the constant common-mode ULCDAC</li><li>(a) CMOS sampling switch and (b) the bootstrapped switch used in this work</li></ul>                                                                                                                                                                                                         | 34                                          |

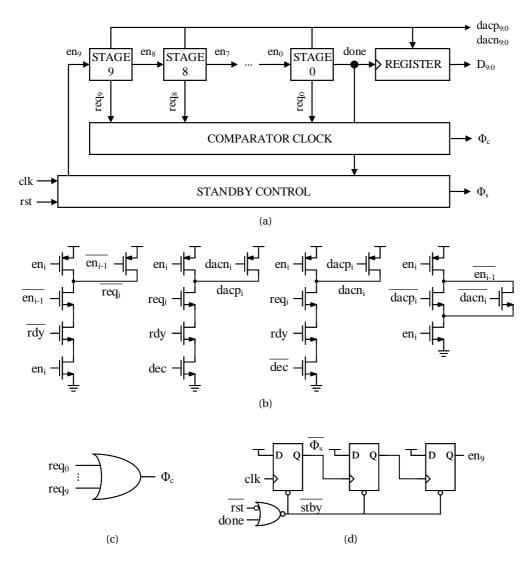

| 2.5<br>2.6                                                                                                            | <ul> <li>(a) Schematic and (b) layout of the constant common-mode ULCDAC</li> <li>(a) CMOS sampling switch and (b) the bootstrapped switch used in this work</li> <li>(a) Asynchronous logic block and its main components: (b) standby controller,</li> </ul>                                                                                                               | 34<br>35                                    |

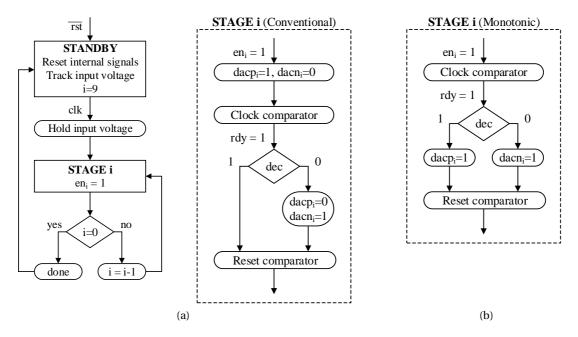

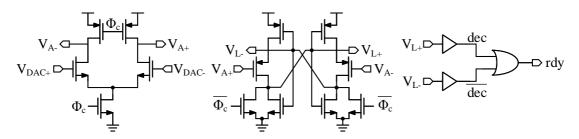

| 2.5<br>2.6<br>2.7                                                                                                     | <ul> <li>(a) Schematic and (b) layout of the constant common-mode ULCDAC</li> <li>(a) CMOS sampling switch and (b) the bootstrapped switch used in this work</li> <li>(a) Asynchronous logic block and its main components: (b) standby controller,</li> <li>(c) comparator clock generator, and (d) unit conversion stage</li> </ul>                                        | 34<br>35<br>36<br>37                        |

| <ol> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol>                                                        | <ul> <li>(a) Schematic and (b) layout of the constant common-mode ULCDAC</li> <li>(a) CMOS sampling switch and (b) the bootstrapped switch used in this work</li> <li>(a) Asynchronous logic block and its main components: (b) standby controller,</li> <li>(c) comparator clock generator, and (d) unit conversion stage</li> <li>Dynamic double-tail comparator</li></ul> | 34<br>35<br>36<br>37                        |

| <ol> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ol>                                           | (a) Schematic and (b) layout of the constant common-mode ULCDAC (a) CMOS sampling switch and (b) the bootstrapped switch used in this work (a) Asynchronous logic block and its main components: (b) standby controller, (c) comparator clock generator, and (d) unit conversion stage Dynamic double-tail comparator                                                        | 34<br>35<br>36<br>37<br>7-                  |

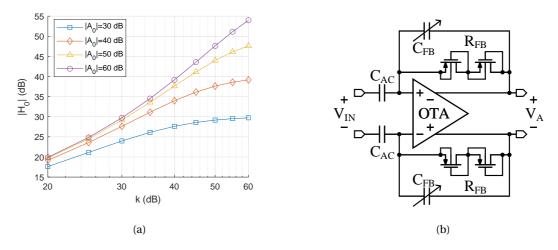

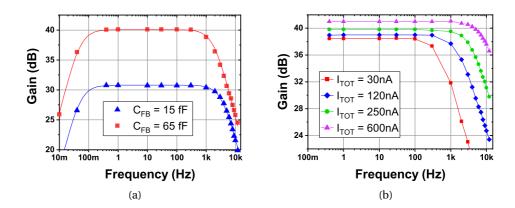

| <ol> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> <li>2.10</li> </ol>                             | (a) Schematic and (b) layout of the constant common-mode ULCDAC (a) CMOS sampling switch and (b) the bootstrapped switch used in this work (a) Asynchronous logic block and its main components: (b) standby controller, (c) comparator clock generator, and (d) unit conversion stage Dynamic double-tail comparator                                                        | 34<br>35<br>36<br>37<br>7-<br>38            |

| <ol> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> <li>2.10</li> <li>2.11</li> </ol>               | (a) Schematic and (b) layout of the constant common-mode ULCDAC (a) CMOS sampling switch and (b) the bootstrapped switch used in this work (a) Asynchronous logic block and its main components: (b) standby controller, (c) comparator clock generator, and (d) unit conversion stage Dynamic double-tail comparator                                                        | 34<br>35<br>36<br>37<br>7-<br>38            |

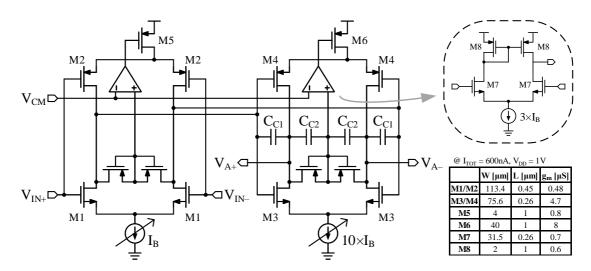

| <ul> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> <li>2.10</li> <li>2.11</li> <li>2.12</li> </ul> | (a) Schematic and (b) layout of the constant common-mode ULCDAC (a) CMOS sampling switch and (b) the bootstrapped switch used in this work (a) Asynchronous logic block and its main components: (b) standby controller, (c) comparator clock generator, and (d) unit conversion stage Dynamic double-tail comparator                                                        | 34<br>35<br>36<br>37<br>-<br>38<br>39       |

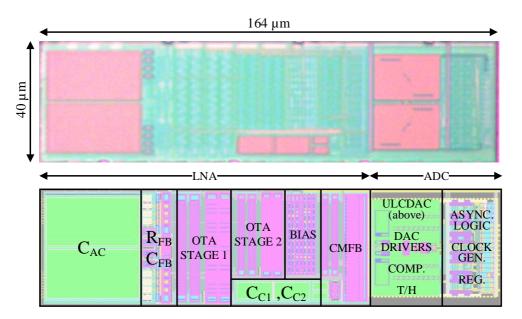

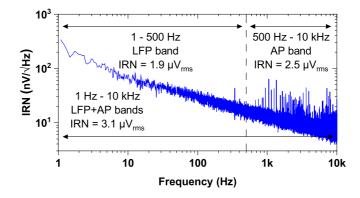

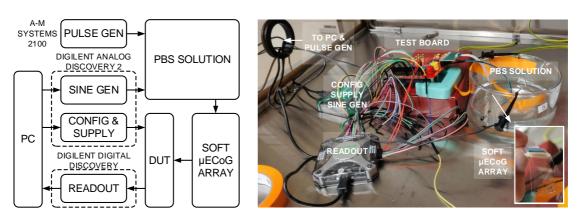

| <ul> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> <li>2.10</li> <li>2.11</li> <li>2.12</li> </ul> | (a) Schematic and (b) layout of the constant common-mode ULCDAC (a) CMOS sampling switch and (b) the bootstrapped switch used in this work (a) Asynchronous logic block and its main components: (b) standby controller, (c) comparator clock generator, and (d) unit conversion stage Dynamic double-tail comparator                                                        | 34<br>35<br>36<br>37<br>-<br>38<br>39<br>40 |

### List of Figures

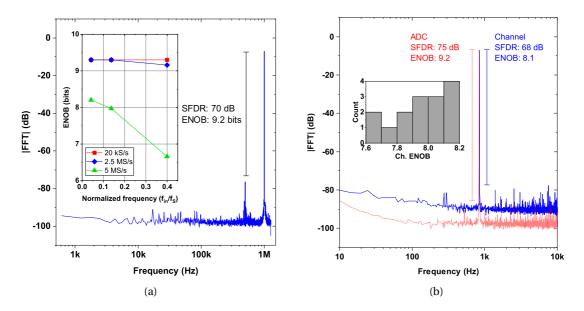

| 2.14 | Measured output frequency spectrum of (a) the standalone ADC and (b) the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

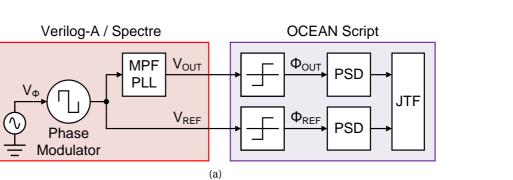

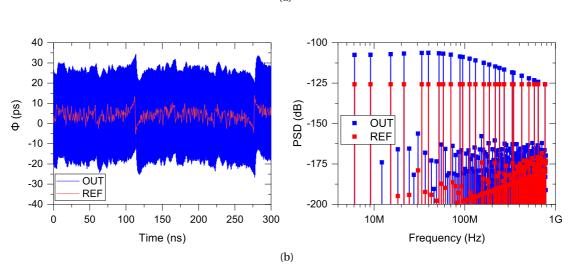

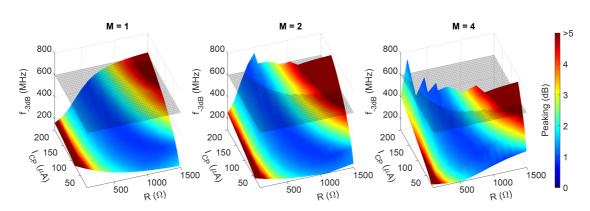

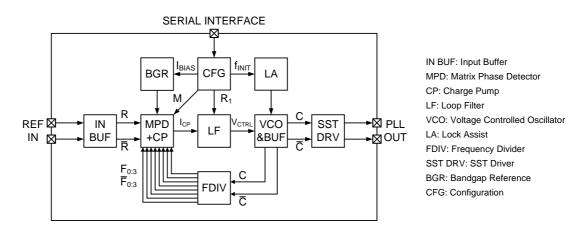

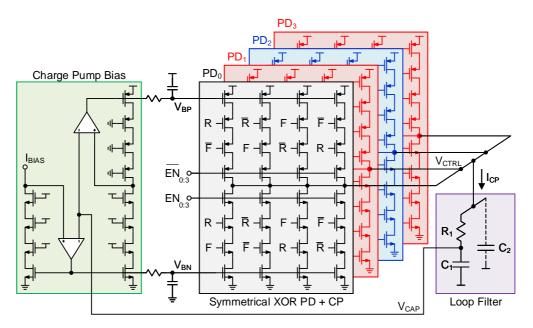

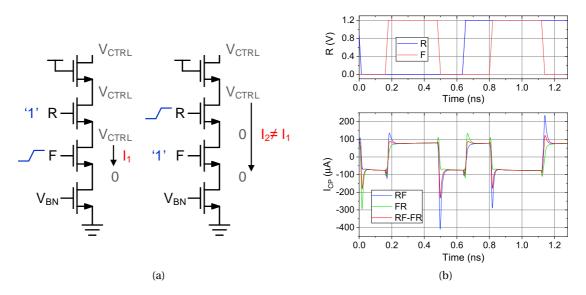

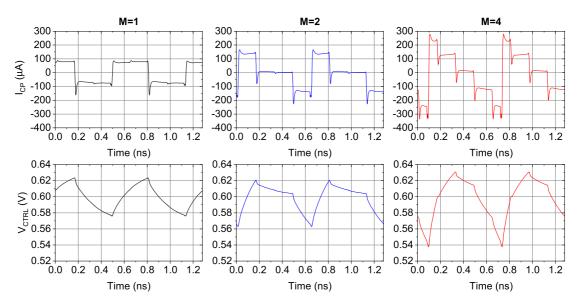

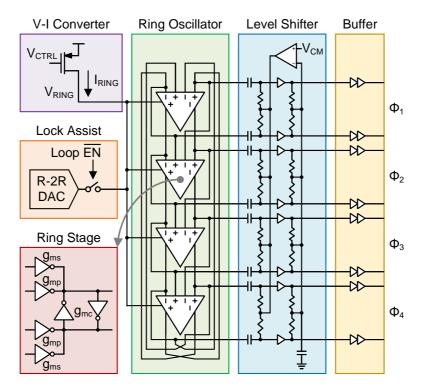

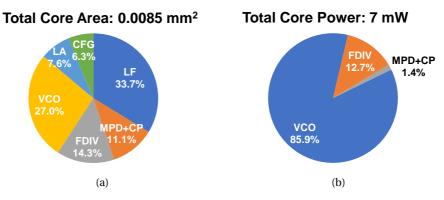

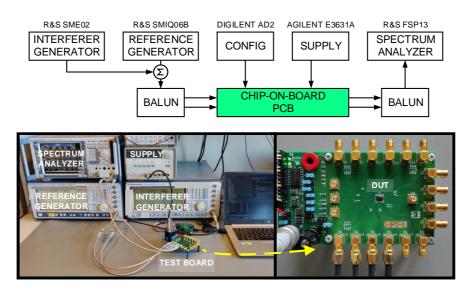

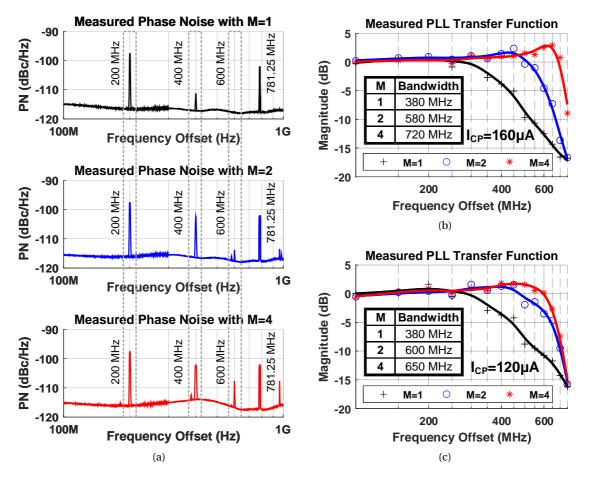

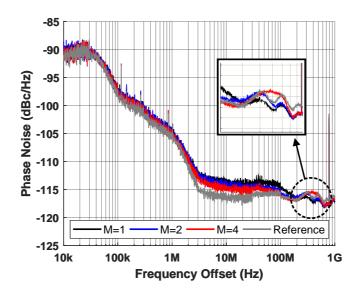

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|