# EPFL

Thèse n° 8050

## Miss-Optimized Memory Systems: Turning Thousands of Outstanding Misses into Reuse Opportunities

Présentée le 3 septembre 2021

Faculté informatique et communications Laboratoire d'architecture des processeurs Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Mikhail ASIATICI

Acceptée sur proposition du jury

Prof. E. Bugnion, président du jury Prof. P. lenne, directeur de thèse Dr K. Vissers, rapporteur Prof. V. Prasanna, rapporteur Prof. G. Alonso, rapporteur

École polytechnique fédérale de Lausanne

2021

Questions you cannot answer are usually far better for you than answers you cannot question. — Yuval Noah Harari

To Maya, Mamiko, and my parents.

### Abstract

Even if Dennard scaling came to an end fifteen years ago, Moore's law kept fueling an exponential growth in compute performance through increased parallelization. However, the performance of memory and, in particular, *Dynamic Random Access Memory* (DRAM), has been increasing at a slower pace for decades, making memory system optimization increasingly crucial. Conventional solutions mitigate the issue by shifting as many memory accesses as possible from off-chip DRAM to on-chip *Static RAM* (SRAM) memory, which has higher performance but lower capacity. This is achieved by relying on spatial and temporal locality or on precise compile-time information about the access pattern. However, when the access pattern is irregular and data-dependent, these solutions are ineffective and the processing-memory gap grows even wider as DRAMs themselves are optimized for sequential accesses.

In this thesis, we present a novel memory system for throughput-oriented compute engines that perform irregular read accesses to DRAM. When accesses are irregular, we acknowledge that obtaining a reasonable benefit from on-chip memory may be unrealistic; therefore, we focus on minimizing stalls and reusing each memory response to serve as many misses as possible without relying on long-term data storage. This is the same insight behind nonblocking caches but on a vastly larger scale in terms of outstanding misses, which greatly increases the opportunities for data reuse when accelerators emit a large number of outstanding reads. Because we optimize miss handling rather than increasing hit rate, we call our architecture *miss-optimized memory system* (MOMS).

We first focus on the microarchitectural level to show how a MOMS can support three orders of magnitude more outstanding misses than a traditional nonblocking cache in a way that can be efficiently implemented on *Field-Programmable Gate Arrays* (FPGAs). Once we maximize the reuse of each individual word returned by the DRAM, we introduce two techniques to increase the DRAM throughput. When the DRAM controller is optimized for burst requests, we group incoming requests over multiple words that are requested as a burst. Conversely, when the DRAM controller handles single requests efficiently, our MOMS reorders requests by DRAM bank and row on a much larger scale than general-purpose DRAM controllers. We then discuss techniques to use efficiently the vast amount of resources provided by multi-die FPGAs and introduce two-level architectures which balance reuse maximization and contention of shared hardware. Finally, we develop a graph processing accelerator backed by a MOMS. On three algorithms on graphs with billions of edges and up to a hundred million nodes, our accelerator outperforms the state-of-the-art on CPUs and GPUs.

Memory systems designers face increasing pressure to keep up with the compute engines performance. Our results suggest that miss-optimized memory systems can help to reduce the memory-processing gap where it is largest, that is, when accesses to memory are irregular and difficult to serve from local buffers.

*Keywords:* DRAMs, nonblocking caches, MSHRs, bandwidth-bound, throughput-oriented, FPGAs

### Sunto

Nonostante lo scaling di Dennard sia terminato quindici anni fa, la legge di Moore ha continuato ad alimentare una crescita esponenziale delle prestazioni di calcolo attraverso una maggiore parallelizzazione. Tuttavia, le prestazioni delle Dynamic Random Access Memories (DRAM) è aumentata ad un ritmo più lento per decenni, rendendo l'ottimizzazione del sistema di memoria sempre più cruciale. Le soluzioni convenzionali come le cache e gli scratchpad mitigano il problema spostando il maggior numero possibile di accessi dalla DRAM esterna alla memoria RAM statica (SRAM) interna, che ha prestazioni più elevate ma una capacità inferiore. Ciò fa affidamento sulla località spaziale e temporale o su precise informazioni a tempo di compilazione sulla sequenza di accessi in memoria. Tuttavia, quando tale sequenza è irregolare, queste soluzioni si rivelano inefficaci e il divario elaborazione-memoria cresce ancora di più poiché le DRAM stesse sono ottimizzate per gli accessi sequenziali.

In questa tesi, si presenta un nuovo sistema di memoria per acceleratori orientati al throughput che eseguono accessi irregolari alla DRAM. Quando gli accessi sono irregolari, riconosciamo che ottenere un beneficio ragionevole tramite buffering locale può essere irrealistico; ci si concentra pertanto sulla minimizzazione degli stalli e sul riutilizzo di ogni risposta di memoria per servire il maggior numero possibile di miss senza fare affidamento sullo stoccaggio di dati a lungo termine. Questa è la stessa intuizione alla base delle cache non bloccanti, ma su una scala molto più grande in termini di miss in sospeso, il che aumenta notevolmente le opportunità di riutilizzo dei dati quando gli acceleratori emettono un gran numero di letture in sospeso. Poiché si ottimizza la gestione delle miss piuttosto che aumentare i cache hits, chiamiamo la nostra architettura *sistema di memoria ottimizzato per le miss (miss-optimized memory system,* MOMS).

Nella prima parte della tesi si mostra ciò che, a livello microarchitetturale, permette ad un MOMS di gestire tre ordini di grandezza in più di miss in sospeso rispetto a una cache non bloccante tradizionale in una maniera che può essere implementata efficientemente su *Field-Programmable Gate Arrays* (FPGAs). Si introducono quindi due tecniche per aumentare il throughput della DRAM, utilizzando richieste *burst* o riordinando richieste singole su una scala molto più grande rispetto ai controller DRAM *general-purpose*. In seguito, si introducono delle linee guida per utilizzare in modo efficiente le FPGA multi-die e si presentano architetture a due livelli che bilanciano la massimizzazione del riutilizzo dei dati ricevuti dalla DRAM e i conflitti di accesso all'hardware condiviso. Si discute infine un acceleratore per elaborazione dei grafi supportato da un MOMS e si dimostra che raggiunge prestazioni superiori rispetto allo stato dell'arte su FPGA ed ha una maggiore efficienza per watt e per unità di banda passante rispetto

allo stato dell'arte su CPU e GPU nell'esecuzione di tre algoritmi su grafi con miliardi di archi e fino a un centinaio di milioni di nodi.

I progettisti di sistemi di memoria devono affrontare una crescente pressione per tenere il passo con le prestazioni dei motori di calcolo. I risultati esposti in questa tesi suggeriscono che i MOMS possono aiutare a ridurre il divario memoria-elaborazione dove è più grande, ovvero quando gli accessi alla memoria sono irregolari e difficili da soddisfare localmente.

*Parole chiave:* DRAMs, cache non bloccanti, MSHRs, bandwidth-bound, throughput-oriented, FPGAs

### Acknowledgements

I am deeply grateful to all the people that made this long journey possible and enjoyable. I sincerely thank my supervisor, Paolo Ienne, for entrusting me with a great deal of freedom and at the same time providing continuous guidance, support, and encouragement. I learned a lot from him at the technical, personal, and research level and I feel particularly lucky for having had the chance to work with him. I would also like to thank the members of my thesis committee, Gustavo Alonso, Edouard Bugnion, Viktor Prasanna, and Kees Vissers for finding the time to review my work and for their valuable feedback.

I had the privilege to work with many great minds who helped me shaping my research direction. I am very much obliged to Kristof Denolf, Kees Vissers, and Stephen Neuendorffer for exposing me to interesting open industrial problems, including the application that inspired my research, and for their feedback along the way. I am also grateful to Michael Adler for the insightful discussions about memory-related challenges on FPGAs, and to David Novo, Gabriel Falcao, and Dick Sites for their comments on my research.

During my PhD, I had the chance to do an internship at Microsoft Research in Cambridge, UK, within Project Honeycomb. I would like to thank Junyi Liu and Aleksandar Dragojevic for giving me the opportunity to explore the world of industrial research and for their valuable guidance. I am very thankful to all of my colleagues at LAP—Ana, André, Andrea, Andrew, Aya, Chantal, Grace, Lana, Nithin, Paolo, René, Sahand, Stefan—for the coffees, lunches, beers, outings, table football games, and the countless other good times we had together. I am particularly grateful to Andrea, Lana, Sahand, and my office mate Stefan for their friendship and support throughout many years at LAP, to Nithin, for introducing me to FPGAs and for his precious guidance, and to Chantal, for always being there to help with any problem, no matter what kind or how big. I would also like to thank Joao and Gabriel, whose short visits were enough to leave many good memories together.

I had great pleasure in working with many excellent interns, including Amna, Andrew, Aya, Kushagra, Sena, Patryk, and my coauthors Damian and Gabor whose work had a significant impact on my research.

A big thank you also to Raffaele, with whom I shared struggles and success since we first set foot in a university back in Italy, all the way to EPFL, as well as Michele and Giuseppe.

Finally, none of this would have been possible without the support and love from my family, to whom I express my deepest gratitude. I am forever indebted to my parents Andrea and Graziella for their unconditional and endless support and for making me the person I am today. I am eternally grateful to my wife Mamiko, for always encouraging me to push beyond my limits

#### Acknowledgements

and having believed in me even when I did not. Her support made it possible to overcome the darkest moments and made the happiest news even more memorable. Last but not least, I am forever grateful to my daughter Maya, who came into my life halfway through this journey, the day after a paper submission deadline, for turning my world upside down and making me more fulfilled that I could have ever imagined.

Lausanne, May 25, 2021

M. A.

## Contents

| Ał | ostra   | ct (English)                                   | i   |

|----|---------|------------------------------------------------|-----|

| Ał | ostra   | ct (Italiano)                                  | iii |

| Ac | knov    | wledgements                                    | v   |

| Li | st of [ | Figures                                        | xi  |

| Li | st of ' | Tables                                         | xv  |

| 1  | Intr    | oduction                                       | 1   |

|    | 1.1     | Memory-Computation Gap                         | 1   |

|    | 1.2     | Limitations of Existing Solutions              | 2   |

|    | 1.3     | Opportunities for Data Reuse                   | 5   |

|    | 1.4     | Pushing Nonblocking Caches to the Extreme      | 6   |

|    | 1.5     | Storing Requests Instead of Data               | 7   |

|    | 1.6     | Thesis Outline                                 | 7   |

| 2  | Bac     | kground and Related Work                       | 9   |

|    | 2.1     | FPGA On-Chip Memory                            | 9   |

|    | 2.2     | Nonblocking Caches                             | 10  |

|    | 2.3     | DRAM Structure and Operation                   | 11  |

|    | 2.4     | Reordering Memory Controllers                  | 14  |

|    | 2.5     | Graph Processing                               | 15  |

|    | 2.6     | Experimental Setup                             | 17  |

|    |         | 2.6.1 SpMV Accelerators                        | 17  |

|    |         | 2.6.2 FPGA Boards and Memories Specifications  | 18  |

|    |         | 2.6.3 Top-Level System Organization            | 20  |

|    |         | 2.6.4 Platform Characterization                | 21  |

| 3  | Fro     | m Tens to Tens of Thousands Outstanding Misses | 27  |

|    | 3.1     | Key Ideas                                      | 27  |

|    |         | 3.1.1 Scalable MSHR Lookup and Storage         | 27  |

|    |         | 3.1.2 Flexible Subentry Storage                | 29  |

|    | 3.2     | Detailed Architecture                          | 29  |

|   |      | 3.2.1   | MSHR Buffer                                                            | 30 |

|---|------|---------|------------------------------------------------------------------------|----|

|   |      | 3.2.2   | Subentry Buffer                                                        | 31 |

|   |      | 3.2.3   | Data Buffer                                                            | 32 |

|   |      | 3.2.4   | Pipeline Efficiency and Throughput                                     | 33 |

|   | 3.3  | Exper   | imental Results                                                        | 34 |

|   |      | 3.3.1   | More Cache or More MSHRs?                                              | 34 |

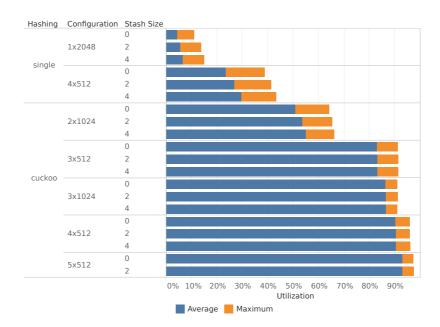

|   |      | 3.3.2   | Number of MSHR Hash Tables and Stash Size                              | 35 |

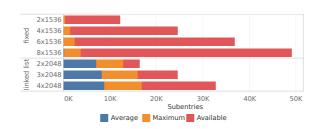

|   |      | 3.3.3   | Subentry Organization                                                  | 36 |

|   |      | 3.3.4   | Number of Outstanding Memory Requests                                  | 38 |

|   |      | 3.3.5   | Resource Utilization                                                   | 39 |

|   | 3.4  | Concl   | lusion                                                                 | 40 |

| 4 | Inci | reasing | Available Bandwidth by Using Bursts                                    | 41 |

|   | 4.1  | Key Ic  | leas                                                                   | 42 |

|   |      | 4.1.1   | Generalizing MSHRs from Single Cache Lines to Variable-Length Memory   |    |

|   |      |         | Areas                                                                  | 42 |

|   |      | 4.1.2   | Dynamically Adjusting Burst Bounds                                     | 43 |

|   |      |         | Minimizing Burst Invalidations                                         | 45 |

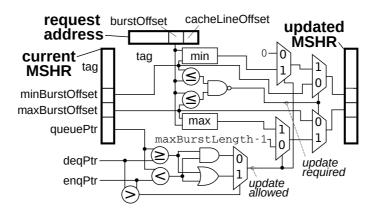

|   | 4.2  | System  | m Architecture                                                         | 46 |

|   | 4.3  | Evalu   | ation                                                                  | 48 |

|   |      | 4.3.1   | Benefits of Dynamically Adjusting the Burst Length and Impact of Maxi- |    |

|   |      |         | mum Burst Length                                                       | 49 |

|   |      | 4.3.2   | Architectural Exploration                                              | 49 |

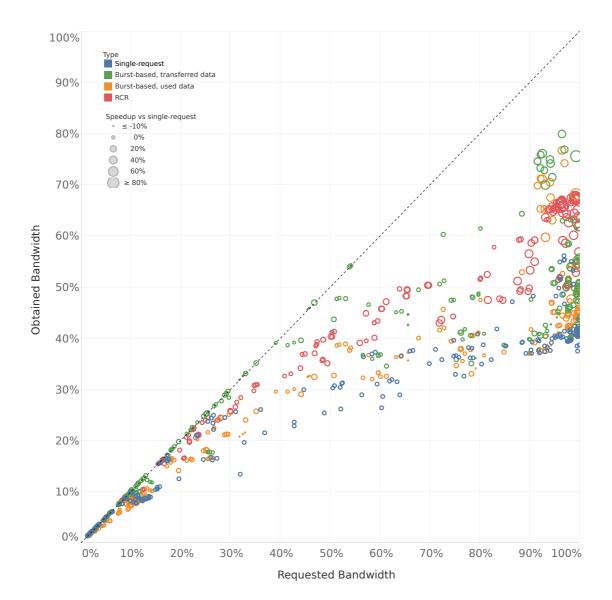

|   |      | 4.3.3   | Detailed Speedup Profile                                               | 51 |

|   |      | 4.3.4   | Analysis of Burst Usage                                                | 52 |

|   |      | 4.3.5   | Resource Utilization                                                   | 53 |

|   | 4.4  | Concl   | lusion                                                                 | 55 |

| 5 | Inci | -       | Available Bandwidth by Large-Scale Request Reordering                  | 57 |

|   | 5.1  | •       | lea: Where and How to Reorder?                                         | 58 |

|   | 5.2  | Row (   | Conflict Reducer                                                       | 59 |

|   |      | 5.2.1   | Row Address Buffer and Deallocation Queue                              |    |

|   |      | 5.2.2   | Column Address Buffer                                                  |    |

|   |      | 5.2.3   | Output Buffer and Address Generator                                    | 62 |

|   | 5.3  | Evalu   | ation                                                                  | 62 |

|   |      | 5.3.1   | Global Speedup and Impact of RCR Size                                  | 63 |

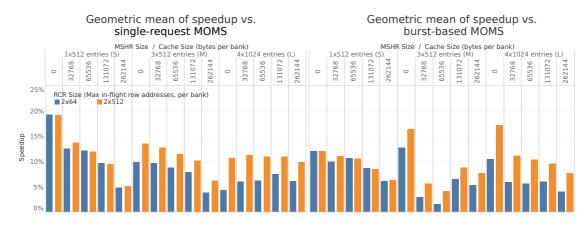

|   |      | 5.3.2   | Memory Bandwidth Utilization                                           |    |

|   |      | 5.3.3   | Speedup on Individual Benchmarks                                       |    |

|   |      | 5.3.4   | Resource Utilization                                                   | 67 |

|   | 5.4  | Concl   | lusion                                                                 | 68 |

| 6  | Goi                  | ng Large: Multi-Die and Multi-Level Architectures 6                           | <b>69</b>  |

|----|----------------------|-------------------------------------------------------------------------------|------------|

|    | 6.1                  | Spanning Over Multiple Dies Without Sacrificing Performance                   | <b>6</b> 9 |

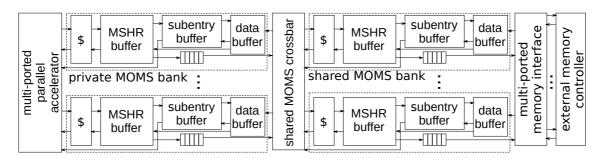

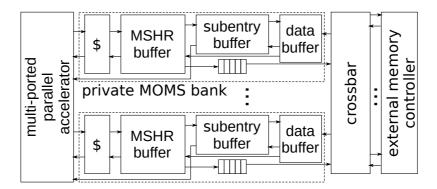

|    | 6.2                  | Private and Two-Level MOMSes                                                  | 72         |

|    | 6.3                  | Evaluation                                                                    | 74         |

|    |                      | 6.3.1 Architecture Exploration                                                | 74         |

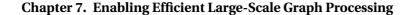

|    |                      | 6.3.2 Impact of Caches                                                        | 78         |

|    |                      | 6.3.3 Contention on the Shared MOMS 7                                         | 78         |

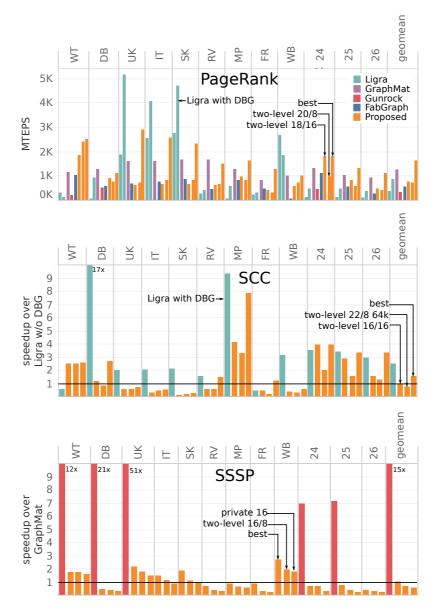

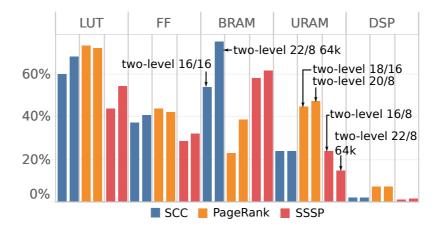

|    |                      | 6.3.4 Resource Utilization and Operating Frequency                            | 31         |

|    | 6.4                  | Conclusion                                                                    | 32         |

| 7  | Ena                  | bling Efficient Large-Scale Graph Processing &                                | 35         |

|    | 7.1                  | Limitations of the State-of-the-Art                                           | 35         |

|    | 7.2                  | Key Ideas                                                                     | 37         |

|    | 7.3                  | Graph Processing Model                                                        | 37         |

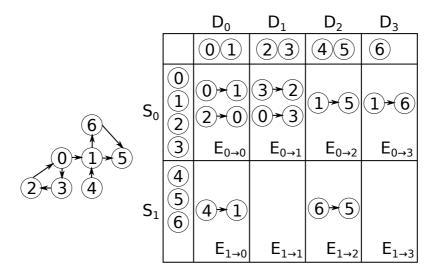

|    |                      | 7.3.1 Graph Partitioning 8                                                    | 37         |

|    |                      | 7.3.2 Programming Model                                                       | 38         |

|    |                      | 7.3.3 Graph Encoding and Memory Layout                                        | 90         |

|    | 7.4                  | System Architecture                                                           | 91         |

|    |                      | 7.4.1 Top-Level Architecture                                                  | 91         |

|    |                      | 7.4.2 PE Architecture                                                         | 93         |

|    |                      | 7.4.3 Handling Efficiently Out-of-Order Responses                             | 94         |

|    |                      | 7.4.4 Node Reordering                                                         | 95         |

|    | 7.5                  | Evaluation                                                                    | 96         |

|    |                      | 7.5.1 Experimental Setup 9                                                    | 96         |

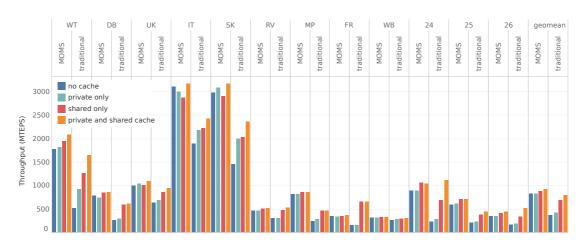

|    |                      | 7.5.2 Architecture Exploration                                                | 97         |

|    |                      | 7.5.3 Preprocessing Cost and Impact                                           | 00         |

|    |                      | 7.5.4 Memory Bandwidth Scalability                                            | 01         |

|    |                      | 7.5.5 Impact of Caches                                                        | 02         |

|    |                      | 7.5.6 Comparison with the State of the Art                                    | 04         |

|    |                      | 7.5.7 Resource Utilization and Operating Frequency                            | 06         |

|    | 7.6                  | Conclusion                                                                    | 07         |

| 8  | Con                  | clusions 10                                                                   | )9         |

|    | 8.1                  | A Cache for Throughput-Oriented Applications with Irregular Access Pattern 10 | 09         |

|    | 8.2                  | Exploiting Every Bit of Memory Bandwidth and FPGA Resources                   | 10         |

|    | 8.3                  | Revisiting Caches for Graph Processing                                        | 11         |

|    | 8.4                  | Future Perspectives                                                           | 12         |

|    | 8.5                  | Final Remarks                                                                 |            |

| Bi | bliog                | raphy 11                                                                      | 15         |

| Cı | Curriculum Vitae 127 |                                                                               |            |

|    |                      |                                                                               |            |

# List of Figures

| 1.1        | Forty-eight years of microprocessor trends                                   | 2  |

|------------|------------------------------------------------------------------------------|----|

| 1.2        | DRAM capacity, bandwidth, and latency trends from 1999 to 2017               | 3  |

| 1.3        | Roofline model definitions                                                   | 3  |

| 1.4        | Impact of memory bandwidth and compute power scaling on the roofline model . | 4  |

| 1.5<br>1.6 | Impact of memory bandwidth variability on the roofline model                 | 4  |

| 1.7        | space                                                                        | 5  |

|            | $\leq x$ , for SpMV of pds-80 and a sequential memory trace                  | 5  |

| 2.1        | Structure of a nonblocking cache                                             | 10 |

| 2.2        | Structure of a DRAM bank with a single memory array                          | 12 |

| 2.3        | Overview of the DRAM hierarchy together with the multiplexers that are used  |    |

|            | during read operations                                                       | 13 |

| 2.4        | Example of memory command schedule                                           | 15 |

| 2.5        | Structure of our benchmark sparse matrix-vector multiplication accelerator   | 17 |

| 2.6        | Multi-die partitioning of SpMV accelerator and MOMS on the AWS F1 FPGA       | 20 |

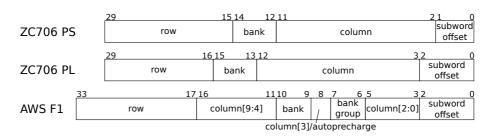

| 2.7        | Address mapping in our experimental platforms                                | 22 |

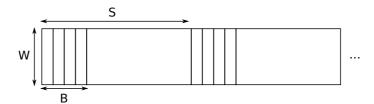

| 2.8        | Strided access pattern                                                       | 22 |

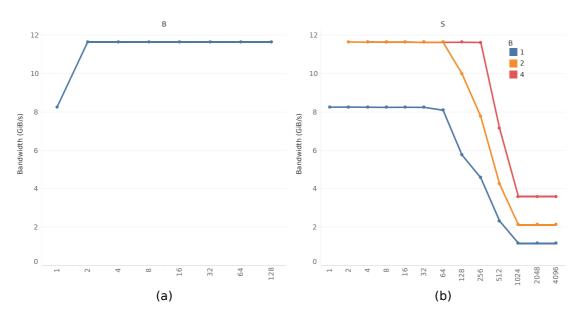

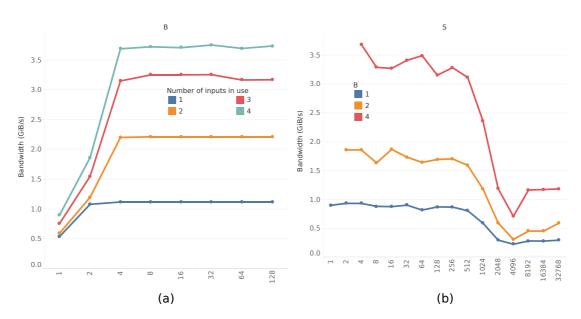

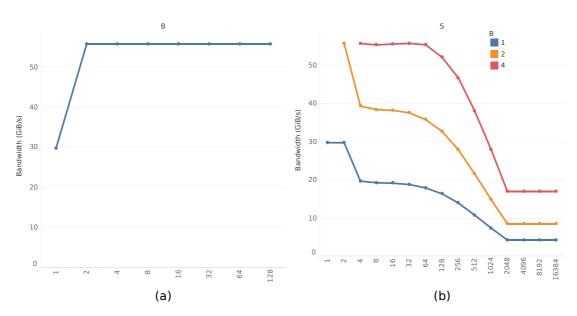

| 2.9        | Bandwidth of the ZC706 PL memory system                                      | 23 |

| 2.10       | Bandwidth of the ZC706 PS memory system                                      | 24 |

| 2.11       | Bandwidth of the AWS F1 memory system                                        | 25 |

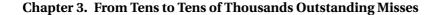

| 3.1        | MSHR-rich architectures for FPGAs                                            | 28 |

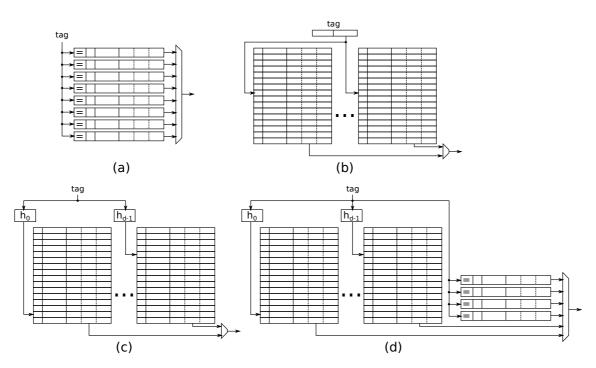

| 3.2        | Subentry organization in memory                                              | 29 |

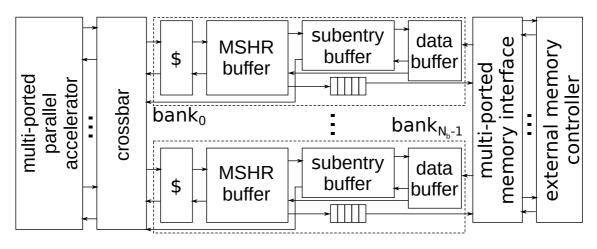

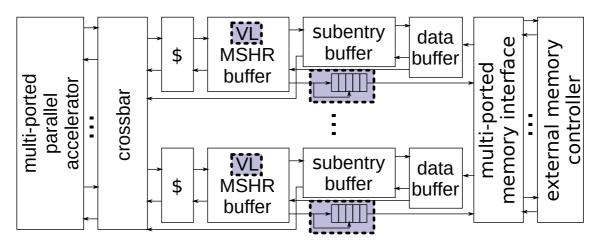

| 3.3        | Top-level view of our MOMS                                                   | 30 |

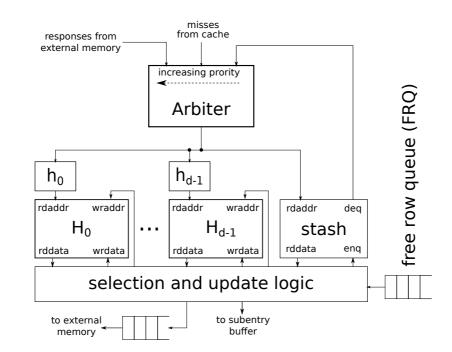

| 3.4        | Block diagram of the MSHR buffer                                             | 31 |

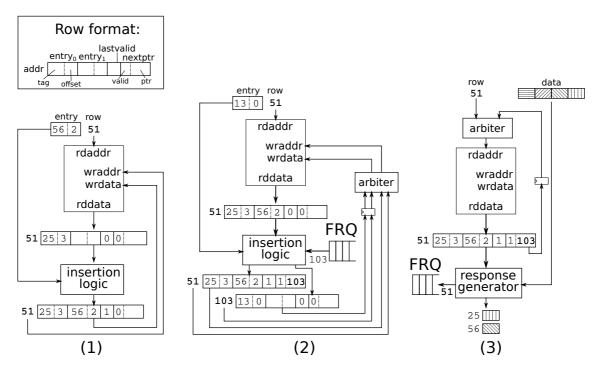

| 3.5        | Block diagram and operation of the subentry buffer                           | 32 |

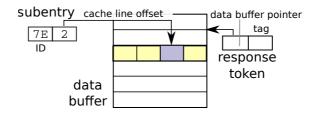

| 3.6        | Retrieval of responses from the data buffer                                  | 33 |

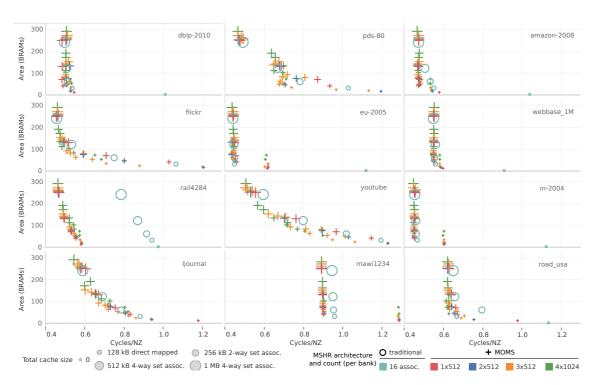

| 3.7        | Area of the memory system and normalized execution time for all benchmarks   |    |

|            | and a broad range of nonblocking cache architectures                         | 35 |

| 3.8        | Achievable MSHR storage load factor for several MSHR architectures           | 36 |

#### List of Figures

| 3.9 | 5                                                                                           |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | a uniformly distributed benchmark                                                           | 36 |

| 3.1 | 0 Average and maximum subentry utilization during the execution of ljournal with a          |    |

|     | $3 \times 512$ cuckoo MSHR                                                                  | 37 |

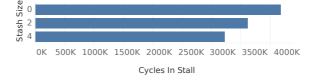

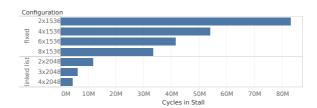

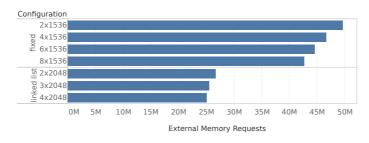

| 3.1 | 1 Number of cycles lost due to subentry-related stalls                                      | 37 |

| 3.1 | 2 Number of external memory requests during the execution of ljournal with a $3 \times 512$ |    |

|     | cuckoo MSHR and no cache                                                                    | 37 |

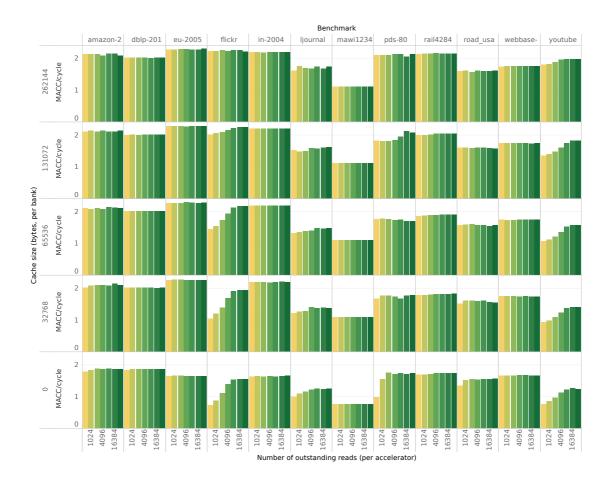

| 3.1 | 3 Throughput as a function of ROB size, cache size, and benchmark                           | 38 |

| 4.1 | Total availability and utilization of DRAM-based external memory bandwidth                  |    |

|     | under short irregular access patterns                                                       | 42 |

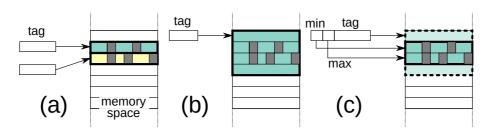

| 4.2 | MSHR memory range and structure                                                             | 43 |

| 4.3 | Burst update policies                                                                       | 43 |

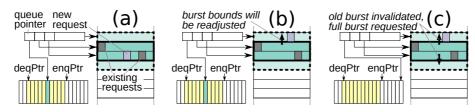

| 4.4 | Burst bounds update circuit                                                                 | 45 |

| 4.5 | Top-level view of the burst-based MOMS                                                      | 46 |

| 4.6 | Block diagram and operation of the subentry buffer with variable-length bursts              | 47 |

| 4.7 | Retrieval of responses from the data buffer                                                 | 47 |

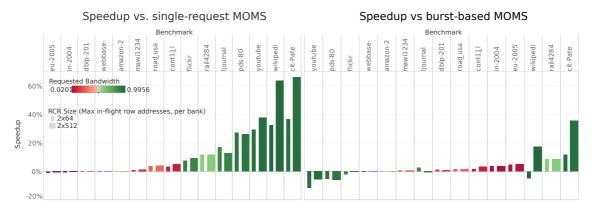

| 4.8 | Speedup obtained in MOMSes by sending bursts of memory requests compared to                 |    |

|     | single-request MOMSes, both with dynamically adjusted burst bounds and always               |    |

|     | requesting full bursts                                                                      | 49 |

| 4.9 | Throughput of a traditional nonblocking cache, a single-request MOMS and                    |    |

|     | variable-length burst MOMS                                                                  | 50 |

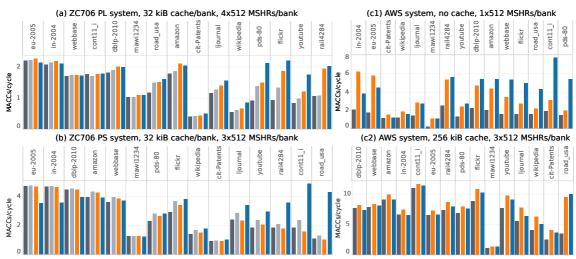

| 4.1 | 0 Throughput of traditional nonblocking cache, single-request MOMS and burst                |    |

|     | MOMS on individual benchmarks for architectures where burst MOMSes have the                 |    |

|     | largest speedup compared to traditional caches                                              | 51 |

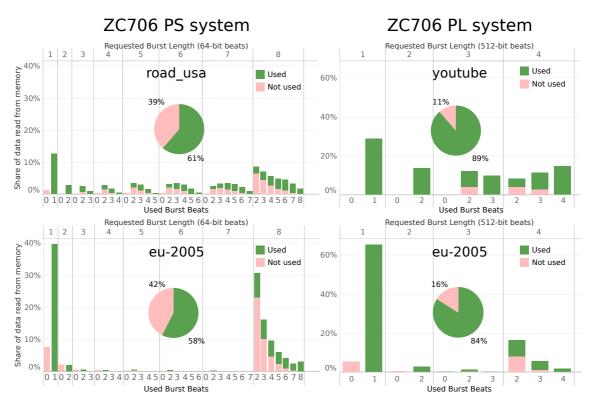

| 4.1 | 1 Distribution of requested, used, and wasted cache lines per burst as a function of        |    |

|     | the burst length, normalized by the total number of cache lines requested from              |    |

|     | memory                                                                                      | 52 |

| 5.1 | Impact of different miss-optimized architectures on the memory access pattern               |    |

|     | and thus on DRAM bandwidth                                                                  | 58 |

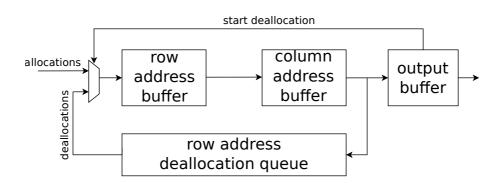

| 5.2 | Top-level architecture of the MOMS with row conflict reducers (RCRs)                        | 58 |

| 5.3 | Architecture of an RCR                                                                      | 59 |

| 5.4 | Interpretation of memory addresses by the miss-handling logic and DRAM memory               | 60 |

| 5.5 | Speedup of the RCR-based MOMS using the smaller and the larger RCRs across all              |    |

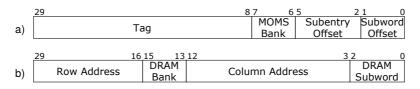

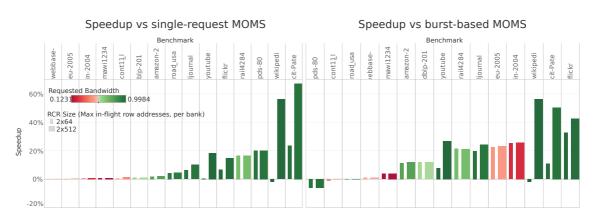

|     | the benchmarks, compared to the single-request and variable-length burst MOMS               | 63 |

| 5.6 | Fraction of requested and obtained DRAM bandwidth during the execution of all               |    |

|     | benchmarks on all configurations, color-coded by MOMS architecture $\ldots$ .               | 65 |

| 5.7 |                                                                                             |    |

|     | particularly favorable to RCRs                                                              | 66 |

| 5.8 | Speedup provided by the RCRs on individual benchmarks, on a configuration                   |    |

|     | where the RCR-based MOMS is moderately competitive to the burst-based MOMS                  | 66 |

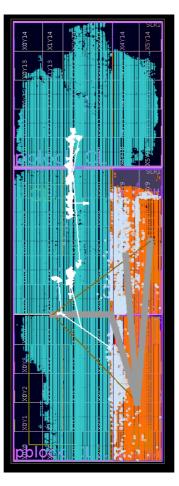

| 6.1  | Layout of the placed-and-routed MOMS with 16 inputs and banks on the AWS F1           |    |

|------|---------------------------------------------------------------------------------------|----|

|      | FPGA when no multi-die-aware design modifications and constrains are used             | 70 |

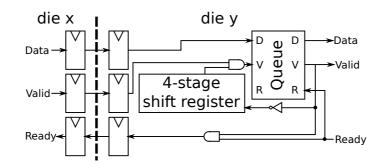

| 6.2  | Inter-die crossing circuit for signals with handshake                                 | 71 |

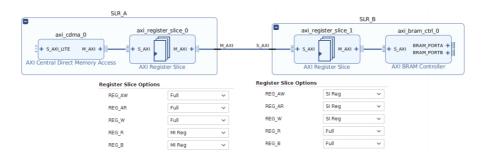

| 6.3  | Circuit that allow high-performance AXI4 connections that cross a die boundary        |    |

|      | at the level of the Xilinx IP Integrator                                              | 71 |

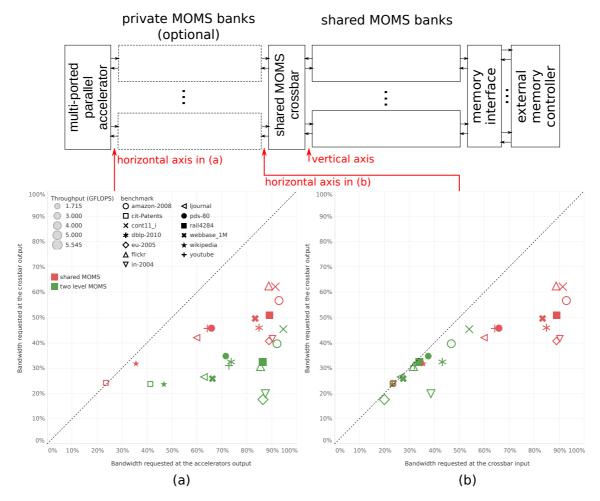

| 6.4  | Structure of a two-level MOMS                                                         | 72 |

| 6.5  | Structure of a private MOMS                                                           | 73 |

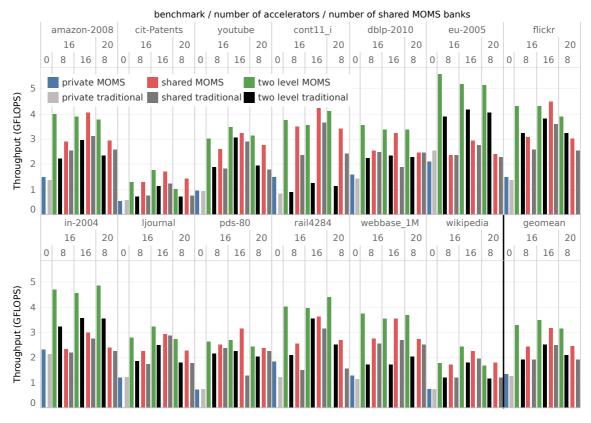

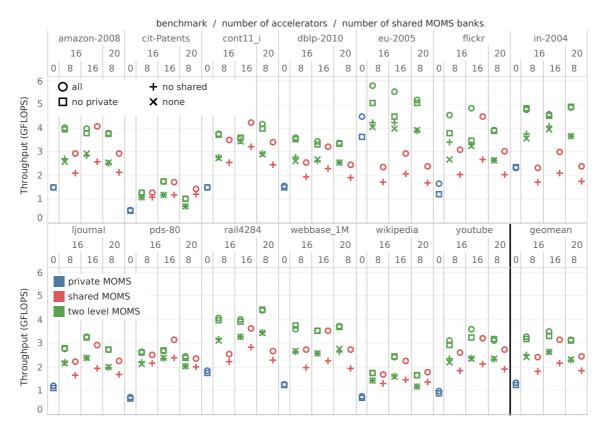

| 6.6  | Throughput of the shared, two-level, and private MOMSes and traditional caches        |    |

|      | presented in Table 6.1                                                                | 76 |

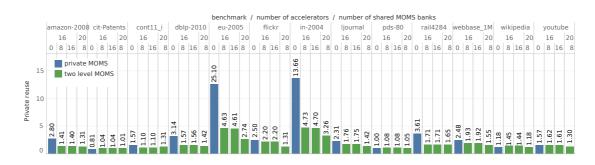

| 6.7  | Private reuse in private-only and two-level MOMSes                                    | 77 |

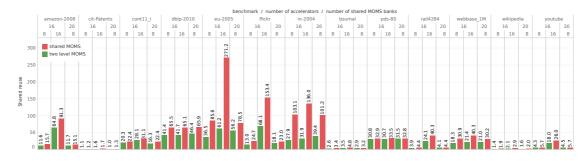

| 6.8  | Shared reuse in shared-only and two-level MOMSes                                      | 77 |

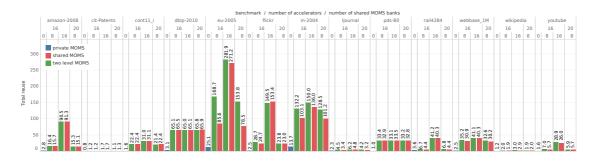

| 6.9  | Total reuse in private-only, shared-only, and two-level MOMSes                        | 78 |

| 6.10 | Impact of private and shared caches in private, shared, and two-level MOMSes .        | 79 |

| 6.11 | Requested bandwidth at the shared MOMS crossbar output as a function of the           |    |

|      | requested bandwidth at the accelerators output and at the crossbar input for the      |    |

|      | 16/16 shared and two-level MOMSes                                                     | 80 |

|      |                                                                                       | ~~ |

| 7.1  |                                                                                       | 86 |

| 7.2  |                                                                                       | 88 |

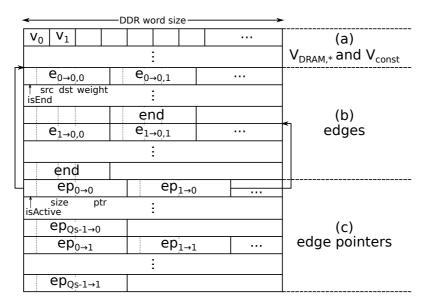

| 7.3  | 1 5 5                                                                                 | 90 |

| 7.4  |                                                                                       | 91 |

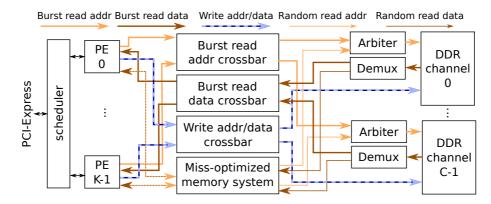

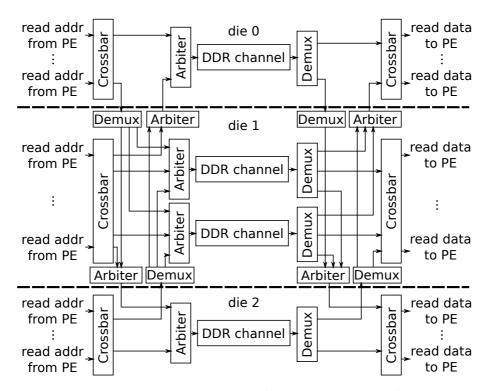

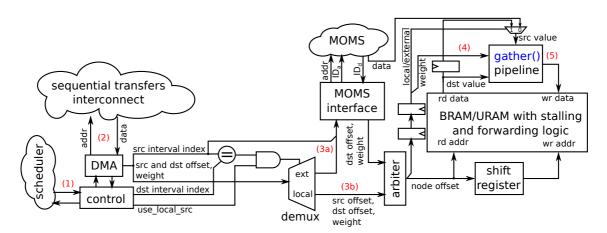

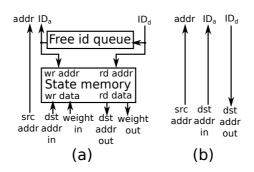

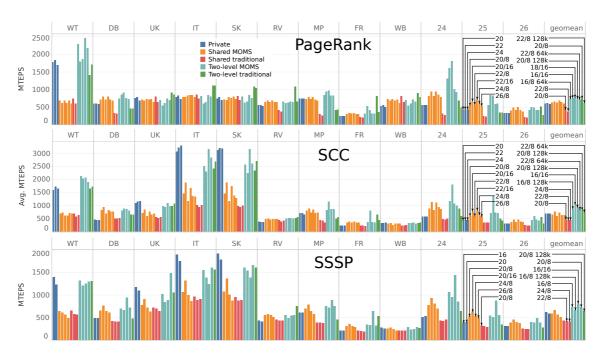

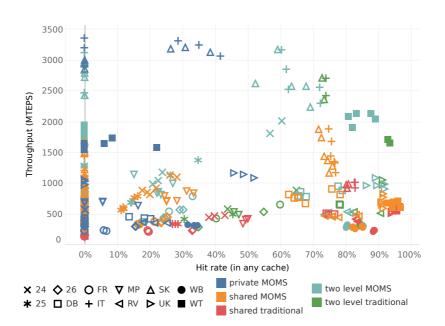

| 7.5  |                                                                                       | 92 |

| 7.6  |                                                                                       | 93 |

| 7.7  |                                                                                       | 94 |

| 7.8  |                                                                                       | 98 |

| 7.9  | 01                                                                                    | 99 |

| 7.10 | PageRank throughput on the 18/16 two-level MOMS architecture depending on             |    |

|      | r r of                                                                                | 00 |

| 7.11 | Scalability of throughput as a function of the number of DDR4 channels for the        |    |

|      | two-level 16/16 MOMS architecture and for PageRank on FabGraph 1                      | 01 |

| 7.12 | Detail of the hit/miss data paths from MOMS to accelerator                            | 02 |

| 7.13 | Throughput on SCC for the 16/16 two-level MOMS and traditional cache, with and        |    |

|      | without shared cache                                                                  | 03 |

| 7.14 | Throughput on SCC for the 20/8 two-level MOMS and traditional cache, with and         |    |

|      | without private and/or shared cache                                                   | 04 |

| 7.15 | Comparison with state of the art on CPU, GPU, and FPGA                                | 05 |

| 7.16 | Relative utilization of resources for the top two architectures of each application 1 | 06 |

## List of Tables

| 2.1 | Properties of the benchmark matrices                                                                                                                        | 18  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Specifications of the FPGAs used in our experiments.                                                                                                        | 19  |

| 2.3 | Specifications of the external memory systems used in our experiments                                                                                       | 19  |

| 3.1 | Resource utilization of MOMSes and traditional cache with 16 MSHRs with 8 subentries each per bank, compared to the resource utilization of the rest of the |     |

|     | experimental system                                                                                                                                         | 39  |

| 3.2 | Resource utilization of the four-bank MOMS with 256 kiB cache as a function of                                                                              |     |

|     | the number of MSHRs                                                                                                                                         | 39  |

| 4.1 | Resource utilization of MOMSes and traditional cache compared to the resource                                                                               |     |

|     | utilization of the rest of the experimental system                                                                                                          | 54  |

| 4.2 | Resource utilization of the 16-bank MOMS on AWS F1 with 256 kiB cache, $3 \times 512$                                                                       |     |

|     | MSHR, $8\times4096$ subentries per bank as a function of the maximum burst length .                                                                         | 55  |

| 5.1 | Analogies and differences between MOMS miss handling and RCR memory request                                                                                 |     |

|     | handling                                                                                                                                                    | 60  |

| 5.2 | Area utilization of the proposed solution and overhead compared to the baselines                                                                            | 67  |

| 6.1 | Configurations evaluated in our experiments                                                                                                                 | 75  |

| 6.2 | Resource utilization and clock frequency of the designs listed in Table 6.1 $\ldots$                                                                        | 82  |

| 7.1 | Examples of algorithm-specific parameters for Template 3                                                                                                    | 89  |

| 7.2 | Benchmarks properties.                                                                                                                                      | 97  |

| 7.3 | Preprocessing time in seconds.                                                                                                                              | 100 |

| 7.4 | Memory bandwidth and power consumption of the platforms considered in Fig-                                                                                  |     |

|     | ure 7.15                                                                                                                                                    | 104 |

### **1** Introduction

Since the inception of electrical computers 80 years ago, the available processing power has been increasing at a tremendous pace. Between 1956 and 2015, the processing power available on a single system has witnessed a 1-trillion fold increase [84] and the number of floating-point operations that an Xbox One X from 2017 can perform in one second would take 190 years on the Atlas, the fastest supercomputer in 1962 [96, 103]. Figure 1.1 shows that the number of transistors in a single *Central Processing Unit* (CPU) has increased by a factor 10<sup>7</sup> in the past 48 years, which led to an exponential increase in single-thread compute performance until the end of Dennard scaling around 2005 and, afterwards, of parallel cores in multicore CPUs.

#### 1.1 Memory-Computation Gap

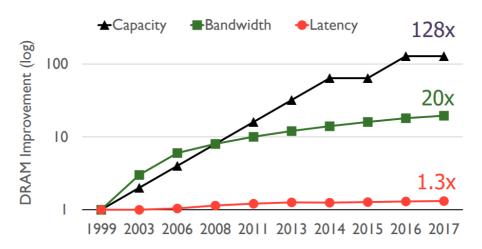

Memory capacity has also increased exponentially with time [39], although at a slower pace than the number of processing cores [65]. However, the same cannot be said about bandwidth and latency, as shown in Figure 1.2. While the number of transistors between 1999 and 2017 increased by  $4,000 \times$  and the number of parallel cores between 2005 and 2020 by  $100 \times$ , the bandwidth of main memory only increased by a factor  $20 \times$  and latency essentially stagnated.

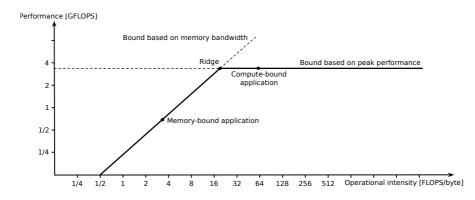

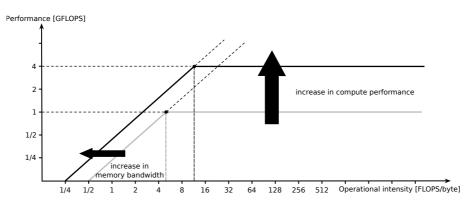

The implications of this gap can be visualized in the roofline model [105], shown in Figure 1.3, which shows the achievable performance in, e.g., *Floating Point Operations per Second* (FLOPS), as a function of the *operational intensity*, i.e., the number of operations per byte read from memory. While at high operational intensities the performance is limited by the processing power of the compute engine, the bottleneck at low operational intensity becomes memory bandwidth. Increasing the processing power shifts the horizontal ceiling up, while increasing the memory bandwidth shifts the sloped memory ceiling leftwards. When the processing power increases more quickly than memory bandwidth as in Figure 1.4, the intersection between the two ceilings (*ridge*) shifts to the right. This means that the minimum arithmetic intensity that is required to fully exploit a compute engine and achieve peak performance increases. Applications where this condition is not satisfied are said to be *memory-bound* and are becoming more and more common [105].

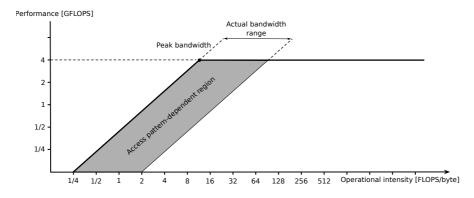

**Figure 1.1** – Forty-eight years of microprocessor trends. The number of transistors in a CPU increased by seven orders of magnitude; while the growth in single-thread performance and clock frequency has slowed down or stopped since the mid-2000s, the number of parallel cores took over and increased by two orders of magnitude in 15 years. Reprinted from Karl Rupp's GitHub repository [86].

The examples introduced so far consider a single value for the memory bandwidth; however, in the case of the *Dynamic Random Access Memories* (DRAM) which make up most of the main memory market as of 2020 [92, 1, 100], this is a simplification. The actual DRAM bandwidth is indeed heavily dependent on the *access pattern*, that is, the pattern of addresses that are sent to the memory, as well as the granularity of each memory operation. Therefore, a more complete roofline model defines a region where the memory bandwidth ceiling can be, depending on the properties of the access pattern, rather than a single line, as shown in Figure 1.5. We will show in Section 2.6.4 that the access pattern alone may decrease the memory bandwidth by up to  $7 \times$ , which can be compounded by another order of magnitude in the case of fine access granularity.<sup>1</sup> As a result, for a broad range of operational intensities, access pattern and granularity will define whether the application will be able to fully exploit the available compute resources or not.

#### **1.2 Limitations of Existing Solutions**

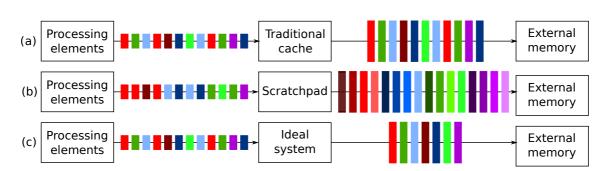

The most common way to increase memory bandwidth is to shift as many accesses as possible to *Static Random Access Memories* (SRAMs), whose bandwidth is not only higher than that of DRAMs but also insensitive to the access pattern. Since SRAMs have a larger area and a higher price per bit than DRAM, memories based on the two technologies are usually combined in a *memory hierarchy*. From the perspective of the compute engine, an ideal memory hierarchy behaves as a memory that is as large as the DRAM but as fast as the SRAM: this is achieved by

<sup>&</sup>lt;sup>1</sup>For example, for a common minimum access granularity of 512 bits, 32-bit irregular accesses can only use  $\frac{1}{16}$  of each response

**Figure 1.2** – DRAM capacity, bandwidth, and latency trends from 1999 to 2017. Scaling efforts focused on capacity, followed by bandwidth; latency remained mostly the same during 18 years. Reprinted from Onur Mutlu's presentation [72].

**Figure 1.3** – Roofline model definitons. The roofline model provides a visual insight on the bottlenecks of a kernel on a given platform. When the number of operations per transferred byte (*operational intensity*) is high, the performance is limited by compute; conversely, memory bandwidth limits performance at low operational intensities. Reprinted with modifications from Wikipedia [104].

serving as many memory accesses as possible directly from the SRAM while at the same time migrating data from DRAM to SRAM as few times as possible.

Custom memory hierarchy design and automatic generation usually rely on access patterns that are regular (scratchpads), have temporal and spatial locality (scratchpads, caches) or are at least known at compile-time (memory banking and address scrambling) [3, 33, 18, 119]. When access patterns are irregular and data-dependent and rewriting the application is not viable, designers are left with maximizing memory-level parallelism (MLP) by generating enough outstanding memory operations to at least make DRAM access fully pipelined. However, the throughput of the memory system is still capped to one operation per cycle per DRAM channel, at best. This imposes severe limitations on the amount of datapath parallelism that is worth implementing, reducing the advantage of hardware specialization.

**Figure 1.4** – Impact of memory bandwidth and compute power scaling on the roofline model. If the peak compute performance scales faster than the memory bandwidth, the ridge of the model shift rightwards, meaning that the minimum operational intensity that makes the kernel compute-bound increases.

**Figure 1.5** – Impact of memory bandwidth variability on the roofline model. The bandwidth in common external memories is heavily dependent on the access pattern; as a result, a particularly unfavorable access pattern may turn a compute-bound kernel into a memory-bound one, wasting compute resources.

In fact, one operation per cycle per DRAM channel is only a theoretical bound: as discussed in Section 1.1, the actual throughput is often significantly lower, especially when accesses are irregular. If accesses are not only irregular but also narrow (such as 32- or 64-bit scalars), the effective bandwidth gets reduced even further. Two separate mechanisms contributes to the bandwidth degradation in those cases. Firstly, both DDR3 and DDR4 operate on bursts of eight beats, normally of 64 bits each [47, 48], which results in a minimum access granularity of a full 512-bit burst. If accesses are narrower than the burst size, the remaining data returned from memory will be discarded, wasting memory bandwidth and energy. In addition, serving uncorrelated streams of requests from multiple accelerators can only be done by time-multiplexing the memory channel, canceling out any benefits due to parallelization when memory bandwidth is the bottleneck. The only way to improve bandwidth utilization, and thus performance, would be to use larger portions of each burst returned from memory.

The second mechanism relates to the organization of bits in DRAM: a few banks (8 and 16 for DDR3 and DDR4 respectively), each consisting of a two-dimensional array of capacitors.

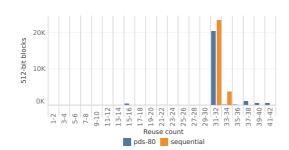

**Figure 1.6** – Spatial locality. Reuse count for each 512-bit block of data, for SpMV of pds-80 and for the same number of read operations performed sequentially over the same memory range, wrapping back at the end. Despite showing very different cache hit rates, both memory traces have similar amounts of data reuse across the entire application execution.

**Figure 1.7** – Temporal locality. Fraction of 512bit block references that have stack distance  $\leq x$ , for SpMV of pds-80 and a sequential memory trace. A large fraction of the reuses that occur in pds-80 are interleaved with references to many different blocks. Blocks can be stored in a cache hoping for future reuse; however, because large stack distances are common, cache lines are likely to be evicted before the next reuse, unless a large cache is used.

Reading data involves first copying the respective row to the *row buffer* [47, 48], an operation that has to be repeated every time a different row is accessed in the same bank. Since this operation is time-consuming, the actual bandwidth decreases when accesses require switching row frequently (row conflicts). DRAM controllers reorder memory requests to reduce the number of DRAM row conflicts [82]; however, because general-purpose controllers must also minimize latency, the internal request queues are relatively shallow and the optimization is possible only for accesses close in time. More details on DRAM operation and on DRAM controllers are provided in Section 2.3 and 2.4.

#### **1.3 Opportunities for Data Reuse**

To discuss the opportunities to increase the utilization of each 512-bit blocks received from memory, Figure 1.6 shows the histogram of the number of reuses of 512-bit blocks for an application with poor locality—accesses to the dense vector of 32-bit integers during sparse matrix-vector multiplication (SpMV) with the pds-80 matrix from SuiteSparse [27] encoded in Compressed Sparse Row (CSR) format. It also illustrates what would happen if the same number of read operations were performed sequentially over the same address span—that is, if instead of reading elements of the dense vector by following the sparsity pattern of the matrix, we simply read the entire vector sequentially, wrapping back to the beginning when reaching the end, until performing the same amount of read operations as in the first case. The sequential access pattern achieves a 15/16 = 94% hit rate on any cache with 512-bit cache lines: the first access to every cache line is a compulsory miss but the following 15 accesses hit on the same cache line which has just been fetched. In contrast, we observed that the SpMV access pattern only achieves a 57% hit rate on a 128 kiB direct-mapped blocking cache, despite having very similar opportunities for reuse across the access pattern as a whole. This is because, in a cache,

eviction limits the time window where data reuse could occur. For the same two access patterns, Figure 1.7 shows the cumulative frequency of *stack distances*, i.e., the number of different 512-bit blocks that have been referenced between two consecutive references to the same blocks [20]. For example, for the memory trace: {389, 261, 124, 4938, 261, 389}, the stack distances for the last access to blocks 261 and 389 are 2 and 3 respectively. While the stack distance of the sequential pattern is always zero, the SpMV cumulative histogram grows very slowly, meaning that a large fraction of reuses have large stack distance. With an ideal fully associative cache with N lines and LRU replacement, reaccessing a cache line with stack distances larger than N will always be a miss; on a realistic cache, even reuses with stack distance lower than N could be misses.

#### 1.4 Pushing Nonblocking Caches to the Extreme

The previous example shows that even applications with poor temporal locality may still have some spatial locality, which caches struggle to harness due to large stack distances between reuses. Even worse, a blocking cache actually hampers performance if the hit rate is too low to compensate for the stall cycles due to the misses. Nonblocking caches, described in detail in Section 2.2, reduce stall penalties by handling a small number of misses without stalling. In addition, they also group misses by cache line so that a single cache line request can be used to serve all the respective misses. This is implemented by storing each in-flight cache line in a *miss status holding register* (MSHR), each comprising multiple *subentries* that contain the offset and source of the respective misses. This organization pushes the maximum MLP beyond the DRAM latency and increases bandwidth utilization as long as there are available MSHRs and subentries [68].

Indeed, adding an MSHR with its subentries enlarges the reuse window just like an extra cache line: while a cache stores entire blocks hoping for future reuse, MSHRs and subentries keep track of which portions of the blocks are actually needed. This way, as soon as a block is received, the miss handling logic serves the block requests that have been accumulated and then discards the block. With typical block and address sizes of hundreds and tens of bits respectively, the on-chip memory cost of reusing a block is hundreds of bits if done using the cache or tens of bits *per reuse* using MSHRs and subentries. This means that if the number of block reuses is greater than one but sufficiently small, reusing it via MSHRs and subentries has a lower on-chip memory cost than relying on the cache for the same purpose.

Nonblocking caches are extensively used in processors; however, MSHRs are usually searched in a fully-associative structure to minimize latency, which limits their number to a few tens. In practice, there is often little benefit in increasing the number of MSHRs beyond this limit on realistic CPUs [64, 98]. On FPGAs, fully-associative searches are even less scalable than in ASICs; yet, high-throughput massively parallel FPGA accelerators that generate a large number of outstanding reads to hide memory latency [66, 23] could potentially benefit from an MSHR-rich architecture even more than a general-purpose processor.

#### 1.5 Storing Requests Instead of Data

This thesis is based on the observation that serving a request (1) by using data that is in cache or (2) by reusing a block that has been already requested to serve another miss have the same impact on throughput. This means that, when latency is irrelevant, both are equally beneficial to performance. While both mechanisms can satisfy the request without generating extra memory traffic, thus without adding pressure to the memory bottleneck, the latter requires less on-chip memory when reuse exists but is limited. Indeed, reusing an in-flight cache line only requires storing some miss metadata until the data returns from memory as opposed to keeping the entire cache line as long as possible in the cache array.

#### 1.6 Thesis Outline

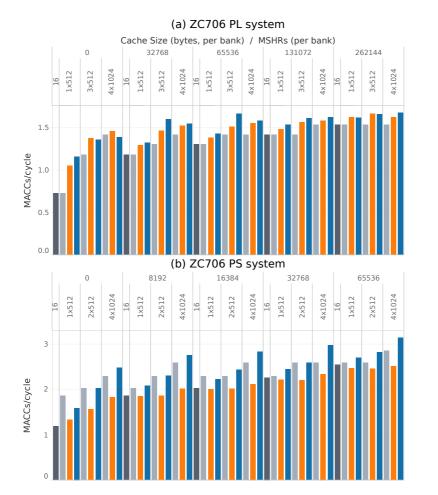

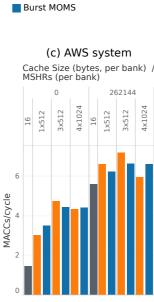

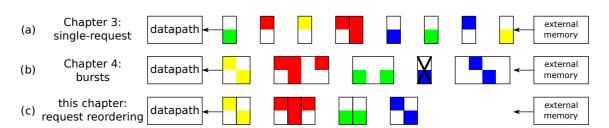

After covering some background and related work on nonblocking caches, DRAM memories, and graph processing in **Chapter 2**, we discuss in **Chapter 3** how to scale up the MSHR array by three orders of magnitude. Doing so maximizes the probability for a miss to target a cache line whose request has been already sent out or at least queued.<sup>2</sup> We show that repurposing some on-chip memory from cache to MSHRs generally proves to be beneficial, especially when the DRAM controller exposes the entire DRAM burst through a wide data port and provides enough bandwidth even to single requests.

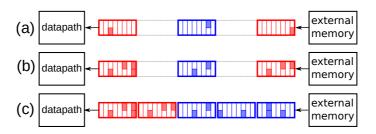

When DRAM controllers instead have multiple narrow ports, which is common on SoC platforms, or are heavily optimized for bursts and individual accesses cannot be fully pipelined, optimizing the reuse of individual memory requests is generally useful but leaves some performance on the table. To address these scenarios, in **Chapter 4** we show how to extend MSHRs to support bursts of variable length on the memory side. When possible, we make bursts longer and exploit more of a DRAM burst or row without being limited to the data width exposed by the specific memory controller. Conversely, when spatial locality is insufficient, we keep burst short and minimize contention in the controller or avoid requesting unnecessary DRAM bursts. Requesting bursts extends the scope of MOMSes to memory controllers with narrow ports or where single accesses are heavily penalized compared to burst accesses. In addition, bursts make accesses locally more sequential which, based on our memory characterization in Section 2.6.4, generally increases the total bandwidth that the memory can deliver.

Extending MSHRs to support bursts only requires minor modifications to the MOMS architecture; however, this simplicity comes with limitations in the way the generated bursts cover the data requested by the accelerators. In particular, the MOMS may end up requesting data that is not needed, which may account for up to 40% of the data received from memory, a fraction that is sometimes high enough to offset the bandwidth gains provided by bursts. To overcome these limitations, we observe that in order to gain visibility over a large number of incoming

<sup>&</sup>lt;sup>2</sup>In other words, to increase the probability that new misses will be secondary rather than primary, using terms that will be introduced in Section 2.2.

#### **Chapter 1. Introduction**

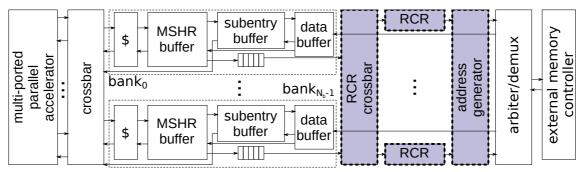

requests with minimal stalls, MOMSes also need a deep output queue for memory requests. As a byproduct, this deep output queue also gives MOMSes access to thousands of future memory requests. In **Chapter 5**, we discuss how to use this information to explicitly reorder individual memory requests across a window that is three orders of magnitude larger than that of a typical DRAM controller. We show that, on controllers where single accesses are not significantly penalized over bursts and where we have control on the DRAM command scheduling policy, we can reduce DRAM row conflicts without incurring in the data wastage associated with bursts.

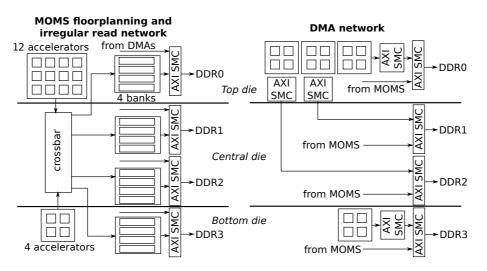

After maximizing the achievable DRAM bandwidth on a single DRAM channel, in **Chapter 6** we address the challenges associated to scaling our MOMS over multi-die FPGAs with larger DRAM bandwidth, allowing us to achieve high resource utilization and operating frequency on large FPGAs. We then tackle the main internal bottleneck of our original MOMS architecture, where all requests are handled by a single shared MOMS, which provides high reuse but is susceptible to high contention. Therefore, we additionally explore private MOMSes, which group requests on a per-accelerator basis with no interaccelerator conflict, and two-level MOMSes, which combine the advantages of private and shared MOMSes.

With MOMSes now able to maximize both DRAM bandwidth and FPGA resource utilization, in **Chapter 7** we show how they can make FPGAs key enablers for large-scale graph processing in the cloud, achieving higher performance than CPUs and better energy and bandwidth efficiency than GPUs without the high NRE costs and long development times typical of ASICs. Finally, in **Chapter 8** we conclude and outline possible directions for future research.

## **2** Background and Related Work

After reviewing the main properties of the various on-chip memories available in modern FPGAs in Section 2.1, we provide some background on nonblocking caches in Section 2.2, on DRAM memories and controllers in Sections 2.3 and 2.4 respectively. We then provide some definitions and present the state-of-the-art of graph processing on CPUs, GPUs, FPGAs, and ASICs in Section 2.5 and conclude the chapter with a detailed presentation and characterization of our experimental setup in Section 2.6.

#### 2.1 FPGA On-Chip Memory

Modern FPGAs have at least three types of on-chip memory: flip flops, LUTRAM, and block RAM (BRAM). Each bit of flip flop-based memory is exposed to the FPGA fabric, providing the highest flexibility in terms of number, type, and width of memory ports and the largest bandwidth. However, flip flop bits are the least abundant and some LUTs must be consumed to implement their access logic. LUTRAMs use LUTs to realize single-, dual-, or quad-port memories with medium depth (32-64 entries). However, they compete with combinational logic for LUTs. BRAMs are dedicated memory resources implemented as hard logic. They provide higher memory density than LUTRAMs and do not require any soft logic; however, they generally provide only two ports and are optimized for narrow and deep memory arrays (at least 512 entries). The most recent FPGA families offer an additional type of on-chip memory (UltraRAM/URAM [112] and eSRAM [43] in Xilinx and Intel FPGAs respectively) with even higher density and lower design flexibility than block RAMs-for example, Xilinx's URAM blocks can only be configured as 72-bit wide, 4,096-entry deep memories, while Intel's eSRAM has a fixed topology with 8 channels, each with up to 42 72-bit wide, 2,048 entry-deep banks, and have a minimum read latency of 10 cycles as opposed to 1-cycle of the finer memory blocks (M20K and MLABs). Therefore, the challenge is to use URAM/eSRAM as much as possible when available, followed by block RAM, LUTRAM, and flip flops.

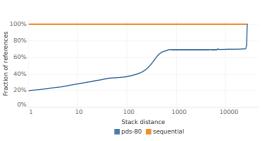

**Figure 2.1** – Structure of a nonblocking cache. On a hit (steps [h1]-[h2]), it behaves just like any cache. On a miss (steps [m1] to [m4]), the miss address and source/ID is stored in an MSHR [m2]. Only on the first miss to a particular cache line, a memory request is additionally generated [m3]. When the cache line data is received from memory, it is stored in the cache [m4a] and used to respond to all its pending misses [m4b].

#### 2.2 Nonblocking Caches

The first nonblocking (*lockup-free*) cache, proposed by Kroft in 1981 [56], introduced the idea of using miss status holding registers (MSHRs) to keep track of multiple in-flight misses. Farkas and Jouppi [31] evaluate a number of alternative miss handling architectures (MHA) for loads and observed that (1) nonblocking caches can reduce the miss stall cycles per instruction by a factor 4 to 10 compared to blocking caches, (2) that they are beneficial even for large cache sizes, and (3) that overlapping as many misses as possible allows processors to maximize the benefit provided by nonblocking caches.

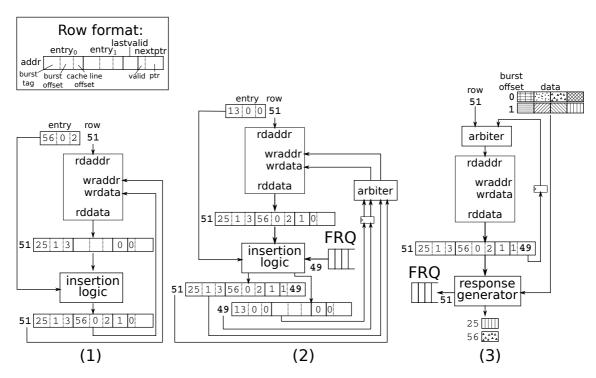

Figure 2.1 shows the organization of a typical nonblocking cache based on explicitly-addressed MSHRs, which is among the architectures proposed by Farkas and Jouppi [31] and that today is a *de facto* standard in industry [37]. In addition to the cache array, a nonblocking cache contains an array of MSHRs, which keeps track of the in-flight misses. Each MSHR refers to one missing cache line and contains a valid bit, the tag of the cache line and one or more subentries to handle multiple misses to the same cache line. On the first miss of a cache line (a *primary* miss), the address of the cache line is sent to memory and stored in an MSHR; the offset of the requested word within the cache line, together with the request source/ID, is stored in a *subentry* for that MSHR. Subsequent misses to the same cache line (*secondary* misses) only require the allocation of a subentry on the same MSHR with no additional memory requests. When the missing cache line is received, it is both stored in the cache and used to serve all of its pending misses [31].

Tuck et al. [98] introduced a novel MHA for single processor cores with very large instruction windows. They propose a hierarchical MHA, with a small explicitly-addressed MSHR file for each L1 cache bank and a larger shared MSHR file. MSHRs are explicitly-addressed and shared MSHRs have more subentries than the dedicated ones. On a number of SPEC2000 benchmarks running on a 512-entry instruction window superscalar single-core processor, dedicated files with 16 MSHRs and 8 subentries and a shared file with 30 MSHRs and 32 subentries achieve speedups that are close to those provided by an unlimited MHA. However, we believe that a

set of parallel accelerators is fundamentally different from a single-core processor even with a large instruction window for two reasons: a) parallel accelerators with, for instance, decoupled access/execution architectures [66, 23] could generate even more requests per cycle with no fundamental limitations on the total number of in-flight operations, and b) unlike multicore CPUs, requests to be merged can come from the same as well as a different accelerator, so it is important to have a shared MHA to maximize the merging opportunities. Our results throughout the thesis indeed show that, for parallel accelerators with massive MLP, thousands of MSHRs paired to a small cache array or even no cache at all can achieve similar or even better performance of larger caches with few MSHRs.

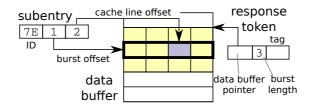

Gu and Chen [37] discussed the advantages of storing subentries in linked lists to accommodate workloads with different ratios of primary and secondary misses in GPUs. We independently and almost simultaneously proposed the same idea, which is discussed in detail in Section 3.1.2, as a fundamental ingredient to massively scale up the number of MSHRs. While our implementation is different as it is optimized for FPGAs and for a large number of MSHRs and subentries, we essentially reach the same conclusions concerning the advantages of arranging subentries in linked lists as opposed to statically allocating a fixed number of subentries to all MSHRs.

#### 2.3 DRAM Structure and Operation

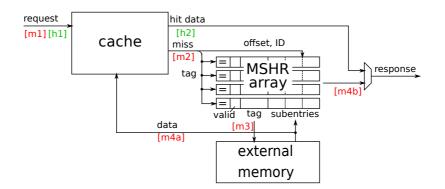

Dynamic random-access memories (DRAMs) use a single transistor-capacitor pair to store a bit of information, as shown in Figure 2.2. This makes DRAMs more area-efficient, and thus cheaper per bit, than SRAMs, where each bit usually requires a six-transistor (6T) cell. However, the capacitor is not perfect and its charge leaks over time. Therefore, each memory cell must be periodically read and rewritten, or *refreshed* [46]. We focus here on *synchronous* DRAMs and on read operations as currently MOMSes do not optimize writes.

Alongside the schematic of a single cell, Figure 2.2 shows the structure of a typical DRAM *bank*. Memory cells are organized in two-dimensional arrays, where each bit is identified by a *row* and a *column* address. Reading a bit first involves *precharging* the bit lines to  $V_{dd}/2$ , which is the average voltage between that of logic 0 and logic 1. Then, the row to be read is *activated*: the row address decoder raises the voltage on the wordline corresponding to the row address, which enables the access transistors of that row and connects each capacitor of the row to the respective bit line. This results in a small voltage change  $\pm \delta$  on each bit line due to charge sharing between the cell capacitor and the bit line capacitance, where the sign of the voltage change depends on the bit that was stored on the capacitor. Such voltage changes are amplified by the *sense amplifiers* in the *row buffer*, which latch the resulting logic levels and restore the charge in each capacitor. Once a row is in the row buffer, individual bits can be accessed randomly with high throughput and low latency using column accesses, essentially using the row buffer as a cache. On the other hand, accessing a different row requires disabling the current word line, followed by a new precharge and activation; all of these operations require extra time during which no data transfers may occur from the DRAM array [46].

**Chapter 2. Background and Related Work**

**Figure 2.2** – Structure of a DRAM bank with a single memory array. One bit of data is stored at every intersection between bit (columns) and word (row) lines. A single row is first activated and latched by the sense amplifiers; once there, column accesses can be performed to read individual bits. Reprinted with modifications from the book of Jacob et al. [46].

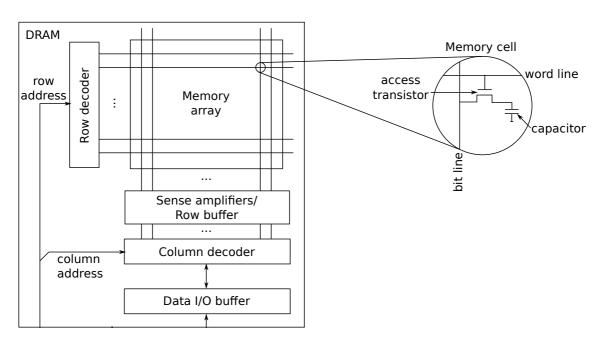

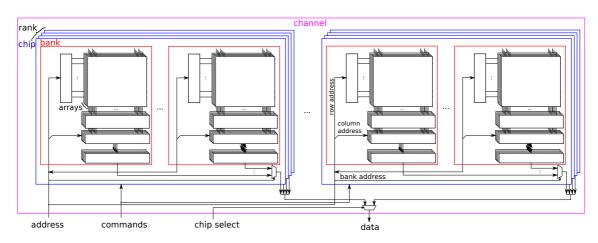

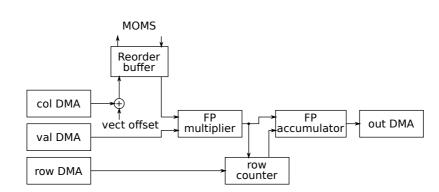

To improve performance, DRAMs implement parallelism at different levels, summarized in Figure 2.3. Multiple arrays can either share address and control signals or operate more or less independently from each other. The first solution is typically used to increase throughput by reading multiple bits with each column access: this has low area overhead but coarsens the granularity of each column operation. Typical DRAMs also implement multiple banks, which is the entire structure shown in Figure 2.2 (possibly with multiple memory arrays sharing the address and control signals). Banks within a DRAM chip are identified by a bank address and while they share the other I/O lines (row/column address, data, and control), they can mostly operate independently from each other. This allows to pipeline memory operations: for example, one bank may service a column access on a row that is already activated while another bank is precharging. A chip with one or more banks can be organize in a *rank* to operate in lockstep and further increase the size of each transfer by concatenating the respective data lines while sharing all the other signals, similarly to having multiple arrays in a bank. Multiple ranks, each identified by a dedicated *chip select*, can coexist within the same *DRAM channel*, which is the highest level in the DRAM hierarchy. While the I/O pins of devices in a DRAM channel are either shared or related to each other (such as the data pins in a rank, which are obtained by concatenating the data I/Os from each chip), different DRAM channels have no common signals and are completely independent from each other [46].

The complexity of DRAMs is not restricted to topology but also on its interface as even the simplest memory operations, such as reading or writing some data, require multiple commands such as bank precharge, row activation, and column access, while also periodically refreshing

**Figure 2.3** – Overview of the DRAM hierarchy together with the multiplexers that are used during read operations [46, 72]. Each *channel* has an independent address, command, and data bus and can be composed of one or multiple *ranks*, which are enabled based on the chip select signals. A rank consists of multiple *chips* that operate in lockstep; the data output of a rank is obtained by concatenating the output of each chip. Each chip contains multiple *banks*, addressed by the *bank address* portion of the address, which operate independently from each other. Each bank in turn typically contains multiple *arrays* so that each column access retrieves multiple bits.

the memory array. Such commands must obey tens of device-dependent timing constraints to ensure proper operation: for example, activation cannot be started until the bit lines reach the proper precharge voltage. Therefore, a *DRAM controller* is typically used to translate the simple memory commands generated by the CPU, GPU, or accelerator into a sequence of legal, and ideally efficient, DRAM commands [46]. Each DRAM controller is typically assigned to a single DRAM channel; modern CPUs [97, 9] and GPUs [77] use on-chip DRAM controllers while, on FPGAs, controllers can be either hardened [109] or in soft logic [108].

Fabrication processes for DRAM are optimized for density of memory cells, whose leakage must be low enough and capacitance large enough to ensure data retention and integrity [46]. Unlike in logic-optimized processes, high operating frequency is a secondary concern and indeed the DRAM core frequency has not increased significantly since the first single data rate (SDR) synchronous DRAMs standardized by JEDEC in the mid-90s. Memory bandwidth has been increased by instead 1) transferring a new data on both clock edges (double data rate, DDR) and 2) increasing the I/O clock frequency from the 100-200 MHz of the first DDR standard to the 667-1600 MHz of DDR4. To match the throughput of the DRAM core to that of the I/Os, all DDR standards use prefetching: each column access inside the DRAM is wider than the I/O data interface and the data read is serialized out in multiple transfers. The prefetch depth has been doubled at every DDR generation until DDR3, where it reached the value of eight, meaning that each column access results in eight transfers across four I/O clock cycles on both clock edges. Note that, on all DDR generations until DDR3, the minimum time between column commands (tCCD) is such that multiple column accesses can be perfectly pipelined as long as they are all row hits (i.e., they target a row that is currently active in one of the banks), leading to the ideal throughput of one transfer per clock edge. If the trend continued, DDR4 would have needed a

prefetch depth of 16; however, considering that most DDR modules have a data width of 64 bit, this would have meant that the minimum access granularity (*burst length*) would have become 1,024 bits. On many processors, including x86 and ARM, this would have corresponded to two cache lines, potentially leading to large data and bandwidth wastage when memory accesses are irregular. Therefore, DDR4 maintained a prefetch depth of eight like DDR3 but introduced the concept of *bank group* instead. While DDR3 has eight fully independent banks, DDR4 has 16 banks organized in four bank groups: column accesses on a given bank group take longer than four I/O cycles and cannot be perfectly pipelined but column accesses on different bank groups can be partially overlapped and thus achieve ideal throughput [94]. This allows DDR4 to preserve the same access granularity as DDR3 at the expense of a higher complexity of the policies that the DRAM controller must implement to achieve high performance.

In general, prefetching has no significant drawbacks as long as the burst size does not exceed the minimum access granularity which, for the CPUs that make up the majority of the market, corresponds to a single 512-bit cache line. However, for application-specific accelerators that perform short irregular memory operations (such as in sparse linear algebra or graph processing), prefetching may cause significant data wastage if only a small fraction of each DRAM burst is used. The key insight behind our MOMS is to use as much of each DRAM burst as possible, even in those cases. We do so in a dynamic, transparent, and application-agnostic manner by maintaining a large pool of short accesses and serve as many of them as possible with every DRAM burst returned by the memory.

#### 2.4 Reordering Memory Controllers

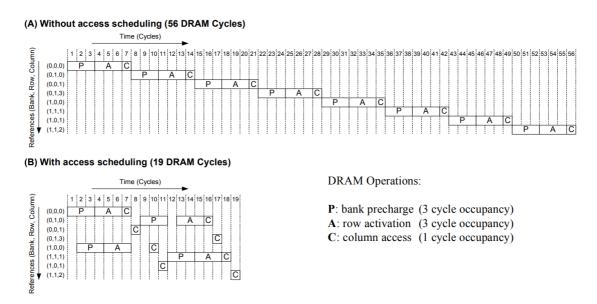

Due to the high complexity of DRAMs, generating a sequence of commands that is both legal and efficient for an arbitrary input memory operation sequence is an active field of research. Rixner et al. [82] first observed that processing memory operations in the same order as they are received is often suboptimal and does not properly exploit bank-level parallelism, as exemplified in Figure 2.4. Their first-ready, first-come, first-serve policy (FR-FCFS) prioritizes ready operations such as column accesses to an active row (row hits) over older operations that would require resources that are not available, such as a bank that is currently being precharged, or that would make some resources idle. FR-FCFS is now a de-facto standard implemented by most DRAM controllers [46], including those used in our experiments [109, 108]. A plethora of other scheduling policies have been proposed [87, 83, 44, 73, 70, 46]; for instance, they try to balance aggregated throughput and fairness in a multi-processor [54] or heterogeneous systems [99] or to maximize bandwidth under real-time latency guarantees [36]. The general-purpose scenarios targeted by those policies must optimize bandwidth together with latency and fairness, which limits queues depth and aggressiveness of reordering. Our MOMS is application-agnostic but targets throughput-oriented systems that can trade more cycles on the miss path and a longer worst-case latency for greater bandwidth through deeper request reordering. In Chapter 4, we propose a mechanism to extend MSHRs to handle multiple consecutive cache lines, which will be requested as a burst. This can be seen as an implicit memory request reordering at

**Figure 2.4** – Example of memory command schedule required to serve the trace shown on the two vertical axis, (A) with strictly in-order operation and (B) with memory command reordering. Reordering memory commands results in a 3× lower latency thanks to a better utilization of the DRAM resources. Reprinted from the publication of Rixner et al. [82].

the granularity of the number of cache lines handled by each MSHR (2–16) but across the tens of thousands of simultaneous misses handled by the MOMS. In Chapter 5, we propose a more explicit policy that groups single requests by DRAM row, effectively implementing a very aggressive row hit-first policy over the thousands of requests naturally exposed by the MOMS.

#### 2.5 Graph Processing

A graph *G* consists of a node or vertex set *V* and an edge set *E* of sizes *N* and *M* respectively. We consider *G* to be a directed graph; undirected graphs can be handled by duplicating each edge. In addition, we focus here on graph algorithms that associate a value to every node and iteratively update them for a fixed number of iterations or until convergence.

Because graphs are the most effective data representation in a wealth of domains, including social networks [59, 81], drug discovery, [95], genomics [17], and robot navigation [16], high-performance graph processing is a very active area of research. While graph problems are usually embarrassingly parallel, the main challenge of graph processing is overcoming the memory bottleneck, which is particularly tight as memory access patterns are often irregular. Indeed, graph processing frameworks typically iterate sequentially over either vertices or edges (and are accordingly called either *vertex-* or *edge-centric*) but access the other set irregularly [28, 29]. In Chapter 7, we show how MOMS can make FPGAs an attractive platform for large-scale graph processing by tackling the memory bandwidth bottleneck with a lightweight preprocessing that has linear complexity with respect to the number of edges. In the remainder of this section, we

review the most representative approaches that have been proposed on CPUs, GPUs, FPGAs, and ASICs.

On CPUs, GraphChi [60] is an out-of-core graph processing system that first introduced the concept of shards to confine random accesses to a smaller range that can be cached in main memory. X-Stream [85] introduced the edge-centric scatter-gather model, where edges are streamed and do not need to be sorted but only partitioned. Frameworks for in-core processing include GraphMat [93], Galois [75], and Totem [34], which also supports hybrid CPU-GPU systems. On a dual-socket Intel Xeon E5-2695 v3 with 28 cores, 240 W TDP, and 136 GB/s of memory bandwidth combined, Aasawat et al. [2] reported 1.3, 1.8, and 9.0 GTEPS for PageRank on RMAT-24 for Galois, GraphMat, and Totem respectively. We achieve 1.8 GTEPS with half the DRAM bandwidth and a  $15 \times$  lower power. Both Galois and Totem only support graphs in CSR format, where edges are sorted by source node. During preprocessing, Totem also sorts edges by vertex degree. Our approach does not need any edge sorting but a faster linear-time partitioning. GPOP [62] is a cache-, work-, and memory-efficient framework that also does not require any edge sorting and achieves significant speedup over Ligra and GraphMat. When running PageRank, SSSP, and SCC on the RV and FR benchmarks presented in Table 7.2, our best architecture is 0.22–5.0× faster and 2.2–49× more energy efficient.

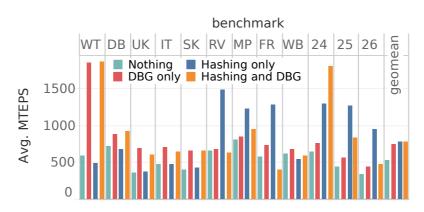

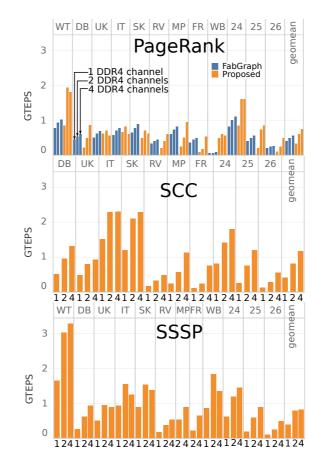

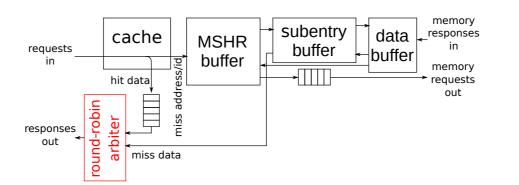

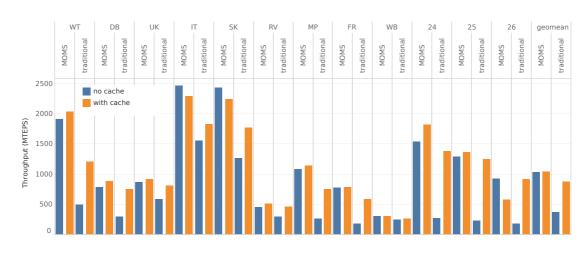

GPUs have a memory bandwidth (and a power budget) that is at least an order of magnitude larger than that of FPGAs; however, it is challenging to fit the irregular workload and memory accesses typical of graphs into the GPU SIMD execution model. One solution, adopted for example by CuSha [53], is to rely on offline preprocessing to balance the workload and group memory accesses, which can constitute a relevant overhead on graphs that are dynamic or used only a few times [69]. While Gunrock [101] shifts this overhead to runtime, Tigr [76] uses a lighter offline preprocessing to convert irregular graphs into equivalent, more regular ones. On a 21M-and a 59M-node graphs, Tigr achieves at most 10% speedup on PageRank compared to Gunrock, which is much lower than the  $1.5-12 \times$  speedup that our system sports against Gunrock on the same application.