## High-Level Synthesis of Dynamically Scheduled Circuits

Présentée le 27 août 2021

Faculté informatique et communications Laboratoire d'architecture des processeurs Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

## Lana JOSIPOVIĆ

Acceptée sur proposition du jury

Prof. B. Falsafi, président du jury

Prof. P. lenne, directeur de thèse

Dr D. Burger, rapporteur

Prof. J. Cong, rapporteur

Prof. J. Cortadella, rapporteur

Prof. G. De Micheli, rapporteur

## Acknowledgments

I would like to express my gratitude to all those who made this thesis possible and who had a significant impact on this great chapter of my life.

First and foremost, I am deeply grateful to my PhD advisor, Paolo Ienne, who introduced me to the world of research and profoundly impacted both my personal and my professional development. His constant feedback, encouragement, and enthusiasm continue to motivate and inspire me to achieve my best. I truly could not have wished for a better mentor to guide me through my PhD journey.

I would like to thank Doug Burger, Jason Cong, Jordi Cortadella, and Giovanni De Micheli for serving on my thesis jury, as well as Babak Falsafi for presiding it. Their insightful comments and questions have significantly improved this thesis. I am also very grateful for the tremendous support and assistance they provided me in defining my future career steps.

I am thankful that I had the opportunity to collaborate and learn from many inspiring and talented people. A very special thanks again to Jordi Cortadella, whose expertise has greatly influenced this thesis and whose continuous support throughout my PhD has enabled me to advance and grow. I had the pleasure of collaborating with George Constantinides, whom I especially thank for his valuable advice and his kind support of my career development. I would also like to extend my gratitude to Steve Neuendorffer for helping me to expand my skills and knowledge, as well as for his friendliness and hospitality during my stay in California.

I thank all the members of the FPGA community that I had the pleasure of meeting and discussing with throughout the years, as well as all my colleagues and friends at Xilinx and Microsoft Research who made my internship experiences unforgettable. I am thankful to all the students and collaborators who contributed to my research and the work described in this thesis.

I was very fortunate to work alongside many current and former LAP members, including Ana, André, Andrea, Andrew, Aya, Chantal, David, Dewmini, Grace, Jovan, Mikhail, Nithin, René, Sahand, and Stefan. I would especially like to thank Andrea for his significant work on Dynamatic, Chantal for helping me survive in French-speaking Switzerland, David for motivating me to pursue a PhD, and Sahand for his constant availability and willingness to help out. Finally, my biggest thanks goes to Grace, whose amazing support, extreme caring, and many hugs made a huge difference in my PhD life.

I am grateful to everyone from EDIC who started the PhD journey with me and stayed close throughout, as well as all the EPFL friends I made along the way, for making my PhD incredibly fun and enjoyable. Special mentions go to Dušan, Helena, and Hermina for making Lausanne feel a bit closer to home, as well as George, Lefteris, and Marios for sharing my skiing enthusiasm and always being up for a day on the slopes. An extra thanks to Lefteris for being a great neighbor and the person that I could always count on. Many thanks to Endri for the weekly coffees and long conversations, as well as to Javier for making TAing surprisingly fun.

Next, I would like to thank all my Croatian friends who enthusiastically cheered me on along the way, including Ami, Dragec, Karla, Kuna, Matea, Petra, Tea, and Tena. I very much appreciate that we managed to stay in touch and that we find time to get together whenever I come home. A very special thanks to Tea and Tena for their lifelong friendship and for being there for me no matter what. Above all, I thank Marko for his endless patience, strong devotion, and continuous encouragement during the past years; I am extremely grateful for having him by my side.

Last, but in no way least, I would like to thank my family: my parents Tatjana and Ivo, and my grandparents Mimi, Zora, and Ante, for enabling me to achieve all my goals with their unconditional love and support.

Lausanne, January 18th, 2021

Lana Josipović

High-Level Synthesis (HLS) tools generate hardware designs from high-level programming languages. These tools almost universally build datapaths that are controlled using a *centralized controller* which relies on a *static, compile-time schedule* to determine the cycle when each operation executes. Such an approach results in high-throughput pipelines in cases where memory accesses *are provably independent* and critical control decisions *are determinable* during code compilation. Unfortunately, when this is not the case, the tools must make pessimistic assumptions, yielding inferior schedules and lower performance. An alternative HLS approach is to create *dataflow circuits* out of high-level code. Dataflow circuits are built out of units which communicate using point-to-point pairs of handshake control signals; data is propagated from unit to unit as soon as memory and control dependences allow it and stalled by the handshaking mechanism otherwise. This distributed control mechanism effectively implements a *dynamic schedule*, where scheduling decisions are made locally in the circuit as it runs, hence achieving behaviors which are beyond the capabilities of statically scheduled circuits.

Although translating high-level code into dataflow circuits seems relatively straightforward, a naive translation is not sufficient to achieve functional correctness, high performance, and area efficiency. Firstly, without appropriate buffer placement and sizing, dataflow circuits exhibit only limited pipelining capabilities. Secondly, in the absence of a static schedule, resource sharing opportunities are difficult to identify; in addition, sharing may cause deadlock and compromise the functionality of the circuit. Thirdly, memory accesses in a dataflow circuit may execute in an order different than the one specified in the original program—a naive memory interface is not always sufficient to guarantee that all memory dependences are honored. Finally, standard dataflow circuits do not support speculation, i.e., the ability to execute some operations before it is certain whether they are correct or required, which prevents pipelining when a memory or a control dependence takes a long time to resolve.

The contribution of this thesis is to develop techniques that make dataflow circuits truly competitive in the HLS context. We first present a complete set of rules and transformations to create dataflow circuits out of high-level specifications (i.e., C/C++ programs). We detail a methodology to systematically place and size buffers in dataflow circuits to achieve high-throughput pipelines. We show how to automatically identify performance-acceptable resource sharing opportunities and describe a sharing mechanism which achieves functionally correct and deadlock-free dataflow designs. We detail the construction of a memory interface (i.e., a load-store queue)

for dataflow circuits that can correctly handle memory accesses arriving out of order and show how to automatically customize this interface to a particular application. Further, we present a generic framework for handling speculation in dataflow circuits. Finally, we show that these techniques can reap significant area/performance benefits in appropriate situations.

All these features enable dataflow circuits to achieve dynamic behaviors similar to those of modern superscalar processors; we believe that these behaviors are key for HLS to be successful in new contexts and broader application domains.

Keywords: high-level synthesis, dataflow circuits, dynamic scheduling.

## Résumé

Des outils de Synthèse de haut-niveau (HLS) peuvent générer des circuits électroniques à partir d'un language de programmation haut-niveau. Ces outils créent quasiment toujours un chemin de données contrôlé à partir d'un controlleur centralisé utilisant un ordonnancement statique connu au temps de compilation pour déterminer le cycle pendant lequel chaque opération s'exécute. Une telle approche permet de créer des pipelines ayant une bande passante élevée dans les cas où les accès à la mémoire sont prouvablement indépendants et que des décisions de contrôle critiques sont déterministiques pendant la compilation du code. Malheureusement, quand ce n'est pas le cas, les outils doivent faire des hypothèses pessimistes, créant ainsi des ordonnancements de plus basse qualité et une performance réduite. Une solution HLS alternative est de créer des circuits dataflow à partir de code de haut niveau. Les circuits dataflow sont conçus à partir d'unités qui communiquent en utilisant des signaux d'établissement de liaison (handshake); les données se propagent d'unité à unité aussitôt que les dépendances de contrôle et de mémoire le permettent, et sont arrêtés par le mechanisme de handshake le cas échéant. Ce mechanisme de contrôle distribué implémente ainsi un ordonnancement dynamique où les décisions d'ordonnancement sont faites de façon local dans le circuit pendant qu'il s'exécute. De tels circuits peuvent ainsi atteindre des comportements qui dépassent les capacités de circuits ordonnancés de façon statique.

Bien que la traduction de code haut-niveau en circuits dataflow est relativement simple, une traduction naïve n'est pas suffisante pour atteindre un fonctionnement correct, une haute performance, ainsi qu'un bon rendement au niveau du surface nécessaire pour concevoir le circuit. Premièrement, sans un bon placement et dimensionnement de mémoires tampon, les circuits dataflow n'auraient qu'une capacité limitée pour être pipeliné. Deuxièement, en l'absence d'un ordonnancement statique, il est difficile de détecter des opportunités pour partager des ressources. De plus, un tel partage de ressources pourrait causer un interblocage et ainsi compromettre la fonctionalité du circuit. Troisièmement, les accès à la mémoire dans un circuit dataflow peuvent s'exécuter dans un ordre différent que celui spécifié dans le programme original — une interface mémoire naïve n'est parfois pas suffisante pour guarantir que toutes les dépendances des accès à la mémoire sont honorées. Finalement, les circuits dataflow standards ne supportent pas de spéculation, c'est à dire la capacité d'exécuter certaines opérations avant qu'il ne soit certain qu'elles soient necessaires, ce qui empêche le pipelining quand une dépendance de donnée ou de contrôle prend du temps à résoudre.

La contribution de cette thèse est de développer des techniques qui permettent aux circuits dataflow d'être véritablement compétitifs dans le contexte de la HLS. Nous présentons en premier un ensemble de règles et de transformations pour créer des circuits dataflow à partir de spécifications de haut-niveau telles que des programmes C/C++. Nous détaillons ensuite une méthodologie pour placer et dimensionner des mémoires tampons dans des circuits dataflow afin de créer des pipelines à bande passante élevée. Nous montrons comment identifier de façon automatique des opportunités de partage de ressources ayant des performances acceptables et décrivons un mécanisme de partage pour créer des circuits dataflow étant fonctionnellement corrects et sans interblocage. Nous détaillons la construction d'une interface mémoire (une *load-store* queue) pour des circuits dataflow qui peut traîter des accès à la mémoire arrivant dans le désordre et montrons comment adapter cette interface à une application spécifique. De plus, nous présentons un cadre générique pour traîter la spéculation dans les circuits dataflow. Finalement, nous montrons que ces techniques permettent de gagner significativement plus de performance et de rendement de surface dans des situations appropriées.

Toutes ces fonctionnalités permettent aux circuits dataflow d'exposer un comportement dynamique similaire à celui des processeurs superscalaires modernes. Nous pensons que ces nouvelles techniques sont la clé pour le succès de la HLS dans de nouveaux contextes ainsi que dans des domaines d'application plus large.

Mots clefs : synthèse de haut-niveau, circuits dataflow, ordonnancement dynamique.

| A  | cknov | wledgments                                              |     |

|----|-------|---------------------------------------------------------|-----|

| Ał | ostra | ct (English/Français)                                   | ii  |

| Li | st of | Figures                                                 | xii |

| Li | st of | Tables                                                  | xvi |

| Li | st of | Algorithms                                              | xvi |

| 1  | Intr  | roduction                                               | ]   |

|    | 1.1   | The Limitations of Today's HLS                          | ]   |

|    | 1.2   | A Completely Different Way to Do HLS                    | 4   |

|    | 1.3   | Computer Architects Have Been There Already             | 5   |

|    | 1.4   | Thesis Contribution                                     | 6   |

| 2  | Dyr   | namically Scheduled High-Level Synthesis                | 7   |

|    | 2.1   | How Does Classic HLS Work?                              | 7   |

|    |       | 2.1.1 Scheduling in HLS                                 | Ç   |

|    | 2.2   | Why Dynamic Scheduling?                                 | 10  |

|    |       | 2.2.1 Dataflow Circuits                                 | 11  |

|    | 2.3   | Synthesizing Dataflow Circuits                          | 12  |

|    |       | 2.3.1 Dataflow Units                                    | 12  |

|    |       | 2.3.2 Implementing Control Flow                         | 14  |

|    |       | 2.3.3 Ensuring Determinism                              | 17  |

|    |       | 2.3.4 Constructing the Datapath                         | 19  |

|    | 2.4   | The Challenges of Dynamic Scheduling                    | 20  |

|    |       | 2.4.1 Achieving High-Performance Pipelines              | 20  |

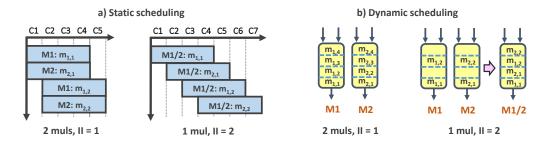

|    |       | 2.4.2 Saving Resources through Sharing                  | 21  |

|    |       | 2.4.3 Introducing Out-of-Order Memory to HLS            | 22  |

|    |       | 2.4.4 Minimizing the Complexity of the Memory Interface | 23  |

|    |       | 2.4.5 Enabling General Speculative Execution            | 25  |

|    |       | 2.4.6 A Complete HLS Methodology                        | 26  |

| 3 | Buf | fer Plac | ement and Sizing for High-Performance Dataflow Circuits | 27 |

|---|-----|----------|---------------------------------------------------------|----|

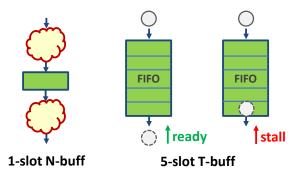

|   | 3.1 | Buffer   | s in Dataflow Circuits                                  | 27 |

|   |     | 3.1.1    | Buffer Properties                                       | 27 |

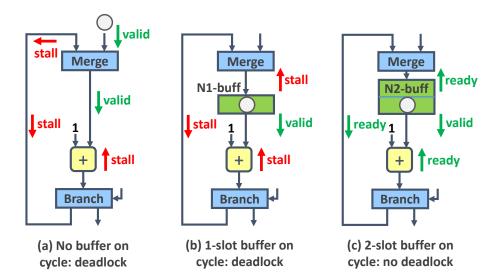

|   |     | 3.1.2    | Buffers and Circuit Functionality                       | 28 |

|   |     | 3.1.3    | Buffers and Avoiding Deadlock                           | 28 |

|   |     | 3.1.4    | Buffers and Performance                                 | 29 |

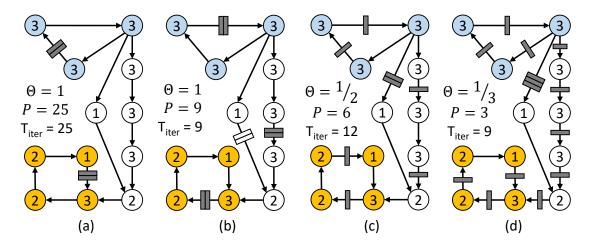

|   | 3.2 | Model    | ing Dataflow Circuits as Marked Graphs                  | 31 |

|   |     | 3.2.1    | Marked Graphs                                           | 31 |

|   |     | 3.2.2    | Key Intuition                                           | 32 |

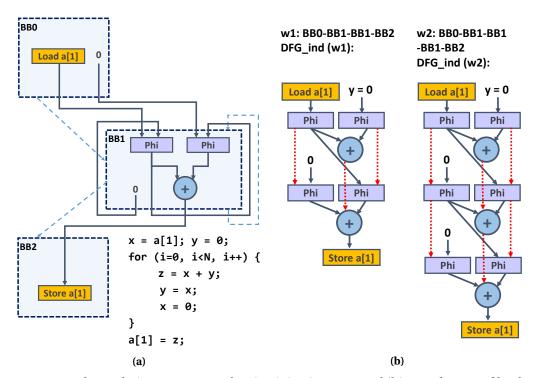

|   | 3.3 | Optim    | izing Performance                                       | 32 |

|   |     | 3.3.1    | Extracting Choice-Free Dataflow Circuits                | 32 |

|   |     | 3.3.2    | Optimizing Choice-Free Circuits                         | 35 |

|   |     | 3.3.3    | MILP Model for Performance Optimization                 | 36 |

|   |     | 3.3.4    | Optimizing Multiple CFDFCs                              | 39 |

|   | 3.4 | Model    | ing Computational Units and If-Conversion               | 41 |

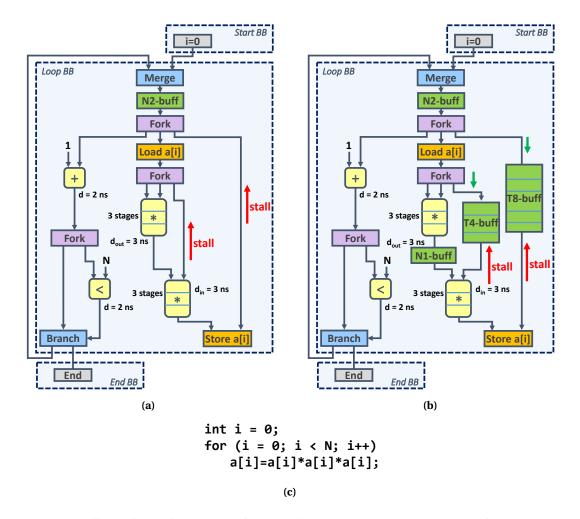

|   |     | 3.4.1    | Modeling Pipelined Units                                | 41 |

|   |     | 3.4.2    | Modeling Variable Initiation Interval                   | 42 |

|   |     | 3.4.3    | Modeling Variable Latency                               | 43 |

|   |     | 3.4.4    | Modeling If-Conversion                                  | 44 |

|   | 3.5 | Scalab   | oility                                                  | 46 |

|   | 3.6 | Evalua   | ntion                                                   | 47 |

|   |     | 3.6.1    | Methodology                                             | 47 |

|   |     | 3.6.2    | Benchmarks                                              | 48 |

|   |     | 3.6.3    | Comparison with Naive Buffer Placement                  | 49 |

|   |     | 3.6.4    | MILP Runtime Analysis                                   | 51 |

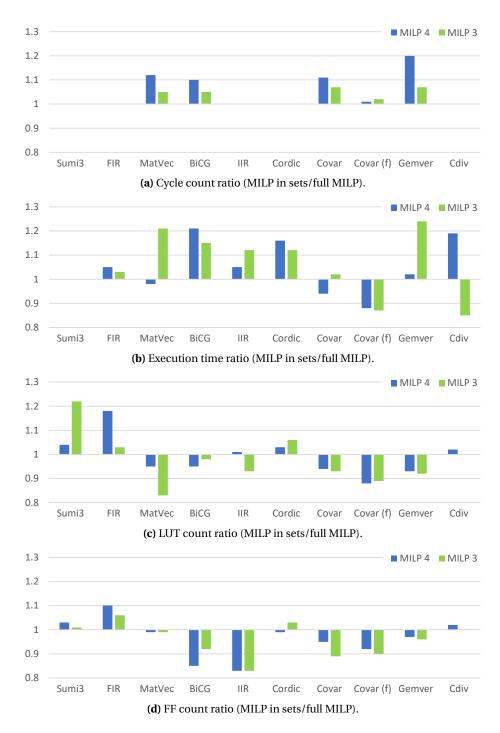

|   |     | 3.6.5    | Comparison of MILP Solutions                            | 52 |

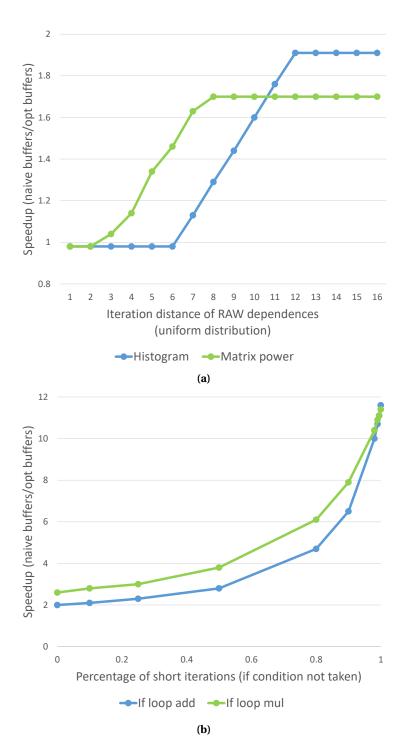

|   |     | 3.6.6    | Variable Latency, II, and If-Conversion                 | 55 |

|   |     | 3.6.7    | Effectiveness of the CP Constraint                      | 57 |

|   | 3.7 | Conclu   | usions                                                  | 58 |

| 4 | Res | ource S  | haring in Dataflow Circuits                             | 59 |

|   | 4.1 | Motiva   | ation                                                   | 59 |

|   | 4.2 | Decidi   | ing What to Share in a Dataflow Circuit                 | 61 |

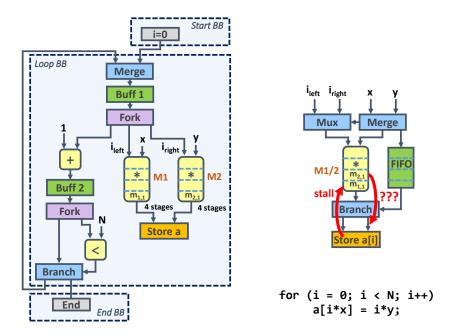

|   | 4.3 | Resou    | rce Sharing in Dataflow Circuits                        | 62 |

|   |     | 4.3.1    | Sharing in Straight Datapaths                           | 62 |

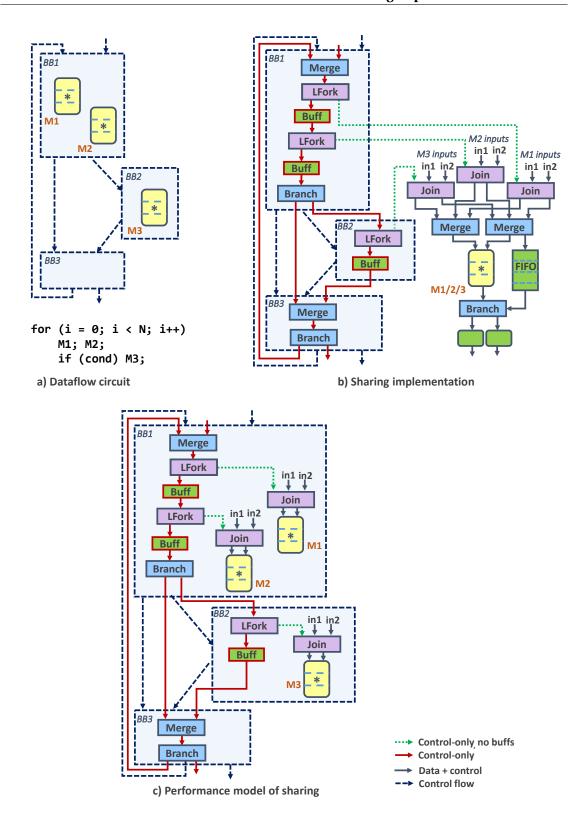

|   |     | 4.3.2    | Sharing in General Datapaths                            | 63 |

|   |     | 4.3.3    | Sharing and Performance                                 | 64 |

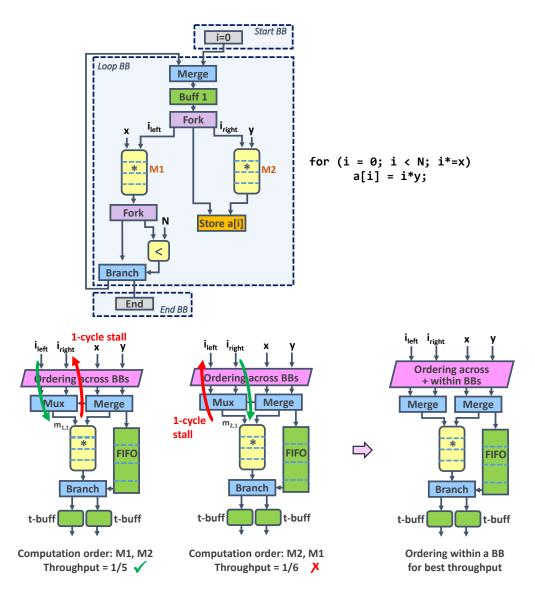

|   |     | 4.3.4    | Extending the Ordering Scheme                           | 66 |

|   | 4.4 | Orderi   | ing Implementation and Model                            | 68 |

|   |     | 4.4.1    | Implementation                                          | 68 |

|   |     | 4.4.2    | Sharing Model for Performance Analysis                  | 68 |

|   |     | 113      | Ontimized Implementation                                | 70 |

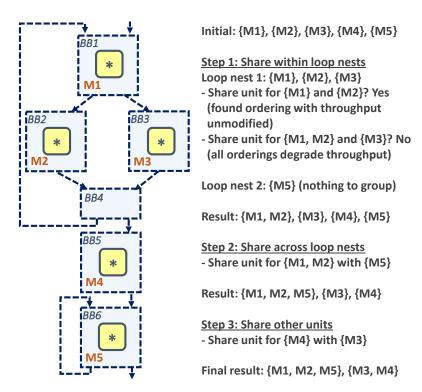

|   | 4.5  | Putting It All Together                              | 72  |

|---|------|------------------------------------------------------|-----|

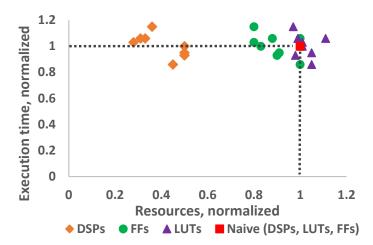

|   | 4.6  | Evaluation                                           | 74  |

|   |      | 4.6.1 Methodology and Benchmarks                     | 74  |

|   |      | 4.6.2 Results: Effectiveness of the Sharing Strategy | 75  |

|   |      | 4.6.3 Results: Comparison with Static HLS            | 77  |

|   | 4.7  | Conclusions                                          | 79  |

| 5 | An ( | Out-of-Order Load-Store Queue for Spatial Computing  | 81  |

|   | 5.1  | Inadequacy of Processor Load-Store Queues            | 81  |

|   | 5.2  | Supplying a Sequential Order to the LSQ              | 85  |

|   | 5.3  | Our Allocation Strategy                              | 86  |

|   | 5.4  | LSQ Implementation                                   | 89  |

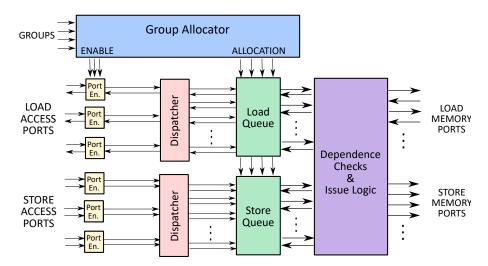

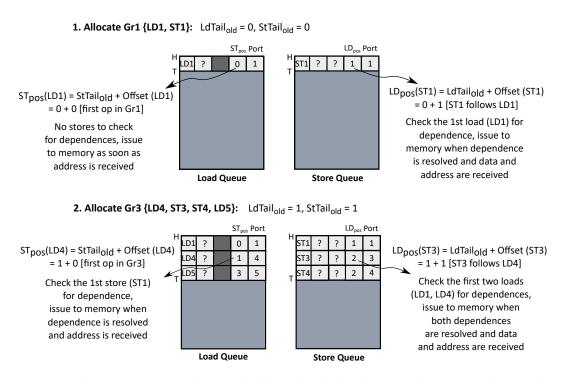

|   |      | 5.4.1 The Queues and the Overall Structure           | 90  |

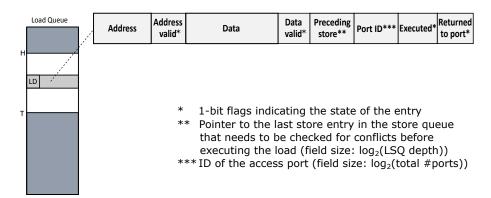

|   |      | 5.4.2 Group Allocator                                | 91  |

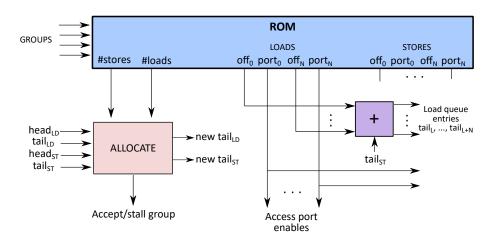

|   |      | 5.4.3 Access Port Enable and Dispatchers             | 93  |

|   |      | 5.4.4 Checking Dependences and Executing             | 94  |

|   | 5.5  | Connecting the Dataflow Circuit to the LSQ           | 94  |

|   | 5.6  | Evaluation                                           | 96  |

|   |      | 5.6.1 Resource Utilization and Timing Analysis       | 97  |

|   |      | 5.6.2 Benchmark Evaluation                           | 98  |

|   | 5.7  | Conclusions                                          | 101 |

| 6 | Min  | nimizing the Use of LSQs in Dataflow Designs         | 103 |

|   | 6.1  | Motivation                                           | 103 |

|   | 6.2  | Background                                           | 105 |

|   |      | 6.2.1 Alias Analysis                                 | 105 |

|   |      | 6.2.2 Polyhedral Analysis                            | 105 |

|   | 6.3  | Memory Interface Optimizations                       | 106 |

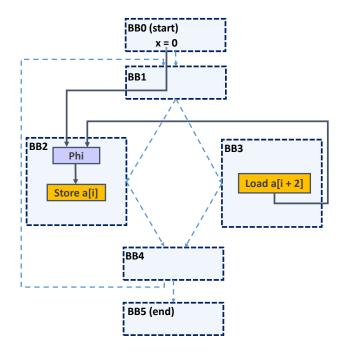

|   |      | 6.3.1 The Ordering Problem                           | 106 |

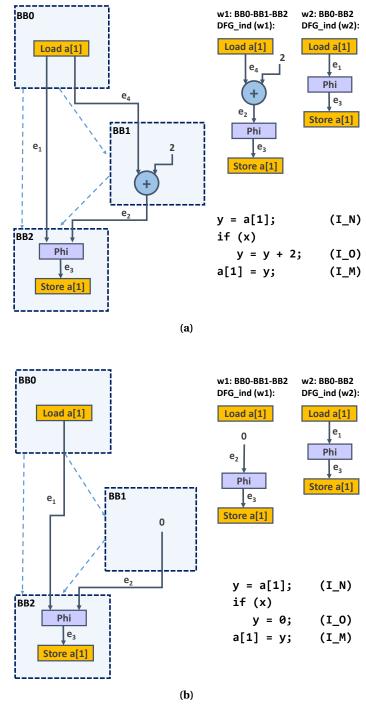

|   |      | 6.3.2 Exploiting Data Dependences                    | 107 |

|   |      | 6.3.3 Global Instruction Dependence                  | 108 |

|   |      | 6.3.4 From Two Memory Instructions to Many           | 109 |

|   |      | 6.3.5 Why Not CFG Dominance?                         | 112 |

|   |      | 6.3.6 Another Ordering Guarantee                     | 113 |

|   |      | 6.3.7 How Long a Walk Does One Need?                 | 114 |

|   | 6.4  | Evaluation                                           | 115 |

|   |      | 6.4.1 Memory Analysis Implementation                 | 115 |

|   |      | 6.4.2 Experimental Methodology                       | 115 |

|   |      | 6.4.3 Benchmarks                                     | 116 |

|   |      | 6.4.4 Results                                        | 117 |

|   | 6.5  | Conclusions                                          | 119 |

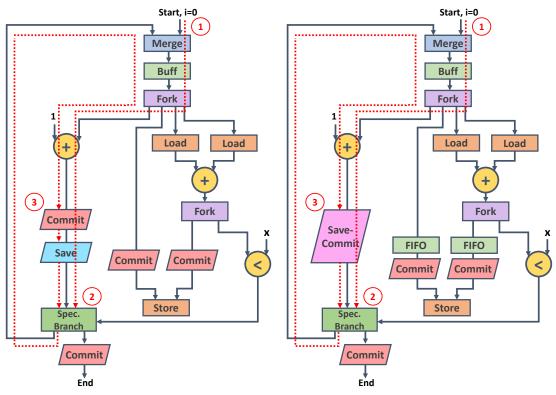

| 7  | Spe  | culative Dataflow Circuits                              | 121 |

|----|------|---------------------------------------------------------|-----|

|    | 7.1  | Why HLS Needs Speculative Behavior                      | 121 |

|    | 7.2  | Speculation in Dataflow Circuits                        | 122 |

|    | 7.3  | Units for Speculation                                   | 125 |

|    |      | 7.3.1 Speculator                                        | 125 |

|    |      | 7.3.2 Commit Unit                                       | 126 |

|    |      | 7.3.3 Save Unit                                         | 127 |

|    | 7.4  | Placing the Units                                       | 128 |

|    | 7.5  | Connecting the Units                                    | 130 |

|    |      | 7.5.1 Connecting the Speculator to the Commit Unit      | 130 |

|    |      | 7.5.2 Connecting the Speculator to the Save Unit        | 131 |

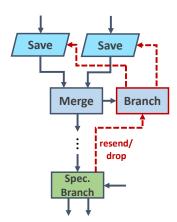

|    | 7.6  | Multiple Speculations from a Single Speculator          | 131 |

|    |      | 7.6.1 Merging the Save and Commit Unit                  | 132 |

|    |      | 7.6.2 Connecting the Speculator to the Save-Commit Unit | 134 |

|    | 7.7  | Speculations from Multiple Speculators                  | 134 |

|    | 7.8  | Evaluation                                              | 134 |

|    |      | 7.8.1 Benchmarks                                        | 135 |

|    |      | 7.8.2 Results                                           | 135 |

|    |      | 7.8.3 Analysis                                          | 137 |

|    | 7.9  | Conclusions                                             | 138 |

| 8  | Rela | ated Work                                               | 139 |

|    | 8.1  | High-Level Synthesis                                    | 139 |

|    | 8.2  | Dynamic Scheduling in HLS                               | 140 |

|    | 8.3  | Performance Optimizations of Dataflow Circuits          |     |

|    | 8.4  | Resource Optimizations of Dataflow Circuits             | 143 |

|    | 8.5  | Speculation in Dataflow Circuits                        | 144 |

|    | 8.6  | Computer Architecture                                   | 144 |

| 9  | A Co | omplete Flow                                            | 147 |

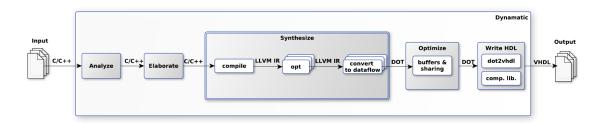

|    |      | Dynamatic HLS Compiler                                  | 147 |

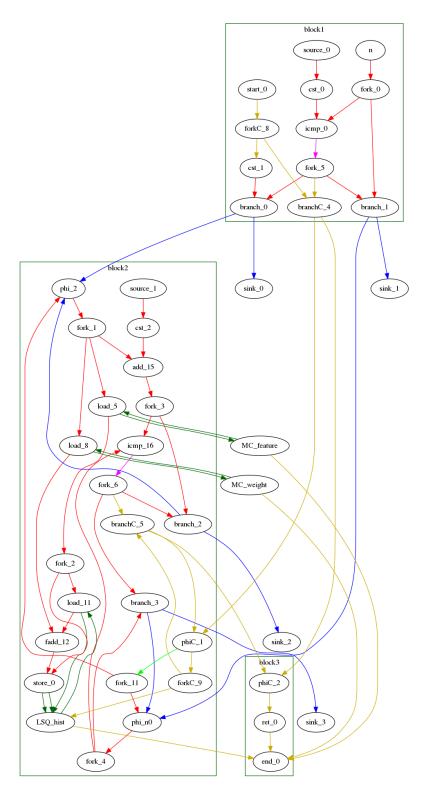

|    |      | 9.1.1 DOT Intermediate Representation                   | 148 |

|    |      | 9.1.2 VHDL Output                                       | 148 |

|    |      | 9.1.3 Functional Verification                           | 150 |

|    | 9.2  | Evaluation                                              | 150 |

|    |      | 9.2.1 Methodology                                       | 151 |

|    |      | 9.2.2 Benchmarks                                        | 151 |

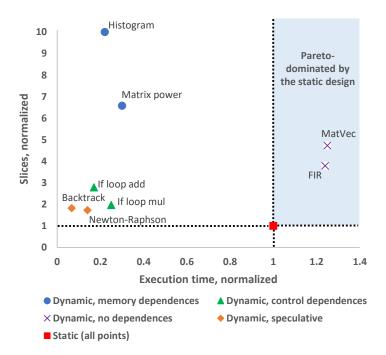

|    |      | 9.2.3 Comparison with Static HLS                        | 152 |

|    |      | 9.2.4 Conclusions                                       | 154 |

| 10 | New  | v Avenues for Dynamic Scheduling                        | 155 |

| -  |      | Application Domains for Dynamically Scheduled HLS       | 155 |

|    |      | Reducing the Costs of Dynamically Scheduled HIS         | 156 |

| Curriculum Vitae                                       | 110   |

|--------------------------------------------------------|-------|

| Bibliography                                           | 176   |

| 10.4 Final Remarks                                     | . 165 |

| 10.3.4 Formal Verification                             |       |

| 10.3.3 Hardware Compilers and Dataflow Representations |       |

| 10.3.2 Reconfigurable Dataflow Architectures           | . 163 |

| 10.3.1 Multithreaded Execution                         | . 162 |

| 10.3 Perspectives                                      | . 162 |

| 10.2.4 Partial Schedule Rigidification                 | . 160 |

| 10.2.3 Memory Interface Simplifications                | . 159 |

| 10.2.2 Backend-Aware Transformations                   | . 158 |

| 10.2.1 Dataflow Graph Optimizations                    |       |

# List of Figures

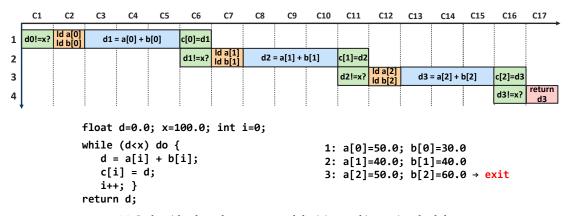

| 1.1  | Limitations of standard HLS                                                           | 3  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | A statically and a dynamically scheduled circuit                                      | 4  |

| 1.3  | Thesis contribution                                                                   | 6  |

| 2.1  | Design space exploration with static HLS                                              | 8  |

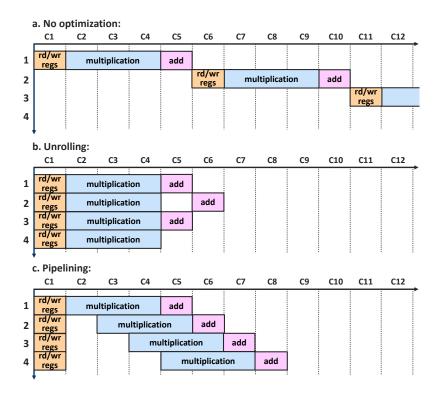

| 2.2  | The schedules of the three design points from Figure 2.1                              | 9  |

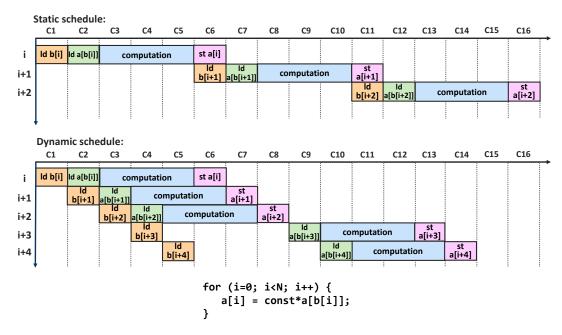

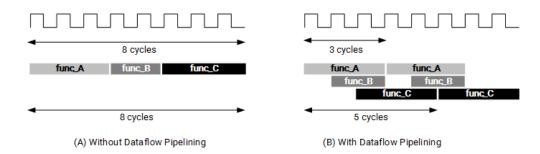

| 2.3  | Static vs. dynamic scheduling.                                                        | 10 |

| 2.4  | A dynamically scheduled, dataflow circuit                                             | 12 |

| 2.5  | Dataflow units                                                                        | 13 |

| 2.6  | Implementing control flow                                                             | 15 |

| 2.7  | Nondeterministic behavior at SSA <i>phi</i> nodes                                     | 17 |

| 2.8  | Ensuring determinism                                                                  | 18 |

| 2.9  | Triggering constants                                                                  | 19 |

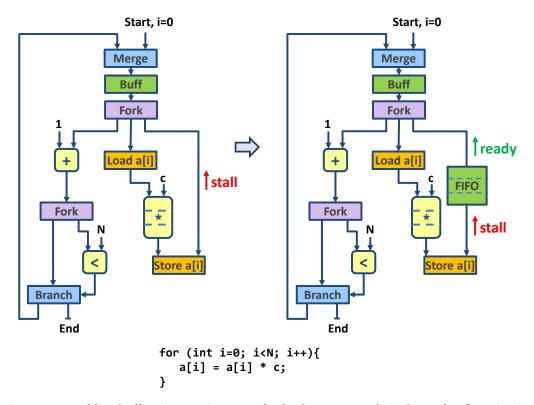

| 2.10 | Adding buffers (i.e., FIFOs) to resolve backpressure and pipeline a dataflow circuit. | 21 |

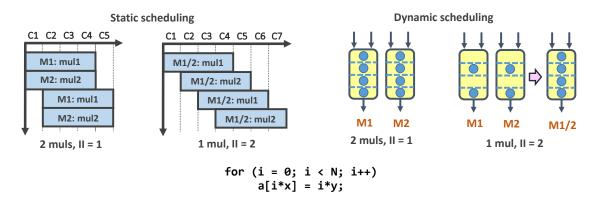

| 2.11 | Resource sharing in static and dynamic scheduling                                     | 22 |

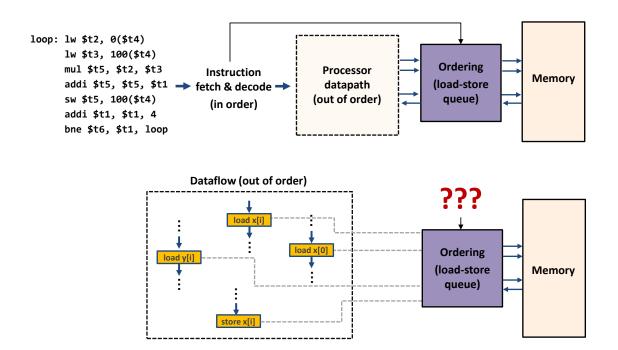

| 2.12 | Conveying program order to the memory interface                                       | 23 |

| 2.13 | Connecting a dataflow circuit to memory                                               | 24 |

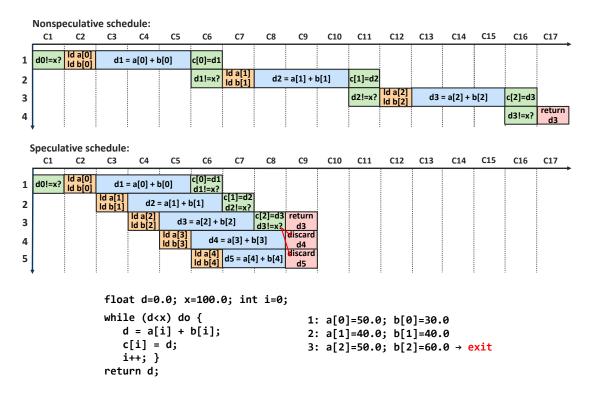

| 2.14 | Nonspeculative and speculative schedule for the code in the figure, repeating the     |    |

|      | situation from Figure 1.1c.                                                           | 25 |

| 3.1  | Buffer properties                                                                     | 28 |

| 3.2  | Adding buffers                                                                        | 29 |

| 3.3  | Buffering for performance                                                             | 30 |

| 3.4  | A choice-free dataflow circuit, which has the properties of a marked graph            | 31 |

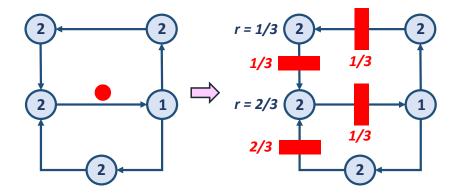

| 3.5  | Extracting CFG cycles                                                                 | 33 |

| 3.6  | Obtaining a choice-free dataflow circuit (CFDFC) from a dataflow circuit              | 34 |

| 3.7  | Performance optimization of a choice-free dataflow circuit                            | 35 |

| 3.8  | Path constraints of the MILP model                                                    | 37 |

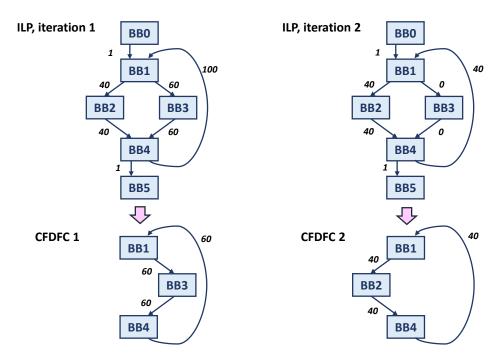

| 3.9  | Token retiming with throughput and path constraints for $P \le 3$                     | 39 |

| 3.10 | Extracting multiple CFDFCs                                                            | 40 |

| 3.11 | A model of a sequential (pipelined) unit                                              | 41 |

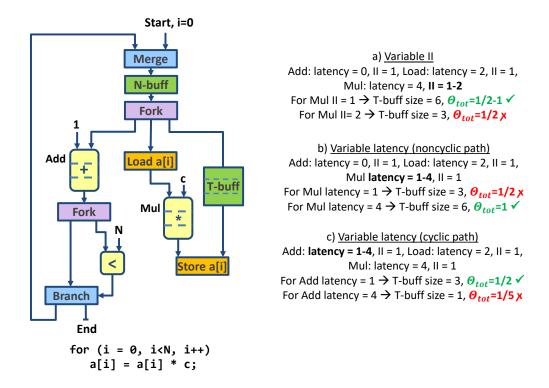

| 3.12 | Modeling variable II and variable latency                                             | 43 |

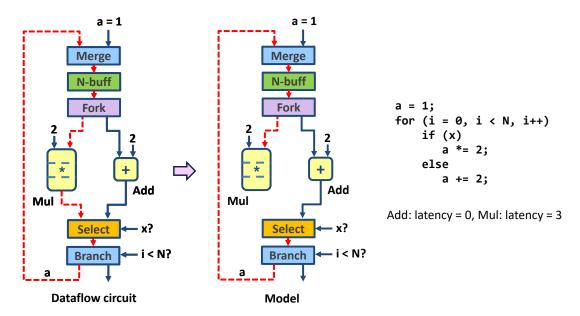

| 3.13 | Modeling if-conversion, implemented using a select unit                               | 45 |

## **List of Figures**

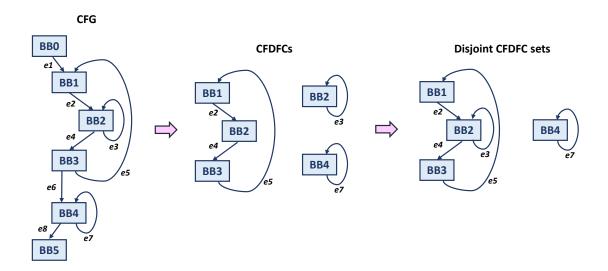

|      | Splitting the circuit into disjoint CFDFC sets to ensure MILP scalability                                   | 46         |

|------|-------------------------------------------------------------------------------------------------------------|------------|

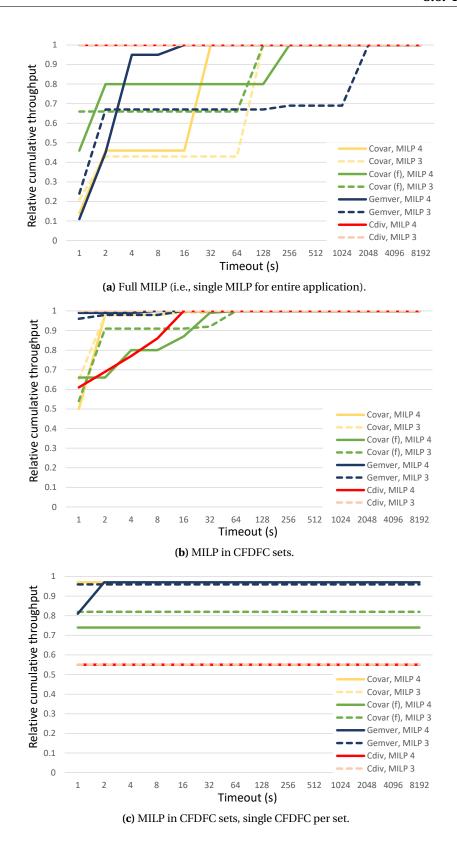

| 3.15 | Runtime comparison of the full MILP with the MILP applied on individual CFDFC                               | <b>5</b> 2 |

| 3.16 | sets                                                                                                        | 53         |

|      | with the optimal MILP solutions.                                                                            | 54         |

| 3.17 | Speedup of the optimized kernels with respect to the naive kernels for varying data and control dependences | 56         |

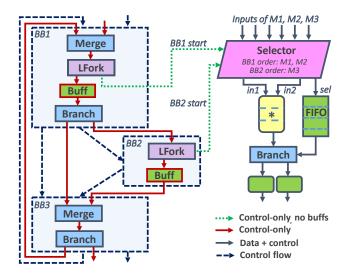

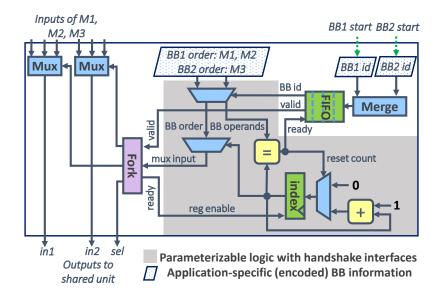

| 4.1  | Dataflow circuit and a possible implementation of resource sharing                                          | 60         |

| 4.2  | Resource sharing in static and dynamic scheduling                                                           | 61         |

| 4.3  | Hardware for sharing                                                                                        | 63         |

| 4.4  | Deadlock situations                                                                                         | 65         |

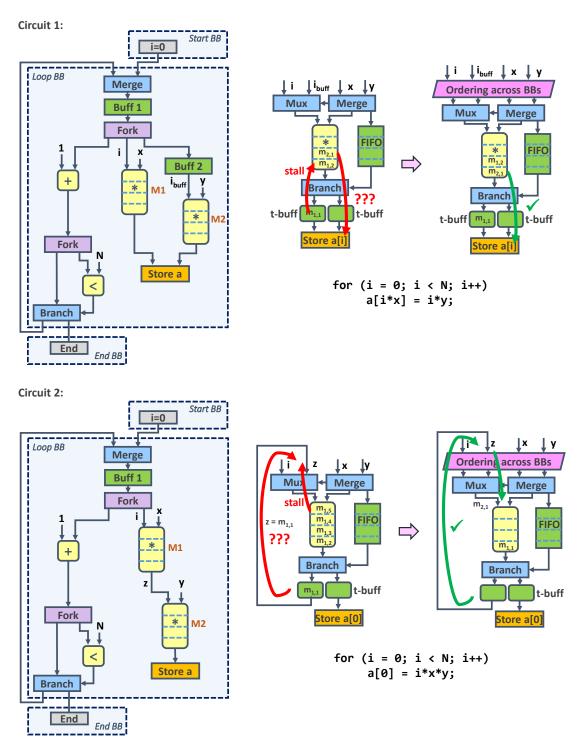

| 4.5  | Performance impact of sharing.                                                                              | 67         |

| 4.6  | Sharing implementation and model                                                                            | 69         |

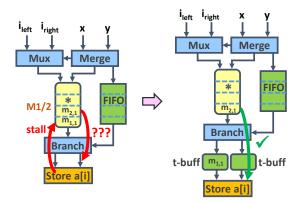

| 4.7  | Optimized sharing implementation                                                                            | 70         |

| 4.8  | Implementation of the selector unit                                                                         | 71         |

| 4.9  | Example execution of our sharing strategy                                                                   | 74         |

| 4.10 | Execution time and resources of dataflow circuits with sharing, normalized to the                           |            |

|      | designs without sharing                                                                                     | 76         |

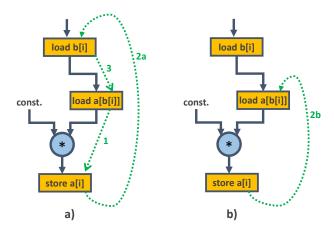

| 5.1  | A schedule created by an HLS tool unable to disambiguate dependences, compared                              |            |

|      | to a dynamic schedule possible with a dataflow approach                                                     | 82         |

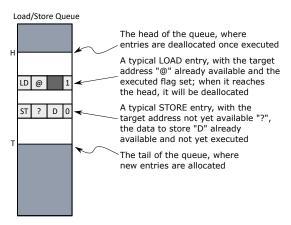

| 5.2  | A typical processor LSQ with head and tail pointers and two sample entries                                  | 83         |

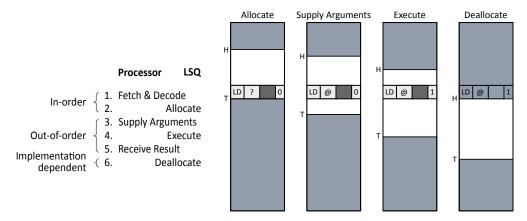

| 5.3  | The basic operation of an LSQ in an out-of-order processor                                                  | 83         |

| 5.4  | A partial dataflow graph derived from the code of Figure 5.1                                                | 84         |

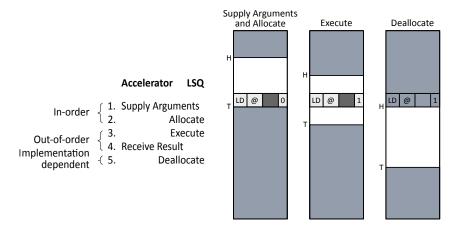

| 5.5  | Allocating entries when the arguments are supplied to the LSQ                                               | 85         |

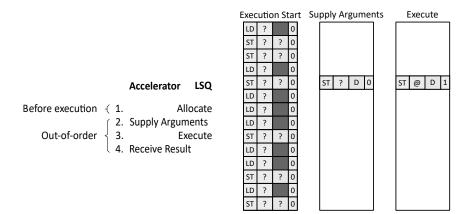

| 5.6  | Allocating entries statically before execution                                                              | 86         |

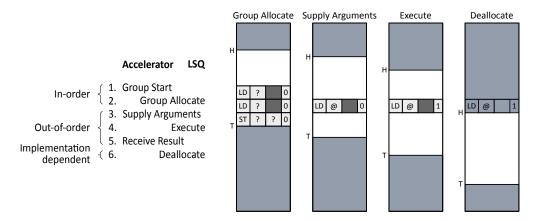

| 5.7  | Allocating entries by groups.                                                                               | 87         |

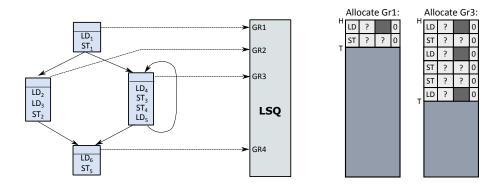

| 5.8  | A program with memory accesses divided into groups which are connected to the                               |            |

|      | LSQ                                                                                                         | 88         |

| 5.9  | Overall structure of the LSQ                                                                                | 90         |

| 5.10 | Detailed load queue entry of the LSQ                                                                        | 91         |

| 5.11 | Group allocator                                                                                             | 92         |

| 5.12 | Allocating groups to the LSQ                                                                                | 93         |

| 5.13 | Connecting the dataflow circuit to the memory interface                                                     | 95         |

| 5.14 | Execution time and resource utilization of the Vivado HLS designs compared to                               |            |

|      | the dynamically scheduled designs with the LSQ in different sizes                                           | 100        |

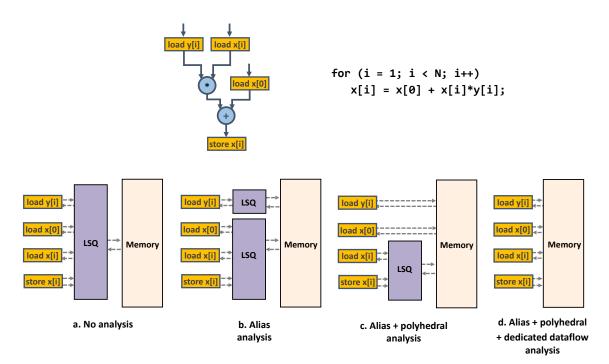

| 6.1  | Memory interface configurations of a dataflow circuit                                                       | 104        |

| 6.2  | Memory traces of two programs with a single load and a single store instruction.                            | 106        |

| 6.3  | Two (out of many) possible memory traces of the code in the figure                                          | 108        |

| 6.4  | Code snippets and their control/data flow graphs which we use to illustrate the                             |            |

|      | global instruction dependence property in Section 6.3.3                                                     | 110        |

| 6.5  | Control/data flow graph of the example in Figure 6.3                              | 112 |

|------|-----------------------------------------------------------------------------------|-----|

| 6.6  | Another ordering guarantee                                                        | 113 |

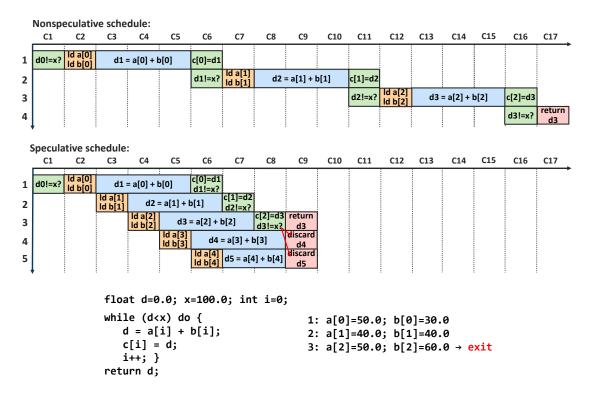

| 7.1  | A nonspeculative schedule, compared to a schedule produced by a system sup-       |     |

|      | porting speculative behavior                                                      | 122 |

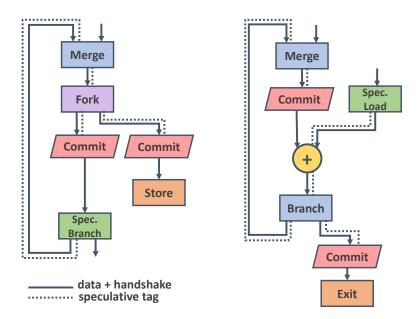

| 7.2  | A dataflow circuit executing the code of Figure 7.1                               | 123 |

| 7.3  | A region of a dataflow circuit implementing our speculative execution paradigm.   | 124 |

| 7.4  | Branch speculator                                                                 | 126 |

| 7.5  | Components for speculation                                                        | 127 |

| 7.6  | Placing commit units                                                              | 128 |

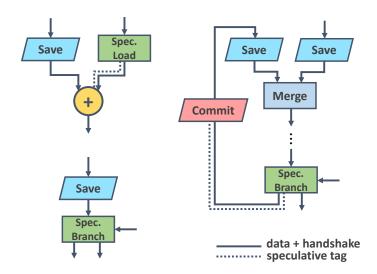

| 7.7  | Placing save units                                                                | 129 |

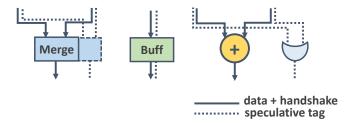

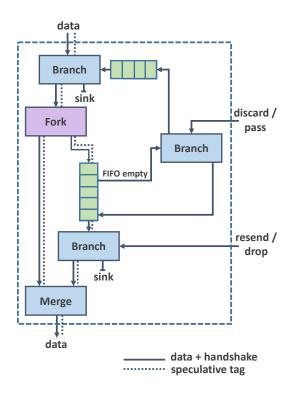

| 7.8  | Extending dataflow units with a speculative tag                                   | 130 |

| 7.9  | Connecting the speculator to the commit units                                     | 130 |

| 7.10 | Connecting the speculator to the save units                                       | 131 |

| 7.11 | Enabling multiple speculations from a single speculator in the example from       |     |

|      | Figure 7.2                                                                        | 132 |

| 7.12 | The structure of the save-commit unit                                             | 133 |

| 7.13 | Code used for the analysis of Section 7.8.3, qualitatively similar to the Newton- |     |

|      | Raphson benchmark                                                                 | 137 |

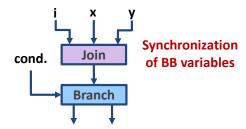

| 8.1  | BB variable synchronization by Huang et al                                        | 140 |

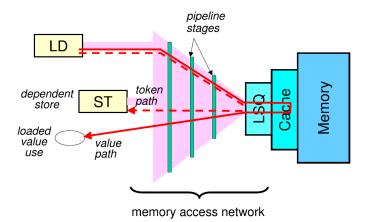

| 8.2  | Memory access synchronization by Budiu et al                                      | 141 |

| 8.3  | Dataflow optimization in Vivado HLS                                               | 142 |

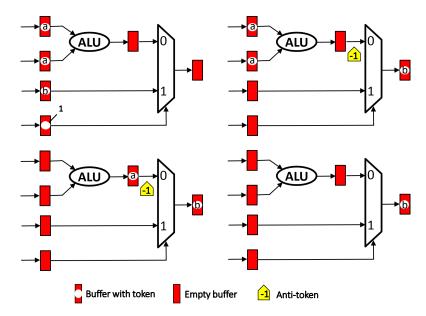

| 8.4  | Early evaluation with anti-tokens in elastic systems                              | 144 |

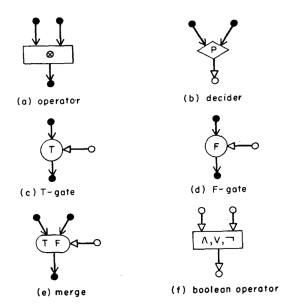

| 8.5  | Actor primitives of a dataflow processor.                                         | 145 |

| 9.1  | Dynamatic HLS compiler: software-to-hardware flow                                 | 148 |

| 9.2  | Intermediate representation of a dataflow circuit in Dynamatic                    | 149 |

| 9.3  | Snippet of the intermediate representation of the dataflow circuit in DOT format. | 150 |

| 9.4  | Resource utilization and execution time of the dynamically scheduled designs,     |     |

|      | normalized to the corresponding static designs produced by Vivado HLS. $$         | 154 |

| 10.1 | Dataflow circuit optimizations                                                    | 157 |

| 10.2 | Limitation of our static timing analysis                                          | 158 |

|      | Memory optimization opportunities                                                 | 159 |

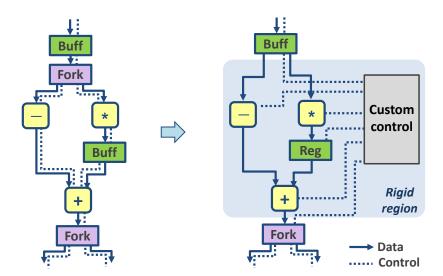

|      | Dataflow circuit rigidification.                                                  | 161 |

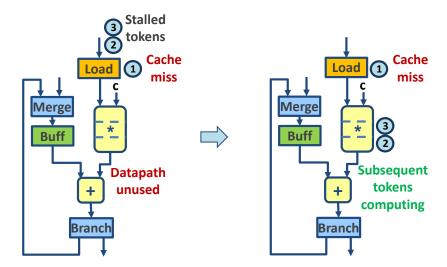

|      | Multithreaded execution                                                           | 162 |

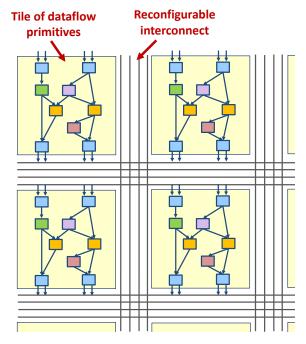

| 10.6 | A reconfigurable dataflow array.                                                  | 163 |

## **List of Tables**

| 3.1 | Benchmark characteristics                                                                                 | 49  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Timing comparison of naive and optimized dataflow circuits                                                | 50  |

| 3.3 | Resource comparison of naive and optimized dataflow circuits                                              | 51  |

| 3.4 | Timing and resources of kernels which contain computational units with variable                           |     |

|     | latency and II, as well as if-conversion                                                                  | 55  |

| 3.5 | Exploration of the effectiveness of the clock period (CP) constraint on a tree of                         |     |

|     | combinational adders                                                                                      | 58  |

| 4.1 | Resources of dataflow circuits without sharing (i.e., Naive) and with sharing (i.e.,                      |     |

|     | Shared), after place-and-route with Vivado.                                                               | 75  |

| 4.2 | Timing of dataflow circuits without sharing (i.e., <i>Naive</i> ) and with sharing (i.e., <i>Shared</i> ) | 76  |

| 4.3 | Resources of circuits produced by Vivado HLS (i.e., <i>Static</i> ) and dataflow circuits                 |     |

|     | with sharing (i.e., <i>Shared</i> )                                                                       | 77  |

| 4.4 | Timing of circuits produced by Vivado HLS (i.e., <i>Static</i> ) and dataflow circuits with               |     |

|     | sharing (i.e., <i>Shared</i> )                                                                            | 78  |

| 5.1 | Comparison of different entry allocation options                                                          | 87  |

| 5.2 | LSQ clock period (CP) and resource utilization for different numbers of groups. $$ .                      | 96  |

| 5.3 | LSQ clock period (CP) and resource utilization for different numbers of ports. $$ . $$ .                  | 97  |

| 5.4 | LSQ clock period (CP) and resource utilization for different queue depths                                 | 98  |

| 6.1 | Memory access patterns of our benchmarks                                                                  | 116 |

| 6.2 | Memory optimization comparison, timing results                                                            | 117 |

| 6.3 | Memory optimization comparison, resource utilization                                                      | 118 |

| 7.1 | Timing and resource requirements of static, dynamic, and speculative circuits                             | 136 |

| 7.2 | Timing and resource requirements of the loop from Figure 7.13                                             | 138 |

| 9.1 | Timing comparison of dynamically scheduled circuits (our dataflow circuits) and                           |     |

|     | statically scheduled circuits (Vivado HLS)                                                                | 152 |

| 9.2 | Resource comparison of dynamically scheduled circuits (our dataflow circuits)                             |     |

|     | and statically scheduled circuits (Vivado HLS)                                                            | 153 |

## **List of Algorithms**

| 2.1 | Implementing control flow                                  | 16 |

|-----|------------------------------------------------------------|----|

| 3.1 | Performance optimization                                   | 48 |

| 4.1 | Sharing strategy                                           | 73 |

| 6.1 | Memory optimization based on global instruction dependence | 11 |

## Introduction

The slowdown in transistor scaling and the end of Moore's law signal a clear need to invest in new computing paradigms [105]. Specialized hardware devices, such as Field Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs), are a promising solution to achieve high processing capabilities and energy efficiency; recently, these devices have been customized for large-scale AI applications [78, 49], integrated into datacenters to accelerate massive data [23, 3], and packaged with processors for high parallelism [29]. However, a major barrier to the global success of specialized computing is the difficulty of hardware design. High-Level Synthesis (HLS) tools can generate hardware designs from high-level programming languages and should liberate designers from the details of hardware description languages like VHDL and Verilog. Despite their progress and some commercial success in the last decade, HLS tools still tend to be criticized for the difficulty of extracting the desired level of performance: generating good circuits from high-level languages still requires peculiar code restructuring, expert user interaction, and extensive experimentation with the tools [72]. Moreover, current HLS techniques face a fundamental issue when handling irregular applications: because they rely on static scheduling, i.e., the cycle in which each operation executes is fixed at compile time [47], they force worst-case assumptions on memory and control dependences. Therefore, HLS tools are still usable only by designers with hardware expertise and acceptable only for some classes of applications. If specialized computing is to play a key role in dealing with the increasing computational demands in the post-Moore era, it is imperative that hardware design becomes accessible to a variety of users from different application domains.

## 1.1 The Limitations of Today's HLS

Circuits produced by HLS tools are typically built out of datapaths that are controlled using a preplanned, central controller. The controller relies on a static schedule, fixed at compile time, to determine the clock cycle when each operation can execute. Such an approach is effective in regular code where compile-time information is sufficient to obtain a high-throughput, pipelined schedule. However, when the code contains unpredictable memory or control de-

pendences, long-latency control decisions, or variable-latency events, the tool must make pessimistic assumptions, yielding inferior schedules and lower performance.

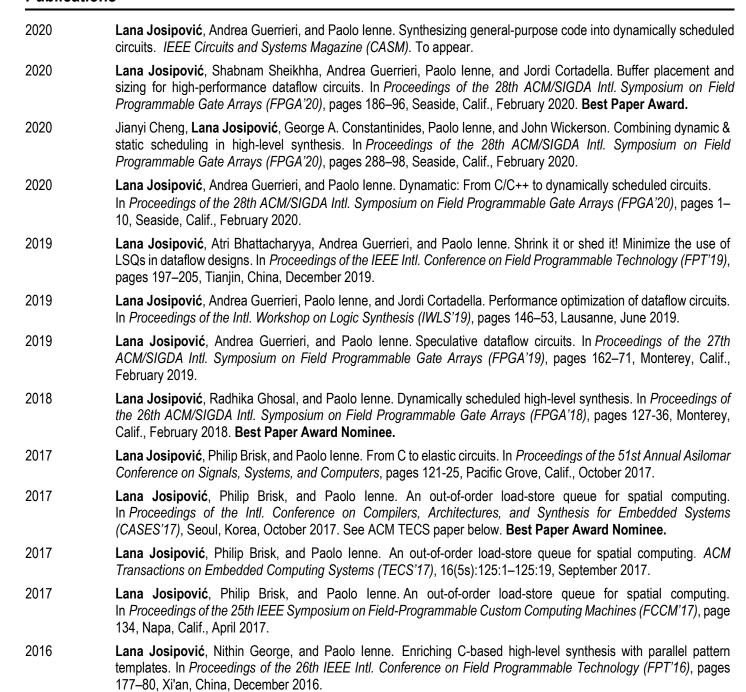

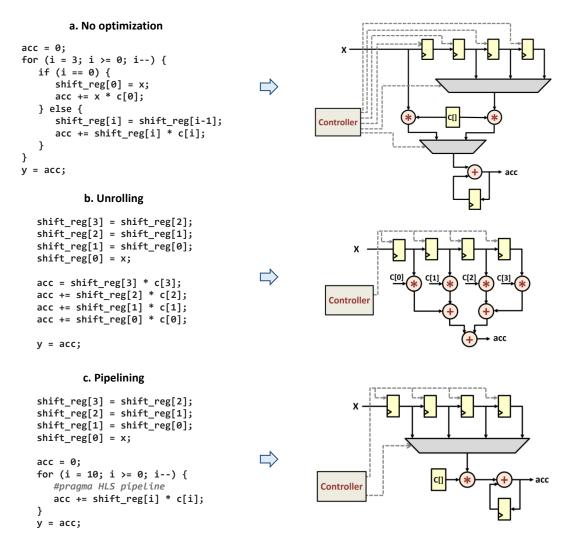

**Unpredictable memory dependences.** The example in Figure 1.1a illustrates the behavior of standard HLS approaches when memory access patterns cannot be determined at compile time. In this loop, there is a *possible* read-after-write dependence between the memory read of hist[x[i+1]] and the memory write to hist[x[i]] of the previous iteration. There is intrinsically no way a compiler or an HLS tool can determine whether such a dependence exists, nor is it, in general, possible for a programmer to help the tool: in practice, the read may seldom or even never address the same value just written in memory, but there is no way to exclude a priori that this might happen. Ultimately, any HLS technique based on static scheduling hits the problem of potential dependences and needs to account for the worst-case scenario, irrespective of the actual data fetched from memory. The result is a conservative schedule, valid for any possible input values, which assumes a dependence in every loop iteration and postpones the read until the previous, possibly dependent write has been completed [70].

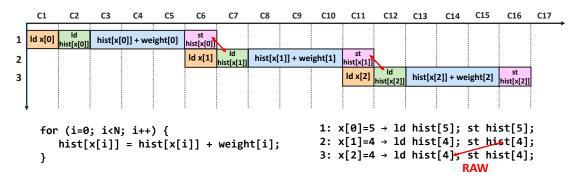

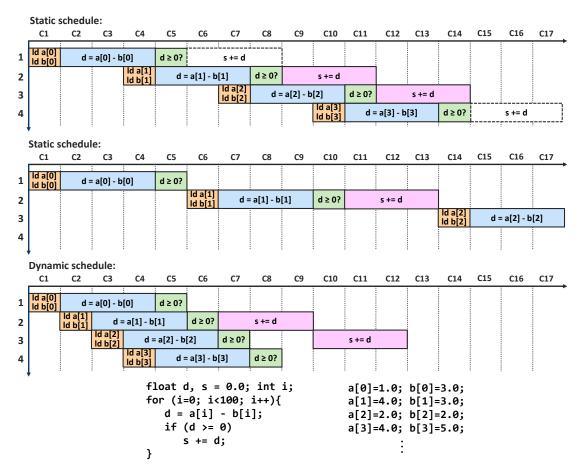

**Unpredictable control flow.** A similar issue occurs in the presence of unpredictable control flow. The loop in Figure 1.1b has a control flow decision (if) which depends on the actual data being read from arrays a[] and b[]. The operation which might take place in a specific iteration (s += d) introduces a dependence between iterations and delays the next iteration whenever the condition is true. When pipelining this loop, a typical HLS tool needs to create a conservative execution plan for the various operations in the loop which is valid in every possible case. The resulting schedule is shown in the figure: although the condition is true only for the second and third iteration, a "space" is reserved in the schedule as if the condition were true everywhere, hence limiting the pipelining of the loop.

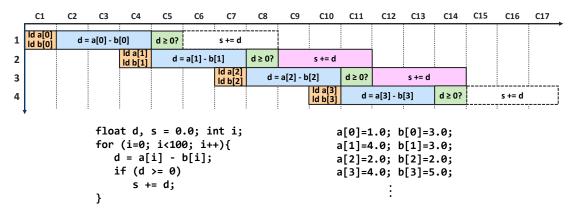

**Long-latency control flow decisions.** Although static scheduling supports predication and if-conversion, these techniques are not applicable to every performance-critical control decision and are limited in the presence of memory accesses or complex control flow. A simple example is illustrated in Figure 1.1c: the condition on the loop continuation takes multiple cycles to compute and a new loop iteration can start only after this condition has been determined, hence completely preventing loop pipelining. This conservatism is due to the limited ability of a static schedule to adapt to different outcomes and to revert the state in case of a failed prediction.

Variable-latency events. Standard HLS techniques suffer in the presence of variable-latency operations or memory accesses: a typical example is that of data accesses from an external shared memory, where latencies may vary due to memory system hierarchy or system-level contentions. In such situations, static HLS techniques typically need to stall the complete pipeline when a long-latency event (e.g., a cache miss) occurs; alternatively, they resort to adding excessive pipeline stages to accommodate for the worst-case delay [108]. These performance- and area-degrading solutions are a clear artifact of the inability of static scheduling to accommodate dynamic events.

(a) Code with memory dependences undeterminable at compile time and its static schedule.

(b) Code with control flow undeterminable at compile time and its static schedule.

$\mbox{(c)}$  Code with a long-latency control decision and its static schedule.

**Figure 1.1** – Limitations of standard HLS. In the presence of unpredictable memory accesses, control flow, or long-latency control flow decisions, static HLS tools create a conservative schedule, resulting in lower performance.

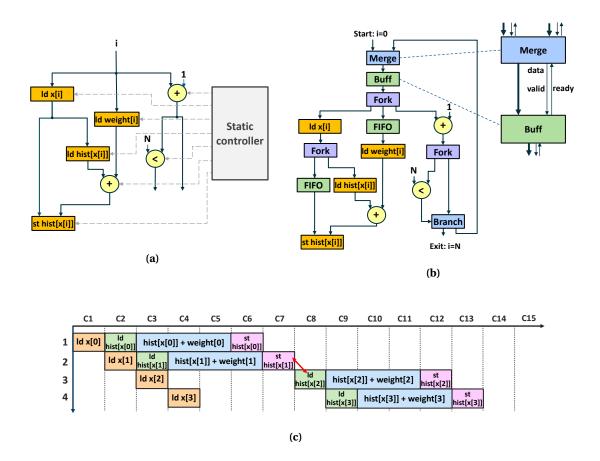

**Figure 1.2** – A statically (Figure 1.2a) and a dynamically (Figure 1.2b) scheduled circuit. The static circuit has a preplanned controller which determines the time when each operation will execute; it implements the conservative schedule from Figure 1.1a. In contrast, the dynamically scheduled circuit contains a distributed control system which enables decision-making at runtime and offers greater flexibility and performance, achieving the schedule in Figure 1.2c.

## 1.2 A Completely Different Way to Do HLS

The key to avoid the limitations of static scheduling is to refrain from triggering the operations through a centralized preplanned controller (Figure 1.2a), but to make scheduling decisions locally in the circuit as it runs: as soon as all conditions for execution are satisfied (e.g., the operands are available or critical control decisions are resolved), an operation starts. *Dataflow circuits* [37] are a natural method to realize such behavior. Such circuits are built out of units that implement *latency-insensitivity* by communicating with their predecessors and successors through point-to-point pairs of handshake control signals, which indicate the availability of a new piece of data from the source unit and the readiness of the target unit to accept it (Figure 1.2b). The data is propagated from unit to unit as soon as memory and control dependences allow it—otherwise, the handshaking mechanism stalls the data on-the-fly. This distributed control mechanism effectively implements a *dynamic schedule*, such as the one in Figure 1.2c:

when a read-after-write dependence exists (in this case, between the second and the third iteration) the dynamically scheduled circuit will stall the pipeline to prevent a hazard. Otherwise, in the absence of an address collision, it will start a new iteration on every cycle and gain, in this case, up to a factor 5 in performance. Similar dynamic behaviors are achievable in the other situations from Figure 1.1—we will discuss them in the following chapters. These behaviors are beyond what classic static techniques can achieve.

## 1.3 Computer Architects Have Been There Already

The contrast between static and dynamic scheduling in HLS is in line with the experience in computer architecture with *Very Long Instruction Processors* (VLIWs) and *superscalar out-of-order* processors [64].

In VLIWs, the problem of deciding when instructions can be executed is left completely to the compiler: the hardware simply fetches at once and executes groups of operations which can be performed together. The program is effectively a schedule computed statically by the compiler, exactly as in the case of statically scheduled HLS. In contrast, superscalar processors rely on complex mechanisms to achieve out-of-order behavior: *reservation stations* hold back fetched and decoded instructions until all of their operands are available; while some instructions are delayed due to a memory dependence or a cache miss, others can execute. Thanks to the *reorder buffer*, these processors can execute instructions speculatively when the outcome of a preceding branch is unknown or the existence of a memory dependence has not yet been ascertained. As with dynamically scheduled HLS, there is no schedule planned in advance: the schedule develops dynamically as operands become available.

While complex compilation techniques have been developed for VLIWs to exploit instruction-level parallelism (often requiring either complex heuristics to drive the optimization or pragmas from the programmers), dynamically scheduled out-of-order processors are capable of achieving good levels of parallelism on-the-fly and without extensive code preparation. In fact, many of the key transformations to exploit fine-grain parallelism between operators in statically scheduled HLS derive from VLIW compilation techniques [82, 103]. Exactly as VLIWs, statically scheduled HLS suffers when handling code with irregular memory or control dependences; they are primarily successful in markets with extremely regular and predictable applications and where it is acceptable to tune code manually.

The dichotomy in computer architecture may tell us something about the future of dynamically scheduled HLS. With FPGAs moving to datacenters and facing broader application classes, HLS tools might have to satisfy the needs of general-purpose markets as well. Apart from the advantage of exploiting parallelism in cases where static scheduling cannot, the ability of dynamic scheduling to find an acceptable solution without the programmer's help may be critical in a future where HLS will not be driven by hardware designers (available to study the generated circuits and to restructure the input code) but by higher-level code generation tools (e.g., Delite [52]) and, ultimately, by software programmers.

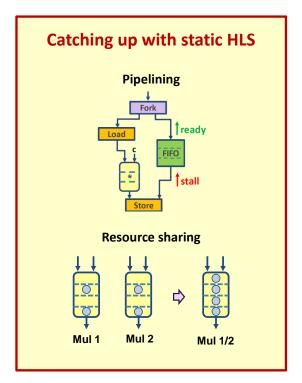

**Figure 1.3** – Thesis contribution. We first describe optimizations which make dataflow circuits competitive with static HLS circuits (i.e., pipelining and resource sharing); then, we implement behaviors which are beyond the capabilities of classic HLS tools (i.e., out-of-order memory accesses and speculation).

## 1.4 Thesis Contribution

In this thesis, we pursue a form of HLS which produces dynamically scheduled, dataflow circuits out of high-level code. However, a straightforward translation is not sufficient to obtain circuits which are truly competitive and useful in the HLS context. The main contribution of this thesis, outlined in Figure 1.3, is to enhance dataflow circuits with the capabilities which are beyond those achievable by naively obtained dataflow circuits and existing HLS techniques. We first describe methodologies to exploit the same optimization opportunities that standard HLS relies on (i.e., pipelining and resource sharing), hence achieving circuits competitive to those created with standard HLS techniques. We then use the properties of dataflow circuits to achieve characteristics that standard HLS cannot support (i.e., out-of-order memory access execution and speculation). The resulting behaviors are similar to those of modern superscalar processors and achieve solutions which are, in particular cases, superior to statically scheduled HLS circuits: similarly to the tradeoff between VLIW processors and superscalars, the performance of demanding applications is very significantly improved at an affordable cost.

## 2

# Dynamically Scheduled High-Level Synthesis

In this chapter, we discuss standard scheduling techniques and we explore in detail an example of a situation where dynamic extraction of operation-level parallelism proves essential for performance. We then present our methodology to automatically generate dynamically scheduled circuits from C code. Our approach borrows several ideas from the asynchronous domain, but produces perfectly synchronous designs which are directly comparable to standard HLS techniques. We conclude this chapter with a summary of challenges in achieving high-performance, area-efficient dataflow circuits and highlight the features that we will explore in the following chapters.

### 2.1 How Does Classic HLS Work?

Hardware description languages (HDLs), such as VHDL and Verilog, have been used in the electronic design industry for decades to specify the details of hardware design in terms of low-level building blocks such as gates, registers, and multiplexers [8]. However, this description level requires hardware expertise and, typically, a longer time to develop the design. High-level synthesis tools allow designers to work at a higher level of abstraction by using a software language to specify the hardware functionality. This approach enables software engineers to program hardware and helps hardware engineers to speed up the design process as well as to efficiently explore the design space [92]. Although HLS can benefit both ASIC and FPGA designers, HLS tools are particularly gaining popularity in the FPGA domain, as the programming challenges are one of the biggest barriers to the mainstream adoption of these devices [8, 33].

Different HLS tools rely on various high-level representations to describe the underlying hardware; the most popular ones use C/C++ as an input language [119, 18]. Generally speaking, the user provides the input functional specification and particular design constraints such as the target device, desired clock frequency, and memory interface description; the tool then automatically analyzes concurrency, inserts registers to achieve the specified frequency, generates

This chapter is based on the work published at the 26th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, 2018 [73].

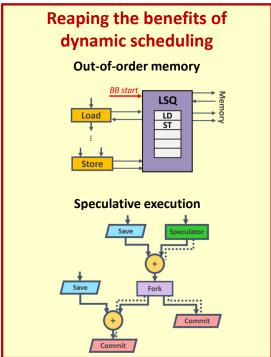

**Figure 2.1** – Design space exploration with static HLS [80]. All three codes in the figure describe the same functionality (i.e., an FIR filter); yet, the resulting HLS solutions differ in area and performance.

the control and datapath logic, and maps data onto storage elements to optimize the bandwidth and resource usage [80]. The user is typically required to restructure the code and annotate it with pragmas to guide the tool in reaching the desired design point.

Figure 2.1 illustrates several possibilities to specify the functionality of a simple FIR filter in C code as well as the resulting circuits produced by an HLS tool [80]; apart from the different datapaths, as shown in the figure, each design has a kernel-specific controller which triggers the datapath components at appropriate clock cycles; we will discuss this functionality in the following section. The first circuit is obtained from a typical software representation, without any hardware-specific annotations or code restructuring. The second code is manually unrolled to explicitly express available parallelism to the HLS tool—as the corresponding circuit suggests, this design will employ multiple operators which can be used concurrently. The third design point uses a pragma to indicate to the tool that the code should be pipelined, i.e., the loop

Figure 2.2 - The schedules of the three design points from Figure 2.1.

iterations should overlap for performance benefits. It is evident from the figure that the circuits differ in the number of employed resources (i.e., adders, multipliers, multiplexers); they also differ in performance, as we will discuss next.

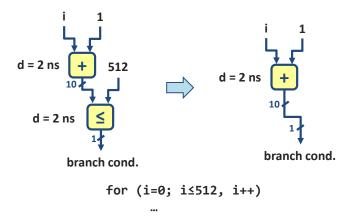

### 2.1.1 Scheduling in HLS

HLS relies on a series of compiler optimizations to achieve performance- and area-efficient designs; some techniques are exploited by compilers in general (e.g., code motion, if-conversion), whereas others are hardware-specific (e.g., bitwidth analysis, operation chaining). One of the key algorithms in HLS synthesis is *scheduling*, i.e., deciding the clock cycle in which each operation will execute. It is typically achieved through *systems of difference constraints* (SDC) modeling which incorporates a variety of constraints, such as resource usage, data dependences, control dependences, and clock frequency [17, 34, 120].

The three schedules in Figure 2.2 correspond to the circuits in Figure 2.1. The schedule of each design is regulated by the controller; it implements a *finite state machine* (FSM) which controls the behavior of the datapath by triggering operations, enabling registers, and multiplexing values in appropriate clock cycles. The first schedule corresponds to the sequential execution of the software code: one iteration starts after the previous one has completed. The code restructuring in the second figure enables operations to execute in parallel, hence lowering the execution time, but with the investment of additional resources. The third circuit employs loop pipelining:

**Figure 2.3** – Static vs. dynamic scheduling. The top and middle schedule (realized as a pipeline and a sequential state machine, respectively) are possible with standard HLS tools. A dynamic schedule (bottom) is achievable with our approach; it results in the best possible parallelism which is reduced only in the presence of actual loop-carried dependences.

a new loop iteration starts on every clock cycle and the resource requirements are minimal (i.e., new data is inserted into the single adder and the single multiplier on every cycle).

Loop pipelining is one of the key performance optimizations in HLS—as the example above suggests, it allows loop iterations to overlap in the best possible manner while honoring all data and control dependences of the program. The technique originates from software pipelining techniques for VLIWs, which rely on modulo scheduling algorithms to exploit instruction-level parallelism among successive loop iterations [82, 103]. A pipeline is characterized by its *initiation interval* (II), i.e, the number of clock cycles between consecutive loop iterations; the ideal II is equal to 1, as is the case for the pipelined schedule in the figure.

## 2.2 Why Dynamic Scheduling?

To illustrate the need to incorporate dynamic behavior into HLS, we revisit in Figure 2.3 the example from Figure 1.1b.

As described before, this loop has a control flow decision (i f) which depends on the actual data being read from arrays a [] and b []. Whenever the condition is true, a long-latency operation (s += d) introduces a dependence between iterations. A typical HLS tool needs to conservatively reserve a "space" in the schedule for this operation, even when it does not occur, as shown on the top of Figure 2.3. An alternative could be to avoid pipelining the loop and creating a sequential finite-state machine to achieve the middle schedule in Figure 2.3, where indeed cycles are spent for the addition only when needed; however, the decision of not pipelining the loop has removed one of the foremost potentials for parallelism (in this case, the memory reads, the subtraction, and the comparison are perfectly independent across iterations and could be pipelined).

Obviously, a good schedule is the bottom one in Figure 2.3: the operations of different iterations are overlapped as much as possible and the parallelism is reduced only when the dependence is actually there (that is, when the addition is executed). Such behavior is beyond what a statically scheduled HLS tool can achieve. In recent years, many authors explored workarounds for such problems—we will discuss these efforts in Chapter 8—but dynamically scheduled circuits represent the most general solution to the problem.

#### 2.2.1 Dataflow Circuits

Dataflow or latency-insensitive circuits [19, 37, 116, 45] realize the dynamic behavior in Figure 2.3. These circuits are built out of units which communicate using pairs of handshake control signals; data is propagated from unit to unit as soon as memory and control dependences allow it and, otherwise, stalled by the handshaking mechanism.

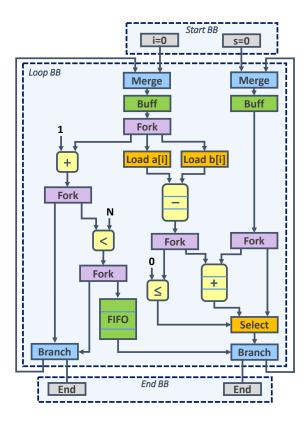

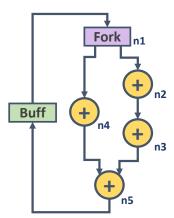

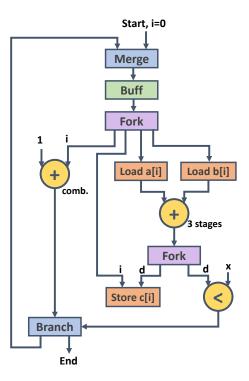

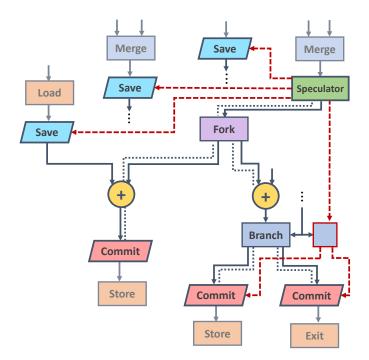

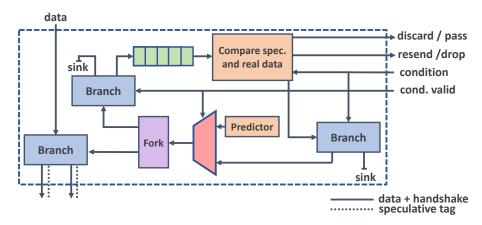

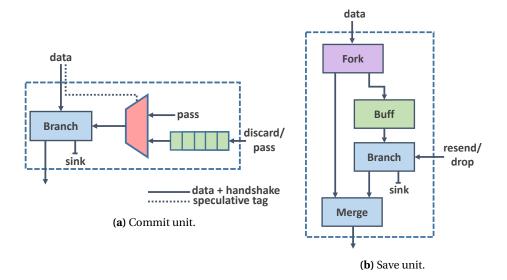

Figure 2.4 shows a simplified version of a dataflow circuit implementing the loop of Figure 2.3. Besides normal datapath units, this circuit uses a few control units labeled buff, merge, select, fork, and branch. All directed edges in the figure represent data signals accompanied by handshake control signals. The loop to the left of the figure shows the part of the circuit which updates the iterator i: At the beginning, the constant 0 is sent from the entry point. The merge unit takes this value and passes it further. The buffer unit is the register which holds i and distributes it on the next clock cycle to three consumers through the fork unit; all successors must consume the value before the fork accepts a new input value. The left branch compares the incremented i with the loop bound; if the bound is not reached, the new value of i is sent back to the register by the branch unit through the merge. Meanwhile, the other outputs of the first fork use i to access a [i] and b [i] and to compute the subtraction, which is propagated to the rest of the circuit.

The key to a good execution of this loop is that, ideally, a new value of i should be used to start computing a[i] - b[i] on every cycle. This is the case in this circuit, contrary to a conservative statically scheduled one: The cycle on the left of Figure 2.4 is completely combinational excluding the buffer and thus a new value for i can be computed on every cycle. It is the right part of the circuit which can delay this: when the if is not taken, the result of the

**Figure 2.4** – A dynamically scheduled, dataflow circuit. This circuit implements the code from Figure 2.3 and achieves the optimal execution schedule (bottom schedule in that figure).

addition is dumped by the select unit as soon as it arrives through the merge and the old value of s becomes immediately the new value that is sent back to the adder on the following cycle; if, on the other hand, the result is needed, the select will wait for the sum to complete and the adder will be stalled next cycle waiting for its right operand. Ultimately, a new subtraction will not be computed and the memory accesses will not be performed due to backpressure from the adder; the top fork will not allow a new i to proceed on the right branch. This slows down the initiation of the loop and is exactly what the dynamic schedule in Figure 2.3 shows.

## 2.3 Synthesizing Dataflow Circuits

In this section, we detail our methodology to convert an arbitrary piece of code into a dataflow circuit. We first present the dataflow units we use; we then show how we implement control flow, ensure deterministic behavior, and construct the datapaths of our circuits.

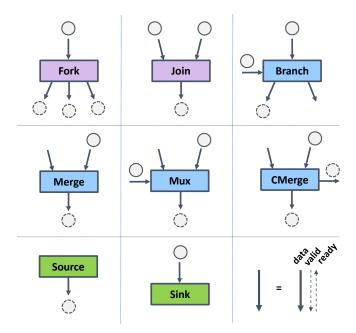

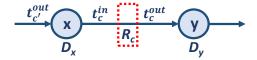

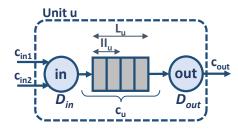

#### 2.3.1 Dataflow Units

Dataflow circuits are built out of *units* that implement latency-insensitivity by communicating with their predecessors and successors through *channels* composed of data lines and paired with handshake control signals: a *valid* signal indicates that a unit is sending a valid piece of data,

**Figure 2.5** – Dataflow units. All data channels are paired with bidirectional control signals, which indicate the validity of data and the readiness of the successor unit to accept it.

referred to as a *token* [90], to its successor(s), whereas the *ready* signal informs the predecessor(s) that a unit can accept a new piece of data.

Figure 2.5 outlines the dataflow units we use; their gate-level descriptions can be found in literature [67, 37].

- An *eager fork (fork)* replicates every token received at the input to multiple outputs; as soon as one successor is ready to accept the token, the fork sends it to the successor; however, the fork can accept a new token only after all successors have accepted the previous one.

- A *lazy fork (lfork)* has the same functionality as the eager fork; however, it distributes a token to all successors at once (i.e., all successors must be ready for the lazy fork to send the token).

- A *join* acts as a synchronizer—its output is triggered only after all of its inputs become available.

- A *branch* implements program control-flow statements; it dispatches a token received at its single input to one of its multiple outputs based on a condition.

- A *merge* is a nondeterministic unit which propagates a token received on any of its input to its single output.

- A *mux* is a deterministic version of the merge; it propagates to its single output the input token selected by a control input.

- A *control merge (cmerge)* is a merge which, apart from the data output, has an output which indicates which of the inputs was taken by the merge.

- A *source* can always issue a valid token to its single successor (e.g., a constant).

• A *sink* is always ready to consume tokens from its single predecessor; the token is simply discarded in the sink.

In addition, we use any functional unit the code requires, such as integer and floating-point units. Units that require multiple operands contain a join to trigger the operation only when all inputs are available. Our circuits will require *buffers* which serve as registers in standard synchronous designs—we will discuss their properties and placement in Chapter 3. Finally, our circuits will interface to memory using read and write ports, yet, interfacing to memory is challenging due to the out-of-order nature of our system; we will address this issue in Chapter 5.

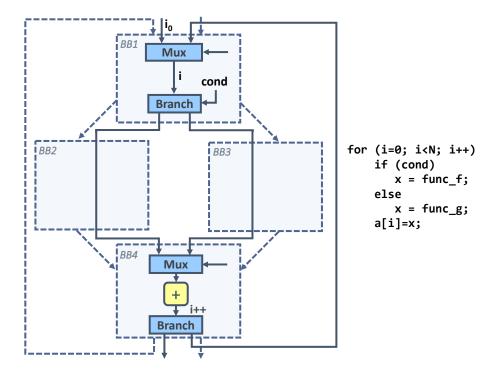

#### 2.3.2 Implementing Control Flow

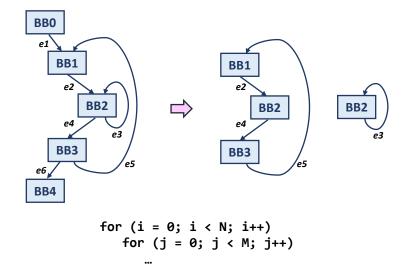

The starting point for out circuit generation is a standard compiler intermediate representation in *static single assignment* (SSA) form, where every variable is defined only once; *phi* nodes are used to define a variable from multiple definitions along multiple control paths [110]. The *control-flow graph* (CFG) of a program is organized into *basic blocks* (BBs), i.e., straight pieces of code separated by control flow decisions. Each BB contains a dataflow graph of program instructions; it receives *live-in* variables from the predecessor BBs and produces *live-out* variables for the successor BBs. Transforming the DFG of each BB into a corresponding interconnect of dataflow units is relatively straightforward—we will describe this process in Section 2.3.4—but there are a couple of problems when implementing control flow and sending values from one BB to another due to the fundamental difference between software programs and dataflow circuits.

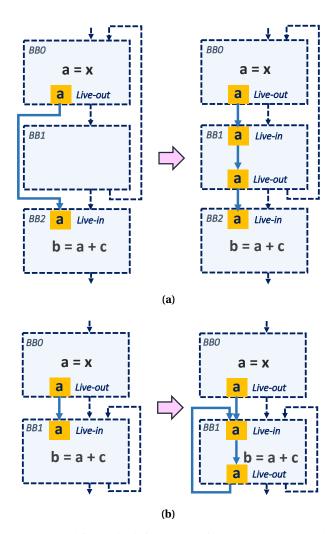

Figure 2.6 shows two examples: (1) In the example in Figure 2.6a, the variable a is defined in BB0 and used in BB2. A typical representation in a compiler (left of the figure) propagates the desired information directly from the source to the destination block (i.e., a live-in of a basic block comes from a basic block which is not its immediate predecessor). This flow does not pose problems in software, as successive values of a would be stored in a register of a processor or in memory and the last value used when BB2 is reached. (2) In the example in Figure 2.6b, BB1 is the only BB in the body of a loop and uses a value a produced in BB0. The value of a does not change during the execution of BB1 and is used at every execution of BB1. Again, the representation on the left would cause no problem in a processor—the value would be stored in a register or memory and read as many times as needed.

Directly implementing such connections in a dataflow circuit would result in incorrect behavior because every generated value is associated with a token; the number of tokens must exactly match the number of distinct uses. The cases in the left of Figures 2.6a and 2.6b violate this principle if implemented literally: (1) In the first case, if the control flow were {BB0-BB1-BB0-BB1-BB2}, two new values (with the respective tokens) for a would have been generated and sent to BB2; yet, BB2 can take only a single token and requires only the most recent value. The execution would be incorrect or the circuit would not terminate because the tokens not absorbed by BB2 would create backpressure to BB0 and stop it indefinitely. (2) In the second case, BB1 would not be able to execute repeatedly due to a starving input. Assuming the control

**Figure 2.6** – Implementing control flow. The left circuits of Figures 2.6a and 2.6b show two cases where a direct conversion of a data and control flow graph into a dataflow circuit would fail. Coupling data and control to ensure correct token transfers between BBs is shown on the right of the figures: data is propagated exclusively from each BB to its immediate successors. For each live-in and live-out (shaded yellow in the figure), we employ merge and branch units, respectively.

flow is {BB0-BB1-BB1}, the first execution of BB1 will consume the single data token for a and any further execution of BB1 would stall indefinitely waiting for a token.

The solution to both problems is to strictly couple data propagation with control flow, as shown on the right of Figures 2.6a and 2.6b. The following properties must hold: (1) every BB must provide a live-out for every live-in of all of its immediate successor BBs and exclusively to them, and (2) every BB must receive all of its live-ins from its immediate predecessor BBs and exclusively from them. We implement these rules as outlined in Algorithm 2.1: (1) we employ a standard liveness analysis algorithm [110] to determine the live-ins and live-outs of each BB, (2) for every BB live-in and live-out, we instantiate a merge and a branch unit in the BB, respectively, (3) we connect all operations within a BB that use a live-in to the appropriate merge

```

// Input: CFG (control-flow graph)

// Input: DFG (SSA-based dataflow graph)

// Output: DFG (dataflow graph with coupled data propagation

// and control flow)

// Determine live-ins and live-outs of each BB in CFG

liveIns, liveOuts = LivenessAnalysis (CFG)

// Place merge for every live-in in every BB

foreach bb \in CFG do

foreach li \in liveIns (bb) do

mg = CreateMerge(bb, li, DFG)

// Connect all operations within the BB

// that use the live-in to the corresponding merge

foreach op \in operations (bb) do

if li \in predecessors (op) then

| Connect (op, mg)

// Place branch for every live-out in every BB

foreach bb \in CFG do

foreach lo \in liveOuts (bb) do

br = CreateBranch (bb, lo, DFG)

// Connect branch to corresponding merges

// in successor BBs

foreach bb_{succ} \in successors (bb) do

mg = FindMerge (lo, bb_{succ})

Connect (br, mg)

```

Algorithm 2.1: Implementing control flow.

of the same BB (i.e., the merge will inject tokens into the BB body to trigger the execution of its operations), and (4) we connect the outputs of all branches to the inputs of the corresponding merges in the immediate successor BBs. In Figure 2.6a, this strategy results in merges for a in BB1 and BB2 and branches for a in BB0 and BB1. In Figure 2.6a, BB0 has a branch for a whereas BB1 has a merge and a branch.

This strategy guarantees that every piece of data is sent correctly from BB to BB, following the control flow of the program. Note that each BB contains as many merge units as it has incoming variables and as many branch units as it has outgoing variables. Some merges correspond to SSA *phi* nodes—they propagate into the BB a value chosen from one of the distinct predecessor values (based on the control flow), whereas other merges propagate a single value (coming from different control flow directions) to honor the rules above. This is the case, for instance, for the merge for variable a in BB1 of Figure 2.6b. All branches of a BB share the same condition and send tokens to the same successor BB based on a control flow decision.

**Figure 2.7** – Nondeterministic behavior at SSA *phis*. The token entering BB4 is produced either by BB2 or BB3; since these values are produced independently, the merge in BB4 may receive its inputs out of order.

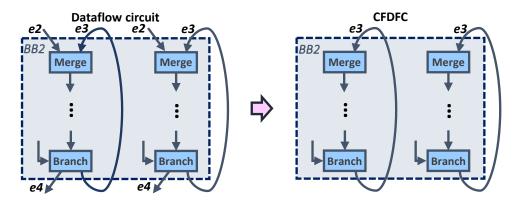

#### 2.3.3 Ensuring Determinism

Although different operations in a dataflow circuit may execute out of order, tokens are expected to arrive to each individual operator *strictly in order*. Yet, there is one particular case in which this property may not hold and which we discuss in this section.

The execution of our dataflow circuits is triggered by injecting a single token for each input (i.e., program argument) into the start BB. The tokens propagate through the BBs, following the control flow of the program—the BBs are triggered in exactly the same order as the software execution of the unmodified original program. When a single value propagates through the BBs, a token will always enter each BB from its single active predecessor—once the token enters through a merge, no other source can reinject a token into the merge until the merge itself produces a token, hence there is nothing that can interfere with the token ordering at the BB input. Tokens will never reorder inside a BB as it contains only straight and unconditional dataflow computation.

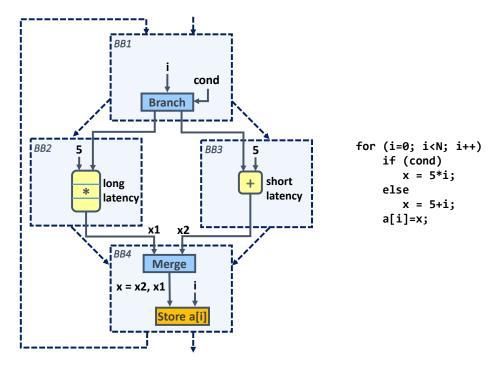

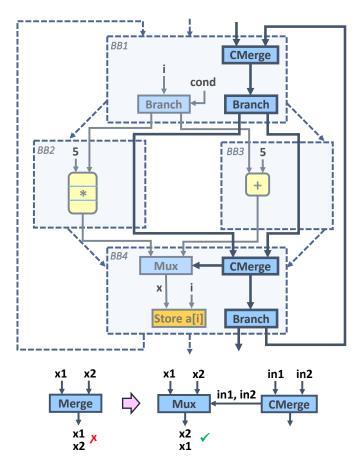

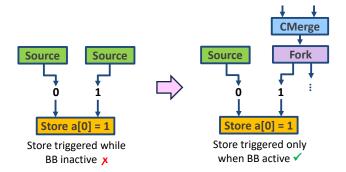

However, the situation is different in BB entry points where a value is redefined (i.e., when a token enters a BB through a merge which corresponds to SSA *phi* node)—as each input represents a distinct and, potentially, uncorrelated value, the input tokens may arrive in an order different than specified in the original program. An example of such a case is illustrated in Figure 2.7, which shows the CFG and a simplified datapath of the code in the figure. Assuming that the control flow is {BB1-BB2-BB4-BB1-BB3-BB4} (determined by the condition cond in BB1), the iterator from BB1 will first be sent to BB2 to compute the value of x1. This value takes multiple

**Figure 2.8** – Ensuring determinism. We extend the circuit from Figure 2.7 with a specialized in-order control network that follows the control flow of the program—the cmerges of this network communicate with the muxes of the same BB to indicate the correct input ordering.

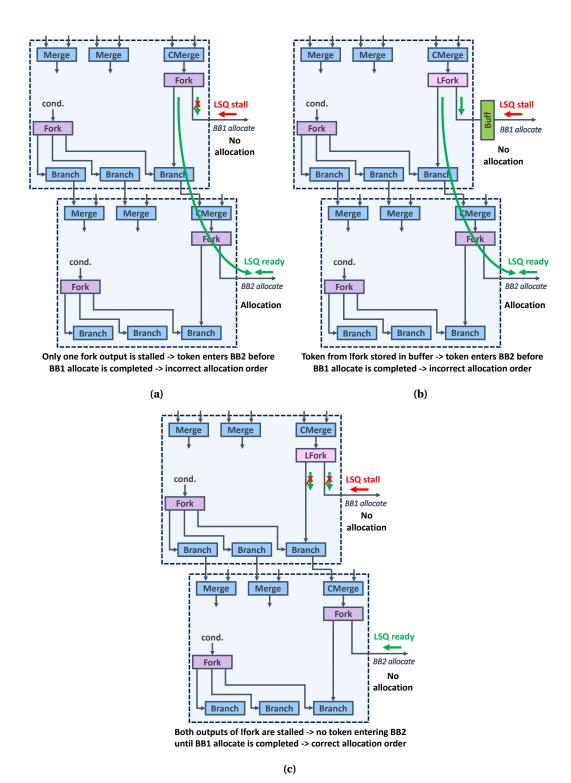

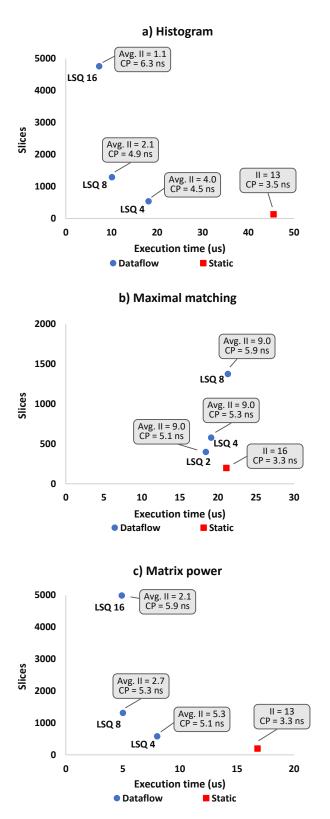

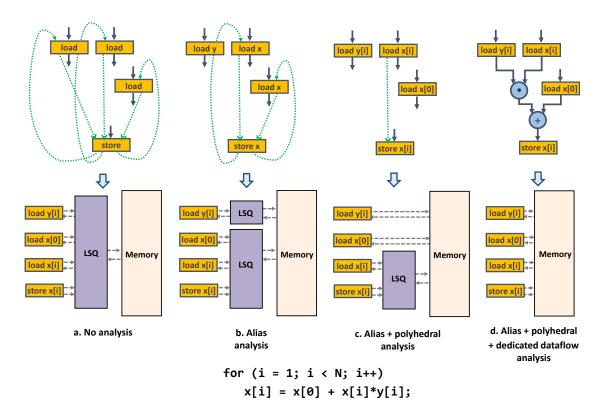

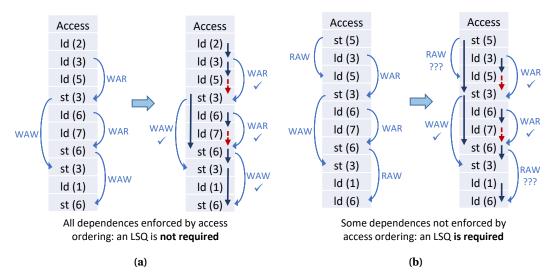

cycles to compute, but the iterator can quickly propagate through BB4 and BB1 (the iterator path is omitted from the figure; as described in the previous section, it follows the control flow of the program). It will then enter BB3 which will trigger the short computation producing  $\times 2$ —this value may arrive to the merge in BB4 before the value of  $\times 1$ ; the merge would send the values to the store out of order which would then produce incorrect results.