# Software Support for Non-Volatile Memory (NVM) Programming

Présentée le 15 juillet 2021

Faculté informatique et communications Laboratoire d'informatique à très grande échelle Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

#### **David Teksen AKSUN**

Acceptée sur proposition du jury

Prof. A. Argyraki, présidente du jury

Prof. J. R. Larus, directeur de thèse

Prof. M. Scott, rapporteur

Prof. M. Seltzer, rapporteuse

Prof. E. Bugnion, rapporteur

We are at the very beginning of time for the human race.

It is not unreasonable that we grapple with problems.

But there are tens of thousands of years in the future.

Our responsibility is to:

do what we can,

learn what we can,

improve the solutions, and

pass them on.

— Richard P. Feynman

To my family...

## Acknowledgements

Looking back at the previous years, I can easily say that my journey was very similar to a voyager during the times of the Age of Exploration. I was searching for new routes, the journey was long, and the future was uncertain. Despite all the difficulties and all the challenges, this journey would not have been possible without the right captain to guide the ship.

I am very lucky to have Prof. James Larus, who was a magnificent thesis advisor, as the captain of the ship. I am very honored to be chosen by Jim, a world-renowned researcher and professor. I am eternally grateful to Jim for giving me this opportunity and allow me to do research with him. He has allowed me to explore and work on many interesting ideas and research projects. He has supported me with his deep and broad knowledge, and patiently guided me throughout difficult times. His weekly constant feedback and his supportive attitude were irreplaceable. I admire Jim's thinking, writing style, and presentation skills and I will always see him as a great role model. I adore Jim's inquisitive approach to challenging topics. He can break apart very complex subjects, even in unrelated fields, and always finds the right question to ask. His fatherly attitude towards his students and his expectation of excellence are what make him so unique. I enjoyed TA'ing his courses, as I saw his diligence and perfection in a different context. I appreciate all the time he has spent with me and I wouldn't have this journey any other way.

Prof. Edouard Bugnion has a very special place for me. Ed was very supportive and helpful throughout this journey and I thank him a lot for this. I learned a lot from Ed. I will always remember his comments about each presentation in our lab meetings, his simple way of approaching problems, and his methodology of finding the right abstraction to analyze complex systems. To this day, I still use the design principles that I learned from Ed's course for building systems.

I would like to thank Prof. Edouard Bugnion, Prof. Margo Seltzer, Prof. Michael L. Scott, and Prof. Katerina Argyraki for being in my thesis committee and providing valuable feedback.

I am very grateful to Nachshon Cohen, who was my collaborator. He is very smart, thoughtful, and a very great researcher as he can come up with great ideas. He taught me a lot of things, not just about research, but about all aspects of life. I will always consider him as a dear colleague and a true friend.

I would like to thank Tania for being supportive and keeping everything organized. Everything

ran smoothly thanks to her.

Maggy was a mom figure and took care of each student. She was very direct and always encouraged every one around her to be a better person. She always kept her smile. Maggy has supported me throughout the most difficult days and I will always remember her support.

Throughout my PhD, I met a lot of smart and hard-working people. However, I cannot tell how much I appreciate my lab mates, Sahand and Mahyar, who always come to my help when in need. Mahyar Emami is a real friend that everybody needs. He has always opened his home to me, has shared everything with me without a question, and I will always remember our research discussions with him. Sahand is a very reliable friend, who is always there for his friends. He was one of my closest friends throughout my PhD and I have a lot of good memories with him.

I would like to thank Mia and Georg for always supporting and helping me. Their insights about research and their feedbacks were very useful. I would like to thank Marios for the research discussions and his feedback. While I met him towards the end of my PhD, I would like to thank Prof. Sanidhya Kashyap for his feedback.

I am very grateful to the rest of my colleagues and friends from VLSC and DCSL at EPFL, who made the experience much better: Stuart, Adrien, Sam, Konstantinos, Jonas, Stanko, George, Dmitrii. I would like to thank my friends and colleagues who made the PhD experience much better and motivated me from EPFL: Sepand, Luis, Siddarth, Atri, Jasmina, Berker, Onur, Tiziano, Kristina, and Jeremie. I would like to thank the people that I know outside EPFL: My childhood friend Doruk, Maggy's son Jimmy, Mendel, and Mushky.

I am very grateful to Madan for providing me with the opportunity to do an internship in MSR. Many thanks to Saeed and Todd for their collaboration.

I would like to extend my thanks to the people at Intel for providing me with access to their servers equipped with Optane, which enabled my research: Mustafa, Sanjay, Arunarasu, Brent, and Aaron.

Finally, I would like to thank my family. My mother, my father, and my grandmother have always supported me since I was born. I will always remember their sacrifices and honor the way in which they have raised me.

Lausanne, June 29, 2021

D. A.

### **Abstract**

Non-Volatile Memory (NVM) is an emerging type of memory device that provides fast, byte-addressable, and high-capacity durable storage. NVM sits on the memory bus and allows durable data structures designs similar to the in-memory equivalent ones. Expensive serialization/deserialization operations, usually associated with block-based storage, are not necessary. Unfortunately, using NVM is not as simple as placing a data structure in NVM and expecting persistence. As NVM sits on the memory bus, processor caches buffer the cache lines from it that are referenced by load and store instructions.

The volatility of the caches and possible power failures at a random point in a program complicate the design and require ways to handle these failures. Prior work focused on implementing crash-consistency mechanisms to correctly recover a program's data after a failure. The goal was to minimize the use of costly cache line write-back and fence instructions, which are necessary for correct durability. Moreover, commercial NVM devices are slower compared to DRAM and affect the design. In addition to performance overheads, correctly implementing crash consistency is hard. The programmers need to carefully reason about cache line write-back instructions and the order of persistent writes. Finding bugs can take from minutes to hours.

In this thesis, we use checkpointing as an effective crash-consistency mechanism with low overhead for building durable data structures. We also describe an inter-procedural dataflow analysis for fast detection of NVM programming bugs. We show the practicality of these ideas through three primary contributions and their implementations.

Firstly, we present *InCLL* to address NVM checkpointing. *InCLL* is a novel technique that uses fine-grained checkpointing and in-cache-line logging to minimize the number of explicit write-back and fence instructions in the fast path of data structure modifications. We evaluate *InCLL* both on DRAM and Optane devices for the Masstree data structure. Secondly, we present a new checkpointing design, *CpNvm*, which minimizes NVM write-back instructions on the critical path of the execution. We achieve low overheads for Masstree and Memcached for write-heavy workloads, and almost no overheads for read-only workloads. In addition, we present *FlowNvm* to find NVM programming bugs. *FlowNvm* can identify NVM programming pattern violations and anti-patterns at compile-time using inter-procedural dataflow analysis.

**Keywords:** non-volatile memory, NVM, durable data structures, checkpointing, dataflow analysis

### Résumé

Non-Volatile Memory (NVM) est un nouveau type de dispositif mémoire qui fournit un stockage durable rapide, adressable par octet, et de grande capacité. La NVM se situe sur le bus mémoire et permet de conçevoir des structures de données durables similaires aux structures équivalentes en mémoire. Les opérations coûteuses de sérialisation/désérialisation, généralement associées au stockage par blocs, ne sont pas nécessaires. Malheureusement, l'utilisation de la NVM n'est pas aussi simple que de placer une structure de données dans la NVM et de s'attendre à de la persistance. Comme la NVM se trouve sur le bus mémoire, les caches des processeurs mettent en mémoire tampon les lignes de cache qui sont référencées par les instructions de chargement et de stockage.

La volatilité des caches et les éventuelles pannes de courant à un moment aléatoire d'un programme compliquent la conception et nécessitent des moyens de gérer ces pannes. Les travaux antérieurs se sont concentrés sur la mise en œuvre de mécanismes de cohérence en cas de panne pour récupérer correctement les données d'un programme après une panne. L'objectif était de minimiser l'utilisation d'instructions coûteuses de réécriture et des barrières mémoire qui sont nécessaires pour une durabilité correcte. De plus, les dispositifs NVM commerciaux sont plus lents que la DRAM et affectent la conception. En plus des surcharges de performance, la mise en œuvre correcte de la cohérence en cas de panne est difficile. Les programmeurs doivent raisonner soigneusement sur les écritures de lignes de cache et sur l'ordre des écritures persistantes. Trouver des bugs peut prendre de quelques minutes à quelques heures.

Dans cette thèse, nous utilisons le checkpointing comme un mécanisme de cohérence en cas de panne efficace et à faible surchargeen pour construire des structures de données durables. Nous décrivons également une analyse interprocédurale du flux de données pour la détection rapide des bugs de programmation NVM. Nous montrons l'aspect pratique de ces idées à travers trois contributions principales et leurs implémentations.

Tout d'abord, nous présentons *InCLL* pour traiter le checkpointing NVM. *InCLL* est une nouvelle technique qui utilise le fine-grained checkpointing et le in-cache-line logging pour minimiser le nombre d'instructions de réécriture explicite et de barrières mémoire dans le chemin rapide des modifications de structure de données. Nous évaluons *InCLL* à la fois sur des dispositifs DRAM et Optane pour la structure de données Masstree. Ensuite, nous présentons une nouvelle conception de checkpointing, *CpNvm*, qui minimise les écritures NVM sur le chemin critique de l'exécution. Nous obtenons de faibles surcharges pour Masstree

#### Résumé

et Memcached pour les charges de travail à forte intensité d'écriture, et presque aucune surcharge pour les charges de travail en lecture seule. De plus, nous présentons *FlowNvm* pour trouver des bugs de programmation NVM. *FlowNvm* peut identifier les violations et les anti-modèles de programmation NVM au moment de la compilation en utilisant l'analyse du flux de données interprocédural.

**Mots clefs** : non-volatile memory, NVM, structures de données durables, points de contrôle, analyse de flux de données

# **Contents**

| Ac | knov  | wledge  | ments                                      | j  |

|----|-------|---------|--------------------------------------------|----|

| Ał | ostra | ct (Eng | dish/Français)                             | ii |

| Li | st of | Figure  | s                                          | xi |

| Li | st of | Tables  |                                            | χι |

| 1  | Intr  | oducti  | on                                         | 1  |

|    | 1.1   | Non-    | volatile Memory (NVM)                      | 2  |

|    |       | 1.1.1   | Intel Optane                               | 3  |

|    | 1.2   | Princ   | iple Problems for Programming NVM          | 5  |

|    | 1.3   | Crash   | -consistency Challenges                    | 7  |

|    |       | 1.3.1   | Cost of Ordering Persistent Writes         | 7  |

|    |       | 1.3.2   | Cost of Using Optane                       | 7  |

|    |       | 1.3.3   | NVM Programming Correctness                | 7  |

|    | 1.4   | Thesi   | s Statement                                | 7  |

|    | 1.5   | Thesi   | s Organization                             | 10 |

|    | 1.6   | Biblio  | ographic Notes                             | 10 |

| 2  | Bac   | kgroui  | ıd                                         | 11 |

|    | 2.1   | NVM     | Programming                                | 11 |

|    |       | 2.1.1   | Failure Model                              | 12 |

|    |       | 2.1.2   | NVM Programming Primitives                 | 12 |

|    |       | 2.1.3   | Alternative and Earlier Programming Models | 17 |

|    |       | 2.1.4   | Optane Configuration                       | 17 |

|    | 2.2   | Crash   | -Consistency Mechanisms for Programming    | 18 |

#### **Contents**

|   | 2.3  | Check                                | pointing                             | 20           |  |  |  |

|---|------|--------------------------------------|--------------------------------------|--------------|--|--|--|

| 3 | Fine | e-Grained Checkpointing with InCLL 2 |                                      |              |  |  |  |

|   | 3.1  | Introd                               | luction                              | 24           |  |  |  |

|   | 3.2  | InCLL                                | Design Overview                      | 26           |  |  |  |

|   |      | 3.2.1                                | Masstree Data Structure              | 26           |  |  |  |

|   |      | 3.2.2                                | Fine-Grained Checkpointing           | 28           |  |  |  |

|   |      | 3.2.3                                | In-Cache-Line Logging                | 28           |  |  |  |

|   |      | 3.2.4                                | External Logging                     | 29           |  |  |  |

|   | 3.3  | InCLL                                | Implementation                       | 29           |  |  |  |

|   |      | 3.3.1                                | Fine-Grained Checkpointing Intervals | 30           |  |  |  |

|   |      | 3.3.2                                | In-Cache-Line Logging                | 30           |  |  |  |

|   |      | 3.3.3                                | External Logging Algorithm           | 37           |  |  |  |

|   |      | 3.3.4                                | Recovery                             | 37           |  |  |  |

|   |      | 3.3.5                                | Persistent Memory Allocation         | 40           |  |  |  |

|   | 3.4  | Evalua                               | ation                                | 42           |  |  |  |

|   |      | 3.4.1                                | Machine Configuration                | 42           |  |  |  |

|   |      | 3.4.2                                | Previous and Current Configuration   | 42           |  |  |  |

|   |      | 3.4.3                                | Baseline Configuration               | 43           |  |  |  |

|   |      | 3.4.4                                | InCLL Configuration                  | 43           |  |  |  |

|   |      | 3.4.5                                | Logging Configuration                | 43           |  |  |  |

|   |      | 3.4.6                                | YCSB Configuration                   | 44           |  |  |  |

|   |      | 3.4.7                                | Measurements                         | 44           |  |  |  |

|   | 3.5  | Summ                                 | nary                                 | 48           |  |  |  |

| 4 | NVA  | M Checkpointing with <i>CpNvm</i>    |                                      |              |  |  |  |

| 1 | 4.1  |                                      | luction                              | <b>51</b> 52 |  |  |  |

|   | 4.2  |                                      | m Design                             | 54           |  |  |  |

|   | 7.2  |                                      | Crash-Recovery Model                 | 56           |  |  |  |

|   | 4.3  |                                      | m Implementation                     | 56           |  |  |  |

|   | T.J  | 4.3.1                                | Execution                            | 57           |  |  |  |

|   |      | 4.3.1                                | Tracking                             | 58           |  |  |  |

|   |      |                                      | Checkpointing                        | 60           |  |  |  |

|   |      | $_{\pm}$ .J.J                        | Checkpointing                        | UU           |  |  |  |

|   |     | 4.3.4  | Background Replay                                    | 61 |

|---|-----|--------|------------------------------------------------------|----|

|   |     | 4.3.5  | Recovery                                             | 63 |

|   |     | 4.3.6  | Masstree Example                                     | 63 |

|   |     | 4.3.7  | Memory Capacity                                      | 65 |

|   | 4.4 | Evalu  | ation                                                | 65 |

|   |     | 4.4.1  | CpNvm Configurations                                 | 65 |

|   |     | 4.4.2  | Measurements                                         | 66 |

|   |     | 4.4.3  | Recipe                                               | 69 |

|   |     | 4.4.4  | InCLL                                                | 71 |

|   |     | 4.4.5  | PMThreads                                            | 71 |

|   |     | 4.4.6  | Recovery                                             | 72 |

|   |     | 4.4.7  | Memcached                                            | 73 |

|   | 4.5 | Relate | ed Work                                              | 75 |

|   |     | 4.5.1  | NVM Programming Systems                              | 75 |

|   |     | 4.5.2  | Checkpointing                                        | 77 |

|   |     | 4.5.3  | Durable Data structures                              | 79 |

|   |     | 4.5.4  | Persistent Memory Allocation                         | 80 |

|   | 4.6 | Sumn   | nary                                                 | 81 |

|   |     |        |                                                      |    |

| 5 |     | Ü      | aflow Analysis to Find NVM Program Bugs with FlowNvm | 83 |

|   | 5.1 |        | luction                                              | 84 |

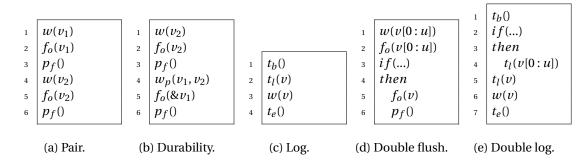

|   | 5.2 | Ü      | amming Pattern Examples                              | 85 |

|   |     | 5.2.1  | Pair Pattern                                         | 85 |

|   |     | 5.2.2  | Durability Pattern                                   | 86 |

|   |     | 5.2.3  | Log Pattern                                          | 87 |

|   |     | 5.2.4  | Double Flush Anti-Pattern                            | 89 |

|   |     | 5.2.5  | Double Log Anti-Pattern                              | 89 |

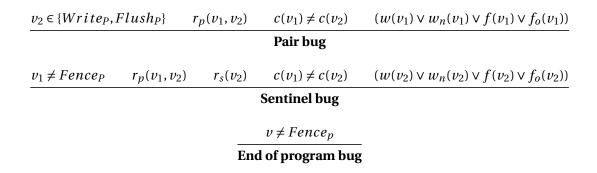

|   | 5.3 | Flow   | Nvm Overview and Design                              | 90 |

|   |     | 5.3.1  | Dataflow Framework Formalization                     | 92 |

|   |     | 5.3.2  | Pair Framework                                       | 92 |

|   |     | 5.3.3  | Durability Framework                                 | 94 |

|   |     | 5.3.4  | Log Framework                                        | 95 |

#### **Contents**

|    |                      | 5.3.5       | Double Flush Framework                     | 97  |  |  |  |

|----|----------------------|-------------|--------------------------------------------|-----|--|--|--|

|    |                      | 5.3.6       | Double Log Framework                       | 99  |  |  |  |

|    | 5.4                  | FlowN       | Nym Implementation                         | 100 |  |  |  |

|    |                      | 5.4.1       | FlowNvm Internals                          | 100 |  |  |  |

|    |                      | 5.4.2       | FlowNvm Annotations                        | 101 |  |  |  |

|    |                      | 5.4.3       | Memory Regions and Modeling                | 104 |  |  |  |

|    |                      | 5.4.4       | Bug Reporting and Custom Functions         | 105 |  |  |  |

|    | 5.5                  | Evalua      | ation                                      | 106 |  |  |  |

|    |                      | 5.5.1       | Bug Finding Results                        | 106 |  |  |  |

|    |                      | 5.5.2       | Performance Evaluation                     | 109 |  |  |  |

|    | 5.6                  | Relate      | ed Work                                    | 110 |  |  |  |

|    |                      | 5.6.1       | Program Analysis and Testing for NVM       | 110 |  |  |  |

|    | 5.7                  | Sumn        | nary                                       | 112 |  |  |  |

| •  | 0                    | .1          |                                            | 110 |  |  |  |

| 6  | Con                  | clusion 113 |                                            |     |  |  |  |

|    | 6.1                  | Future      | e Directions                               | 114 |  |  |  |

|    | 6.2                  | Discu       | ssion                                      | 115 |  |  |  |

|    |                      | 6.2.1       | Avoiding Write-Back and Fence Instructions | 115 |  |  |  |

|    |                      | 6.2.2       | Using Optane                               | 115 |  |  |  |

|    |                      | 6.2.3       | Bug Finding at Compile Time                | 116 |  |  |  |

|    | 6.3                  | Concl       | usion                                      | 116 |  |  |  |

|    |                      |             |                                            |     |  |  |  |

| Bi | bliog                | raphy       |                                            | 117 |  |  |  |

| C1 | Curriculum Vitae 137 |             |                                            |     |  |  |  |

| ~  |                      | ALGERIA V   | 1100                                       | 101 |  |  |  |

# **List of Figures**

| 1.1  | Intel Optane platform                                                                                              | 4  |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Book example for a library program                                                                                 | 5  |

| 1.3  | Book example with transactions                                                                                     | 6  |

| 2.1  | Possible ways to write data to NVM durably                                                                         | 14 |

| 2.2  | Flushing multiple cache lines.                                                                                     | 15 |

| 2.3  | Program without flush, non-temporal move, and fences                                                               | 16 |

| 2.4  | Provisioning NVM for different operation modes using ipmctl                                                        | 17 |

| 2.5  | Durable memory device configuration using ndctl                                                                    | 18 |

| 3.1  | Masstree's leaf node structure                                                                                     | 27 |

| 3.2  | Layout for the permutation field                                                                                   | 28 |

| 3.3  | Visual durable Masstree leaf node layout                                                                           | 30 |

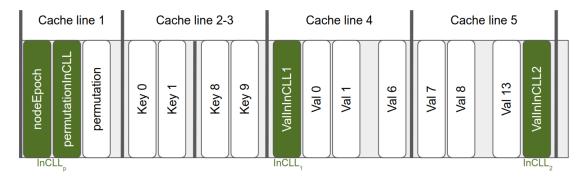

| 3.4  | InCLL's leaf node structure                                                                                        | 31 |

| 3.5  | Durable Masstree operations                                                                                        | 32 |

| 3.6  | Order of operations using $InCLL_p$ fields for insertions and deletions                                            | 34 |

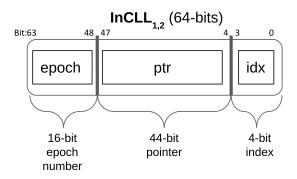

| 3.7  | InCLL <sub>1,2</sub> layout                                                                                        | 35 |

| 3.8  | Durable Masstree recovery.                                                                                         | 38 |

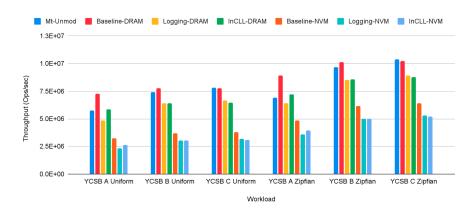

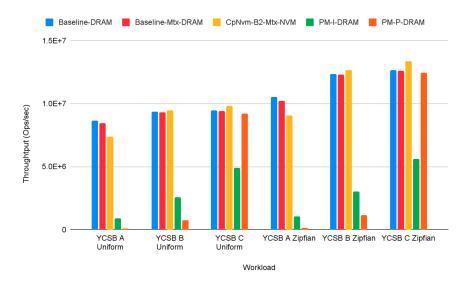

| 3.9  | Throughput of unmodified Masstree, baseline Masstree and <i>InCLL</i> with DRAM and Optane evaluations             | 44 |

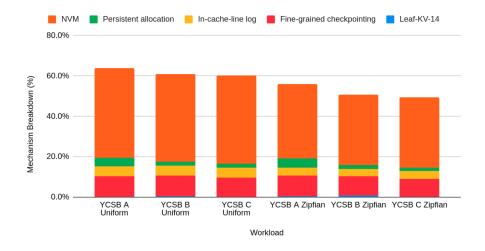

| 3.10 | Mechanism breakdown of <i>InCLL</i> features                                                                       | 45 |

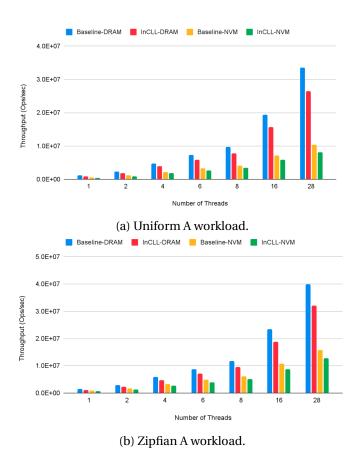

| 3.11 | Throughput of baseline Masstree and <i>InCLL</i> with DRAM and Optane evaluations for different number of threads  | 47 |

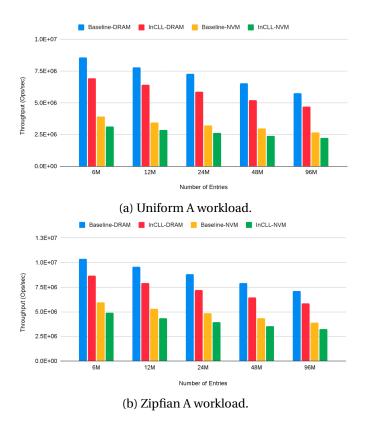

| 3.12 | Throughput of baseline Masstree and <i>InCLL</i> with DRAM and Optane evaluations for different initial tree sizes | 48 |

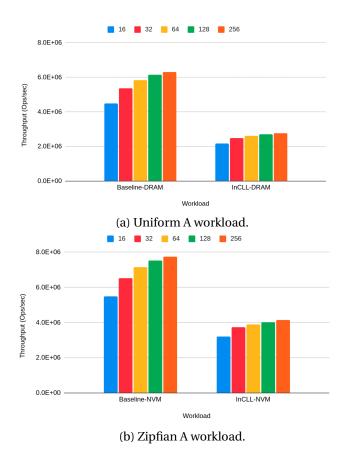

| 3.13 | Throughput of baseline Masstree and <i>InCLL</i> with DRAM and Optane evaluations for different number of checkpointing intervals   | 49 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

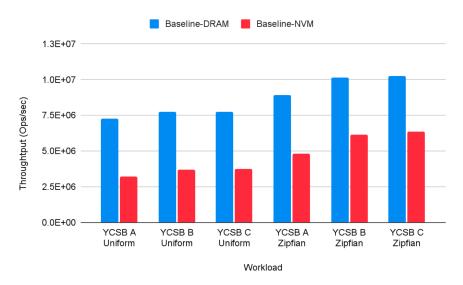

| 4.1  | Throughput of Masstree for DRAM and Optane evaluations                                                                              | 52 |

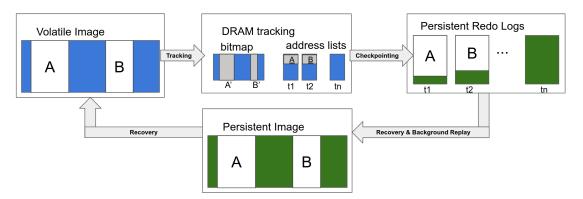

| 4.2  | CpNvm design.                                                                                                                       | 55 |

| 4.3  | <i>CpNvm</i> API                                                                                                                    | 57 |

| 4.4  | Pseudocode for <i>CpNvm</i> tracking and checkpointing                                                                              | 59 |

| 4.5  | Pseudocode for <i>CpNvm</i> background replay and recovery                                                                          | 62 |

| 4.6  | CpNvm Masstree example                                                                                                              | 64 |

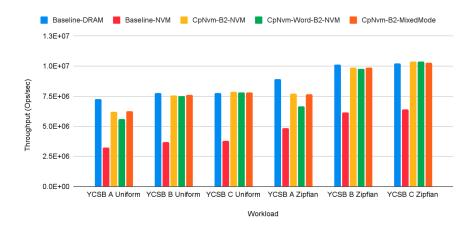

| 4.7  | Throughput of Masstree for different implementations                                                                                | 66 |

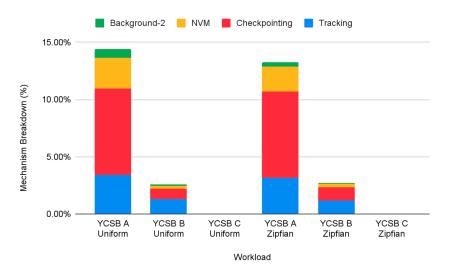

| 4.8  | Mechanism breakdown for <i>CpNvm-B2-NVM</i>                                                                                         | 67 |

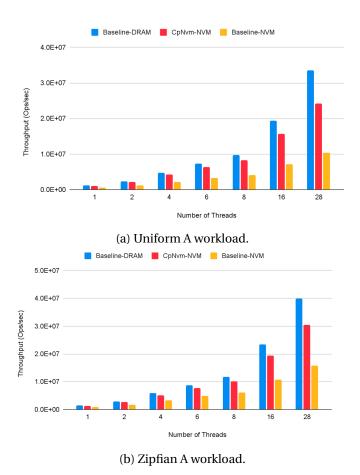

| 4.9  | Throughput of the <i>CpNvm</i> implementation of Masstree for different numbers of threads                                          | 68 |

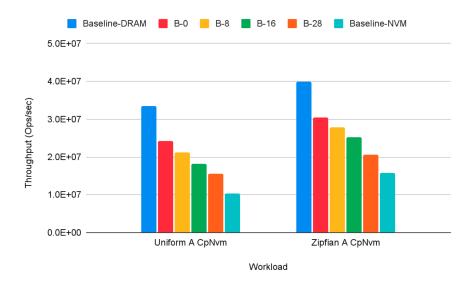

| 4.10 | Throughput of the <i>CpNvm</i> implementation of Masstree with 28 worker threads and different numbers of background replay threads | 69 |

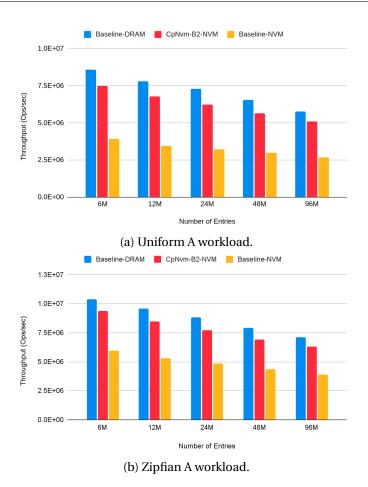

| 4.11 | Throughput of baseline Masstree and <i>CpNvm</i> with DRAM and Optane evaluations for different initial tree sizes                  | 70 |

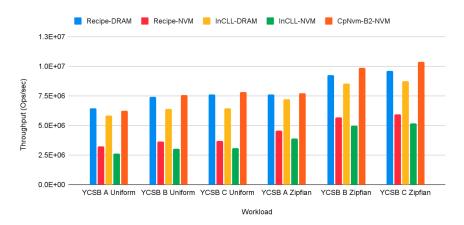

| 4.12 | Throughput of Recipe and InCLL compared to different Masstree implementations                                                       | 71 |

| 4.13 | Throughput of <i>CpNvm</i> and PMThreads implementation of pthread_mutex_lock Masstree                                              | 72 |

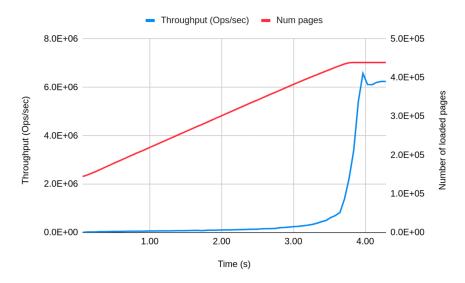

| 4.14 | Execution of <i>CpNvm</i> after a restart                                                                                           | 73 |

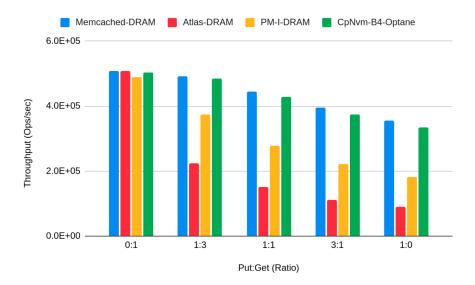

| 4.15 | Throughput for different versions of Memcached                                                                                      | 74 |

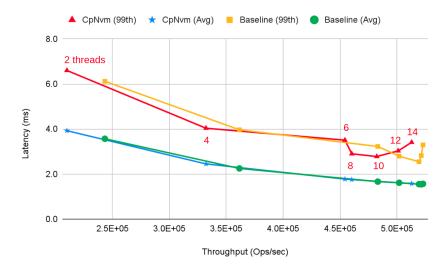

| 4.16 | Latency vs. throughput measurements for Memcached and <i>CpNvm</i> for 1:1 (Put:Get)                                                | 75 |

| 5.1  | Pair programming pattern with a log entry example                                                                                   | 86 |

| 5.2  | Durability programming pattern with a linked list example                                                                           | 87 |

| 5.3  | Log programming pattern with a linked list example                                                                                  | 88 |

| 5.4  | Double flush anti-pattern with log entry example                                                                                    | 89 |

| 5.5  | Double log anti-pattern                                                                                                             | 89 |

| 5.6  | Context-free grammar rules for the imperative language                                                                              | 90 |

| 5.7  | Example snippets for each pattern in the toy language                                                                               | 91 |

| 5.8  | $F_P$ : Dataflow transition rules for keeping track of persistence state                                                            | 93 |

| 5.9  | Meet example for the pair framework and depiction of the <i>pair bug.</i>                                                           | 93 |

| 5.10 Pair pattern violation bugs.                                                           | 94  |

|---------------------------------------------------------------------------------------------|-----|

| 5.11 Durability pattern violation bug                                                       | 95  |

| 5.12 Meet example for the durability framework and depiction of the $durability$ $bug$ .    | 95  |

| 5.13 $F_L$ : Dataflow transition rules for keeping track of logging state                   | 96  |

| 5.14 Meet example for the log framework and depiction of the $\log bug$                     | 97  |

| 5.15 Log pattern violation bugs.                                                            | 97  |

| 5.16 $F_F$ : Dataflow transition rules for keeping track of double flush state              | 98  |

| 5.17 Meet example for the double flush framework and depiction of the <i>double flush</i>   |     |

| bug                                                                                         | 98  |

| 5.18 Double flush anti-pattern bug                                                          | 98  |

| 5.19 Meet example for the double log framework and depiction of the <i>double log bug</i> . | 99  |

| 5.20 Log pattern violation bugs.                                                            | 100 |

| 5.21 Annotations for the pair framework                                                     | 102 |

| 5.22 Annotations for the durability framework                                               | 103 |

| 5.23 Annotations for the log and double framework                                           | 104 |

| 5.24 Function to flush a range of memory                                                    | 106 |

| 5.25 Example for red-black tree alias analysis issue                                        | 108 |

| 5.26 New bug found in Echo key value store                                                  | 109 |

## **List of Tables**

| 1.1 | Approximate DRAM and Optane maximum bandwidth (in GB/s) characteristics.                                | 3   |

|-----|---------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Possible NVM states for book example                                                                    | 5   |

| 1.3 | Possible NVM states for transactional book example                                                      | 6   |

| 2.1 | Formal operations and relations for NVM programming                                                     | 15  |

| 5.1 | A possible state at the time of power failure if data field of the log entry is not flushed explicitly. | 86  |

| 5.2 | A possible state at the time of power failure if newnode is not flushed explicitly.                     | 87  |

| 5.3 | A possible state at the time of power failure if node is not tracked explicitly                         | 88  |

| 5.4 | FlowNvm annotations                                                                                     | 101 |

| 5.5 | NVM program breakdown of bug locations.                                                                 | 106 |

| 5.6 | Bug type breakdown of bug locations                                                                     | 107 |

| 5.7 | Correctly reported bug locations                                                                        | 108 |

| 5.8 | Time measurement for bug reporting                                                                      | 109 |

## 1 Introduction

**Non-volatile memory (NVM)** is an emerging type of memory that offers fast, byte-addressable durable storage. It is possible to store and manipulate pointer-based data structures such as B+ trees and hash maps directly in NVM using load and store instructions. These structures are accessible even after a power failure or a process crash.

One promising use for NVM is constructing robust, high-performance internet and cloud services, which often maintain very large, in-memory data structures and need to quickly recover from faults or failures. In data centers, failures are rare, but they do occur. Barroso [20] reports that, at Google, in a year, a server is restarted between 1.2-16 times. Approximately 45% of machines restart at least once in a 6-month period and approximately 5% of machines restart more than once per month.

A challenge in restarting large-scale services is the size of computer memories, which has grown far faster than bandwidth to external storage devices, exacerbating a long-standing bottleneck in persisting and restoring memory state [16]. For example, Facebook [71] reports that restoring 120GB of data for a single machine can require 2.5-3 hours due to low disk bandwidth and in-memory format translations. NVM can avoid most of these costs and provides higher bandwidth than disk.

**NVM programming**, using NVM as a durable memory device, requires crash-consistency. Crash consistency ensures that after a reboot, the program data is in a consistent state and will not lead to any failures. Unlike traditional block-level storage, NVM programming requires careful reasoning about cache lines and ordering persistent writes.

In the rest of the section, we expand on:

- 1. background information about NVM devices,

- 2. key challenges and issues associated with NVM programming,

- 3. our contributions to NVM programming to provide crash consistency using checkpointing and to find programming mistakes using dataflow analysis.

#### 1.1 Non-volatile Memory (NVM)

Non-volatile memory devices promise performance characteristics similar to DRAM and allow byte-addressable access. On top of these features, an NVM device also provides persistence, making it effectively a durable storage media. There are many competing technologies such as PCM [34, 105, 192], STT-RAM [162], ReRAM [14], and CTN [47] for constructing NVM devices.

While NVM devices are still evolving, several products are currently available in the market. These are 3D-XPoint Optane devices from Intel and ReRAM devices from Crossbar. There are also substitute technologies such as battery-backed devices that provide functionalities similar to NVM technologies. We first cover the range of NVDIMMs in the market then continue our discussion with the actual NVM technologies.

In practice, durable memory interfaces come in the form of a non-volatile dual in-line memory module (NVDIMM). NVDIMMs can be attached to the memory bus of a server, which is NVM compatible, to provide durable memory. There are several alternative NVDIMM options to choose from, such as NVDIMM-F, NVDIMM-N, and NVDIMM-P [106, 152].

**NVDIMM-F** is NAND Flash storage attached to the memory bus. Compared to DRAM, it can have higher capacities. It has the bandwidth of Flash storage and is much slower than DRAM. NVDIMM-F uses block-based storage.

**NVDIMM-N** is battery-backed DRAM with NAND Flash. The program accesses the DRAM with a byte-addressable interface. If a power failure occurs, the data from DRAM is copied to the Flash storage. Either a battery or a supercapacitor ensures power during the data transfer. The capacity is limited by the DRAM size. In 2019, the market share of NVDIMM-N was 72.5% [152].

**NVDIMM-P** interface combines DRAM and a non-volatile device such as PCM, STT-RAM, ReRAM, and CTN to provide high capacity main memory. NVDIMM-P provides a byte-addressable interface and can be used as a durable memory device.

NVDIMM-P interface is the recent technology that allows a modern NVM technology to be deployed to run on a server. In this thesis, we consider only NVM devices with an NVDIMM-P interface.

There are several NVM technologies that are commercially available, such as Intel Optane and Crossbar ReRAM. Crossbar Inc. [13] released NVM devices based on ReRAM technology. The specifications state that the ReRAM device has a maximum of  $4\mu s$  random read latency and a maximum of  $4\mu s$  of write latency without caching. The device supports  $10^5$  write cycles.

#### 1.1.1 Intel Optane

Intel released their 3D-XPoint NVM device based on PCM technology in cooperation with Micron. The NVM device is commercially available under the brand name of Intel® Optane<sup>TM</sup> DC Persistent Memory (Intel Optane DCPMM). Optane comes in a variety of capacities ranging from 128GB to 512GB [15]. Optane devices are cost-effective compared to DRAM. Dell's server price list specifies approximately \$2700 for 128GB of DRAM and \$940 for 128GB of Optane (DRAM is approximately 3x costly) [12].

| Device             | Read | Write |

|--------------------|------|-------|

| DRAM               | 106  | 77    |

| Optane             | 7    | 2     |

| Optane-Interleaved | 39   | 14    |

Table 1.1 – Approximate DRAM and Optane maximum bandwidth (in GB/s) characteristics.

Table 1.1 depicts the maximum bandwidths for the Intel Optane device. Optane is slower than DRAM [188, 91]. Yang [188] reports that NVM's sequential read latency is 2x DRAM and its random read latency is 3x. However, peak NVM read bandwidth is approximately 6% of DRAM and peak write bandwidth is approximately 3% of DRAM. Interleaving can improve NVM bandwidth, but DRAM still has higher bandwidth.

For the rest of the thesis, we focus solely on Optane as an NVM device and ignore the other technologies. There are several reasons for this decision. Servers using Optane are widely available. Optane is exhaustively studied [69, 91, 120, 180, 184, 188] and its performance characteristics are well-known. The reported measurements match the promise of NVM, which is a high-capacity durable memory device with performance nearing DRAM. Many enterprises such as Facebook, Oracle, Huawei, Alibaba, and Tencent have already incorporated Intel Optane into their data centers or are in the process of integration [5, 56].

We will not consider Crossbar ReRAM, as we do not have access to ReRAM based devices and its reported latencies are an order of magnitude worse than DRAM. We will not consider NVDIMM-N as battery-backing introduces its own fault-tolerance problems and complications. Batteries can fail, increase hardware cost, consume space, require cooling, and overall complicate fault-tolerance and system testing [97].

#### **Intel Optane Operation Modes**

Optane has different modes of operation [8] in which Optane acts either as volatile memory or as a durable memory device. These modes are *Memory Mode* and *App-Direct Mode*. There is also *Mixed Mode*, which is a combination of these two modes.

**Memory Mode** uses Optane as the backing store for volatile main memory. DRAM is used as a direct-mapped physically indexed and physically tagged cache for NVM with 4KB

granularity [69]. Since NVM offers high-density memory, the program's main memory benefits from Optane's large capacity. DRAM caching can improve performance compared to directly accessing NVM. Unfortunately, the DRAM cache is volatile and the NVM backing store is not kept consistent, so the program data is not accessible after program execution or power failure.

**App-Direct Mode** provides durable memory to a program. The program maps the NVM device into its virtual address space and accesses memory locations in NVM using load and store instructions. The writes that are flushed from the caches into NVM are durable and available even after a power failure. In this mode, DRAM acts as a normal volatile memory and does not act as a cache.

**Mixed Mode** allows use of both Memory Mode and App-Direct Mode. A portion of NVM memory can be used for Memory Mode while the remaining portions can be allocated for App-Direct use. This allows some part of NVM to be used as volatile main memory while the rest is durable memory.

For the remainder of the thesis, we focus on App-Direct Mode and consider NVM as a durable memory device. We mainly focus on the performance challenges that arise from introducing crash consistency and checking the correctness of the implementation. We briefly discuss Mixed Mode to extend the capacity of DRAM. We defer a more detailed discussion of NVM programming in App-Direct Mode to section 2.1.

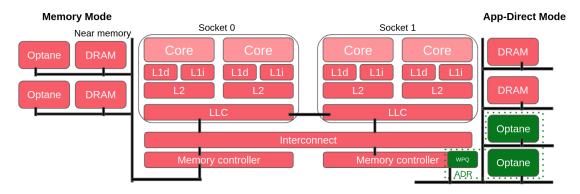

Figure 1.1 – Intel Optane platform.

Figure 1.1 shows an Intel Cascade Lake *x86-64* machine [155, 188] using Optane with different modes. We briefly explain each component in the figure. The cores perform computation and data processing. The program normally uses L1 (data and instruction), L2, LLC (last-layer cache) caches to ensure fast data access. Caching buffers modifications to memory.

Optane uses Intel's proprietary DDR-T interface [188] to communicate with the memory controller. The interface is similar to DDR4 and uses cache-line granularity (64B) for data transfers. It is possible to bypass the processor caches and directly send data to the memory controllers using *x86-64* non-temporal move instructions.

The left side shows one possible configuration, which is the Memory Mode. DRAM acts as a cache to NVM and can buffer the modifications.

The right side of the figure depicts App-Direct Mode. The region within the green boundary indicates the persistence domain and is power-fail safe. Any data within the persistent domain is ensured to be durable by the underlying hardware. The persistence domain includes Optane and Write-Pending Queues (WPQs) of the memory controller. On power failure, Asynchronous DRAM Refresh (ADR) allows WPQs to drain its contents to NVM. The rest of the hardware including CPU registers, caches, and DRAM are volatile and lose data upon power failure. We explain the importance of the ADR assumption to our work in section 2.1.1.

#### 1.2 Principle Problems for Programming NVM

The simple model presented in figure 1.1 depicts the critical issues related to NVM programming: processor caches are volatile. During a power failure, all program data residing in the caches are lost. This power failure can leave the program data in NVM in an unrecoverable state and can lead to runtime errors after a restart [104]. The cache lines can be evicted differently than the program order leading to unexpected states [40]. Furthermore, failure can happen while an operation is ongoing.

```

book* create_book(title, author, ...){

//allocate and fill the book

b→ title = title;

b→ author = author;

...

return b;

}

```

Figure 1.2 – Book example for a library program.

Consider the library example in figure 1.2 to motivate inconsistencies due to power failure. The library program stores a list of books. The code in the figure 1.2 creates a new book, which is later added to the list and made visible to the users. This program is incorrect.

| Book Attributes      | Title                 | Author    |

|----------------------|-----------------------|-----------|

| Initial NVM State    | -                     | -         |

| Cache State          | Computer Architecture | Patterson |

| Possible NVM State 1 | -                     | -         |

| Possible NVM State 2 | Computer Architecture | -         |

| Possible NVM State 3 | -                     | Patterson |

| Possible NVM State 4 | Computer Architecture | Patterson |

Table 1.2 – Possible NVM states for book example.

Table 1.2 shows the possible states that can occur after a crash. Initially, the title and

the author fields are not modified and contain old data. Once the create\_book function completes, the caches reflect the changes to the book and contain the name as well as the author of the book.

If additional code for durability is not introduced, power failure at the end of the create\_book function can leave the book data in NVM in a corrupt state. There are 4 possible NVM states for the book data if we just consider the two fields. The book is not updated in NVM and the old data remains unwritten (State 1). Only the title (State 2) or the author (State 3) fields of the book are updated. The book is updated completely (State 4).

A crash at the end of the create\_book function creates uncertainty about the possible NVM states. If the book is added to the list in States 1-3, then users might see incorrect data after a power failure.

```

book* create_book_tx(title, author, ...){

transactional {

//allocate and fill the book

b→ title = title;

b→ author = author;

return b;

}

}

```

Figure 1.3 – Book example with transactions.

Transactions [76] can be used to provide atomic durability. Figure 1.3 sketches the use of a transaction to avoid bad states.

| Book Attributes      | Title                 | Author    |

|----------------------|-----------------------|-----------|

| Initial NVM State    | -                     | -         |

| Cache State          | Computer Architecture | Patterson |

| Possible NVM State 1 | -                     | -         |

| Possible NVM State 2 | Computer Architecture | Patterson |

Table 1.3 – Possible NVM states for transactional book example.

Table 1.3 shows the states for execution of the book creation function with transactions. When the code region atomically executes, either the book is created properly or the NVM region is left untouched. There is no partial update of NVM after execution. For safety, the book insertion to the list should also be a single atomic transaction.

#### 1.3 Crash-consistency Challenges

There is no free lunch when it comes to using a crash-consistency mechanism for NVM. There are trade-offs between different crash-consistency mechanisms. They have different runtime performance, space, recovery overhead costs. We leave the detailed discussion of crash-consistency mechanisms to section 2.2.

#### 1.3.1 Cost of Ordering Persistent Writes

To provide atomic durability [155], crash-consistency mechanisms usually rely on cache line flush instructions to force cache line contents back to NVM and fence instructions to ensure that these instructions complete. Otherwise, the program can use non-temporal move instructions with a fence instruction for persistent writes. Executing these instructions for persistent writes is costly and can reduce program performance [118, 177].

#### 1.3.2 Cost of Using Optane

Besides the cost of ordering persistent writes to NVM, Optane has intrinsic costs. Crash consistency designs must take into account the peculiar characteristics of the underlying hardware. Optane has latencies close to DRAM and provides good performance. However, DRAM is still significantly faster than Optane [91, 188]. Moreover, Optane performs worse under heavy concurrent load, mixed-access patterns (mixed read/writes), and random access patterns [91, 188].

#### 1.3.3 NVM Programming Correctness

NVM programming is a challenging endeavor. Programs [126] that use NVM as a durable memory device are mostly written in bug-friendly unmanaged and unsafe programming languages, such as C/C++ [109]. Reasoning about cache line write-back instructions and ordering persistent writes is not conventional in programming and can be challenging.

Using a library for NVM programming remains challenging. The programmer still needs to use the library correctly, for example, finding the right boundaries for a transaction. In addition, libraries such as Intel PMDK offer a complicated programming interface that expects a programmer to use its logging interface to denote persistent memory regions for a transaction.

#### 1.4 Thesis Statement

There should be a diverse set of tools for NVM programming to address the programmer's needs. The goal of this thesis is to expand the software support for NVM programming by providing low-overhead crash-consistency mechanisms through the use of checkpointing

techniques and static analysis techniques for discovering NVM programming bugs.

Instead of using transactions, we suggest using checkpointing [1]. Checkpointing avoids eagerly propagating changes to NVM and can persist writes in batches. We show that periodic checkpoints every few milliseconds are achievable with low overheads for NVM programming. In the thesis, we also show that, by carefully exploiting DRAM, the slowdown due to crash-consistency can be greatly reduced over transaction-based systems.

In addition, NVM programming requires tools that reassure a programmer after writing a program. If a power failure occurs, the last thing a programmer wants is to have a program failure after a restart or to find the program data in an inconsistent state. It is necessary to have tools that allow the programmer to reason about the order of the persistence of writes. To achieve this goal, we introduce a static data flow analysis tool to find NVM programming bugs during the compile time.

The statement of this thesis is:

We can provide software support for NVM programming by building checkpointing tools that allow building durable data structures with low crash-consistency overhead. We can also build tools based on dataflow analysis for finding NVM programming bugs without executing the program code.

Firstly, we present *InCLL* a fine-grained checkpointing technique tailored for NVM with an undo logging strategy. *InCLL* shows that fine-grained intervals, on the order of milliseconds, are feasible to build durable data structures for NVM. Instead of solely relying on an external undo log for backing up data before doing in-place updates, *InCLL* keeps the log inside a cache line to avoid explicit cache-line write-back instructions, effectively improving runtime performance. *InCLL* ensures that no cache-line write-backs are necessary for the fast path data structure modifications using in-cache-line logging and fine-grained checkpointing. We describe our modifications to Masstree [117] and evaluate *InCLL*.

Secondly, we present *CpNvm* to correct the shortcomings of the *InCLL* algorithm. *InCLL* was specifically implemented for Masstree and required careful reasoning about the data structure layout. *InCLL* periodically executes a privileged instruction to flush the entire cache hierarchy (Dalí-style cache flush). The invalidation and eviction create challenges in multitenant systems and impact runtime performance by periodically increasing the cache-miss rate. Moreover, *InCLL* does not take the performance characteristics of Optane into account and experiences significant performance degradation when running on Optane.

With *CpNvm*, we marry the ideas from traditional application-level checkpointing and durable data structure design. We tailor *CpNvm* for Optane by using DRAM as a middle layer to do write-combining before propagating modifications to NVM. Heavily read or written data resides in DRAM, where it can be accessed at a fraction of the cost, and only modified values propagate to NVM periodically. *CpNvm* API is general and easy to use with a simple API. We

show that *CpNvm* has low overhead for Masstree and Memcached with minimal code changes in both benchmarks.

Finally, we present *FlowNvm* to find bugs in NVM programs using static analysis. To reduce the state explosion of a program, we reduce the problem to a dataflow analysis and explore properties across all program paths. *FlowNvm* detects issues in program ordering, which can leave program data in NVM in an inconsistent state. *FlowNvm* defines programming patterns and anti-patterns and uses inter-procedural data flow analysis to detect the validity of the patterns and occurrence of the anti-patterns to find bugs. *FlowNvm* design is inspired by well-known correctness bugs such as failing to order the persistent writes properly or performance bugs such as flushing a cache line unnecessarily.

In summary, this thesis makes the following contributions:

InCLL, a fine-grained checkpointing technique for building durable data structures

with an undo logging approach, which minimizes the number of explicit cache line

write-back instructions for fast-path data structure modifications.

Specifically, its contributions are:

- Fine-Grained Checkpointing, a technique to ensure a consistent, quickly recoverable data structure in NVM after a system failure.

- In-Cache-Line Logging, an undo-logging technique that enables recovery of the state from the beginning of an epoch without requiring cache-line flushes in the normal case.

- Implementation of these techniques for the Masstree data structure and making Masstree durable.

- Evaluation of durable Masstree to demonstrate a low (< 20% DRAM evaluation) runtime overhead cost.

- *CpNvm*, a checkpointing tool using DRAM write-combining during execution and an NVM copy for fast recovery with a simple application-level checkpointing API.

Specifically, its contributions are:

- An application-level checkpointing API with checkpointing-based crash-consistency guarantees with low-overheads.

- The design and implementation of *CpNvm*, a new C/C++ library that implements these checkpoints at low cost.

- Evaluation of *CpNvm* using Masstree and Memcached on Optane, demonstrating its low run-time overhead.

- *FlowNvm*, static inter-procedural data flow analysis tool for finding NVM programming bugs using program properties and anti-patterns.

Specifically, its contributions are:

- Identification and description of several NVM programming patterns and antipatterns.

- Description of static program analysis for identifying many instances of these pattern violations and the existence of the anti-patterns.

- Implementation of an extension to LLVM for C/C++ applications that identifies and reports these bugs.

- Evaluation of this tool on existing NVM programs and demonstration that the tool can detect and report previously known errors as well as a new bug.

#### 1.5 Thesis Organization

The thesis organization starts with detailed background information followed by the contributions. Chapter 2 provides the background context for NVM Programming, crash-consistency mechanisms for NVM, and checkpointing. Chapter 3 describes the design, implementation and evaluation of *InCLL*. Chapter 4 describes the design, implementation and evaluation of *CpNvm*. Chapter 5 describes the design, implementation and evaluation of *FlowNvm*. Chapter 6 summarizes the key points of the thesis, presents the future work, and concludes.

#### 1.6 Bibliographic Notes

The major implementation work for *InCLL* was done in 2018-2019 and Optane evaluations were done in 2020. *InCLL* is a joint work previously published with Nachshon Cohen and Hillel Avni in the paper: "Fine-Grained Checkpointing with In-Cache-Line Logging". Nachshon came up with the idea and contributed to the implementation. Hillel Avni contributed to the design. The Optane evaluation was done independently.

## 2 Background

In this chapter, we describe NVM programming in detail and provide the technical background to understand the contributions. We describe how programmers can use NVM as durable memory, the ordering axioms for properly persisting writes, and the failure model. We illustrate high-level approaches for designing crash-consistency mechanisms. We explain the performance advantages of using checkpointing as a relaxed crash-consistency model.

#### 2.1 NVM Programming

We first describe the NVM programming specification [164] and explain how to order the writes to make them persistent. We specify the axioms and instructions that are necessary for ordering persistent writes. We specifically focus on the *x86-64* instruction set and Linux operating system, which is our evaluation setting. We discuss some other instruction sets, deprecated configurations, and operating systems.

The Storage Networking Industry Association (SNIA) is a non-profit organization that produces standards for the storage industry. SNIA'S NVM Programming Model specification is currently the accepted standard for using NVM. The first version was published in 2013 and contains the memory-mapped file paradigm for using NVM as a durable memory device. We discuss the recent version of the standard (v1.2 [164]) published in 2017. We mainly focus on the App-Direct Mode with a byte-addressable interface, not the File I/O Mode, which provides block-level access.

The NVM Programming Model specifies that the primary method to provide durable memory address space for NVM programming is to use *memory-mapped* files with the *Direct Access* (*DAX*) feature. A programmer uses the mmap system call on Linux and MapViewOfFile call on Windows to map NVM into the processor's virtual address space. A programmer then accesses NVM through loads and stores to these mapped addresses.

Traditionally, modifying data in durable storage media such as SSD or disk requires bringing pages from the storage media to page caches, which are in DRAM memory. In this situation,

calling mmap [10] duplicates the persistent data in memory. The second copy in the page cache wastes space [24] and can cause performance degradation [100]. Both Linux and Windows support the *DAX* feature, which allows a program to bypass page caches and access NVM directly. DAX is a crucial feature for NVM Programming as it eliminates the unnecessary overhead of the kernel I/O stack and context switching. However, using DAX introduces programming challenges when dealing with failures such as system crash, power failure, or reboot.

#### 2.1.1 Failure Model

To understand the challenges related to NVM programming, we must first discuss its failure model. Our failure model is based on the *fail-stop/crash-recovery* as described in Atlas [32]. If a failure such as a power failure occurs, the process crashes and stops. After the cause of the failure is mitigated, such as providing power again, the process restarts and continues execution. We do not consider Byzantine faults [103].

Because of the failure model, the notion of persistence domain becomes important. A persistence domain specifies which parts of the hardware are durable (retain values) even after a power failure. The current industry standard is to have *Asynchronous DRAM Refresh (ADR)* as the persistence domain [155]. We described ADR in section 1.1.1. ADR is available with Cascade Lake *x86-64* processors.

The NVM Programming specification also includes another persistence domain configuration, *Enhanced Asynchronous DRAM (eADR)* [11]. *eADR* extends the persistence domain to include the processor caches, effectively making caches durable. The eADR feature is provided with 3rd generation Ice Lake chips.

For the thesis, we only consider the ADR persistence domain. Both *InCLL* and *FlowNvm* require and assume an ADR system. On the other hand, *CpNvm* offers benefits to eADR systems as its main goal is to improve the performance of a data structure while using Optane.

#### 2.1.2 NVM Programming Primitives

The key design decisions in this thesis stem from the fact that processor caches are **volatile** (ADR persistence domain) and a program might crash at a random point.

In *x86-64*, NVM programming primitives allow (1) ordering writes and (2) guarantee that the data is in the persistence domain. Ordering and persistence can be done using cache line flush or non-temporal move combined with fence instructions. For normal stores to the memory, controlling the eviction of cache lines explicitly is necessary for persistence. *x86-64* provides cache line flush instructions (clflush, clflushopt, clwb) or entire cache hierarchy flush instruction (wbinvd) to evict cache lines from the software. Another approach is to bypass

the caches for persistent writes and propagate data directly to the persistence domain. x86-64 provides non-temporal move instructions (movnti,movntq, movntps, movntpd, movntdq, maskmovq, maskmovdqu) to bypass the caches. Fence instructions are useful for ordering both cache line flush instructions and weakly-ordered non-temporal move instructions. x86-64 provides fence instructions (sfence, mfence) to ensure that outstanding memory operations are finished.

#### Cache Flush

These instructions flush cache lines:

clflush Invalidates and transfers a single cache line to the memory controller.

**clflushopt** Invalidates and transfers a single cache line to the memory controller. Instruction executes asynchronously.

**clwb** Transfers a single cache line to the memory controller. The cache line is not invalidated. Instruction executes asynchronously.

**wbinvd** A privileged serializing instruction that invalidates the entire cache hierarchy of the CPU and writes back all dirty cache lines.

Invalidating a cache line removes it from the cache hierarchy. Invalidating ensures that the next access to it will trigger a *cache miss*. clflush is synchronous and ensures that the operation completes when the instruction finishes. clflushopt and clwb are asynchronous instructions that are non-blocking and can be run concurrently for different cache lines. Both clflushopt and clwb initiate the cache line transfer. However, these instructions return before the cache line is flushed to the memory controller.

The clwb instruction is expected not to invalidate the cache line explicitly. However, it should be noted that Cascade Lake chips use clflushopt's mechanism for the implementation of clwb and clwb invalidates the cache line [170]. We do not rely on clwb instruction in our checkpointing tools.

wbinvd invalidates all cache entries and writes back dirty cache lines on the CPU that executes the instruction. The wbinvd instruction flushes and writes back the L1 and L2 caches local to the CPU and the shared L3 caches. It is synchronous and waits until completion. As wbinvd invalidates the cache hierarchy, subsequent program performance will be lower due to cache line misses. Sizes of the caches are a major factor in the execution time of wbinvd instruction. As wbinvd is serializing, a fence instruction is not necessary for ordering.

#### Non-temporal Move

Non-temporal move instructions allow bypass of the caches [88]. The cache line corresponding to the memory address is not fetched and the cache hierarchy is not used. Writes directly propagate to the memory controller using *write-combining (WC)* buffers. Non-temporal move instructions are weakly ordered and require fence instructions for ordering. Otherwise, non-temporal stores to two different memory regions can happen independent of the program order and can lead to bugs.

#### **Fence**

The Intel *x86-64* memory model is *Total-Store-Order (TSO)* [146]. In TSO, stores cannot be reordered after stores. Raad et al. [147] provide a formal model for the semantics of the ordering of operations for *x86-64* systems. In the thesis, we focus only on a subset of the model. We consider the ordering of the write instructions, non-temporal move instructions, cache-line flush instructions, and fence instructions.

These instructions act as a fence:

sfence Orders stores and flushes.

**mfence** Orders loads, stores, and flushes.

Both sfence and mfence are useful for ordering stores and flushes. However, mfence also orders loads. Usually relevant work in this field solely focuses on sfence as a fence instruction [159]. A single fence instruction is sufficient to ensure the durability of all the previous cache line write-back and non-temporal move instructions.

```

\begin{array}{|c|c|c|c|c|c|}\hline & x = 1; & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & &

```

Figure 2.1 – Possible ways to write data to NVM durably.

Figure 2.1a shows an example of clflushopt usage. Figure 2.2 shows how multiple cache lines are flushed concurrently. Completion of the write back is ensured by the sfence.

We can think of clflush as executing a flush and a fence instruction. The reason is that once clflush executes, it is synchronous and runs to completion. Figure 2.1b shows an example for clflush.

Non-temporal move instructions are weakly ordered. It is possible that two writes to the

```

// x and y are in different cache lines x = 1; y = 1; clflushopt(&x); // initiate write back of cache line belonging to x clflushopt(&y); // initiate write back of cache line belonging to y sfence(); //both x and y are durable

```

Figure 2.2 – Flushing multiple cache lines.

same cache line do not occur in program order unless there is a fence instruction in between. Figure 2.1c shows an example for non-temporal move instructions.

Another important idea is to order the writes to the same cache line. Ensuring that a write reaches NVM is expensive. On the other hand, ordering the writes to a cache line is almost free. If there are two writes to the same cache line, the order of writes reaching the cache is the same as the order of reaching the persistence domain.

It is possible to use release memory ordering [25] from C++11 to order writes to the same cache line. A release fence creates a *happens-before* relation between writes. This release fence ensures that the writes are ordered as intended by the program order. In x86-64, a release fence does not incur any extra runtime overhead and only prevents the compiler from reordering writes.

#### **Ordering Axioms**

In this section, we define the formal ordering axioms, which we use for building crash-consistent NVM programs. Formally, we assume different memory regions x, y and denote the cache line addresses via c(x) and c(y). c(x) = c(y) denotes that the memory regions are in the same cache line. Table 2.1 defines the formal operations and the relations that we use.

| Operation       | Explanation                                                   |  |

|-----------------|---------------------------------------------------------------|--|

| w(x)            | write to memory region x                                      |  |

| $w_n(x)$        | non-temporal write to memory region $x$                       |  |

| f(x)            | synchronous flush memory region $x$ (e.g., clflush)           |  |

| $f_o(x)$        | asynchronous flush memory region $x$ (e.g., clflushopt, clwb) |  |

| $p_f()$         | persist fence (e.g., sfence)                                  |  |

| Relation        | Explanation                                                   |  |

| < <sub>hb</sub> | standard happens-before                                       |  |

| < <sub>p</sub>  | persists-before                                               |  |

| ~_p             | both operations can persist in any order                      |  |

Table 2.1 – Formal operations and relations for NVM programming.

The main goal is to ensure the persistence of writes. For crash-consistency mechanism design,

it is necessary to be able to order the persistent writes correctly. Specifically, our goal is to persist w(x) before persisting w(y) if x is written before y.

The following axioms determine the order of persistence for normal write operations:

- 1)  $w(x) <_{hb} w(y) \land c(x) = c(y) \Rightarrow w(x) <_{p} w(y)$  (same cache-line)

- 2)  $w(x) <_{hb} w(y) \land c(x) \neq c(y) \Rightarrow w(x) \sim_p w(y)$  (different cache-line)

The first axiom states that if the writes w(x) and w(y) are to the same cache line, the first write w(x) will not persist later than the second write w(y). The second axiom states that two writes can persist out-of-order if the writes are to different cache-lines.

Figure 2.3 – Program without flush, non-temporal move, and fences.

The second axiom can lead to the situation as presented in figure 2.3. The program writes value 1 to x, then writes value 1 to y where initially both x and y are 0. If the program crashes after executing y = 1 and is restarted afterward, NVM can be left in a state where the value of y is 1 and the value of x is 0. This is inconsistent with the program order and can lead to hard-to-find bugs [115].

We need to ensure that a write w(x) persists before write w(y). The following axioms show how to enforce this ordering:

- 3)  $w(x) <_{hb} f_o(x) <_{hb} p_f(x) <_{hb} w(y) \Rightarrow w(x) <_p w(y)$  (asynchronous flush)

- 4)  $w(x) <_{hb} f(x) <_{hb} w(y) \Rightarrow w(x) <_{p} w(y)$  (synchronous flush)

- 5)  $w_n(x) <_{hb} p_f(x) <_{hb} w(y) \Rightarrow w(x) <_p w(y)$  (non-temporal move)

Axioms 3, 4, 5 ensure the durability of the writes by propagating the write to the persistence domain. The specific programming pattern ensure that the second write does not propagate to the persistence domain before the first write. The third axiom specifies that asynchronous flush needs a fence instruction to complete. The fourth axiom specifies that after synchronous flush instruction completes, the write is durable. The fifth axiom specifies that a non-temporal move requires a fence instruction to order the two writes. In these axioms (3-5), the second write w(y) can be done using non-temporal move instruction  $w_n(y)$  and the persistence order remains the same.

#### 2.1.3 Alternative and Earlier Programming Models

The current NVM programming specification [164] evolved over many years. We briefly mention earlier models to set our work apart from the previous models. When persistence domain did not include the buffers in the memory controllers, programmers used the pcommit [4] instruction to explicitly flush memory controller buffers to NVM. The pcommit is now deprecated. In earlier models, clflush was weakly ordered and required the use of the mfence instruction [88].

ARM has a weak memory ordering model [148]. Stores can be reordered with respect to other stores [110], which can be prevented by using a fence instruction such as dmb. ARM provides durability and ordering instructions. The "Data or unified Cache line Clean by VA to PoP" (dc cvap) instruction, which is similar to clflushopt, flushes a cache line to the memory controller asynchronously. ARM also provides "Data or unified Cache line Clean by VA to PoDP" (dc cvadp) instruction, which flushes a cache line asynchronously to NVM directly. This is useful for cases where the programmer does not trust the persistence of the ADR domain. "Data Synchronization Barrier" (dsb) is a memory barrier instruction, which has similarities to mfence as it orders loads and stores while ensuring the completion of the previous write-back instructions.

If *DAX* mode is not used, range-based msync or file-based fsync and fdatasync calls can be used. These calls are suitable for the File I/O mode and ensure that the changes to the memory-mapped file get propagated to NVM durably. These calls are block-based. For *DAX* it is better to do cache line flushes for performance [187].

There are many persistency models proposed in academia [90, 137, 146, 148] and different instruction set and hardware proposals [126, 159] to handle persistence.

#### 2.1.4 Optane Configuration

In this section, we explain Optane configuration [6] used for evaluating our checkpointing contributions. The bug finding tool does not require a machine with Optane. We use ipmctl and ndctl command-line programs to configure NVM. ipmctl program is useful for configuring the operation mode and enable/disable interleaving. ndctl program is useful for using Optane as a durable memory device with a byte-addressable interface in App-Direct Mode. Figure 2.4 and 2.5 show how to configure NVM.

```

> ipmctl create -goal MemoryMode=100 #Memory Mode configuration (1)

> ipmctl create -goal PersistentMemoryType=AppDirect #App-Direct configuration (2)

> ipmctl create -goal MemoryMode=25 Reserved=50 #Mixed Mode configuration (3)

```

Figure 2.4 – Provisioning NVM for different operation modes using ipmctl.

```

> ndctl create—namespace —m fsdax #Namespace creation using fsdax (1)

> mkfs.ext4 —F /dev/pmem0 #Create a file system to manage the device (2)

> mount —o dax /dev/pmem0 /mnt/memext4 #Mount (3)

```

Figure 2.5 – Durable memory device configuration using ndctl.

#### 2.2 Crash-Consistency Mechanisms for Programming

To recap, *crash consistency* allows a program to ensure a consistent state after events such as power failure, system failure, reboots. We present high-level design ideas [114] for building crash-consistency mechanisms. The high-level design ideas are mainly software-based solutions and do not require architectural changes to the hardware.

To implement crash-consistency mechanisms, we need to ensure that a set of operations can execute with *atomic durability* [73]. *Atomic durability*, is an **all-or-nothing** characteristic. It states that either all operations commit their changes to durable storage or none of the operations commit to durable storage.

Completion of a set of operations can be thought of in terms of either *transactions* [76] or *check-pointing* [99]. Transactions provide *atomicity, consistency, isolation, durability* (ACID) [145] properties. Transactions traditionally have stronger guarantees.

An alternative is to use checkpointing and persist data after a passage of time. Checkpointing [153] takes a snapshot of the program state and stores the state in a safe location where it can be accessed after a restart. The state can be the program state [138] including the stack and the registers or a subset of the program data in the heap [185]. In either case, recovery after a crash returns the state to the last valid checkpoint. The safe media can be durable storage such as disk and SSD [138], NVM [185], parallel file system [22] or memory of other processes [139]. We provide a detailed discussion about checkpointing in section 2.3.

Implementations of transactions and checkpointing relies on several design ideas and mechanisms. The *x86-64* ensures that up to 8-byte aligned stores are atomically executed [157]. We describe the high-level software design patterns (e.g., undo logging, redo logging, recovery via resumption, copy-on-write, operational logging) to provide a context for our design conributions.