Development of a Data Concentrator ASIC for the High Luminosity upgrade of the CMS Outer Tracker detector with tracking trigger

Présentée le 10 juin 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de systèmes microélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### Simone SCARFÌ

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury Prof. Y. Leblebici, Dr K. Kloukinas, directeurs de thèse

Dr P. Valerio, rapporteur

Dr R. Beccherle, rapporteur

Prof. A. P. Burg, rapporteur

### **Abstract**

With the increasing capabilities of the microelectronics technology, future particle detectors in high energy physics will be able to yield high level features that are not only simple geometrical positions or energy measurement in the silicon sensors used, but also high level primitives. The ability to compute such high level primitives in near real-time is what we characterize as "intelligence" and will allow constructing detectors with novel functionalities and easing the offline analysis in experiments to handle immediately more complex features of the measurements.

This thesis presents a novel approach adopted for the development of silicon sensor detectors capable of rejecting locally signals from low transverse momentum  $(p_T)$  particles. The basic concept consists of correlating signals in two closely-spaced sensors. The readout and control electronics for these type of sensors require the development of a set of ASICs that incorporate dedicated specialized signal processing techniques, generating in real time trigger primitives and transmitting them to the Level-1 (L1) central trigger system, while, at the same time, transmitting the L1 triggered data to the detector readout system. In order to exploit the full bandwidth of the optical fiber transmission links it is necessary to implement a data concentrator ASIC, called CIC (Concentrator IC).

The thesis focuses on system level studies needed to assist and develop the CIC ASIC architecture. In this context, system level simulations and modeling with modern EDA tools have been employed to optimize the readout chain and set synchronization techniques for the interconnects with the readout ASICs. The thesis describes also the CIC ASIC architecture and the prototype results to evaluate final performances. The developed CIC ASIC should be able to operate within a very tight power budget and in a radiation environment of 100 Mrad. Radiation tolerance design techniques have been employed in order to mitigate the effects of Total Ionizing Dose as well as of Single Event Upsets. For the implementation of the readout ASICs it is proposed to

use a 65 nm CMOS process.

During my doctoral studies I have developed a new methodology for readout chain modeling. In the target application, particles hits represent the input vectors of the readout chain. I could extract statistics from Monte Carlo data from physics simulations in worst case scenario and create a programmable input stimuli for a complex simulation environment with the full readout chain of the front-end ASICs, via the CIC ASIC to the off-detector electronics. Thanks to the simulation environment, developed in UVM and SystemVerilog, I could study and compare different architectures in terms of performances, power consumption and radiation tolerance. For the first time a clock-cycle accurate simulation of the complete readout electronics chain (from sensors to off-detector data receivers) is utilised in a particle physics experiment to enable the development of a chipset of ASICs and to facilitate their functional and performance verification.

My work is focusing primarily on the following topics:

- help in the development of the CIC ASIC to decrease the required readout bandwidth, power budget and radiation tolerance;

- architectural choices at RTL level for power optimization;

- development of radiation hardening techniques for the whole ASIC;

- full design from RTL, through synthesis, implementation and verification signoff of digital IP blocks, as the configuration block. Main requirements were radiation tolerance and power consumption optimization;

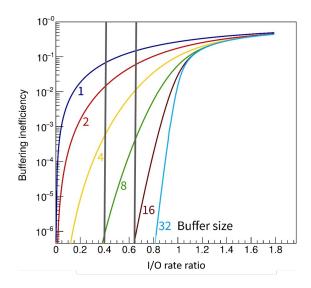

- FIFO sizing in the ASICs composing the readout chain to achieve a buffer inefficiency of  $10^{-6}$  in worst case particles occupancy and based on Poissonian arrival time of the signal requesting the full event;

- high energy particles can potentially flip every node in the circuit in the 65 nm CMOS technology. I have added a Single Event Effect (SEE) component to emulate particles effects on ASIC node to reproduce corrupted data packets at system level. I have helped developing a robust and complex FSM at the level of MPA and CIC ASICs for handling better system level synchronization issues arising due to SEE or FIFO overflow.

#### Résumé

Avec les capacités croissantes de la technologie microélectronique, les futurs détecteurs de particules en physique des hautes énergies pourront acquérir des caractéristiques de haut niveau qui ne sont pas seulement de simples positions géométriques ou des mesures d'énergie dans les capteurs au silicium utilisés, mais également des primitives de haut niveau. La capacité de calculer ces primitives de haut niveau en temps quasi réel est ce que nous qualifions d'intelligence et permettra de construire des détecteurs avec de nouvelles fonctionnalités et de faciliter l'analyse hors ligne dans les expériences pour traiter immédiatement des caractéristiques plus complexes des mesures.

Cette thèse présente une nouvelle approche adoptée pour le développement de détecteurs de capteur au silicium capables de rejeter localement des signaux de particules à faible impulsion transversale (p<sub>T</sub>). Le concept de base consiste à corréler les signaux dans deux capteurs très rapprochés. L'électronique de lecture et de contrôle pour ce type de capteurs nécessite le développement d'un ensemble d'ASIC qui intègrent des techniques de traitement de signal spécialisées dédiées, générant en temps réel des primitives de déclenchement et les transmettant au système de déclenchement central de niveau 1 (L1), tout en en même temps, transmettre les données déclenchées par L1 au système de lecture du détecteur. Afin d'exploiter toute la bande passante des liaisons de transmission par fibre optique, il est nécessaire de mettre en œuvre un concentrateur de données ASIC, appelé CIC (Concentrator IC). La thèse se concentre sur les études au niveau du système nécessaires pour aider et développer l'architecture CIC ASIC. Dans ce contexte, des simulations et une modélisation au niveau du système avec des outils EDA modernes ont été utilisées pour optimiser la chaîne de lecture et définir des techniques de synchronisation pour les interconnexions avec les ASIC de lecture. La thèse décrit également l'architecture CIC ASIC et les résultats du prototype pour évaluer les performances finales. L'ASIC

CIC développé devrait être capable de fonctionner dans un budget de puissance très restreint et dans un environnement de rayonnement de 100 Mrad. Des techniques de conception de tolérance aux radiations ont été employées afin d'atténuer les effets de la dose ionisante totale ainsi que des perturbation par une particule isolée (SEE). Pour la mise en œuvre des ASIC de lecture, il est proposé d'utiliser un processus CMOS 65 nm.

Au cours de mes études doctorales, j'ai développé une nouvelle méthodologie pour la modélisation de la chaîne de lecture. Dans l'application cible, les impacts de particules représentent les vecteurs d'entrée de la chaîne de lecture. J'ai pu extraire des statistiques des données de Monte Carlo à partir de simulations physiques dans le scénarion le moins favorable et créer des stimuli d'entrée programmables pour un environnement de simulation complexe avec la chaîne de lecture complète des ASIC frontaux, via le CIC ASIC vers l'électronique hors détecteur. Grâce à l'environnement de simulation, développé en UVM et SystemVerilog, j'ai pu étudier et comparer différentes architectures en termes de performances, de consommation d'énergie et de tolérance aux rayonnements. Pour la première fois, une simulation précise du cycle d'horloge de la chaîne électronique de lecture complète (des capteurs aux récepteurs de données hors détecteur) est utilisée dans une expérience de physique des particules pour permettre le développement d'un chipset d'ASIC, pour faciliter leur vérification fonctionnelle et la vérification des performances.

Mon travail se concentre principalement sur les sujets suivants:

- l'aide au développement du CIC ASIC pour réduire la bande passante de lecture requise, le bilan de puissance et la tolérance aux rayonnements;

- les choix architecturaux au niveau RTL pour l'optimisation de la puissance;

- le développement de techniques de durcissement par rayonnement pour l'ensemble de l'ASIC;

- la conception complète de RTL, à travers la synthèse, l'implémentation et la validation de vérification des blocs IP numériques, en tant que bloc de configuration. Les principales exigences étaient la tolérance aux rayonnements et l'optimisation de la consommation d'énergie;

- le dimensionnement FIFO dans les ASICs composant la chaîne de lecture pour atteindre une inefficacité de tampon de 10<sup>-6</sup> dans une situation critique d'occupation des particules et sur la base du temps d'arrivée poissonnien du signal demandant l'événement complet;

- l'ajout d'un composant SEE (Single Event Effect), étant donné la capacité des particules de haute énergie de potentiellement retourner tous les nœuds du circuit dans la technologie 65 nm CMOS, pour émuler les effets de particules sur le nœud ASIC afin de reproduire les paquets de données corrompus au niveau du système. J'ai aidé à développer un FSM robuste et complexe au niveau des ASIC MPA et CIC pour gérer de meilleurs problèmes de synchronisation au niveau du système résultant d'un débordement de SEE ou FIFO.

# **Contents**

| Ał | ostra   | ct / Rés | sumé                                                                   | 7    |

|----|---------|----------|------------------------------------------------------------------------|------|

| Li | st of ] | Figures  | S                                                                      | XV   |

| Gl | ossaı   | ry and   | Acronyms                                                               | xxi  |

| 1  | Intr    | oducti   | on                                                                     | 1    |

| 2  | The     | Challe   | enges of State of the Art CMS Outer Tracker Upgrade                    | 7    |

|    | 2.1     | Silico   | n for particle detection                                               | 8    |

|    | 2.2     | The C    | MS experiment upgrade for High Luminosity                              | 10   |

|    |         | 2.2.1    | The CMS tracker                                                        | 13   |

|    |         | 2.2.2    | Silicon tracker upgrade                                                | 14   |

|    | 2.3     | CMS t    | rigger system at HL-LHC                                                | 17   |

|    | 2.4     | Innov    | ative approach: the $p_T$ module concept $\ldots \ldots \ldots \ldots$ | 19   |

|    | 2.5     | CMS t    | tracker structure                                                      | 20   |

|    | 2.6     | The p    | T modules in the CMS Outer Tracker                                     | 21   |

|    |         | 2.6.1    | 2S-module structure                                                    | 22   |

|    |         | 2.6.2    | PS-module structure                                                    | 23   |

|    |         | 2.6.3    | Charge detection in the analog front-end electronics                   | 24   |

|    |         | 2.6.4    | Digital readout system                                                 | 27   |

|    |         | 2.6.5    | Data aggregation                                                       | 27   |

|    | 2.7     | PS-me    | odule and 2S-module studies                                            | 28   |

|    |         | 2.7.1    | Data bandwidth estimation for pT modules                               | 30   |

|    |         | 2.7.2    | Concentrator ASIC in pT modules                                        | 32   |

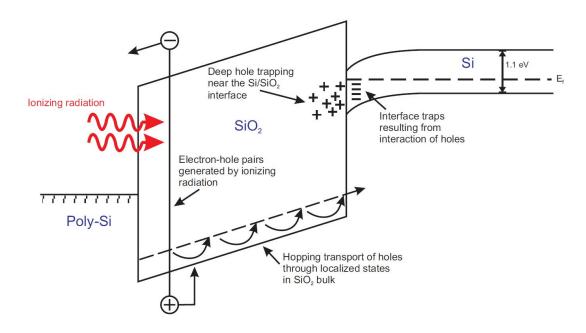

|    | 2.8     | Radia    | tion effects on CMOS technology                                        | 33   |

|    |         | 2.8.1    | Cumulative effects: Total Ionizing Dose and Displacement Damage        | e 33 |

|    |         | 2.8.2    | Single Event Effects                                                   | 35   |

| 3  | pT-1    | module   | es studies and system level simulation environment                     | 37   |

#### **Contents**

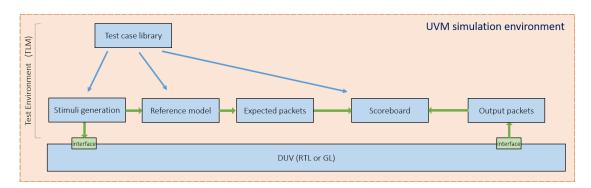

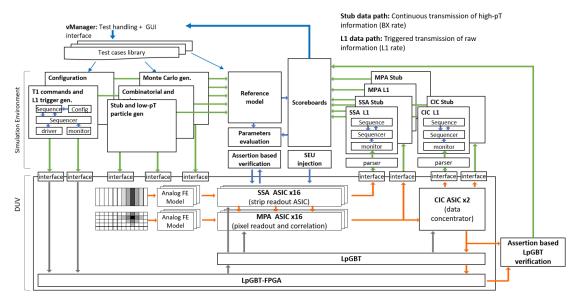

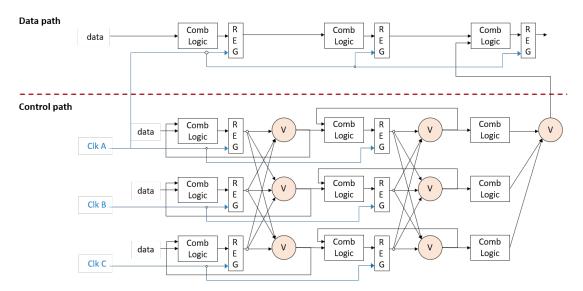

|   | 3.1 | Advan   | tages of a SystemVerilog and UVM simulation environment | 39  |

|---|-----|---------|---------------------------------------------------------|-----|

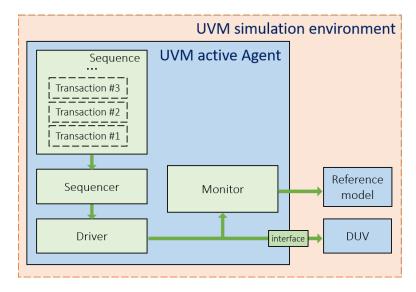

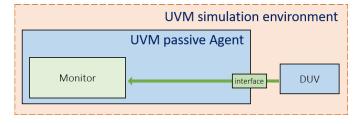

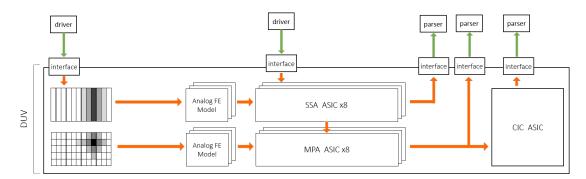

|   | 3.2 | UVM s   | simulation environment for pT-modules                   | 40  |

|   |     | 3.2.1   | UVM active Agent for stimuli generation                 | 42  |

|   |     | 3.2.2   | UVM passive Agent for DUV output                        | 43  |

|   |     | 3.2.3   | Reference model in TLM                                  | 44  |

|   |     | 3.2.4   | UVM Scoreboard component                                | 44  |

|   |     | 3.2.5   | Library of test cases                                   | 44  |

|   |     | 3.2.6   | Code and functional coverage                            | 45  |

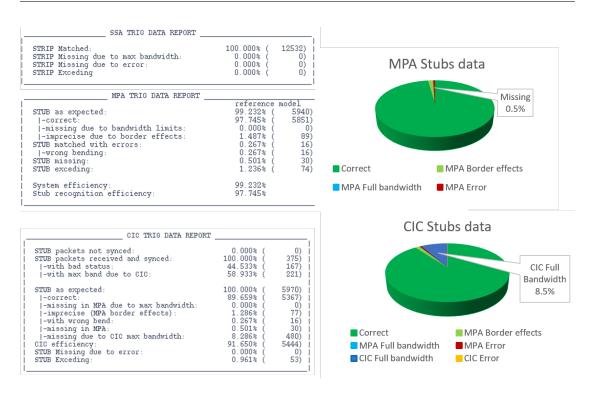

|   | 3.3 | CIC AS  | SIC studies for two different pT-modules                | 46  |

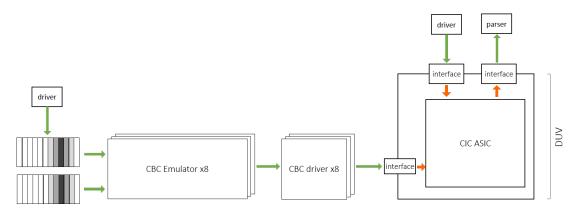

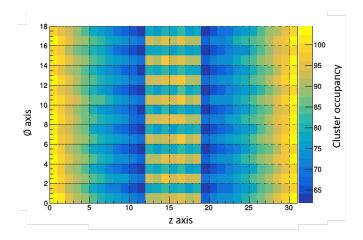

|   |     | 3.3.1   | Stub occupancy and efficiency studies for PS-module     | 47  |

|   |     | 3.3.2   | L1 data studies for PS-module                           | 48  |

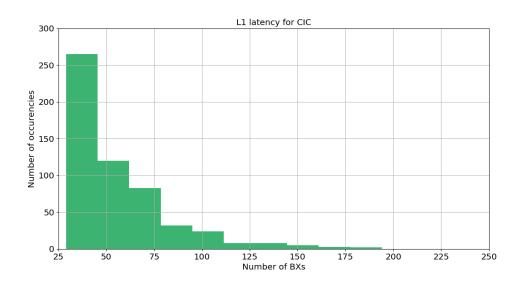

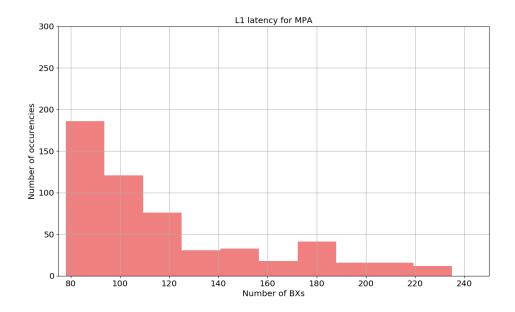

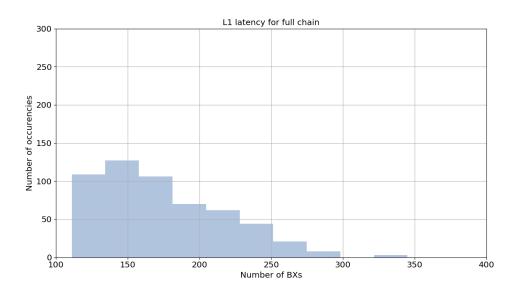

|   |     |         | 3.3.2.1 FIFO sizing methodology                         | 49  |

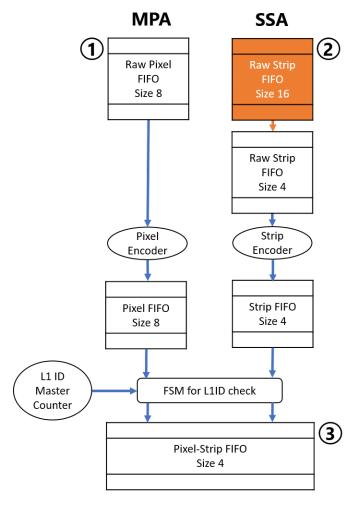

|   |     |         | 3.3.2.2 MPA-SSA buffer sizes and data rate studies      | 51  |

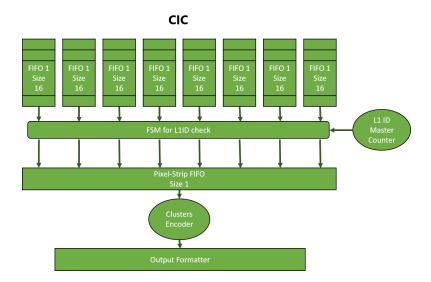

|   |     |         | 3.3.2.3 CIC buffer sizes and data rate studies          | 54  |

|   |     | 3.3.3   | SEU simulation                                          | 55  |

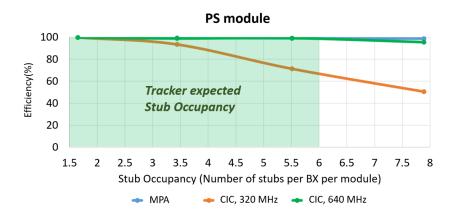

|   | 3.4 | LpGB    | Γ communication for pT-modules                          | 55  |

|   | 3.5 | UVM s   | simulation environment features and performances        | 56  |

|   |     |         |                                                         |     |

| 4 |     | _       | ent of the Concentrated Integrated Circuit ASIC         | 59  |

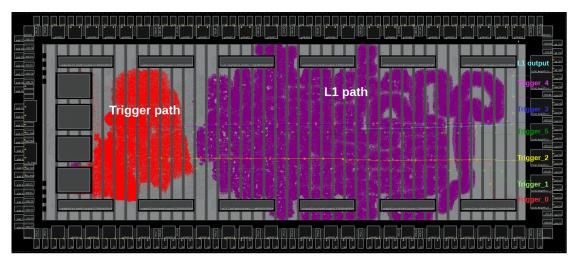

|   | 4.1 |         | mission of high-pT particles primitives                 | 61  |

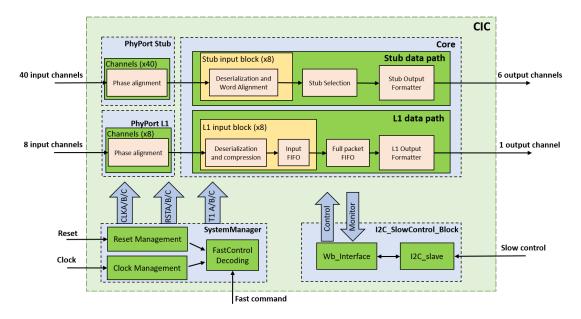

|   | 4.2 |         | eneral architecture                                     | 61  |

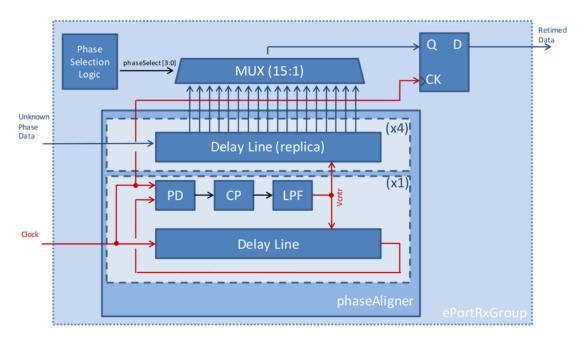

|   | 4.3 | Input   | data phase alignment                                    | 61  |

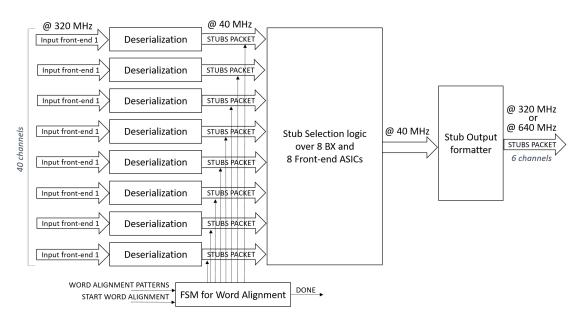

|   |     | 4.3.1   | Input stub data format from MPA or CBC                  | 64  |

|   |     | 4.3.2   | Deserialization and word alignment                      | 65  |

|   |     | 4.3.3   | Bitonic Stub sorting algorithm                          | 66  |

|   |     | 4.3.4   | Stub packet formatter                                   | 67  |

|   | 4.4 | Transı  | mission of triggered raw data                           | 70  |

|   |     | 4.4.1   | Input raw data format from CBC or MPA                   | 70  |

|   |     | 4.4.2   | CIC L1 input block                                      | 72  |

|   |     | 4.4.3   | FIFO controller                                         | 72  |

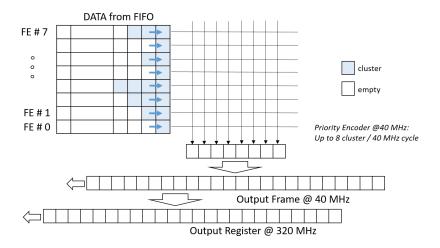

|   |     | 4.4.4   | Priority encoder for clusters sorting                   | 74  |

|   |     | 4.4.5   | Output packet formatter                                 | 75  |

|   |     | 4.4.6   | Output serializer                                       | 76  |

|   | 4.5 | CIC slo | ow control and fast commands                            | 77  |

|   | 4.6 | Design  | n and ASIC implementation                               | 79  |

|   | 1.0 | D00181  |                                                         | • • |

|       |         | Con                                                 | tents |

|-------|---------|-----------------------------------------------------|-------|

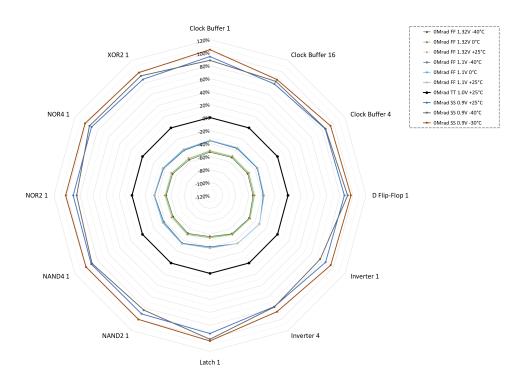

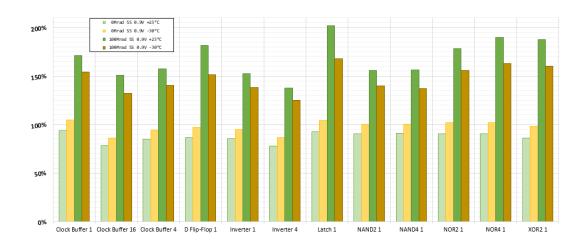

|       | 4.6.2   | Timing corners and TID effects                      | 79    |

|       | 4.6.3   | SEU hardening techniques and TID tolerance          | 82    |

|       |         | 4.6.3.1 Triplicated memory cells placement          | 84    |

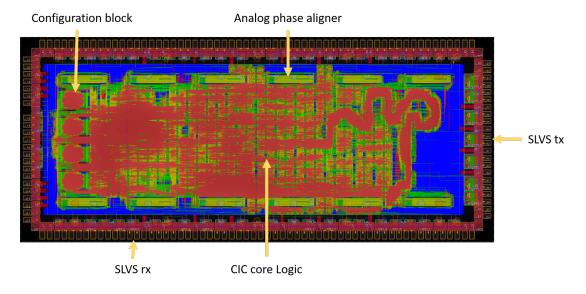

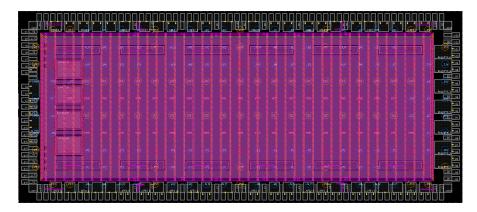

|       | 4.6.4   | Floorplan and power distribution                    | 85    |

|       | 4.6.5   | Power consumption                                   | 88    |

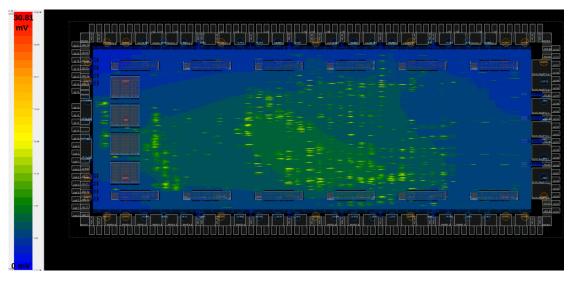

|       | 4.6.6   | IR drop                                             | 89    |

|       | 4.6.7   | Triplicated clock distribution                      | 89    |

| S CIC | C proto | type characterization results                       | 93    |

| 5.1   | Stand   | alone testbench for CIC prototype                   | 95    |

|       | 5.1.1   | CIC phases and modes                                | 97    |

| 5.2   | First s | silicon prototype: CIC1                             | 98    |

|       | 5.2.1   | Tests with 2S hybrid prototype                      | 98    |

|       | 5.2.2   | Power consumption                                   | 99    |

| 5.3   | Secon   | nd silicon prototype: CIC2                          | 102   |

|       | 5.3.1   | Power consumption                                   | 102   |

|       | 5.3.2   | Temperature characterization                        | 103   |

|       | 5.3.3   | IR-drop issue                                       | 10    |

|       | 5.3.4   | TID tests                                           | 100   |

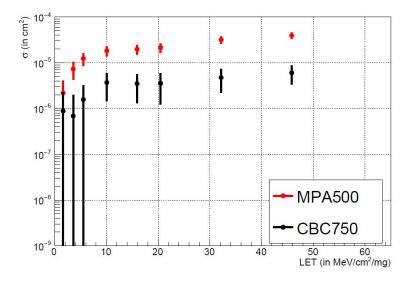

|       | 5.3.5   | SEU tests                                           | 10'   |

|       | 5.3.6   | SEU results analysis and cross-section measurements | 109   |

Bibliography

About the author

115

125

# **List of Figures**

| 1.1  | chamber                                                             | 2  |

|------|---------------------------------------------------------------------|----|

| 1.2  | The complex of the LHC accelerators                                 | 4  |

| 2.1  | n-in-p silicon detector structure                                   | 8  |

| 2.2  | Cutaway diagram of CMS detector                                     | 11 |

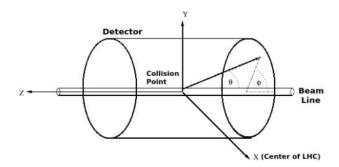

| 2.3  | Coordinate system used by CMS experiment at the LHC                 | 12 |

| 2.4  | The pseudorapidity function                                         | 12 |

| 2.5  | CMS current silicon tracker                                         | 13 |

| 2.6  | Material budget in the CMS tracker                                  | 16 |

| 2.7  | Integrated particle fluence for the Phase-2 tracker                 | 17 |

| 2.8  | Total Ionizing Dose for the the Phase-2 tracker                     | 17 |

| 2.9  | Data flow in CMS Trigger DAQ system                                 | 18 |

| 2.10 | The pT spectrum for CMS tracker at HL-LHC                           | 19 |

| 2.11 | Illustration of the pT-module concept                               | 20 |

| 2.12 | Tracker Layout section and $p_T$ -modules disposition, $r - z$ view | 22 |

| 2.13 | Exploided view of 2S module structure                               | 23 |

| 2.14 | Exploided view of PS module structure                               | 24 |

| 2.15 | Capacitance model of a pixel sensor                                 | 25 |

| 2.16 | Block diagram of a generic analog FE circuit                        | 26 |

| 2.17 | Stub rate in CMS Outer Tracker                                      | 29 |

| 2.18 | PS-module cross section                                             | 29 |

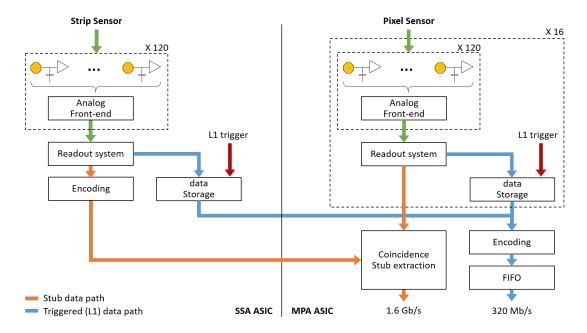

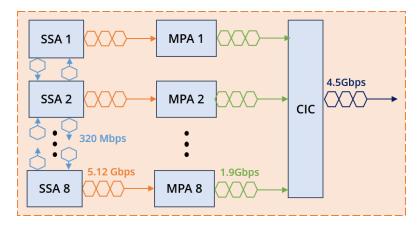

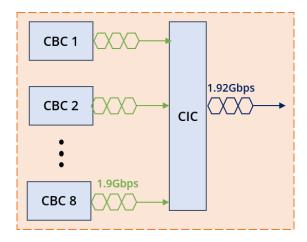

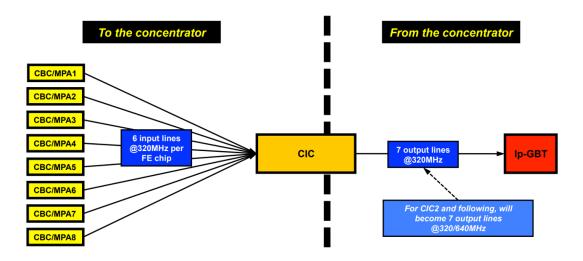

| 2.19 | MPA-SSA architecture                                                | 30 |

| 2.20 | PS-module structure with ASICs bandwidth                            | 31 |

| 2.21 | 2S-module structure with ASICs bandwidth                            | 31 |

| 2.22 | CIC input/output lines                                              | 32 |

| 2.23 | Effect of ionising radiation in MOS devices                         | 34 |

| 3.1  | General block diagram of the UVM framework implementation           | 41 |

| 3.2  | UVM Agent for stimuli generation                                    | 42 |

| 3.3  | UVM Agent for stimuli generation                                    | 43 |

#### **List of Figures**

| 3.4  | UVM Scoreboard summary for stub data collected at the output of each                     |

|------|------------------------------------------------------------------------------------------|

|      | ASIC of the readout chain                                                                |

| 3.5  | DUV for PS module                                                                        |

| 3.6  | DUV for 2S module                                                                        |

| 3.7  | PS module efficiency at the MPA output and CIC output for two different                  |

|      | output frequencies                                                                       |

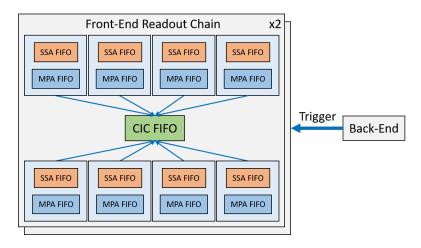

| 3.8  | CMS Outer Tracker half-module readout chain                                              |

| 3.9  | CIC latency for L1 data packets measured in BXs at the nominal trigger                   |

|      | rate frequency of 750 kHz $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$        |

| 3.10 | MPA latency for L1 data packets measured in BXs at the nominal trigger                   |

|      | rate frequency of 750 kHz                                                                |

| 3.11 | Full PS-module chain latency for L1 data packets measured in BXs at                      |

|      | the nominal trigger rate frequency of 750 kHz                                            |

|      | Buffer inefficiency with respect to I/O rate ratio $\ \ldots \ \ldots \ \ldots \ \ldots$ |

| 3.13 | FIFO-based architecture of the front-end ASICs                                           |

| 3.14 | Cluster occupancy at pileup 300 in the innermost barrel layer (cylinder                  |

|      | external surface)                                                                        |

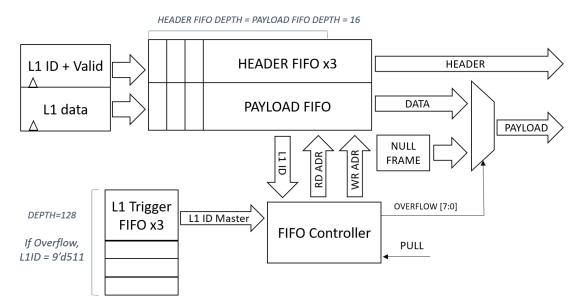

| 3.15 | FIFO-based architecture of the Data Concentrator ASIC $\ldots\ldots$                     |

| 3.16 | UVM framework with LpGBT and FPGA added to the DUV                                       |

| 4.1  | Block diagram of the entire CIC ASIC                                                     |

| 4.2  | Block diagram of the analog phase aligner                                                |

| 4.3  | CBC stub format                                                                          |

| 4.4  | MPA stub format                                                                          |

| 4.5  | MPA stub block diagram                                                                   |

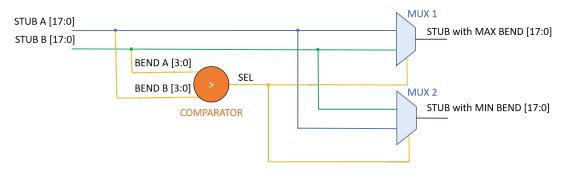

| 4.6  | Basic sorting cell composed of a comparator and 2 multiplexers                           |

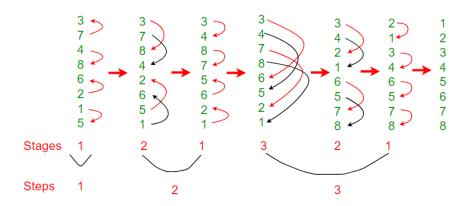

| 4.7  | Bitonic sorting example                                                                  |

| 4.8  | CIC stub format for 2S-module                                                            |

| 4.9  | CIC stub format for PS-module                                                            |

| 4.10 | CIC output configuration modes                                                           |

| 4.11 | CBC raw format                                                                           |

| 4.12 | MPA raw format                                                                           |

| 4.13 | Block diagram for FIFO controller                                                        |

| 4.14 | Block diagram for the CIC raw data output formatter                                      |

| 4.15 | CIC raw data output format for PS-module                                                 |

| 4.16 | CIC raw data output format for 2S-module in zero-suppression mode .                      |

|      | CIC raw data output format for 2S-module in debug mode                                   |

| 4.18 | Delay propagation for some standard cells in different corners with                      |

|      | respect to typical corner                                                                |

| 4.19 | Table with corners used for CIC implementation                                           |

| 4.20 | Delay propagation for SS corners at two different temperatures with and    |     |

|------|----------------------------------------------------------------------------|-----|

|      | without radiation models                                                   | 82  |

|      | Triple Module Redundancy implementation in the CIC                         | 83  |

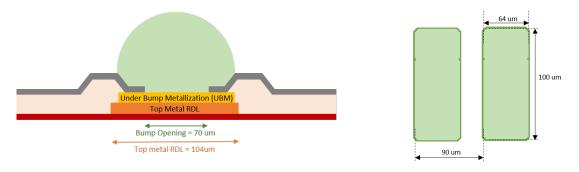

|      | 2 Implementation of the C4 bump and and wire-bond metallizations           | 85  |

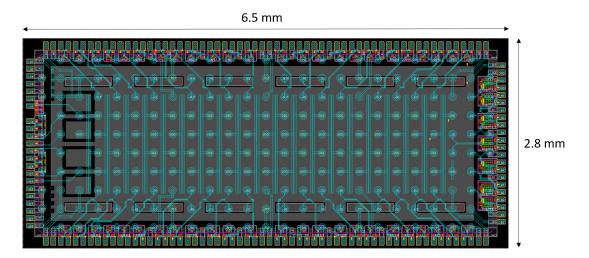

|      | 3 View of the final CIC ASIC top-metal layer                               | 86  |

|      | View of the final CIC ASIC layout                                          | 86  |

| 4.25 | 5 View of the final CIC ASIC with metal 6 distributed vertically and metal |     |

|      | 7 horizontally for uniform power distribution                              | 87  |

| 4.26 | Table with power consumption during word alignment and data sending        |     |

|      | for the two different modules in typical case and worst case               | 88  |

| 4.27 | CIC IR drop simulation with normal activity during data sending            | 89  |

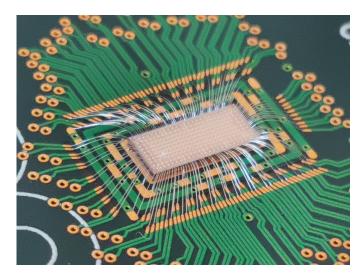

| 5.1  | CIC ASIC with wire bonds sitting on the carrier board                      | 95  |

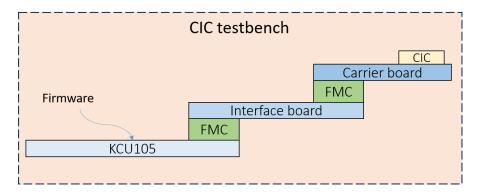

| 5.2  | Block diagram of CIC standalone testbench                                  | 95  |

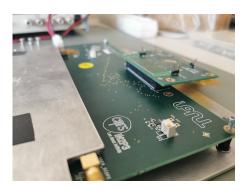

| 5.3  | CIC Carrier board plugged on a custom interface board                      | 96  |

| 5.4  | CIC FPGA board                                                             | 96  |

| 5.5  | Prototype of half of a 2S-module hybrid including eight CBC3.1 ASICs       |     |

|      | and one CIC1                                                               | 99  |

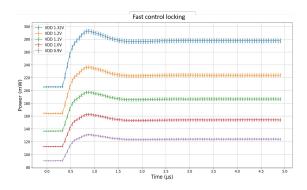

| 5.6  | CIC1 power consumption during fast control locking mode for different      |     |

|      | power supply voltages                                                      | 99  |

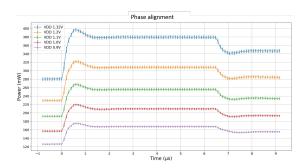

| 5.7  | CIC1 power consumption during phase alignment procedure for differ-        |     |

|      | ent power supply voltages                                                  | 100 |

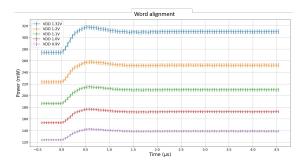

| 5.8  | CIC1 power consumption during word alignment procedure for different       |     |

|      | power supply voltages                                                      | 100 |

| 5.9  | CIC1 power consumption worst case scenario                                 | 100 |

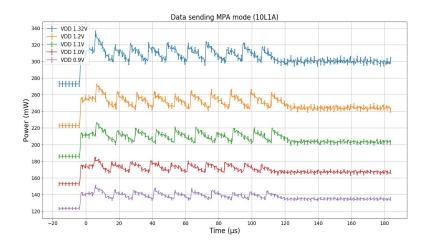

| 5.10 | CIC1 power consumption in data taking mode with 10 L1 triggers in          |     |

|      | PS-module                                                                  | 101 |

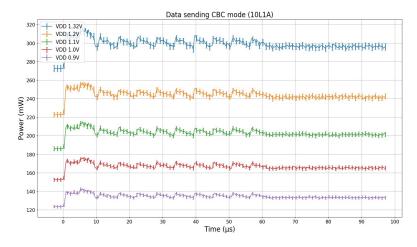

| 5.11 | CIC1 power consumption in data taking mode with 10 L1 triggers in          |     |

|      | 2S-module                                                                  | 101 |

| 5.12 | 2 CIC2 power consumption during data taking at different power supply      |     |

|      | voltages                                                                   | 103 |

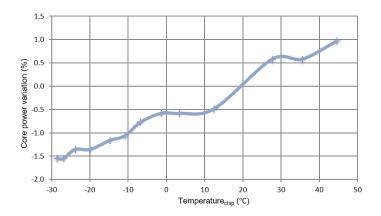

| 5.13 | Core power variation at different temperatures in the range between        |     |

|      | -30°C and 45°C                                                             | 104 |

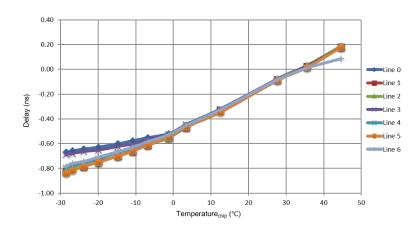

| 5.14 | Output delay variation for each CIC2 ASIC output line at different tem-    |     |

|      | peratures in the range between $-30^{\circ}$ C and $45^{\circ}$ C          | 104 |

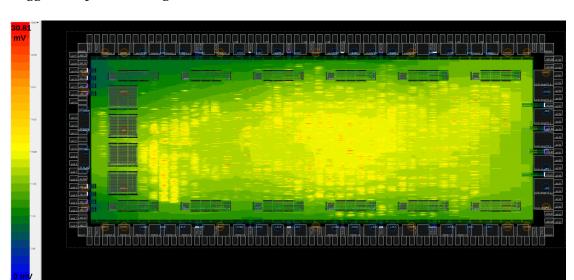

| 5.15 | 6 CIC IR drop simulation around current peak due to L1 trigger with high   |     |

|      | input activity                                                             | 105 |

| 5.16 | 6 CIC IR drop simulation around current peak due to L1 trigger with high   |     |

|      | input activity                                                             | 105 |

|      |                                                                            |     |

#### **List of Figures**

| 5.17 CIC2 output lines delay variation over TID irradia     | ation at 1.0V power   |     |

|-------------------------------------------------------------|-----------------------|-----|

| supply                                                      |                       | 106 |

| 5.18 CIC2 output lines delay variation over TID irradia     | ation at 1.2V power   |     |

| supply                                                      |                       | 107 |

| 5.19 CIC2 ready for SEU on a cooling plate $\dots \dots$    |                       | 108 |

| 5.20 Stub SEU errors for CIC2 ASIC at different values of I | LET for two different |     |

| configurations                                              |                       | 111 |

| 5.21 L1 SEU errors for CIC2 ASIC at different values of L   | ET for two different  |     |

| configurations                                              |                       | 111 |

# **Glossary and Acronyms**

**2S module** p<sub>T</sub>-module composed by two ation, modification, analysis, or optimizasilicon-strip detectors 0.0, 1.0, 2.6–2.7, 3.0, tion of a design

3.3, 4.0–4.1, 4.3, 4.6, 5.3

1.0

4.4-4.6, 5.0, 5.3

ATLAS Toroidal LHC ApparatuS detector. path Large Hadron Collider (LHC), 1.0

$20 \,\mathrm{cm} < r < 120 \,\mathrm{cm}$ , 2.6

**BEBC** Big European Bubble Chamber, 1.0 **BX** The instant at which the particles bunch are brought into collision. In the LHC, the BX rate is 40 MHz., 1.0, 2.2, 2.4, conductor, 1.0, 2.1, 4.6 2.7, 3.3, 3.5, 4.0–4.1, 4.3

also known as Flip-Chip technology, is a Hadron Collider (LHC), 1.0, 2.0, 2.2–2.3, method for interconnecting semiconduc- 2.7, 3.0, 3.3, 4.1, 6.0 tor devices with solder bumps deposited **cross-section** The section normal to the in the die area, 2.1

**CBC** CMS Binary Chip (CBC). Is the strip ALICE A Large Ion Collider Experiment, sensor readout ASIC of the CMS Outer Tracker 2S-module, 2.6-2.7, 3.3

**ASIC** Application-Specific Integrated Cir- **CCOpt** Clock Concurrent Optimization, it cuit, 1.0, 2.0, 2.2, 2.6–2.7, 3.0–3.2, 4.0–4.1, is used during CTS to optimize clock tree distribution taking into account the data-

It is a general-purpose detector at the **CERN** in French "Conseil Européen pour la Recherche Nucléaire", or European Orbarrel Concentric cylindrical layers cen-ganization for Nuclear Research, 1.0, 6.0 tered in the in the nominal interaction CIC Concentrator Integrated Circuit. It point and located in the CMS tracker at is the data concentrator ASIC of the CMS Outer Tracker PS and 2S modules for the phase-2 upgrade, 2.6–2.7, 3.0, 3.3, 4.0–4.1, 4.4-4.6, 5.0

**CMOS** Complementary Metal Oxide Semi-

**CMS** Compact Muon Solenoid detector. It C4 Controlled Collapse Chip Connection, is a general-purpose detector at the Large

beam direction outside of that the particle CAD Computer-aided design. It repre- is not deflected. It can be considered as sents software that aim to aid in the cre- a measure of the interaction probability, 5.3 FIFO First In First Out circuit element, **CSA** Charge Sensitive Amplifier, 2.6 3.0, 3.2 - 3.3FPGA Field Programmable Gate Array, 3.4 **CTS** Clock Tree Synthesis, it is a step of the physical implementation flow 0.0, 4.6 FSM Finite State Machine, 3.3 DAC Digital to Analog Converter, 2.6 GL Gate Level, 3.1-3.2 **HCAL** Hadron Calorimeter of the CMS ex-**DAQ** Data AcQuisition system, 4.5 DD Displacement Damage, 2.8 periment, 2.2 DLL Delay-Locked Loop. Similar to a PLL HDL Hardware Description Language, where the internal voltage-controlled os- 3.1 cillator is replaced by a delay line, 4.3, 4.5 **HEP** High Energy Physics, 1.0, 2.8 **DRC** Design Rule Checking, it is a step of **high-p**<sub>T</sub> high transverse momentum (p<sub>T</sub>) sign-off to determine whether the chip lay- particle. In this context it refers to partiout satisfies a number of rules as defined cles with  $p_T > 2 \text{ GeV}/c$ , 2.4–2.5, 3.0, 4.1, 4.3 by the semiconductor manufacturer, 4.6 **HL-LHC** High Luminosity Large Hadron **DUV** Design Under Verification, 3.1–3.2 Collider, 1.0, 2.0, 2.2–2.3, 3.3, 4.1, 6.0 ECAL Electromagnetic Calorimeter of the HLT High Level Trigger system, 2.3 CMS experiment, 2.2 **HPD** Hybrid Pixel Detector, 2.1 EDA Electronic Design Automation, also integrated luminosity The integrated lureferred to as electronic computer-aided minosity over the operation time  ${\mathscr L}$  defines the total amount of data recorded by design (ECAD) **E**<sub>**DEP**</sub> Deposited ionizing energy an experiment ELT Enclosed Layout Transistor. It is a lay- IT Inner Tracker, 2.2, 2.5 out technique to reduce the leakage cur- L1 Level-1 trigger system (hardware trigrent increase due to the charge trapped in ger) of the CMS detector, 2.3-2.7, 3.3, 4.0the STIs for devices exposed to ionizing 4.1, 4.4 radiation, 4.6 L1 data Raw sensor image transmitted end-cap Parallel disks centered in the in only when required by a L1 trigger the z located in the CMS tracker at z >**L1 latency** latency between the transmis-130 cm, 2.6 sion of a trigger request and the cor-**ESD** Electro-Static Discharge responding event occurrence. It corre-FC7 flexible, µTCA compatible Advanced sponds to the time available for the L1 Mezzanine Card (AMC) for generic data data processing acquisition/control applications L1 rate Average occurrence frequency of **FE** Front-End 0.0, 2.6 the CMS Level-1 trigger request **FEC** Forward Error Correction, 3.4 latch-up Latch-up is a type of short circuit which can occur in an integrated circuit. , (i.e in the PS module is  $100 \times 1467 \,\mu\text{m}$ ) 2.8

of energy that an ionizing particle trans- duces a limiting factor for the detection fers to the material traversed per unit dis- ratios of particles that may interact with tance, 2.8, 4.6, 5.3

Level-1 Level-1 trigger system (hardware expected to recognize trigger) of the CMS detector

LHC Large Hadron Collider, 1.0, 2.0, 2.7-2.8, 4.0

**LHCb** Large Hadron Collider beauty, 1.0 **low-p**<sub>T</sub> Low transverse momentum  $(p_T)$ cles with  $p_T < 2 \text{ GeV}/c$ , 2.4

**LpGBT** Low Power GigaBit Transceiver (LpGBT). Is a radiation tolerant serializer/deserializer device that can be used on pixel-sensor readout ASIC of the CMS the front-end electronics of the HL-LHC detectors. This component is foreseen to tem upgrades, 2.6–2.7, 3.4, 4.0, 4.5

tector to allow the upgrade operations

LSB Least Significant Bit

**luminosity** The events rate occurrence in a particle interaction is defined as  $\frac{dN}{dt}$  =  $\sigma\ell$ , where  $\ell$  represents the instantaneous **nMOS** n-channel Metal Oxide Semiconnumber of interactions per second, called ductor (MOS) device, 2.8 luminosity while  $\sigma$  represents the cross- **OT** Outer Tracker, 2.2 section of the interaction, 1.0

the ASIC layout corresponds to the orig- 3.0, 4.0–4.1 inal schematic or circuit diagram of the PCB Printed Circuit Board design, 4.6

macro-pixel pixel with high aspect ratio Phase-2 Upgrade CMS detector upgrade

material budget the quantity of mate-LET Linear Energy Transfer. The amount rial in the tracker volume, that introit and compromise what the detector is

MIP Minimum Ionizing Particle, 2.1

MMMC Multi-Mode Multi-Corner analysis

Monte Carlo A broad class of computational algorithms that rely on repeated particle. In this context it refers to parti-random sampling to obtain numerical results, 2.7

**MOS** Metal Oxide Semiconductor

MPA Macro Pixel ASIC (MPA). It is the Outer Tracker PS-module, 2.6-2.7

MPW Multi Project Wafer, because IC fabbe used by CMS and ATLAS for their sys-rication costs are extremely high, it makes sense to share mask and wafer resources LS3 Third long shutdown of the CMS de- to produce designs in low quantities, 4.6 NDR Non-Default Rules, are additional parameters to set during CTS step to control better clock physical implementation

, 4.6

**Outer Tracker** CMS tracker barrel layers **LVS** Layout Versus Schematic, whether and end-cap disk located at  $r > 200 \,\mathrm{mm}$ ,

PDK Process Design Kit, 4.6

during HL-LHC LS3

**pileup** in HEP experiments it represents the average amount of overlapped signals in the event reconstruction, and in our case is the number of proton-proton collisions per BX, 2.0, 2.2, 2.4, 3.3, 4.1, 4.4, 5.3

**PLL** Phase-Locked Loop. It is a control system that generates an output signal whose phase is related to the phase of an input signal

**pMOS** p-channel Metal Oxide Semiconductor (MOS) device, 2.8

pp proton-proton collisions, 2.2-2.4

**pseudorapidity** Kinematical variable of a relativistic particle defined as  $\eta =$  $-\ln \tan \frac{\theta}{2}$ , where  $\theta$  is the particle zenith angle referenced to the direction of the crossing beams, 2.2

**PS module** p<sub>T</sub>-module that combines a silicon micro-strip sensor with a siliconpixel sensor 0.0, 1.0, 2.6-2.7, 3.0, 3.3, 4.0-4.1, 4.3, 4.6, 5.3

**p**<sub>T</sub> Particle transverse momentum 0.0, 2.2, 2.4

pable to provide transverse momentum measurements 0.0, 2.0, 2.4-2.7, 3.0, 3.2-3.4

**PVT variations** Process Voltage Tempera-, 4.0, 4.6 ture (PVT) variations, 1.0, 4.3, 4.6

**Python** An interpreted, general-purpose programming language traction tool ideal for advanced nodes

**RDL** Re-Distribution Layer, 4.6

RTL Register Transfer Level, is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals, 3.1–3.3

SDF Standard Delay Format (SDF) is an IEEE standard for the representation and interpretation of timing data for use at any stage of an electronic design process, 4.6 **SEE** Single Event Effect. Effects caused by one single ionizing particle striking a sensitive node in a micro-electronic device, 2.8, 4.0, 4.6

**SEL** Single Event Latch-up. Latch-up is a type of short circuit which can occur in an integrated circuit., 2.8

**SET** Single Event Transient. Time limited change of logical state caused by one single ionizing particle striking a sensitive node in a micro-electronic device, 2.8, 5.3 **SEU** Single Event Upset. Change of logical state caused by one single ionizing parti**p**<sub>T</sub>-module Silicon detectors modules ca- cle striking a sensitive node in a microelectronic device, 1.0, 2.8, 3.3, 4.4–4.5, 5.3 **SLVS** Scalable Low Voltage Signaling. It is a differential signal transmission standard

**SM** Standard Model in particle physics high-level, is the theory describing three of the four known fundamental forces (electromag-Quantus QRC Quantus Extraction Solunetic, weak, and strong interactions, and tion, it is production-proven signoff ex- not including the gravitational force) and classifying the known elementary particles

**SOI** Silicon On Insulator technology

**SPS** Super Proton Synchroton, 1.0

**SSA** Short Strip ASIC (SSA). Is the microstrip-sensor readout ASIC of the CMS Outer Tracker PS-module, 2.6–2.7, 4.6

**STI** Shallow Trench Isolation. Isolation which prevents electric current leakage between adjacent semiconductor devices , 2.8

**strip** Detectors obtained by segmenting the doped side into strips over the full length of the detector, 1.0, 2.6

**stub** High- $p_T$  particles primitives transmitted by  $p_T$ -modules , 2.4, 2.7, 4.1

**SystemVerilog** IEEE 1800 standard hardware description and verification language used to model, design and simulate electronic systems, 3.1

**TCL** Tool Command Language. It is a high-level, general-purpose, interpreted, dynamic programming language, 4.6

**TID** Total Ionizing Dose, The cumulative damage of the semiconductor lattice caused by ionizing radiation over the exposition time, 1.0, 2.2, 2.5, 2.8, 4.6, 5.3

**TLM** Transaction Level Modeling abstraction, 3.1–3.3

**TMR** Triple Modular Redundancy. Circuit technique to increase tolerance to radiation related single-event effects, 4.0, 4.6 **ToA** Time of Arrival of a particle

**ToF** Time of Flight, in this context it refers to the particles time required to reach the

silicon detector

**ToT** Time over Threshold method to determine the amplitude of an analog signal. The signal is compared to a threshold and the duration of the output pulse is measured

**tracker** CMS sub-detector that allows reconstructing the particle trajectory and transverse momentum  $p_T$  in the 3.8T magnetic field provided by the superconducting solenoid, 2.2, 2.6

**tracker volume** material crossed by a straigth line between the origin and the farthest silicon sensor met by the line

tracking volume tracking volume, 2.2

**Trigger DAQ** Trigger Data AcQuisition system, 2.3, 3.3

**UBM** Under Bump Metalization

**UVC** Universal Verification Methodology Verification Component , 3.2

**UVM** Universal Verification Methodology, is a standardized methodology for verifying integrated circuit designs, 3.0–3.2, 3.5

**VCD** Value Change Dump

**Verilog** IEEE 1364 standard hardware description language (HDL) used to model electronic systems , 3.1

**Verilog-AMS** It is a derivative of Verilog HDL language that includes analog and mixed-signal extensions (AMS)

**vManager** vManager is a Cadence tool for verification planning for tests management of complex verification projects, 3.2

V<sub>T</sub> Threshold voltage, 4.6

## 1 Introduction

High energy physics (HEP) is a branch of physics that explores the nature of particles and the fundamental interactions necessary to explain their behaviour.

Particles, or their nuclear decay products, have been studied for the first time more than 100 years ago, using scintillation screens and photographic films. In that case there was no need for a particle detector, since particles were visible with the human eye [16].

Since then, several technologies have contributed to achieve significant results in high energy physics field. In particular, in 1911 C. T. Wilson invented the cloud chambers [17], that played a dominant role in particle physics between 1920 and 1950. An energetic charged particle interacts with the supersaturated vapor inside the cloud chamber, leaving behind a trail of ionized particles that act as condensation centers. Small droplets are observable as a "cloud" track lasting for several seconds. Each particle has a characteristic shape and can then be identified. The cloud chamber allowed the discovery of the positron in 1932 [18] and of the K meson in the 1947 [19].

In 1952, Donald A. Glaser invented the bubble chamber [20]. The working principle was the same of the cloud chamber. The cylindrical shape chamber is filled with a liquid heated to just below the boiling temperature. Exactly when particles enter the chamber, a piston decreases its pressure, and the liquid enters into a superheated, metastable phase. The liquid vaporizes around the ionizing track generated by the charged particles forming visible bubbles. A constant magnetic field is applied to the whole chamber so that charged particles travel along helical paths giving the

opportunity to measure particle momentum. Bigger is the chamber, larger are the bubbles to be seen or photographed. Figure 1.1 shows the decay products of a kaon particle spiraling in the magnetic field of a bubble chamber [21].

**Figure 1.1.** Photograph of the real track left by a positive kaon. The decay products formed a typical spiral shape in the magnetic field of a bubble chamber [21].

In 1954 the European Organization for Nuclear Research (CERN) was founded thanks to the common effort of 12 European countries. Its objective is to provide a scientific facility for particle physics research.

Right at CERN, in 1973 the Gargamelle bubble chamber detector, filled with heavy-liquid, led to the discovery of weak neutral currents [22] thanks to the beam provided by the Super Proton Synchroton (SPS). The largest bubble chamber ever built, and also the last one, is the Big European Bubble Chamber (BEBC) with 6.3 millions of photographs taken and 3000 km of developed film [23]. It allowed the discovery of D mesons [24]. The main limitations of this detector was the large amount of time needed to develop the film and optically scan it for interesting events.

The first electronic particle detector, with high statistics and reasonable resolution, was the Multi Wire Proportional Chamber (BEBC), developed in 1968 [25]. It consisted of 1000 wires spaced of 1 mm. As the charged particle passes, the hit wire sends out an electrical signal. That was the end of the bubble chamber detectors, in favor of faster electronic particle detectors.

Another way of building a particle detector is exploiting the properties of semiconductor devices. Charged particles create electron-hole pairs in the depletion region that

are drifted to the electrodes. The drift current creates the signal which is amplified by an amplifier connected to each strip. The first example of working silicon-strip detector was built at CERN in 1983 [26].

In order to detect short-living particles, in the late eighties, silicon-strip detectors became more and more common thanks to an excellent spatial resolution of  $5\mu$ m-range and, in particular, the introduction of planar technology that boosted their industrial production. The next breakthrough came with the possibility of integrating detectors and electronics on the same device [27]. At the end of nineties, also pixel detectors started being used successfully in the experiments. Still today, strip and pixel detectors are the leading technology for particles tracking.

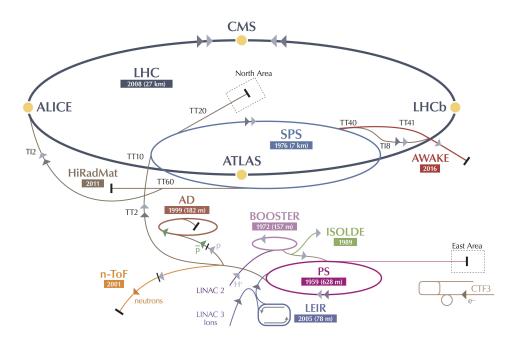

Nowadays, CERN is supported by 23 member states and 8 associated members [28] and hosts the world's largest and most powerful particle accelerator: the Large Hadron Collider (LHC) [29], [30]. Built between 1998 and 2008 in collaboration with over 10000 scientists and engineers from over 100 countries, the LHC sits in a circular tunnel 27 km long excavated 100 m underground. Superconducting magnets, as well as accelerating structures, boost the energy of protons along the way up to 7 TeV. Two counter-rotating protons beams, travelling in opposite directions in separate tubes kept at ultrahigh vacuum, are made to collide at a center of mass energy of 14 TeV. In the LHC there are four collisions points, around which different experiments are set up, as shown in Figure 1.2: (ATLAS) [31], (CMS) [32], LHCb [33] and ALICE [34] detectors.

The number of instantaneous collisions occurring in a particle accelerator is given by the **luminosity**, defined as  $\ell = \sigma \frac{dN}{dt}$ , where N is the number of particles in a given time t squeezed through a given space, called cross-section  $\sigma$  of the interaction. A parameter to characterize the performance of a particle accelerator is the integrated luminosity, that gives an idea of the total number of collisions happened over the operation time. The integrated luminosity can be expressed as:

$$\mathscr{L} = \int_0^T \frac{\ell_0}{(1+t/\tau)}.$$

The LHC reached a luminosity of  $2.1 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> during the 2018 [36]. The expected integrated luminosity collected by the CMS experiment in its most recent run is

**Figure 1.2.** The complex of the LHC accelerators [35].

around 300 fb<sup>-1</sup>. The collision rate is 40 MHz and is called **bunch-crossing (BX) rate**.

LHC was commissioned to observe the missing particle in the Standard Model [37]: the Higgs boson. A new particle was observed at about 125 GeV [38], as theorized in 1964 by P. Higgs, R. Brout and F. Englert [39], [40], and announced by CMS and ATLAS experiments in 2012.

After Higgs boson discovery, that represents a milestone in the history of particle science, new theories need to be validated and proven: existence of super-symmetry, nature of dark matter and existence of extra dimensions. The Higgs boson itself will need to be studied and characterized better [41]. LHC needs a major upgrade to exploit all its potential increasing its luminosity of a factor five up to  $5 \cdot 10^{34} \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$ , and integrated luminosity of a factor ten up to  $7.5 \cdot 10^{34} \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$  [42]. The novel machine configuration, called High Luminosity LHC (HL-LHC or HiLumi), will be ready in 2025 after 10 years of development. The HL-LHC upgrade was approved in 2016 representing the highest priority of the European Strategy for particle physics [43], [44].

Consequently, CMS detector will face a major upgrade in 2025 [45]. In this context, the CMS tracker will be completely replaced by a new one able to work with the expected

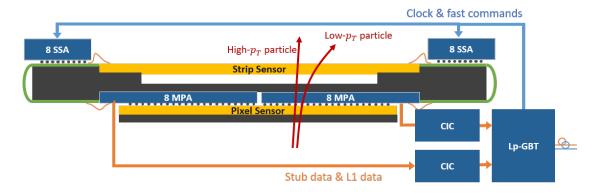

luminosity of HL-LHC. CMS tracker will feature for the first time intelligent particle tracking. The front-end ASICs will be able to locally discriminate interesting physics event before transmitting them to the back-end. This new approach would make possible to do event-reconstruction in the HL-LHC.

This thesis focuses on the studies and design of a data concentrator ASIC to be employed in two different readout systems: a two layers pixel-strip detector readout system and two layer strip-strip detector readout system, both for CMS Outer Tracker.

#### This thesis is structured as follows:

- Chapter 1 (this chapter) is an introduction to HEP experiments in the history up to today;

- Chapter 2 describes High Luminosity-LHC improved performances and CMS

Tracker upgrade requirements for electronics, with particular focus on new

tracker features and radiation effects on CMOS electronics;

- Chapter 3 describes the simulation framework developed to study and assist the design of a data concentrator ASIC working in two different modules: PS module and 2S module;

- Chapter 4 describes the different steps of the design from the architecture to the final implementation of the data concentrator ASIC;

- Chapter 5 shows the results of the silicon prototype characterization under different PVT variations and under irradiation, such as TID and SEU effects;

- Chapter 6 is the conclusion of the main research points providing a brief summary of the achieved objectives together with some recommendations for work on a similar topic.

The explanation of all terminology used in the thesis are collected in the glossary.

# 2 The Challenges of State of the Art CMS Outer Tracker Upgrade

The Compact Muon Solenoid (CMS) experiment has the objective of studying the Standard Model, including Higgs boson, and searching for new physics at the new energies and luminosity frontiers. The current CMS detector is using a silicon strip tracker composed of 15000 modules with a sensitive area of  $200\,\mathrm{m}^2$  and has been designed to work with an integrated luminosity of  $500\,\mathrm{fb}^{-1}$ . The LHC is expected to increase its integrated luminosity to  $3000\,\mathrm{fb}^{-1}$ . This configuration is called High Luminosity (HL-LHC). CMS experiment will receive a fundamental upgrade of its tracker detector and front-end electronics, featuring higher granularity and readout bandwidth to cope with the large number of pileup events. The main challenges for CMS tracker upgrade will be described in section 2.2 together with the innovative concept of  $p_T$ -module in section 2.4. Section 2.2.2 introduces the requirements and the choice of the silicon detector and the readout electronics. In the last part of the chapter, section 2.8 describes the challenges due to radiation effects on electronics and strict power requirements for ASICs operating in the innermost regions of the LHC experiments.

#### 2.1 Silicon for particle detection

Silicon is a semiconductor solid material that thanks to its properties revolutionized the development of electronics and has many other uses, as silicon sensors. The small energy band gap, which is 1.12 eV at room temperature allows to an ionizing particle passing trough silicon producing a large number of charge carriers proportional to the energy loss. The major advantage of silicon is the availability of a developed technology, which allows the simple integration of detector and electronics on the same substrate [46].

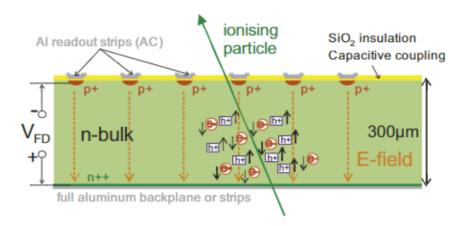

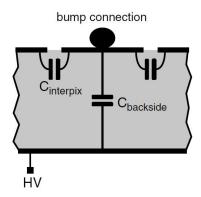

The working principle of a silicon sensor (pixel o strip), shown in Figure 2.1, is based on a narrow and highly doped silicon layer on a substrate of the opposite polarity to form a diode structure, which is reversed biased. As charged particles traverse the pixel or the strip, they generate electron-hole pairs. Due to the high bias voltage applied to the back-side plane, the full volume is depleted so that holes drift to the  $p^+$  doped layer and electrons drift to the  $n^{++}$ , or vice versa for a n-type sensor. Thus, the electric field would create small ionization currents that can be detected and measured.

Figure 2.1. n-in-p silicon detector structure.

The average charge loss of a charged particle passing trough a medium, silicon or gas, is given by the Bethe-Bloch formula:

$$-\frac{dE}{dx} = 4\pi N_a r_e^2 m_e c^2 z^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \left( \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} \right) - \beta^2 - \frac{\delta(\gamma)}{2} \right],$$

where:

- $N_a$ : is Avogadro's number.

- $r_e$ : is the classical electron radius.

- $m_e$ : is the mass of an electron.

- *c*: is the speed of light.

- *z*: is the charge of the incident particle.

- *Z*: is the atomic number or proton number.

- *A*: is the atomic mass.

- $\beta$ : is given by the ratio v/c.

- $\gamma$ : is given by the formula  $1\sqrt{1-\beta^2}$ .

- $T_{max}$ : is the maximum kinetic energy that can be provided to a free electron in a single collision.

- *I*: is the mean excitation energy.

- $\delta$ : is the density effect correction.

The minimum of the deposited energy in a given medium is found for  $\beta\gamma\approx 3$ . A detector has to be designed to detect the Minimum Ionizing Particle (MIP) with the minimum deposited energy. For every 3.6 eV, released by a particle crossing silicon, one electron-hole pair is produced. Silicon has an intrinsic energy resolution, better than other materials, for instance 30 eV energy loss creates only one electron-hole pair in a gas detector. In a silicon detector, the number of electron-hole pairs is high due to the high silicon density of  $2.33\,\mathrm{g\cdot cm^{-3}}$ , e.g., the average energy loss of  $309\,\mathrm{eV/\mu m}$  create  $\sim 108$  electron-hole pairs. Therefore, the silicon detector thickness is the result of a trade-off between energy resolution and capability to produce a signal large enough to be measured. Indeed, charges are collected in few ns on the doped strips (or pixels) and then induced, by capacitive coupling, to the aluminum readout strips (or pixels). If a thin layer, few  $\mu m$ , of  $SiO_2$  or  $Si_3N_4$  covers the doped strips or pixels, it prevents leakage currents to flow through the electronics and the silicon detector is called AC-coupled. On the other hand, if the aluminum contact

is directly connected to the doped strips or pixels, the silicon detector is called DC-coupled [47], [48]. The aluminum contact allows to electrically connect strips or pixels to the readout electronics. Strips aluminum contacts can be easily wire-bonded to the readout electronics because they reach the end of the sensor. On other hand, pixels aluminum contacts, featuring a two-dimensional arrangement, exploit a bump-bonding technology, called C4, that allows to solder bumps directly onto the chip pads. This kind of pixel detector is called Hybrid Pixel Detector (HPD) [49]. In HPD the pixel sensor and the readout electronics are produced separately, but using the same technology: standard Complementary Metal-Oxide-Semiconductor (CMOS) technology, which provides a microscopic structuring thanks to industrial lithography process.

Silicon sensors combine a high precision and resolution with a high readout speed, and, therefore, applicable in HEP experiments [50].

#### 2.2 The CMS experiment upgrade for High Luminosity

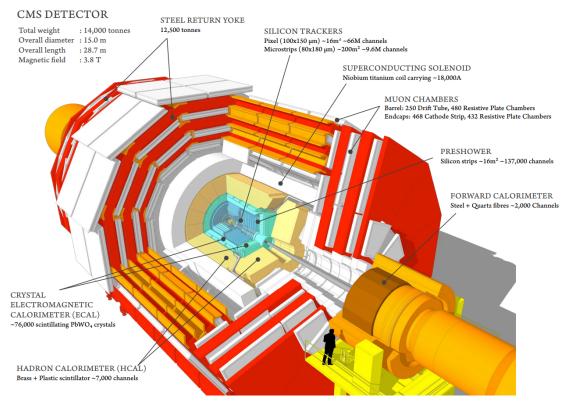

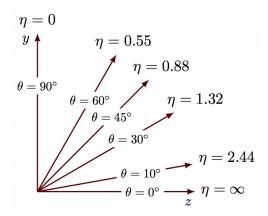

The CMS detector has a cylindrical shape and is 21.6 m long with an outer radius of 7.5 m. It is built around one of the LHC collision points and is composed of two main regions: barrel in the central region (subdetectors arranged along the radius) and endcaps in the two lateral regions (subdetectors arranged along z coordinate). As shown in the cutaway diagram in Figure 2.2, the tracker is located at the centre of the detector and is immersed in a uniform magnetic field of 3.8 T provided by a superconducting solenoid. The tracker is able to detect secondary particles trajectory and transverse momentum  $p_T$ , that is a physical quantity linked to the speed and the mass of the particle. Both electromagnetic calorimeter (ECAL) and hadronic calorimeter (HCAL), located farther away from the collision point, but still within the solenoid volume, are able to measure the particle energy. Muon chambers are located outside the solenoid volume and are able to detect muons, particles that can penetrate deep in matter. A more detailed description of the detector is reported in the CMS collaboration report [32].

The coordinate system adopted by CMS is shown in Figure 2.3. The origin of the coordinate system is located in the collision point. The beam direction defines the *z*-axis, while the *x-y* plane is transverse to the beam. The positive *x*-axis points from

the collision point to the centre of LHC ring, whereas the *y*-axis points upwards. The transverse momentum  $\mathbf{p_T}$ , the transverse energy  $\mathbf{E_T}$ , the missing transverse energy  $\mathbf{E_T}$ , and other transverse variables are defined in the *x-y* plane, called transverse plane.

Due to the shape of CMS detector, a cylindrical coordinates system can be also adopted. In this context, given a vector r, its module is defined as  $|r| = \sqrt{\eta^2 + \phi^2}$ , where  $\eta$  is defined as **pseudorapidity** and  $\phi$  is the azimuthal angle. The pseudorapidity is commonly used as spatial coordinate and describes the angle of a particle relative to the beam axis following the relation  $\eta = -\ln(\tan(\theta/2))$ , where  $\theta$  is the polar angle on the r-z plane from beam axis. On the other hand, the azimuthal angle  $\phi$  is measured around the beam axis, with  $\phi = 0$  in the positive x-axis and increasing clockwise [52].

The CMS experiment will require a substantial upgrade of its detector to handle the increased integrated luminosity of the HL-LHC [45], up to  $3000\,\mathrm{fb}^{-1}$  that corresponds to  $5\cdot10^{34}\,\mathrm{cm}^{-2}\mathrm{s}^{-1}$ . Higher luminosity translates into:

Figure 2.2. Cutaway diagram of CMS detector [51].

**Figure 2.3.** Coordinate system used by CMS experiment at the LHC [52].

- higher radiation damages on electronics;

- higher number of collisions that could cause, eventually, an overlap of signals coming from collisions occurred in the same BX or consecutive BXs in the case of low energy particles creating loops due to the high magnetic field. The amount of signals generated by multiple pp collisions in the same BX is defined as **pileup**.

The CMS experiments employs a particle flow event reconstruction [53] exploiting the combination of all the subdetectors information: charged-particles trajectories revealed by the **tracker**; neutral particles energy deposition measured by the **calorimeters**; muons, able to penetrate deep in matter, revealed by **muon system** [54].

An increased granularity and higher resolution are necessary to keep acceptable detector performance in the extreme pileup conditions.

**Figure 2.4.** The pseudorapidity function.

Figure 2.5. CMS silicon tracker currently installed.

#### 2.2.1 The CMS tracker

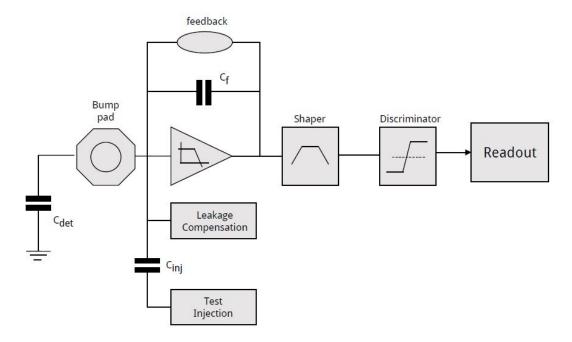

The CMS silicon tracker is the subdetector closest to the collision point [55]. It consists of two parts, Inner Tracker (IT) and Outer Tracker (OT). The current IT is based on silicon pixel detectors that are arranged in multiple layers providing true 2D points with 10 – 15 µm resolution. Farther away from the collision point where the flux of particles is reduced, silicon strip sensors are used. More than 24000 micro-strip sensors with a total of 10 million channels are arranged in multiple layers covering an area of ~ 210 m<sup>2</sup> [56]. Modules with different geometries and strip pitches ranging from  $80\mu m$  to  $205\mu m$  are currently used to achieve acceptable resolution. The signals coming from the silicon strips of a module are read by more strip readout ASICs, called APV25, implemented in 0.25 µm CMOS technology [57]. It can sample up to 128 channels at 40 MHz. The data are sent out only upon the reception of a trigger signal. The back-end of CMS experiment decides to send a trigger according to continuous data coming from calorimeters and muon system. The maximum trigger rate in the current CMS detector is limited to 100 kHz and the latency is 3.2 µs [55]. The tracker, together with information from the calorimeters and the muon system, allows reconstructing precisely the trajectory of interesting particles through the bending in the magnetic field.

# 2.2.2 Silicon tracker upgrade

By 2025 the HL-LHC will increase its integrated luminosity to 250 fb<sup>-1</sup> per year for further 10 years of operation. Under these conditions, both the events pileup and cumulative radiation effects will increase substantially. The current 50 pileup events will increase to 250 in the new HL-LHC. The current CMS tracker cannot guarantee acceptable performances in the new HL-LHC environment and will need to be replaced by a new CMS silicon tracker with enhanced functionalities and radiation robustness to keep high performances in particle trajectories recognition [45]. Cumulative radiation damages concern all the electronics, and in particular pixel sensors, causing a reduced spatial resolution and eventually reduced hit efficiency.

The new CMOS technologies allow for higher transistor density and more complex ASICs, able to feature higher number of functionalities. At the HL-LHC. the nominal pileup will be 5 times higher the one in the current LHC, consequently, the large amount of data alone provided by the calorimeter does not guarantee an acceptable event selection rate. For this reason it is fundamental to include information at the level of the CMS Tracker. For the first time, the CMS Tracker will be able to send out relevant information for the trigger decision taken by the experiment back-end. Moreover, the full data events will be stored locally for a maximum to 12.5 µs and the trigger rate will be increased to 750 KHz.

The new tracker will consist of an Inner Tracker (IT) based on silicon pixel modules and an Outer Tracker (OT) made from silicon modules with strip and macro-pixel sensors. The main requirements for the tracker upgrade are:

- **Increased granularity**. In order to guarantee efficient tracking performance with high level of pileup, up to 300, the channel occupancy for the IT should be below the per mille level, while that for the OT below the per cent level (less than 3 %).

- **Robust pattern recognition**. Track finding under pileup conditions becomes increasingly more difficult and time consuming.

- Local storage and increased latency. The higher number of collisions requires a local storage of full event data for a maximum of 12.5 µs. In the current CMS detector the maximum latency is 3.8 µs. For the first time, data from the tracker

will be used for the trigger decision. The increased latency is required by the CMS experiment back-end to evaluate more data than before and take the trigger decision.

- **Higher trigger rate**. Due to the higher average number of collisions in the HL-LHC, the trigger rate needs to be increased from the current 100kHz to 750kHz.

- Improved two-track separation. The current CMS tracker is limited in tracking finding performance in highly energetic jets, due to hit merging in the pixel detector. In order to handle large amount of collisions, two-track separation needs to be improved.

- Increased bandwidth and data compression. Higher bandwidth, data compression algorithms and higher data rates are required to handle a substantial increase in the amount of data allowing CMS experiment to be efficient at the expected luminosity of  $5 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>.

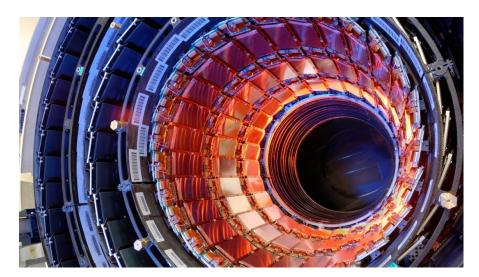

- Reduced material budget in the tracking volume. The current CMS tracker performances are affected by the large amount of material that interact with the particles. Therefore, in the future tracker, called Phase-2 tracker, the material budget has been reduced. The estimation of the material volume is evaluated in units of nuclear radiation lengths, defined as the characteristic length that describes the energy decay of a beam of electrons. Both the current CMS tracker material budget and that of Phase-2 tracker are shown in Figure 2.6. These simulations have been performed using tkLayout tool [58]. The material budget is calculated in function of pseudorapidity  $(\eta)$ . The current CMS calorimeter performances are highly affected by the large amount of material in CMS tracker, in particular for a value of  $|\eta|$  around 1.5 (left in Figure 2.6). The large amount of material used causes particle energy loss and scattering which affects tracking resolution. The Phase-2 tracker material budget (right in Figure 2.6) expects to be significantly decreased for an improvement in detector performances [2]. Due to the silicon sensors optimal operational temperature of −30°C [59] a cooling system is required. The new cooling system will be base on a CO2 twophase cooling to reduce the amount of passive material in the tracking volume [60]. As it will be highlighted in Section 2.6, the maximum power consumption and power density for the ASIC discussed in Chapter 4 is respectively 250 mW in

one module and 312.5 mW in the other one. An excess in power consumption would overload the power converters and the cooling structure, increasing the temperature of the module.

**Figure 2.6.** Material budget in the current (left) and future (right) CMS tracker detector. The material in front of the Inner Tracker is shown in brown, that inside IT tracking volume in yellow, that between IT and OT in green, and that inside the Outer Tracker tracking volume in blue [2].

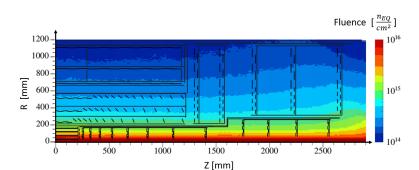

• Radiation tolerance. The new CMS detector has to work efficiently up to a target integrated luminosity of 3000 fb<sup>-1</sup>. The Phase-2 tracker requires to be fully operational for 10 years without maintenance for the Outer Tracker (OT). On the other hand, the Inner Tracker (IT) will be more accessible giving the option to extract the IT and replace those modules that accumulated too high radiation damage. FLUKA simulations have been performed to estimate the radiation damage of different detector regions, which is about one order of magnitude higher than the one used to project the current CMS tracker [61], [62]. The integrated particle fluence corresponding to a total of 3000 fb<sup>-1</sup> is shown in Figure 2.7. The maximum value in the innermost regions is about  $2.3 \cdot 10^{16} \, n_{EO}/cm^2$ , corresponding to a Total Ionizing Dose (TID) accumulated in 10 years of 12 MGy (1200 Mrad), as shown in Figure 2.8. Both fluence and TID decrease along the radius direction moving away from the beam axis. The OT modules are at distance from the beam axis ranging between about 20 cm to 120cm collecting around 100Mrad in the regions closer to the beam axis. Radiation hardening techniques need to be employed in the development and

design of custom readout electronics [2].

**Figure 2.7.** Integrated particle fluence for the Phase-2 tracker corresponding to 3000 fb<sup>-1</sup> of proton-proton collisions at 14 TeV, obtained with FLUKA [2].

**Figure 2.8.** Total Ionizing Dose for the Phase-2 tracker corresponding to 3000 fb<sup>-1</sup> of proton-proton collisions at 14 TeV, obtained with FLUKA [2].

# 2.3 CMS trigger system at HL-LHC

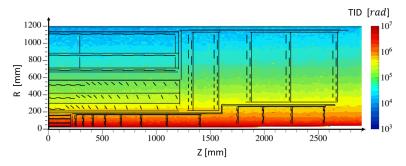

The current CMS detector is designed to measure precisely physical properties of leptons, photons and jets, together with other particles, in proton-proton (pp) collisions at LHC. Protons collide at a center-of-mass energy of 14 TeV and a instantaneous luminosity of  $10^{34}\,\mathrm{cm^{-2}s^{-1}}$  with a rate larger 1 GHz. Out of millions of collisions only  $\sim$  20 are interesting for CMS physics program. At the LHC the proton beams will cross each other at a frequency of 40 MHz. Thus, due to the limit in events storage for offline analysis, CMS detector delegates to a Trigger Data Acquisition (Trigger DAQ) system the work of selecting events of potential physics interest for new discoveries.

CMS Trigger DAQ system uses two levels of event selection, as shown in Figure 2.9. The first level (L1) of the CMS trigger is implemented in custom hardware with a fixed

latency. In the current CMS detector, within  $4\mu s$  of a collision the L1 trigger system decides if an event is selected or not, using only information from the calorimeter and muon detectors. This step allows reducing the total events rate of  $40\,\mathrm{MHz}$  to interesting events rate of  $100\,\mathrm{KHz}$ . A second level trigger, called High-Level Trigger (HLT), composed of array of commercially available computers running high-level physics algorithms, manages to achieve a value of accepted interesting events rate of  $100\,\mathrm{Hz}$  [63], [64].

Figure 2.9. Data flow in CMS Trigger DAQ system [64].

In the HL-LHC the pp collisions increase from 20 to 200 would make the current Trigger DAQ system not efficient enough. The large amount of detected hits would cause random combinations of hits creating a combinatorial background that would affect eventually the event reconstruction. A solution could be to increase the L1 trigger rate, but it has been demonstrated that this would not be enough. Therefore, the help of tracker information used in real time for the L1 trigger decision is fundamental to be able to reconstruct events efficiently improving substantially the rejection of combinatorial background [65], [66]. Therefore, an average L1 trigger rate of 750 KHz with a maximum latency of 12.5  $\mu$ s has been found to be optimal to reconstruct events efficiently [45].

# 2.4 Innovative approach: the $p_T$ module concept

The new HL-LHC will be characterized by an increased number of collisions that will generate a large amount of hit data at each Bunch Crossing (BX). The new tracker should provide real time data from each BX important for the L1 trigger decision while respecting the power budget and bandwidth limitations. As explained in Section 2.2.2, material budget in the tracker should be reduced to not affect calorimeter performance. Therefore, an increase in power cables and transmission lines in the tracker would not be a viable solution.

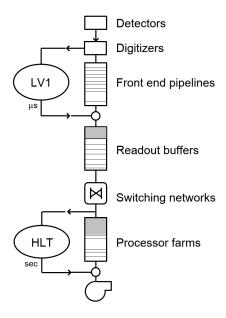

The L1 trigger should use a limited set of data from the tracker. Figure 2.10 (left) shows the number of tracks per event in function of  $p_T$ . In other words, it shows the  $p_T$  spectrum, normalised per BX, for a pileup of 400.

**Figure 2.10.** The pT spectrum, averaged per BX, (on the left) for charged particle that generate hit data at a radius of 25 cm for a pileup of 400 pp collisions per BX. The fraction of tracks with  $p_T$  less than the given  $p_T$  [67].

It is important to notice that particles with a transverse momentum  $p_T < 0.7$  are not of interest for the trigger decision since they do not reach other subdetectors due to the bending power of the 3.8T magnetic field [67]. Figure 2.10 (right) shows that the fraction of tracks with  $p_T$  less than 1 GeV is around 85%.

The L1 trigger decision and event reconstruction require the development of an "intelligent" module, which exploits the power of the strong magnetic field over particle trajectories thanks to two closely spaced layers made of silicon strip or pixel

sensors with a pitch of around 100  $\mu m$ . This is referred to as  $p_T$ -module, shown in Figure 2.11.

**Figure 2.11.** Illustration of the  $p_T$ -module concept [2].

The module performs a binary readout providing one bit information per channel to indicate whether the charge deposited by the particle, passing through the silicon sensor, is above the threshold or not. A particle, hitting the module, would create one cluster per layer (black squares in Figure 2.11).

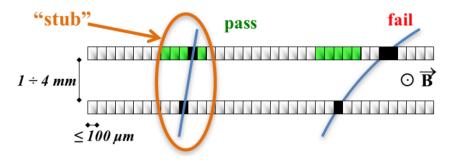

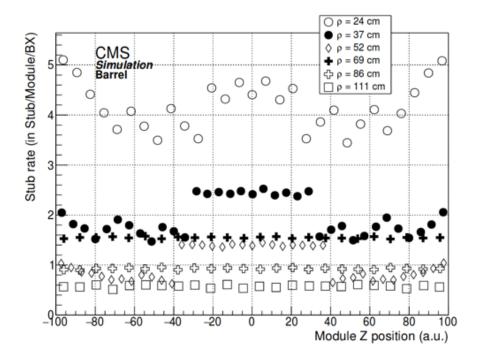

The particle energy and transverse momentum are inversely proportional to the particle trajectory curvature. The front-end electronics on the module must be able to locally select high- $p_T$  particles that thanks to their high energy are less affected by the strong magnetic field of 3.8 T. On the other hand, low- $p_T$  particles, falling below a certain threshold, are locally rejected. An accepted pair of clusters is called **stub** and this is the information that is sent out at every BX to the Trigger DAQ system to make the L1 trigger decision [68]. At the same time, the front-end electronics needs to store in a memory the full event data read upon the reception of a L1 trigger. The maximum time the full event data remains in the memory is 12.6 $\mu$ s, before it is discarded [45].

The ultimate objective of the  $p_T$  threshold is to reduce the data rate processed by the L1 trigger decision and to maintain an adequate resolution. With a threshold set to 2 GeV/c and L1 trigger rate of 750 KHz data rate reduces of a factor 10 [69].

#### 2.5 CMS tracker structure

The CMS Tracker is the subdetector closest to the collision point extending up to 1.2 m radially from the beam axis. As seen in section 2.2.2, the radiation levels are higher in the innermost regions and gradually decrease for modules along the radius. Moreover,

modules closer to the collision point require higher granularity and resolution.

According to the distance from the beam axis, the CMS tracker is composed of two parts:

- Inner Tracker (IT) extends between 3 cm and 20 cm from the beam axis. At this distance, it is impossible to detect particle trajectories bending due to the magnetic field, or, in other words, it is not possible to locally discriminate interesting high-p<sub>T</sub> particles. Therefore, the IT does not participate to the L1 trigger decision. The main requirement for the module that will be developed for this region is the radiation hardness. As seen in section 2.2.2 the TID collected at about 3 cm from the beam axis over 10 years of operation will be of 1 Grad.

- Outer Tracker (OT) extends between 20 cm and 120 cm from the beam axis.

The distance from the collision point allows exploiting the p<sub>T</sub>-module concept. Moreover, the TID expected over 10 years of operation is 100 Mrad, still challenging.

# 2.6 The p<sub>T</sub> modules in the CMS Outer Tracker

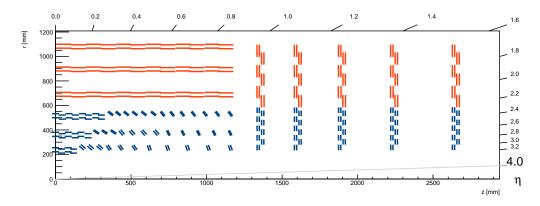

CMS Outer Tracker design, presented in Figure 2.12, has been optimized in terms of performance and material used. Assuming the collision point at the coordinate (0,0), six cylindrical barrel layers of modules are used for  $|z| < 1200 \, \text{mm}$ . For  $|z| > 1200 \, \text{mm}$  five "end-cap" double-discs. This disposition of modules allows an efficient and robust event reconstruction [70], [71]. Moreover, in order to respect the material budget requirement two different  $p_T$ -modules are being developed for the Outer Tracker:

- **Pixel-Strip(PS) modules**, in blue in Figure 2.12, are 7084, disposed at a radius distance between 20 cm and 60 cm, covering an area of  $60 \,\mathrm{m}^2$ . They consist of a pixel layer and a strip layer and provide the particle trajectories in  $\phi$  and z coordinates.

- **Strip-Strip(2S) modules**, in red in Figure 2.12, are 8424, disposed at a radius larger than 60 cm, covering an area of  $150 \,\mathrm{m}^2$ . Since they have two strip layers, they only provide the particle trajectories in  $\phi$  coordinate.

**Figure 2.12.** Tracker Layout section (one quarter) and  $p_T$ -modules disposition

PS modules need to offer higher resolution, therefore, a precise measurements of the z coordinate is achieved thanks to a pixelated sensor. However, a pixel sensor cannot be used everywhere in the tracker due to the higher power consumption and, consequently, higher material needed for cooling.  ${\rm CO_2}$  two-phase cooling will be used to remove heat from electronics and sensors. This technology helps to reduce the amount of passive material in the tracking volume. For thermal performance, the tracking system cannot operate at room temperatures since damage induced by traversing particles would render it inoperable earlier than the expected 10 years of operation: electric currents trough the sensors increase linearly with radiation damage. Luckily, these currents are also exponentially dependent on the temperature, can be largely reduced by running at low temperatures. The design requirement is to achieve a sensor temperature of  $-20^{\circ}{\rm C}$  or lower with a coolant temperature of  $-30^{\circ}{\rm C}$  for innermost modules. Solution in Figure 2.12 is the result of many studies and represents the optimum solution for tracking performance, cost of the silicon and material in the tracking volume.

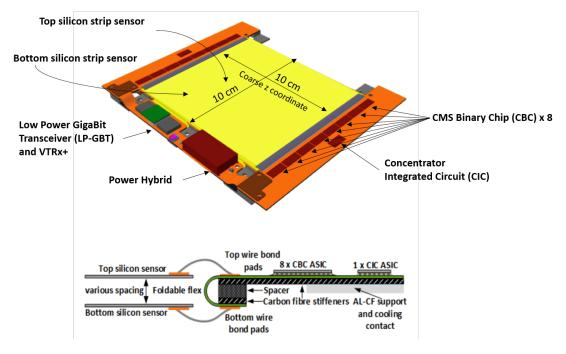

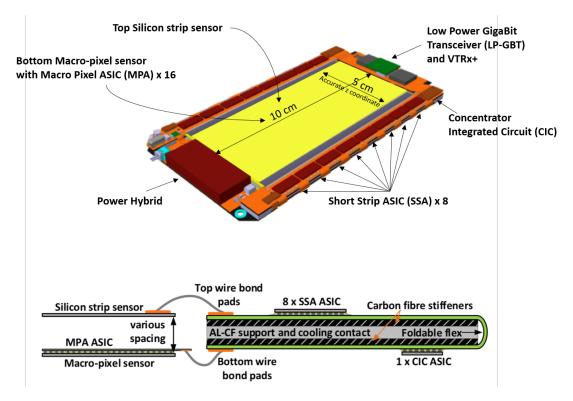

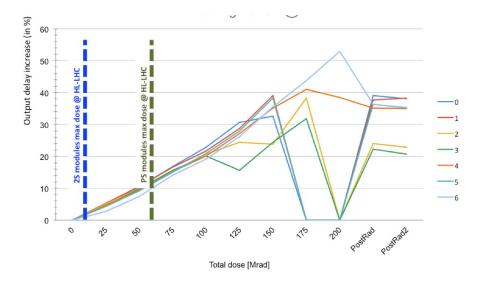

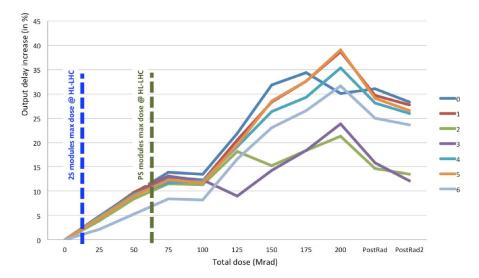

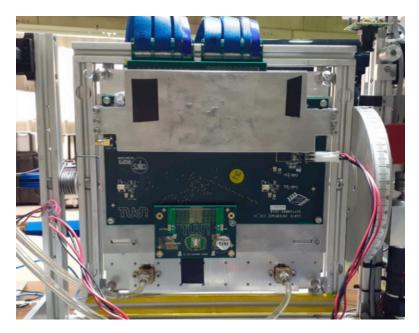

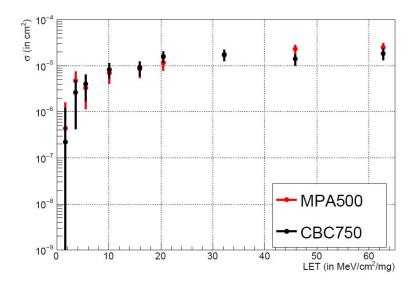

#### 2.6.1 2S-module structure