# Micro-architectural Analysis of Database Workloads

Présentée le 11 mai 2021

Faculté informatique et communications Laboratoire de systèmes et applications de traitement de données massives Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

# **Utku SIRIN**

Acceptée sur proposition du jury

Prof. K. Aberer, président du jury

Prof. A. Ailamaki, directrice de thèse

Dr S. Chaudhuri, rapporteur

Prof. S. Dwarkadas, rapporteuse

Prof. J. Larus, rapporteur

# Acknowledgements

In this small section, I would like to thank the people with whom I shared my PhD journey. This journey would not be possible without them.

First and foremost, I would like to thank my advisor, Anastasia Ailamaki, for her great guidance, teaching, care, help, and support. I learned so much from her that she is one of the major figures in my life who shaped my perspective. She is a great advisor, a fascinating teacher, and a true source of inspiration. It is a privilege to be her student, and I am so lucky to be one of them.

Next, I would like to thank my thesis committee members, Surajit Chaudhuri, Sandhya Dwarkadas, and James Larus. Their feedback and comments have greatly improved my thesis. I am so grateful for their time and effort in working with me and providing feedback. I would also like to thank my thesis jury president, Karl Aberer, for his valuable time and effort in organizing and coordinating my thesis exam.

I would like to thank my collaborators, Pinar Tozun, Danica Porobic, Vivek Narasayya, Surajit Chaudhuri, Sandhya Dwarkadas, Foteini Alvanaki, Anisa Llaveshi, Robert West, Nick Koudas, Ahmad Yasin, Angelos-Christos Anadiotis, Raja Appuswamy, Eliezer Levy, Shay Goikhman, Anthony Iliopoulos, Christina Mantonanaki, Jovan Djukic, Mariem Ali Belhaj, Mouadh Hamdi, and Doruk Cetin. I have been so lucky to be surrounded by such amazing people and work with them. They are great minds, incredible scientists, and great friends. Thank you so much for sharing your work, passion, and dedication with me.

When we started working on my first project with Pinar and Danica, I was super-excited. However, I soon realized that the life was harder than I thought, as I was struggling with adapting to a new country, university, and culture. Pinar and Danica were great mentors, who taught me a lot and also helped me in adapting to my new environment. Thank you so much for the great tutoring and the great friendship.

I have done my summer internship at the Data Management, Exploration and Mining (DMX) group at Microsoft Research, Redmond, closely working with Vivek Narasayya and Surajit Chaudhuri. I would like to thank them and the DMX group for the great opportunity and collaboration. It was super-fun and exciting working with you.

#### Acknowledgements

In December 2017, Sandhya gave a talk at EPFL. The talk was so interesting that I contacted her right away, and we started a collaboration. It was so educating and so much fun to work with her. I am so grateful for her time and support. I learned a lot from her, and I hope to keep doing so.

Anisa and I worked on a summer intern project, which were planned to last three months. Anisa, however, was so passionate about her work that she continued working on the project during the whole next year, until she writes a paper on it and makes it published. She is one of the smartest and most passionate people I know. Thank you for sharing your work and passion with me.

When I first joined DIAS, it was almost immediate that I felt at home. It is a big family with incredibly smart, generous, and fun people: Manos Karpathiotakis, Matthias Olma, Ioannis Alagiannis, Stella Giannakopoulou, Panagiotis Sioulas, Periklis Chrysogelos, Aunn Raza, Viktor Sanca, Iraklis Psaroudakis, Renata Borovica-Gajic, Georgios Psaropoulos, Eleni Tzirita-Zacharatou, Mirjana Pavlovic, Adrian Popescu, Odysseas Papapetrou, Tahir Azim, Darius Sidlauskas, Satya Valluri, Xuesong Lu, Miguel Branco, Thomas Heinis, Erietta Liarou, Cesar Matos, Benjamin Gaidioz, Eleni Zapridou, Bikash Chandra, Srinivas Venkatesh, Ioannis Mytilinis, Haoqiong Bian, Christina Mantonanaki, and Konstantinos Koukas. Thank you so much for always being there, and always supporting me through the hard times. You guys and gals are the best.

I would like to thank our admins, Lionel Sambuc and Stephane Ecuyer, for their great dedication, help, and support. They patiently bore with me. Thank you so much.

I would like to thank Dimitra Tsaoussis Melissargos and Erika Raetz for their great help and care.

For a PhD student, EPFL is a place where you meet your lifelong friends. I would like to thank the EPFL community who made my life at EPFL super-fun and exciting: Miranda Krekovic, Elie Najm, Mario Paulo Drumond, Winston Haaswijk, Dana Kianfar, Lionel Parreaux, Ana Hernandez-Lopez, Radu Cristian Ionescu, and many others. I had such a good time with all of them. Life would be much harder without their friendship.

I would like to thank my theatre group, The Village Players of Lausanne, for sharing their theatre passion with me. Margot Jaggy, Paul-James Hauduroy, Chris Hemmens, and all the others: Thanks so much.

I would like to thank the GirlsCoding organization, Miranda Krekovic, Marta Martinez, Pavle Belanovic, and all the other mentors, for the great initiative and making my life more meaningful and fun.

I would like to thank my friends from Turkey who always supported me and backed me up for my choices in life.

Lastly, I would like to thank my parents, Hatice Oflazoglu Sirin and Hayrettin Sirin. They are the hero of my, their, and many other children's lives. I am so lucky to be their child and grow up with the light in their hearts.

This research has been supported by grants from DIAS Lab, European Union Seventh Framework Programme (ERC-2013-CoG), under grant agreement no 617508 (ViDa)), Swiss National Science Foundation, Project No.: 200021\_146407/1 (Workload- and hardware-aware transaction processing), and HUAWEI Technologies Co., Ltd, P.R. China.

# **Abstract**

Database workloads have significantly evolved in the past twenty years. Traditional database systems that are mainly used to serve Online Transactional Processing (OLTP) workloads evolved into specialized database systems that are optimized for particular types of workloads. Data warehousing applications have led to Online Analytical Processing (OLAP) workloads and real-time analytical processing applications have led to Hybrid Transactional and Analytical Processing (HTAP) workloads.

Similarly, modern hardware has significantly evolved in the past twenty years. Unicore, simple processors with megabytes of main memory have evolved into multi-core, power-limited processors with hundreds of gigabytes of main memory. Furthermore, the processors have complex micro-architectural features such as Single Instruction Multiple Data (SIMD) instructions and complex branch predictors. Advancements in processor technology have led to further evolution of database systems with novel system architectures and query processing paradigms.

We present the micro-architectural behavior of modern database workloads on a modern processor for various categories of workloads and generations of database systems. We examine three main categories of database workloads and study them separately: OLTP, OLAP, and HTAP. We show that OLTP systems spend most of their execution time waiting for instruction-cache or data-cache misses, where the data-cache misses are due to the random data-accesses during the index lookup operation. While using an efficient index structure can significantly reduce the number of data-cache misses, the main micro-architectural bottleneck remains the data-cache misses due to the costly random data-accesses. Hence, OLTP systems should adopt techniques that mitigate the random data-accesses.

OLAP systems spend most of their execution time in data-cache misses, where the data-cache misses are due to high pressure on the memory bandwidth for sequential-scan-heavy queries, and are due to random data-accesses for join-intensive queries. OLAP systems that follow tuple-at-a-time execution models efficiently use the CPU cycles. However, they require executing a significantly larger number of instructions hence are significantly slower than the systems that follow vector-at-a-time and compiled execution models. Therefore, OLAP systems should use efficient execution models and adopt techniques that mitigate data-cache misses.

#### Abstract

HTAP systems combine OLTP and OLAP systems into a single, unified system, where the OLTP and OLAP systems run on the same hardware and on the same data. Running on the same hardware results in hardware-level interference, where the OLTP throughput significantly drops due to the OLAP side sharing the hardware resources. Running on the same data results in increased OLAP query execution time due to the need for the OLAP side to process the fresh tuples generated by the OLTP side. Therefore, HTAP systems should adopt techniques that mitigate the hardware-level interference and should make sure that the OLAP side uses enough resources to minimize the increased query execution time.

**Keywords:** Database management systems, micro-architecture, micro-architectural behavior, performance characterization, modern hardware, hardware-software co-design, benchmarking, transactional processing, analytical processing, hybrid transactional and analytical processing.

# Résumé

Les charges de travail des bases de données ont considérablement évolué au cours des vingt dernières années. Les systèmes de base de données traditionnels qui sont principalement utilisés pour servir les charges de travail de traitement transactionnel en ligne (OLTP) ont évolué vers des systèmes de base de données spécialisés qui sont optimisés pour des types particuliers de charges de travail. Les applications d'entreposage de données ont conduit à des charges de travail de traitement analytique en ligne (OLAP) et les applications de traitement analytique en temps réel ont conduit à des charges de travail de traitement transactionnel et analytique hybride (HTAP).

De même, le matériel moderne a considérablement évolué au cours des vingt dernières années. Unicore, des processeurs simples avec des mégaoctets de mémoire principale ont évolué vers des processeurs multicœurs à puissance limitée avec des centaines de gigaoctets de mémoire principale. En outre, les processeurs ont des caractéristiques micro-architecturales complexes telles que des instructions SIMD (Single Instruction Multiple Data) et des prédicteurs de branche complexes. Les progrès de la technologie des processeurs ont conduit à une nouvelle évolution des systèmes de bases de données avec de nouvelles architectures système et des paradigmes de traitement des requêtes.

Nous présentons le comportement micro-architectural des charges de travail de base de données modernes sur un processeur moderne pour différentes catégories de charges de travail et générations de systèmes de base de données. Nous examinons trois catégories principales de charges de travail de base de données et les étudions séparément : OLTP, OLAP, et HTAP. Nous montrons que les systèmes OLTP passent la majeure partie de leur temps d'exécution à attendre les échecs du cache d'instructions ou du cache de données, où les échecs du cache de données sont dus aux accès aléatoires aux données pendant l'opération de recherche d'index. Bien que l'utilisation d'une structure d'index efficace puisse réduire considérablement le nombre d'échecs de cache de données, le principal goulot d'étranglement micro-architectural reste les échecs de cache de données en raison des accès aléatoires coûteux aux données. Par conséquent, les systèmes OLTP devraient adopter des techniques qui atténuent les accès aléatoires aux données.

Les systèmes OLAP passent la majeure partie de leur temps d'exécution dans des échecs de cache de données, où les échecs de cache de données sont dus à une pression élevée sur

la bande passante de la mémoire pour les requêtes lourdes d'analyse séquentielle, et sont dus à des accès aléatoires aux données pour les requêtes à jointure intensive . Les systèmes OLAP qui suivent des modèles d'exécution tuple à la fois utilisent efficacement les cycles du processeur. Cependant, ils nécessitent l'exécution d'un nombre beaucoup plus important d'instructions et sont donc beaucoup plus lents que les systèmes qui suivent des modèles d'exécution vectoriels à la fois et compilés. Par conséquent, les systèmes OLAP doivent utiliser des modèles d'exécution efficaces et adopter des techniques qui atténuent les erreurs de cache de données.

Les systèmes HTAP combinent les systèmes OLTP et OLAP en un système unique et unifié, où les systèmes OLTP et OLAP fonctionnent sur le même matériel et sur les mêmes données. L'exécution sur le même matériel entraîne des interférences au niveau matériel, où le débit OLTP diminue considérablement en raison du partage des ressources matérielles du côté OLAP. L'exécution sur les mêmes données entraîne une augmentation du temps d'exécution de la requête OLAP en raison de la nécessité pour le côté OLAP de traiter les nouveaux tuples générés par le côté OLTP. Par conséquent, les systèmes HTAP doivent adopter des techniques qui atténuent les interférences au niveau matériel et doivent s'assurer que le côté OLAP utilise suffisamment de ressources pour minimiser l'augmentation du temps d'exécution des requêtes.

**Mots clés :** Systèmes de gestion de base de données, micro-architecture, comportement micro-architectural, caractérisation des performances, matériel moderne, co-conception matériel-logiciel, benchmarking, traitement transactionnel, traitement analytique, traitement transactionnel et analytique hybride.

# **Contents**

| Ac | cknov | wledgements                                                              | j  |

|----|-------|--------------------------------------------------------------------------|----|

| Ał | ostra | ct (English/Français)                                                    | v  |

| 1  | Intr  | roduction                                                                | 1  |

|    | 1.1   | Database Management Systems                                              | 1  |

|    | 1.2   | Evolution of Modern Processors                                           | 2  |

|    | 1.3   | Database Management Systems on Modern Processors                         | 3  |

|    | 1.4   | Micro-architectural Behavior of Database Workloads                       | 4  |

|    | 1.5   | Thesis Statement and Contributions                                       | 4  |

|    | 1.6   | Roadmap                                                                  | 6  |

| 2  | Bac   | kground                                                                  | 9  |

|    | 2.1   | A Modern Processor Micro-architecture                                    | g  |

|    | 2.2   | Online Transactional Processing                                          | 10 |

|    |       | 2.2.1 In-memory Online Transaction Processing                            | 11 |

|    | 2.3   | Online Analytical Processing                                             | 13 |

|    |       | 2.3.1 Column-stores                                                      | 14 |

|    |       | 2.3.2 Query Processing Paradigms                                         | 14 |

|    | 2.4   | Hybrid Transactional and Analytical Processing                           | 15 |

|    | 2.5   | Profiling A Modern Processor Micro-architecture                          | 16 |

|    | 2.6   | Related Work on Micro-architectural Analysis of Data-Intensive Workloads | 17 |

| 3  | Mic   | ro-architectural Analysis Methodologies                                  | 19 |

|    | 3.1   | Introduction                                                             | 19 |

|    | 3.2   | Micro-architectural Analysis Methodologies                               | 20 |

|    |       | 3.2.1 Retiring                                                           | 20 |

|    |       | 3.2.2 Cache-Miss-Based Methodology                                       | 21 |

|    |       | 3.2.3 Top-down Micro-architectural Analysis Methodology                  | 22 |

|    | 3.3   | Setup and methodology                                                    | 23 |

|    | 3.4   | Experimental Evaluation                                                  | 25 |

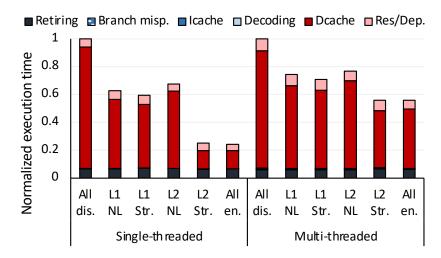

|    |       | 3.4.1 High-level analysis                                                | 25 |

|    |       | 3.4.2 Front-end stalls                                                   | 26 |

|    |       | 3.4.3 Back-end stalls                                                    | 27 |

### **Contents**

|   | 3.5  | Conclusion                                             | 27 |

|---|------|--------------------------------------------------------|----|

| 4 | Onli | ine Transactional Processing Workloads                 | 29 |

|   | 4.1  | Introduction                                           | 29 |

|   | 4.2  | Setup and Methodology                                  | 31 |

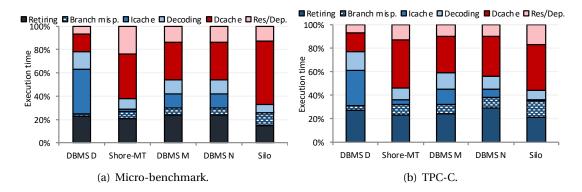

|   | 4.3  | Micro-benchmark                                        | 34 |

|   |      | 4.3.1 Sensitivity to Data Size                         | 35 |

|   |      | 4.3.2 Sensitivity to Work per Transaction              | 39 |

|   | 4.4  | TPC Benchmarks                                         | 43 |

|   |      | 4.4.1 TPC-B                                            | 43 |

|   |      | 4.4.2 TPC-C                                            | 44 |

|   | 4.5  | Index and Compilation Optimizations, and Data Types    | 45 |

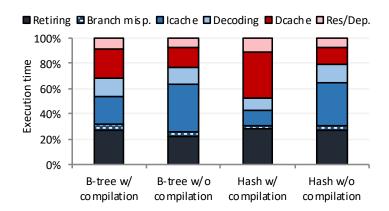

|   |      | 4.5.1 Impact of index type and compilation             | 46 |

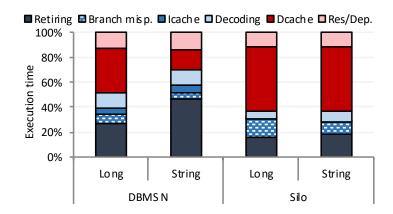

|   |      | 4.5.2 Impact of data type                              | 47 |

|   | 4.6  | Impact of Multi-threading                              | 48 |

|   | 4.7  | Memory Bandwidth Consumption                           | 49 |

|   |      | 4.7.1 Data Size Micro-benchmark                        | 49 |

|   |      | 4.7.2 Work per Transaction Micro-benchmark             | 50 |

|   |      | 4.7.3 TPC-C                                            | 51 |

|   | 4.8  | Acceleration Features                                  | 52 |

|   |      | 4.8.1 Hyper-threading                                  | 52 |

|   |      | 4.8.2 Turbo-boost                                      | 53 |

|   |      | 4.8.3 Hardware prefetchers                             | 53 |

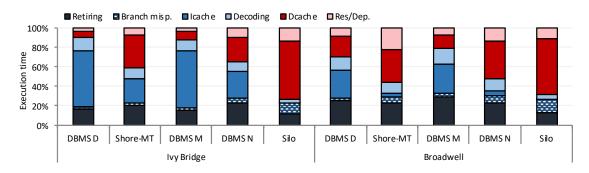

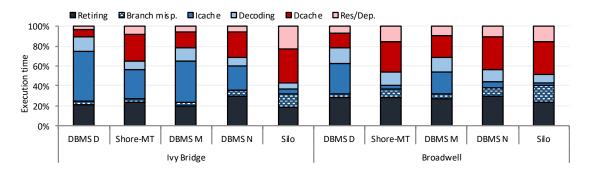

|   | 4.9  | Ivy Bridge vs. Broadwell                               | 54 |

|   | 4.10 | Conclusion                                             | 55 |

| 5 | Onli | ine Analytical Processing Workloads                    | 57 |

| • | 5.1  | Introduction                                           | 57 |

|   | 5.2  | Setup & Methodology                                    | 59 |

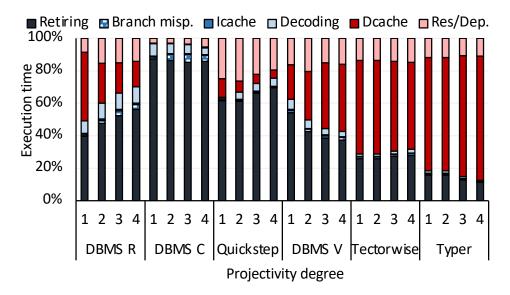

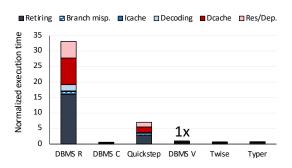

|   |      | Projection                                             | 62 |

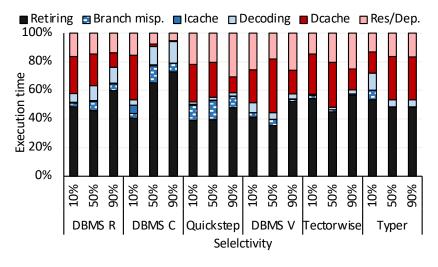

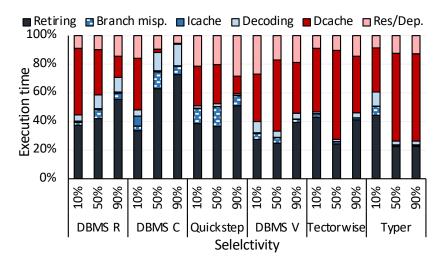

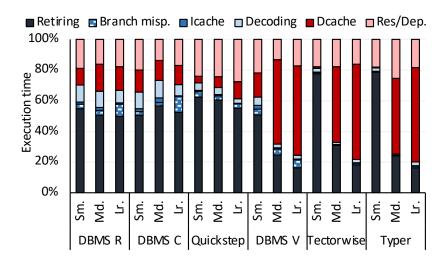

|   | 5.4  | Selection                                              | 65 |

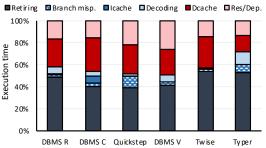

|   | 5.5  | Join                                                   | 69 |

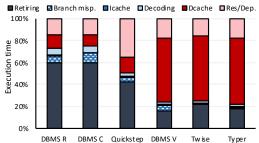

|   | 5.6  | TPC-H                                                  | 71 |

|   | 5.7  | Mixed Query Workload                                   | 77 |

|   | 5.8  | Predication                                            | 78 |

|   | 5.9  | SIMD                                                   | 79 |

|   |      | 5.9.1 Projection & Selection                           | 80 |

|   |      | 5.9.2 Join                                             | 81 |

|   | 5.10 | Hardware Prefetchers                                   | 81 |

|   |      | Hyper-threading and Turbo-boost                        | 82 |

|   |      | Conclusion                                             | 84 |

| 6 |      | orid Transactional and Analytical Processing Workloads | 85 |

|    | 6.1    | Introduction                                         | 85  |

|----|--------|------------------------------------------------------|-----|

|    | 6.2    | Setup and Methodology                                | 87  |

|    | 6.3    | <i>DBMS A</i>                                        | 89  |

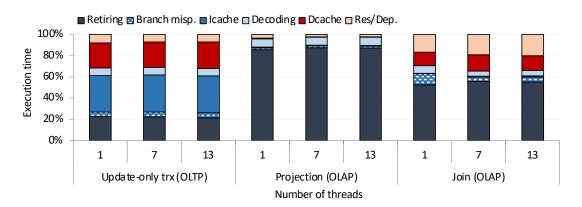

|    |        | 6.3.1 Micro-benchmark                                | 89  |

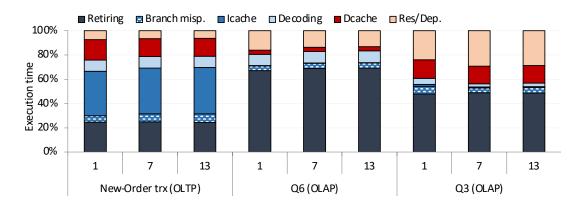

|    |        | 6.3.2 CH benchmark                                   | 93  |

|    | 6.4    | <i>DBMS B</i>                                        | 95  |

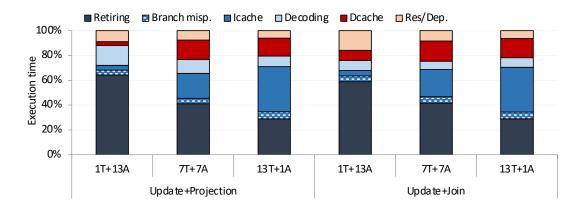

|    |        | 6.4.1 Micro-benchmark                                | 95  |

|    |        | 6.4.2 CH benchmark                                   | 98  |

|    | 6.5    | Academic Prototype                                   | 100 |

|    |        | 6.5.1 HTAP Architecture                              | 100 |

|    |        | 6.5.2 Software-level Interference                    | 101 |

|    |        | 6.5.3 Hardware-level Interference                    | 107 |

|    | 6.6    | Conclusions                                          | 111 |

| 7  | Less   | sons Learned, Conclusions, and Future Outlook        | 113 |

|    | 7.1    | Lessons Learned                                      | 113 |

|    |        | 7.1.1 Online Transactional Processing                | 113 |

|    |        | 7.1.2 Online Analytical Processing                   | 116 |

|    |        | 7.1.3 Hybrid Transactional and Analytical Processing | 117 |

|    | 7.2    | Conclusions and Future Outlook                       | 118 |

| A  | App    | pendix                                               | 121 |

|    |        |                                                      | 121 |

|    |        | Read-write Micro-benchmark                           |     |

|    |        | A.2.1 Sensitivity to Data Size                       |     |

|    |        | A.2.2 Sensitivity to Work per Transaction            |     |

|    |        | A.2.3 Index, Compilation and Data Type               |     |

| Bi | bliog  | graphy                                               | 127 |

|    |        | graphy                                               | 135 |

|    |        |                                                      | 100 |

| Cı | ırricı | ulum Vitae                                           | 137 |

# 1 Introduction

## 1.1 Database Management Systems

Today's world is data-driven. Regular media sources, social media sources, individual people, as well as industrial and community organizations all produce and consume data. This leads to an enormous size for the data and demand to produce and consume the data [1, 36, 37, 38]. Database Management Systems (DBMS) have been at the centre of storing, managing and processing data. As the data size and the demand to produce and consume the data is evergrowing, researchers and developers from academia and industry have proposed numerous techniques and novel DBMS architectures to cope with the ever-growing size of the data and the speed that the data is produced and consumed [8, 34, 40, 54, 105].

One of the most important driving-forces behind novel DBMS architectures has been the advancements in the modern hardware [4]. Modern hardware advancements include the growing-sized main memories and the main-memory bandwidths, complex micro-architectural features such as strong branch prediction features and deep cache hierarchies features, and wide data-parallel execution units such as Single Instruction Multiple Data (SIMD) execution units. The novel hardware-aware DBMS architectures allowed DBMS to use their hardware resources more efficiently, and hence deliver orders of magnitude higher performance [2, 71].

In addition to the modern hardware, the evolving workload demands and characteristics have been the other major driving-force behind novel DBMS architectures. Early relational database systems were mostly driven by Online Transaction Processing (OLTP) workloads, where the workloads are composed of several short-lived transactions that read or write to small amount of records [21, 22]. During the late 1990s, data warehousing applications gained significant attention, where Online Analytical Processing (OLAP) workloads have emerged. OLAP workloads are composed of read-only, long-running queries that process large number of records. Due to the significant differences between the OLAP and OLTP workloads, a specialized set of DBMS have been designed and developed to serve for OLAP workloads [19].

In the past five years real-time analytical processing applications have gained a significant

attention. Real-time analytical processing applications aimed to perform complex OLAP queries on fresh, transactional data. As a result, Hybrid Transactional and Analytical Processing (HTAP) workloads have emerged. HTAP workloads are mix of OLTP and OLAP workloads and are served by HTAP systems designed to efficiently support both OLTP and OLAP workloads [14, 83]. Having designed and developed DBMS that efficiently use their hardware resources and specialized for individual types of workloads allowed DBMS to deliver high performance and cope with the ever-growing size of the data and demand to produce and consume the data.

### 1.2 Evolution of Modern Processors

Commodity processors have been continuously evolving over the past five decades, in the light of Moore's Law. Initial processor technology focused on improving the single-threaded performance by providing wider instruction-level parallelism (ILP) (through wider-issue superscalar execution), higher clock frequency rates, and complex micro-architectural features such as highly-accurate branch prediction units and aggressive pipelined execution. During the late 1990s, multiprocessor technology has gained a rise due to the scalability limitations in providing higher ILP and the dissipated heat [82].

Multiprocessor technology has widely been adopted. Numerous applications, such as transaction processing and scientific processing applications, benefited the thread-level parallelism that the multiprocessor technology provides. As a result, multiprocessor technology has lead to popular multi-core processors, where a single Central Processing Unit (CPU) contains multiple communicating cores sharing a coherent main memory. The processor designers gradually increased the number of cores per processor to supply the increasing demand for the thread-level parallelism. Moore's Law coupled with Dennard scaling allowed to have more and more cores on the same CPU. Moore's Law stated that the number of transistors on chip doubles every 18 months. Whereas, Dennard scaling stated that the reduced-sized transistors also consume proportionally reduced power per transistor. As a result, processors accommodated an increasing number of transistors within a similar power budget [24, 77].

In the past five years, the increased core counts have slowed down due to the failure of Dennard scaling. While the number of transistors kept increasing according to Moore's Law, the amount of heat dissipated per transistor failed to decrease. As a result, the increased number of transistors' heat dissipation has hit the maximum level of dissipated heat that the processor silicon can accommodate. The number of cores per processor is more and more flattened, and the applications have stopped benefiting from the exponentially increasing performance freely provided by the hardware [27].

Having hit the power wall, the processor vendors and application developers have considered alternative micro-architectures. In particular, beefy, power-hungry multi-core processors are compared with wimpy, low-power multi-core processors. The goal has been using relatively larger number of low-power cores compared to the number of power-hungry cores, and

benefiting from high thread-level parallelism that the applications exhibit. While this idea has led to several important system architectures [6], wimpy cores failed to gain a wide adoption. The reason has been that, despite the applications exhibit high degree of thread-level parallelism, the scalability of an application is more and more limited as the number of parallel threads it uses is increased. By following Amdahl's law, even a small serialization point has become a performance bottleneck for the system. This required careful and explicit parallelization of many applications, putting a prohibitive software development cost on the programmers [78].

As a result, today's commodity servers are evolved into power-hungry multi-core chips with dozens of cores, where each core contains complex micro-architectural features such as complex branch predictor, deep pipelines, superscalar out-of-order execution units, and deep cache hierarchies. As the processors have evolved into a particular micro-architecture with modest performance improvements over the new generations, software has gained a significant importance in exploiting the modern hardware features to deliver a high performance, and cope with the ever-growing size of the data and the demand to produce and consume the data [4].

### 1.3 Database Management Systems on Modern Processors

Database systems have long been optimized to efficiently use modern hardware features. Initial work has concentrated on multi-core scalability of traditional, disk-based transaction processing systems, where centralized database system components such as lock and log managers have become bottlenecks inhibiting the multi-core scalability [48, 84, 110]. Later work has concentrated on exploiting large main memory sizes, and eliminating heavy-weight components of disk-based transaction processing systems. This has lead to popular in-memory transaction processing systems that are tightly optimized for modern hardware, providing orders of magnitude higher performance than traditional disk-based systems [25, 54, 106].

Simultaneously, column-stores have gained a significant attention, where specialized analytical processing engines serve for read-only, complex queries over column-wise stored data. Column-stores keep the two-dimensional relational tables column-by-column, rather than traditionally-adopted row-by-row (i.e., record-by-record). This way, column-stores process only the necessary columns, i.e., attributes such as age and name, which allows more efficiently using disk/memory bandwidth and significantly reducing the data processing overheads. Column-stores gained a wide adoption. Most of the major DBMS vendors has now their specialized column-store engines to serve for read-only, analytical processing workloads [2, 17, 40].

### 1.4 Micro-architectural Behavior of Database Workloads

Micro-architectural behavior defines where the CPU cycles are spent within the core micro-architecture when running a particular workload. The core micro-architecture components include the instruction fetch and decoding units, branch prediction unit, instruction execution units and data load and store units. Early work on understanding the micro-architectural behavior of database management systems have focused on architectural features that are useful for commercial database systems, such as out-of-order execution, on-chip cache sizes and size of the instruction queue [11, 32, 53, 90, 103]. The studies examined the architectural features for a single, commercial, well-established system, when running the two major types of database workloads, OLTP and OLAP, on a hardware simulation environment.

A later work took a step further and examined micro-architectural behavior of several commercial DBMS to identify the micro-architectural behavioral trends that hold across different DBMS running on real hardware [3]. This was the first work that examined micro-architectural behavior across different DBMS and focused on general trends across the DBMS. Later on, several studies have concentrated on traditional, disk-based transaction processing systems running on real hardware, and associated micro-architectural behavioral components, such as instruction-cache stalls, with particular transaction processing system components, such as lock manager [109, 112, 116].

Despite the large body of micro-architectural characterization work for database workloads, existing work has only focused on either single class of a DBMS, e.g., a well-established commercial DBMS, or a single type of database workload, such as OLTP workloads. However, both DBMS and database workloads have gone through a significant evolution over the past 20 years, by following the advancements in the hardware and the application demands. Furthermore, the commodity processor micro-architecture has significantly advanced over the past twenty years. Hence, the micro-architectural behavior of state-of-the-art database workloads remains unclear.

As the processor performance is stagnating due to power limitations, it has been ever more important to understand the micro-architectural behavior in order to efficiently use the micro-architectural resources and extract maximum performance out of the server hardware. This thesis presents micro-architectural analysis of database workloads across different generations of DBMS and categories of database workloads. Its goal is to understand the micro-architectural behavior of the state-of-the-art database workloads, identify general trends and main performance bottlenecks at the software- and hardware-levels, and highlight investigation directions for future database management systems to deliver high performance and efficiently use their hardware resources.

### 1.5 Thesis Statement and Contributions

The statement of this thesis is as follows.

#### **Thesis Statement**

Understanding a database system's interaction with compute and memory resources is key to efficiently using hardware. Database systems spend most of their execution time waiting for instruction-cache or data-cache misses, where data-cache misses are due to high pressure on the memory bandwidth if the data access pattern is sequential, and due to random data-accesses if the data access pattern is random. Workloads with mixed sequential and random data-access patterns also suffer from interference. Hence, database system architects should design and develop data structures and algorithms that are aware of the data access pattern and cache behavior to efficiently use the hardware resources.

Below, is a summary of our contributions in this thesis:

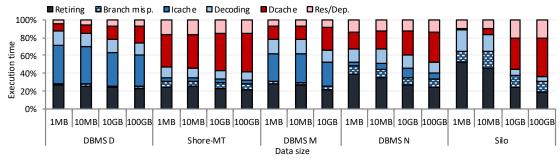

- We examine state-of-the-art micro-architectural analysis methodologies. We compare and contrast conventional cache-miss-based methodology with Intel's recently-proposed Top-down Micro-architecture Analysis Methodology (TMAM). We observed that cache-miss-based methodology under- or over-estimates the execution time due to under- or over-estimating the instruction or data-cache stalls. We adopt Intel's TMAM methodology in our analyses.

- We show that Online Transaction Processing (OLTP) systems spend more than half of the execution time waiting for instruction-cache or data-cache misses. The disk-based OLTP systems suffer mainly from instruction-cache misses, whereas the in-memory OLTP systems suffer from either instruction-cache or data-cache misses. The data-cache misses are due to the random data-accesses during the index lookup operation. While using an efficient index structure can significantly reduce the number of data-cache misses, it does not change the main micro-architectural bottleneck due to the costly random data-accesses.

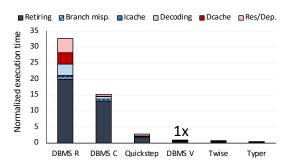

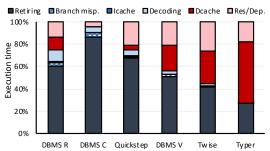

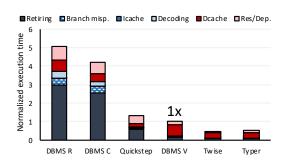

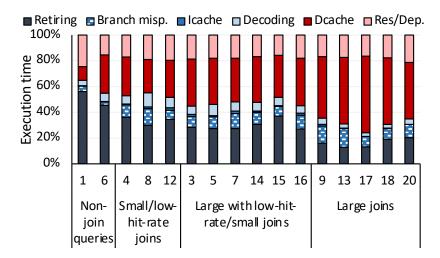

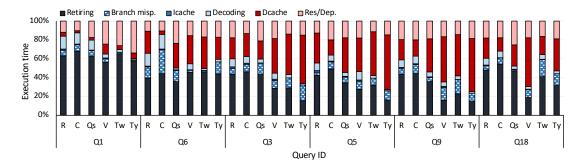

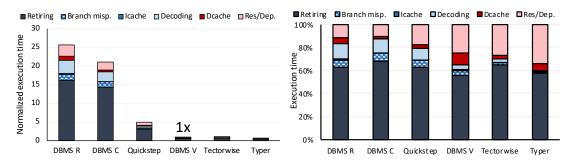

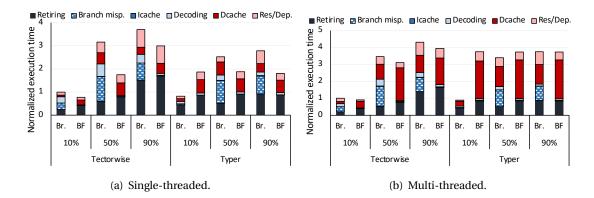

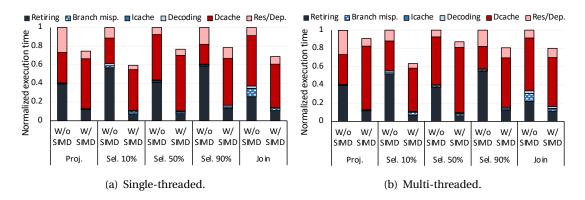

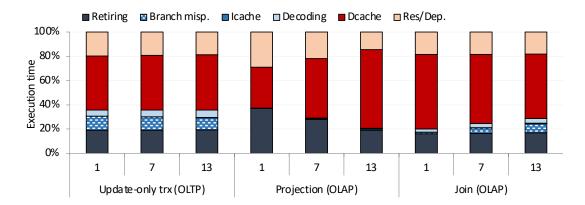

- We show that, if the system follows vector-at-a-time or compiled execution model, Online Analytical Processing (OLAP) systems spend most of their execution time waiting for data-cache misses. The data-cache misses are due to high pressure on the memory bandwidth for sequential-scan-heavy queries, and are due to random data-accesses for join queries. The OLAP system that follows the tuple-at-a-time execution model efficiently uses the CPU cycles. However, it requires executing a significantly larger number of instructions hence is 1.7 to 5 times slower than the systems that follow the vector-at-a-time and compiled execution models.

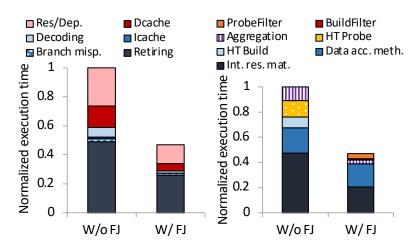

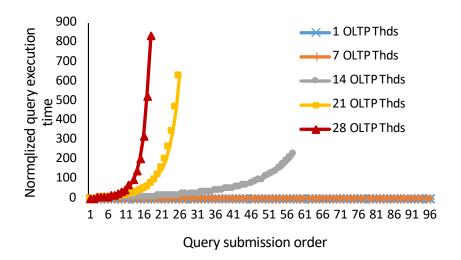

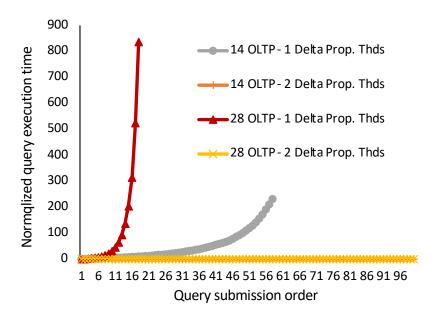

- Hybrid Transactional and Analytical Processing (HTAP) systems combine OLTP and OLAP systems into a single, unified system, where the OLTP and OLAP systems run on the same data and on the same hardware. We show that running the OLTP and OLAP systems on the same hardware results in hardware-level interference. The OLTP

throughput is decreased by 22 to 40% due to the OLAP side sharing the hardware resources. Running the OLTP and OLAP systems on the same data results in software-level interference. The query execution time at the OLAP side is increased due to the additional work processing the fresh tuples generated by the OLTP side. We show that, to minimize the increase in the OLAP query execution time, the OLAP component should be allocated enough resources to be able to process the fresh tuples faster than the OLTP component generates them.

## 1.6 Roadmap

In this section, we present the organization of the thesis.

- Chapter 2 presents the background for this thesis. It presents the micro-architectures of today's server processors, and the workload characteristics for the state-of-the-art database workloads: OLTP, OLAP and HTAP workloads. It describes the performance monitoring units (PMU) of today's modern processors, and how to profile performance of a modern processor. Lastly, it presents the related work on the micro-architectural analysis of data-intensive workloads.

- Chapter 3 compares and contrasts the state-of-the-art micro-architectural analysis methodologies: the popular cache-miss-based methodology and Intel's recently-proposed Top-down Micro-architecture Analysis Methodology (TMAM). It concludes that, while the two methodologies provide similar high-level micro-architectural behavior, Intel's TMAM is more powerful as it provides end-to-end execution time breakdown and also accounts for non-memory-stalls. Based on our conclusions in this chapter, we chose Intel TMAM as our micro-architectural analysis methodology, and use it in the rest of this thesis.

- Chapter 4 presents the micro-architectural analysis of OLTP workloads. It presents micro-benchmark as well as standard TPC-C benchmark evaluation. It uses micro-benchmarks for sensitivity analyses that vary the size of the data and the amount of work per transaction. It uses the standard TPC-B and TPC-C benchmarks to confirm that the conclusions drawn using the micro-benchmark apply for a standard benchmark. It further presents the impact of index, transaction compilation, data type and multi-threading on the micro-architectural behavior. It examines the effect of hardware acceleration features and also compares and contrasts the micro-architectural behavior of different Intel micro-architectures. The chapter concludes that OLTP workloads spend most of their execution time in instruction-cache or data-cache misses, where the data-cache misses are due to the random-data-access-heavy nature of OLTP workloads.

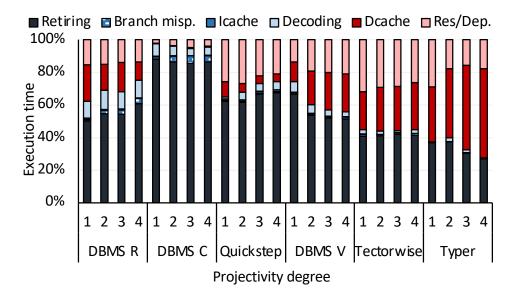

- Chapter 5 presents the micro-architectural analysis of OLAP workloads. Unlike OLTP workloads, OLAP workloads are read-only, have highly iterative nature in their computation, and also exhibit both random and sequential data access patterns. The chapter

performs sensitivity analyses by using micro-benchmarks, and also presents standard TPC-H benchmark analysis to confirm that the findings by the micro-benchmark analyses apply to the standard benchmark. The chapter further performs mixed query workload evaluation where workloads with heterogeneous data access patterns are evaluated. The chapter examines software-level optimizations, such as predication, and hardware-level acceleration features, such as SIMD and hyper-threading. The chapter concludes that OLAP workloads spend most of their execution time in data-cache misses, where the data-cache misses are due to either high pressure on the memory bandwidth or to random data-accesses. Although OLAP systems that follow the tuple-at-a-time execution model efficiently use the CPU cycles, they are 1.7 to 4.5 times slower than the OLAP systems that follow vector-at-a-time and compiled execution models due to executing a significantly larger number of instructions.

- Chapter 6 presents HTAP workloads evaluation. HTAP workloads are composed of mixed OLTP and OLAP workloads, where the OLTP and OLAP workloads share both data and hardware. In this chapter, we examine how data and hardware sharing affects the OLTP and OLAP throughput of an HTAP system. The chapter performs micro-benchmark evaluation with workloads that mix basic data-access patterns: sequential and random, as well as the complex CH benchmark evaluation. In this chapter, we examine last-level cache, memory-bandwidth and hyper-thread sharing. We conclude that, while the OLAP throughput does not drop, the OLTP throughput drops by 22 to 40% when OLTP and OLAP workloads share hardware resources. When OLTP and OLAP workloads share data, the OLAP query execution time is minimally affected by the OLTP workload if the OLAP workload is allocated enough resources to process the fresh tuples faster than the OLTP workload generates them.

- Chapter 7 finally presents the conclusions and highlights future investigation directions for modern database systems to efficiently use the hardware resources and deliver a high performance.

# 2 Background

This chapter covers the necessary background for the thesis and the related work on micro-architectural analysis of data-intensive workloads. The background includes description of the modern processor micro-architectures, and the descriptions of the modern database workloads: Online Transactional Processing (OLTP), Online Analytical Processing (OLAP), and Hybrid Transactional and Analytical Processing (HTAP) workloads. Lastly, the background describes how to profile a modern processor micro-architecture.

### 2.1 A Modern Processor Micro-architecture

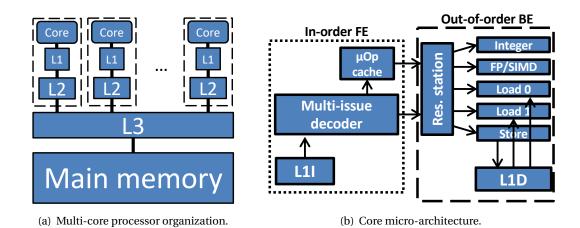

This section outlines the micro-architecture of today's modern processors. Figure 2.1 shows the simplified block diagram of the Intel Sandy/Ivy Bridge micro-architecture [42]. The left-hand side of the figure presents the multi-core processor organization, whereas the right-hand side of the figure presents the core micro-architecture. The multi-core processor includes multiple cores with private L1 and L2 level of caches, and a shared L3 level of cache. The L3 level of cache is connected to the main memory. The number of clock cycles needed to access to the caches is increased as the level in the cache is increased in the memory hierarchy. For the Intel Sandy/Ivy Bridge micro-architecture, it takes ~4, 12, 30 and 200 clock cycles to access to L1, L2, L3 and main memory, respectively.

The right-hand side of Figure 2.1 zooms into a single core, and presents the core micro-architecture. The core micro-architecture contains two major building blocks, the front-end (FE) and the back-end (BE). FE contains the micro-architectural structures to fetch, decode and issue instructions, which are L1 instruction (L1I) cache, a multi-issue instruction-to-micro-operation( $\mu$ Op) decoder and a small (1.5KB [42])  $\mu$ Op cache. The L1I cache is responsible for keeping the instructions that the processor will execute next. The decoder decodes the fetched instructions into  $\mu$ Ops. As Intel uses complex instruction set architecture, i.e., CISC, it needs to decode complex instructions into simpler  $\mu$ Ops. The decoder is multi-issue, i.e., it is able to decode and deliver multiple instructions in one cycle. Delivering multiple instructions in one cycle enables exploiting instruction-level parallelism, and using the resources of the BE

Figure 2.1 – An out-of-order processor model based on Intel Sandy/Ivy Bridge microarchitecture [42]. FE: front-end, BE: back-end.

more efficiently. Lastly, the  $\mu$ Op cache is responsible for keeping the most recently decoded  $\mu$ Ops to avoid re-decoding them.

BE contains the micro-architectural structures to execute the issued  $\mu$ Ops, which are a reservation station (RS), several execution units and L1 data (L1D) cache. When a µOp arrives to BE, BE registers the  $\mu$ Op to the RS. RS is then responsible for tracing the operands and dependencies of the  $\mu$ Op, and delivering the  $\mu$ Op to the relevant execution unit. The execution units are responsible for executing the instruction, e.g., adding two integers, or loading an integer to a register. All execution units operate in parallel unless there is a dependency. Parallel execution enables exploiting instruction-level parallelism, and therefore, executing multiple instructions in one cycle. An out-of-order processor can theoretically execute as many instructions as issued in one cycle. Furthermore, every execution unit has its own private buffer. For example, the Sandy/Ivy Bridge micro-architecture contains a 64-entry load and a 36-entry store buffer, which enables buffering up to 64/36 load/store operations. Buffering allows to overlap the same kinds of  $\mu$ Ops when some are not ready to complete. For example, if a load operation misses from L1D cache, another load operation can start its execution without waiting for the former load operation to finish. Lastly, L1D cache is incorporated to BE and works cooperatively with the load and store execution units to deliver data from/to memory hierarchy to/from processor. The L1D cache of today's processors contains a set of registers for tracking the outstanding cache misses, i.e., miss status handling registers (MSHRs). MSHRs allow processors to continue their execution when there is a cache miss, and further improve parallelism.

## 2.2 Online Transactional Processing

A transaction is an indivisible unit of work that should atomically be executed over a database. A transaction can read or write to the database. The atomic execution implies that either all or none of the actions of the transaction should be executed. Online Transaction Processing

(OLTP) systems are used for consistently maintaining a database across multiple, concurrently executing transactions. OLTP systems are responsible for maintaining the *ACID* features, where *A* stands for *Atomicity*, *C* stands for *Consistency*, *I* stands for *Isolation*, and *D* stands for *Durability*. Below we briefly describe each *ACID* property.

- *Atomicty:* A transaction is an indivisible unit of work. It should either be fully executed, or not executed at all.

- *Consistency:* A transaction should start its execution over a consistent database and finish its execution by leaving the database in another consistent state.

- *Isolation:* Concurrently executing transactions should perform their actions as if each transaction performs its actions alone in the database.

- *Durability:* Transactional modifications should be durable, i.e., should be persisted to a durable medium such as a disk.

Online Transaction Processing (OLTP) systems are composed of four main components: (i) Buffer manager, (ii) lock manager, (iii) log manager, and (iv) access methods. These components are tightly intertwined to be able to satisfy the *ACID* properties and also provide fast access to the database [35]. We briefly describe each component below.

- *Buffer manager:* Traditional OLTP systems keep the data on persistent disk. However, disk access time is orders of magnitude higher than main memory access time. Buffer manager's goal is to keep most frequently used disk pages in main memory to minimize the time needed to access the data.

- *Lock manager:* Traditional OLTP systems use a centralized lock manager. The lock manager is responsible for granting the lock acquire/release requests. It maintains the list of worker threads and acquired/released locks, and manages which transactions should be actively executed or blocked based on the lock acquire/release requests.

- *Log manager:* Log manager is responsible for logging the transactional modifications to the database to be able to satisfy the durability property. In case of a system failure, e.g., a power outage, the system can recover the database to a consistent state thanks to having the transactional modifications logged to a durable medium such as a disk.

- *Access methods:* Access methods are used to access the data fast. An index structure, e.g., a B+tree index, is a commonly used access method in OLTP systems.

### 2.2.1 In-memory Online Transaction Processing

Commodity servers of the last decade follow two fundamental trends: (1) main-memory becoming cheaper and (2) number of cores increasing exponentially. Simply increasing the

buffer pool size and the number of worker threads in the system to exploit the large mainmemory and all the available cores, respectively, lead to marginal gains. Therefore, these two hardware trends have triggered alternative design opportunities for the new generation database systems.

As DRAM prices become cheap enough to buy 1TB main-memory for ~\$30K, today it is possible for most OLTP applications to keep all of their data working set in main-memory while running on a commodity server hardware. This has led to the development of various inmemory or main-memory optimized OLTP systems. These systems either manage all the data in main-memory or make sure that the hot data resides in main-memory. Since they manage to eliminate/minimize the disk I/O for the data page accesses, the overheads associated with managing the buffer pool overweigh its benefits [33]. Therefore, the in-memory OLTP systems omit the buffer pool component even though it is essential for the traditional disk-based database systems as it gives the illusion of an infinite main-memory to the system.

On the other hand, in step with Moore's law, the hardware vendors keep providing more and more opportunities for parallelism. Modern servers tend to have multiple multicore processors in the same machine and allow OLTP systems to handle increasing number of transactional requests in parallel. However, the traditional concurrency control mechanisms that ensure isolation among concurrent transactions using a centralized lock manager and two-phase locking are designed at an era where the server hardware were uniprocessors. Therefore, they do not scale on multicores preventing OLTP systems from exploiting the sheer number of cores available to them [84, 120].

In order to achieve better scalability on multicore architectures, in-memory OLTP systems adopt alternative concurrency control mechanisms. These mechanisms can be broadly grouped into two categories based on whether they partition the data or not. The ones that partition the data choose an extreme form of physical partitioning where there is a data partition for each core and a single worker thread for each partition. Systems like VoltDB [107] (or its ancestor H-Store [104]) and the initial version of HyPer [55] deploy this approach. As a result, they can avoid any form of locking within a partition and need to coordinate worker threads only when a transaction requires data from multiple partitions (i.e., in the case of distributed transactions). On the other hand, the systems that prefer avoiding any kind of data partitioning, like Hekaton [61], SAP HANA [64], or the latest version of HyPer [81], rely on optimistic and multiversion concurrency control [13].

In addition to alternative concurrency control mechanisms, in-memory database systems also deploy cache-conscious index structures. They align the index page sizes to the size of a cache line as opposed to the size of a disk page and/or adopt lock-free index page access mechanisms rather than using traditional page latches [67, 114]. Moreover, the in-memory OLTP systems tend to depend on pre-determined stored procedures instead of ad-hoc queries [55, 61, 107] and apply efficient compilation optimization techniques that optimize the instruction stream for a particular transaction [61, 80]. Finally, the new-age in-memory OLTP systems have

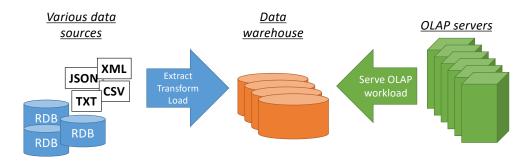

Figure 2.2 – Data Warehouse Architecture (taken from [19]).

codebases that are implemented from scratch. Therefore, they are expected to have a cleaner codebase compared to the traditional disk-based systems where the codebase consists of many branch statements and obsolete code paths due to different release versions spanning several decades of development.

Overall, in-memory OLTP engines deploy lighter storage manager components compared to the traditional disk-based systems aiming to utilize the resources of the modern server hardware in a more effective way.

## 2.3 Online Analytical Processing

OLTP applications were the main driving force for the invention of relational database systems [21, 22]. During late 90s, data warehousing applications have gained a significant attention and led to Online Analytical Processing (OLAP) systems specialized for OLAP workloads. OLAP workloads are composed of read-only, complex, analytical processing queries that aim to extract valuable information out of the data.

Data warehouses are implemented separately from the transactional databases. Transactional databases usually keep the fresh, up-to-date data. However, executing data warehousing applications on a transactional database would result unacceptably high response time due to the additional work that transactional systems require to keep the data consistent, such as locking and logging. As OLAP workloads are read-only, they are fined-tuned on a separate database to provide fast access to the masses of collected data.

Figure 2.2 presents how data warehouses are typically built. Transactional data is collected from various sources and goes through a procedure called Extract, Transform and Load (ETL). At the end of the ETL procedure the data is ready for the data warehousing applications. Data warehousing applications run complex OLAP queries over the data warehouse. The OLAP queries can be executed on Relational OLAP, i.e., *ROLAP* servers, or Multi-dimensional OLAP, i.e., *MOLAP* servers. Both ROLAP and MOLAP servers provide multi-dimensional view of the data, which is useful for data warehousing applications. While ROLAP servers extend traditional relational databases (RDBs) by using an intermediate layer to provide efficient multi-dimensional view of the data, MOLAP servers directly support the multi-dimensional

storage of the data. Both ROLAP and MOLAP servers use materialized views and optimized indices to provide fast access to massive amounts of data [19].

#### 2.3.1 Column-stores

In early 2000s, column-stores have gained a significant attention. Column-stores relied on the observation that most OLAP queries require accessing only a subset of the attributes of the relational tables that the queries process. Hence, column-stores stored the data column-by-column, as opposed to traditional row-by-row storage. Furthermore, column-stores adopted numerous optimizations such as late materialization, predication and vectorization. Researchers have shown that column-stores can provide orders of magnitude faster performance than traditional OLAP servers thanks to their lean storage layout and the adopted optimizations [2, 17, 18]. As a result, column-stores have gained a wide adoption and become standard for OLAP workloads. Most of the major database system vendors today have a column-store offering as a specialized engine embedded in the main database system [60, 89].

### 2.3.2 Query Processing Paradigms

When a query is submitted to a database system, the query optimizer parse the query and produce an optimized query execution plan. The query plan is usually expressed in the form of a tree, where every node represents a particular operator, such as a project, select, or join operator. Query processing engine executes the query plan to produce the desired output. There are three main query processing paradigms that modern database systems use: (i) tuple-at-a-time, (ii) vector-at-a-time, and (iii) compiled query processing.

**Tuple-at-a-time query processing:** In tuple-at-a-time query processing, all query operators use the same abstract class, usually called the Iterator class, that exposes three main methods: open(), next(), and close(). The open() method starts the operator's processing. The next() method fetches the next tuple to process. And, the close() method finalizes the processing of the operator. The open() and close() functions are called once per operator, whereas the next() function is called for every single tuple processed for every operator in the query plan. The tuple-at-a-time query processing paradigm is simple and intuitive as it uses the same abstract class to implement all the query operators. However, it suffers from the high cost of the next() function calls, as the next() function is called once per tuple, which can be of millions. Most early database systems used the tuple-at-a-time query processing paradigm [29].

**Vector-at-a-time query processing:** Vector-at-a-time query processing aims to mitigate the high cost of the next() function calls. To do so, instead of fetching a single tuple per next() function call, vector-at-a-time processing fetches a vector of tuples per next() function call. As a result, it significantly reduces the number of time the next() function is called and hence reduces the high cost of the next() function calls. A vector of tuples is usually an array

of values that is passed from one operator to another. The vector size is a tunable system parameter and is usually in the orders of a few thousands. *VectorWise* has been the pioneering system that follows the vector-at-a-time query processing paradigm, which later on evolved into a commercial system [2, 17].

Compiled query processing: Compiled query processing also aims to mitigate the high cost of the next() function calls of the tuple-at-a-time query processing. It fuses multiple query operators into a single meta-query-operator and makes one function call for processing the whole meta-query-operator. As the query plan, which specifies the query operators that are needed to execute the query, is only know at run-time, compiled query processing relies on run-time code generation. After the query optimizer produces the query plan, the compiled query processing paradigm generates the code that will be run to execute the query and compiles the generated code down into the machine code at run-time. The generated and compiled code is run to execute the query and produce the desired output. *HyPer* has been the pioneering system that follows compiled query processing paradigm, which later on evolved into a commercial system [54, 79].

**Quickstep:** In traditional tuple-at-a-time query processing, the base class is abstract. Hence, the next() function calls are a virtual function calls, which is costlier than regular function calls. A recently proposed system, *Quickstep*, argues that using aggressive function inlining to mitigate the high cost of the next() function calls coupled with using efficient parallelization techniques and several filtering-based optimizations enable delivering a similar level of performance to that of the vector-at-a-time query processing paradigm. We examine how costly the next() function calls and how useful the filtering-based optimizations for *Quickstep* in Chapter 5 in more detail [85].

# 2.4 Hybrid Transactional and Analytical Processing

Traditionally OLAP queries run on the data that is collected from various sources as shown in Figure 2.2. This requires an expensive Extract, Transform, Load (ETL) operation on the transactional data. ETL is an expensive operation, and usually is performed once a day/week. Hence, the OLAP queries run on data that is stale. Recently, there is an increasing demand on running real-time analytical queries on fresh, transactional data. Fraud detection, risk analysis, financial trends tracking applications are examples that demand real-time analytical processing [14, 83].

Real-time analytics applications have led to Hybrid Transactional and Analytical Processing (HTAP) systems. HTAP systems combine OLTP and OLAP systems into a single unified framework to run OLAP queries on fresh OLTP data. Hence, HTAP workloads contain both transactional and analytical requests performed on the same database.

There has been several proposed HTAP architectures. The most popular HTAP architecture is the two-copy, mixed format (TCMF) architecture. TCMF architecture keep two copies of

the data, one for OLTP and one for OLAP component. To keep the data consistent across the OLTP and OLAP components, TCMF architecture uses an intermediate data structure, *delta*, that keeps track of the recently modified, fresh tuples. Periodically, TCMF architecture flushes the delta to the OLAP-side to make the OLAP-copy of the data consistent with the OLTP-copy. The OLTP-copy is usually kept in row format as row-wise storage is more optimized for OLTP, whereas the OLAP-copy is usually kept in columnar format as columnar format is more optimized for OLAP. Microsoft SQL Server [62], Oracle [59], and BatchDB [73] use TCMF architecture.

Another popular architecture is single-copy, mixed-format (SCMF) architecture. SCMF architecture keeps a single copy of the data. Furthermore, it keeps an intermediate data structure called *delta* (similar to the TCMF architecture) to keep the fresh, recently-modified OLTP data. OLTP transactions only modify the delta, whereas OLAP queries read both delta and the main copy of the data. The main copy of the data usually kept in columnar format to largely serving for OLAP workloads, whereas the delta structure keeps the data usually in row format. The architecture trades off OLTP performance for reduced memory consumption thanks to keeping a single copy of the data. SAP HANA [95] and MemSQL [100] follow this type of architecture.

Lastly, single-copy, single-format (SCSF) architecture keeps a single-copy of the data and uses only single format, i.e., only row or columnar, both for OLTP and OLAP workloads. It relies on copy-on-write snapshotting or multi-version concurrency control mechanisms to keep multiple versions of the data, through which analytical queries can access to the fresh-most transactional data. HyPer [81] and Caldera [7, 91] follow this type of architecture.

## 2.5 Profiling A Modern Processor Micro-architecture

Today's processors contain a Performance Monitoring Unit (PMU). PMUs contain a set of registers that the PMU can configure and collect certain types of hardware events such as number of L1 instruction-cache misses. Today's processors feature large number of hardware events. We have observed 422 events on the Ivy Bridge machine that we used in Chapter 3.

VTune is Intel's popular micro-architectural analysis tool that allows accessing the hardware event and defining micro-architectural analysis methodologies. VTune requires the user to identify the set of hardware events that the user is interested in. VTune, then, runs together with the application and collects how many times the identified event has occurs during the application run. Having the application stopped, VTune reports the final numbers for each identified event [44].

Hardware has only a fixed number of registers to collect the event numbers. If the number of events is larger than the number of registers, VTune uses its internal multiplexing algorithm, where VTune collects every event during different periods of the application, and for statistically significant many times. VTune has predefined duration types: very short, short, medium

and long. Having specified the duration type, VTune uses its internally optimized multiplexing algorithm to provide statistically significant times. We have observed that short and medium duration types provide statistically significant results [45].

VTune has a low overhead. It affects the performance of the application, which it concurrently runs with, less than 5% [43].

VTune has several built-in micro-architectural methodologies such as general-exploration that adopts Intel's published Top-down Micro-architecture Analysis Methodology (TMAM) [117] and provides end-to-end execution time breakdown inside the core micro-architecture, or memory-access that provides memory bandwidth consumption values. The built-in analysis methodologies use a set of events and a set of formulas that uses the set of events to produce a meaningful micro-architectural analysis component, such as the amount of time spent for L1 instruction-cache misses. We study VTune's built-in general-exploration in Chapter 3.

# 2.6 Related Work on Micro-architectural Analysis of Data-Intensive Workloads

There is a large body of related work analyzing the micro-architectural behavior of data-intensive workloads. Barrosso et al. [11] investigate the memory system behavior of OLTP and OLAP style workloads both on a real machine and with a full-system simulation. They argue that these two types of workloads would benefit from different architectural designs in terms of the memory system. Ranganathan et al. [90] perform a similar analysis. However, they only focus on the effectiveness of out-of-order execution on SMPs while running these workloads in a simulation environment. On the other hand, Keeton et al. [53] and Stets et al. [103] experiment only with OLTP benchmarks (TPC-B and TPC-C) on real hardware. These studies agree that OLTP workloads utilize the underlying micro-architectural resources very poorly, wasting most of the execution cycles on memory stalls and exhibiting a low IPC value.

Ailamaki et al. [3] examine where the time goes on four commercial database systems using a micro-benchmark to have a fine-grain understanding of the memory system behavior on multiprocessors, whereas Hardavellas et al. [32] analyze TPC-C and TPC-H on both inorder and out-of-order machines in a simulation environment. These studies focus on the implications for the database systems rather than the hardware to achieve better hardware utilization.

More recent workload characterization studies [111] analyze the OLTP benchmark, TPC-E, and show that micro-architecturally TPC-E behaves very similarly to the TPC-B and TPC-C benchmarks. Ferdman et al. [28] present micro-architectural analysis of a suite of cloud workloads, by concluding that there is a fundamental mismatch among what today's server processors provide and what the cloud workloads demand. These studies corroborate the findings of the previous studies in terms of the inefficient use of the memory hierarchy when

running OLTP. They highlight that the L1-I stalls are the dominant factor in the overall stall time followed by the long-latency data misses.

Yasin et al. [117] introduce Top-Down Micro-architecture Analysis Methodology (TMAM) deployed by Intel VTune as general-exploration. Yasin et al. [118] examine Naive Bayes algorithm and its hardware behavior in an Hadoop execution environment. The study shows that software stack, such as the used JVM, and application code efficiency has a significant impact on the overall performance. Kanev et al. [50] examine collective of machines in a Google datacenter running collective of Google datacenter applications. The study shows that the datacenter workload collection spends most of the time waiting for dependent data-cache accesses due to the data-intensive nature of the datacenter workloads. Beamer et al. [12] presents a graph workload analysis and highlights that graph workloads severely under-utilize the memory bandwidth. Sridharan and Patel [102] examine the evaluation of workloads on the popular data analysis language R, over a commodity processor. Awan et al. [9, 10] present a micro-architectural analysis of Spark.

Harizopoulos et al. [33] demonstrate that traditional OLTP systems spend more than half of their execution time inside the buffer pool, latching, locking, and logging components. On the other hand, Wenisch et al. [116] and Tozun et. al [108] tie the micro-architectural behavior of the disk-based OLTP into specific code modules by presenting the breakdown of the cache misses into specific code parts of the traditional OLTP software stack at different code granularities.

Kersten et al. [56] examine vectorized and compiled OLAP engines without getting deep into the micro-architectural behavior. Sompolski et al. [101] present a comparison between vectorized and compiled engines in terms of particular optimizations, such as predication and SIMD.

Despite the large body of existing work on the micro-architectural analysis of data-intensive workloads, the existing work falls short on evaluation the micro-architectural behavior of state-of-the-art database workloads that are composed of different categories of workloads, such as OLTP, OLAP and HTAP, and different generations of machines, such as traditional, well-established systems, ground-up designed, new-generation systems, and academic prototypes. This thesis aims to fill the gap for the micro-architectural analysis of state-of-the-art database workloads by considering each category of the database workloads running on different generations of database systems, separately.

# 3 Micro-architectural Analysis Methodologies

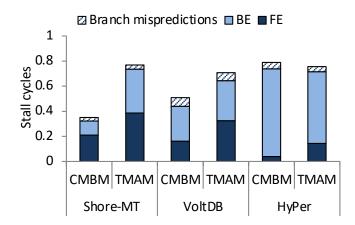

Today's out-of-order processors provide a rich set of hardware events for micro-architectural analyses. However, database workload characterization studies usually use a simple cachemiss-based micro-architectural analysis methodology (CMBM), which uses only a simple set of events that count the number of cache misses. Intel has recently announced Top-down Micro-architecture Analysis Method (TMAM). TMAM provides instruction-issue-slot-level breakdown by using new hardware events. Hence, it is able to account for an end-to-end execution time breakdown.

In this chapter, we compare the conventional CMBM with TMAM. Our goal is to see whether CMBM is successful enough to account for end-to-end execution time breakdown. The results show that CMBM is inadequate to account for the end-to-end execution time breakdown. CMBM under/over-estimates the number of stall cycles due to not accounting for all types of stalls and/or not being able to account for the overlapping capability that today's out-of-order processors have.

### 3.1 Introduction

Modern processors provide a performance monitoring unit (PMU) exposing hundreds of hardware events to examine the hardware-software interaction. The hardware events can be used to understand how efficiently a workload uses the processor resources [28]. On the other hand, modern processors are aggressively optimized for speed featuring wide-issue, out-of-order execution engines, deep cache hierarchies, deep pipeline stages and large pipeline buffers. While these features allow processors to exploit instruction- and memory-level parallelism, the increasing complexity of the micro-architecture makes the micro-architectural analysis harder.

Intel has recently announced its Top-down Micro-architecture Analysis Methodology (TMAM) proposing a hierarchical CPU cycles breakdown based on a set of new performance events [117]. TMAM examines every instruction issue slot independently. Hence, it provides an

accurate slot-level breakdown. Although TMAM is an ambitious methodology, it has not been adopted by the studies characterizing the micro-architectural behavior database workloads. The database workload characterization studies usually use a cache-miss-based methodology (CMBM) [98]. While it is conventional knowledge that database workloads spend most of their time in cache misses, it is not clear whether this assumption still holds, and if not what the other reasons for the stalls are when running database workloads.

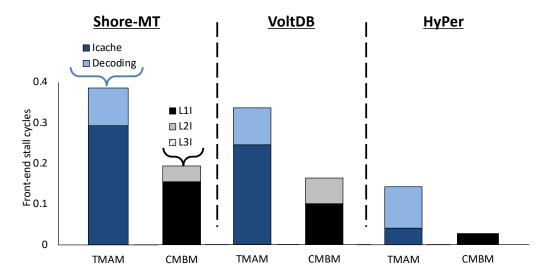

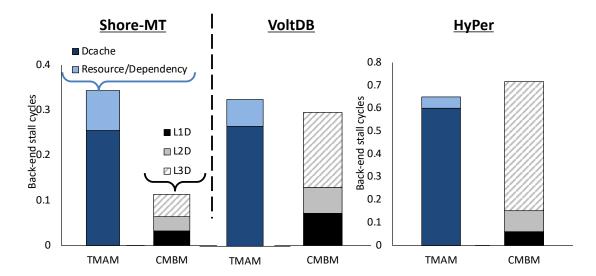

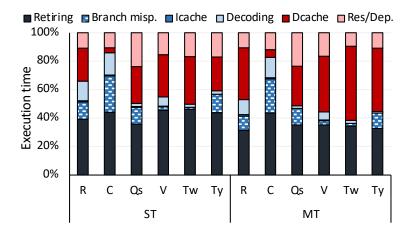

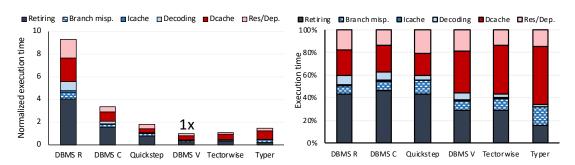

In this chapter, we compare CMBM with TMAM for Online Transaction Processing (OLTP) workloads. We use one traditional disk-based system, *Shore-MT* [93], and two in-memory systems, *VoltDB* [115] and *HyPer* [39], running the standard TPC-C benchmark. Our goal is to estimate how well CMBM represents the micro-architectural behavior on today's aggressive out-of-order processors compared to TMAM. This chapter shows that:

- CMBM under-estimates stalls at the front-end due to: (i) not being able to account for the true penalty of instruction starvation, and (ii) not being able to account for instruction decoding stalls.

- CMBM under-estimates the back-end stalls for the disk-based system due to not being able to account for L1 hit stalls that cover the stalls due to complex micro-architectural features such as load-store forwarding and 4K aliasing. CMBM slightly over-estimates the back-end stalls for the in-memory systems due to not being able to account for the overlapping capability of today's out-of-order processors.

The rest of the chapter is organized as follows. Section 3.2 describes the micro-architectural analysis methodologies we examine. While Section 3.3 presents the experimental setup and methodology, Section 3.4 compares the analysis methodologies we discuss. Finally, Section 3.5 concludes.

# 3.2 Micro-architectural Analysis Methodologies

In this section, we explain the two methodologies we compare: CMBM and TMAM. We firstly cover how to estimate the fraction of the time spent for retiring instruction without any stalls, i.e., *Retiring* cycles. Retiring cycles is part of TMAM, but not part of CMBM. Hence, we cover it separately in the first section below. We, then, explain in detail how CMBM and TMAM estimates the stalls.

### 3.2.1 Retiring

In this section, we describe the *Retiring* time component. Retiring time represents the fraction of the time that CPU spends retiring instructions without any stalls.

Retiring time is found based on the hardware events that count the number of retired  $\mu$ Ops

and that count the number of clock cycles. The used formula for Retiring time is as follows.

$$Retiring = \frac{NumberOfRetired\mu Ops}{IssueWidth \times NumberOfClockCycles}$$

The number retired  $\mu$ Ops is divided by the multiplication of the issue width and the number of clock cycles. This is because the out-of-order processors can retire up to issue-width many  $\mu$ Ops in one cycle. As a result, the Retiring time component describes how many number of  $\mu$ Ops are retired, out of the maximum possible number of retired  $\mu$ Ops given a certain number of clock cycles.

## 3.2.2 Cache-Miss-Based Methodology

| Component             |     | Description                         |  |  |

|-----------------------|-----|-------------------------------------|--|--|

| F                     | Е   | Stalls at front-end                 |  |  |

| L1I                   |     | Stalls due to L1I misses            |  |  |

|                       | L2I | Stalls due to L2I misses            |  |  |

|                       | L3I | Stalls due to L3I misses            |  |  |

| В                     | E   | Stalls at back-end                  |  |  |

|                       | L1D | Stalls due to L1D misses            |  |  |

|                       | L2D | Stalls due to L2D misses            |  |  |

|                       | L3D | Stalls due to L3D misses            |  |  |

| Branch mispredictions |     | Stalls due to branch mispredictions |  |  |

Table 3.1 – Stall cycles breakdown for CMBM for a three-level of cache hierarchy.

This section covers the cache-miss-based methodology (CMBM). Table 3.1 presents stall cycles breakdown for CMBM. CMBM decomposes stall cycles into three main components: front-end (FE) stalls, back-end (BE) stalls and stalls due to the branch mispredictions. It approximates FE stalls by the sum of L1, L2 and L3 instruction (L1I, L2I, L3I) cache miss stalls. It approximates BE stalls by the sum of L1, L2 and L3 data (L1D, L2D, L3D) cache miss stalls<sup>1</sup>. CMBM uses the conventional hardware events that count the number of instruction-/data-cache misses for every level of caches<sup>2</sup>. CMBM uses an estimated cache miss penalty for every level of caches, and multiplies the number of misses with the estimated penalty to obtain how many cycles the processor would stall due to the cache misses for each level of caches. The cache miss penalties are usually available at the optimization reference manual of the profiled processor. For example, Intel's cache miss penalties can be found in page 2-24 and B-42 of [42]. CMBM assumes L1I and L1D hits do not cause any stalls.

Lastly, CMBM estimates branch misprediction stalls based on the conventional hardware

<sup>&</sup>lt;sup>1</sup>Based on a three level of cache hierarchy.

<sup>&</sup>lt;sup>2</sup>Note that only L1 cache is split for instruction and data, whereas L2 and L3 caches are unified. However, Intel provides performance events counting the instruction and data misses separately for all the three levels of caches.

| Con                  | nponent             |              | Description                                      |

|----------------------|---------------------|--------------|--------------------------------------------------|

| FE                   | FE                  |              | Stalls at front-end                              |

|                      | Icache              |              | Stalls due to instruction fetch starvation       |

|                      | Decoding            |              | Stalls due to inefficiencies at FE units such as |

|                      | Decouning           |              | decoder and $\mu$ Op cache                       |

| BE                   |                     |              | Stalls at back-end                               |

|                      | Dcache              |              | Stalls due to memory accesses                    |

|                      |                     | L1           | Stalls due to L1D hits                           |

|                      |                     | L2           | Stalls due to L1D misses w/ L2 hit               |

|                      |                     | L3           | Stalls due to L2D misses w/ L3 hit               |

|                      |                     | DRAM         | Stalls due to L3D misses                         |

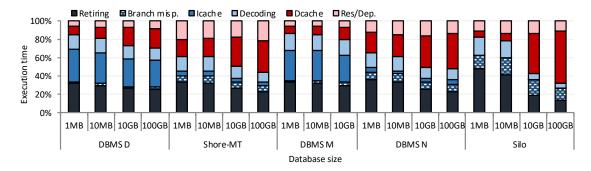

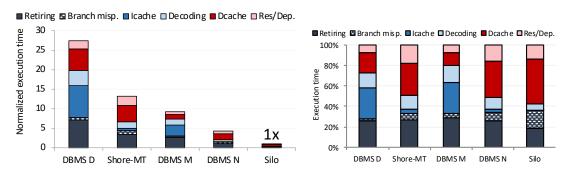

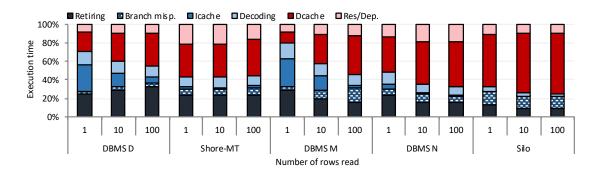

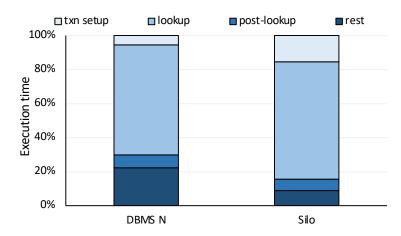

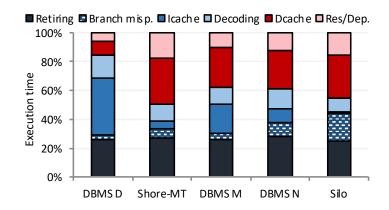

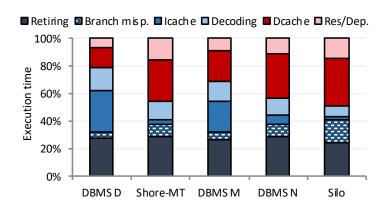

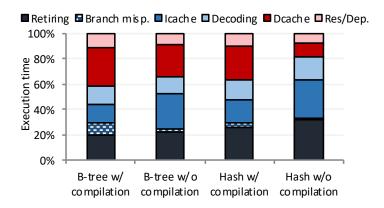

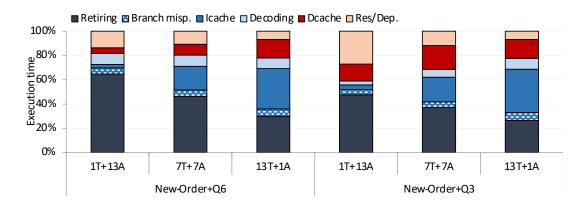

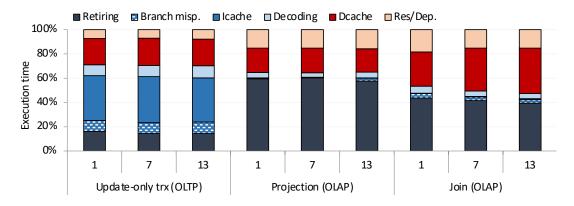

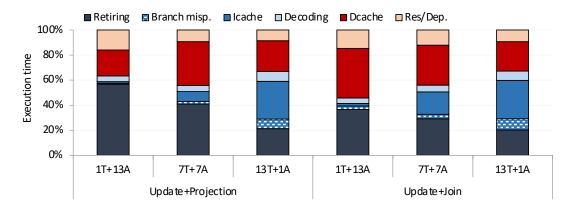

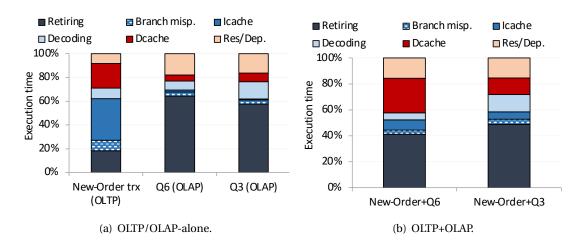

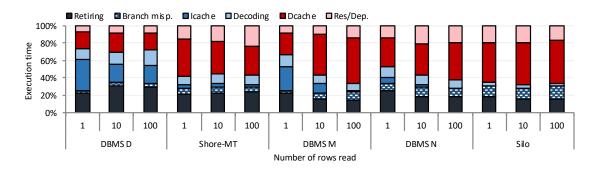

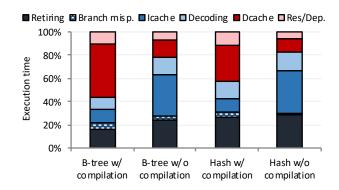

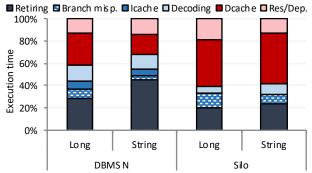

|                      |                     | Store Buffer | Stalls due to store buffer overflow              |