### Characterization and Modeling of Total Ionizing Dose Effects on Nanoscale MOSFETs for Particle Physics Experiments

Présentée le 30 avril 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de circuits intégrés Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### **Chunmin ZHANG**

Acceptée sur proposition du jury

Prof. M. A. Ionescu, président du jury

Prof. C. Enz, directeur de thèse

Prof. D. Fleetwood, rapporteur

Dr N. Collaert, rapporteuse

Dr J.-M. Sallese, rapporteur

Nothing in life is to be feared, it is only to be understood.

Now is the time to understand more, so that we may fear less.

— Marie Curie

To my family, for their unbounded love and unwavering support

## Acknowledgements

Pursuing a PhD has been one of the most fulfilling journeys in my life. It has been my privilege to enjoy this journey and achieve this dissertation on a wonderful platform. Over the past few years, I have gained so much from my supervisor, collaborators, jury members, colleagues, friends, and families. I wish I could deliver my genuine gratitude to each person who has helped me.

First, I would like to thank my thesis director, Prof. Christian Enz, for his constant support and helpful guidance. He has not only transferred a lot of knowledge about device modeling to me but also encouraged me to be methodical and rigorous in my work. It has been his advice and encouragement that guide me through many challenges and promote me to reach the highest goals. My sincere gratitude is extended to Dr. Claudio Bruschini for his first email about the GigaradMOST project, Dr. Farzan Jazaeri for those illuminating discussions from the technical perspective, Dr. Alessandro Pezzotta for his inspiration about practical skills for scientific research, and all of them for their daily support during a certain period.

Then, I would like to thank our collaborators from CERN, University of Padova, and University of Milano-Bicocca for the fruitful collaboration. I am particularly grateful to Dr. Federico Faccio, Dr. Giulio Borghello, Henri Koch, and Sebastiano Costanzo for sparing no effort to support my experiments, sharing their knowledge in interesting analysis, and integrating me in their social life during my stay at CERN. I have deeply exploited the radiation world with their insights and greatly enjoyed the working experience with them.

My sincere thanks also go to Prof. Mihai Adrian Ionescu, Dr. Nadine Collaert, Prof. Daniel Fleetwood, and Dr. Jean-Michel Sallese for being part of my PhD jury, taking time to read my thesis, and evaluating my PhD work carefully. They have shared many valuable ideas and constructive comments about how to improve my thesis.

Now, I would like to thank Lysiane Bourquin, Sandrine Piffaretti, and Lucie Auberson for their administrative help and encouraging words along my PhD journey. I would also like to thank my mentor, Prof. Herbert Shea, for always listening to me patiently, understanding my problem precisely, and providing me with helpful suggestions. It would have been impossible for me to reach the destination without their support.

I would like to express my sincere appreciation to my current and former colleagues from

#### Acknowledgements

ICLAB, including Andrea Kraxner, Antonino Caizzone, Antonio D'Amico, Anurag Mangla, Arnout Beckers, Assim Boukhayma, Daniel Bold, Francesco Chicco, Huaiqi Huang, Hung-Chi Han, Jérémy Schlachter, Maria-Anna Chalkiadaki, Marta Franceschi, Mattia Cacciotti, Minhao Yang, Raffaele Capoccia, Raghavasimhan Thirunarayanan, Sammy Cerida, Tijmen Spreij, Vincent Camus, and Vladmir Kopta, for making my working time pleasant and those past few years memorable, and especially to those with whom we end up being real friends and enjoying life outside the lab. In particular, I would like to thank Vincent Camus for kindly accepting to translate the abstract of my thesis into French.

Next, I would like to deliver my great thanks to all my good friends for bringing me happiness and strength. There are so many of them, being not only my good friends but also my earnest teachers, that I cannot name one by one and thank enough. I give my special thanks to Anne-Catherine Pauchard and Jean-Daniel Pauchard for warmly including me in their local life and becoming my supportive friends in the beginning of my PhD. I also give my special thanks to Manon Garzuel and Julie Dréon for their family-like help in my daily life and their significant support during my thesis writing. I am also grateful to my amazing friend, Wei Wang, for always providing me with a different perspective on any matter.

Finally, I would like to convey my deep gratitude to my parents, Xiaoxia Wei and Yanfa Zhang, and my sisters, Min Zhang and Panpan Zhang. My parents have always showered me with their unlimited love and unconditional support. My sisters' presence is a corner stone of my life wherever I travel in the world. Last but not least, I would like to thank my boyfriend and my soulmate, Hao Yu, for standing by me on all occasions, holding my hands through adventures, and filling my life with his love. Moved by his pure attitude towards the world, I have picked up those valuable philosophies not only in research but also in life. I love you all and thank you deeply (我爱你们,并深深地感谢你们)!

Neuchâtel; April 11, 2021

Chunmin Zhang

### **Abstract**

Total ionizing radiation compromises electrical characteristics of microelectronic devices and even causes functional failures of integrated circuits. It has been identified as a potential threat to electronic components, especially those in high-energy physics experiments, space and avionic systems, and nuclear power plants. Among all harsh radiation environments, the future High Luminosity Large Hadron Collider (HL-LHC) at European Organization for Nuclear Research (CERN), is expected to have by far the highest levels of total ionizing dose (TID) with a peak of 1 Grad(SiO<sub>2</sub>) in the innermost electronics. Also, the number of pileup events per bunch crossing can reach up to 200, challenging trigger and data acquisition systems of its particle experiments. To reach long-term reliable operation, the HL-LHC will require innovative detecting and tracking systems with a higher level of granularity and bandwidth as well as robust radiation-tolerant front-end electronics.

Complementary metal-oxide-semiconductor (CMOS) scaling allows extended circuit functionality and enhanced computing power. It also improves the TID tolerance of MOS field-effect transistors (MOSFETs) with relieved charge trapping related to ultrascaled gate dielectrics. To evaluate the potential use of highly scaled devices in the HL-LHC and eventually support circuit design for radiation-tolerant applications, this thesis characterizes and models the effects of TID up to 1  $Grad(SiO_2)$  on a commercial 28-nm bulk CMOS process. The characterization part focuses on evaluating measurable radiation effects and identifying dominant physical mechanisms. The modeling part aims at improving the understanding of the observed radiation effects and developing a design-oriented compact model for comprehensively accounting for them.

Under various bias and temperature conditions, devices are irradiated, annealed, and tested after each irradiation and annealing step. Most of them demonstrate slight parametric shifts, confirming the very high TID tolerance of ultrathin gate dielectrics. TID-induced degradation in this technology primarily depends on charge trapping related to thick shallow trench isolation (STI) oxides. STI-trapped positive charges in *n*MOSFETs open parasitic channels along STI sidewalls and cause a significant increase in the drain leakage current, which however almost disappears after high-temperature annealing. STI-related charge trapping can even be strong enough to influence the central part of a narrow channel and is seen seriously degrading the performance of narrow-channel MOSFETs, which however can be relieved by shortening the channel.

#### **Abstract**

The TID-induced parasitic leakage current of *n*MOSFETs is modeled via a gateless charge-controlled transistor. To model the effects of TID on inversion operation, a generalized Enz-Krummenacher-Vittoz (EKV) charge-based MOSFET model is developed through the incorporation of radiation-induced trapped charges into the original EKV MOSFET model. Despite a small number of parameters, this model demonstrates an excellent match with measurement results over a wide range of device operation. The effects of TID on MOSFET characteristics are efficiently described by those few model parameters. This newly-developed radiation-aware EKV MOSFET model also demonstrates a width dependence of TID effects on 28-nm bulk MOSFETs, which can be explored for the model extension to a broad range of device dimensions even for a continuous range of TID levels.

### **Keywords**

Charge trapping, compact modeling, EKV charge-based MOSFET model, gate oxide, HL-LHC, interface-trapped charges, nanoscale bulk CMOS, 1 Grad(SiO<sub>2</sub>), oxide-trapped charges, parameter extraction, parasitic drain-to-source leakage current, radiation effects, radiation-induced narrow-channel effects, RINCE, radiation-induced short-channel effects, RISCE, shallow trench isolation, STI, total ionizing dose, TID.

### Résumé

Les rayonnements ionisants compromettent les caractéristiques électriques des composants micro-électroniques et peuvent provoquer des dysfonctionnements des circuits intégrés. Ils ont été identifiés comme une menace pour les composants électroniques, en particulier dans les domaines de la physique des hautes énergies, l'aérospatial, et les centrales nucléaires. Parmi les environnements sujets à de sévères rayonnements, l'électronique du Grand Collisionneur de Hadrons à Haute Luminosité (HL-LHC de l'anglais High Luminosity Large Hadron Collider), qui sera prochainement mis en place par le CERN (Conseil Européen pour la Recherche Nucléaire), devra faire face aux niveaux les plus élevés de radiations, avec une dose ionisante cumulée (TID de l'anglais Total Ionizing Dose) de l'ordre de 1 Grad(SiO<sub>2</sub>). Egalement, il pourra y avoir jusqu'à 200 évènements par collision, ce qui rendra très difficile le déclenchement et l'acquisition des données lors d'expérimentations. Pour atteindre un fonctionnement fiable à long terme, le HL-LHC nécessitera donc des détecteurs innovants dotés d'une granularité et d'une bande passante plus élevées, ainsi que des systèmes électroniques robustes et résistants aux rayonnements.

La réduction de la taille des technologies "complementary metal-oxide-semiconductor" (CMOS) permet d'augmenter l'efficacité et la puissance de calcul des circuits intégrés. Elle s'accompagne aussi d'une amélioration de la résistance des transistors à effet de champ à grille métal-oxyde (MOSFET de l'anglais Metal-oxide-semiconductor Field-effect Transistor) grâce à une diminution des charges piégées dans un diélectrique de grille de plus en plus fin. Afin d'évaluer le potentiel d'utilisation de technologies plus récentes dans le HL-LHC ainsi que d'aider la conception de circuits pour des applications soumises à de hauts rayonnements, la présente thèse caractérise et modélise les effets du TID jusqu'à 1 Grad(SiO<sub>2</sub>) sur une technologie CMOS 28 nm bulk. La première partie de ce travail se concentre sur la caractérisation des effets des rayonnements ionisants et l'identification de leurs principaux mécanismes physiques. La deuxième partie vise à améliorer la compréhension des effets des rayonnements observés au travers du développement d'un modèle compact décrivant de manière exhaustive les effets des TID et pouvant être utilisé pour la conception de circuits intégrés.

De multiples composants intégrés ont été irradiés, recuits, et testés après chaque étape d'irradiation et de recuit sous différentes températures et tensions de polarisation. La plupart d'entre eux ne montrent que de légères variations de leurs paramètres principaux, confirmant la haute tolérance aux rayonnements des diélectriques de grille ultra-minces. Pour cette tech-

#### Résumé

nologie CMOS 28 nm bulk, la dégradation induite par les rayonnements ionisants dépend principalement du piégeage de charges lié à l'épaisseur des oxydes d'isolation "shallow trench" (STI). Les charges positives piégées dans les oxydes STI des transistors MOSFET à canal n induisent un courant de fuite parasite le long des flancs du STI. Ceci conduit à une augmentation du courant de fuite du drain qui disparaît néanmoins après un recuit à haute température. La charge piégée peut être suffisamment grande pour influencer la partie centrale des canaux étroits et sérieusement dégrader le comportement des transistors MOSFET à canaux étroits, anomalie qui se résout en raccourcissant le canal.

Le courant de fuite parasite des transistors MOSFET à canal n a été modélisé par un transistor sans grille mais à contrôle par la charge. Pour modéliser les effets des rayonnements en situation d'inversion, un modèle du transistor MOSFET généralisé s'appuyant sur le modèle Enz-Krummenacher-Vittoz (EKV) a été développé, en injectant dans le modèle EKV original des charges piégées dans l'oxyde et dans l'interface du transistor MOSFET. Ce modèle montre une excellente capacité à prédire avec précision les résultats mesurés sur une large zone d'inversion malgré un nombre de paramètres très réduits. Ces derniers permettent une reproduction fidèle des effets des rayonnements sur les caractéristiques des composants intégrés. Ce nouveau modèle incorporant l'effet des rayonnements ionisants démontre aussi leur relation à la largeur du composant sur cette technologie CMOS 28 nm bulk. Enfin, ce modèle peut être généralisé à une large gamme de dimensions de composants et de niveaux de radiation.

### Mots clés

Charges piégées, modélisation compacte, un modèle du transistor MOSFET s'appuyant sur le modèle EKV, oxyde de grille, HL-LHC, charges piégées dans l'interface, CMOS en masse à l'échelle nanométrique, 1 Grad(SiO<sub>2</sub>), charges piégées dans l'oxyde, extraction de paramètres, courant de fuite parasite drain-source, effets des radiations, effets de canal étroit induits par les rayonnements, RINCE, effets de canal court induits par les rayonnements, RISCE, isolation de tranchée peu profonde, STI, dose ionisante totale, TID.

## 摘要

总剂量电离辐射会引起微电子器件电学性能退化,甚至导致集成电路功能失效。特别是在高能物理实验、航空航天系统、以及核电站等领域,总电离辐射已被视作电子元器件可靠性的潜在威胁。在所有苛刻的辐射环境中,欧洲核子中心(European Organization for Nuclear Research,CERN)未来的高亮度大型强子对撞机(High Luminosity Large Hadron Collider,HL-LHC)预计将具有最高的总电离辐射剂量—最中心的电子设备将面临高达1 Grad(SiO<sub>2</sub>)的总剂量电离辐射。而且,每个交叉束要采样的事例数目可高达200个,这将使得粒子实验触发装置和数据采集系统的设计极具挑战性。为了确保系统长期可靠运转,HL-LHC的新型探测和追踪系统将需要具有更高粒度和带宽并有抗超高总剂量电离辐射能力的前端电子系统。

互补金属氧化物半导体(Complementary Metal-oxide-semiconductor,CMOS)工艺的持续发展拓展了集成电路的功能并加强了微电子系统的计算能力。而且,栅极电介质层的极度减薄可缓解相关的电荷俘获,进而改善金属氧化物半导体场效应管(Metal-oxide-semiconductor Field-effect Transistor,MOSFET)的抗总剂量电离辐射性能。为了评估先进CMOS工艺下微电子元器件在HL-LHC中的应用前景并最终支持抗辐射应用相关的电路设计,本论文对商用28纳米体硅CMOS工艺进行了高达1 Grad(SiO<sub>2</sub>)的超高总剂量电离辐射效应的表征和建模研究。本论文的表征部分集中于可测量辐射效应的评估以及主要物理机制的识别。本论文的建模部分旨在完善对观察到的实验现象的理解,并且开发一个全面考虑总剂量电离辐射效应的面向设计的紧凑模型。

这部分工作在不同偏置和温度下对器件进行了辐照和退火,并在辐照和退火的每个步骤前后对器件进行了电学测试。实验结果表明,大多数MOS管的参数在辐射后呈现轻微变化,证实了超薄栅极电介质层的较强抗总剂量电离辐射的能力。28纳米体硅CMOS工艺下总剂量电离辐射造成的退化主要取决于较厚浅槽隔离(Shallow Trench Isolation,STI)氧化层相关的电荷俘获。在N型MOS管中,STI俘获的正电荷会开启沿着STI侧墙的寄生沟道,导致漏端泄漏电流明显增加,但此漏端泄漏电流增加在高温退火后基本消失。STI相关的电荷俘获甚至也会影响窄沟道器件的沟道中央部分,严重影响窄沟道MOS管的性能,但此严重影响可通过降低沟道长度来缓解。

总剂量电离辐射在N型MOS管中引起的寄生泄漏电流通过由电荷控制的无栅器件进行模拟。为了模拟总剂量电离辐射对器件反型区的影响,辐射导致的俘获电荷被引入原始的基于电荷的Enz-Krummenacher-Vittoz (EKV) MOSFET模型,最终得到一个广义的EKV MOSFET模型。尽管模型中参数数量较少,这个模型还是在器件工作的很大范围内与测试结果匹配良好。少数几个模型参数有效描述了总剂量电离辐射对MOS管特性的影响。

该基于辐射的最新EKV MOSFET模型还证明了总剂量电离辐射效应在28纳米体硅CMOS工艺中的器件沟道宽度相关性。此沟道宽度相关性可进而用于将该模型推广适用于更广泛的器件尺寸范围,甚至适用于连续的辐射总剂量。

### 关键字

电荷俘获,紧凑建模,基于电荷的EKV MOSFET模型,栅氧化层,HL-LHC,界面俘获电荷,纳米级体硅CMOS,1 Grad(SiO<sub>2</sub>),氧化层俘获电荷,参数提取,寄生漏-源泄漏电流,辐射效应,辐射引起的窄沟道效应,RINCE,辐射引起的短沟道效应,RISCE,浅槽隔离,STI,总剂量电离辐射,TID。

## **Contents**

| Ac  | know    | ledgen   | nents                                                    | j           |

|-----|---------|----------|----------------------------------------------------------|-------------|

| Ab  | ostrac  | t (Engli | ish/French/Chinese)                                      | <b>ii</b> i |

| Li  | st of f | igures   |                                                          | xii         |

| Lis | st of t | ables    |                                                          | XX          |

| Lis | st of s | ymbols   |                                                          | xxii        |

| Lis | st of a | bbrevia  | ations                                                   | xxvi        |

| 1   | Intr    | oductio  | on                                                       | 1           |

|     | 1.1     | Backg    | round and motivation                                     | 1           |

|     | 1.2     | State    | of the art                                               | 5           |

|     |         | 1.2.1    | Overview of radiation effects on solid-state electronics | 5           |

|     |         | 1.2.2    | Overview of TID effects on nanoscale MOSFETs             | 8           |

|     |         | 1.2.3    | Modeling of TID effects on nanoscale MOSFETs             | 10          |

|     | 1.3     | Goals    | and approach                                             | 14          |

| 2   | Basi    | c mech   | nanisms of TID effects on MOS devices                    | 17          |

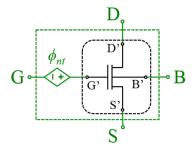

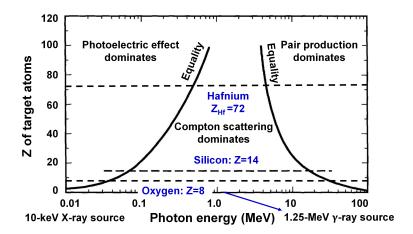

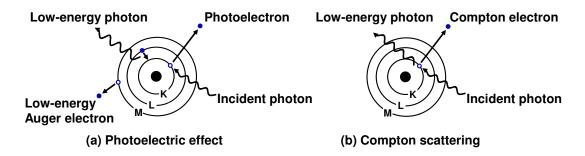

|     | 2.1     | Photo    | on interactions with solid targets                       | 17          |

|     | 2.2     | Basic    | physical processes of TID effects on MOS structures      | 20          |

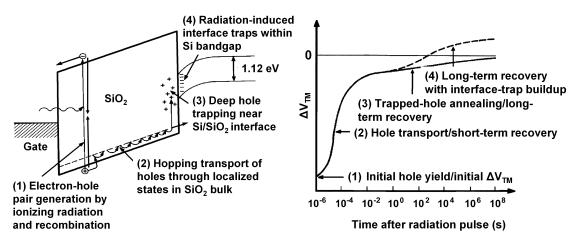

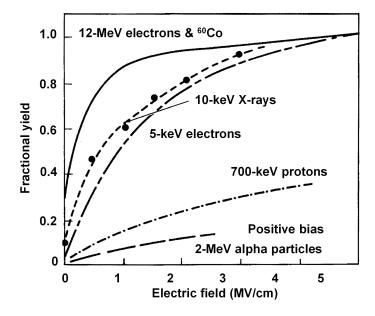

|     |         | 2.2.1    | Electron-hole pair generation and recombination          | 21          |

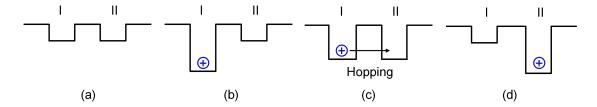

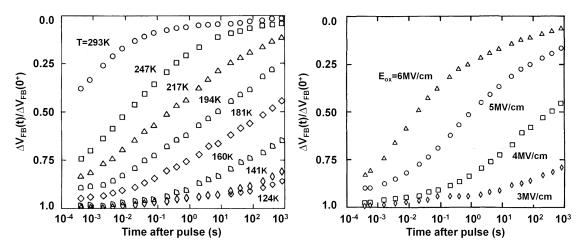

|     |         | 2.2.2    | Hole transport in the oxide bulk                         | 22          |

|     |         | 2.2.3    | Deep hole trapping and annealing                         | 24          |

|     |         | 2.2.4    | Interface-trap formation                                 | 28          |

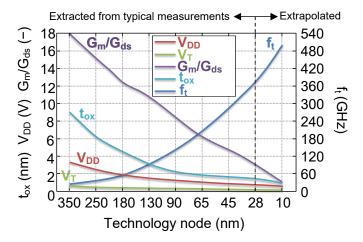

|     | 2.3     | TID ef   | ffects versus CMOS scaling                               | 31          |

|     |         | 2.3.1    | Gate-oxide-related TID effects                           | 32          |

|     |         | 2.3.2    | STI-related TID effects                                  | 33          |

|     |         | 2.3.3    | Spacer-related TID effects                               | 36          |

|     | 2.4     | Sumn     | nary                                                     | 39          |

| 3   | Exp     | erimen   | tal details and results                                  | 41          |

|     | 3.1     | Exper    | imental details                                          | 41          |

### **Contents**

|   |      | 3.1.1   | Test structures                                       | 42  |

|---|------|---------|-------------------------------------------------------|-----|

|   |      | 3.1.2   | Experimental setup                                    | 43  |

|   |      | 3.1.3   | Measurement protocol                                  | 45  |

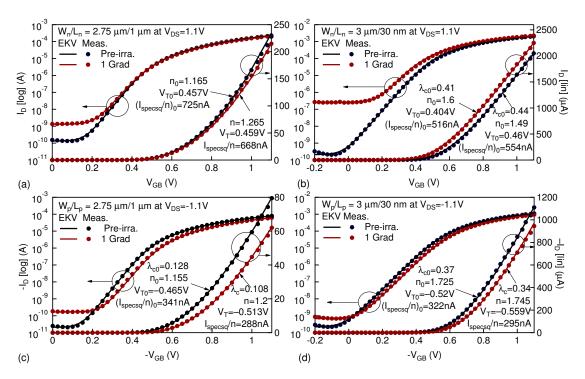

|   | 3.2  | Overvi  | iew of TID effects on 28-nm bulk MOSFETs              | 46  |

|   |      | 3.2.1   | TID effects on transfer characteristics               | 48  |

|   |      | 3.2.2   | TID effects on device parameters                      | 51  |

|   |      | 3.2.3   | Post-irradiation annealing effects                    | 59  |

|   |      | 3.2.4   | Bias dependence of TID effects                        | 60  |

|   |      | 3.2.5   | Temperature dependence of TID effects                 | 65  |

|   | 3.3  | Main e  | experimental phenomena                                | 66  |

|   |      | 3.3.1   | TID-induced drain leakage current                     | 66  |

|   |      | 3.3.2   | Geometry dependence of TID effects                    | 68  |

|   | 3.4  | Summ    | ary                                                   | 73  |

| 4 | Inve | •       | on of TID effects on design parameters                | 77  |

|   | 4.1  | Investi | igation of TID effects on inversion operation         | 77  |

|   |      | 4.1.1   | The simplified EKV MOSFET model                       | 78  |

|   |      | 4.1.2   | Parameter extraction                                  | 84  |

|   |      | 4.1.3   | TID effects on large-signal characteristics           | 86  |

|   |      | 4.1.4   | TID effects on small-signal characteristics           | 89  |

|   | 4.2  | Investi | igation of TID-induced mobility degradation           | 92  |

|   |      | 4.2.1   | Y-function-based mobility extraction                  | 93  |

|   |      | 4.2.2   | TID effects on effective channel mobility             | 95  |

|   | 4.3  | Investi | igation of TID effects on drain leakage current       | 97  |

|   |      | 4.3.1   | Experimental analysis                                 | 97  |

|   |      | 4.3.2   | Semi-empirical modeling of drain leakage current      |     |

|   |      | 4.3.3   | Modeling of a gateless charge-controlled device       | 105 |

|   | 4.4  | Summ    | ary                                                   | 111 |

| 5 | Cha  | rge-bas | ed physical modeling of TID effects                   | 113 |

|   | 5.1  | -       | eralized EKV MOSFET model including traps             |     |

|   |      | 5.1.1   | Incorporation of oxide- and interface-trapped charges |     |

|   |      | 5.1.2   | Inversion charge linearization                        | 118 |

|   |      | 5.1.3   | Revised EKV MOSFET model equations                    |     |

|   |      | 5.1.4   | Model validation with wide-channel MOSFETs            | 130 |

|   |      | 5.1.5   | Main observations about model parameters              |     |

|   | 5.2  | Design  | n-oriented compact modeling of TID effects            | 139 |

|   |      | 5.2.1   | A radiation-aware design-oriented compact model       |     |

|   |      | 5.2.2   | TID effects on large-signal characteristics           |     |

|   |      | 5.2.3   | TID effects on small-signal characteristics           | 142 |

|   | 5.3  | Scalab  | ility of the radiation-aware MOSFET model             | 144 |

|   | 5.4  | Summ    | arv                                                   | 147 |

|     |                |          | Conte                                 | ents |

|-----|----------------|----------|---------------------------------------|------|

| 6   | Con            | clusion  | ns and perspectives                   | 149  |

|     | 6.1            | Concl    | lusions of this work                  | 149  |

|     |                | 6.1.1    | TID tolerance of 28-nm bulk MOSFETs   | 150  |

|     |                | 6.1.2    | Physics-based modeling of TID effects | 150  |

|     |                | 6.1.3    | General remarks                       | 152  |

|     | 6.2            | Sugge    | estions for future work               | 153  |

| Bi  | Bibliography 1 |          |                                       | 155  |

| Lis | st of p        | oublicat | tions                                 | 175  |

| Cu  | ırricu         | ılum vit | tae                                   | 177  |

# List of figures

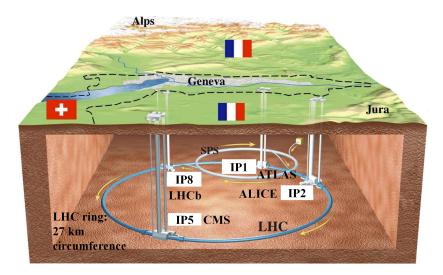

| 1.1  | Schematic layout of the Large Hadron Collider (LHC) with the particle injector             |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | and four main particle detectors                                                           | 1   |

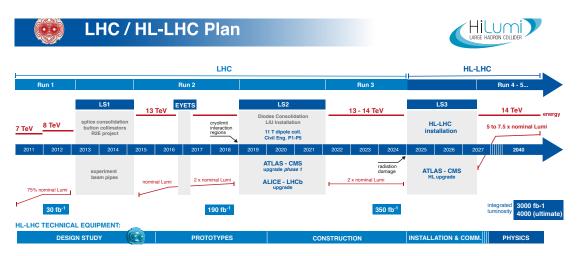

| 1.2  | Upgrade plan from the LHC to the High Luminosity LHC (HL-LHC)                              | 2   |

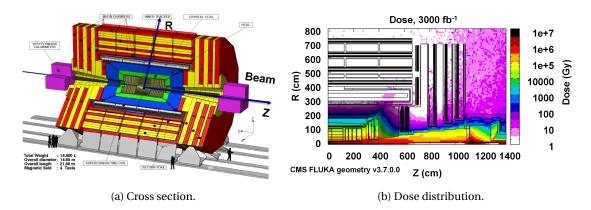

| 1.3  | Simulated total dose distribution over the cross section of the Compact Muon               |     |

|      | Solenoid (CMS) experiment                                                                  | 3   |

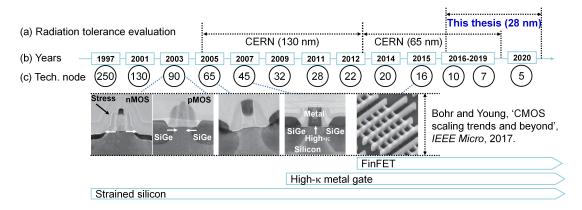

| 1.4  | Radiation tolerance evaluation for CERN's particle experiments along with the              |     |

|      | minimum feature size scaling of complementary metal-oxide-semiconductor                    |     |

|      | (CMOS) technologies over years.                                                            | 4   |

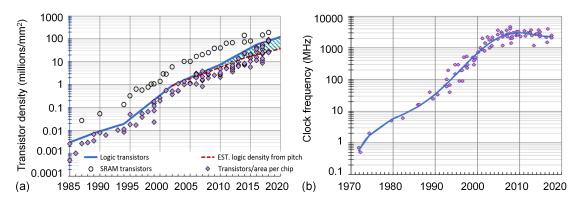

| 1.5  | Evolution of the transistor density and the microprocessor clock frequency over            |     |

|      | years                                                                                      | 5   |

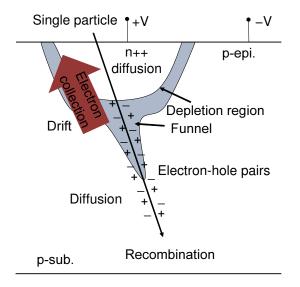

| 1.6  | Illustration of charge collection mechanisms that result in single-event upsets.           | 6   |

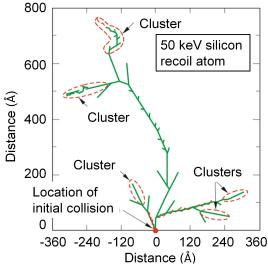

| 1.7  | Displacement cascade damage calculated from a theoretical model                            | 6   |

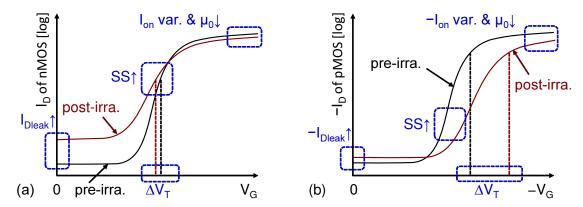

| 1.8  | Basic total ionizing dose (TID) effects on transfer characteristics ( $ I_D  -  V_G $ ) of |     |

|      | n- and p-types of MOS field-effect transistors (MOSFETs)                                   | 7   |

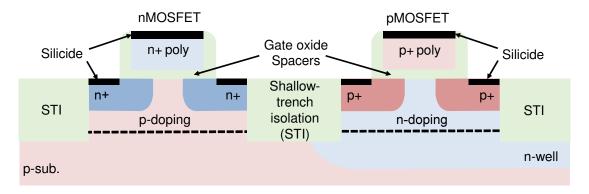

| 1.9  | Cross section of an $n$ MOSFET and a $p$ MOSFET from a generic deep-submicron              |     |

|      | bulk CMOS process, highlighting the gate oxide, spacers, and shallow-trench                |     |

|      | isolation (STI) oxides                                                                     | 8   |

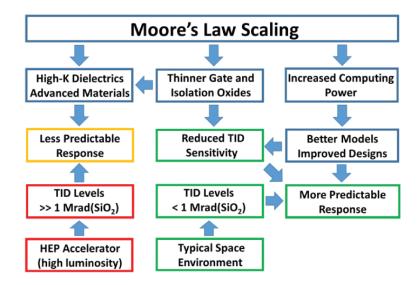

| 1.10 | Schematic illustration of the effects of Moore's law scaling on ionizing radiation         |     |

|      | response of MOSFETs                                                                        | 9   |

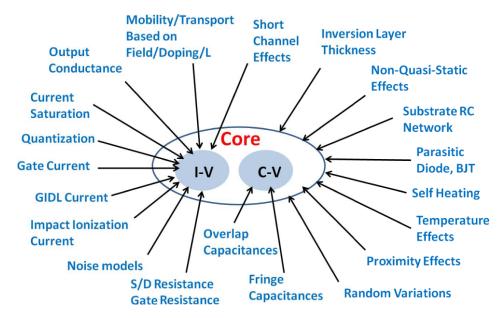

| 1.11 |                                                                                            |     |

|      | MOSFET compact model composed of a charge-based core model and models                      |     |

|      | of non-ideal effects                                                                       | 11  |

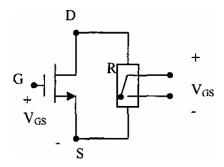

| 1.12 | Circuit schematic of a MOSFET with a TID-controlled variable resistor repre-               | • • |

|      | senting the TID-induced drain leakage current.                                             | 12  |

| 1.13 | Circuit schematic of a MOSFET with a voltage-controlled voltage source model-              | 10  |

|      | ing the TID-induced voltage shift                                                          | 12  |

| 1.14 | Key device parameters versus CMOS generations                                              | 13  |

| 2.1  | Photon-matter interactions versus the atomic number and the photon energy.                 | 18  |

| 2.2  | Schematic representation of the photoelectric effect and Compton scattering.               | 19  |

| 2.3  | Basic physical processes of TID effects on MOS structures, including radiation-            |     |

|      | induced charge generation, recombination, transport, and trapping                          | 20  |

|      |                                                                                            |     |

| 2.4  | Charge yield of various radiation sources in silicon dioxide $(SiO_2)$ samples as a function of the electric field                                                 | 22 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | Schematic illustration of polaron hopping between two nearby shallow trap                                                                                          |    |

|      | states                                                                                                                                                             | 23 |

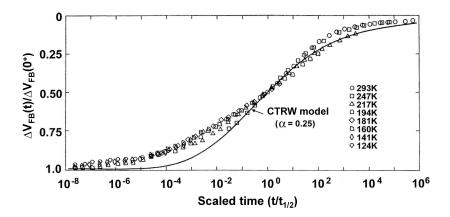

| 2.6  | Flatband voltage evolution of MOS capacitors at various temperature and field conditions, highlighting a strong dependence of hole hopping transport on the        |    |

|      | operating temperature and the applied field                                                                                                                        | 23 |

| 2.7  | Flatband voltage evolution of MOS capacitors as a function of the scaled time at various temperature conditions, presenting the universal and dispersive           |    |

|      | features of hole hopping transport                                                                                                                                 | 24 |

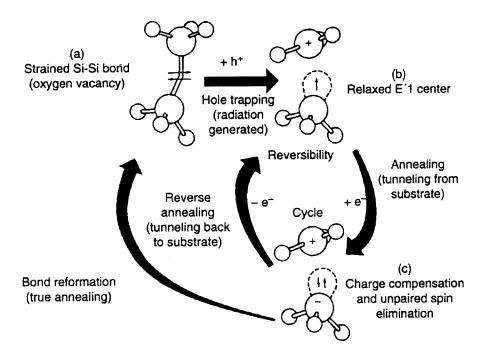

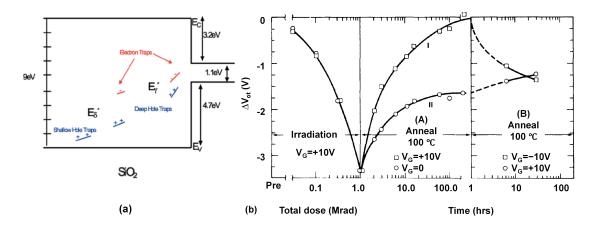

| 2.8  | A model of deep hole trapping and annealing together with intermediate com-                                                                                        |    |

|      | pensation and reversible annealing.                                                                                                                                | 25 |

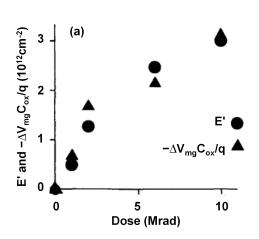

| 2.9  | Correlation between the density of $E'$ centers and the oxide-trapped charge                                                                                       |    |

|      | density.                                                                                                                                                           | 26 |

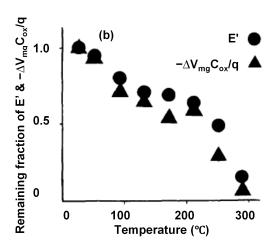

| 2.10 | Energy level distribution of oxide traps and bias-polarity dependence of trapped-hole annealing                                                                    | 27 |

| 2.11 | Schematic diagram that distinguishes the physical location of defects from                                                                                         |    |

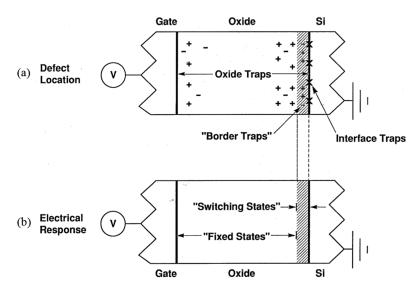

|      | their electrical properties.                                                                                                                                       | 28 |

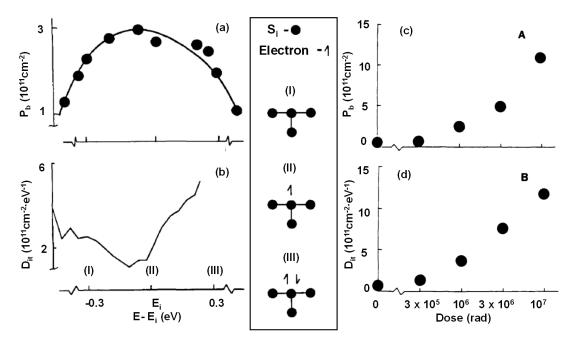

| 2.12 | Correlation between the density of $P_{\rm b}$ centers and the interface-trap density                                                                              | 29 |

| 2.13 | Field and temperature dependence of interface-trap formation, confirming the                                                                                       |    |

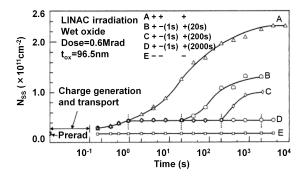

|      | two-stage process with proton transport                                                                                                                            | 30 |

| 2.14 | Effects of gate-oxide-thickness scaling on radiation-induced charge trapping in                                                                                    |    |

|      | MOS capacitors                                                                                                                                                     | 32 |

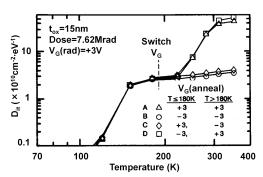

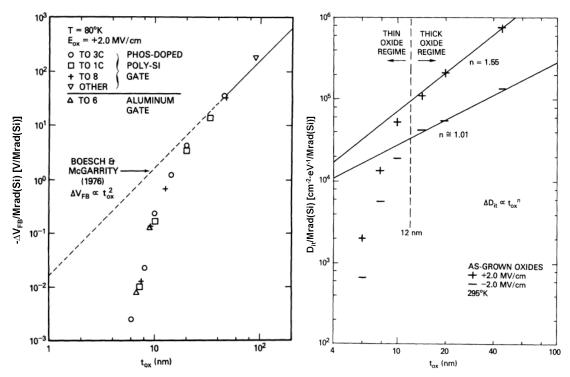

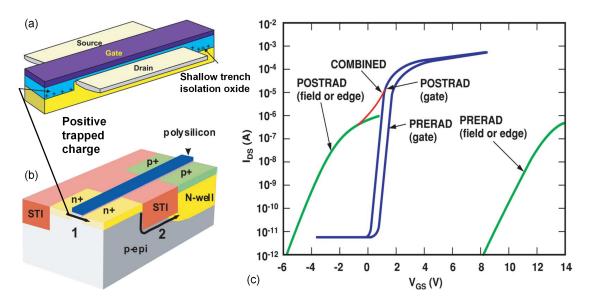

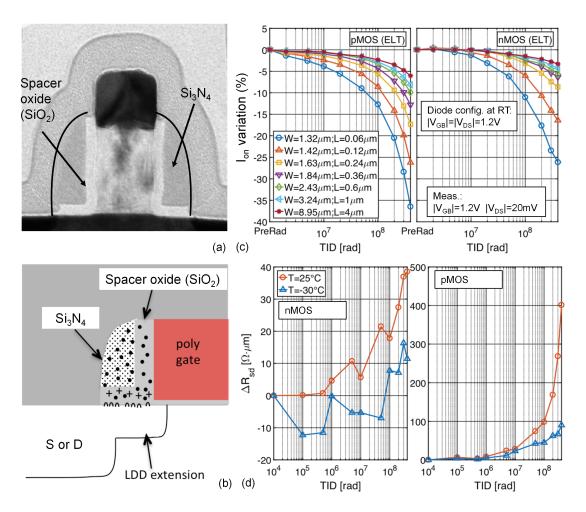

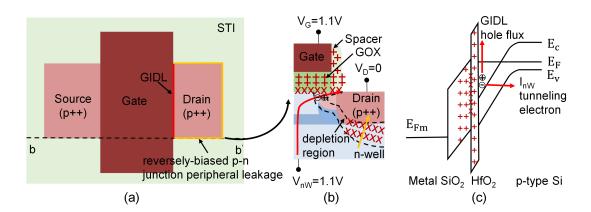

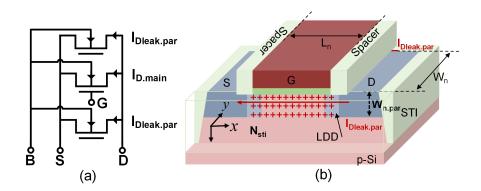

|      | Investigation of the TID-induced parasitic leakage current related to STI oxides.                                                                                  | 34 |

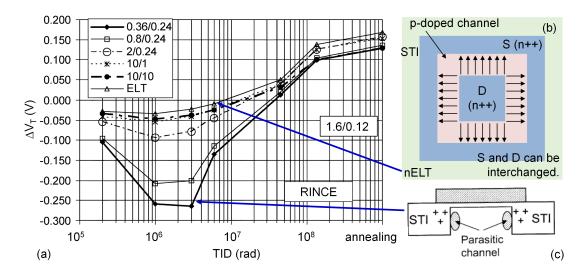

| 2.16 | Illustration of STI-related radiation-induced narrow-channel effects (RINCE) through an analysis of the threshold voltage shift versus TID up to 136 Mrad          | 35 |

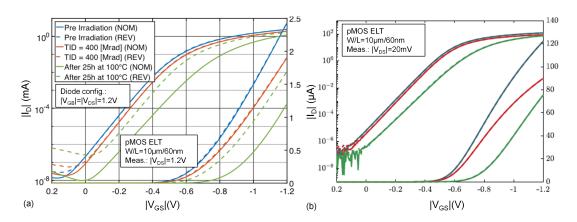

| 2.17 | Spacer-related TID effects on the on-current and the series resistance of diodebiased 65-nm bulk MOSFETs                                                           | 36 |

| 2.18 | Forward and reverse transfer characteristics in saturation and linear operation of a diode-biased 65-nm bulk <i>p</i> MOSFET, indicating spacer-related asymmetric |    |

|      | effects                                                                                                                                                            | 37 |

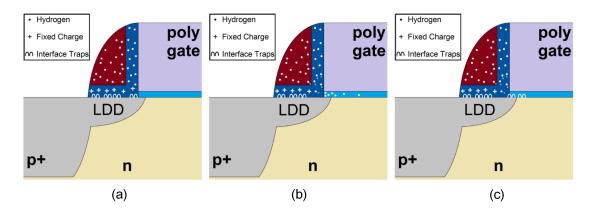

| 2.19 | Schematic representation of spacer-related TID effects                                                                                                             | 38 |

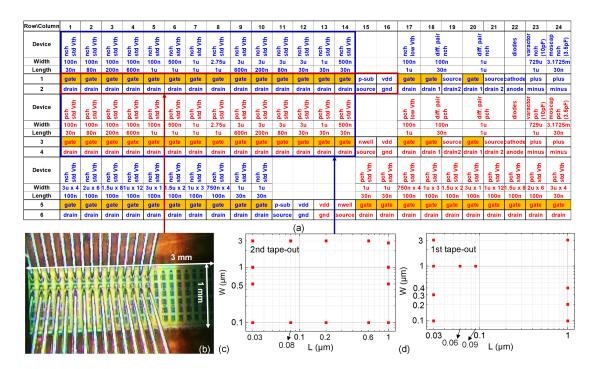

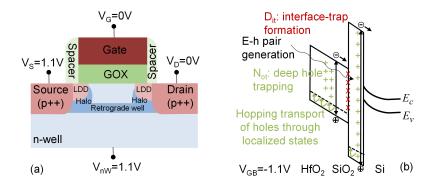

| 3.1  | Pad distribution and geometry information of test structures from a commercial 28-nm bulk CMOS process                                                             | 42 |

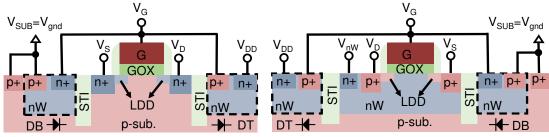

| 2.2  | Cross sections of 28-nm bulk MOSFETs from the second tape-out with two elec-                                                                                       | 42 |

| 3.2  | trostatic discharge (ESD) protection diodes implemented at each gate terminal.                                                                                     | 43 |

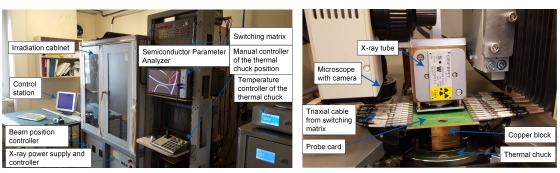

| 3.3  | CERN's X-ray machine and associated measurement instruments                                                                                                        | 44 |

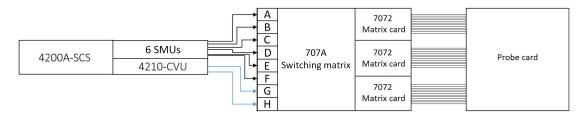

| 3.4  | Switching matrix and its connection with the probe card and the semiconductor                                                                                      |    |

|      | parameter analyzer                                                                                                                                                 | 44 |

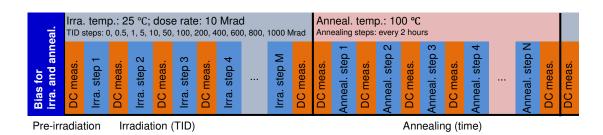

| 3.5  | Typical procedure for obtaining test results, including sequential steps of irradiation at room temperature and annealing at a high temperature with associated |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | static electrical measurements                                                                                                                                  | 45 |

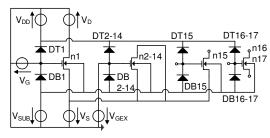

| 3.6  | Circuit schematics of both $n$ - and $p$ MOSFET arrays under test, highlighting                                                                                 |    |

|      | common pads between test structures                                                                                                                             | 46 |

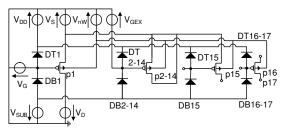

| 3.7  | Schematic illustration of TID-induced charge trapping in the oxide bulk and at                                                                                  |    |

|      | the silicon/oxide interface of a bulk MOSFET                                                                                                                    | 47 |

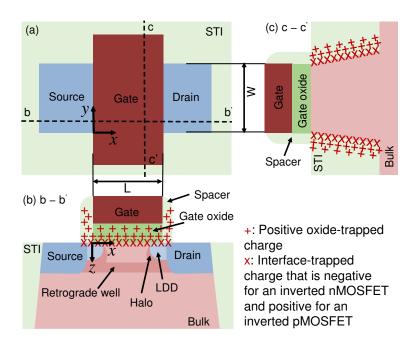

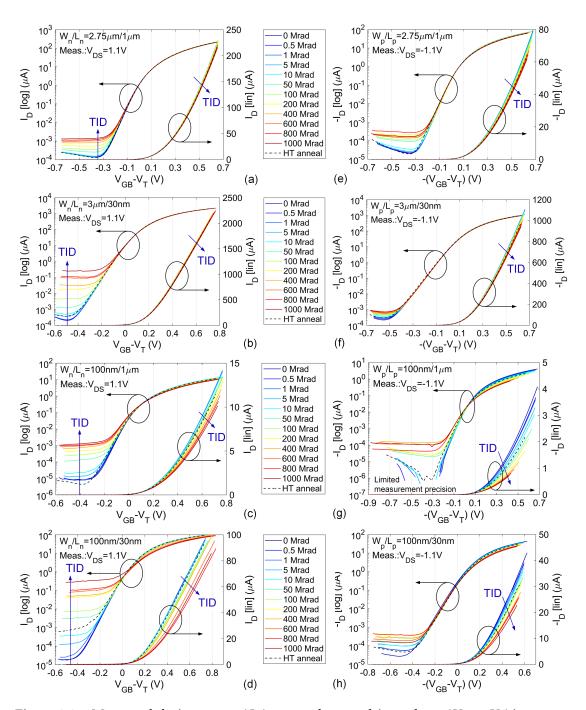

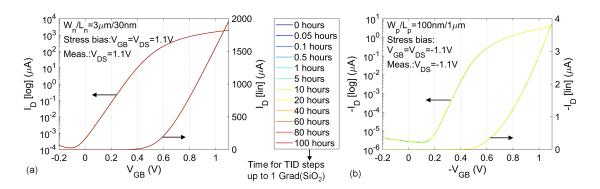

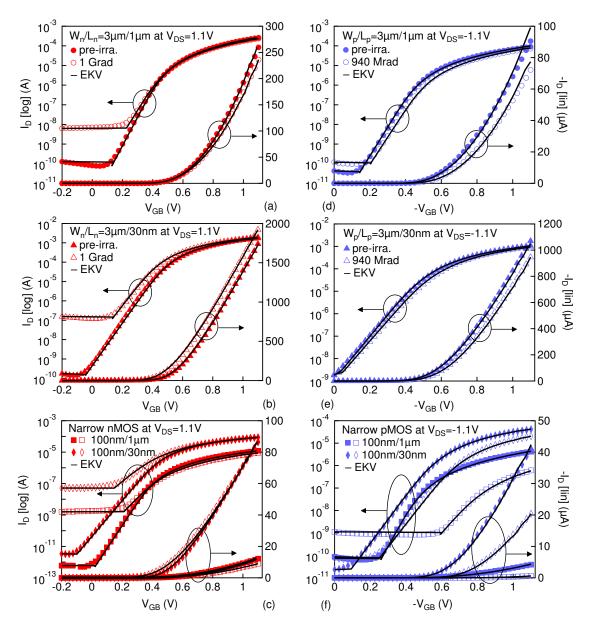

| 3.8  | Measured drain current $ I_{\rm D} $ versus the gate-to-bulk voltage $ V_{\rm GB} $ in saturation                                                               |    |

|      | operation ( $ V_{DS}  = 1.1 \text{V}$ ) of four corner <i>n</i> - and <i>p</i> MOSFETs irradiated at room                                                       |    |

|      | temperature (25 °C) and annealed at a high temperature (100 °C) under the                                                                                       |    |

|      | diode condition ( $ V_{GB}  =  V_{DS}  = 1.1 \text{ V}$ )                                                                                                       | 49 |

| 3.9  | Measured drain current $ I_D $ versus the overdrive voltage $ V_{GB} - V_T $ in saturation                                                                      |    |

|      | operation ( $ V_{DS}  = 1.1 \text{ V}$ ) of four corner <i>n</i> - and <i>p</i> MOSFETs irradiated at room                                                      |    |

|      | temperature (25 °C) and annealed at a high temperature (100 °C) under the                                                                                       |    |

|      | diode condition ( $ V_{GB}  =  V_{DS}  = 1.1 \text{ V}$ )                                                                                                       | 50 |

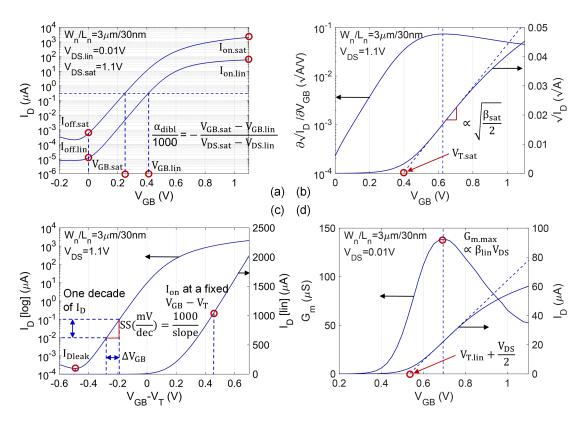

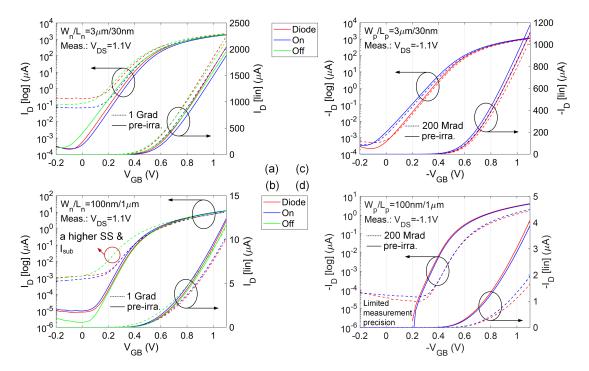

| 3.10 | Definitions and extractions of crucial device parameters for investigating the                                                                                  |    |

|      | radiation response of test structures                                                                                                                           | 52 |

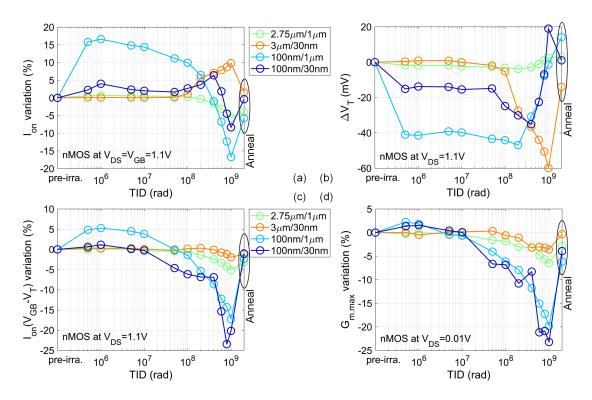

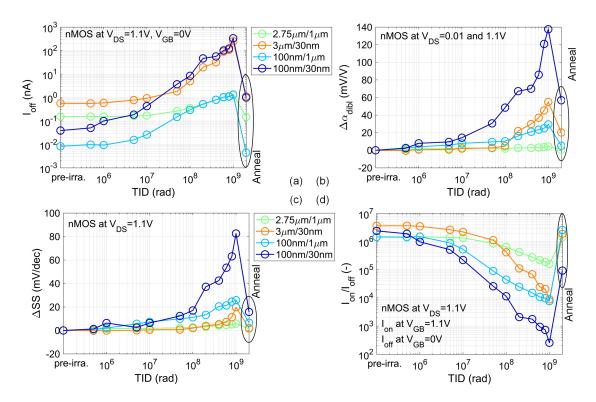

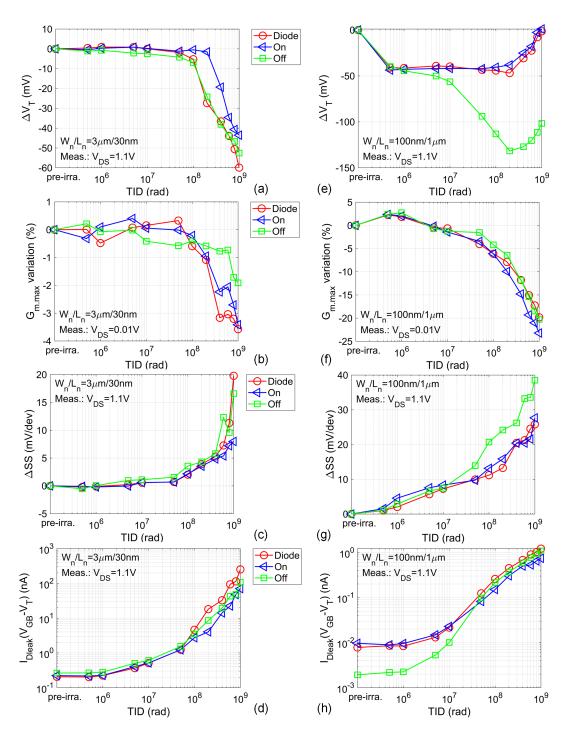

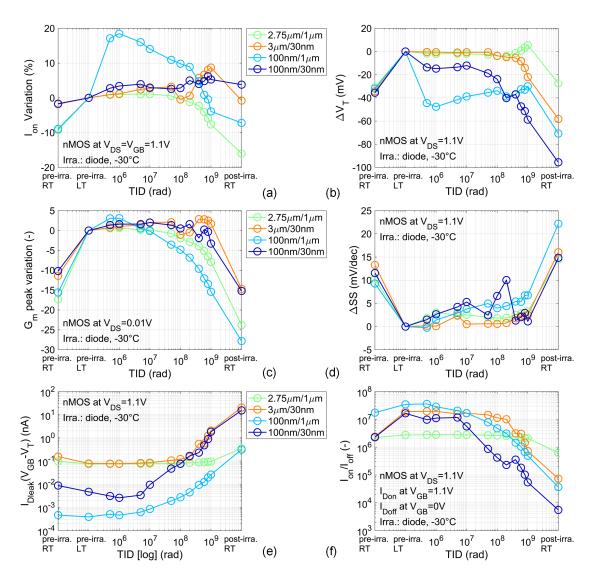

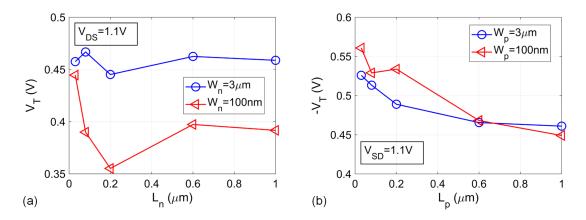

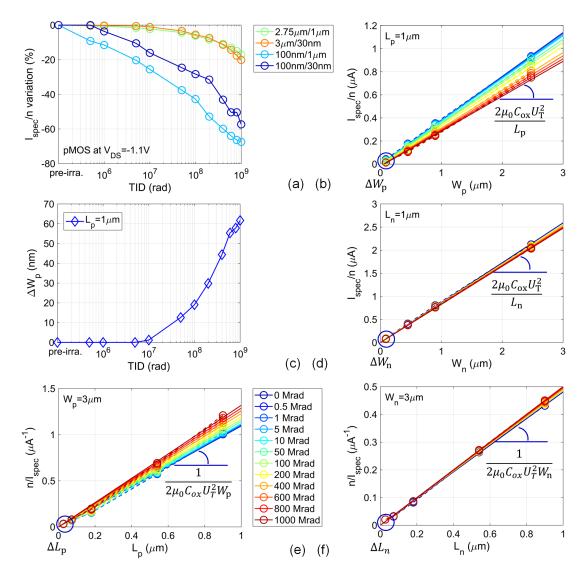

| 3.11 | TID effects on extracted parameters of four corner <i>n</i> MOSFETs, including the                                                                              |    |

|      | on-current $I_{\text{on}}$ , the threshold voltage $V_{\text{T}}$ , the $V_{\text{T}}$ -shift-isolated on-current $I_{\text{on}}$ ,                             |    |

|      | and the peak transconductance $G_{\text{m.max}}$                                                                                                                | 54 |

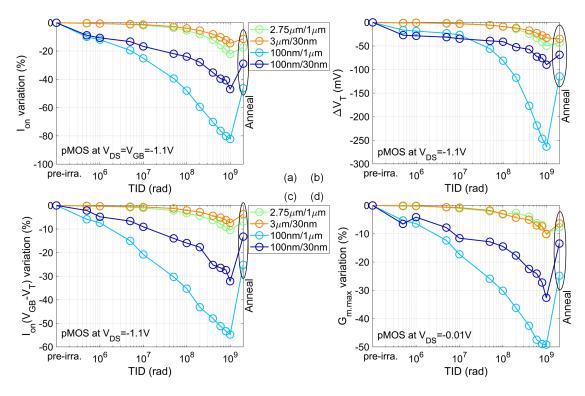

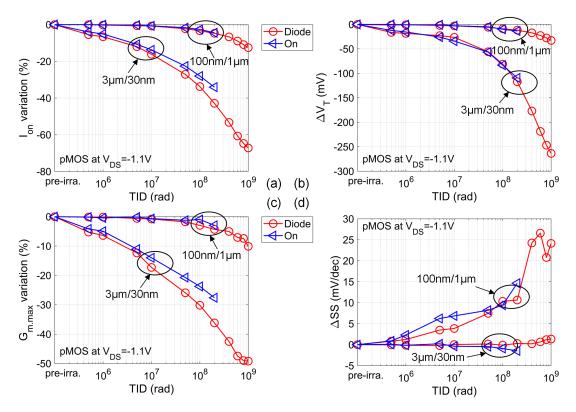

| 3.12 | TID effects on extracted parameters of four corner <i>p</i> MOSFETs, including the                                                                              |    |

|      | on-current $I_{\text{on}}$ , the threshold voltage $V_{\text{T}}$ , the $V_{\text{T}}$ -shift-isolated on-current $I_{\text{on}}$ ,                             |    |

|      | and the peak transconductance $G_{\mathrm{m.max}}$                                                                                                              | 55 |

| 3.13 | TID effects on extracted parameters of four corner $n$ MOSFETs, including the                                                                                   |    |

|      | off-current $I_{\text{off}}$ , the drain-induced barrier lowering (DIBL) parameter $\alpha_{\text{dibl}}$ , the                                                 |    |

|      | subthreshold swing SS, and the on-to-off current ratio $I_{\rm on}/I_{\rm off}$                                                                                 | 56 |

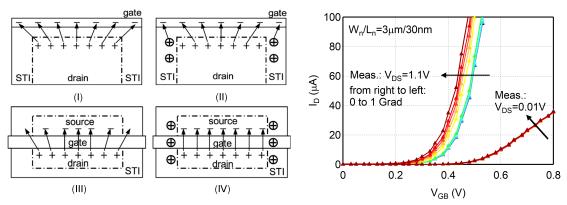

| 3.14 | (a) Dipole theory illustrating the increased drain-to-source coupling and the                                                                                   |    |

|      | more compact electric field pattern as a result of STI-trapped positive charges;                                                                                |    |

|      | (b) measured $I_D$ – $V_{GB}$ curves in linear and saturation operation of the wide/short-                                                                      |    |

|      | channel $n$ MOSFET, highlighting the radiation-enhanced DIBL effect                                                                                             | 57 |

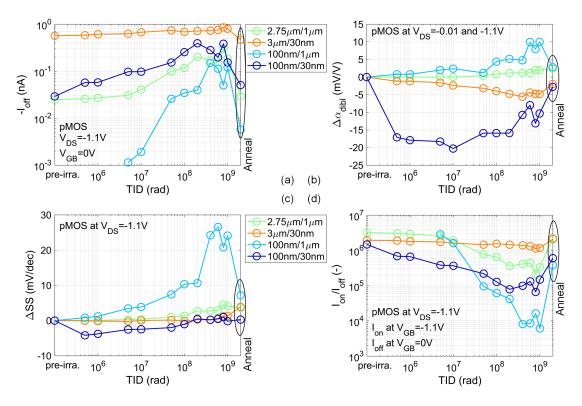

| 3.15 | TID effects on extracted parameters of four corner <i>p</i> MOSFETs, including the                                                                              |    |

|      | off-current $I_{\text{off}}$ , the DIBL parameter $\alpha_{\text{dibl}}$ , the subthreshold swing SS, and the                                                   |    |

|      | on-to-off current ratio $I_{\rm on}/I_{\rm off}$                                                                                                                | 58 |

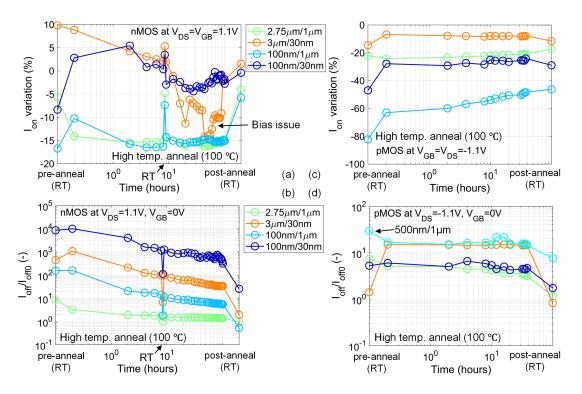

| 3.16 | Post-irradiation annealing effects on the on-current $I_{\rm on}$ and the off-current $I_{\rm off}$                                                             |    |

|      | of diode-biased $n$ - and $p$ MOSFETs at a high temperature (100 °C)                                                                                            | 59 |

| 3.17 | Measured $ I_D  -  V_{GB} $ curves in saturation operation ( $ V_{DS}  = 1.1 \text{ V}$ ) of the wide/sho                                                       |    |

|      | channel <i>n</i> MOSFET and the narrow/long-channel <i>p</i> MOSFET at room tempera-                                                                            |    |

|      | ture (25 °C), indicating negligible non-irradiation stress-induced effects under                                                                                |    |

|      | the diode condition ( $ V_{GB}  =  V_{DS}  = 1.1$ V)                                                                                                            | 61 |

| 3.18 | Measured $ I_D  -  V_{GB} $ curves in saturation operation ( $ V_{DS}  = 1.1 \text{ V}$ ) of wide/short-                                                        |    |

|      | and narrow/long-channel $n$ - and $p$ MOSFETs irradiated at room temperature                                                                                    |    |

|      | (25°C) under various hias conditions                                                                                                                            | 61 |

| 3.19 | Bias dependence of TID effects on parameters of wide/short- and narrow/long-channel <i>n</i> MOSFETs               | 62 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 3.20 | Bias dependence of TID effects on parameters of wide/short- and narrow/long-                                       |    |

| 0.01 | channel pMOSFETs                                                                                                   | 63 |

| 3.21 | TID effects on parameters of four corner <i>n</i> MOSFETs irradiated under the diode                               |    |

|      | condition ( $V_{\rm GB} = V_{\rm DS} = 1.1\rm V$ ) at a low temperature (-30 °C)                                   | 6  |

| 3.22 | TID effects on parameters of four corner <i>p</i> MOSFETs irradiated under the diode                               | 0  |

|      | condition ( $V_{\rm GB} = V_{\rm DS} = -1.1$ V) at a low temperature (-30 °C)                                      | 6  |

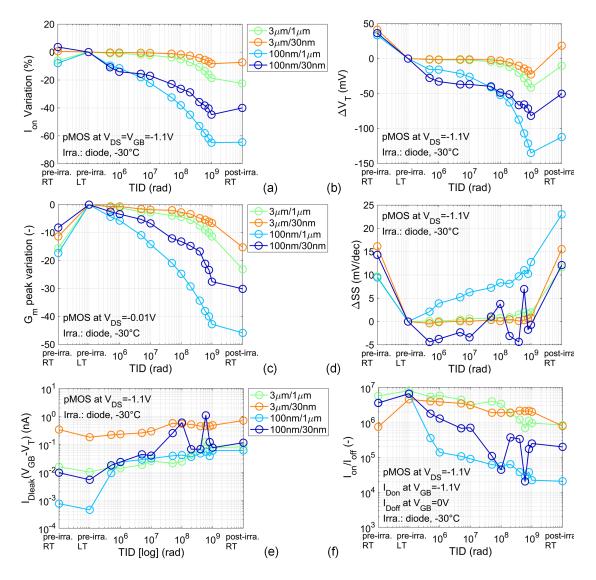

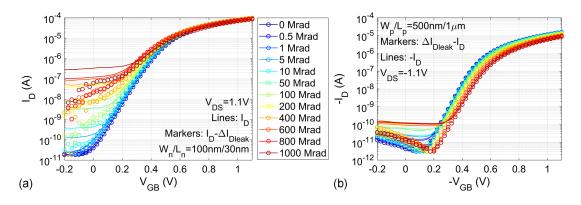

| 3.23 | Measurement results and schematic illustration of the TID-induced drain leak-                                      | _  |

|      | age current of 28-nm bulk MOSFETs                                                                                  | 6  |

| 3.24 | Extracted drain leakage current of <i>n</i> MOSFETs as a function of TID, indicating                               |    |

|      | the dominant contribution of the parasitic drain-to-source leakage current at                                      |    |

|      | high TID levels                                                                                                    | 6  |

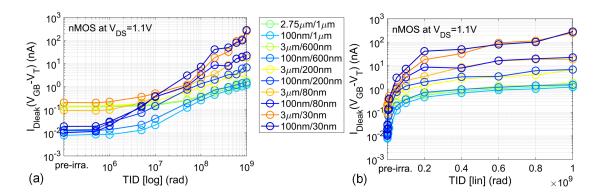

| 3.25 | TID-induced on-current variation in saturation operation ( $ V_{DS}  = 1.1  \text{V}$ ) of                         |    |

|      | long-channel <i>n</i> - and <i>p</i> MOSFETs, indicating the channel width dependence of                           |    |

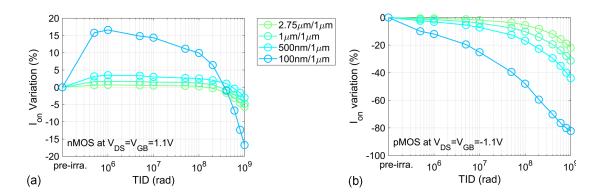

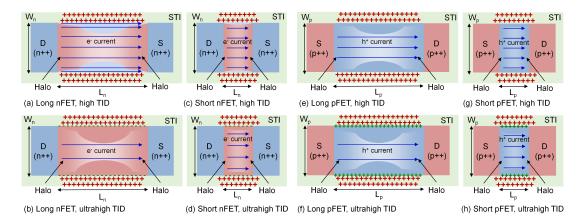

|      | TID effects and RINCE                                                                                              | 6  |

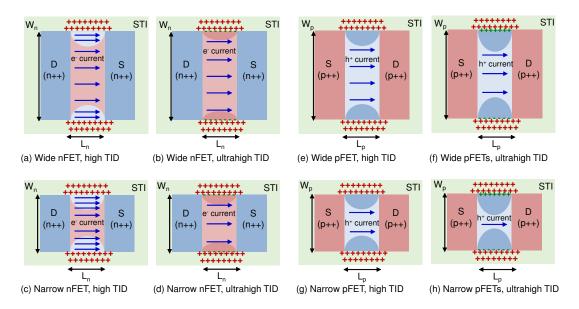

| 3.26 | Top views of wide- and narrow-channel <i>n</i> - and <i>p</i> MOSFETs along a longitudinal                         |    |

|      | cut-plane right below the gate oxide, illustrating RINCE at high and ultrahigh                                     | _  |

|      | TID levels                                                                                                         | 7  |

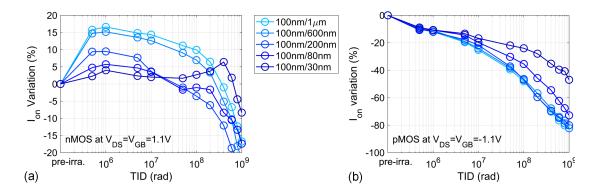

| 3.27 | TID-induced on-current variation in saturation operation ( $ V_{DS}  = 1.1 \text{V}$ ) of                          |    |

|      | narrow-channel $n$ - and $p$ MOSFETs, indicating the channel length dependence                                     |    |

|      | of TID effects and reverse radiation-induced short-channel effects (RISCE)                                         | 7  |

| 3.28 | Forward and reverse transfer characteristics in saturation operation ( $ V_{DS} $ =                                |    |

|      | 1.1V) of the wide/short-channel MOSFET of both types, indicating no signifi-                                       |    |

|      | cant asymmetric behavior                                                                                           | 7  |

| 3.29 | Threshold voltage $V_T$ versus the channel length $L$ of fresh $n$ - and $p$ MOSFETs,                              |    |

|      | indicating the halo-induced $V_{\mathrm{T}}$ roll-off                                                              | 7  |

| 3.30 | Top views of wide- and narrow-channel <i>n</i> - and <i>p</i> MOSFETs along a longitudinal                         |    |

|      | cut-plane right below the gate oxide, illustrating the reverse RISCE at high and                                   |    |

|      | ultrahigh TID levels                                                                                               | 7  |

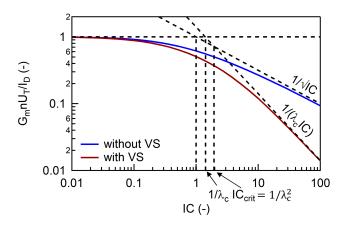

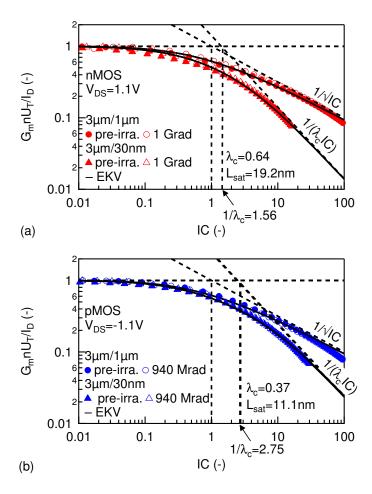

| 4.1  | Description of the asymptotoes of the normalized transconductance efficiency                                       |    |

| 1.1  | $G_{\rm m} n U_{\rm T} / I_{\rm D}$ with respect to the inversion coefficient $IC.\ldots\ldots\ldots$              | 8  |

| 4.2  | Extraction of EKV model parameters: the slope factor $n$ , the specific current                                    | Ū  |

| 1.2  | $I_{\rm spec}$ , the velocity saturation parameter $\lambda_{\rm c}$ , the threshold voltage $V_{\rm T}$ , and the |    |

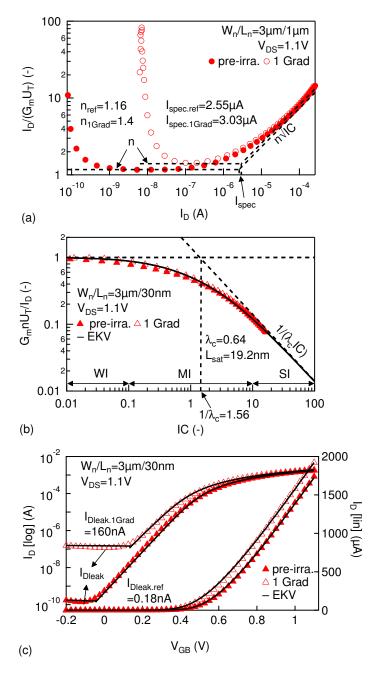

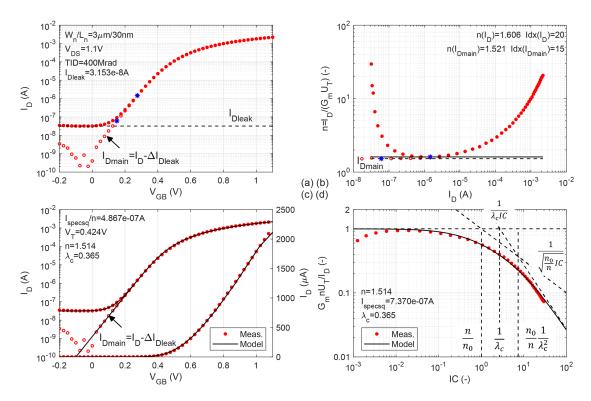

|      | drain leakage current $I_{\text{Dleak}}$                                                                           | 8  |

| 4.3  | The simplified EKV MOSFET model versus the measured $ I_{\rm D}  -  V_{\rm GB} $ curves of                         | 9  |

| 1.0  | four corner $n$ - and $p$ MOSFETs with respect to pre-irradiation and an ultrahigh                                 |    |

|      | TID                                                                                                                | 8  |

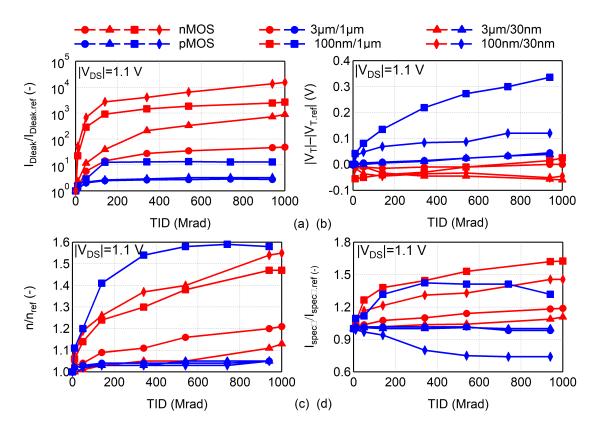

| 4.4  | TID effects on the drain leakage current $I_{\text{Dleak}}$ , the threshold voltage $V_{\text{T}}$ , the           | ,  |

|      | slope factor $n$ , and the specific current per square $I_{\text{spec}_{\square}}$ of four corner 28-nm            |    |

|      | bulk $n$ - and $p$ MOSFETs                                                                                         | 8  |

|      |                                                                                                                    |    |

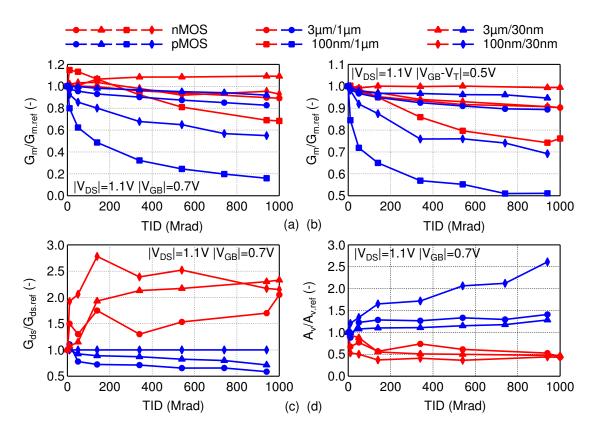

| 4.5  | TID effects on the transconductance $G_{\rm m}$ , the output conductance $G_{\rm ds}$ , and the intrinsic gain $A_{\rm v}$ of four corner $n$ - and $p$ MOSFETs                                        | 89  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

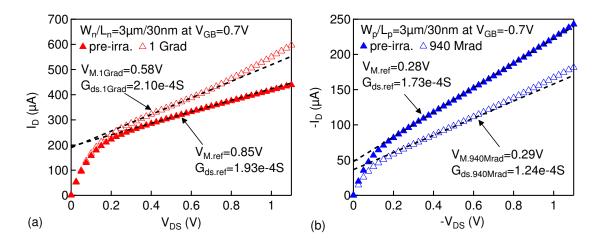

| 4.6  | Output characteristics of the wide/short-channel MOSFET of both types with respect to pre-irradiation and an ultrahigh TID.                                                                            | 90  |

| 4.7  | Normalized transconductance efficiency $G_{\rm m}nU_{\rm T}/I_{\rm D}$ of wide/long- and wide/sho channel $n$ - and $p$ MOSFETs with respect to pre-irradiation and an ultrahigh                       |     |

| 4.8  | TID                                                                                                                                                                                                    | 91  |

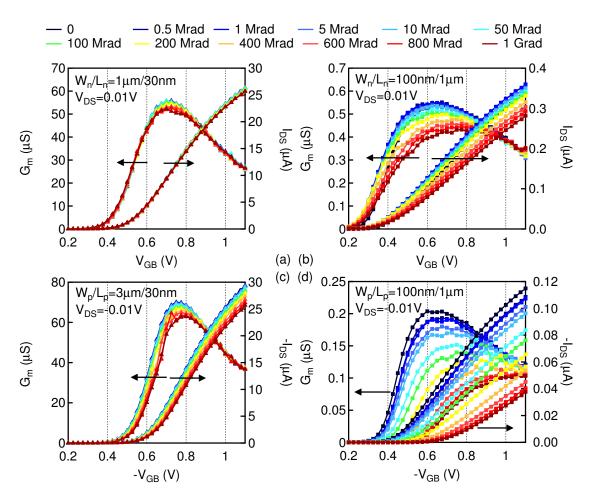

| 4.9  | ture (25 °C)                                                                                                                                                                                           | 92  |

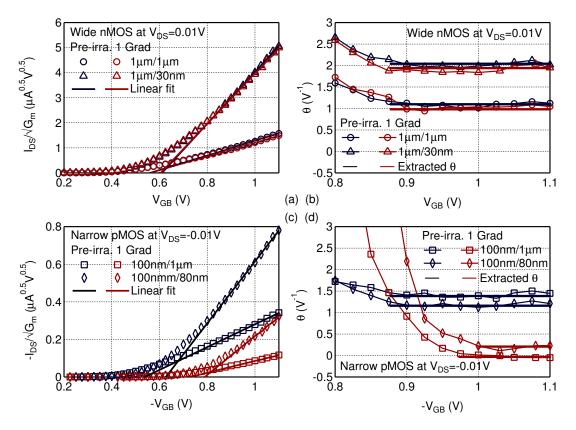

|      | $n$ MOSFETs and narrow-channel $p$ MOSFETs as a function of $ V_{GB} $ with respect to pre-irradiation and 1 Grad of TID                                                                               | 94  |

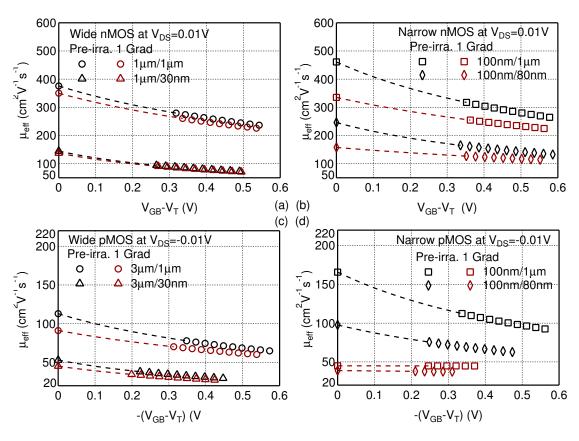

| 4.10 | overdrive voltage $ V_{\rm GB}-V_{\rm T} $ with respect to pre-irradiation and 1 Grad of TID.                                                                                                          | 95  |

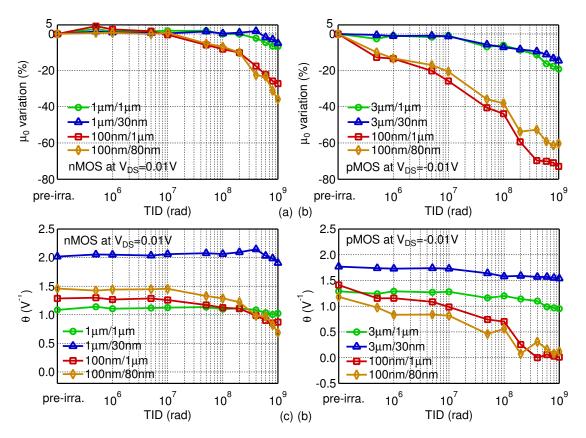

| 4.11 | TID-induced evolution of the low-field channel mobility $\mu_0$ and the effective mobility degradation coefficient $\theta$ of four corner $n$ - and $p$ MOSFETs                                       | 96  |

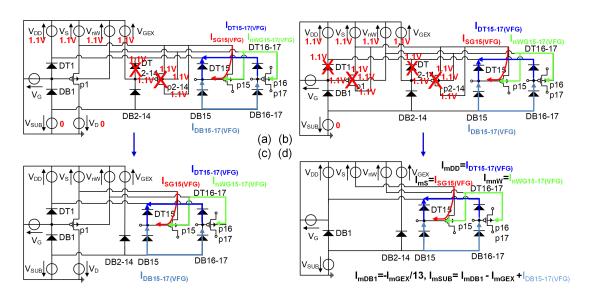

| 4.12 | Circuit schematics of $p$ MOSFETs in the same cluster for extracting intrinsic leakage components                                                                                                      | 98  |

| 4.13 | Extracted additional leakage components versus TID for identifying the intrinsic leakage components of each $p$ MOSFET                                                                                 | 99  |

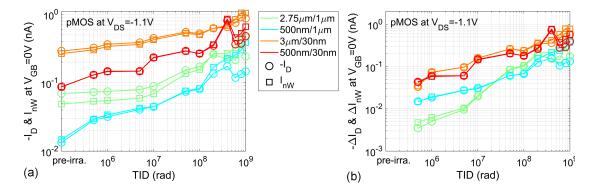

| 4.14 | Drain current $I_D$ and n-well current $I_{nW}$ of $p$ MOSFETs extracted at $V_{GB} = 0$ V as well as their net increase as a function of TID, suggesting the dominant                                 |     |

| 4.15 | contribution of the n-well leakage to the off-current                                                                                                                                                  | 99  |

| 4.16 | <i>p</i> MOSFET                                                                                                                                                                                        | 100 |

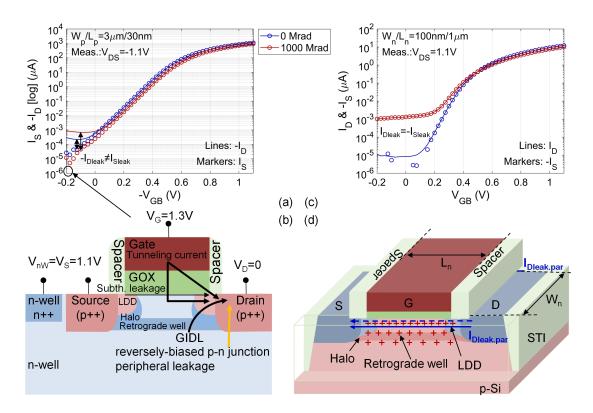

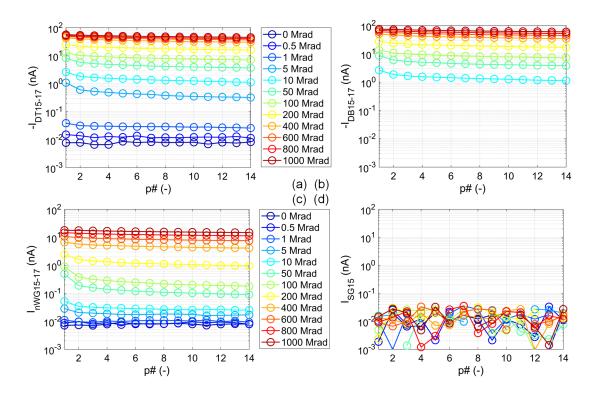

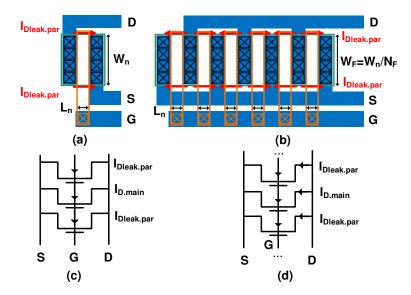

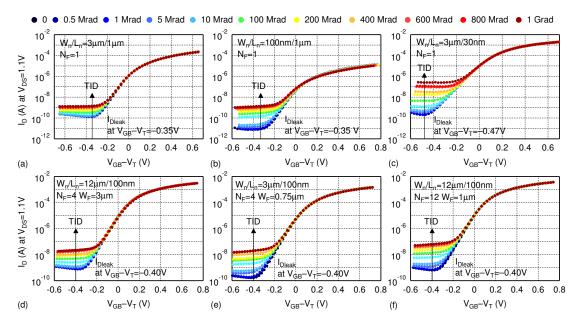

| 4.17 | with the number of fingers                                                                                                                                                                             |     |

| 4.18 | finger and multi-finger $n$ MOSFETs                                                                                                                                                                    | 101 |

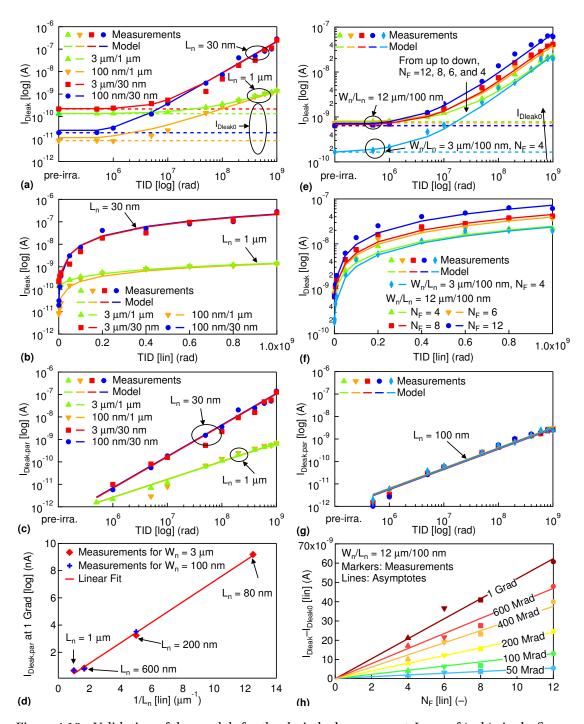

| 4.19 | drain-to-source leakage current $I_{\text{Dleak,par}}$ as a function of TID Equivalent circuit and schematic illustration of an irradiated $n$ MOSFET with                                             | 103 |

|      | two gate-independent lateral parasitic devices                                                                                                                                                         | 106 |

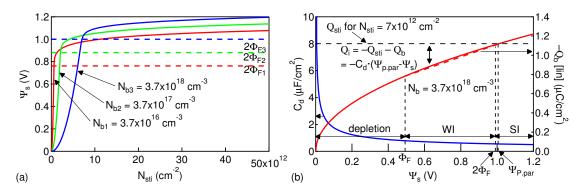

| 4.20 | Surface potential $\Psi_s$ versus the equivalent STI-related trap density per unit area $N_{sti}$ ; linearization of the inversion charge density $Q_i$ with respect to the surface potential $\Psi_s$ | 107 |

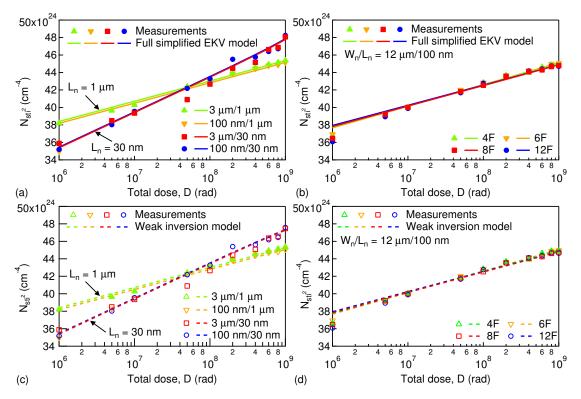

| 4.21 | The square of the STI-related trap density per unit area $N_{\text{sti}}^2$ obtained from measurements and the models as a function of the total dose $D$                                              |     |

|      |                                                                                                                                                                                                        |     |

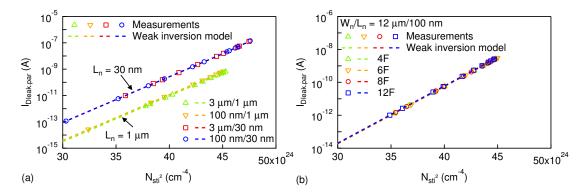

| 4.22 | Extracted and modeled parasitic drain-to-source leakage current $I_{\rm Dleak,par}$ as a function of the square of the equivalent STI-related trap density $N_{\rm sti}^2$ using weak inversion approximation                                                                                                                            | 111 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

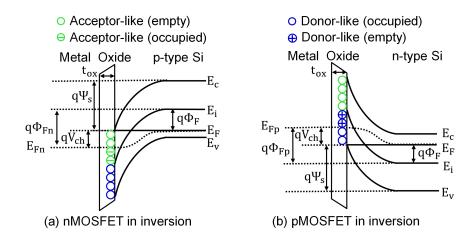

| 5.1  | Energy band diagrams illustrating interface-charge trapping in an $n$ MOSFET and a $p$ MOSFET in inversion                                                                                                                                                                                                                               | 115 |

| 5.2  | Equivalent scheme of a MOSFET for CV characteristics                                                                                                                                                                                                                                                                                     | 116 |

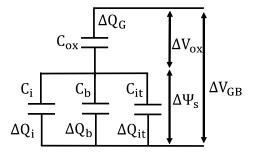

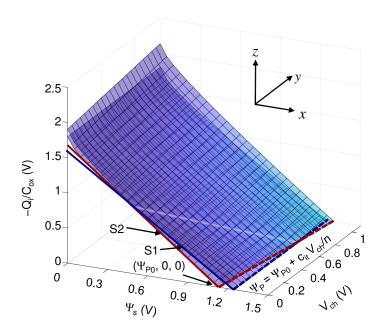

| 5.3  | Surface potential $\Psi_s$ and inversion-charge-density-related potential $-Q_i/C_{ox}$ versus the gate-to-bulk voltage $V_{GB}$ at different values of the oxide-trap density $N_{ot}$ and the interface-trap density $D_{it}$ for an $n$ MOSFET, illustrating the impact of oxide- and interface-trapped charges on MOS electrostatics | 117 |

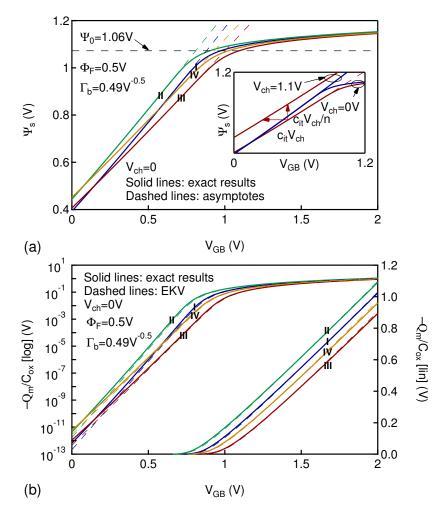

| 5.4  | Methodology of solving the inversion charge density from 1-D Poisson's equation and boundary conditions.                                                                                                                                                                                                                                 |     |

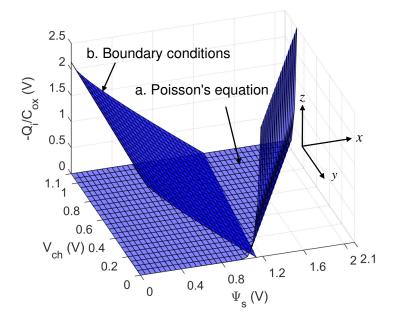

| 5.5  | Inversion-charge-density-related potential $-Q_i/C_{\rm ox}$ versus the surface potential $\Psi_{\rm s}$ and the channel voltage $V_{\rm ch}$ at a given gate-to-bulk voltage ( $V_{\rm GB}=1.1\rm V$ ) for an $n$ MOSFET, illustrating the validation of inversion charge linearization                                                 | 119 |

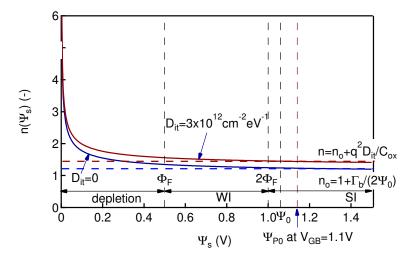

| 5.6  | Slope $n(\Psi_s)$ of the inversion-charge-density-related potential $-Q_i/C_{ox}$ versus the surface potential $\Psi_s$ at a given gate-to-bulk voltage ( $V_{GB}=1.1$ V) and different values of the interface-trap density $D_{it}$ for an $n$ MOSFET, illustrating the validation of inversion charge linearization                   | 121 |

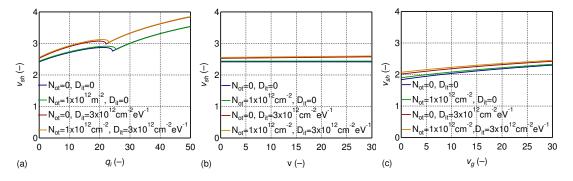

| 5.7  | Normalized threshold shift $v_{\rm sh}$ as a function of the normalized inversion charge density $q_{\rm i}$ , the normalized channel voltage $v_{\rm sh}$ and the normalized gate-to-bulk voltage $v_{\rm g}$                                                                                                                           | 122 |

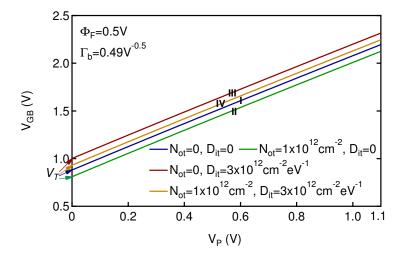

| 5.8  | Gate-to-bulk voltage $V_{\rm GB}$ versus the pinch-off voltage $V_{\rm P}$ at different values of the oxide-trap density $N_{\rm ot}$ and the interface-trap density $D_{\rm it}$ for an $n$ MOSFET, illustrating the influence of oxide- and interface-trapped charges on the thresh-                                                   | 122 |

| 5.9  | old voltage                                                                                                                                                                                                                                                                                                                              | 124 |

| 0.0  | on the vertical field $E_z$ at a low longitudinal field                                                                                                                                                                                                                                                                                  | 127 |

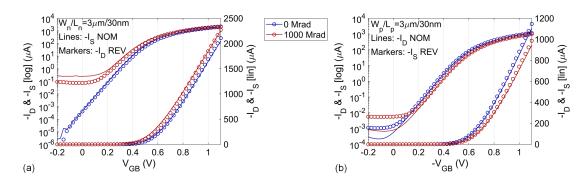

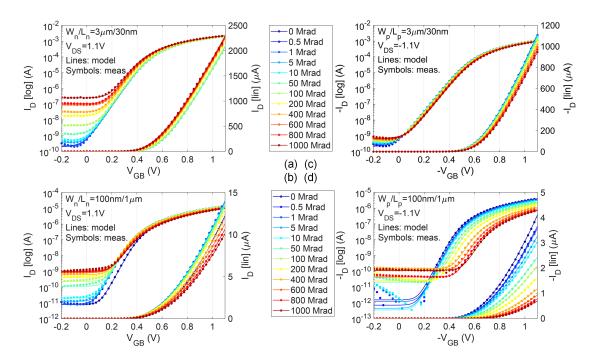

| 5.10 | Validation of the generalized EKV MOSFET model with the measured $ I_{\rm D} - V_{\rm GB} $ curves in saturation operation ( $ V_{\rm DS} =1.1\rm V$ ) of long- and short-channel $n$ - and $p$ MOSFETs corresponding to pre-radiation and 1 Grad of TID                                                                                 |     |

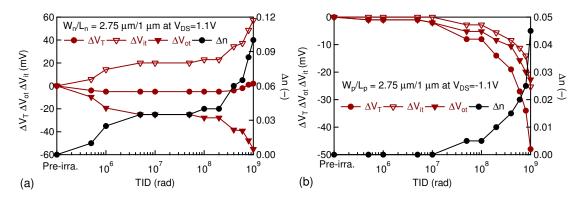

| 5.11 | Threshold voltage shift $\Delta V_{\mathrm{T}}$ (on the left axis) and slope factor increase $\Delta n$ (on                                                                                                                                                                                                                              |     |

|      | the right axis) with respect to TID for a long-channel MOSFET of both types. $$ .                                                                                                                                                                                                                                                        | 132 |

| 5.12 | Cross section of a high- $\kappa$ $p$ MOSFET along the channel width and its schematic illustration of TID-induced charge trapping under the diode condition                                                                                                                                                                             | 132 |

| 5.13 | Parameter extraction with the generalized EKV MOSFET model using an $n$ MOSFE                                                                                                                                                                                                                                                            | Τ   |

|      | as an example                                                                                                                                                                                                                                                                                                                            | 134 |

| 5.14 | Measured $ I_D $ and calculated $ I_D - \Delta I_{Dleak} $ versus $ V_{GB} $ curves of an $n$ MOSFET and a $p$ MOSFET, showing the influence of the drain leakage current increase                                                                                                                                                       |     |

|      | on device performance                                                                                                                                                                                                                                                                                                                    | 134 |

|      |                                                                                                                                                                                                                                                                                                                                          |     |

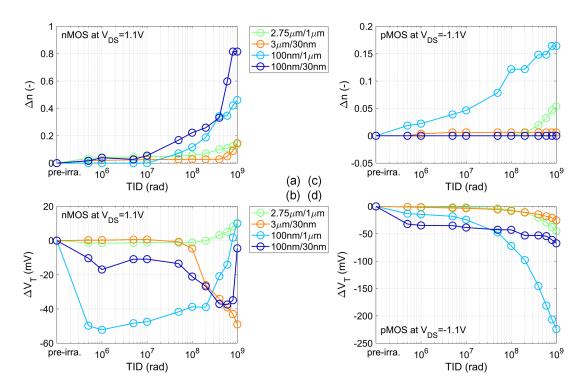

| 5.15 | Extracted slope factor increase $\Delta n$ and threshold voltage shift $\Delta V_{\rm T}$ of four                  |     |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

|      | corner $n$ - and $p$ MOSFETs using the generalized EKV MOSFET model                                                | 136 |

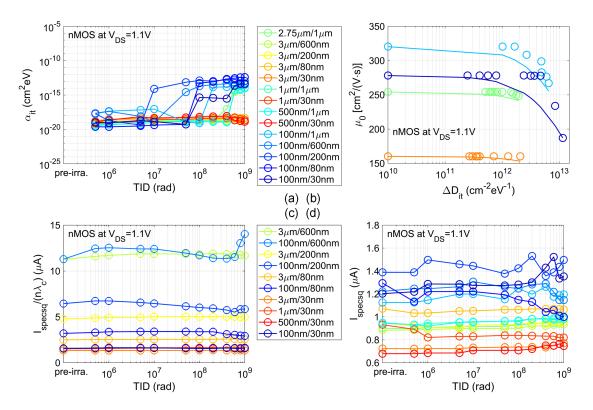

| 5.16 | $TID\text{-}induced\ evolution\ of\ mobility-related\ parameters\ of\ 28-nm\ bulk\ MOSFETs.}$                      | 137 |

| 5.17 | TID-induced evolution of geometry-related model parameters                                                         | 138 |

| 5.18 | Extraction of the reduced channel width $\Delta W_{\rm p}$ of pMOSFETs and the low-field                           |     |

|      | channel mobility $\mu_0$ of both $n$ - and $p$ MOSFETs using the design-oriented com-                              |     |

|      | pact model                                                                                                         | 141 |

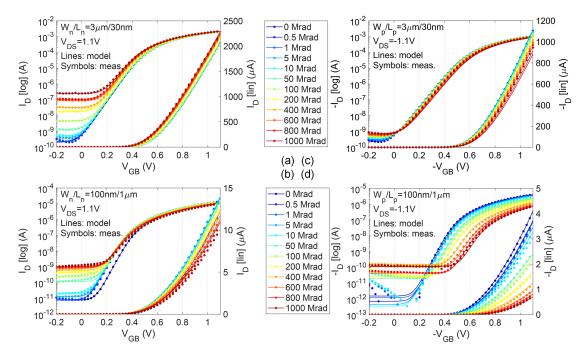

| 5.19 | Validation of the design-oriented compact model with the measured $ I_{\rm D}  -  V_{\rm GB} $                     |     |

|      | curves of two corner $n$ - and $p$ MOSFETs with respect to TID up to 1 Grad                                        | 142 |

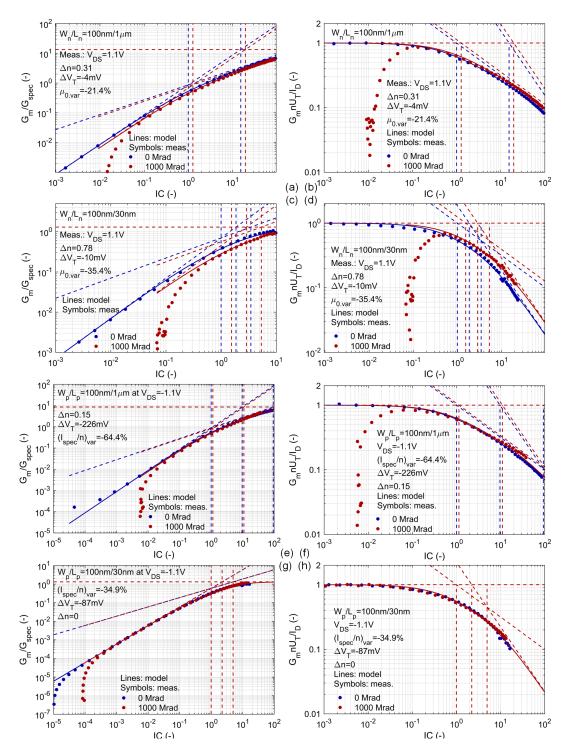

| 5.20 | Model results and measurement points of the normalized transconductance                                            |     |

|      | $G_{\rm m}/G_{\rm spec}$ and the normalized transconductance efficiency $G_{\rm m}nU_{\rm T}/I_{\rm D}$ of narrow- |     |

|      | channel $n$ - and $p$ MOSFETs with respect to pre-irradiation and 1 Grad of TID                                    | 143 |

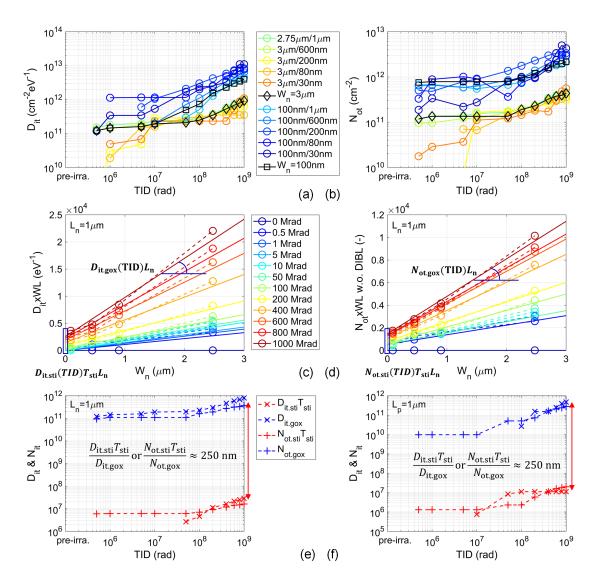

| 5.21 | Width dependence of TID-induced trapped charges and trapped-charge scaling                                         |     |

|      | over device dimensions.                                                                                            | 145 |

| 5.22 | Validation of the design-oriented compact model with the measured $ I_{\rm D}  -  V_{\rm GB} $                     |     |

|      | curves of two corner $n$ - and $p$ MOSFETs using using approximated oxide- and                                     |     |

|      | interface-trapped charge densities                                                                                 | 146 |

## List of tables

| 1.1 | Ionizing radiation levels for harsh radiation environments                    | 10  |

|-----|-------------------------------------------------------------------------------|-----|

| 4.1 | Parameters of the semi-empirical physical model for the drain-to-source leak- |     |

|     | age current                                                                   | 105 |

| 5.1 | Parameters of the generalized EKV MOSFET model for wide-channel MOSFETs       | 131 |

# List of symbols

| Symbol                                                            | Description                                         | Quantity/Unit                        |  |

|-------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------|--|

|                                                                   | Physical parameters                                 |                                      |  |

| q                                                                 | Elementary charge                                   | $1.60 \times 10^{-19} \mathrm{C}$    |  |

| k                                                                 | Boltzmann constant                                  | $1.38 \times 10^{-23}  \text{J/K}$   |  |

| T                                                                 | Room temperature (unless stated otherwise)          | 298.15 K                             |  |

| $U_{\rm T} = kT/q$                                                | Thermodynamic voltage                               | $0.026\mathrm{V}$                    |  |

| $\epsilon_0$                                                      | Vacuum permittivity                                 | $8.85 \times 10^{-12} \mathrm{F/m}$  |  |

| $\epsilon_{ m si}$                                                | Permittivity of silicon (Si)                        | $11.9\epsilon_0$                     |  |

| $\epsilon_{ m ox}$                                                | Permittivity of silicon dioxide (SiO <sub>2</sub> ) | $3.9\epsilon_0$                      |  |

| $n_{ m i}$                                                        | Intrinsic carrier concentration in Si               | $1.48 \times 10^{16}  \text{m}^{-3}$ |  |

| $\mu_0$                                                           | Low-field channel mobility                          | $m/(V \cdot s)$                      |  |

|                                                                   |                                                     |                                      |  |

|                                                                   | Process parameters                                  | _                                    |  |

| $N_{ m b}$                                                        | Channel doping concentration                        | $\mathrm{m}^{-3}$                    |  |

| $\Phi_{\rm F} = U_{\rm T} \ln(N_{\rm b}/n_{\rm i})$               | Fermi potential                                     | V                                    |  |

| $v_{ m drift}$                                                    | Drift velocity                                      | m/s                                  |  |

| $v_{sat}$                                                         | Saturated drift velocity                            | m/s                                  |  |

| $T_{ m sti}$                                                      | Thickness of the shallow trench isolation (STI)     | m                                    |  |

| $X_{j}$                                                           | Junction depth                                      | m                                    |  |

| $t_{ m ox}$                                                       | Equivalent oxide thickness to SiO <sub>2</sub>      | m                                    |  |

| $C_{\rm ox} = \epsilon_{\rm ox} / t_{\rm ox}$                     | Gate oxide capacitance per unit area                | F/m <sup>2</sup>                     |  |

| $\Gamma_{\rm b} = \sqrt{2qN_{\rm b}\epsilon_{\rm si}}/C_{\rm ox}$ | Substrate modulation factor                         | $V^{0.5}$                            |  |

| $\gamma_{\rm b} = \Gamma_{\rm b} / \sqrt{U_{\rm T}}$              | Normalized substrate modulation factor              | _                                    |  |

| Geometry                                                          |                                                     |                                      |  |

| W                                                                 | Channel width                                       | m                                    |  |

| $N_{ m F}$                                                        | Number of fingers                                   | -                                    |  |

| $W_{ m F}$                                                        | Channel width of each finger                        | m                                    |  |

| $W_{ m eff}$                                                      | Effective channel width                             | m                                    |  |

| $\Delta W$                                                        | Channel width modification                          | m                                    |  |

| L                                                                 | Channel length                                      | m                                    |  |

|                                                                   |                                                     |                                      |  |

| Symbol                                                    | Description                                             | Quantity/Unit |  |  |

|-----------------------------------------------------------|---------------------------------------------------------|---------------|--|--|

| $L_{ m eff}$                                              | Effective channel length                                | m             |  |  |

| $\Delta L$                                                | Channel length modification                             | m             |  |  |

| x                                                         | Distance from the source along the channel              | m             |  |  |

| $\xi = x/L$                                               | Normalized position along the channel                   | _             |  |  |

| y                                                         | Distance across the channel                             | m             |  |  |

| Z                                                         | Vertical distance down from the surface                 | m             |  |  |

|                                                           | Voltages and potentials                                 |               |  |  |

| $\Phi_{\mathrm{Fn}}$                                      | Electron quasi-Fermi potential                          | V             |  |  |

| $\Phi_{	ext{Fp}}$                                         | Hole quasi-Fermi potential                              | V             |  |  |

| $\Psi_{ m s}$                                             | Surface potential                                       | V             |  |  |

| $\Psi_0 = 2\Phi_{\rm F} + (2-4)U_{\rm T}$                 | Constant potential slightly larger than $2\Phi_{\rm F}$ | V             |  |  |

| $\Psi_{ m P}$                                             | Pinch-off potential                                     | V             |  |  |

| $\Phi_{ m ms}$                                            | Metal-silicon work function difference                  | V             |  |  |

| $V_{ m FB}$                                               | Flatband voltage                                        | V             |  |  |

| $V_{ m T}$                                                | Threshold voltage                                       | V             |  |  |

| $V_{ m GB}$                                               | Gate-to-bulk voltage                                    | V             |  |  |

| $V_{ m DS}$                                               | Drain-to-source voltage                                 | V             |  |  |

| $V_{ m DD}$                                               | Power supply                                            | V             |  |  |

| $V_{ m ox}$                                               | Voltage drop across the gate oxide                      | V             |  |  |

| $V_{ m ch}$                                               | Channel voltage                                         | V             |  |  |

| $V_{ m P}$                                                | Pinch-off voltage                                       | V             |  |  |

| $V_{ m mg}$                                               | Mid-gap voltage                                         | V             |  |  |

| $\phi_{ m f} = \Phi_{ m F}/U_{ m T}$                      | Normalized Fermi potential                              | _             |  |  |

| $\psi_{\rm S} = \Psi_{\rm S}/U_{\rm T}$                   | Normalized surface potential                            | _             |  |  |

| $\psi_{\rm p} = \Psi_{\rm P}/U_{\rm T}$                   | Normalized pinch-off potential                          | _             |  |  |

| $v_{ m sh}$                                               | Threshold shift                                         | _             |  |  |

| $v = V_{\rm ch}/U_{\rm T}$                                | Normalized channel voltage                              | _             |  |  |

| $v_{\rm p} = V_{\rm P}/U_{\rm T}$                         | Normalized pinch-off voltage                            | _             |  |  |

| Currents                                                  |                                                         |               |  |  |

| $I_{ m D}$                                                | Drain current                                           | A             |  |  |

| $I_{ m Dleak}$                                            | Drain leakage current                                   | A             |  |  |

| $I_{\text{on}}$                                           | Drive current                                           | A             |  |  |

| $I_{ m S}$                                                | Source current                                          | A             |  |  |

| $I_{ m nW}$                                               | Substrate current flowing from the n-well               | A             |  |  |

| $I_{\rm spec_{\square}} = 2n\mu_0 C_{\rm ox} U_{\rm T}^2$ | Specific current per square with $n$ defined below      | A             |  |  |

| $I_{\text{spec}} = I_{\text{spec}_{\square}} W/L$         | Specific current                                        | A             |  |  |

| $i_{\rm d} = I_{\rm D}/I_{\rm spec}$                      | Normalized drain current                                | _             |  |  |

| $IC = i_{\rm d}$                                          | Inversion coefficient                                   | _             |  |  |

| Symbol                                           | Description                                            | Quantity/Unit                            |

|--------------------------------------------------|--------------------------------------------------------|------------------------------------------|

|                                                  | Charges                                                |                                          |

| $Q_{\mathrm{G}}$                                 | Gate charge density per unit area                      | $C/m^2$                                  |

| $Q_{ m f}$                                       | Fixed oxide-charge density per unit area               | $C/m^2$                                  |

| $Q_{ m si}$                                      | Total silicon charge density per unit area             | $C/m^2$                                  |

| $Q_{\mathrm{i}}$                                 | Inversion charge density per unit area                 | $C/m^2$                                  |

| $Q_{\mathrm{b}}$                                 | Depletion charge density per unit area                 | $C/m^2$                                  |

| $Q_{\rm spec} = -2nC_{\rm ox}U_{\rm T}$          | Specific charge density with $n$ defined below         | $C/m^2$                                  |

| $q_{\rm i} = Q_{\rm i}/Q_{\rm spec}$             | Normalized inversion charge density                    | _                                        |

| $q_{ m s}$                                       | Normalized inversion charge density at source          | _                                        |

| $q_{ m d}$                                       | Normalized inversion charge density at drain           | _                                        |

|                                                  | Small signals                                          |                                          |

| $G_{m}$                                          | Gate transconductance                                  | S=A/V                                    |

| $G_{ m ms}$                                      | Source transconductance                                | S=A/V                                    |

| $G_{ m md}$                                      | Drain transconductance                                 | S=A/V                                    |

| $G_{ m ds}$                                      | Output conductance                                     | S=A/V                                    |

| $A_{\rm v} = -G_{\rm m}/G_{\rm ds}$              | Intrinsic gain                                         | _                                        |

| $G_{\text{spec}} = I_{\text{spec}}/U_{\text{T}}$ | Specific transconductance                              | S=A/V                                    |

| $g_{\rm m} = G_{\rm m}/G_{\rm spec}$             | Normalized gate transconductance                       | _                                        |

| $g_{\rm ms} = G_{\rm ms}/G_{\rm spec}$           | Normalized source transconductance                     | _                                        |

| $g_{\rm md} = G_{\rm md}/G_{\rm spec}$           | Normalized drain transconductance                      | _                                        |

| $G_{\rm m} n U_{\rm T} / I_{\rm D}$              | Normalized transconductance efficiency                 | _                                        |

| $f_{t}$                                          | Transit frequency                                      | Hz                                       |

|                                                  | Radiation-related parameters                           |                                          |

| D                                                | Total ionizing dose (TID) referred to SiO <sub>2</sub> | rad                                      |

| $g_0$                                            | Charge pair density per unit volume per rad            | pairs/[cm <sup>3</sup> ·rad]             |

| $\rho$                                           | Material density                                       | g/cm <sup>3</sup>                        |

| $E_{ m p}$                                       | Electron-hole pair generation energy                   | eV                                       |

| $N_{ m h}$                                       | Initial hole yield                                     | $\mathrm{m}^{-2}$                        |

| $Q_{\mathrm{it}}$                                | Interface-trapped charge density per unit area         | $C/m^2$                                  |

| $D_{ m it}$                                      | Interface-trap density per unit area and energy        | $\mathrm{m}^{-2} \cdot \mathrm{eV}^{-1}$ |

| $g_{t}$                                          | Ground-state degeneracy factor                         | _                                        |

| $C_{\rm it} = q^2 D_{\rm it}$                    | Interface-charge capacitance                           | $F/m^2$                                  |

| $c_{\rm it} = C_{\rm it}/C_{\rm ox}$             | Normalized interface-charge capacitance                | _                                        |

| $lpha_{ m it}$                                   | Interface-trap-related mobility reduction factor       | $m^2 \cdot eV/C$                         |

| $Q_{ m ot}$                                      | Oxide-trapped charge density per unit area             | $C/m^2$                                  |

| $N_{ m ot}$                                      | Oxide-trap density per unit area                       | $\mathrm{m}^{-2}$                        |

| $ ho_{ m ox}$                                    | Oxide-trap density per unit volume                     | $m^{-3}$                                 |