# Networks of Coupled VO<sub>2</sub> Oscillators for Neuromorphic Computing

Présentée le 28 avril 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire des dispositifs nanoélectroniques Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### Elisabetta CORTI

Acceptée sur proposition du jury

Prof. E. D. N. Matioli, président du jury

Prof. M. A. Ionescu, Dr S. Karg, directeurs de thèse

Prof. S. Datta, rapporteur

Prof. B. Linares-Barranco, rapporteur

Prof. C. Enz, rapporteur

# Acknowledgements

This work would have never been possible without the guidance and the support of colleagues, family and friends which helped me walking this path and keeping up with the difficulties as well the success of this exciting field of research.

In particular, I would like to thank my supervisor **Dr. Siegfried Karg** for his support during the past three and a half years. I really appreciated how you followed me closely when I first joined the lab and dedicated so much of your time to train me in all the aspects of the work which were unfamiliar to me. At the same time, you gave me the freedom to try my own ideas and to learn from mistakes. Your guidance in this project was essential for all the progress we made.

My deepest gratitude goes to my manager, **Dr. Kirsten Moselund**, for establishing a collaborative and motivating environment in our group, as well as for the many technical discussions which greatly contributed to the results presented in this thesis. Thank you for your support and the sincere interest you take in creating an inspiring, friendly and also fun working atmosphere.

I would like to thank **Prof. Adrian Mihai Ionescu** for his academic supervision and valuable advice. The fresh perspective you brought to our exchanges has been a great contribution to the research.

Special thanks to **Dr. Bernd Gotsmann**, for all the time he dedicated to my project, for the sincere feedback on my work and for keeping my spirits up when I was facing this or that challenge in my research. Thank you also for all the coffee breaks you organized in our neighborhood in the home office times, they have been the highlight of my weeks while I was drafting this thesis.

Thank you to the members of the PhD jury, **Prof. Suman Datta** from Notre Dame Unviersity, **Prof. Christian Enz** and **Prof. Elison Matioli** from EPFL, **Prof. Bernabé Linares-Barranco** from the Seville Microelectronics Institute, which took the time to evaluate this work and for their helpful feedback.

I am grateful to the S&T department manager **Dr. Heike Riel** for closely following my research and providing valuable advice.

I would like to acknowledge the work of two formidable students, **Joaquin Cornejo** and **Federico Balduini**, which joined me in this path during the period of their Master's theses. You started your work at the beginning of the pandemic, but despite the confusion and delays

you were both able to convey extraordinary results in this research. It was a pleasure to work with you.

A special acknowledgment to **Abhishek Khanna** from Notre Dame University. During your short period in the lab you accelerated my work, shared with me long evenings in the lab, powered by low quality pizzas and coffees to see a very important part of the results coming to life.

I am also grateful to our collaborators, which provided me with the material to fabricate the devices presented in this thesis. Many thanks **Matteo Cavalieri** from EPFL for your PLD work. A very special thank to the team in Cambridge University, **Prof. John Robertson**, **Dr. Kham Niang**, **Guadong Bai** and **Haichang Lu**. Not only you have exchanged with me valuable ideas and samples, but you also hosted me as a visitor scientist in your lab. It was a great experience, a lot of good work and also quite some fun.

Thank you to our collaborators in the NeurONN project, for scientific discussions and the ideas they brought to the project. In particular, I am grateful to **Dr. Aida Todri-Sanial**, for additionally providing such an exceptional organization to the project. A sincere acknowledgment also to the other partners and in particular to **Corentin Delacour**, **Dr. Stefania Carapezzi**, **Prof. Maria J. Avedillo**, **Juan N. Martinez** and **Dr. Ahmed Nejim** for the insightful exchange and for the essential expertise they brought to the project.

I would like to acknowledge the partners in the Phase Change Switch project, for providing important insights on the material characteristics and the device processing.

Many successful ideas rise from discussions with experienced colleagues. I would like to thank **Dr. Bert Offrein** and **Dr. Abu Sebastian**, together with their teams in IBM for the multiple exchanges and the scientific input they provided me during the past three years.

This work would have not been possible without the combined effort of the engineers and scientists which provide support and take care of the numerous tools that are needed for our research. Special thanks to my colleague and friend **Marilyne Sousa**, for performing ellipsometry and TEM characterization on my samples. To **Ronald Grundbacher**, for setting up and optimizing the ALD deposition. To **Steffen Reidt**, for performing unconventional anneals in the PLD tool. To **Ute Dreschler**, **Dr. Diana Davila Pineda** and **Daniele Caimi** for all their advice and help in the cleanroom processes.

I was very lucky to be part of an amazing team of smart colleagues and friends at IBM. Thank you **Heinz**, for your technical input and for the discussions about technology and life. **Fabian**, **Federico** and **Nele**, thank you for your work on the SThM set-up and for the incredible characterization you provided on the devices. **Pengyan**, I am grateful for your work on the device simulations. I would like to thank **Clarissa** and **Cezar**, my two office mates, with whom I shared so many serious and fun discussions and to the other half of my lab, **Svenja**, **Preksha** and **Markus S.**, for the reciprocal support when our experiments failed and for cheering with me when results came out for a change. Thank you to my skilled colleagues and partners in crime in parties and adventures, **Philipp**, **Fabian**, **Morten**, **Tushar**, **Preksha** and **Andrea**, for the good times inside and outside work. A special acknowledgment to **Markus R.** for being present when he would have rather not, to **Daniel** for the young fresh air he brought to our lab and to **Simon** for the interesting experiments and conversations. Thank you to the friends and

colleagues **Noelia**, **Alan** and **Kasia**, for the travels, the ski adventures and the amazing dinners we had together.

Most importantly, I would like to acknowledge my family for being with me through thick and thin. In particular I thank my parents **Marialuisa** and **Maurizio**, **Nonna Rosanna** and my sister **Francesca**, for their continuous support through my long study path. Special thanks to our friends **Carla** and **Fabio**, for shipping mutliple packages of essential italian food which gave me the energy to write this thesis. Lastly, thank you to **Philipp**, for sharing this adventure with me and to all the friends in Italy and in other parts of the world, for being there for me.

Zurich, April 10, 2021

Elisabetta

## **Abstract**

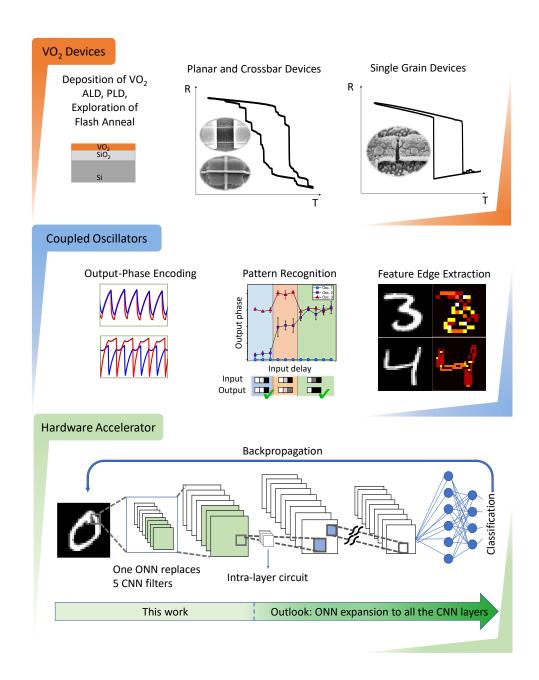

Neuromorphic computing is a wide research field aimed to the realization of brain-inspired hardware, apt to tackle computation of unstructured data more efficiently than currently done with standard computer architectures. Oscillatory neural networks are known for their associative memory capability, which enables to retrieve the information stored in the system from noisy or incomplete data. The development of phase-transition materials such as vanadium dioxide ( $VO_2$ ) allows to design compact relaxation oscillator units which can be coupled in frequency and phase to realize an oscillatory neural network in hardware. In this thesis, we investigate the oscillatory neural network technology from the realization of the basic oscillator components with  $VO_2$  to the exploitation of the coupled oscillators as analog filters in convolutional neural networks applications.

$VO_2$  phase-transition devices are realized in a CMOS compatible process in two geometries, a planar and a crossbar configuration. The impact of the polycrystallinity of the  $VO_2$  film on the insulator-to-metal transition of the device is analyzed; through the contacting of a single grain we demonstrate the realization of a  $VO_2$  device with a single, sharp phase transition.

The  $VO_2$  devices are connected in circuits to build networks of coupled oscillators. Through coupling with resistive and capacitive elements, experimental demonstrations of a 4- $VO_2$  coupled oscillator network is shown. The network encodes the input and output information in the relative phase of the oscillators. The associative memory capability of the system is used to extract features from hand-written digits. By expanding the network to a  $3\times3$  coupled oscillator system, we demonstrate in simulations how an oscillatory neural network can replace up to five digital filters in a convolutional neural network, retaining the same image processing capabilities.

**Keywords:** oscillatory neural network • vanadium dioxide (VO<sub>2</sub>) • relaxation oscillator • frequency locking • phase locking • associative memory • neuromorphic computing • convolutional neural networks • time encoded information

# Zusammenfassung

Neuromorphic Computing ist ein weites Forschungsfeld, das auf die Realisierung von hirninspirierter Hardware abzielt und dazu geeignet ist, unstrukturierte Daten effizienter als mit

derzeitigen Prozessoren zu berechnen. Oszillierende neuronale Netzwerke sind für ihre assoziativen Speicherfähigkeiten bekannt, die es ermöglichen, die im System gespeicherten

Informationen aus verrauschten oder unvollständigen Daten zu gewinnen. Die Nutzung von

Phasenübergangsmaterialien wie Vanadiumdioxid (VO<sub>2</sub>) ermöglicht den Entwurf kompakter

Relaxationsoszillatoreinheiten, die in Frequenz und Phase gekoppelt werden können, um ein

oszillierendes neuronales Netzwerk in Hardware zu realisieren. In dieser Arbeit untersuchen

wir die oszillierende neuronale Netzwerktechnologie von der Realisierung der grundlegenden

Oszillatorkomponenten mit VO<sub>2</sub> bis zur Nutzung der gekoppelten Oszillatoren als analoge

Filter in Anwendungen von faltenden neuronalen Netzwerken.

${

m VO_2}$  Phasenübergangsbauelemente werden in einem CMOS-kompatiblen Prozess in zwei Geometrien realisiert, einer planaren und einer crossbar-Konfiguration. Der Einfluss der Polykristallinität des  ${

m VO_2}$  -Films auf den Metall-Isolator-Übergang der Bauelemente wird analysiert. Durch die Kontaktierung eines einzelnen Kristallits demonstrieren wir die Realisierung eines  ${

m VO_2}$  Bauelements mit einem einzelnen, scharfen Phasenübergang.

Die  $\mathrm{VO}_2$  Bauelemente sind in Schaltungen verbunden, um Netzwerke gekoppelter Oszillatoren aufzubauen. Durch Kopplung mit resistiven und kapazitiven Elementen werden experimentelle Demonstrationen eines  $4\text{-}\mathrm{VO}_2$ -gekoppelten Oszillatornetzwerks gezeigt. Das Netzwerk codiert die Eingangs- und Ausgangsinformationen in der relativen Phase der Oszillatoren. Die assoziativen Speicherfunktionen des Systems werden verwendet, um Merkmale aus handgeschriebenen Ziffern zu extrahieren. Durch die Erweiterung des Netzwerks auf ein  $3\times3$ -gekoppeltes Oszillatorsystem zeigen wir in Simulationen, wie ein oszillatorisches neuronales Netzwerk verwendet werden kann, um bis zu fünf digitale Filter in einem faltendem neuronalem Netzwerk zu ersetzen, wobei die gleichen Bildverarbeitungsfähigkeiten beibehalten werden.

**Stichwörter:** Oszillierende neuronale Netzwerke • Vanadiumdioxid ( $VO_2$ ) • Relaxationsoszillatoreinheiten • Frequenz locking • Phase locking • assoziativen Speicherfähigkeiten • neuromorphic computing • convolutional neural networks • zeitcodierte Information

# **Contents**

| A  | cknov           | wledge | ements                                                  | iii |

|----|-----------------|--------|---------------------------------------------------------|-----|

| Al | ostra           | ct     |                                                         | vi  |

| Ζι | usam            | menfa  | ssung                                                   | ix  |

| Li | st of           | Public | ations                                                  | xii |

| Li | st of           | Figure | s and Tables                                            | xv  |

| Li | st of           | Acrony | /ms                                                     | xix |

| 1  | Intr            | oducti | on                                                      | 1   |

|    | 1.1             | The C  | Computational Challenge of Deep Learning                | 1   |

|    | 1.2             | Neuro  | omorphic Computing: an Overview of the State of the Art | 3   |

|    |                 | 1.2.1  | Biologically-Inspired Platforms                         | 3   |

|    |                 | 1.2.2  | Neuromorphic Accelerators for Neural Networks           | 4   |

|    |                 | 1.2.3  | Beyond Neural and Synaptic Behaviors                    | 5   |

|    |                 | 1.2.4  | Motivation for Oscillatory Neural Networks              | 6   |

|    | 1.3             | Aim o  | f the Thesis                                            | 8   |

| 2  | VO <sub>2</sub> | Oscill | ators: from the Material to the Applications            | 11  |

|    | 2.1             |        | dium Dioxide                                            | 11  |

|    |                 |        | $VO_2$ Fabrication                                      |     |

|    |                 |        | VO <sub>2</sub> Electrically-Triggered Transition       |     |

|    | 2.2             | _      | Relaxation Oscillators                                  |     |

|    |                 |        | Coupled Oscillators                                     | 21  |

|    | 2.3             | Oscill | atory Neural Networks                                   | 22  |

|    |                 | 2.3.1  | Hopfield Neural Network                                 | 23  |

|    |                 | 2.3.2  | Models of Oscillatory Neural Networks                   |     |

|    | 2.4             |        | nologies that Compute with Oscillators: an Overview     |     |

|    |                 | 2.4.1  | Materials and Devices for Oscillatory Neural Networks   |     |

|    |                 | 2.4.2  | Image Processing with Oscillators                       | 32  |

### **Contents**

|    | 2.5                       | Convolutional Neural Networks                                                          | 35  |  |  |  |  |  |

|----|---------------------------|----------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| 3  | 3 Experimental Methods 41 |                                                                                        |     |  |  |  |  |  |

|    | _                         | Device Fabrication                                                                     | 41  |  |  |  |  |  |

|    |                           | 3.1.1 Deposition Techniques                                                            | 41  |  |  |  |  |  |

|    |                           | 3.1.2 Raman Spectroscopy                                                               | 44  |  |  |  |  |  |

|    |                           | 3.1.3 Annealing Techniques                                                             | 46  |  |  |  |  |  |

|    |                           | 3.1.4 Device Processing                                                                | 49  |  |  |  |  |  |

|    | 3.2                       | Scanning Thermal Microscopy                                                            | 51  |  |  |  |  |  |

|    | 3.3                       | Device Model for Circuit Simulations                                                   | 53  |  |  |  |  |  |

| 4  | Cha                       | racterization of the Phase Transition in scaled VO <sub>2</sub> Devices                | 55  |  |  |  |  |  |

|    | 4.1                       | Characterization of VO <sub>2</sub> Planar Devices                                     | 55  |  |  |  |  |  |

|    |                           | 4.1.1 Characterization via Scanning Thermal Microscopy                                 | 59  |  |  |  |  |  |

|    |                           | 4.1.2 Simulation of Phase Transitions in Planar Devices                                | 61  |  |  |  |  |  |

|    | 4.2                       | Crossbar Devices                                                                       | 63  |  |  |  |  |  |

|    | 4.3                       | Single Grain Devices                                                                   | 65  |  |  |  |  |  |

|    | 4.4                       | Main Achievements                                                                      | 69  |  |  |  |  |  |

| 5  |                           | pled Oscillator Networks based on VO <sub>2</sub> Devices                              | 71  |  |  |  |  |  |

|    |                           | VO <sub>2</sub> Oscillators: Characteristic and Performances                           | 71  |  |  |  |  |  |

|    | 5.2                       | Coupled Oscillators                                                                    | 72  |  |  |  |  |  |

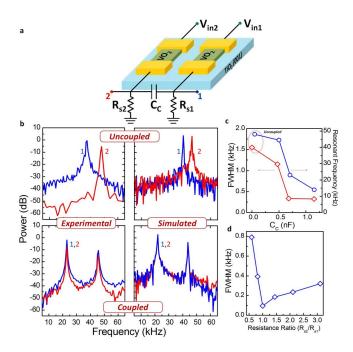

|    |                           | 5.2.1 Two Coupled Oscillators based on VO <sub>2</sub> Devices                         | 74  |  |  |  |  |  |

|    |                           | 5.2.2 Pattern Recognition with Three Coupled Oscillators                               | 78  |  |  |  |  |  |

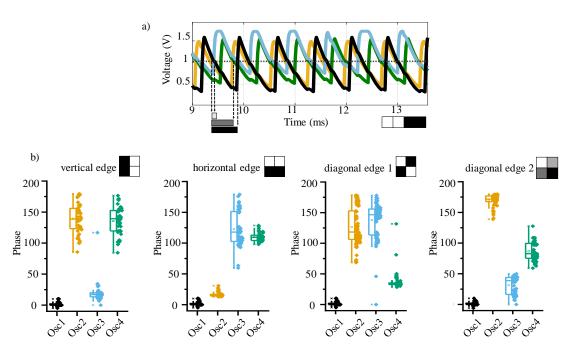

|    |                           | 5.2.3 Feature Edge Extraction with Four Coupled Oscillators                            | 81  |  |  |  |  |  |

|    | 5.3                       | Main Achievements                                                                      | 84  |  |  |  |  |  |

| 6  |                           | Coupled Oscillators as Filters in Convolutional Neural Networks                        | 85  |  |  |  |  |  |

|    | 6.1                       | VO <sub>2</sub> Coupled Oscillators as Analog Filters in Convolutional Neural Networks | 85  |  |  |  |  |  |

|    | 6.2                       | Backpropagation Algorithm applied to the ONN                                           | 88  |  |  |  |  |  |

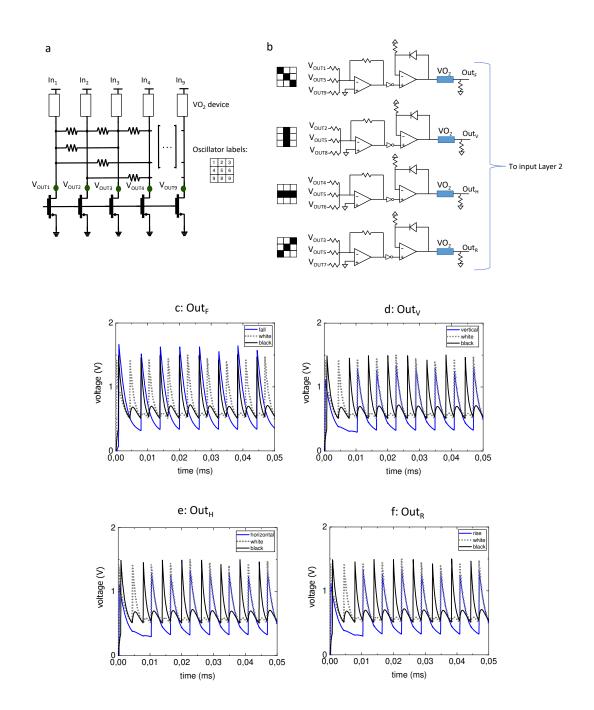

|    |                           | Phase-Detector Circuit for ONN Second Layer                                            | 90  |  |  |  |  |  |

|    | 6.4                       | Benchmark                                                                              | 93  |  |  |  |  |  |

|    | 6.5                       | Main Achievements                                                                      | 94  |  |  |  |  |  |

| 7  |                           | clusion and Outlook                                                                    | 95  |  |  |  |  |  |

|    | 7.1                       | Future Directions                                                                      | 99  |  |  |  |  |  |

| A  |                           | endix                                                                                  | 101 |  |  |  |  |  |

|    |                           | SThM Characterization                                                                  | 101 |  |  |  |  |  |

|    | A.2                       | Simulation of Multi-Grain Switching in VO <sub>2</sub> Devices                         | 103 |  |  |  |  |  |

| Re | fere                      | nces                                                                                   | 107 |  |  |  |  |  |

| Cı | ırricı                    | ulum Vitae                                                                             | 133 |  |  |  |  |  |

### **List of Publications**

Most of the results presented in this thesis have been published in peer-reviewed scientific journals. For the papers presented here, I planned the experiments, performed the majority of the experimental work and data analysis, and wrote the largest part of the manuscripts:

- <u>E. Corti</u>, J. A. C. Jimenez, K. Niang, J. Robertson, K. E. Moselund, B. Gotsmann, A. M. Ionescu and S. Karg, "Coupled VO<sub>2</sub> Oscillators Circuit as Analog First Layer Filter in Convolutional Neural Networks", *Frontiers in Neuroscience*, **15**, 19 (2020)

- <u>E. Corti</u>, A. Khanna, K. Niang, J. Robertson, K. E. Moselund, B. Gotsmann, S. Datta and S. Karg, "Time-Delay Encoded Image Recognition in a Network of Resistively Coupled VO<sub>2</sub> on Si Oscillators", *IEEE Electron Device Letters*, **41**(1), 686–693 (2020)

- <u>E. Corti</u>, B. Gotsmann, K. Moselund, A. M. Ionescu, J. Robertson and S. Karg, "Scaled resistively-coupled VO<sub>2</sub> Oscillators for Neuromorphic Computing", *invited paper: Solid State Electronics*, **168**, 107729, 2020

- <u>E. Corti</u>, B. Gotsmann, K. Moselund, I. Stolichnov, A. Ionescu and S. Karg, "Resistive Coupled VO<sub>2</sub> Oscillators for Image Recognition", *Proceedings of IEEE International Conference on Rebooting Computing (ICRC)* IEEE, p. 1-7 2018

In the scope of this thesis I filed 2 patent applications:

- <u>E. Corti</u> and S. Karg, "Feature Recognition with Oscillating Neural Networks,", *Filed at the United States Patent Office*, (2020)

- <u>E. Corti</u> and S. Karg, "Training of Oscillatory Neural Networks", *Filed at the United States Patent Office*, (2020)

### **List of Publications**

At the same time I contributed to several other projects, which are not included in this thesis. A continued collaboration within the NeurONN European Project resulted in the following manuscripts (in preparation):

- J. Núñez, M. J. Avedillo, M. Jiménez, J. M. Quintana, A. Todri-Sanial, <u>E. Corti</u>, S. F. Karg and B. Linares-Barranco, "Oscillatory Neural Networks using VO<sub>2</sub> based Phase Encoded Logic", *accepted in Frontiers in Neuroscience*

- J. Núñez, J. M. Quintana, M. J. Avedillo, M. Jiménez, A. Todri-Sanial, <u>E. Corti</u>, S. Karg and B. Linares-Barranco, "Insights into the Dynamics of VO<sub>2</sub> Coupled Oscillators for ONNs", accepted in IEEE Transactions in Circuits and Systems II

- A. Todri-Sanial, S. Carapezzi, M. Abernot, T. Gil, <u>E. Corti</u>, S. F. Karg, J. N. Martinez and M. J. Avedillo, "How Frequency Injection Locking Can Train Oscillatory Neural Networks to Compute in Phase", *under review*

- S. Carapezzi, <u>E. Corti</u>, S. Karg and A. Todri-Sanial, "Understanding of Self-Heating and Resistive Switching in VO<sub>2</sub> Devices: A TCAD Approach", *under review*

# **List of Figures and Tables**

| 1.1  | morphic Computing Landscape                                                                              | 6  |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.1  | Properties of Vanadium Oxides                                                                            | 11 |

| 2.2  | $VO_2$ structural phase change                                                                           | 12 |

| 2.3  | $VO_2$ band diagram                                                                                      | 13 |

| 2.4  | Representation of a Peierls instability                                                                  | 15 |

| 2.5  | Current-voltage characteristic of a $VO_2$ device                                                        | 17 |

| 2.6  | Oscillator based on a VO <sub>2</sub> Device                                                             | 19 |

| 2.7  | Frequency-locking of two coupled oscillators                                                             | 22 |

| 2.8  | Periodic attractor in an oscillatory neural network                                                      | 25 |

| 2.9  | Image recognition performed with a system of coupled oscillators                                         | 27 |

| 2.10 | Fully-Connected and Frequency-Modulated Oscillatory Neural Networks $$                                   | 28 |

| 2.11 | Benchmark of oscillators technologies                                                                    | 31 |

| 2.12 | Image filtering operations performed with ONNs                                                           | 34 |

| 2.13 | $Summary\ of\ demonstration\ of\ image\ filtering\ operations\ performed\ with\ ONNs$                    | 35 |

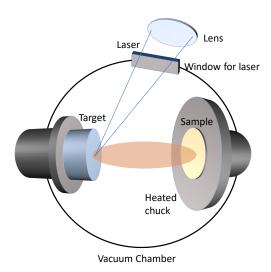

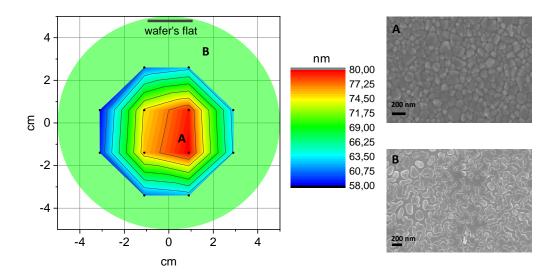

| 3.1  | Scheme of a PLD system                                                                                   | 42 |

| 3.2  | Characteristics of $VO_2$ PLD films                                                                      | 43 |

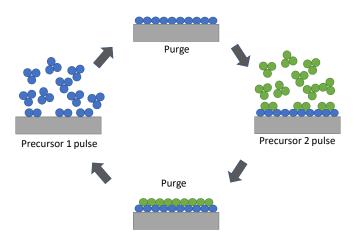

| 3.3  | Scheme of an ALD process                                                                                 | 44 |

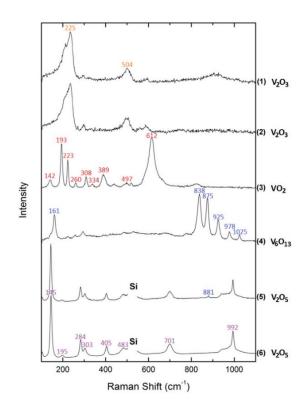

| 3.4  | Raman Spectra of Vanadium Oxides                                                                         | 45 |

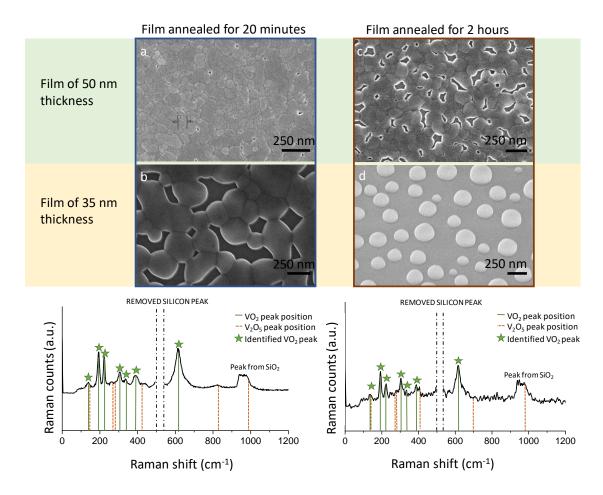

| 3.5  | Effect of the Annealing Time on $VO_2$ ALD Films                                                         | 46 |

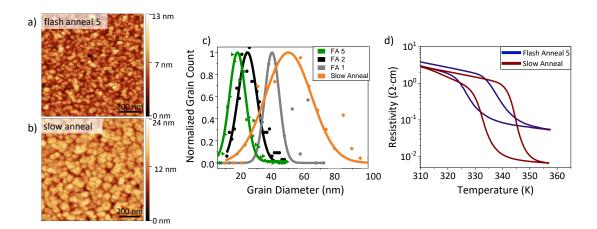

| 3.6  | Summary of flash anneal parameters                                                                       | 48 |

| 3.7  | Comparison between flash annealed and slow annealed $VO_2$ films $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ | 48 |

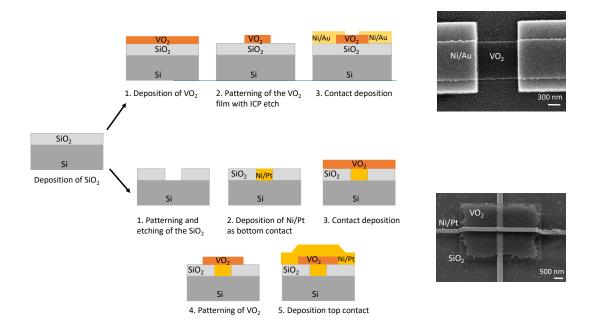

| 3.8  | Processing of VO <sub>2</sub> Planar and Crossbar Devices                                                | 50 |

### **List of Figures and Tables**

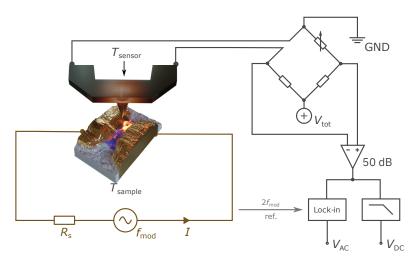

| 3.9  | Simplified schematic of the SThM setup                                                      | 52 |

|------|---------------------------------------------------------------------------------------------|----|

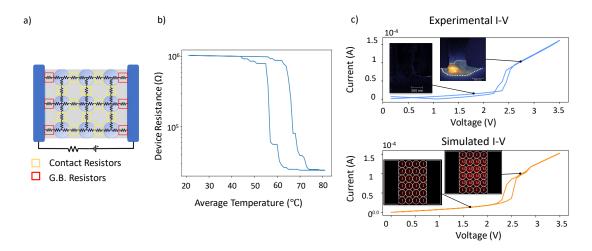

| 3.10 | $VO_2$ circuit model employed in simulations $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 54 |

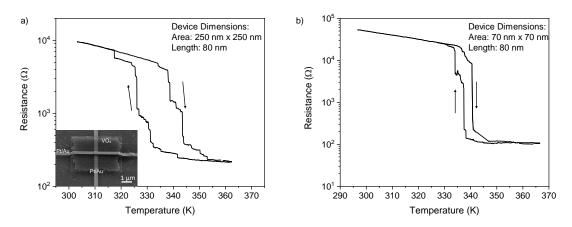

| 4.1  | Hysteresis curves of VO <sub>2</sub> planar devices                                         | 56 |

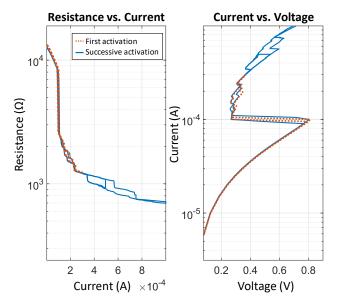

| 4.2  | IV curve of a $VO_2$ planar device                                                          | 58 |

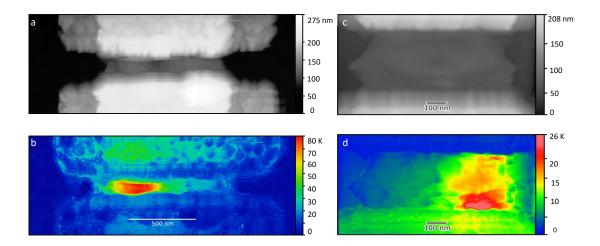

| 4.3  | SThM imaging of the filament formation in the IMT of $\mbox{VO}_2$ planar devices           | 59 |

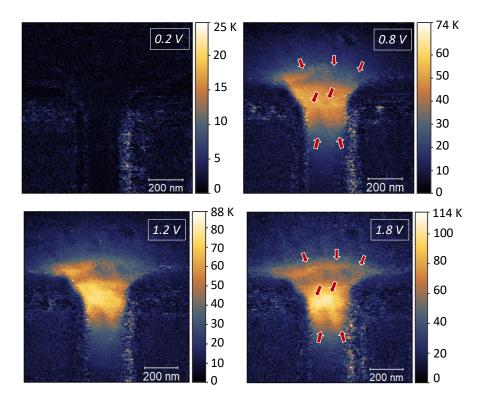

| 4.4  | Evolution of the metallic filament in a VO <sub>2</sub> planar device for increasing bias   |    |

|      | voltage                                                                                     | 60 |

| 4.5  | Simulation of a planar VO <sub>2</sub> device                                               | 62 |

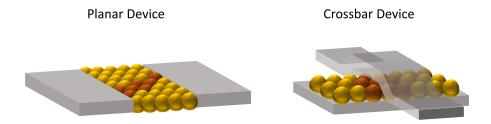

| 4.6  | Illustration of a planar and a crossbar device                                              | 63 |

| 4.7  | Hysteresis curve of crossbar devices with different dimensions                              | 64 |

| 4.8  | I-V characteristic of a crossbar device                                                     | 64 |

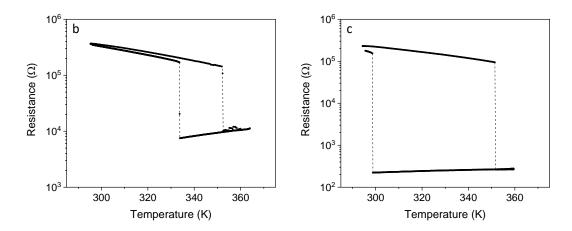

| 4.9  | Electrical characterization of a $VO_2$ single-grain device $\ldots \ldots \ldots \ldots$   | 66 |

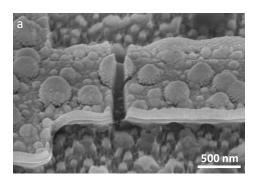

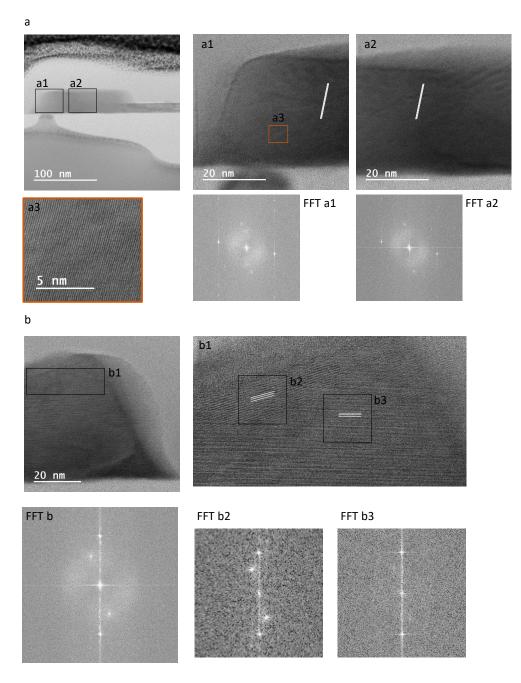

| 4.10 | TEM Characterization of a VO $_2$ single-grain device $\hdots$                              | 67 |

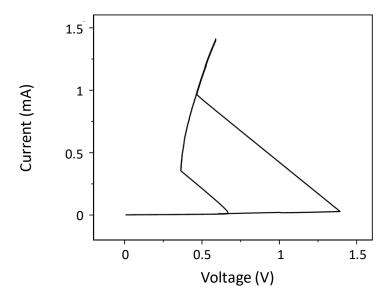

| 4.11 | IV curve of a VO $_2$ single-grain device                                                   | 68 |

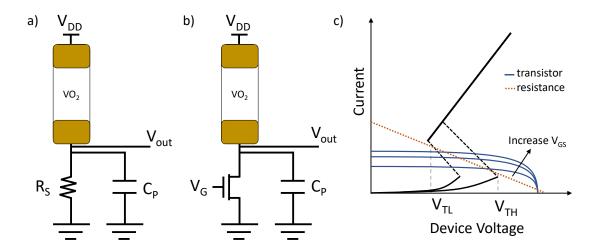

| 5.1  | Circuit realizations of a single oscillator unit                                            | 72 |

| 5.2  | Characteristics of the best-performing devices                                              | 73 |

| 5.3  | Schematic of the oscillatory neural network circuit                                         | 74 |

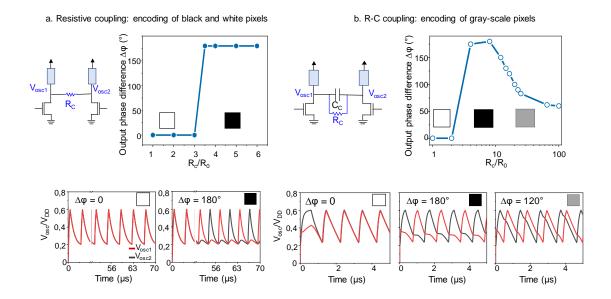

| 5.4  | Resistively-Coupled Oscillators Circuit                                                     | 75 |

| 5.5  | Experiment of phase encoding in a two-resistively-coupled oscillators circuit $$ .          | 75 |

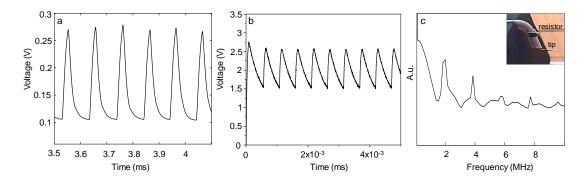

| 5.6  | Effect of $VO_2$ multi-step switching on the oscillating waveform                           | 76 |

| 5.7  | Grey-scale pixel encoding in two-coupled oscillators                                        | 78 |

| 5.8  | Time-Delay inference with two-coupled oscillators                                           | 79 |

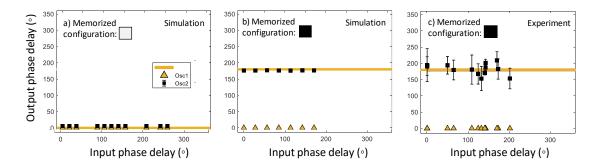

| 5.9  | Pattern recognition with 3-coupled oscillators                                              | 80 |

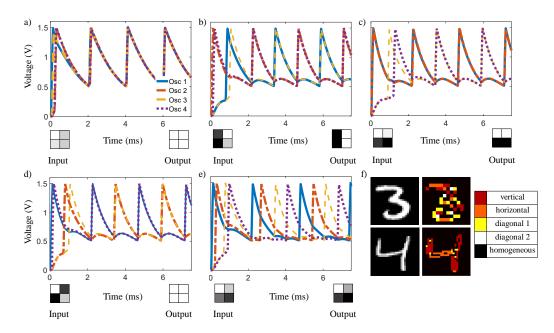

| 5.10 | Edge extraction experiments with 4-coupled oscillators                                      | 81 |

| 5.11 | Edge extraction simulations with 4-coupled oscillators                                      | 83 |

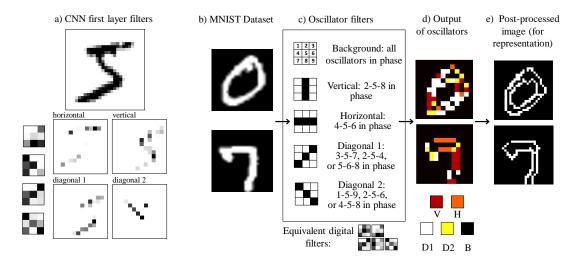

| 6.1  | Structure of the CNN under consideration                                                    | 87 |

| 6.2  | A single ONN performs the filtering actions of 5 digital CNN filters                        | 87 |

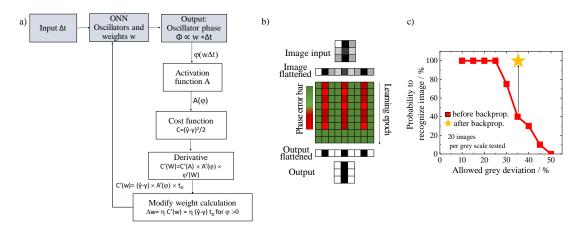

| 6.3  | Schematic of the backpropagation algorithm for ONNs                                         | 89 |

| 6.4  | Phase detector and connector circuit between two ONN layers                                 | 92 |

| 7.1  | Summary of results                                                                          | 97 |

| 7.2  | Summary of the achievements of this work compared to the state of the art                   | 99 |

### **List of Figures and Tables**

| A.1 | IV Characteristic of a device measured with the SThM $ \ldots  \ldots  \ldots  \ldots  \ldots  \ldots$ | 102 |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| A.2 | SThM Measurement of the Metallic Filament Expansion in a VO $_2$ Device $\ .\ .\ .$                    | 102 |

| A.3 | Example of discrimination between metallic and insulating paths in $VO_2$ planar                       |     |

|     | devices with SThM characterization                                                                     | 104 |

| A.4 | Parameters for the simulation of VO <sub>2</sub> granular devices                                      | 105 |

# **List of Acronyms**

| ASIC | application-specific integrated circuit | MEMS | micro electro-mechanical<br>system        |

|------|-----------------------------------------|------|-------------------------------------------|

| AFM  | atomic force microscopy                 | MIT  | metal to insulator transition             |

| ALD  | atomic layer deposition                 | NEMS | nano electro-mechanical system            |

| CMOS | complementary metal-oxide-              | ONN  | oscillatory neural network                |

|      | semiconductor                           | PCM  | phase change memory                       |

| CNN  | convolutional neural network            | PLD  | pulsed laser deposition                   |

| CPU  | central processing unit                 | RAM  | random access memory                      |

| DL   | deep learning                           | RO   | ring oscillator                           |

| DNN  | deep neural network                     | RRAM | resistive random access memory            |

| DOM  | degree of match                         | R-T  | resistance temperature                    |

| DTC  | digital to time converter               |      | characteristic                            |

| FA   | flash anneal                            | SEM  | scanning electron microscopy              |

| FC   | fully-connected                         | SNN  | spiking neural network                    |

| FFT  | fast Fourier transform                  | STDP | spike-timing-dependent plasticity         |

| FM   | frequency modulated                     |      |                                           |

| FPGA | field-programmable gate array           | STEM | scanning transmission electron microscopy |

| GPU  | graphics processing unit                | SThM | scanning thermal microscopy               |

| ICP  | inductively coupled plasma              | STO  | spin torque oscillator                    |

| IMT  | insulator to metal transition           | TDC  | time to digital converter                 |

| I-V  | current voltage characteristic          | TEM  | transmission electron microscopy          |

|      |                                         |      |                                           |

$\begin{array}{ll} \textbf{TEMAV} & \textbf{tetrakis}(\textbf{ethylmethylamino}) \textbf{-} \\ & \textbf{vanadium} \end{array}$

VTOP

vanadyltriisopropoxide

# 1 Introduction

### 1.1 The Computational Challenge of Deep Learning

The 21st century, with the development of advanced electronic technologies, has seen an exponential increase in the amount of data that is daily created and processed worldwide. A recent report from the International Data Corporation [1] predicts that 59 zettabytes of data will be produced, copied or consumed only this year. With the growth of edge computing, it is estimated that in the next three years we will further create more data than what has been generated in the last thirty years world wide [1]. In parallel to the extended availability of information, machine learning algorithms have arisen with the aim to extract relevant knowledge from diverse and unstructured data. These algorithms, which rely on multi-level layered networks and back propagation training, have been devised theoretically in the 80's. However, as they require high computational power and a large amount of data for training, they have been only recently brought to commercial use. The advances in hardware technologies, which enabled to have faster, more powerful computing machines, together with the increased data-availability, allowed the exploitation of machine learning, and in particular, deep neural networks to perform data analysis and information extraction that was not easily implementable in the past. Therefore, the need of processing the spectacular amount of data available today required the employment of deep-learning techniques. At the same time, deep learning would have never been possible without the availability of large datasets [2].

Deep learning is a branch of machine learning which uses brain-inspired concepts to perform learning of a task on a machine. Deep learning nowadays powers many aspects of our society: it is used in web searches to select relevant results, content filtering and personalized advertisements in social networks, facial recognition and speech recognition. Moreover, it is successfully employed also for aiding the synthesis of new drugs [3], for diagnostics [4] and cybersecurity [5]. These algorithms are based on a representation-learning method for which raw data is fed into a network. The network automatically computes and discovers the set of features needed to perform a classification or a detection task [6]. The deep neural network algorithms are constructed on a set of subsequent layers, which are composed by

simple, non-linear modules. Each module transforms the raw data from the previous level, performing a weighted sum of the various inputs, which on a high level resembles the accumulation of spikes from the incoming synapses performed by neurons in the human brain. After undergoing a non-linear activation function, the output of each layer results in a more abstract representation of the information; the last module structures the output information as, for example, a classification vector for an image classification application. The training of the network consists in the tuning of the weights between the network nodes, usually performed by a back-propagation algorithm. Per definition, the higher the number of layers in the network, the deeper the network is. It has been shown that deeper networks perform with better accuracy than shallow networks [7]. Naturally, the bigger the network, the higher is the number of weights to be trained. State-of-the-art deep neural networks, such as the VGG [8] or ResNet [9] architectures, comprise hundreds of layers and millions of weights [10]. The training of such networks becomes extremely energy and time consuming and requires to run on powerful or specialized hardware, such as graphic unit cards (GPUs) or field programmable gate arrays (FPGA). The success of GPUs as a platform to run neural network algorithms is found in the parallelization of the basic operation behind neural networks computation, the vector-matrix multiplication [11]. The best performing NVIDIA GPU, the Tesla A100, released in May 2020 with a 7 nm transistor technology, can operate at 312 GFLOPS/W for singleprecision floating-point data format. It is reported that a ResNet-101 (where 101 refers to the number of layers in the network) can be trained on the ImageNet dataset [12] in about 5 hours using 8 of such GPUs [13], for a total power consumption of 16 kWh. This power consumption is almost four times what an European household needs in average for one day [14] and can increase steeply when the training is performed on older generation hardware platforms [15].

One of the major limitations of standard computer architectures in performing deep learning computation is the so-called von Neumann bottleneck, that results from the physical separation between the memory and the computation units. The imbalance arising from the difference between the speed of the computation and the speed of data retrieval from the Random Access Memory (RAM), causes the processor to remain idle during the time needed to access the RAM or the cache memories [16, 17, 18, 19]. Moreover, the access to the memory is also responsible for a high power consumption [20]. For each operation in a deep neural network, the data to be processed, together with the connection weights of the layers, need to be transferred from the memory to the computational unit. The result of this operation is then moved back to the memory. These algorithms require therefore an extensive usage of memory resources, which contributes to increase the time needed for performing the computation.

In comparison, the human brain can perform tasks as recognition and classification much more efficiently than modern processors. Counting around  $10^{10}$  neurons and  $10^{15}$  synapses, the massively parallel, plastic structure of the brain serves as an inspiration to design novel hardware architectures, or neuromorphic chips, which are devised to bring the memory and the computation unit close together, with the aim of increasing the computing performance.

### 1.2 Neuromorphic Computing: an Overview of the State of the Art

The concept of neuromorphic computing was first proposed by Carver Mead in 1990 [21] and relies on using analog electronic circuits and systems to mimic the biological architecture of the human brain. Multiple approaches to realize specialized hardware for neuromorphic computing applications are currently under investigation, with the aim of designing a highly parallel, interconnected and reconfigurable system which does not suffer from the separation between computational and memory unity. In [11], Kendall et al. have identified 10 characteristics for a successful neuromorphic hardware: the neuromorphic system should be highly parallel (1) and perform in-memory computing (2), therefore storing the information next to the computational units; it should perform analog, low precision but noise resilient computation similarly to the human brain (3); therefore, it should be accepted that its output will be a probabilistic solution (4) and should allow for mistakes produced by causality (5); plasticity (6) is needed to reconfigure the state of the system and enable learning (7); non-linearity (8) is essential to reproduce neural network behaviors; finally the system should be highly scalable (9) and implement sparsity (10) of the neuron-to-neuron connections. Building a system that respects all these characteristics is very challenging and there is no clear direction on which architecture is ultimately more apt to embed the expectation of neuromorphic hardware. Neuromorphic engineering is a very wide research field, featuring thousands of contributions which often follow diverging paths. The research attention nowadays spans from new systems and architecture designs, to the re-thinking of silicon based technology, in favor of novel materials and devices which offer more flexibility for an analog approach to computing [22, 23]. One common ground among neural network algorithms and the various computing platforms, including the oscillating neural network concept discussed in this thesis, is the original inspiration to the massively-parallel architecture of the brain. Following the steps of [24, 11], we distinguish between research projects that aim to build hardware accelerators for deep neural networks and those more directly inspired by neuroscience.

### 1.2.1 Biologically-Inspired Platforms

The primary goal of biologically-inspired platforms is the emulation of large-scale biological neural networks. These platforms often rely on the hardware implementation of spiking neural networks (SNNs), in which the information is communicated through asynchronous and sparse binary events, or spikes, between neurons [25]. The neurons are connected via synaptic weights, whose value can be tuned during the training of the SNN through the spike-timing dependent plasticity (STDP) concept [26, 27]: a synaptic connection between two neurons is strengthened when the post-synaptic neuron spikes after the pre-synaptic neuron; vice versa, it is weakened when the post-synaptic neuron spikes before the pre-synaptic one. With STDP, contrary to what happens in deep neural networks (DNNs), it is possible to implement unsupervised learning; however, the STDP-based learning architectures so far devised are not as reliable as the supervised learning implemented with the backpropagation algorithm in DNNs [28].

Many realization of SNNs have been developed with standard CMOS technology, offering prototypes containing millions of neurons and synapses. Between the most complex realizations, we mention IBM's True North chip in 2014, counting one million neurons and 256 million synapses [29]; the SpiNNaker system, which counts low power ARM cores to perform real time simulations of SNNs [30, 31]; Loihi from Intel [32, 33], which counts 130'000 neurons and 130 million synapses. Even though the primary purpose of these implementations is the emulation of biological networks, they are also increasingly considered as accelerators for deep neural networks algorithms, even though so far they demonstrated lower accuracy than DNNs running on standard GPU hardware [24, 34, 35, 36, 37].

Special attention is also given to the realization of the single neuron or synapse unit [38, 27]. Many efforts have been carried out to design neuron models in CMOS technology, spanning from biologically-plausible designs [39, 40] to simpler compact models [41, 42]. With CMOS technology, multiple transistors are usually required to implement a spiking element. As an alternative, emerging technologies have been proposed, which can reproduce the spiking behavior with single compact components, from electrochemical metallization neurons [43, 44], to resistive random access memory (RRAM) technologies [45, 46], to volatile phase-transition oxides neurons [47, 48]. Similarly, nanoscale emerging memory technologies which can encode multiple memory states have been studied to realize the synapses. Resistive RAMs [49, 50], phase change memories (PCM) [51], and magneto-resistive random-access memories (MRAM) [52] have the potential to improve the circuit integration density and to greatly reduce the power dissipation in neuromorphic systems [53, 54].

### 1.2.2 Neuromorphic Accelerators for Neural Networks

As mentioned before, in contrast to SNNs, DNNs lack of biological realism, favouring linear algebra techniques of vector-matrix multiplication combined with non-linear activation functions to compute. They are based on supervised learning through back-propagation techniques, which require large, labelled datasets and benefit from the highly parallel matrix multiplication techniques offered by modern GPUs. The second branch of neuromorphic engineering is devoted to the design of neuromorphic accelerators, which are fast, energy efficient platforms specialized for DNN algorithms and able to bridge the physical separation between the memory and the processor units.

From an architecture point of view, many accelerators have been produced bringing the computational units next to the memory, therefore increasing the bandwidth between CPU and the storage units [55]. In the past, the efforts of realizing in-processing memory by positioning dynamic RAMs and CPU close together have been hindered by the technological challenge of bridging the manufacturing differences between the processes utilized to realize them [56]. Recent advances in 3-D memory stacking pose a promising route in this direction [57, 58].

One of the most encouraging emerging concepts for neural networks hardware accelerators consists in implementing in-memory computing with memristive devices (RRAM, PCM,

MRAM). The idea comes from the consideration that analog resistive memory elements can perform the multiply-accumulate operations, which are at the heart of DNNs, exploiting the physical attributes of nanoscale devices. By building a crossbar array of memristive devices, the multiply operation can be performed at the crosspoint of each memory element by Ohm's law; similarly, the summation can be computed through the sum of currents following Kirchhoff's first law, as explained in [28]. Therefore, the memory itself, while storing the information, can also perform the computation. By avoiding the movement of data, it is expected to allow for a significant reduction of the power consumption and an increased computation speed [59, 60]. The entrance to the market of this technology is currently impeded by problems like non-linear conductance response, limited dynamic range, variability and drifts, which hinder the mapping of DNNs weights and the recognition performances of such platforms [59, 61, 62]. However multiple efforts are carried out to allow scaling of memristive arrays to large dimension [63] and to design more fault-tolerant approaches for mapping DNNs in these accelerators [64].

### 1.2.3 Beyond Neural and Synaptic Behaviors

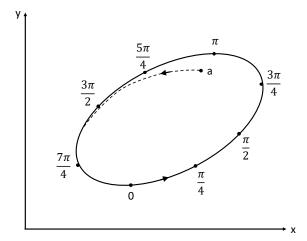

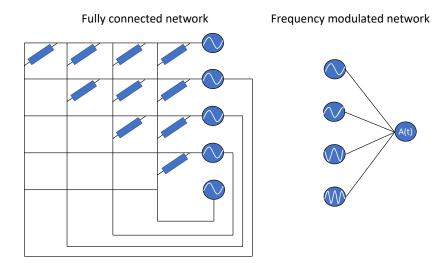

Parallelism and in-memory computation are key ingredients in neuromorphic computing. To build a memory platform capable to perform also computation, it is of interest to understand how the biological memory works. In particular, it has been demonstrated that rhythmic firing of neurons is connected to long-term information processing in the memory [65, 66]. Following this observation, algorithms have been designed that use the evolving dynamics of non-linear systems to perform computation. In particular, Hopfield in 1980s proposed a recurrent, fully-connected network based on the collective behavior of simple non-linear elements (neurons) to perform several tasks, including image recognition [67]. This network has the unique function of possessing an associative memory, that can be programmed by tuning the connection weights between the neurons. The associative memory is able to identify accurately objects (or input electrical signals) even if they are contaminated by noise [68]. One of the possible realization of such a memory system is through the exploitation of the frequency and phase synchronization of coupled oscillators [69, 70]. Designing an Oscillatory Neural Network (ONN) in hardware is interesting as it yields the advantages of utilizing the same devices that are storing the patterns to perform the computing, therefore representing another kind of in-memory computing platform. Second, the nature of the associative memory provides a more robust way of pattern recognition compared to algorithms based on contentaddressable memories, as it is highly resilient to input pattern distortion and noise [71]. Figure 1.1 attempts to put into context the research of ONN hardware with the major players in neuromorphic computing discussed above. Coupled oscillators systems are traditionally researched as hardware computing platforms for Oscillatory Neural Networks. In this work, we will bring the research a step forward, and investigate the possible exploitation of the associative memory of coupled oscillators as hardware accelerators for convolutional filters in neural networks.

### **Neural Network Algorithms** Hardware Accelerators Biologically-inspired Platforms In-Memory **Deep Learning** Computing for Vector-Convolutional Spiking Neural Networks Matrix-Multiplication Training: Neural Devices: Novel Networks Synapses: Novel Neurons: non-linear memory devices devices (metal-(MRAM, RRAM, (MRAM, RRAM, PCM...) insulator transition. negative differential Enabled by Linear Training: STDP resistance...) Algebra Processors Other (CMOS (GPU, FPGAs, ASIC) based etc...) Other CMOS-based **Recurrent Neural Coupled Oscillators** demonstrators: Loihi, Networks: TrueNorth... Devices: Novel oscillatory devices Hopfield NN and Other (transition-metal oxides, STOs, VO<sub>2</sub>...) Oscillatory NN Training: Hebbian Learning Rule Training: Hebbian Learning Rule

**Brain-Inspired Computing**

# **Figure 1.1** | Brain-inspired computing is a wide technological field which comprises the design of neural networks algorithms and the realization of neuromorphic computing hardware. Neuromorphic computing platforms can be classified in hardware accelerators for neural network applications and biologically-inspired systems. An important example in the first category is the development of inmemory computing concepts such as the crossbar arrays for vector-matrix multiplication discussed in the previous section. The research of coupled oscillator hardware for ONNs also falls under this category. In particular, a principal investigation of this thesis concerns the exploitation of ONNs for convolutional neural networks applications. Spiking neural networks belong instead to the biologically-inspired platforms, which more closely mimic the human brain behavior. The neuromorphic computing field is however much more complex and varied than what exposed in this brief discussion and showed in this figure.

Apart from pattern retrieval, other problems can be successfully tackled by computing with Hopfield neural networks and oscillatory devices. For example, networks of chaotic oscillators can solve constrained optimization problems better than many state-of-the-art GPUs or ASIC designs [72]. In other works, it was shown that coupled oscillators can solve NP-hard combinatorial optimization problems such as vertex graph coloring [73] and the travelling salesman problem [74], or can be used as an Ising machine [75].

### 1.2.4 Motivation for Oscillatory Neural Networks

Compared to the more mature platforms described in the previous sections, the realization of neuromorphic computing hardware based on coupled oscillator technology is still in the first stage of development, and presents numerous challenges. In order to build an associative memory based on oscillators, it is necessary to build a network of oscillators, which can be synchronized with tunable coupling elements. Until now, image recognition with coupled oscillators requires relatively large networks, with many tunable interconnecting elements [76]. This demands for material and device research in order to fabricate reliable

oscillating devices, which can work over a high number of cycles and have low device-to-device variability. The attractiveness of oscillatory neural networks largely depends on designing a suitable oscillator as a building block. Even though they were invented more than 40 years ago, the research on ONNs has only recently gained momentum thanks to the advances in nanoscale device technology, which now allow to realize very compact, energy efficient oscillators based on the non-linearity of novel material such as phase-transition materials [77, 78, 79] or spintronic nano-devices [80, 81, 76]. It is argued that the physical realization of the oscillators is determinant for their success in real-life applications [82]. Between the various technologies, oscillators realized with the phase-change material vanadium dioxide (VO<sub>2</sub>) have been widely researched for ONN applications [78, 48, 83, 84]. VO<sub>2</sub> presents several characteristics that make it one of the top candidate for oscillatory neural network technology: it shows a phase transition with a large jump between the insulating and the metallic state [85]; the phase transition happens near room-temperature, which is an important requirement for hardware applications; the phase transition can be triggered by an electrical stimuli [86] and it has been proven to be ultra-fast [87]; finally, VO2 oscillators can be coupled with standard electrical components, such as capacitors [78].

Given the early stage of the research, it is challenging to precisely state the advantage of this technology compared to other very promising neuromorphic computing implementations. Almost no benchmarks have been drawn between oscillator-based computing versus other digital or analog solutions so far. As mentioned in [82], there are several reasons why researching this technology is interesting:

- Firstly, oscillatory neural networks are noise-tolerant: their associative memory is resilient to noisy or distorted input.

- Moreover, they allow for computing with the synchronization time or with the relative phase of the oscillators, which can be an advantage compared to systems working with a very scaled voltage power supply as they do not use the amplitude of the electrical variables of the system to process information.

- Lastly, they can be flexibly used for a wide range of possibly disruptive applications, from pattern retrieval to the solving of NP-hard problems.

Ultimately, networks of coupled oscillators require still extensive research spanning between various fields: from the materials and device, to fabricate reliable, power efficient oscillators; to the design of circuit for the interconnection and the read-out of the input and out signal; to the algorithms and computational models, to adapt them to the circuit and device technologies and to allow for practical fast, power efficient applications of these networks.

### 1.3 Aim of the Thesis

The scope of this thesis is to demonstrate that systems of coupled oscillators can be used as hardware accelerators for neural network algorithms. With specific attention to convolutional neural networks, we aim to demonstrate how the associative memory capabilities of an oscillatory neural network can be used to perform different filtering actions on an image, exploiting the fault-tolerant, time-encoded information processing of the oscillatory system.

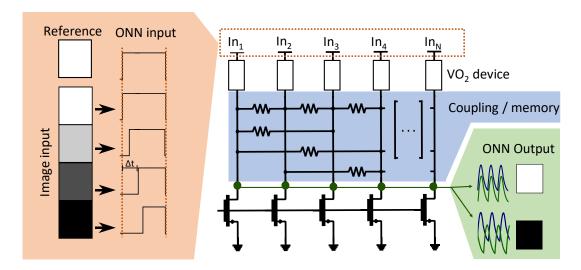

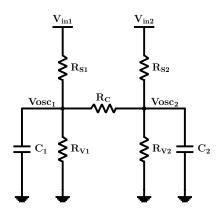

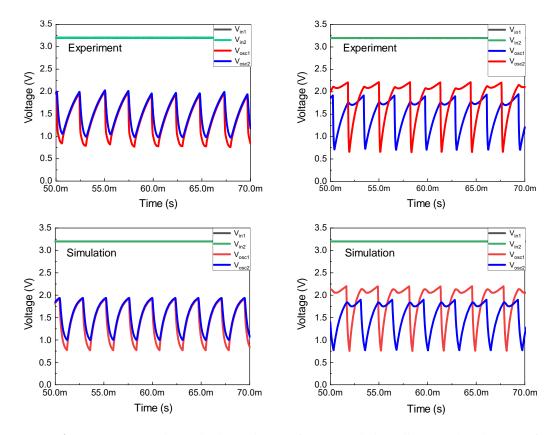

This work combines the research of a novel oscillatory device, based on the phase change material vanadium dioxide (VO<sub>2</sub>), with the circuit implementation of small networks of coupled oscillators. Starting from the realization of VO<sub>2</sub> devices, we explore their integration on a silicon platform and the scaling of their dimensions down to 70 nm. The phase-transition of the film in planar and crossbar devices is investigated, with special attention to the characteristic of the transition in the polycrystalline material and its impact on the device-to-device variability. We explore the frequency and phase synchronization of the compact oscillators with a coupling scheme realized with simple electrical components. In particular, we focus on the realization and encoding of the system memory with resistive coupling elements, which in perspective can be realized with the emerging memory technologies exploited for in-memory computation (RRAM, PCMs). With the aim of realizing a computing unit which works entirely through the timing of the electrical signals, we investigate the injection of the input information based on the relative delays between the voltage signals of the devices, rather than with amplitude-encoded schemes. Finally, we simulate a network design which can be integrated as an analog filter in convolutional neural networks, replacing several digital convolutional filters. The convolutional neural network accelerated by the oscillatory neural network hardware is tested on an image classification task, but can ultimately be flexibly used for other applications employing convolutional neural networks.

The thesis is structured as follows:

### **Chapter 1: Introduction**

In the first chapter the topic has been introduced and placed in a wider scientific context.

### Chapter 2: VO<sub>2</sub> Oscillators: from the Material to the Applications

The second chapter presents a theoretical overview of oscillatory neural network technology based on  $VO_2$  devices. Starting from the analysis of the material, we discuss the origin of the phase transition and how to exploit it in order to realize compact relaxation oscillators, which can be coupled in frequency with simple electrical connections. We then offer a brief overview of the oscillatory neural networks, from the mathematical theory of their associative memory capabilities, to the available demonstrations of coupled oscillator computing. Finally, we introduce convolutional neural network algorithms and their application for image classification tasks.

### **Chapter 3: Experimental Methods**

In this chapter the experimental methods which are relevant for this thesis are presented. Starting from the deposition of  $VO_2$  thin films, we discuss the fabrication and characterization techniques of planar and cross-bar devices, including a scanning thermal microscopy technique for the mapping of the temperature inside the device. We briefly present the device model used for the circuit simulation.

### Chapter 4: Characterization of the Phase Transition in Scaled VO<sub>2</sub> Devices

In this chapter the phase transition in planar and crossbar  $VO_2$  devices is presented. Through electrical characterization and scanning thermal probe microscopy technique the impact of the polycrystallinity of the  $VO_2$  film deposited on a  $SiO_2/Si$  substrate is analyzed. Finally, we present the realization of a sharp transition in a single-grain device.

### Chapter 5: Coupled Oscillator Networks based on VO<sub>2</sub> Devices

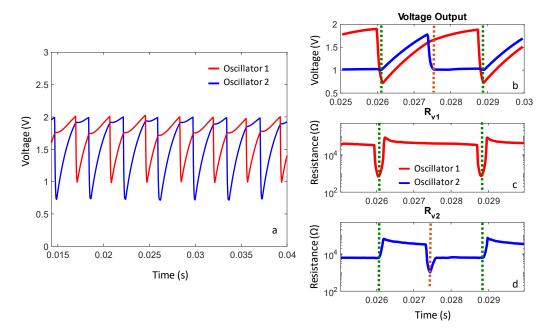

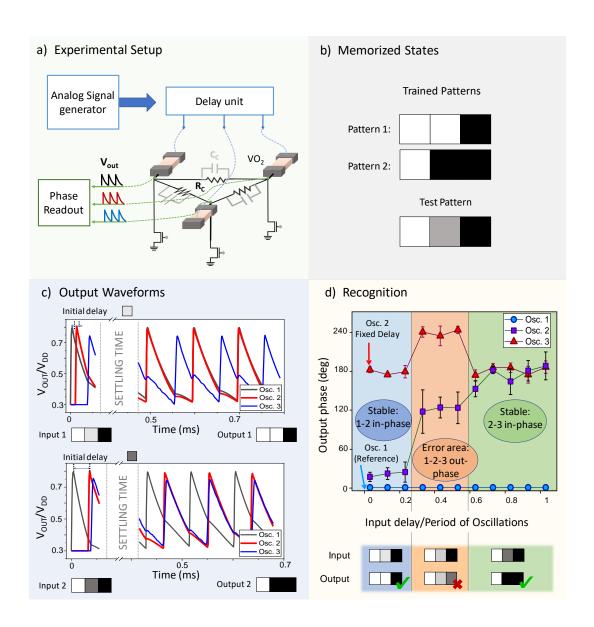

In chapter 5 we present the experimental implementation of an Oscillatory Neural Network based on the phase-transition of  $VO_2$  devices. The information is computed in the time-relations of the network signals. In particular, the storage of multiple output patterns in the relative phase of the oscillators is presented. Moreover, we offer experimental demonstrations of a computational scheme based on the encoding of the input information in the time-delays of the voltage signals in the oscillatory nodes. A demonstration of feature edge-extraction operated by a network of 4- $VO_2$  on Si oscillators is presented.

### Chapter 6: VO<sub>2</sub> Coupled Oscillators as Filters in Convolutional Neural Networks

In chapter 6 the integration of oscillatory neural networks as analog filters in convolutional neural networks is discussed. Through a simulation framework, we demonstrate that a single oscillatory neural network unit is able to replace five convolutional filters. A backpropagation algorithm which can train the ONN is also presented. Lastly, envisioning the connection of the oscillatory neural unit in multi-layered networks, we examine a phase detector circuit which could buffer the information from the previous to the subsequent layer.

### **Chapter 7: Conclusion**

The last chapter presents a conclusion of the thesis followed by an outlook for future developments.

# **2** VO<sub>2</sub> Oscillators: from the Material to the Applications

This chapter provides the fundamentals of devices based on vanadium dioxide. We discuss the origins of the phase transition of vanadium dioxide and how it can be exploited to build compact relaxation oscillators. We further present the theory on Oscillatory Neural Networks and review the state of the art of its technological applications. Finally, we briefly introduce the architecture of conventional convolutional neural networks employed for image recognition tasks.

### 2.1 Vanadium Dioxide

Vanadium oxides are strongly correlated materials, which have been extensively studied due to the possible applications of their insulating to metallic (IMT) transition [88]. They can be synthesized with standard deposition techniques, as chemical vapour deposition or atomic layer deposition. They present a variety of stoichiometries, which, given their different crystal structure and band diagrams, can be identified with standard Raman and X-ray spectroscopy characterization. When present, the insulator-to-metal phase transition happens at different temperature for the different oxidation states. An overview of the stable vanadium oxides that present an IMT is given in table 2.1.

Between the various stoichiometries,  $V_2O_3$ ,  $VO_2$  and  $V_2O_5$  are the most researched for practical

**Table 2.1** | Table listing various vanadium compound, their crystalline structure and phase transition temperatures. Information from [88].

|                               | cristal structure            | transition temperature |

|-------------------------------|------------------------------|------------------------|

| V <sub>2</sub> O <sub>3</sub> | monoclinic/trigonal          | 150 - 160 K            |

| $V_nO_{2n-1}$                 | triclinic                    | 250 - 70 K             |

| VO <sub>2</sub>               | monoclinic-tetragonal rutile | 340 K                  |

| V <sub>2</sub> O <sub>5</sub> | orthorombic                  | none                   |

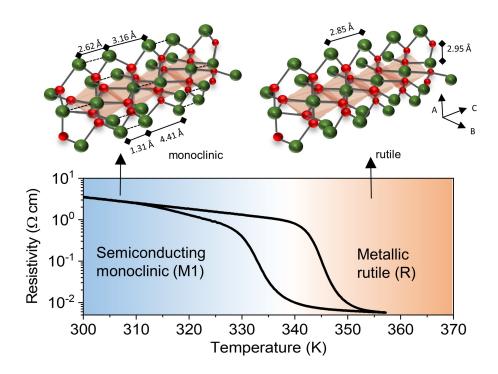

**Figure 2.2** | Vanadium dioxide presents a phase transition around 340 K that comprises a change in the resistivity of the material of 3 to 5 orders of magnitude. The phase change is accompanied by a structural transition from a monoclinic to a rutile crystal structure. Adapted from [93] with permission from AAAS.

applications. In particular,  $V_2O_3$  is investigated for its well defined Mott phase transition characteristics [89], which happens at a temperature of around 150 K. Vanadium pentoxide  $(V_2O_5)$  is the most stable compound, that features the highest oxidation state of vanadium oxides [90]. It does not present an IMT transition, however it is extensively researched for its electrochromic applications [91, 92].

In recent years, vanadium dioxide (VO<sub>2</sub>) attracted the interest of the scientific community given its near-room temperature insulator to metal (IMT) phase transition, which enables more practical applications for novel electronic devices. The phase transition in VO<sub>2</sub> happens in fact at a critical temperature  $T_{\rm C}$  = 68° C (340 K) and it is accompanied by a change in its structural and electronic properties [94]. At room temperature, VO<sub>2</sub> presents a monoclinic (M1) crystal structure and semiconducting properties, with a resistivity of about 10  $\Omega$ · cm, as depicted in figure 2.2. In this phase, the crystal structure sees a doubling of the unit cell, with the formation of V-V dimers that are responsible for the opening of the VO<sub>2</sub> band gap and consequently for the low conductance of the material. Above 340 K the material experiences an insulator to metal transition with a rise of several orders of magnitude in its electrical conductivity, accompanied by a structural transition to a tetragonal, rutile crystal structure [95, 93, 96, 97]. The phase change is volatile, meaning that when the external stimuli inducing the phase change is removed, the material goes back to its insulating state. In figure 2.3

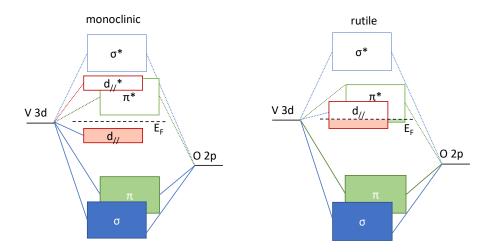

**Figure 2.3** | Left: the band diagram of the monoclinic phase presents an energy gap between the  $d_{//}$  and the  $d_{//}$ \* orbitals. Right: in the rutile phase the Fermi level is position in the conduction band, justifying the metallic nature of this phase. Adapted from [98], by permission from Springer Nature Customer Service Centre GmbH: Springer Nature, Nature Physics, 2013.

we can see a schematic representation of the VO<sub>2</sub> band diagram. The phase transition is determined by the vanadium d electrons, whose bonding modifies the electronic structure near the Fermi level (E<sub>F</sub>) across the phase transition. In fact, the V 3d orbitals hybridize with the O 2p orbitals, forming  $\sigma$ ,  $\pi$  and  $d_{ff}$  orbitals. In the metallic state, the  $d_{ff}$  orbitals are parallel to the rutile c-axis and not bonded. They partially overlap with  $\pi^*$  orbitals and result not completely filled, therefore leading to the metallic properties of the material [98]. Across the phase transition, the formation of V-V dimers results in a splitting of the  $d_{ff}$  orbitals in a bond and anti-bond configuration, in which the  $d_{ff}$  is empty . In addition, the  $\pi^*$  orbitals are shifted to higher energy [99]. The formed band gap is responsible for the semiconductive nature of the monoclinic VO<sub>2</sub>.

Apart from the electrical conductivity, other properties of the material are affected by the phase transition, in particular optical properties [100, 101] and thermal properties like the thermal conductivity [102, 103] and the Seeback coefficient [104]. This wide range of effects makes this material an attractive candidate for various applications, spanning from fast electrical switches [105], to optical devices [106, 107], to thermochromic coatings [108].

Researchers still debate about the nature of the phase transition of  $VO_2$ . The strong electronelectron interaction would classify the material along the Mott transition materials [109, 110, 111]. Following this theory, the study of the material usually proceeds from the Hubbard hamiltonian for strongly correlated fermions [112]:

$$H = -\sum_{ij(\sigma)} t_{ij} c_{i\sigma}^{\dagger} c_{j\sigma} + U \sum_{i} n_{i\uparrow} n_{i\downarrow}. \tag{2.1}$$

In this equation,  $t_{ij}$  represents the probability for a non-interacting electron to hop between

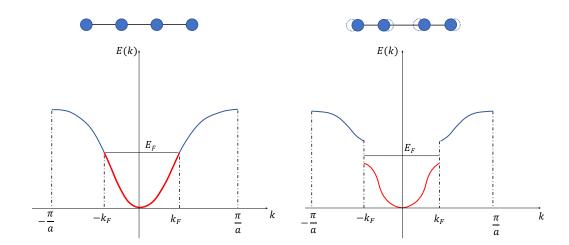

sites i and j. The operator  $c_{i\sigma}$  is the creation operator for the electron at site i, and  $c_{i\sigma}^+$  the corresponding annihilation operator. This first summation term is a kinetic energy term that describes the energy needed for an electron to hop from site to site in the lattice, therefore from atom to atom. The second summation term takes instead into account the Coulomb repulsion between two electrons present in the same site i. In particular,  $n_{i\sigma} = c_{i\sigma}^+ c_{i\sigma}^-$  represents the density of electrons with spin  $\sigma$  at a site i, while U is the Coulomb energy cost for two electrons to occupy the same site. A qualitative explanation of the meaning of the Hubbard hamiltonian can be given considering the outermost electronic orbital in a one dimensional chain of atoms. In the non interacting limit, i.e. without considering the Coulomb repulsion (second term equal to 0), the first term would favor the sharing of the electrons among the lattice, therefore the material would be a metal. In contrast, when the second term is predominant, charge localization is favored. Consequently, for increasing values of U, a material that is traditionally a metal can transition to an insulating behavior, with the opening of an energy gap in the band structure of the material proportional to the energy U [113, 114]. From this basic principle, materials which traditionally would be considered metallic present instead a transition to a so-called Mott insulator. It is to be noted that Mott transition materials are not subject to a structural phase change. However, as already briefly discussed, the VO<sub>2</sub> IMT is accompanied by a structural transition, which suggests the presence of a Peierls instability in the material, caused by electrons-lattice interactions [115, 95]. The origins of a Peierls instability can be also qualitatively explained by considering a one-dimensional chain of atoms. Assuming the presence of one electron at each site of the chain and assuming the outermost energy band of the system half-filled, the Fermi wavevector falls at half of the Brillouin zone  $\pi/a$  (figure 2.4). If a periodic distortion is introduced in the lattice, bringing two atoms closer together of a factor  $\delta$ , such that the lattice periodicity is doubled, a band gap opens exactly at the Fermi energy of the material, decreasing the electron energy. This decrease of the electron energy would compensate the increase of the lattice energy introduced by the distortions [116]. Two bands form, one filled and one empty, therefore changing the material from a metal to an insulator. In support of the Peierls transition is the fact that in the monoclinic phase the V-V bonds are dimerized and cause a doubling of the lattice constant compared to the rutile phase, therefore justifying a splitting of the bands.

Many studies have shown that the two contribution (Peierls and Mott mechanism), cannot really be separated and therefore attribute the phase change to an interplay between the two effects [118, 119]. However, more recent works have shown that the IMT in  $VO_2$  can happen without the occurrence of the structural phase transition [120, 121]. In addition, the IMT was obtained also by pure carrier injections, which would support the idea of a band splitting occurring because of the contrasting energy terms in the Hubbard hamiltonian, in the framework of the Mott transition [122]. Even though the origin of the transition is still debated, the change in conductivity of  $VO_2$  was recorded multiple times in experiments and achieved through various techniques, comprising electrical activation [123, 124, 125, 126], optical activation [127, 128], and strain [129, 130], for exploitation in various technological applications.

**Figure 2.4** | Dispersion relation E(k) of undistorted (left) and distorted (right) atom chain. The dimerization of the atom chain causes the appearance of a band gap in the first Brillouin zone [117].

### 2.1.1 VO<sub>2</sub> Fabrication

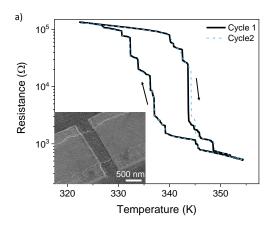

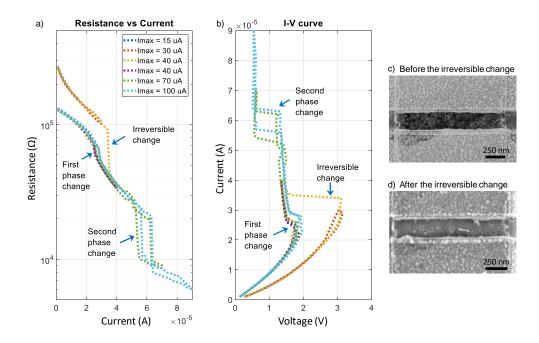

The sharpness, as well as the width of the vanadium dioxide phase transition are greatly impacted by the quality of the material, and specifically by impurities and crystal defects [131]. It is recorded that the resistivity ratio between the insulating and the metallic state can be as high as 10<sup>5</sup> in bulk [132]. However, the on/off ratio, the sharpness and the width of the hysteresis can be greatly impaired when fabricating VO<sub>2</sub> thin films [133]. VO<sub>2</sub> has been synthesized with various deposition techniques, such as pulsed layer deposition (PLD), chemical vapour deposition [134], atomic layer deposition (ALD) [135], sputtering [136] and sol-gel techniques [137]. The quality of the film and the impact on the phase transition for film deposited on different substrates has been extensively studied. For epitaxial growth, Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> are the most used substrates [138]. Film grown on Al<sub>2</sub>O<sub>3</sub> report a very narrow hysteresis width and quite large on/off ratio. In particular, experiments have shown that the hysteresis width can be as narrow as 1° C when  $VO_2$  is deposited with PLD on sapphire (1010) [132]. A narrow hysteresis is desirable for practical implementation of VO2 devices, as it reduces the power needed for switching the phase. It is known that the phase transition characteristics of VO<sub>2</sub> can degrade in polycrystalline films, due to the presence of grain boundaries [139]. In particular, it has been shown that films which present smaller grains result in a widening of the hysteresis and a reduced on/off ratio, while bigger grains are associated with narrower hysteresis and larger on/off ratio [133].

In addition, stress introduced by lattice mismatch with the substrate has proven to have an effect on the temperature at which the phase transition occurs. In particular, tensile stress results in an increase of the transition temperature, while compressive strain brings to a decrease of the transition temperature. This has been demonstrated with  $VO_2$  deposited on sapphire and on  $TiO_2$  [140, 141]. When deposited on Si, the  $VO_2$  relaxes in a polycrystalline film, where no stress in the lattice is introduced [142]. In particular, many works utilize  $SiO_2$  as

a buffer layer, on top of which the  $VO_2$  breaks in granular films. As in this case no tensile stress is present, the phase transition is reported to happen at 68° C, however, it is affected by the widening of the hysteresis and the reduction of the on/off ration mentioned above [143].

Apart from stress, also doping can change the temperature transition of  $VO_2$ . Introduction of dopants like Fe, Co, Ni lower the transition temperature [144], while it is experimentally demonstrated that Ge can bring the transition temperature up to  $90^{\circ}$  C [145, 146, 147]. For technological reasons, it would be advantageous to control the transition temperature and engineer it to higher values. In fact, envisioning commercial electronics applications, any  $VO_2$ -based technology should guarantee its functionality up to temperatures higher then  $80^{\circ}$  C, which is the temperature commonly reached by a computer processor.

### 2.1.2 VO<sub>2</sub> Electrically-Triggered Transition

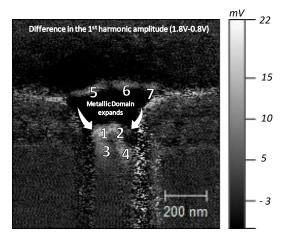

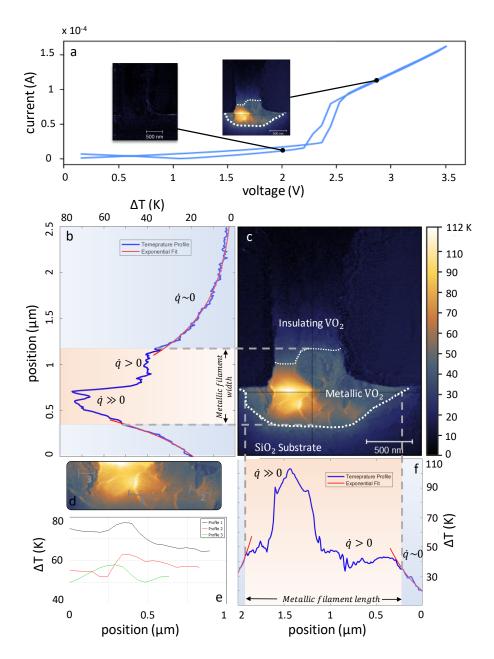

Already in 1959 it was shown that the insulator to metal transition of  $VO_2$  can be electrically triggered in planar devices [104]. In these early works, it was possible to image with an optical microscope the portion of the film that was undergoing the IMT transition, therefore highlighting the filamentary character of the transition. The transition was attributed to the reaching of the temperature threshold by Joule heating in the device [148]. However, recent investigations of the IMT on scaled devices, mostly conducted through simulation efforts, pointed out that the Joule-heating effect could be insufficient to justify the transition and consequently opened a debate on the concurrence of non-thermal effects in the phase change. In this section the origin of the electrically-driven transition is briefly discussed, with a focus on the hypothesis regarding the nucleation of the phase transition and the evolution of the metallic filament in electrical devices.

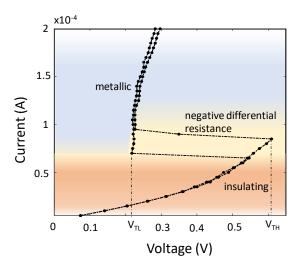

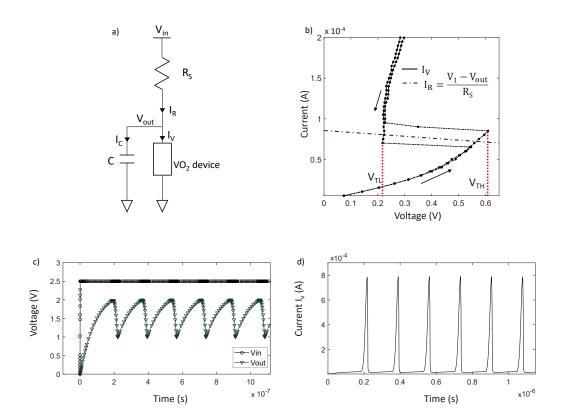

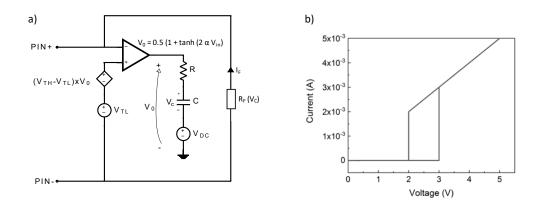

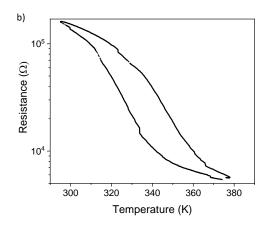

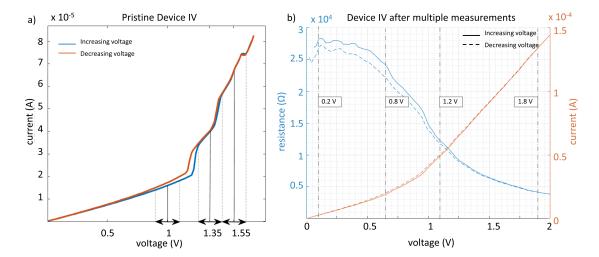

A typical current versus voltage (I-V) curve of a vanadium dioxide device is shown in figure 2.5. In the first part of the curve, the  $VO_2$  device is in its insulating state and acts as as a high impedance resistance. The power dissipated in form of Joule heat increases the local temperature of the device. When hitting a threshold voltage value  $V_{TH}$ , the device undergoes the insulator to metal transition. During this process, the voltage measured on the device decreases even though the current increases, which is reported as a feature of negative differential resistances [149]. After the transition, the device stabilizes to a low resistance value. Upon lowering of the voltage applied to the device, the voltage threshold  $V_{TL}$  for the metal to insulator phase transition is reached. The device therefore switches back to its high impedance state.

As the phase transition in vanadium dioxide happens as a function of temperature, it would be natural to assume that Joule heating is responsible for the transition to the metallic state in an electrically activated device. However, the nature of the electrically driven transition, similarly to the nature of the transition itself, is greatly disputed in literature. In fact, many studies suggest that the Joule heating generated in the devices is insufficient to rise the temperature of the device above the phase transition. In addition, it has been shown that the phase transition

**Figure 2.5** | The current vs. voltage characteristic of a  $VO_2$  device presents three regions: at first, the device is in its insulating state. As the voltage drop across the device is high enough to trigger the phase transition, the material undergoes the phase change and a negative differential resistance regime is formed. Lastly, the device stabilizes in its metallic state. The measurement was conducted sourcing a current and measuring the voltage across a  $VO_2$  device.

can be triggered by carrier injection with the use of electrolyte gating [124] and it is predicted to occur upon the application of high electric fields, on the order of 1-10  $MV/cm^2$  [150], which might be reached in very scaled devices.