# High-Speed ADC Design and Optimization for Wireline Links

Présentée le 22 avril 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de systèmes microélectroniques Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

# Ayça AKKAYA

Acceptée sur proposition du jury

Dr J.-M. Sallese, président du jury

Prof. Y. Leblebici, Prof. A. P. Burg, directeurs de thèse

Prof. F. Maloberti, rapporteur

Prof. A. Tajalli, rapporteur

Dr A. Koukab, rapporteur

# Acknowledgements

First and foremost, I would like to express my sincere gratitude to my thesis advisor Prof. Yusuf Leblebici for giving me the opportunity to pursue my doctoral studies at the Microelectronic Systems Laboratory (LSM). He always encouraged me, gave me freedom in my work, and trusted me. I can never thank him enough for his endless support and positive attitude. I am also grateful to my co-advisor Prof. Andreas Peter Burg for all his support and valuable comments on my publications.

I would like to thank my thesis committee members Dr. Jean-Michel Sallese, Prof. Franco Maloberti, Prof. Armin Tajalli, and Dr. Adil Koukab for their valuable time and insightful comments.

I would like to thank all the former LSM members. During my time at LSM, I had the chance to work with a wonderful group of colleagues. I would like to thank Dr. Alain Vachoux for his support on CAD tools and Dr. Alexandre Schmid for his support with the computing infrastructure. I especially thank my officemate Duygu Kostak for being a great colleague and a friend. I would like to thank Tugba Demirci for her constant support, for sharing her experience and knowledge during my M.Sc. and Ph.D., and for her friendship.

I would like to thank my friends Isinsu, Nergiz, Cem, Seniz, Deniz, Behnoush, Selman, Elmira, Bilal, and Mustafa for the joyful moments we shared together and for making Lausanne feel like home to me.

My deepest gratitude is for Firat Celik who always encouraged me and believed in me. I deeply appreciate his contribution to this thesis, both technical and mental. Without his support, patience, and companionship, this thesis would not have been possible.

Last but not least, I am grateful to my family for their endless support and love.

Lausanne, 16 January 2021

Ayça Akkaya

# **Abstract**

The ever-growing global internet traffic has increased demand for higher speed data transmission. As the bandwidth requirements of wireline links increase, extensive digital equalization techniques are required to compensate for the high-frequency channel loss. Analog-to-digital converter (ADC) based links consisting of high-speed ADCs and digital signal processors enable the implementation of powerful equalization algorithms in the digital domain. Such systems are implemented using advanced technology nodes to benefit from the power and area advantages that the advanced technology nodes provide for the digital blocks. In addition to the speed, the power efficiency and the compatibility with technology scaling are important parameters in the design of ADCs used in such systems. Successive approximation register (SAR) ADCs have become a popular choice in wireline applications because of their power efficiency and compatibility with advanced technology nodes due to consisting of mostly digital blocks.

This thesis focuses on high-speed SAR ADC design techniques to improve both conversion speed and power efficiency. First, a single-channel asynchronous SAR ADC design using a single comparator is presented to find out the achievable sampling rate with only one comparator. The 9-bit asynchronous SAR ADC prototype in 65 nm CMOS achieves 47.6 dB SNDR and 29.6 fJ/conv.-step figure-of-merit near Nyquist frequency at 222 MS/s and occupies an area of 0.017 mm<sup>2</sup>. Then, the use of comparator delay information for quantization is analyzed and a self-calibrated delay-based least significant bit extraction circuit, which achieves 3.35 dB SNDR for a 9-bit 200 MS/s with insignificant degradation in power consumption, speed, and area, is presented.

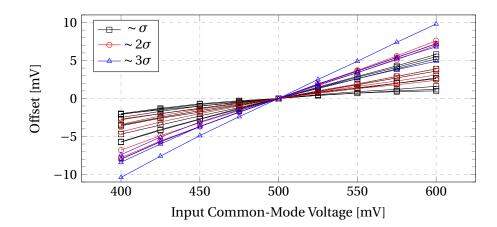

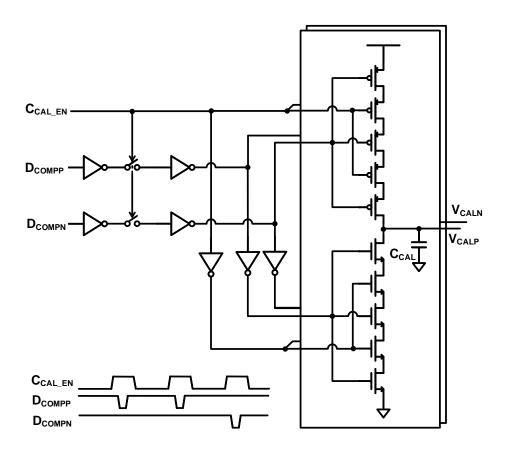

Next, loop-unrolled (LU) SAR ADC topology, which uses multiple comparators to improve the SAR loop delay, and comparator offset calibration techniques in LU-SAR ADCs are reviewed. Common-mode voltage variation in LU-SAR ADCs due to comparator kickback and the common-mode dependency of the comparator offset are addressed. A common-mode adaptive background offset calibration for LU-SAR ADCs is proposed. The proposed calibration scheme ensures that the comparators are calibrated at the same input common-mode voltage at which they each operate during the SAR conversion to prevent the common-mode dependent offset mismatch between the comparators. Besides, the common-mode variation immunity of the proposed calibration scheme is exploited to optimize the figure-of-merit of

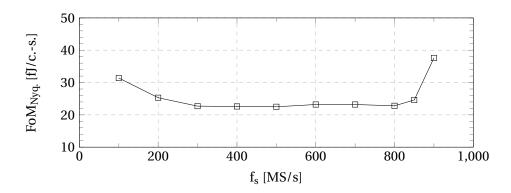

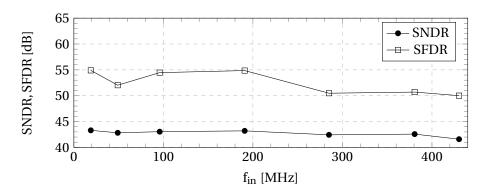

the LU-SAR ADC. The prototype 8-bit LU-SAR ADC manufactured in 28 nm FDSOI achieves 42.57 dB SNDR and 22.8 fJ/conv.-step figure-of-merit at 800 MS/s with near Nyquist frequency input and occupies an area of only  $0.0037~\rm mm^2$ .

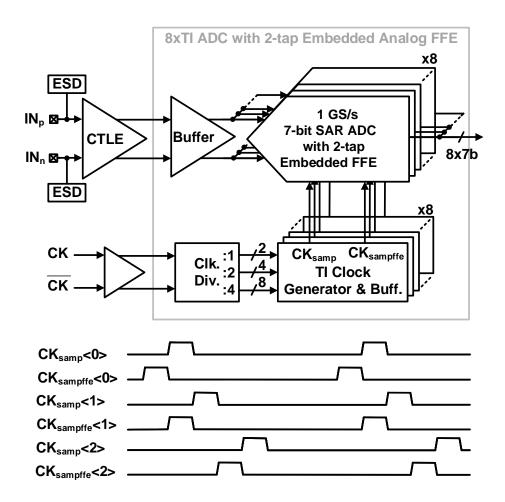

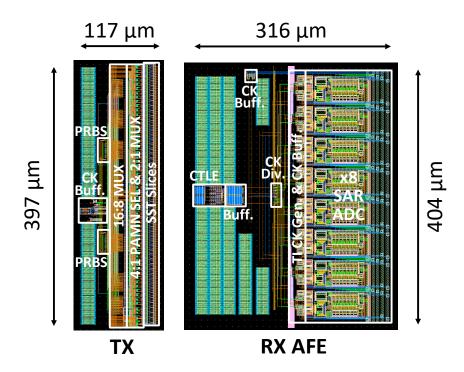

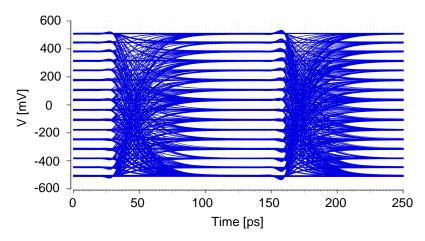

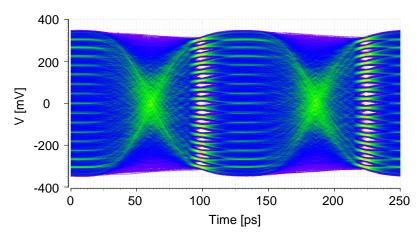

Lastly, an ADC-based receiver analog front-end (AFE) design in 28 nm FDSOI is presented and the feasibility of high order pulse amplitude modulation (PAM) is examined for a moderate-loss channel. The high order PAM compatible ADC-based AFE consists of a continuous-time linear equalizer and an 8 GS/s 8-way time-interleaved 7-bit SAR ADC with an embedded 2-tap feed-forward equalizer. All the equalization is implemented in the analog domain to avoid the circuit complexity and high power consumption of the digital equalization with high order modulation. The ADC-based AFE consumes 49.36 mW at 8 Gbaud, which corresponds to 1.54 pJ/bit at 32 Gb/s with PAM-16 and 2.06 pJ/bit at 24 GS/s with PAM-8.

**Keywords:** Analog-to-digital converter, ADC, successive approximation register, SAR, asynchronous clocking, loop-unrolling, offset calibration, time-interleaving, ADC-based receiver, wireline links, pulse amplitude modulation, PAM, feed-forward equalizer, FFE.

# Résumé

Le trafic internet mondial en constante augmentation a accru la demande de transmission de données à plus grande vitesse. À mesure que les besoins en bande passante des liaisons filaires augmentent, des techniques d'égalisation numérique extensives sont nécessaires pour compenser la perte de canal haute fréquence. Les liaisons basées sur un convertisseur analogique-numérique (CAN) composées de CAN à grande vitesse et de processeurs de signaux numériques permettent la mise en œuvre d'algorithmes d'égalisation puissants dans le domaine numérique. De tels systèmes sont mis en œuvre à l'aide de nœuds de technologie avancée pour bénéficier des avantages de puissance et de surface que les nœuds de technologie avancée fournissent pour les blocs numériques. Outre la vitesse, l'efficacité énergétique et la compatibilité avec la mise à l'échelle de la technologie sont des paramètres importants dans la conception de CAN utilisés dans ces systèmes. Les CAN à registres d'approximation successifs (SAR) sont devenus un choix populaire dans les applications filaires en raison de leur efficacité énergétique et de leur compatibilité avec les nœuds de technologie de pointe en raison de leur composition principalement numérique.

Cette thèse se concentre sur les techniques de conception CAN SAR à haute vitesse pour améliorer à la fois la vitesse de conversion et l'efficacité énergétique. Tout d'abord, une conception CAN SAR asynchrone à canal unique utilisant un seul comparateur est présentée pour déterminer la fréquence d'échantillonnage réalisable avec un seul comparateur. Le prototype CAN SAR asynchrone 9 bits en CMOS 65 nm atteint un SNDR de 47,6 dB et un facteur de mérite de 29,6 fJ/conv.-step près de la fréquence de Nyquist à 222 MS/s et occupe une zone de 0,017 mm². Ensuite, l'utilisation des informations de retard du comparateur pour la quantification est analysée et un circuit d'extraction de bits les moins significatifs basé sur un retard auto-calibré, qui atteint 3,35 dB SNDR pour une résolution de 9 bits et une vitesse de 200 MS/s avec une dégradation insignifiante de la consommation d'énergie, de la vitesse et la surface, est présenté.

Ensuite, la topologie CAN SAR en boucle déroulée (LU), qui utilise plusieurs comparateurs pour améliorer le délai de boucle SAR, et les techniques d'étalonnage de décalage de comparateur dans les CAN LU-SAR sont examinées. La variation de tension en mode commun dans les CAN LU-SAR due au rebond du comparateur et à la dépendance de mode commun du décalage du comparateur est traitée. Un calibrage du décalage de fond adaptatif en mode

commun pour les CAN LU-SAR est proposé. Le schéma de calibration proposé garantit que les comparateurs sont calibrés à la même tension de mode commun d'entrée à laquelle ils fonctionnent chacun pendant la conversion SAR pour éviter le décalage dépendant du mode commun entre les comparateurs. En outre, l'immunité aux variations de mode commun du schéma d'étalonnage proposé est exploitée pour optimiser la figure de mérite du CAN LU-SAR. Le prototype de CAN LU-SAR 8 bits fabriqué en FDSOI 28 nm atteint un SNDR de 42,57 dB et un facteur de mérite par pas de 22,8 fJ/conv.-step à 800 MS/s avec une entrée de fréquence proche de Nyquist et occupe une zone de seulement 0,0037 mm².

Enfin, une conception de récepteur analogique frontal (AFE) basé sur CAN en 28 nm FDSOI est présentée et la faisabilité de la modulation d'impulsion en amplitude d'ordre élevé (PAM) est examinée pour un canal à perte modérée. L'AFE basé sur CAN compatible PAM d'ordre élevé se compose d'un égaliseur linéaire en temps continu et d'un CAN SAR 7 bits à 8 voies entrelacées 8 Géch/s avec un égaliseur à anticipation à 2 prises intégrés. Toute l'égalisation est mise en œuvre dans le domaine analogique pour éviter la complexité du circuit et la consommation d'énergie élevée de l'égalisation numérique avec une modulation d'ordre élevé. L'AFE basé sur CAN consomme 49,36 mW à 8 Gbauds, ce qui correspond à 1,54 pJ/bit à 32 Gb/s en PAM-16 et 2,06 pJ/bit à 24 GS/s en PAM-8.

**Mots-clés :** Convertisseur analogique-numérique, CAN, registre d'approximation successive, SAR, cadencement asynchrone, déroulement de boucle, étalonnage d'offset, entrelacement temporel, récepteur basé sur CAN, liaisons filaires, modulation d'amplitude d'impulsion, PAM, égaliseur par anticipation, FFE.

# Contents

| A  | knov  | wledge  | ments                           | i   |

|----|-------|---------|---------------------------------|-----|

| Al | ostra | ct (Eng | dish/Français)                  | iii |

| 1  | Intr  | oducti  | on                              | 1   |

|    | 1.1   | Thesi   | s Goal                          | 2   |

|    | 1.2   | Thesi   | s Organization                  | 3   |

| 2  | Ove   | rview   |                                 | 7   |

|    | 2.1   | ADC I   | Errors                          | 7   |

|    |       | 2.1.1   | Quantization Noise              | 7   |

|    |       | 2.1.2   | Sampling Noise                  | 9   |

|    |       | 2.1.3   | Sampling Jitter                 | 9   |

|    | 2.2   | ADC I   | Performance Metrics             | 10  |

|    | 2.3   | Conve   | entional SAR ADC                | 14  |

|    | 2.4   | High-   | Speed SAR ADC Design Techniques | 14  |

|    |       | 2.4.1   | Asynchronous Clocking           | 16  |

|    |       | 2.4.2   | Monotonic Switching             | 17  |

|    |       | 2.4.3   | Two Alternating Comparators     | 20  |

|    |       | 2.4.4   | Loop-Unrolling                  | 21  |

|    |       | 2.4.5   | DAC Redundancy                  | 21  |

|    |       | 2.4.6   | Multi-bit per Conversion Step   | 23  |

|    |       | 2.4.7   | Pipelined SAR                   | 24  |

|    |       | 2.4.8   | Time-Interleaving               | 24  |

| 3  | Asy   | nchror  | nous SAR ADC                    | 27  |

|    | 3.1   | ADC A   | Architecture                    | 27  |

|    |       | 3.1.1   | Overview                        | 27  |

|    |       | 3.1.2   | Capacitive DAC                  | 29  |

|    |       | 3.1.3   | Bootstrapped Sampling Switch    | 31  |

|    |       | 3.1.4   | SAR Memory                      | 32  |

|    |       | 3.1.5   | Asynchronous Clock Generation   | 34  |

|    | 3.2   | Measi   | urement Results                 | 34  |

|    | 3.3   |         | usion                           | 36  |

## **Contents**

| 4  | Dela    | ay-Based LSB Extraction                           | 41  |

|----|---------|---------------------------------------------------|-----|

|    | 4.1     | Delay-Based LSB Extraction                        | 42  |

|    |         | 4.1.1 Overview of the Method                      | 42  |

|    |         | 4.1.2 Circuit-Level Implementation                | 45  |

|    | 4.2     | Simulation Results                                | 49  |

|    | 4.3     | Conclusion                                        | 53  |

| 5  | Loo     | p-Unrolled SAR ADC                                | 57  |

|    | 5.1     | Overview of the LU-SAR ADC Calibration Techniques | 58  |

|    | 5.2     | ADC Architecture                                  | 59  |

|    |         | 5.2.1 Timing and the Calibration Scheme           | 62  |

|    |         | 5.2.2 Comparator                                  | 63  |

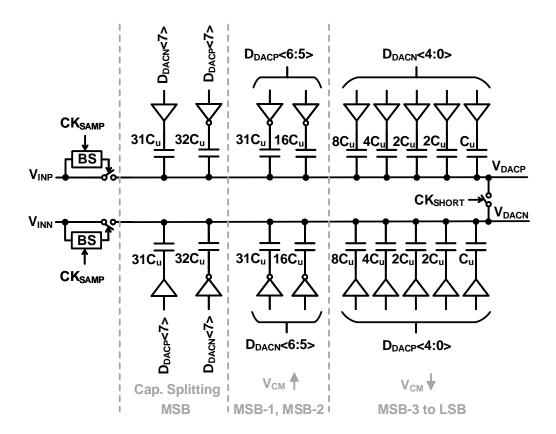

|    |         | 5.2.3 Capacitive DAC                              | 67  |

|    | 5.3     | Measurement Results                               | 71  |

|    | 5.4     | Conclusion                                        | 74  |

| 6  | ADO     | C-Based Receiver                                  | 77  |

|    | 6.1     | Pulse Amplitude Modulation                        | 77  |

|    |         | 6.1.1 Overview                                    | 77  |

|    |         | 6.1.2 Modulation Order                            | 78  |

|    | 6.2     | Transceiver System                                | 79  |

|    | 6.3     | ADC-Based RX AFE                                  | 79  |

|    |         | 6.3.1 Overview                                    | 79  |

|    |         | 6.3.2 CTLE                                        | 80  |

|    | 6.4     | Time-Interleaved ADC                              | 82  |

|    |         | 6.4.1 7-bit SAR ADC with 2-Tap Embedded FFE       | 83  |

|    | 6.5     | Simulation Results                                | 89  |

|    | 6.6     | Conclusion                                        | 93  |

| 7  | Con     | nclusion                                          | 99  |

|    | 7.1     | Future Work                                       | 100 |

|    |         |                                                   |     |

| Bi | bliog   | graphy                                            | 103 |

| Li | st of   | Acronyms                                          | 109 |

| Cı | ırricı  | ulum Vitae                                        | 111 |

| Li | st of l | Publications                                      | 113 |

# **List of Figures**

| 1.1  | block diagram of a wheline transcerver with an ADC-based receiver                     |    |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | Energy efficiency trend of ADCs over the years [1]                                    | 3  |

| 1.3  | Energy efficiency versus SNDR plot for different ADC architectures [1]                | 4  |

| 1.4  | Walden FoM versus sampling rate plot for different ADC architectures [1]              | 4  |

| 2.1  | Ideal input-output characteristic of a 3-bit ADC                                      | 8  |

| 2.2  | Quantization error of a 3-bit ADC                                                     | 8  |

| 2.3  | Simple sampler circuit and its noise equivalent                                       | ç  |

| 2.4  | SNR vs. input frequency plot of an 8-bit ADC with only the effect of jitter included. | 10 |

| 2.5  | DNL of a 3-bit ADC                                                                    | 12 |

| 2.6  | INL of a 3-bit ADC                                                                    | 12 |

| 2.7  | A conventional 3-bit charge-redistribution SAR ADC in sample mode                     | 15 |

| 2.8  | A conventional 3-bit charge-redistribution SAR ADC in hold mode                       | 15 |

| 2.9  | A conventional 3-bit charge-redistribution SAR ADC after the first step of the        |    |

|      | redistribution mode                                                                   | 15 |

| 2.10 | Final switch configuration of a conventional 3-bit charge-redistribution SAR          |    |

|      | ADC for output code of "01001"                                                        | 15 |

| 2.11 | Timing of a 5-bit (a) synchronous and (b) asynchronous SAR ADC                        | 16 |

| 2.12 | A 5-bit SAR ADC with monotonic capacitor switching (in sample mode)                   | 17 |

| 2.13 | Common-mode change in a 5-bit SAR ADC with monotonic capacitor switching              |    |

|      | during SAR conversion                                                                 | 17 |

| 2.14 | A 5-bit SAR ADC with split monotonic capacitor switching (in sample mode). $$ .       | 19 |

| 2.15 | Common-mode change during SAR conversion in a 5-bit SAR ADC with split                |    |

|      | monotonic capacitor switching.                                                        | 19 |

| 2.16 | A 5-bit Loop-Unrolled SAR ADC with monotonic capacitor switching                      | 20 |

| 2.17 | A 5-bit Loop-Unrolled SAR ADC with monotonic capacitor switching                      | 21 |

| 2.18 | Binary search with decision error due to incomplete capacitive DAC settling           | 22 |

| 2.19 | Redundant search with decision error due to incomplete capacitive DAC settling.       | 22 |

| 2.20 | 2-bit per conversion step SAR ADC                                                     | 23 |

| 2.21 | Two-Stage Pipelined SAR ADC                                                           | 24 |

| 2.22 | Time-Interleaving.                                                                    | 25 |

| 3.1  | Block diagram of the proposed asynchronous SAR ADC                                    | 28 |

## **List of Figures**

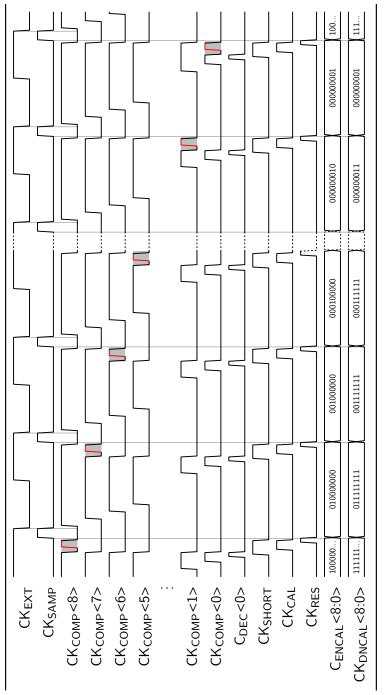

| 3.2  | Timing scheme of the proposed asynchronous SAR ADC                                               | 28 |

|------|--------------------------------------------------------------------------------------------------|----|

| 3.3  | capacitive DAC with bottom plate switches.                                                       | 29 |

| 3.4  | Bootstrapping with ideal switches                                                                | 30 |

| 3.5  | Schematic of the bootstrapped switch                                                             | 30 |

| 3.6  | SAR memory.                                                                                      | 33 |

| 3.7  | Proposed modified SAR memory cell                                                                | 34 |

| 3.8  | Comparator and the potential SAR memory error without the cross-coupled                          |    |

|      | NMOS transistors.                                                                                | 35 |

| 3.9  | Asychronous comparator clock generation circuitry                                                | 35 |

| 3.10 | Chip micrograph                                                                                  | 36 |

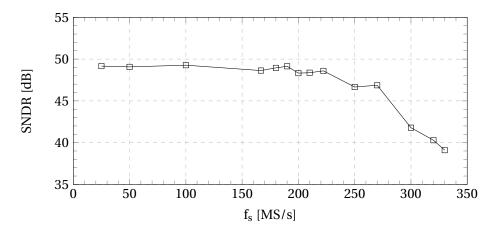

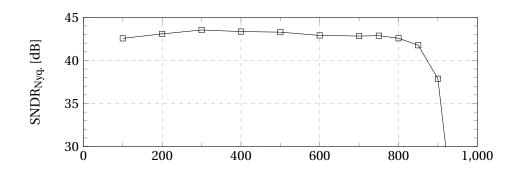

| 3.11 | SNDR vs. sampling frequency (f_s), $f_{in} \approx 10$ MHz                                       | 37 |

| 3.12 | Power vs. sampling frequency ( $f_s$ ), $f_{in} \approx 10$ MHz                                  | 37 |

| 3.13 | FoM vs. sampling frequency (f <sub>s</sub> ), $f_{in} \approx 10$ MHz                            | 37 |

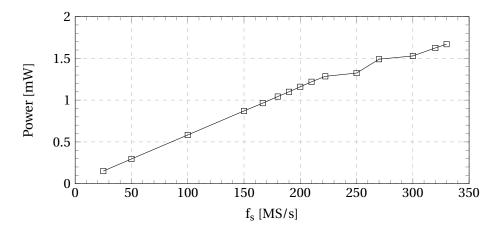

| 3.14 | Measured output spectrums at $f_s = 222  \text{MS/s}$ with low frequency and near Nyquist        |    |

|      | rate input signal                                                                                | 38 |

| 3.15 | Measured DNL and INL plots                                                                       | 38 |

| 4.1  | Block diagram of the SAR ADC with LSB extraction circuitry and background                        |    |

|      | calibration loop                                                                                 | 42 |

| 4.2  | Schematic of the comparator based on StrongArm latch                                             | 43 |

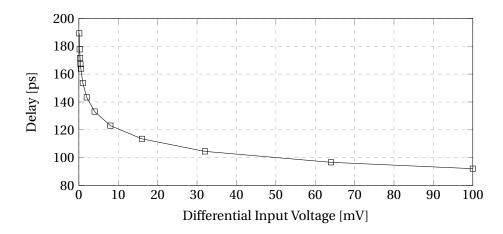

| 4.3  | Decision delay vs. differential input voltage plot of the comparator                             | 44 |

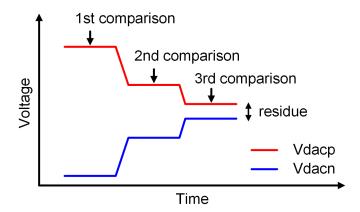

| 4.4  | Differential DAC output voltages of a 3-bit SAR ADC during the SA cycle                          | 44 |

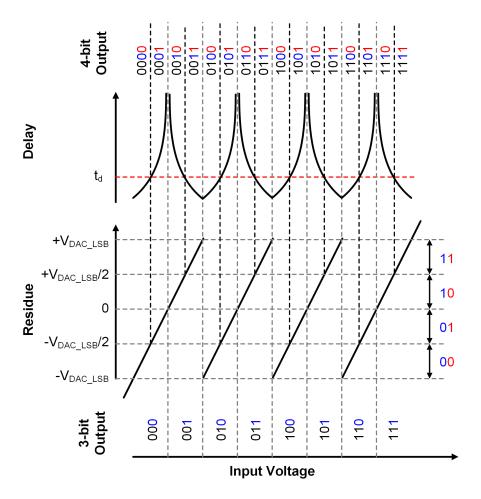

| 4.5  | The diagram showing the relationship between the ADC decision levels, SA                         |    |

|      | residue voltage and the comparator decision delay for a 3-bit SAR ADC with LSB                   |    |

|      | extraction from comparator decision delay                                                        | 45 |

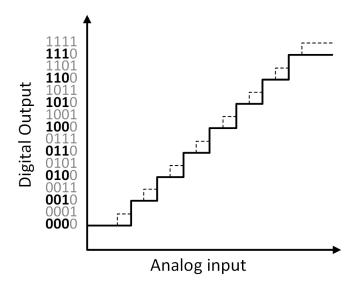

| 4.6  | Ideal input-output characteristic of a 3-bit SAR ADC without LSB extraction                      |    |

|      | circuit (in solid line) and with LSB extraction circuit (in dashed line)                         | 46 |

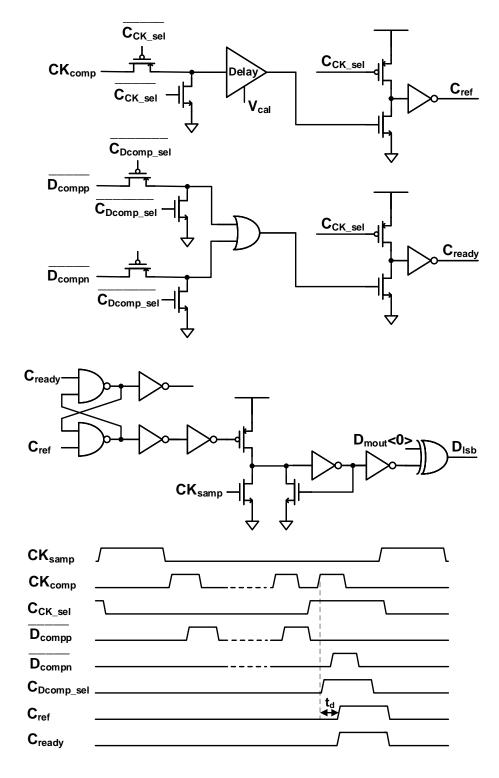

| 4.7  | LSB extraction circuitry and the timing scheme of the signals                                    | 47 |

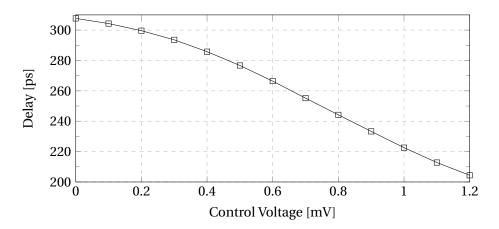

| 4.8  | Delay of the reference signal vs. control voltage                                                | 48 |

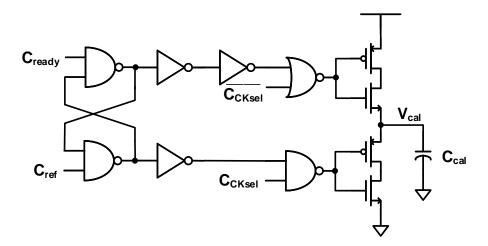

|      | Self-calibration loop to generate the control voltage for the reference delay. $$ . $$ .         | 49 |

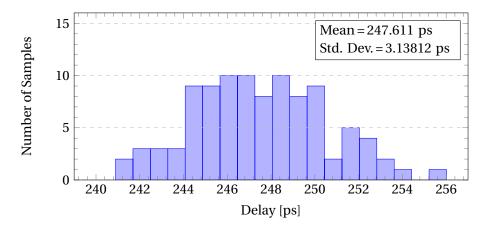

|      | Histogram showing the effect of noise on the delay of the ready signal                           | 50 |

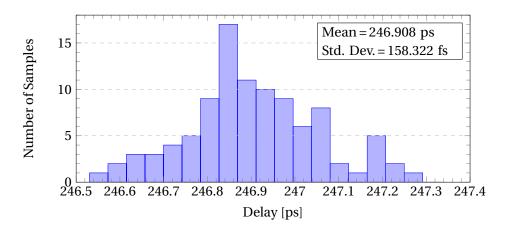

|      | Histogram showing the effect of noise on the delay of the reference signal                       | 50 |

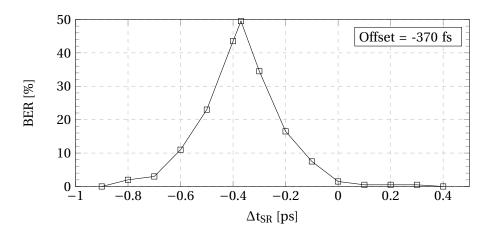

|      | BER vs. time difference between the rising edges of the SR latch inputs                          | 51 |

| 4.13 | SNDR vs. the time difference between the rising edges of the reference and ready signals         | 51 |

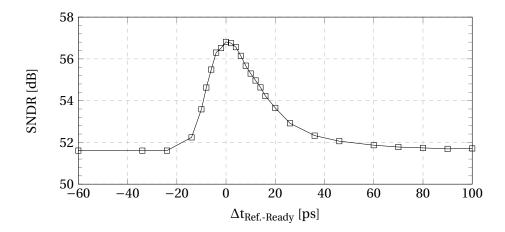

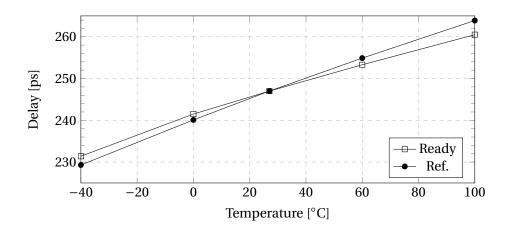

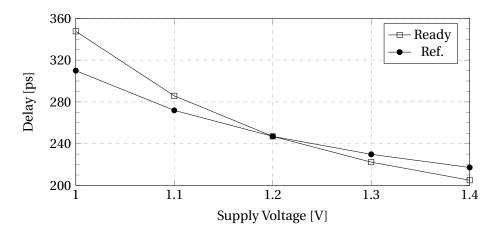

| 4.14 | Effect of temperature variation on the delays of the ready and reference signals.                | 52 |

|      | Effect of power supply variation on the delays of the ready and reference signals.               | 52 |

|      | Effect of input common-mode variation on the delays of ready and reference                       |    |

|      | signals                                                                                          | 53 |

| 4.17 | FFT plot of the $(9+1)$ -bit ADC with self-calibrated LSB extraction $(f_s = 200 \text{MS/s})$ . | 54 |

| 4.18 | Layout of the ADC.                                                                               | 55 |

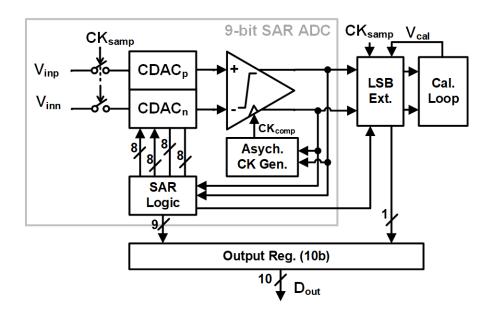

| 5.1  | Block diagram of the proposed LU-SAR ADC with common-mode adaptive                             |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | background offset calibration                                                                  | 60 |

| 5.2  | Timing scheme of the proposed LU-SAR ADC with common-mode adaptive                             |    |

|      | background offset calibration.                                                                 | 61 |

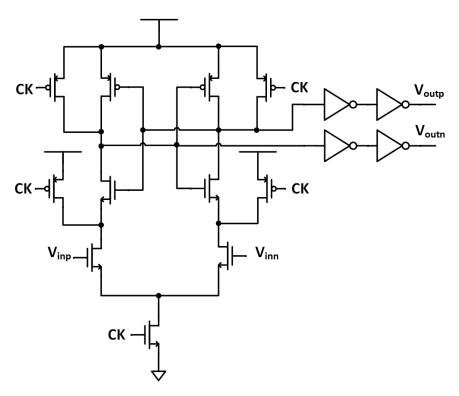

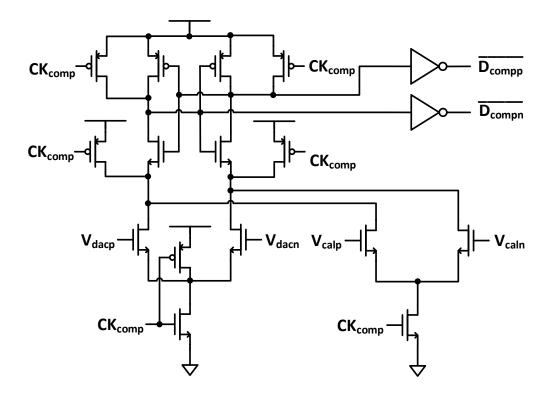

| 5.3  | Schematic of the comparator                                                                    | 63 |

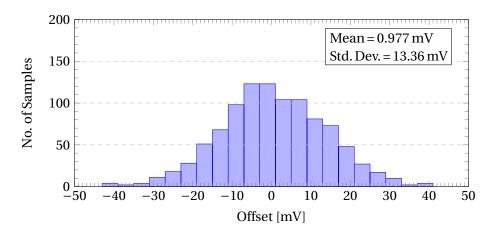

| 5.4  | Monte Carlo simulation result of the comparator offset at 500 mV input common-                 |    |

|      | mode                                                                                           | 64 |

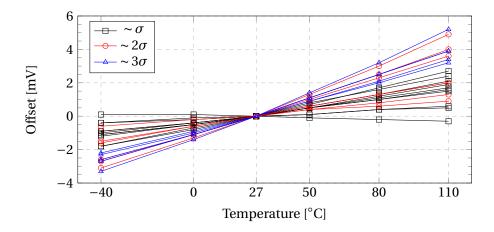

| 5.5  | Comparator offset vs. temperature (calibrated to zero-offset at 27 °C)                         | 64 |

| 5.6  | Comparator offset vs. comparator input common-mode (calibrated to zero-                        |    |

|      | offset at 500 mV common-mode)                                                                  | 65 |

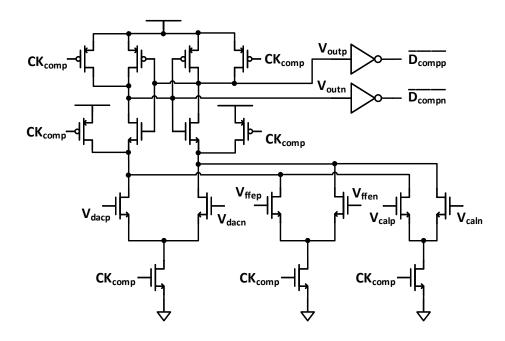

| 5.7  | Schematic of the comparator offset calibration circuit                                         | 66 |

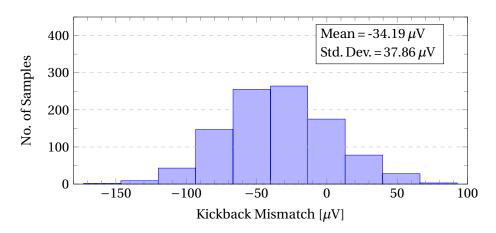

| 5.8  | Monte Carlo simulation result of the comparator kickback mismatch                              | 67 |

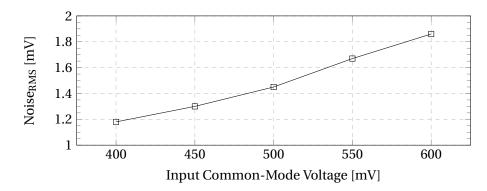

| 5.9  | Input referred RMS noise vs. input common-mode voltage of the comparator (at                   |    |

|      | 80 °C)                                                                                         | 67 |

| 5.10 | Schematic of the capacitive DAC                                                                | 68 |

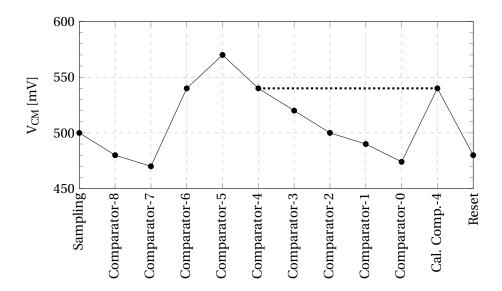

| 5.11 | Common-mode voltage during SAR conversion                                                      | 69 |

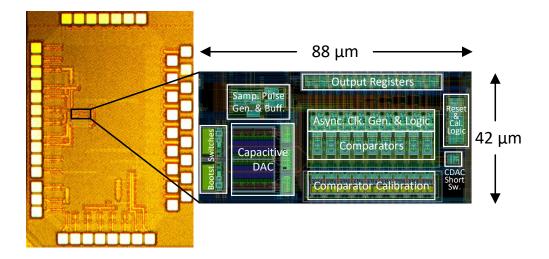

| 5.12 | Chip micrograph                                                                                | 71 |

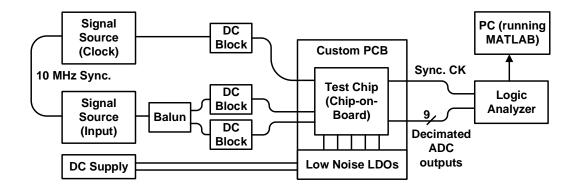

| 5.13 | Measurement setup                                                                              | 71 |

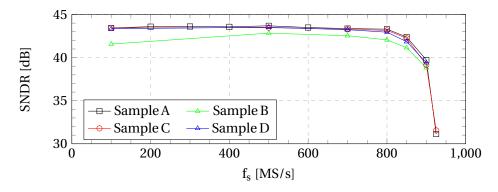

| 5.14 | SNDR vs. sampling frequency plots for different chip samples ( $f_{in} \approx 18\text{MHz}$ ) | 72 |

| 5.15 | SNDR vs. sampling frequency plots for different supply voltages ( $f_{in} \approx 18$ MHz).    | 72 |

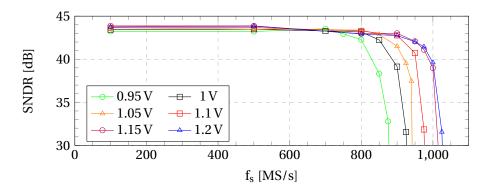

| 5.16 | Measured power spectral density, $f_{samp} = 800 \text{ MS/s}$ (ADC outputs are decimated      |    |

|      | by 13)                                                                                         | 73 |

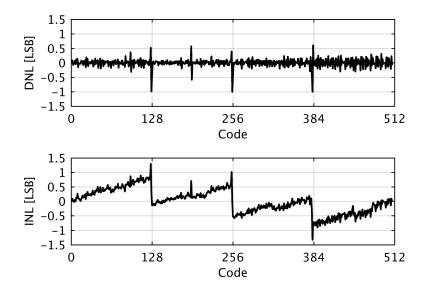

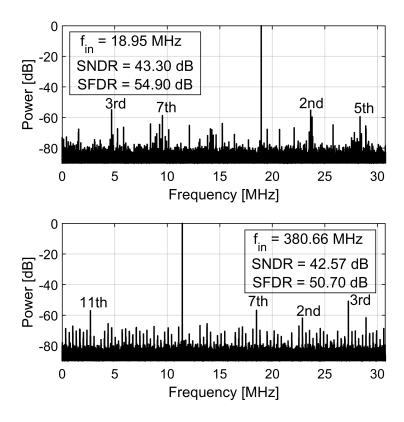

| 5.17 | Measured DNL and INL                                                                           | 74 |

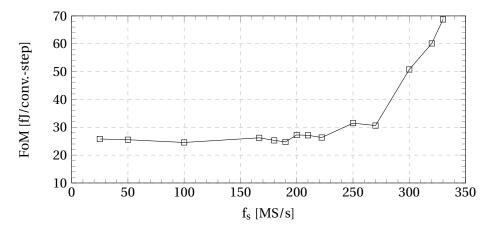

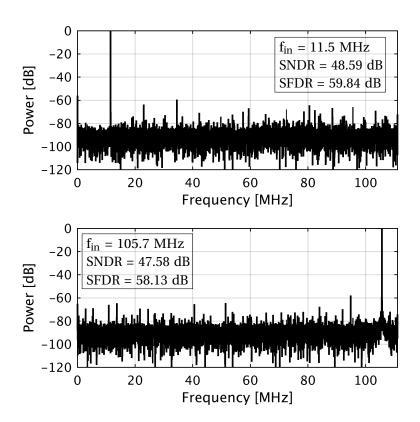

| 5.18 | SNDR vs. sampling rate (with near Nyquist rate input)                                          | 75 |

|      | Power consumption vs. sampling rate (with near Nyquist rate input)                             | 75 |

|      | FoM vs. sampling rate (with near Nyquist rate input)                                           | 75 |

|      | SNDR vs. input frequency, f <sub>samp</sub> = 800 MS/s                                         | 76 |

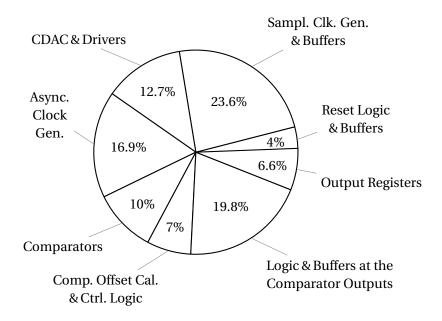

|      | Power breakdown.                                                                               | 76 |

|      |                                                                                                |    |

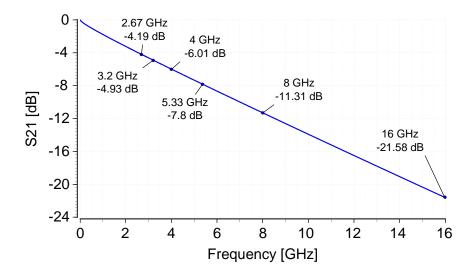

| 6.1  | Loss characteristic of the channel                                                             | 78 |

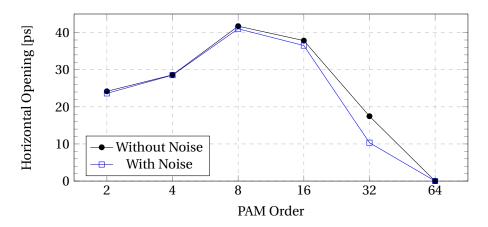

| 6.2  | Horizontal eye-opening values of different PAM orders                                          | 79 |

| 6.3  | Block diagram and the timing scheme of the ADC-based RX AFE                                    | 80 |

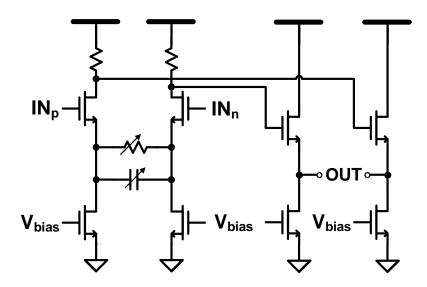

| 6.4  | Schematic of the CTLE and the ADC input buffer                                                 | 81 |

| 6.5  | Trim settings of the CTLE                                                                      | 82 |

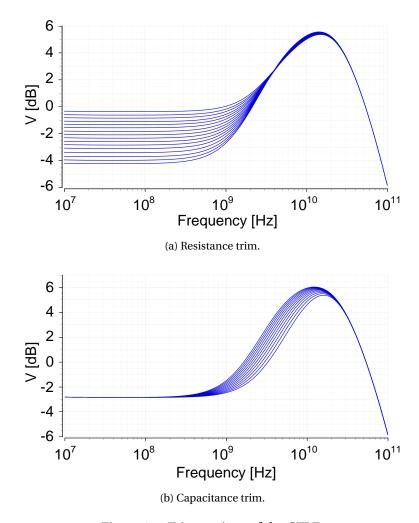

| 6.6  | Pulse response at the output of the channel, CTLE, and FFE block                               | 83 |

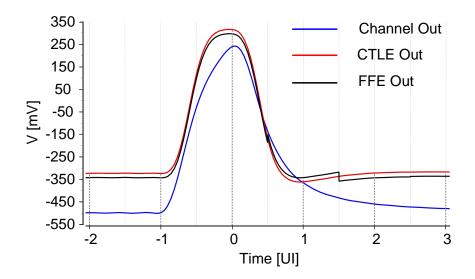

| 6.7  | Schematic of the sampling clock generator block                                                | 84 |

| 6.8  | Block diagram and the timing scheme of the single-channel 7-bit SAR ADC with                   |    |

|      | 2-tap embedded FFE                                                                             | 85 |

| 6.9  | Block diagram of the 2-tap embedded FFE                                                        | 86 |

| 6.10 | Schematic of the CDAC and the timing of the control signals                                    | 87 |

| 6.11 | Schematic of the CDAC <sub>SAR</sub>                                                           | 88 |

|      | Schematic of the dynamic comparator                                                            | 89 |

## **List of Figures**

| 6.13 Layout of TX and ADC-based RX AFE                                          | 90 |

|---------------------------------------------------------------------------------|----|

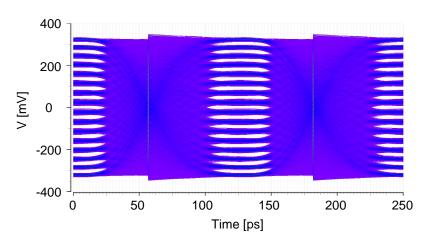

| 6.14 Simulated eye-diagrams                                                     | 91 |

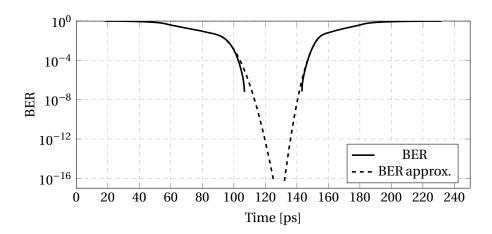

| 6.15 Timing bathtub curve of the eye-diagram at the output of the FFE block     | 92 |

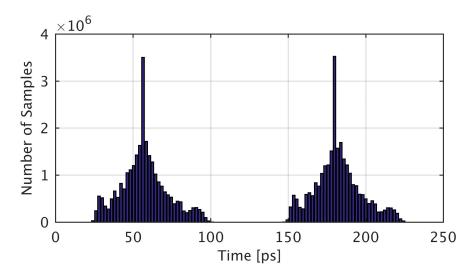

| 6.16 Horizontal histogram of the eye-diagram at the output of the FFE block. $$ | 92 |

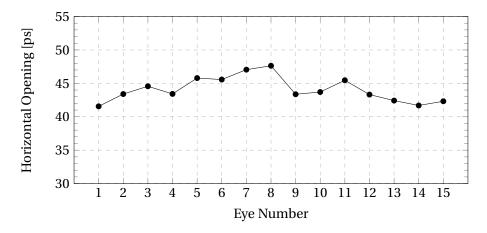

| 6.17 Horizontal eye-openings of each PAM-16 eye at the output of the FFE block  | 93 |

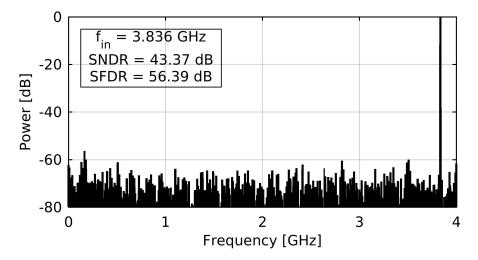

| 6.18 Power spectral density of the TI ADC                                       | 93 |

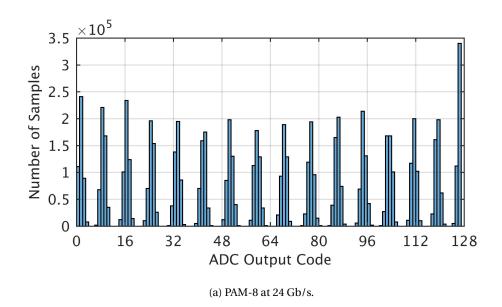

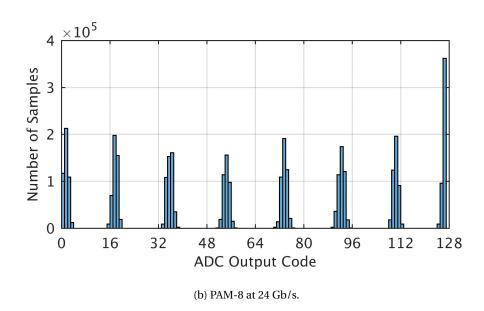

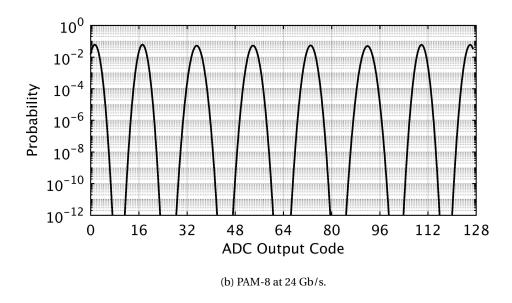

| 6.19 Histogram of the ADC output codes                                          | 94 |

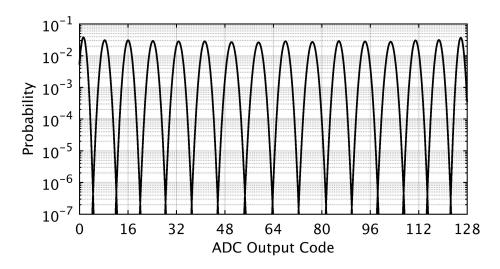

| 6.20 Extrapolated probability distribution of the ADC output codes              | 95 |

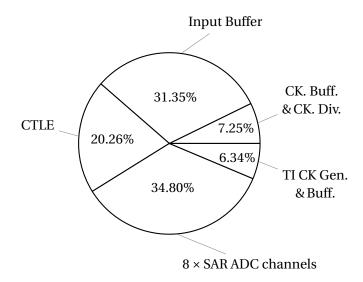

| 6.21 Power breakdown of the ADC-based RX AFE                                    | 96 |

# **List of Tables**

| 3.1 | Performance comparison of the asynchronous SAR ADC                                                                    | 39 |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Performance comparison of the 9-bit SAR ADC and the (9+1)-bit ADC (with LSB extraction and self-calibration circuity) | 53 |

| 5.1 | Performance comparison of the LU-SAR ADC                                                                              | 70 |

| 6.1 | Performance comparison of the ADC-based RX AFE                                                                        | 97 |

# 1 Introduction

Global IP traffic has experienced massive growth in recent years. By 2022, the global IP traffic is expected to reach 4.8 zettabytes per year, which is nearly 11 times more than all IP traffic generated in 2012 [2]. This massive growth in IP traffic increased the demand for higher speed data transmission. Increasing the bandwidth to meet the demand for faster data transmission in wireline links increased the amount of channel-loss that needs to be equalized as well. As a result, circuit designers move from two-level pulse amplitude modulation (PAM-2) signaling, also known as non-return-to-zero (NRZ), to more spectrally efficient PAM-4 signaling [3, 4, 5, 6, 7, 8]. This way the Nyquist frequency is halved and the corresponding channel loss is decreased. However, PAM-4 is more sensitive to residual inter-symbol interference (ISI) because it has a smaller vertical opening. Therefore, it requires more robust equalizers with many number of taps. To perform complex equalization algorithms in the digital domain, implementations using an analog-to-digital converter (ADC) and a digital signal processor (DSP) have become more common [3, 4, 5, 6, 7, 8].

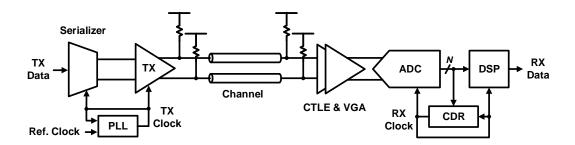

Figure 1.1 shows a block diagram of a wireline link that employs an ADC and DSP in the receiver side [9]. Employing DSP to implement the equalization algorithms in the digital domain provides various advantages. First, DSP has less sensitivity to process, voltage, and temperature (PVT) variations. Second, advanced technology nodes offer reduced power consumption and area advantage for DSP. Third, the DSP has the advantage of portability to new technology nodes. High-speed moderate resolution ADCs play an important role in ADC-based receivers. The ADC and the DSP in these systems are implemented on the same chip to avoid additional power consumption for transferring the ADC data to DSP. Therefore, the ADCs are implemented in the same advanced technology nodes as well.

Both ADC and DSP consume a significant amount of power in ADC-based designs [9]. Consequently, ADC-based receivers are less energy efficient compared to their mixed-signal counterparts [10]. Therefore, improving the energy efficiency of the ADC is desirable to improve the energy efficiency of the wireline links.

The resolution requirement of the ADCs used in ADC-based receivers is dependent on the

Figure 1.1: Block diagram of a wireline transceiver with an ADC-based receiver.

channel loss, equalization capability of the transmitter and receiver analog front-end, modulation order, and the targeted bit error rate (BER). Typical ADC resolution in PAM-4 ADC-based receivers is generally 6-8 bits [4, 5, 6, 7, 8, 11].

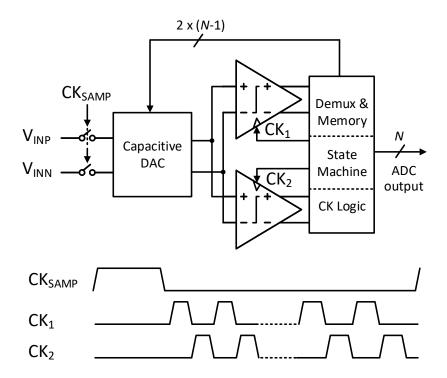

The need for medium-resolution ADCs operating at multi-GS/s sampling rates has increased with the use of ADC-based receivers. Time-interleaving is commonly employed to reach multi-GS/s sampling rates. The successive approximation register (SAR) ADC architecture has become a popular choice in time-interleaving, thanks to its energy efficiency and suitability to advanced technology nodes [12, 13, 14].

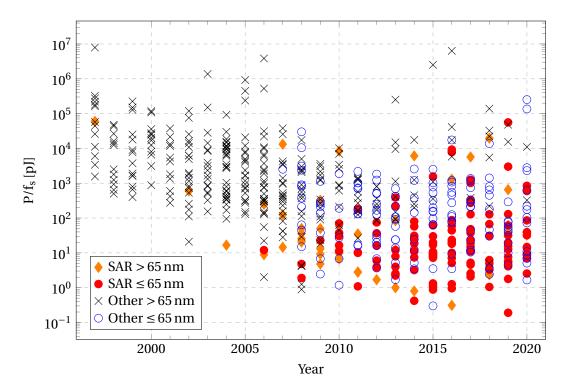

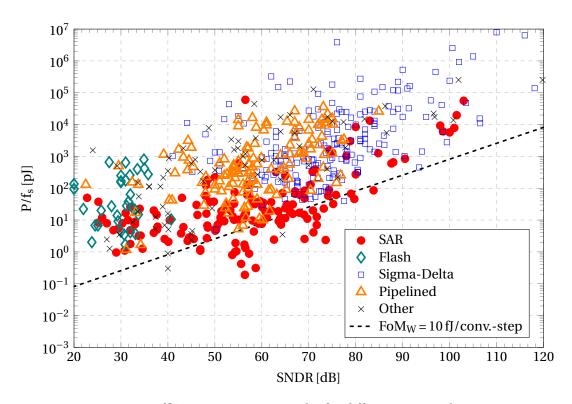

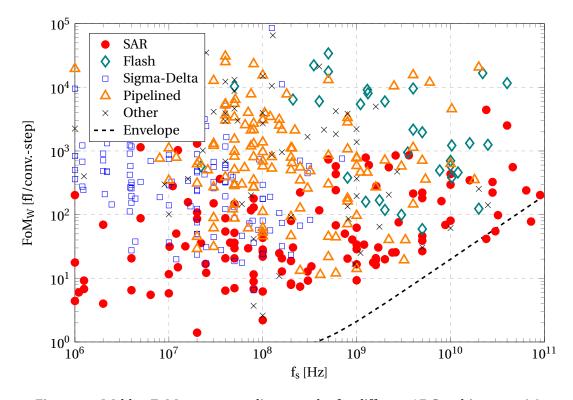

Figure 1.2, Figure 1.3, and Figure 1.4 are plotted using the data from ADC designs presented at the IEEE International Solid-State Circuits Conference (ISSCC) and the VLSI Circuit Symposium between 1997 and 2020 [1]. Figure 1.2 shows the improvement of energy per conversion of ADCs over the years. In the last two decades, energy per conversion has reduced significantly. The reason for such reduction is due to both technology scaling and architectural innovations. This plot shows the increasing popularity of SAR ADCs in the last decade and the energy efficiency of the SAR ADCs compared to other architectures. However, energy efficiency itself is not the only criterion for the choice of ADC architecture. Certain applications have certain resolution and sampling-rate requirements. Therefore, architectural comparison requires to examine these parameters as well. Figure 1.3 shows the energy efficiency versus SNDR plot and Figure 1.4 shows the Walden figure-fo-merit (FoM<sub>W</sub>) versus sampling rate (f<sub>s</sub>) plot for different ADC architectures. In Figure 1.3, SAR ADC designs achieves lower energy per conversion starting from low resolution to medium-to-high resolution. Some of the medium-to-high resolution SAR ADC designs achieve even lower than 10 fJ/conversion-step FoM<sub>W</sub>. In Figure 1.4, from 1 MS/s to 90 GS/s, SAR ADC designs achieve significantly lower FoM<sub>W</sub> compared to other architectures. As a result, SAR ADCs have become the architecture of choice in many different applications with their energy efficiency.

### 1.1 Thesis Goal

The goal of this thesis is to investigate the high-speed ADC design techniques, design, and implement a high-speed and low-power ADC with moderate-resolution for wireline applica-

Figure 1.2: Energy efficiency trend of ADCs over the years [1].

tions. Considering the speed and energy efficiency advancements in SAR ADCs fueled by both technology scaling and new design techniques in recent years, the SAR architecture is chosen as the starting point.

## 1.2 Thesis Organization

Chapter 2 gives the theory review of the SAR ADCs. First, it explains the fundamentals of SAR ADCs and important ADC metrics. Then, gives a summary of the innovative design techniques that are used in state-of-the-art high-speed SAR ADC.

Chapter 3 presents an asynchronous SAR ADC design in 65 nm CMOS. A SAR ADC architecture with a single comparator is chosen as the starting point because it is relatively simple and does not require any calibration. The proposed 9-bit asynchronous SAR ADC design uses a combination of design techniques summarized in Chapter 2 to minimize the SAR loop delay and power consumption.

Chapter 4 presents a self-calibrated delay-based LSB extraction circuit for SAR ADCs. The proposed circuit can be implemented on a SAR ADC to improve the resolution without compromising the speed and with a negligible increase in power consumption and area.

Chapter 5 presents an 8-bit loop-unrolled SAR ADC design with common-mode adaptive background offset calibration in 28 nm FDSOI. Since the sampling-rate that can be achieved

Figure 1.3: Energy efficiency versus SNDR plot for different ADC architectures [1].

Figure 1.4: Walden FoM versus sampling rate plot for different ADC architectures [1].

using only one comparator is limited, the chapter focuses on the loop-unrolling technique which uses multiple comparators. In this chapter, the common-mode variation in loop-unrolled SAR ADCs and the common-mode mismatch between the comparators due to common-mode dependency of offset is addressed. To solve the addressed issues, a common-mode adaptive background offset calibration is proposed.

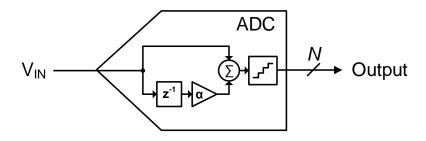

Chapter 6 presents an ADC-based receiver analog front-end design and examines the feasibility of high order PAM for moderate loss channel. The presented analog front-end consists of a CTLE and an 8×TI 7-bit SAR ADC with 2-tap embedded analog FFE. The details of the embedded FFE implementation are provided in the chapter.

Finally, conclusions are given and the future work is discussed in Chapter 7.

# 2 Overview

This chapter summarizes the error sources limiting ADC performance, lists important ADC metrics, reviews the recent innovations on high-speed ADC design.

### 2.1 ADC Errors

#### 2.1.1 Quantization Noise

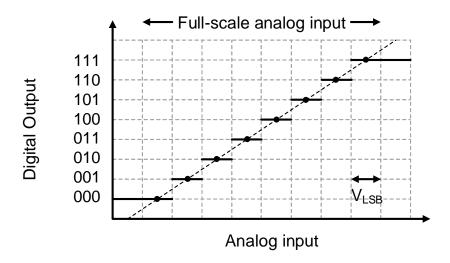

ADCs converts continuous-amplitude input signal into discrete values with quantization. Quantization noise due to the finite resolution N of an ADC limits the SNR of an ADC. Figure 2.1 shows the ideal input-output characteristic of a 3-bit ADC. For an ideal N-bit ADC, each quantization step is equal and given by

$$V_{LSB} = \frac{V_{FS}}{2^N},\tag{2.1}$$

where  $V_{FS}$  is the full-scale analog input range. Quantization error is bounded by -V<sub>LSB</sub>/2 and +V<sub>LSB</sub>/2 for input voltages within the full-scale input range as shown in Figure 2.2. Average power of quantization noise is [15]

$$P_{Q} = \frac{V_{LSB}^{2}}{12} = \frac{V_{FS}^{2}}{2^{2N}.12}.$$

(2.2)

The signal-to-quantization noise ratio (SQNR) of an ideal N-bit quantizer with full-scale sinusoidal input signal is given by

$$SQNR_{dB} = 10log \frac{P_{signal}}{P_{Q}} = 10log \frac{\frac{V_{FS}^{2}}{8}}{\frac{V_{FS}^{2}}{2^{2N}.12}} = 6.02N + 1.76.$$

(2.3)

Figure 2.1: Ideal input-output characteristic of a 3-bit ADC.

Figure 2.2: Quantization error of a 3-bit ADC.

Figure 2.3: Simple sampler circuit and its noise equivalent.

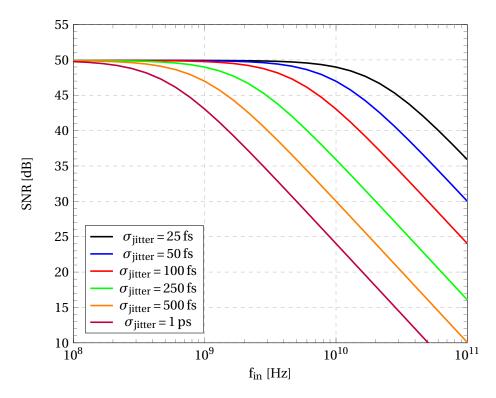

### 2.1.2 Sampling Noise

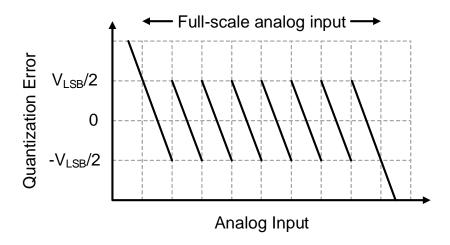

Sampling noise is a fundamental limit in sampled-data systems. kT/C sampling noise occurs because of the thermal noise of the sampling switch. Figure 2.3 shows a simple sampler circuit and the equivalent circuit for the noise estimation. The thermal noise of the equivalent sampling resistor  $4kTR_{samp}$  is multiplied by the square of the transfer function to find the noise spectrum across the sampling capacitor as

$$v_{n,samp}^{2}(f) = \frac{4kTR_{samp}}{1 + (2\pi f R_{samp} C_{samp})^{2}}.$$

(2.4)

The total noise power stored on the sampling capacitor is calculated by the integral of Equation 2.4 over all the folded bands as [16]

$$P_{n,samp} = \int_0^\infty \frac{4kTR_{samp}}{1 + \left(2\pi f R_{samp} C_{samp}\right)^2} df. = \frac{kT}{C_{samp}}.$$

(2.5)

$P_{n,samp}$  is independent from  $R_{samp}$ . As  $R_{samp}$  increases, the white noise floor increases as well. But  $P_{n,samp}$  is not effected since the bandwidth of the low-pass filtering decreases as well. Therefore, this noise is commonly referred to as kT/C noise.

For example, for  $V_{FS}$  = 500 mV at 100 C, if the kT/C sampling noise is equal to the quantization noise, the total sampling capacitance should be 256 fF for a 10-bit ADC and 16 fF for an 8-bit ADC. Having the kT/C noise equal to the quantization noise means SNR decreases by 3 dB.

### 2.1.3 Sampling Jitter

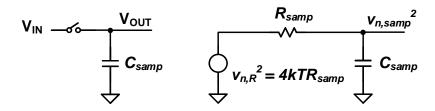

The maximum SNR value that an ADC can achieve with RMS timing jitter of  $\sigma_{\rm jitter}$  is given by

$$SNR_{jitter,dB} = 20log \frac{1}{2\pi f_{in}\sigma_{jitter}},$$

(2.6)

Figure 2.4: SNR vs. input frequency plot of an 8-bit ADC with only the effect of jitter included.

where f<sub>in</sub> is the frequency of the sinusoidal input signal.

SNR of an N-bit ADC with only the effect of jitter can be calculated by adding the quantization noise in addition to the power of jitter as

$$SNR_{jitter,N-bit,dB} = -10log\left(\frac{2}{3.2^{2N}} + \left(2\pi f_{in}\sigma_{jitter}\right)^{2}\right). \tag{2.7}$$

The corresponding SNR versus input frequency plot for an 8-bit ideal ADC is provided in Figure 2.4 for various RMS jitter values.

#### 2.2 ADC Performance Metrics

Several terms, which are used in other chapters in this thesis to characterize the ADC performance are defined in this section.

**Sampling rate** ( $f_s$ ) is the rate at which the ADC converts the analog input into a digital output. It is also referred to as sampling frequency. The unit of sampling rate is samples per second (S/s).

**Resolution** (N) is the number of bits that corresponds to the  $2^N$  different quantization levels

of the ADC.

**Signal-to-noise ratio (SNR)** is the ratio between the signal power and the total noise power including the quantization noise and the noise of the circuit and expressed as

$$SNR_{dB} = 10log \frac{P_{signal}}{P_{poise}}.$$

(2.8)

**Signal-to-noise-and-distortion ratio (SNDR)** is the ratio between the signal power and the total power of noise and distortion and expressed as

$$SNDR_{dB} = 10log \frac{P_{signal}}{P_{noise} + P_{distortion}}.$$

(2.9)

It is a commonly used metric to describe the effective resolution of the ADC. It is commonly expressed in dB.

**Spurious free dynamic range (SFDR)** is the ratio of the carrier signal power to the power of the highest spurious signal in the output.

**Effective number of bits (ENOB)** is derived from the SNDR, as

ENOB =

$$\frac{\text{SNDR}_{\text{dB}} - 1.76 \,\text{dB}}{6.02 \,\text{dB}}$$

. (2.10)

Generally, it is derived from the peak SNDR value or when a full-scale input signal is applied to the ADC.

**Figure-of-merit (FoM)** is a metric that is commonly used to compare the performance of an ADC. ADCs have many different performance metrics related to speed, resolution, and power. FoM combines several performance metrics into a single number. There are two commonly used FoM expressions for ADCs: Walden FoM [17] and Schreier FoM [18]. Walden FoM is more commonly used for low-to-medium resolution ADCs while the Schreier FoM for high-resolution ADCs. Walden FoM is expressed as

$$FoM_W = \frac{Power}{2^{ENOB} f_s}.$$

(2.11)

The unit of Walden FoM is joules per conversion-step (J/conv.-step). The lower the Walden FoM, the better the ADC performance. In this thesis, FoM refers to the Walden FoM.

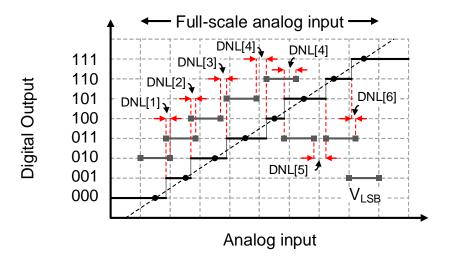

**Differential non-linearity (DNL)** is used to measure the deviation of the analog input range from the ideal LSB voltage as shown in Figure 2.5. DNL is calculated after gain and offset

Figure 2.5: DNL of a 3-bit ADC.

Figure 2.6: INL of a 3-bit ADC.

correction. DNL[i] which corresponds to the ith ADC output code is calculated as

$$DNL[i] = \frac{V[i+1] - V[i]}{V_{LSB}} - 1,$$

(2.12)

where  $V_{LSB}$  is the average step width and V[i] is the voltage that the transition from (i-1)th ADC output code to i th occurs. DNL is specified in LSBs. Positive DNL means the step width is larger than the average while negative means it is smaller. DNL[i] can be minimum -1 LSB, which means that the i th ADC output code is missing in the ADC input-output characteristic. The sum of the DNL[i] values should be zero:

$$\sum_{i=1}^{2^{N}-1} \text{DNL}[i] = 0, \tag{2.13}$$

where N is the resolution of the ADC in bits. DNL data of the first code (DNL[0]) and the last code (DNL[ $2^{N-1}$ ]) are not defined.

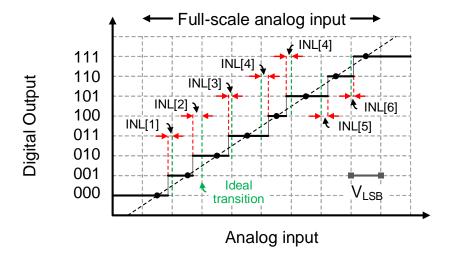

**Integral non-linearity (INL)** is the deviation of the actual transition points from the ideal in the ADC input-output characteristic as shown in Figure 2.6. Similar to DNL, INL is also given in LSBs. INL[k] can be calculated from the cumulative sum of the DNL vectors as

$$INL[k] = \sum_{i=1}^{k-1} DNL[i] = 0.$$

(2.14)

Generally, the maximum and minimum values of DNL and INL are given while specifying the performance of an ADC.

The input-output characteristic of an ADC can be measured by applying a ramp input signal. DNL and INL can also be measured with a sinusoidal input signal when an accurate ramp signal is not available. Since DNL and INL show the static performance of the ADC, generally a low-frequency input signal is used in these measurements. Code transition points for testing with sinusoidal input are calculated as [19]

$$V[i] = C - A\cos\frac{\pi H_{c}[i-1]}{S} \quad \text{for} \quad i = 1, 2, ..., (2^{N} - 1),$$

(2.15)

where C is the offset, A is the amplitude of the measured sinusoidal signal, and S is the total number of samples used in the histogram.  $H_c[j]$  is the number in the j th bin of the cumulative histogram of samples given as

$$H_{c}[j] = \sum_{i=0}^{j} H[i],$$

(2.16)

where H[i] is the number of histogram samples in code bin i.

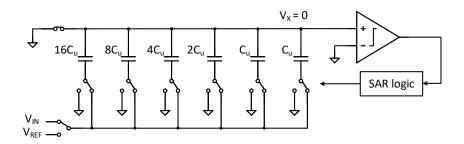

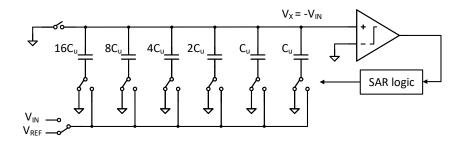

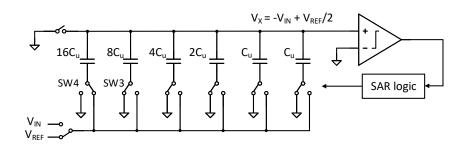

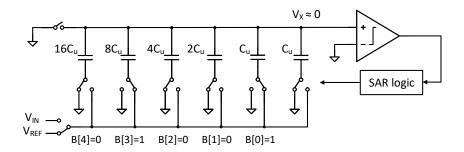

## 2.3 Conventional SAR ADC

The conventional 5-bit charge-redistribution SAR ADC is shown in Figure 2.7 for single-ended implementation [20]. It consists of a binary-weighted capacitive array, switches, a comparator, and a logic. A conversion is composed of three main operation modes. The first one is the sample mode shown in Figure 2.7. In sample mode, the top plate is connected to the ground and all the bottom plates of the capacitors in the capacitive array are connected to the input. The second mode is the hold mode shown in Figure 2.8. In the hold mode, the switch connecting the top plate to the ground is opened and the bottom plates are connected to the ground. Therefore, the top plate voltage becomes - $V_{\rm IN}$  because the sampled charge is conserved. The third mode is the redistribution mode. As a first step of the redistribution mode, the bottom plate of the largest capacitor is connected to  $V_{\rm REF}$  as shown in Figure 2.9 and the voltage at the top plate becomes

$$V_{\rm X} = -V_{\rm IN} + \frac{V_{\rm REF}}{2}.$$

(2.17)

Then the first comparison takes place. If  $V_X>0$ , the MSB of the output code B[4] is logic-1, else B[4] is logic-0. In the case  $V_X>0$ , then SW1 is returned to the ground and the SW2 is connected to  $V_{REF}$ . In the case  $V_X<0$ , then SW4 is returned to the ground; in the case  $V_X>0$ , then SW1 is kept connected to  $V_{REF}$ . Then the next switch SW3 is connected to  $V_{REF}$ . Therefore, the voltage at the top plate becomes

$$V_{X} = -V_{IN} + B[4] \frac{V_{REF}}{2} + \frac{V_{REF}}{4}.$$

(2.18)

The conversion continues in the same way until the LSB is decided. Towards the end of the conversion, the voltage at the top plate converges to zero. The switch configuration at the end of the conversion for ADC output code "01001" is provided in Figure 2.10. An N-bit SAR ADC requires N steps to find the N-bit code corresponding to the sampled input voltage.

# 2.4 High-Speed SAR ADC Design Techniques

In the last decades, several techniques have been proposed to enhance the sampling rate and the power consumption of SAR ADCs. These techniques and the technology scaling have enabled the sampling rates of SAR ADCs to exceed 1 GS/s. Most of the techniques summarized in this section are used in the ADC designs presented in the following chapters. Therefore, this section provides the basis for them.

Figure 2.7: A conventional 3-bit charge-redistribution SAR ADC in sample mode.

Figure 2.8: A conventional 3-bit charge-redistribution SAR ADC in hold mode.

Figure 2.9: A conventional 3-bit charge-redistribution SAR ADC after the first step of the redistribution mode.

Figure 2.10: Final switch configuration of a conventional 3-bit charge-redistribution SAR ADC for output code of "01001".

Figure 2.11: Timing of a 5-bit (a) synchronous and (b) asynchronous SAR ADC.

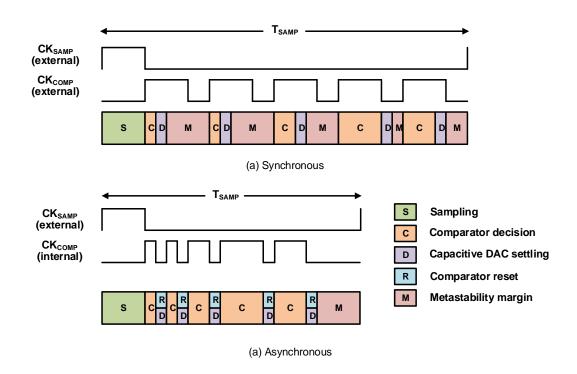

#### 2.4.1 Asynchronous Clocking

The comparator delay in a SAR ADC depends on the input voltage. In a conventional SAR ADC with a synchronous clock, the clock that initiates the comparison cycles is externally provided and limited by the worst-case comparator delay. Only one of the comparisons performed for each sample experiences a decision with input voltage less than 1/2 LSB in a binary search SAR ADC, considering the nature of the SAR algorithm. Therefore, there could be only one comparison in each conversion cycle with this worst-case delay in a binary search SAR ADC. Therefore, the synchronous clocking of the comparator in the conventional SAR architecture does not offer the optimal use of the conversion time. The asynchronous SAR architecture, first proposed in [21], improves the sampling rate by triggering the comparator asynchronously depending on the completion of the previous decision.

If the input voltage is small and comparison cannot be completed in the given time interval, the comparison is called metastable. The probability of metastable comparison increases towards the LSB decisions during the SAR conversion. By providing additional time, the probability of metastability can be improved. But in a synchronous ADC, this additional time is provided for every decision and even though only one of the comparisons can be metastable. For asynchronous SAR ADCs, the additional time to improve the metastability is added for only one comparison per conversion period and it is allocated to that metastable decision. Therefore, improving the metastability is not as costly as the synchronous ADC design in

Figure 2.12: A 5-bit SAR ADC with monotonic capacitor switching (in sample mode).

Figure 2.13: Common-mode change in a 5-bit SAR ADC with monotonic capacitor switching during SAR conversion.

terms of sampling speed [22]. The timing of synchronous and asynchronous SAR ADCs with additional time to provide metastability margin is shown in Figure 2.11.

Besides optimizing the timing, the internally generated asynchronous clock eliminates the need for a high-frequency clock. In time-interleaved ADC designs, routing of the high-speed external clock becomes harder and requires additional power consumption.

## 2.4.2 Monotonic Switching

Monotonic switching, also known as the set-and-down switching, is an energy-efficient switching method to lower the switching energy of the capacitive DAC in SAR ADCs [23, 24, 25]. It has been shown that this switching method reduces the power consumption by 81%, and the total capacitance of the capacitive DAC by 50% [23].

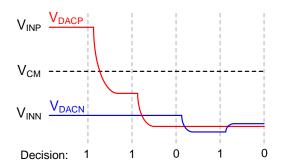

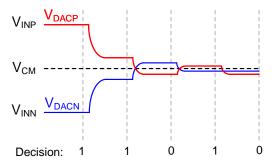

Figure 2.12 shows a SAR ADC with monotonic switching. The analog input voltage is sampled on the top plates of the capacitive DAC while all the bottom plates are connected to  $V_{REF}$

and after the top plate sampling switch turns off, the first comparison starts immediately without any prior switching. Depending on the MSB comparison, the bottom plate of the largest capacitor ( $8C_u$ ) on the higher voltage side is switched to the ground while the bottom plate of the largest capacitor ( $8C_u$ ) on the lower voltage side remains unchanged. Then, then the MSB-1 comparison takes place. Depending on the MSB-1 decision, the same procedure is applied to the second-largest capacitor ( $4C_u$ ), and the same procedure continues until the LSB is decided. The common-mode voltage of the top plates decreases at each switching step as shown in Figure 2.13.

Compared to the conventional SAR ADC switching described in Section 2.3, the monotonic switching is faster because the first comparison starts immediately after the sampling without prior switching, which saves from switching energy as well. The monotonic switching requires less switching power and reduces the logic complexity of the SAR logic since only one capacitor switches for each bit cycle. Considering that a comparator with two outputs is employed in the SAR ADC with monotonic switching, the comparator outputs are reset to the same logic level initially and one of the outputs changes its logic level depending on the comparator decision. Therefore, the bottom plates of the capacitors are controlled by the outputs of the comparator stored in a memory. Other than storing the comparator in a memory, no additional logic operation is required. Therefore logic complexity, the SAR loop delay is reduced. Furthermore, inverters can be used as the bottom plate switches since the bottom plate switching is performed only between  $V_{\rm REF}$  and the ground.

The disadvantage of the monotonic switching is that the charge injection of the sampling switch at the top-plate causes degradation in SNDR for high-resolution ADCs. The input voltage dependent charge injection problem of the top plate sampling in monotonic switching can be improved by employing a bootstrapped sampling switch.

Another disadvantage of the monotonic switching is that the common-mode of the comparator input changes during the SAR conversion, and the common-mode dependency of the comparator offset causes dynamic offset that results in a degradation in the comparator precision. Also, the comparator decision time might increase as the common-mode decreases towards the end of the SAR conversion cycle.

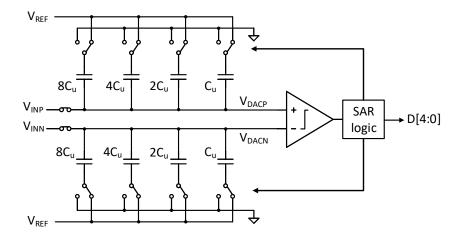

## **Splitting Monotonic Switching**

The dynamic offset problem in the monotonic switching due to common-mode variation can be solved by splitting the capacitors [26, 27, 28, 29] as shown in Figure 2.14. By splitting all the capacitors in the capacitive DAC into two halves, constant common-mode can be provided for all the comparisons [27] or only some of the capacitors can be split to keep the common-mode in a small range that does not degrade the comparator precision severely [28, 29]. In Figure 2.14, all the capacitors in the capacitive DAC except for the LSB is split into two halves. During the sampling, bottom plates of the upper row of the split capacitors are connected to  $V_{\rm REF}$  while the bottom plates of the lower row are connected to the ground. Depending of

Figure 2.14: A 5-bit SAR ADC with split monotonic capacitor switching (in sample mode).

Figure 2.15: Common-mode change during SAR conversion in a 5-bit SAR ADC with split monotonic capacitor switching.

Figure 2.16: A 5-bit Loop-Unrolled SAR ADC with monotonic capacitor switching.

the comparator decision, either ( $C_{XPa}$  and  $C_{XNb}$ ) or ( $C_{XPb}$  and  $C_{XNa}$ ) switch while the others remain unchanged. Therefore, the voltage changes in  $V_{DACP}$  and  $V_{DACP}$  are symmetrical and the common-mode is constant for the split capacitor switchings as shown in Figure 2.15.

#### 2.4.3 Two Alternating Comparators

In a SAR ADC design with a single comparator, the comparator needs to be reset to remove the history from the previous decision after the comparator decision is complete. While the comparator is reset, capacitive DAC settles in parallel. In a SAR ADC design with a short capacitive DAC settling time, the sampling rate is limited by the reset time of the comparator.

SAR ADC design presented in [27] employs two comparators to remove the reset time of the comparator from the critical path. Two comparators alternate; while one of them is being reset, the other makes its decision as shown in Figure 2.16. Since this architecture uses more than one comparator, any offset mismatch between the comparators causes dynamic offset errors; therefore, comparator offset calibration should be included in the design.

Figure 2.17: A 5-bit Loop-Unrolled SAR ADC with monotonic capacitor switching.

#### 2.4.4 Loop-Unrolling

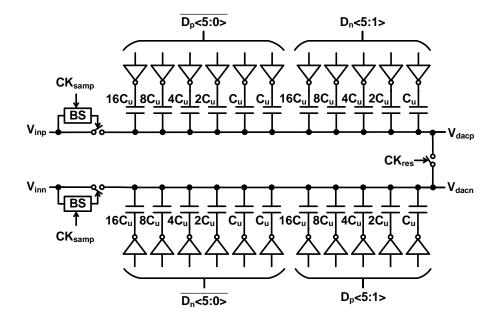

The loop-unrolled (LU) SAR architecture, also known as domino-SAR, first proposed in [30], uses N comparators for N-bit conversion and the outputs of the comparators control the capacitive digital-to-analog converter (DAC) directly without any additional logic operation as shown in Figure 2.17. The 6-bit SAR ADC in [30] combines loop-unrolling with the monotonic switching to minimize the SAR loop delay. Unlike the architecture with two alternating comparators, the LU-SAR architecture does not require demultiplexing of the comparator outputs to generate the capacitive DAC control bits. Because the additional delay due to demultiplexing is avoided, loop-unrolling enables smaller SAR loop delay with minimal logic complexity. Moreover, loop-unrolling also mitigates electro-migration issues since each comparator is triggered only once per SAR conversion. Similar to the architecture with two alternating comparators, LU-SAR architecture requires comparator offset calibration to prevent errors due to dynamic offset during the SAR conversion.

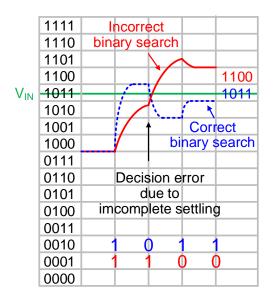

### 2.4.5 DAC Redundancy

Conventional SAR ADC uses binary-weighted capacitive DAC. Each voltage step at the output of the capacitive DAC scales down by two with each capacitive switching. Capacitive DAC should settle within 1/2 LSB before the next decision is made to prevent errors. Settling time

Figure 2.18: Binary search with decision error due to incomplete capacitive DAC settling.

|                 | 1111 | Decision | Redundant step     |

|-----------------|------|----------|--------------------|

|                 | 1110 | error    |                    |

|                 | 1101 |          |                    |

|                 | 1100 |          |                    |

| $V_{\text{IN}}$ | 1011 | - /      | 1011               |

|                 | 1010 |          |                    |

|                 | 1001 | /*       |                    |

|                 | 1000 | / \      | Redundant          |

|                 | 0111 | Redu     | undant search with |

|                 | 0110 | searc    | ch with complete   |

|                 | 0101 | incor    | nplete settling    |

|                 | 0100 | set      | tling              |

|                 | 0011 |          |                    |

|                 | 0010 | 1 (      | 1 1 0              |

|                 | 0001 | 1 1      |                    |

|                 | 0000 |          |                    |

Figure 2.19: Redundant search with decision error due to incomplete capacitive DAC settling.

Figure 2.20: 2-bit per conversion step SAR ADC.

depends on the capacitor size, the resistance of the switches, and the output impedance of the voltage reference, and it might take significant time for large capacitive DACs. Figure 2.18 shows the output voltage of a binary capacitive DAC during SAR conversion without and with error due to incomplete settling. The error causes the conversion error to be larger than  $\pm 1/2$  LSB which is the boundary of the quantization error.

The settling time of the capacitive DAC can be the bottleneck in high-speed SAR ADCs, especially the settling time of the MSB capacitor. Implementing redundancy in the capacitive DAC allows us to recover errors due to incomplete DAC settling [31, 32]. Redundancy can be implemented by using radix < 2 [33, 34] or radix = 2 with redundant steps [35, 27]. In Figure 2.19, the output voltage of a redundant capacitive DAC with one additional redundant step during SAR conversion (weights = 4, 2, 1, 1) is shown. Since the total weight of the remaining steps is greater than the erroneous step, it is possible to recover the error and reach the correct code. Redundancy makes it possible to reach a code level from multiple paths as opposed to the binary search where reaching a code is possible using only one path.

Redundancy in capacitive DAC can correct other dynamic errors such as decision errors due to noise and or errors due to offset mismatch in loop-unrolled SAR ADCs. However, redundancy might cause the number of decisions with input voltage less than 1/2 LSB and might increase the probability of metastable decisions.

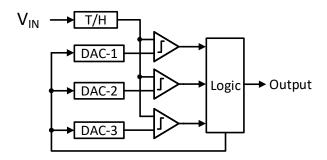

#### 2.4.6 Multi-bit per Conversion Step

Conventional SAR ADCs convert only one bit per conversion step. By increasing the number of bits resolved in each step, the number of conversion steps can be reduced, and the sampling rate can be increased as a result [36, 37, 38]. To resolve multiple bits in one conversion step, multiple comparators are employed as in flash ADC architecture. Figure 2.20 shows the block diagram of a 2-bit per conversion step SAR ADC. Since multiple comparators are employed, the comparator offset should be matched for the conversion accuracy.

Figure 2.21: Two-Stage Pipelined SAR ADC.

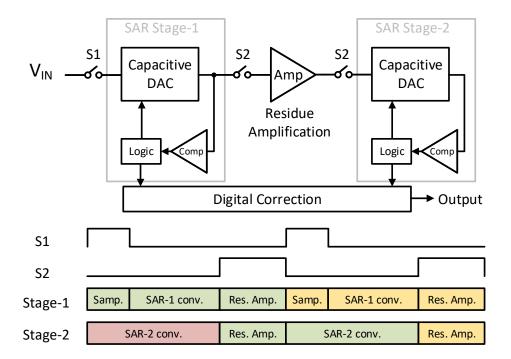

#### 2.4.7 Pipelined SAR

Pipelined SAR ADC architecture is based on pipelining two or more stages with residue amplifiers between them. Figure 2.21 shows the block diagram and timing of a two-stage pipelined SAR ADC. Pipelining SAR stages increase the sampling rate because the two SAR stages operate in parallel while resolving different samples. Amplification of the residue between the stages decreases the comparator noise requirements of the following stages. Therefore, pipelined SAR architecture is useful in achieving high resolution in addition to a higher sampling rate. In [39], a single-channel 10-bit two-stage pipelined SAR ADC achieving 50 dB SNDR at 1.5 GS/s is presented.

### 2.4.8 Time-Interleaving

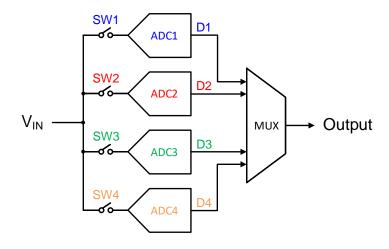

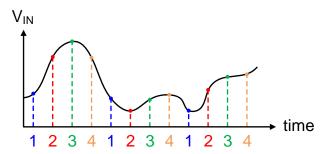

Time-interleaving is a technique that combines multiple ADCs in an interleaved fashion to increase the conversion rate where the conversion rate of a single-channel ADC is not sufficient. In Figure 2.22, 4-way time-interleaved ADC is shown as an example. The sampling rate of  $f_s$  can be achieved using M channels with the sampling rate of  $f_s/M$  in a time-interleaved configuration.

Mismatches between the interleaved channels, such as offset, gain, timing, and bandwidth mismatches, degrade the linearity of the time-interleaved ADC.

Figure 2.22: Time-Interleaving.

**Offset mismatch** between the ADC channels causes spurs in the output spectrum of the interleaved ADC system located at [40]

$$f_{spur,offset} = k \times \frac{f_s}{M} \qquad k = 1, 2, ..., M.$$

(2.19)

In SAR ADCs, the gain of the ADC depends on the capacitive DAC, its parasitics, and the capacitive DAC reference voltage. **Gain mismatch** between the time-interleaved ADC channels causes spurs dependent on the frequency of the input signal located at [40]

$$f_{spur,gain} = \pm f_{in} + \frac{k}{M} f_s$$

$k = 1, 2, ..., M.$  (2.20)

The time intervals between the consecutive sampling instances are equal in an ideal time-interleaved ADC system. However, **timing skew mismatch** occurs when the timing instant is skewed compared to its ideal value. This timing skew is not random as jitter. Spurs due to skew mismatch depends on the frequency of the input signal and are at the same frequencies

as the spurs due to gain mismatch [40]:

$$f_{spur,skew} = \pm f_{in} + \frac{k}{M} f_s$$

$k = 1, 2, ..., M.$  (2.21)

**Bandwidth mismatch** between the sampling networks of the ADC channels causes input frequency dependent amplitude and phase errors. Similar to gain and skew mismatch, bandwidth mismatch causes spurs in the spectrum also at [40]

$$f_{spur,bandwidth} = \pm f_{in} + \frac{k}{M} f_s$$

$k = 1, 2, ..., M.$  (2.22)

Offset and gain mismatch errors can be corrected by post-processing the digital ADC output [41]. But digital correction after the quantization is not as precise as the analog correction and reduces the dynamic range of the system [42]. In [13], the offset of each ADC channel is internally auto-zeroed by background calibration, the gain of each channel can be adjusted by changing the reference voltage of the capacitive DAC using R-3R ladder driving the reference buffer, and the skew between the clock phases is digitally trimmed [13].

# 3 Asynchronous SAR ADC<sup>1</sup>

This chapter presents a low-power 9-bit 222 MS/s single-bit/cycle asynchronous SAR ADC design. The proposed design combines asynchronous clocking, top plate sampling, binary-weighted custom-designed capacitive digital-to-analog converter (CDAC) with small unit capacitors, splitting monotonic capacitor switching with constant capacitive DAC common-mode except for the last switching, and dynamic SAR memory to optimize both power consumption and SAR loop delay using a single comparator in 65 nm. Measurement results show that the 9-bit SAR ADC achieves 47.6 dB SNDR and 29.6 fJ/conversion-step figure-of-merit (FoM) near Nyquist frequency at 222 MS/s, consuming 1.07 mA from a 1.2 V supply. All the building blocks in the SAR ADC are dynamic, it does not consume any static current, and the power consumption scales linearly with the sampling rate over a wide range. Therefore, it can operate at sampling rates up to 222 MS/s with almost constant figure-of-merit (FoM), providing flexibility in terms of power consumption.

#### **Outline**

This chapter is organized as follows. Section 3.1 describes the proposed SAR ADC architecture with circuit details, and explains the techniques used to achieve faster sampling rate and lower power consumption. Section 3.2 summarizes the measurement results and Section 3.3 concludes the chapter.

### 3.1 ADC Architecture

#### 3.1.1 Overview

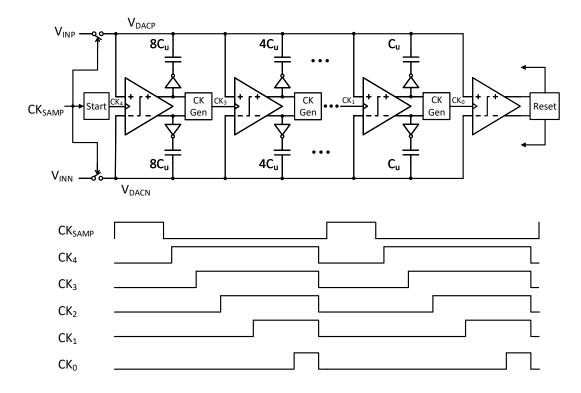

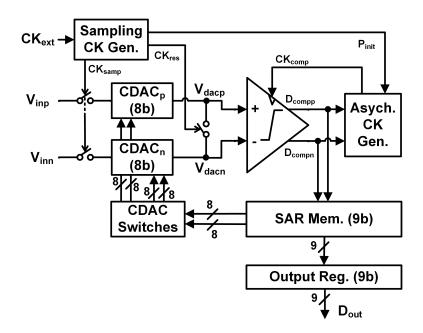

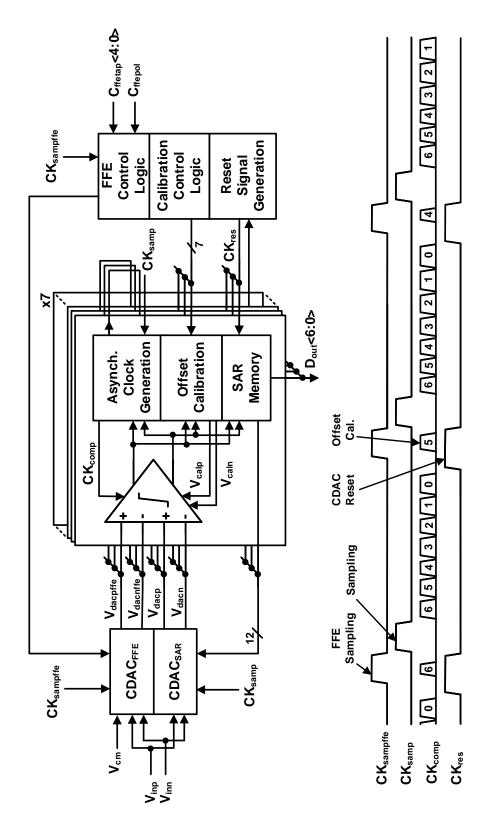

Figure 3.1 shows the block diagram, and Figure 3.2 shows the timing scheme of the proposed 9-bit SAR ADC. The ADC consists of two bootstrapped sampling switches, a sampling clock

<sup>&</sup>lt;sup>1</sup>This chapter is based on: A. Akkaya, F. Celik, and Y. Leblebici, "A Low-Power 9-Bit 222 MS/s Asynchronous SAR ADC in 65 nm CMOS," *2020 IEEE International Symposium on Circuits and Systems (ISCAS)*, Sevilla, 2020, pp. 1-5, (©IEEE) [29].

Figure 3.1: Block diagram of the proposed asynchronous SAR ADC.

Figure 3.2: Timing scheme of the proposed asynchronous SAR ADC.

generation block, two 8-bit capacitive DACs, capacitive DAC switches that drive the bottom plates of the capacitive DAC capacitors, a reset switch that shorts the top plates of the capacitive DAC capacitors after each SAR conversion, a dynamic comparator, an asynchronous clock generation block, a SAR memory to control the capacitive DAC switches, and an output register.

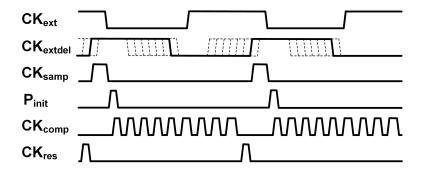

The differential input signal is sampled by the sampling clock  $CK_{samp}$  via top plate sampling; therefore, the first comparison starts immediately after the sampling without any charge redistribution, saving both energy and time. Bootstrapping is applied to the sampling switches to sample the differential input signal with sufficient linearity over a wide input voltage range.  $CK_{samp}$  which controls the bootstrapped sampling switches is generated internally in the sampling clock generator block using the external clock with 50% duty cycle  $CK_{ext}$  and the delayed  $CK_{ext}$ , namely  $CK_{extdel}$ . As shown in Figure 3.2,  $CK_{samp}$  is generated by the AND operation of  $CK_{ext}$  and  $CK_{extdel}$ . The duration of the sampling interval can be adjusted by

Figure 3.3: capacitive DAC with bottom plate switches.

selecting different delay line outputs. The beginning of the tracking is decided by the rising edge of  $CK_{extdel}$ , and the input tracking always ends with the falling edge of  $CK_{ext}$ . Since the sampling precision depends on the falling edge jitter of the sampling clock which does not depend on  $CK_{extdel}$ , the jitter requirement of the delay line is relaxed.

A StrongARM latch [43] is used as a comparator. Since it is fully dynamic, it does not consume any static power. Because only one comparator is used for all decisions and the comparator input common-mode is almost constant, its offset does not degrade the precision; therefore, offset calibration is not required. The comparator clock is generated asynchronously to shorten the overall SAR conversion time and to avoid a fast external clock.

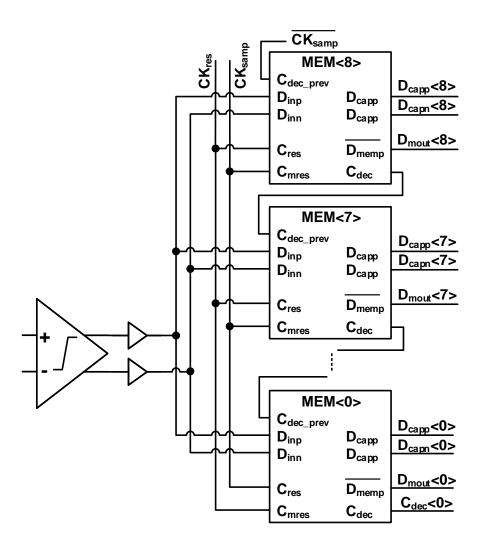

A SAR memory block replaces the SAR logic in this design. It generates the control signals of the capacitive DAC switches that drives the bottom plates of the capacitive DAC capacitors and provides the ADC output bits which correspond to the result of the successive-approximation. Then, the ADC output bits are sampled by the output registers.

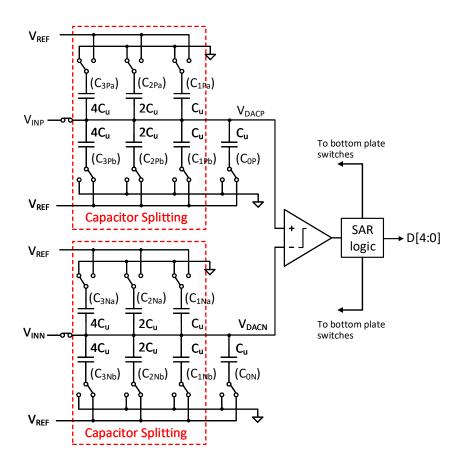

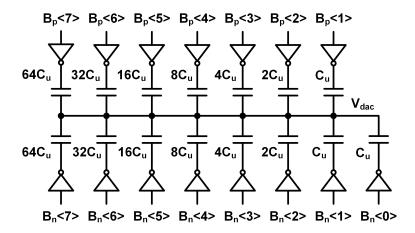

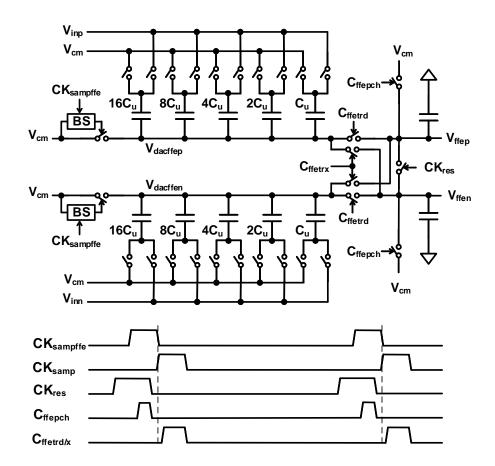

#### 3.1.2 Capacitive DAC

Top plate sampling with monotonic capacitor switching provides the advantage of using 8-bit capacitive DACs in a 9-bit SAR ADC. Binary-weighted capacitive DACs also serve as the sampling capacitors. The splitting monotonic capacitor switching [26] which provides constant common-mode voltage is applied in the capacitive DAC except for the last capacitor, as shown in Figure 3.3. Since the comparator offset is dependent on the input common-mode, constant common-mode switching provides better comparator precision. The last capacitor is switched only on the single side, in  $CDAC_p$  or  $CDAC_n$ , to decrease the total number of unit capacitors in the capacitive DAC from 510 to 255. Because the common-mode shift generated by the single side switching of the last capacitor is small, its effect on the comparator precision is negligible. capacitive DAC switches are implemented using inverters and they only use

Figure 3.4: Bootstrapping with ideal switches.

Figure 3.5: Schematic of the bootstrapped switch.

the supply voltage provided off-chip as reference voltage. Besides being a power efficient switching scheme, splitting monotonic switching provides faster SAR loop operation with reduced logic complexity because the bottom plates of the capacitors in capacitive DAC are directly controlled by the comparator decisions stored in a memory. The capacitive DAC is custom-designed to keep the size of the unit capacitor small (0.7 fF). Small unit capacitor size helps to have a smaller area, less parasitics, less routing, less switching energy, and faster capacitive DAC settling although it degrades the capacitor matching. Moreover, the total sampling capacitance is large enough to meet the kT/C noise requirement for 9-bit resolution.

# 3.1.3 Bootstrapped Sampling Switch

Bootstrapped switches are used for sampling the input signal with better linearity. Sampling linearity of a simple NMOS switch or a T-gate switch is limited because both on-resistance and the amount of charge injected when the switch is turned off depend on the input voltage. Since top plate sampling is employed in the capacitive DAC, the input voltage dependent charge injection affects the sampling linearity negatively. The bootstrapping technique ensures a constant gate-source voltage for a wide range of input voltages and achieves better sampling linearity.

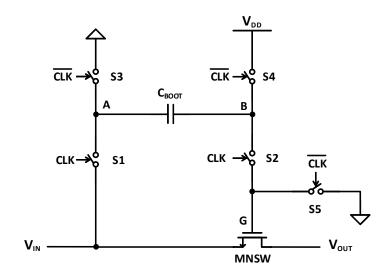

Figure 3.4 shows the implementation of bootstrapping on an NMOS switch with ideal switches [44]. Bootstrapping the sampling switch provides a constant gate-source voltage of  $V_{DD}$  during the sampling. When the clock (CLK) is low, the bootstrapped switch is in the precharging phase. In the precharging phase, S3 connects node-A to the ground and S4 connects node-B to  $V_{DD}$ ; therefore, the bootstrapping capacitor  $C_{BOOT}$  is precharged to  $V_{DD}$ . The gate of the sampling switch, node-G is connected to the ground via S5, hence the sampling switch MNSW is turned-off. In the sampling phase, S3, S4, and S5 turn off; S1 and S2 turn on. Since  $C_{BOOT}$  is precharged to  $V_{DD}$  and node-A is connected to  $V_{IN}$ , node-G becomes  $V_{DD}$ + $V_{IN}$ . As a result, the gate-source voltage of the sampling switch MNSW is equal to  $V_{DD}$ , independent of the  $V_{IN}$ .

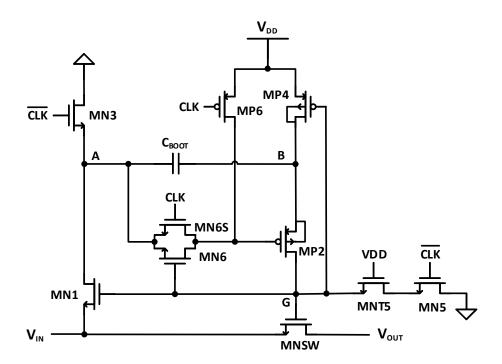

The schematic of the bootstrapped switch is depicted in Figure 3.5 [44]. MN1, MP2, MN3, MP4, and MN5 correspond to the switches S1, S2, S3, S4, and S5 in Figure 3.4, respectively. This bootstrapped switch supports rail-to-rail input. The following modifications provide reliable operation even when  $V_{IN} = V_{DD}$ , which is the worst case. The gate of MN1 is controlled by the boosted voltage to ensure conductivity even when  $V_{IN} \ge V_{DD}$ - $V_{TH}$ . MP6 connects the gate of MP2 to  $V_{DD}$  to turn MP2 off in the precharging phase.

Unlike the simple implementation given in Figure 3.4, the gate of MP2 is not controlled by  $\overline{\text{CLK}}$  or connected to the ground to turn it on to prevent the gate-source voltage of MP2 to become -2V<sub>DD</sub> when V<sub>IN</sub> = V<sub>DD</sub>. MN6S connects node-A to the gate of MP2 at the beginning of the sampling phase to initiate the conductivity of MP2. MNS6 is not conductive when node-A rises above V<sub>DD</sub>-V<sub>TH</sub>. The addition of MN6 ensures that the gate of MP2 could reach up to DD. The conductivity of MN6 is loop dependent; therefore, it is turned on after the voltage on node-G rises. To ensure that MP4 is off during the sampling phase, its gate is controlled by the

voltage on node-G instead of CLK. MNT5 is added to prevent the gate-drain voltage of MN5 to exceed  $V_{\rm DD}$ . The bulks of MP4 and MP2 are connected to the node-B, which has the highest potential, instead of  $V_{\rm DD}$ .

The parasitic capacitance at node-B could be large due to the well capacitance. Due, to this large parasitic capacitance at node B, the gate-source voltage of the sampling switch MNSW becomes less than  $V_{DD}$  during the sampling phase. To achieve a gate-source voltage closer to  $V_{DD}$ , a larger  $C_{BOOT}$  is required.

Since bootstrapping the sampling switch provides a gate-source voltage of  $V_{\rm DD}$ , a smaller sampling switch can be employed. Using a smaller switch decreases the non-linear junction parasitic capacitance at the top plate of the capacitive DAC. This non-linear parasitic capacitance introduces dynamic gain error during the SAR conversion and decreases the conversion accuracy of the SAR ADC.

#### 3.1.4 SAR Memory

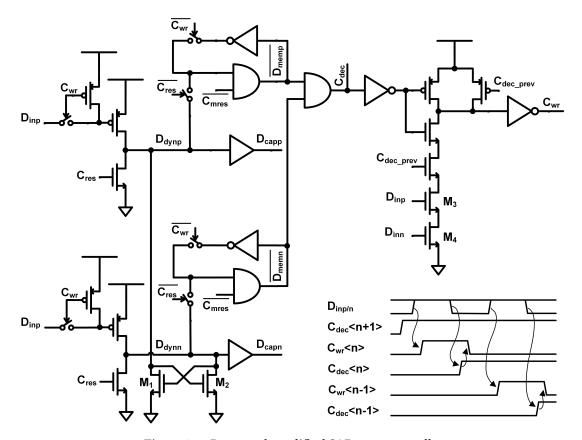

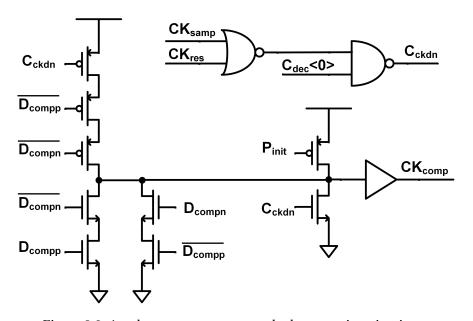

Thanks to the splitting monotonic switching method, differential comparator outputs should only be stored and fed to the capacitive DAC switches without any complex logic operation. Therefore, a SAR memory can replace the SAR logic implemented with the state machine approach in the traditional SAR architecture. The block diagram of the SAR memory is shown in Figure 3.6, and each SAR memory cell is implemented in dynamic logic to improve the speed and the power efficiency, as shown in Figure 3.7. The proposed memory cell is based on [27]; however, there are some modifications applied to prevent potential problems with the implementation of this memory cell with the proposed SAR ADC design. Writing to the memory cell is enabled by the  $C_{\rm wr}$  signal generated internally. The logic circuitry that generates  $C_{\rm wr}$  is modified by adding  $M_3$  and  $M_4$  in series. Therefore, it is ensured that the writing to a cell is activated after the comparator is reset to prevent the previous decision to be written to the current cell.

The memory cell operates by pulling up one of the output nodes,  $D_{capp}$  or  $D_{capn}$ , which are reset to logic-0 previously. The SAR memory cell in the literature [27] is modified also by adding cross-coupled NMOS transistors,  $M_1$  and  $M_2$  in Figure 3.7, between the dynamic nodes  $D_{dynp}$  and  $D_{dynn}$  to prevent both of the dynamic nodes to be pulled-up at the same time. Since it is implemented using dynamic logic, once the  $D_{dynp}$  or  $D_{dynn}$  is pulled-up, they cannot be pulled-down until the next SAR conversion, if the cross-coupled NMOS transistors are not added. In this case, any incorrect pull-up cannot be recovered; if both  $D_{dynp}$  and  $D_{dynn}$  are pulled-up, the SAR conversion cannot continue properly, and the ADC gives a wrong output code. This problem might happen especially when the differential input voltage of the comparator is very small; the comparator cannot resolve the input quickly and the waveform of the comparator outputs becomes similar to the waveforms shown in Figure 3.8. Since both comparator outputs might be discharged together, the following logic might propagate this as logic-0 to the memory. Modifying the SAR memory cell by adding the cross-coupled NMOS

Figure 3.6: SAR memory.

#### transistors prevents this error.

The bottom plate switches of the differential capacitive DACs are controlled by  $D_{capp}$ ,  $D_{capn}$  and the inverted versions of them. Before each sampling phase,  $CK_{res}$  resets the outputs of the SAR memory which control the capacitive DAC switches, also the differential capacitive DAC outputs are shorted before each input tracking starts. The latch loops that store the comparator decisions in the memory cells are reset with the rising edge of the  $CK_{samp}$  allowing enough time margin for the SAR ADC outputs to be sampled by the output registers before a new conversion begins.

Figure 3.7: Proposed modified SAR memory cell.

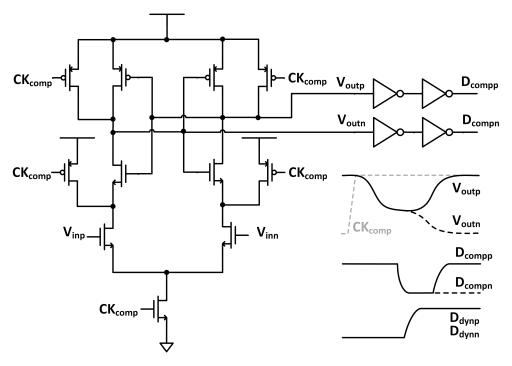

### 3.1.5 Asynchronous Clock Generation

Asynchronous clock generation circuitry shown in Figure 3.9 generates the asynchronous comparator clock  $CK_{comp}$  using the comparator outputs. The first rising edge of the asynchronous comparator clock is generated with the  $P_{init}$  signal after the sampling of the input. Then, after one of the comparator outputs,  $D_{comp}$  or  $D_{comn}$ , goes to logic-0, the  $CK_{comp}$  is pulled down. After both comparator outputs are reset to logic-1,  $CK_{comp}$  rises again. It is verified by the simulation results that the rising edge of the clock is generated after the capacitive DACs settle. After the last comparator decision,  $C_{dec}$ <0> signal generated in the SAR memory goes to logic-1 and  $CK_{comp}$  is kept at logic-0 until resetting the SAR memory before the next conversion. While the sampling clock  $CK_{samp}$  or the reset signal  $CK_{res}$  is high,  $CK_{comp}$  is also forced to be logic-0.

# 3.2 Measurement Results

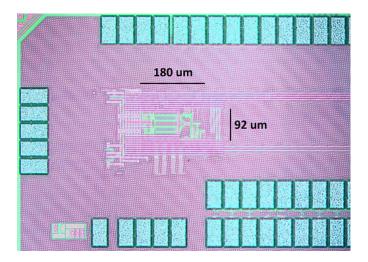

The prototype ADC is fabricated in 65 nm CMOS and it occupies an active area of 92  $\mu$ m × 180  $\mu$ m (0.017 mm<sup>2</sup>) as shown in the micrograph in Figure 3.10.

Figure 3.8: Comparator and the potential SAR memory error without the cross-coupled NMOS transistors.

Figure 3.9: Asychronous comparator clock generation circuitry.

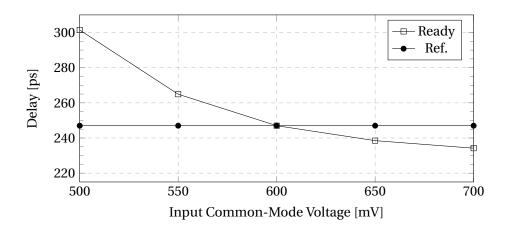

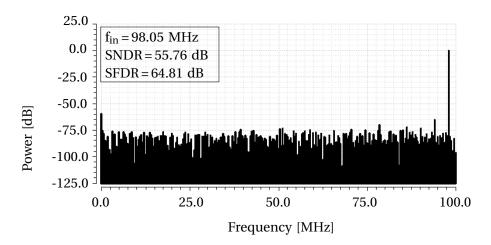

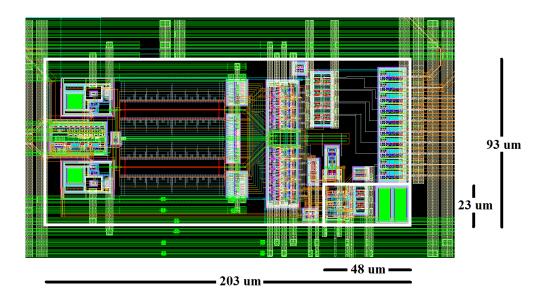

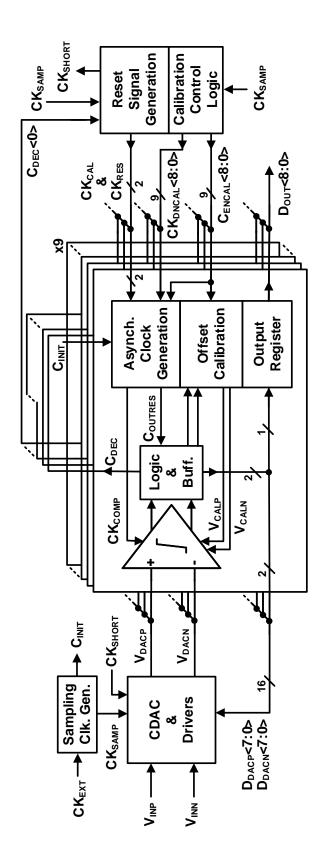

Figure 3.10: Chip micrograph.