# Enhancement Mode Tri-gate GaN Power Devices and Logic Circuits

Présentée le 9 avril 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de dispositifs semiconducteurs de puissance Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### Minghua ZHU

Acceptée sur proposition du jury

Prof. D. Dujic, président du jury

Prof. E. D. N. Matioli, directeur de thèse

Dr T. Detzel, rapporteur

Prof. B. Bakeroot, rapporteur

Prof. A. Rufer, rapporteur

### Acknowledgements

This has always been such a wonderful journey to complete my PhD in EPFL. First of all, I would like to thank my supervisor and my best friend prof. Elison Matioli for having accepted me in POWERlab since 2016. His knowledge, insight, and continuous support during my whole PhD journey would inspire me forever in my future life. He was always there for help when I met any obstacle in my research or daily life.

I would also thank prof. Drazen Dujic, prof. Alfred Rufer, prof. Benoit Bakeroot and Dr.Thomas Detzel for reviewing my thesis and fruitful discussions during the doctoral oral exam. Their suggestions are extremely helpful for improving my thesis. I would also like to thank prof. Maher Kayal and prof. Alfred Rufer as the jury for my PhD candidacy exam for defining my research orientation.

I would like also to thank all my colleagues that have been worked together. In particular, I thank Muriel and Anne-Francoise for their hard administrative work and their help for my personal issues as well, which is essential for completing my PhD. I would like to thank Jun and Giovanni for setting up the measurement equipments and creating the process flow for us. I would like to thank Catherine for her help for GaN physics related simulations, long cooperation and her help to my family. I would like to thank Riyaz for answering a lot of my basic questions when I was a beginner in GaN field. I would like to thank Armin always act as good friend and always been helpful. I would like to thank Mohammad Luca, Pirouz and Chao for their academic cooperation and discussions. A big thanks also goes to Reza, Taifang, George, Remco, Nirmana, Alessandro, Martel, Firmin, Jianing, and Dante for both work and all the time spent together. I would also like to thank all the staff members in CMi and IPHYS for their continuous support during the fabrication process.

A huge thanks goes to my wife Shuang. She always cheer me up when I got stucked during the research and her unconditional support for my life in Lausanne. Especially, she spent much more time to take care of the babies to make our family works more smoothly. Also I would like to thank my two lovely boys: Jian and Yi. You are the best gift for us and you will alway relieve our tiredness with your lovely smile.

Last but not least, I would like to thanks my family back in China: My fater Shuisheng, my mother Taohua, my elder brother Guanghua, my sister Yanqin, my fater-in-law Shunqi, and mother-in-law Hong. I could not achieve my success without all your support. The PhD is also dedicated for you all!

Lausanne, 16 December 2020

Minghua ZHU

### **Abstract**

Gallium Nitride (GaN) is one of the most promising materials for high frequency power switching due to its exceptional properties such as large saturation velocity, high carrier mobility, and high breakdown field strength. The high switching frequency of GaN-based power converters can lead to a significant reduction of the size of passive components, such as capacitors and inductors, and thus, increasing the power density of the overall system .

Due to the polarization effect induced high density and high mobility 2DEG in AlGaN/GaN heterostructure, GaN HEMT is an intrinsic normally-on (D-mode) transistor. However, normally-off transistors are required in most power eletronics system for safe operation and easier driver design. Despite the presence of several commercial GaN HEMT based devices, current GaN device performance is far from the fundamental material capabilities, as relatively large on-resistance ( $R_{\rm ON}$ ), smaller threshold voltage ( $V_{\rm TH}$ ) and insufficient breakdown voltage ( $V_{\rm BR}$ )

.

Recently, tri-gate structures are attracting considerable attention due to their better gate control and enhanced  $V_{\rm BR}$  compared to planar devices, without degrading the  $R_{\rm ON}$ . In addition, tri-gates allow a controllable positive shift of  $V_{\rm TH}$  by changing the fin width, due to the partial relaxation of the AlGaN barrier and the enhanced electrostatic control from the tri-gate sidewalls. This would offer the possibility to maintain high  $V_{\rm TH}$  and low  $R_{\rm ON}$  at the same time.

In this thesis, we propose a few technologies combined with tri-gate structure to overcome these challenges. Firstly, we demonstrate normally-off GaN metal-oxide-semiconductor field-effect transistors (MOSFETsbased on the combination of tri-gate with barrier recess in the gate region to yield a more positive  $V_{\rm TH}$ , while maintaining a low  $R_{\rm ON}$  and high current density ( $I_{\rm D}$ ). The tri-gate structure offer excellent channel control, enhancing the  $V_{\rm TH}$  up to +1.4 V at 1 $\mu$ A/mm for the recessed tri-gate, along with a much reduced hysteresis in  $V_{\rm TH}$ , and a significantly increased transconductance ( $g_{\rm m}$ ). Additional conduction channels at the sidewalls of the tri-gate trenches compensated the degradation in  $R_{\rm ON}$  from the gate recess, resulting in a small  $R_{\rm ON}$  of 7.32 ± 0.26  $\Omega$ ·mm for gate to drain length  $L_{\rm GD}$  of 15  $\mu$ m, and an increase in the maximum output current ( $I_{\rm D}^{\rm max}$ ).

Secondly, we propose a novel concept for normally-off GaN MOS-HEMTs based on the combination of tri-gate, p-GaN, and MOS structures to achieve low  $R_{\rm ON}$  and high  $V_{\rm TH}$ . The p-GaN is used to change the band structure and reduce the carrier density ( $N_{\rm s}$ ) combined with the tri-gate structure for a high  $V_{\rm TH}$ . The gate control is mainly achieved from field-effect through the tri-gate sidewalls, and does not rely on injection of gate current. The MOS structure enables much

larger gate voltages ( $V_G$ ) and the effective sidewall modulation results in excellent switching performance at high switching frequencies. In addition, this concept eliminates the need for thin barriers (typical in p-GaN devices), which combined to the conduction channels formed at the tri-gate sidewalls, resulted in a smaller  $R_{ON}$  compared with planar p-GaN structures.

Finally, we investigated NMOS GaN-based logic gates including NOT, NAND, and NOR by integration of E/D-mode GaN MOSHEMTs. The GaN NMOS inverter was achieved with logic swing voltage of 4.93 V at a supply voltage of 5 V, low-input noise margin of 2.13 V and high-input noise margin of 2.2 V at room temperature. However, these logic gates suffer from unstable transient voltage, low noise margin, and high logic leakage current. Additionally, the large size mismatch between the E-mode and D-mode transistors hinders their compact integration. Thus, high-performance logic gates with monolithic integration of tri-gate E/D-mode tri-gate MOSHEMTs were fabricated. The tri-gate structure in the logic gate offers unique advantages compared with conventional planar E/D-mode design with much compact size match and more stable  $V_{\rm TH}$ .

The results in this thesis reveal the great potential of GaN transistors and GaN based logic gate for high switching frequency, which would pave the path for future GaN power IC.

Key words: HEMT, GaN transistors, power device, III-Nitride,tri-gate, trench conduction, breakdown voltage, on resistance

### Résumé

Le nitrure de gallium (GaN) est l'un des matériaux les plus prometteurs pour la commutation de puissance à haute fréquence en raison de ses propriétés exceptionnelles telles que la grande vitesse de saturation, la haute mobilité et la tension de claquage élevée. La fréquence de commutation élevée des convertisseurs de puissance à base de GaN peut conduire à une réduction significative de la taille des composants passifs, tels que les condensateurs et les inductances, et donc à augmenter la densité de puissance de l'ensemble du système.

En raison de la haute densité du gaz électronique à deux dimensions (2DEG) induit par la polarisation, transistor AlGaN/GaN à electrons à haute mobilité (AlGaN/GaN HEMT) est normalement à l'état passant. Cependant, la plupart des systèmes électroniques de puissance necessitent des tarnsistors normalement bloqués pour la sécurité de fonctionnement. Malgré la présence de plusieurs appareils commerciaux basés sur GaN HEMT, les performances actuelles des appareils GaN sont loin des capacités des matériaux fondamentaux à cause de la résistance à l'état passant relativement élévée ( $R_{\rm ON}$ ), tension de seuil trop petite ( $V_{\rm TH}$ ) et la tension de claquage insuffisante ( $V_{\rm BR}$ ).

Récemment, les structures à trois grilles ont attiré l'attention considérable en raison de leur meilleur contrôle de grille et de l'amélioration de  $V_{\rm BR}$  par rapport aux dispositifs planaires, sans dégrader le  $R_{\rm ON}$ . De plus, les tri-grilles permettent un décalage positif contrôlable de  $V_{\rm TH}$  en modifiant la largeur des tranchées, en raison de la relaxation partielle de la barrière AlGaN et du contrôle électrostatique amélioré des parois latérales des tri-grilles. Cela offrirait la possibilité de maintenir un  $V_{\rm TH}$  élevé et un  $R_{\rm ON}$  réduit en même temps.

Dans cette thèse, nous proposons plusieurs technologies basées sur la structure trois grilles pour surmonter ces défis. Premièrement, nous présentons des MOSFET GaN-on-Si normalement bloqués basés sur la combinaison de tri-grille avec une barrière légèrement enfoncée pour produire un grand  $V_{\rm TH}$  positif, tout en maintenant un  $R_{\rm ON}$  et une densité de courant élevée ( $I_{\rm D}$ ). La structure à trois grilles offre l'un excellent contrôle de canal, améliorant le  $V_{\rm TH}$  jusqu'à +1.4 V à 1  $\mu$  A / mm , avec hystérésis de  $V_{\rm TH}$  très réduite , et la transconductance significativement accrue ( $g_{\rm m}$ ). Des canaux de conduction supplémentaires sur les parois latérales compensent la dégradation de  $R_{\rm ON}$  en plus du renfoncement de la grille, résultant en un petit  $R_{\rm ON}$  de 7.32  $\pm$  0.26  $\Omega$  · mm pour la longueur de la grille au drain ( $L_{\rm GD}$  de 15  $\mu$  m, et en une augmentation du courant de sortie maximum ( $I_{\rm D}^{\rm max}$ ).

Deuxièmement, nous proposons un nouveau concept pour les MOS-HEMT AlGaN / GaN-on-Si normalement bloqué sur la combinaison de structures p-GaN, tri-grille et MOS pour atteindre un

$V_{\mathrm{TH}}$  élevé et un faible  $R_{\mathrm{ON}}$ . Le p-GaN est utilisé pour concevoir la structure des bandes et réduire la densité de grilleuse ( $N_{\mathrm{s}}$ ) dans la structure à trois grilles pour un  $V_{\mathrm{TH}}$  élevé. La commande de grille est principalement réalisée par l'effet de champ à travers les parois latérales à trois grilles et ne repose pas sur l'injection de courant de grille. La structure MOS permet des tensions de grille beaucoup plus importantes ( $V_{\mathrm{G}}$ ) et la modulation efficace de la paroi latérale se traduit par d'excellentes performances de commutation à des fréquences de commutation élevées. De plus, ce concept élimine le besoin de barrières minces (typiques des dispositifs p-GaN), qui, combinées aux canaux de conduction formés au niveau des parois latérales à trois grilles, ont abouti à un  $R_{\mathrm{ON}}$  plus petit par rapport au structures planaired dopées p GaN.

Enfin, nous avons étudié les grilles logiques NMOS basées sur GaN, y compris NOT, NAND et NOR par intégration de MOSHEMT GaN en mode E / D. L'onduleur GaN NMOS a été réalisé avec une tension de basculement logique de 4.93 V à une tension de 5 V, une marge de bruit d'entrée faible de 2.13 V et une marge de bruit d'entrée élevée de 2.2 V à température ambiante. Cependant, ces grilles logiques souffrent d'une tension transitoire instable, d'une faible marge de bruit et d'un courant de fuite logique élevé. De plus, le décalage de grande taille entre les transistors en mode E et en mode D empêche leur intégration compacte. Ainsi, les grilles logiques à haute performance avec intégration monolithique de MOSHEMT à trois grilles à trois modes E / D ont été fabriquées. La structure à trois grilles de la grille logique offre des avantages uniques par rapport à la conception en mode E / D planaire conventionnelle avec une correspondance de taille beaucoup plus compacte et plus stable  $V_{\rm TH}$ .

Les résultats de cette thèse révèlent le grand potentiel des transistors GaN et de la grille logique basée sur GaN pour une fréquence de commutation élevée, ce qui ouvrirait la voie à un futur circuit intégré de puissance GaN.

Mots clefs : HEMT, transistors GaN, dispositif de puissance, nitrure III, tri-gate, conduction de tranchée, tension de claquage, résistance

# **Symbols and Acronyms**

### Symbols

| Symbol                          | Quantity                         | Measurement unit or value          |

|---------------------------------|----------------------------------|------------------------------------|

| $\epsilon$                      | Relative dielectric constant     |                                    |

| $\epsilon_0$                    | Vacuum dielectric constant       | $8.85 \times 10^{-12} \text{ F/m}$ |

| $g_{\mathrm{m}}$                | Transconductance                 | S                                  |

| $\mu$                           | Mobility                         | cm <sup>2</sup> /Vs                |

| $N_{ m s}$                      | Sheet carrier concentration      | $cm^{-2}$                          |

| DIBL                            | Drain induced barrier lowering   | mV/V                               |

| SS                              | Subthrehsold slope               | mV/dec                             |

| $V_{ m BR}$                     | Breakdown voltage                | V                                  |

| $V_{ m on}$                     | Turn-on voltage                  | V                                  |

| $v_{ m sat}$                    | Saturation velocity              | cm/s                               |

| $w_{ m sd}$                     | Sidewall depletion width         | nm                                 |

| $R_{\mathrm{ON}}$               | On-resistance                    | $\Omega \cdot mm$                  |

| $V_{ m TH}$                     | Threshold voltage at $1\mu$ A/mm | V                                  |

| $V_{ m G}$                      | Gate voltage                     | V                                  |

| $I_{\mathrm{D}}$                | Output current density           | A/mm                               |

| $I_{\mathrm{D}}^{\mathrm{max}}$ | Maximum output current           | A/mm                               |

| $I_{ m OFF}$                    | OFF-state leakage current        | A/mm                               |

| $I_{\mathrm{ON}}$               | On-state current                 | A/mm                               |

| $V_{ m G}^{ m max}$             | Maximum gate voltage             | V                                  |

| $L_{ m G}$                      | Gate length                      | $\mu$ m                            |

| $L_{ m GD}$                     | Gate to source length            | $\mu$ m                            |

| $L_{GS}$                        | Gate to drain length             | $\mu$ m                            |

| $w_{\mathrm{fin}}$              | fin width                        | $\mu$ m                            |

| FF                              | Filling factor                   | %                                  |

| $l_{ m fin}$                    | Length of the fins               | nm                                 |

| $V_{ m OL}$                     | Low-level output voltages        | V                                  |

| $V_{\mathrm{OH}}$               | High-level output voltages       | V                                  |

| $NM_{ m L}$                     | Low noise margin                 | V                                  |

| $NM_{ m H}$                     | High noise margin                | V                                  |

| $\alpha$                        | Driver to load resistance ratio  | %                                  |

| $C_{\text{top}}$                | Top capacitor of tri-gate fin    | F                                  |

$C_{\text{side}}$  Sidewall capacitor of tri-gate fin F

Acronyms

#### Chapter 0. Symbols and Acronyms

**Abbreviation** Full name

GaN Gallium Nitride

Si Silicon

SiC Silicon carbide

2DEG 2-Dimensional Electron Gas

PV photovoltaic

D-mode Depletion-mode

E-mode Enhancement-mode

BFM Baliga's Figure of Merit

JFoM Johnson figure of merit

BHFFM Baliga's High Frequency Figure of Merit

$P_{

m pz}$  piezoelectro polarization  $P_{

m sp}$  spontaneous polarization

DUT Device under test

HEMT High Electron Mobility Transistor

MESFET Metal-Semiconductor Field-Effect Transistor

MOSFET Metal-Oxide Field-Effect Transistor

MISFET Metal-insulator-Semiconductor Field-Effect Transistor

FP Field plate LV Low voltage HV High voltage

CMOS Complementary Metal Oxide Semiconductor

NMOS N-type Metal-Oxide-Semiconductor

DCFL Direct-coupled FET logic IC Integrated Circuits

MMIC Monolithic Microwave Integrated Circuits

RF Radio Frequency **UVLO** Under voltage-lockout Gate injection transistor **GIT** Electron-Beam Lithography **EBL MSBA** Multi-stage boost architecture **CSI** Common source inductance **FinFET** Fin field-effect transistor VTC voltage transfer characteristic

VSD Voltage Source Driver CSD Current Source Driver RGD Resonant Gate Driver

HCl Cloridric acid Cl<sub>2</sub> Chlorine

BCl<sub>3</sub> Boron trichloride SiO<sub>2</sub> Silicon dioxide BOE Buffered Oxide Etch

SEM Scanning electron microscopy

FIB Focused Ion Beam

ALD Atomic layer deposition

RTA rapid thermal annealing

AFM Atomic force microscopy

RT Room Temperature

<sup>X</sup>HSQ Hydrogen Silsesquioxane

ICP RIE Inductive coupled plasma reactive-ion

KOH Potassium hydroxide

TMAH Tetramethylammonium hydroxide

# Contents

| A  | cknov    | vledgen  | nents                                                | i     |

|----|----------|----------|------------------------------------------------------|-------|

| A  | bstrac   | ct (Engl | lish/French)                                         | iii   |

| Sy | ymbol    | s and A  | Acronyms                                             | vii   |

| C  | onten    | ts       |                                                      | xi    |

| Li | ist of 1 | figures  |                                                      | XV    |

| Li | ist of 1 | tables   |                                                      | xxiii |

| 1  | Intr     | oductio  | on                                                   | 1     |

|    | 1.1      | Advar    | ntages of GaN power devices                          | 3     |

|    | 1.2      | The G    | GaN-on-Si Normally-on/off power device technology    | 4     |

|    |          | 1.2.1    | Recessed gate normally-off transistors               | 6     |

|    |          | 1.2.2    | Implanted gate transistors                           | 7     |

|    |          | 1.2.3    | p-GaN gate structure                                 | 8     |

|    |          | 1.2.4    | Cascode structure                                    | 10    |

|    | 1.3      | GaN b    | pased logic gates                                    | 11    |

|    | 1.4      |          | lithic integration of GaN power IC                   |       |

|    | 1.5      | Major    | challenges                                           | 15    |

|    | 1.6      | Thesis   | s outline                                            | 16    |

| 2  | Tri-     | _        | chnologies for normally-off MOSHEMT                  | 19    |

|    | 2.1      |          | luction                                              |       |

|    | 2.2      | •        | et of tri-gate structure on normally-on transistors  |       |

|    |          | 2.2.1    | Improved gate control                                |       |

|    |          | 2.2.2    | Tunable threshold voltage                            |       |

|    |          | 2.2.3    | Enhanced breakdown voltage                           |       |

|    | 2.3      | •        | et of tri-gate structure on normally-off transistors |       |

|    |          | 2.3.1    | Trench conduction                                    |       |

|    |          | 2.3.2    | Novel p-GaN MOS conduction mechanism                 |       |

|    |          | 2.3.3    | Enhanced $V_{\text{BP}}$                             | 28    |

### **Contents**

| 3 | 2.4<br>Normalian 3.1<br>3.2 | mally-o | Reduced short channel effect                                  | 29<br>30 |

|---|-----------------------------|---------|---------------------------------------------------------------|----------|

| 3 | <b>Nor</b> 3.1              | mally-o |                                                               | 30       |

| 3 | 3.1                         | •       |                                                               |          |

|   |                             |         | ff transistors with recessed tri-gate technologies            | 31       |

|   | 3.2                         | Introdu | uction                                                        | 31       |

|   |                             | Device  | e design and fabrication                                      | 32       |

|   | 3.3                         | Device  | e optimization and characterization                           | 33       |

|   |                             | 3.3.1   | Device optimization                                           | 33       |

|   |                             | 3.3.2   | Device performance                                            | 34       |

|   |                             | 3.3.3   | Equivalent model of recessed tri-gate devices                 | 35       |

|   |                             | 3.3.4   | Breakdown Characterization of Recessed Tri-gate and Benchmark | 37       |

|   | 3.4                         | Conclu  | asion                                                         | 38       |

| 4 | Nor                         | mally-o | ff p-GaN MOSHEMTs with tri-gate technology                    | 41       |

|   | 4.1                         | Introdu | uction                                                        | 41       |

|   | 4.2                         | Motiva  | ation and Approaches                                          | 42       |

|   | 4.3                         | Top-do  | own approach: Tri-gates on p-GaN/AlGaN/GaN wafer              | 43       |

|   |                             | 4.3.1   | Device structure                                              | 43       |

|   |                             | 4.3.2   | Selective p-GaN/AlGaN etching and fabrication                 | 44       |

|   |                             | 4.3.3   | Device Characterization of p-GaN MOS Planar                   | 45       |

|   |                             | 4.3.4   | p-GaN MOS Tri-gate DC characterization                        | 46       |

|   |                             | 4.3.5   | p-GaN MOS tri-gate optimization                               | 47       |

|   |                             | 4.3.6   | Tri-gate MOS conduction mechanism                             | 49       |

|   |                             | 4.3.7   | Improved breakdown voltage                                    | 50       |

|   | 4.4                         | Botton  | n-up approach: growth of p-GaN layers over tri-gates          | 51       |

|   |                             | 4.4.1   | Introduction                                                  | 51       |

|   |                             | 4.4.2   | Regrowth Process                                              | 51       |

|   |                             | 4.4.3   | Challenges: Growth issues due to hard-mask residues           | 52       |

|   |                             | 4.4.4   | Challenges: Thickness inhomogeneity                           | 54       |

|   | 4.5                         | Conclu  | asion                                                         | 55       |

| 5 | GaN                         | l-based | logics and driving circuits                                   | 57       |

|   | 5.1                         |         | uction                                                        | 57       |

|   | 5.2                         |         | S or NMOS GaN logic circuits                                  | 58       |

|   |                             | 5.2.1   | Ideal logic switch and typical logic switch                   | 58       |

|   |                             | 5.2.2   | CMOS GaN logic gates                                          | 59       |

|   |                             | 5.2.3   | GaN based NMOS logic                                          | 59       |

|   | 5.3                         |         | Mode MOSHEMTs based GaN NMOS digital logic gate circuit       | 60       |

|   | - /-                        | 5.3.1   | Integrated logic design and fabrication                       | 60       |

|   |                             | 5.3.2   | DCFL inverter                                                 | 62       |

|   |                             | 5.3.3   | NAND and NOR logic gate                                       | 64       |

|   | 5.4                         |         | mode tri-gate MOSHEMTs based GaN NMOS logic gate circuits     | 67       |

|   |                             | 5.4.1   | Introduction and motivation                                   | 67       |

| $\sim$ |   |   |    |   |    |

|--------|---|---|----|---|----|

| Co     | n | t | O. | n | tc |

| \ \U   |   | u | u  |   | LO |

|    |          | 5.4.2    | Device structure and logic design                                    | 67  |

|----|----------|----------|----------------------------------------------------------------------|-----|

|    |          | 5.4.3    | Device optimization and characterization                             | 68  |

|    | 5.5      | GaN-b    | pased voltage source driver (VSD)                                    | 70  |

|    |          | 5.5.1    | Introduction                                                         | 70  |

|    |          | 5.5.2    | Development of the GaN HEMT gate charging model                      | 74  |

|    |          | 5.5.3    | Simulation of VSD versus different driver resistance and driver loop |     |

|    |          |          | inductance                                                           | 77  |

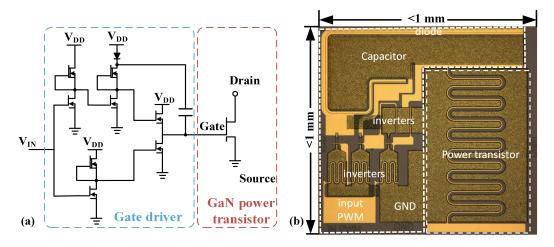

|    |          | 5.5.4    | Design and fabrication of VSD                                        | 79  |

|    | 5.6      | Conclu   | asion                                                                | 81  |

| _  | <b>C</b> |          |                                                                      | 0.2 |

| 6  | Con      |          | and future directions                                                | 83  |

|    | 6.1      |          | asions                                                               | 83  |

|    | 6.2      | Future   | development                                                          | 84  |

| Re | eferen   | ices     |                                                                      | 102 |

| Cı | ırricu   | ılum Vi  | tae                                                                  | 103 |

| Fa | brica    | tion pro | ocess flow                                                           | 107 |

| Re | ecesse   | d tri-ga | te R_ON model                                                        | 111 |

| T  | CAD      | simulati | ion of field plate                                                   | 115 |

# List of Figures

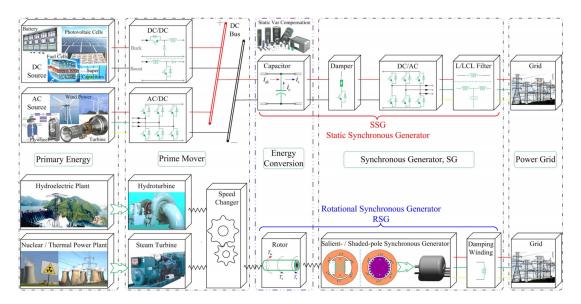

| 1.1 | Generalized structure of renewable/conventional energy generation system [2]                                                                                                                                                                                                                                                                                                                                                                                 | 1    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

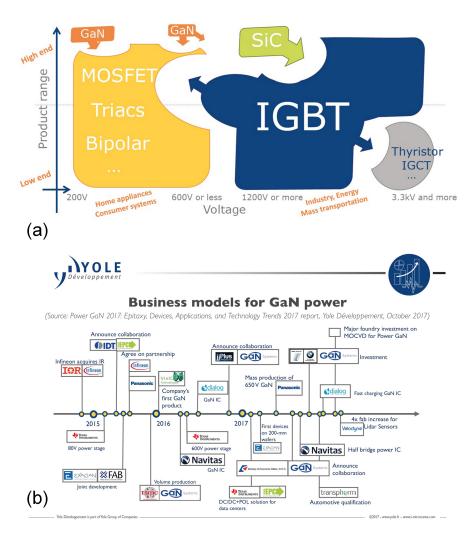

| 1.2 | (a) The current position of power device, showing the GaN and SiC existing market and potential market, obtained from https://www.slideshare.net/Yole_Developper/status-of-power_electronicsindustry2015sample [8].(b) Business models for GaN power device, indicating the massive growth of GaN power device industry, obtained from https://www.systemplus.fr/gan-power-device-industry-the-supply-chain-is-acting-to-support-market-growth/#_ftnref1 [8] | ment |

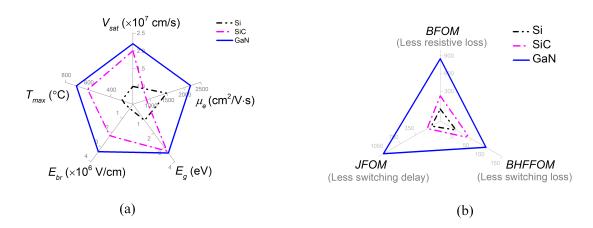

| 1.3 | Comparison of Si, SiC, and GaN in terms of (a) normalized fundamental material properties as well as (b) three kinds of normalized Figure of Merits (FOM)                                                                                                                                                                                                                                                                                                    | 3    |

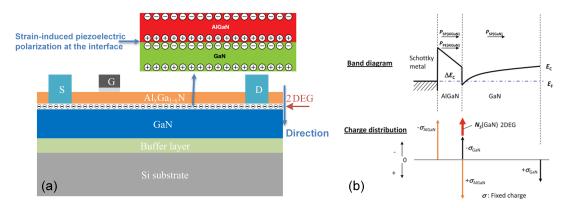

| 1.4 | (a) Cross-sectional schematic of an AlGaN/GaN HEMT. (b) Band diagram of the AlGaN/GaN heterostructure and the 2DEG at the interface [15]                                                                                                                                                                                                                                                                                                                     | 4    |

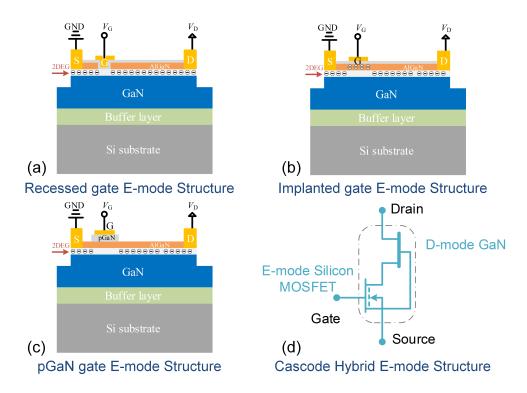

| 1.5 | Cross-sectional schematic of a (a) recessed gate, (b) implated gate, and (c) p-GaN gate E-mode structure. (d) Schematic of a typical cascode hybrid E-mode structure.                                                                                                                                                                                                                                                                                        | 5    |

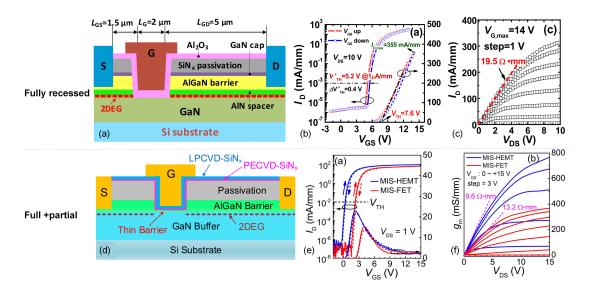

| 1.6 | Fully recessed GaN devices: (a) Schematic of recessed devices. (b) Transfer and (c) output characteristics of fully recessed GaN transistors [62]. Fully+partially recessed GaN transistors: (d) Schematic of partially etched MESHEMT.(e) Transfer and (f) output characteristics of MIS-HEMT and MISFET [63]                                                                                                                                               | 6    |

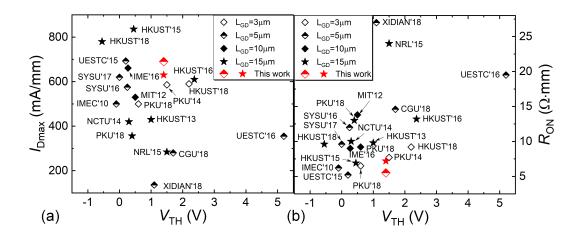

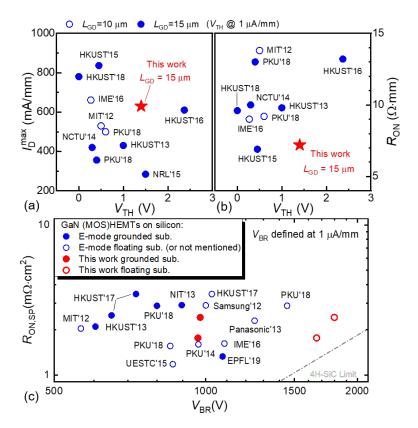

| 1.7 | Benchmarking of (a) $I_{\rm D}^{\rm max}$ and (b) $R_{\rm ON}$ versus $V_{\rm TH}$ (defined at 1 $\mu$ A/mm) of the recessed tri-gate against E-mode GaN-on-Si transistors. [65]                                                                                                                                                                                                                                                                             | 7    |

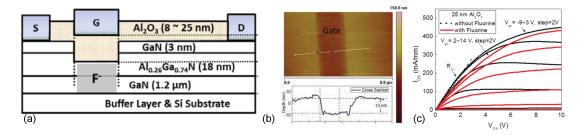

| 1.8 | (a) Schematic of the E-mode MOS-HEMT by fluorine plasma treatment. (b) Atomic force microscope picture of the HEMT structure after 150 s CF <sub>4</sub> plasma treatment in the gate region. (c) Output characteristics of standard and fluorinated MOS-HEMTs with 25 nm Al <sub>2</sub> O <sub>3</sub> as gate oxide. [46]                                                                                                                                 | 8    |

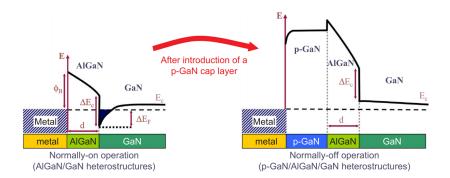

| 1.9 | Schematic of the operation principle of the normally-off HEMT with a p-GaN gate. The introduction of the p-GaN layer lifts up the conduction band of the AlGaN, leading to the depletion of the 2DEG. [25]                                                                                                                                                                                                                                                   | 8    |

| 1.10 | Simulated conduction band diagrams of a p-GaN/AlGaN/GaN heterostructure, for two different values of Al molar fraction (a), or two different values of the |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | AlGaN thickness (b). The borderline between normally-on and normally-off                                                                                   |    |

|      | operation mode as function of the Al molar fraction and AlGaN thickness in                                                                                 |    |

|      | p-GaN/AlGaN/GaN heterostructures (c) based on the simulations performed in                                                                                 |    |

|      | Ref. [25]. (d) Calculated [36,55] $V_{\rm TH}$ (in Volt) of the p-GaN gate AlGaN/GaN                                                                       |    |

|      | HEMT as a function of mole fraction and thickness of the AlGaN barrier. The                                                                                |    |

|      | diamond symbol represents our AlGaN barrier reference                                                                                                      | 9  |

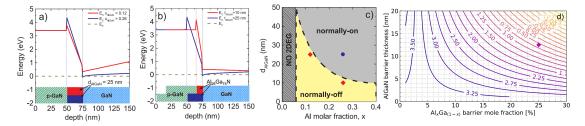

| 1.11 | (a) AFM measurement of the step height as a function of the etching time; (b)                                                                              |    |

| 1.11 | Cross sectional TEM image of the p-GaN/AlGaN/GaN heterostructure after                                                                                     |    |

|      | p-GaN removal from access regions. [25]                                                                                                                    | 9  |

| 1 12 |                                                                                                                                                            | 7  |

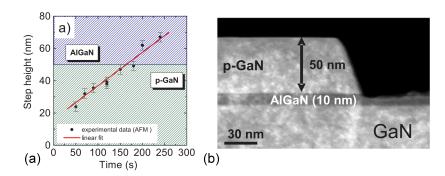

| 1.12 | (a) Schematic cross view of the operation of the a hybrid-drain-embedded-GIT.                                                                              | 10 |

| 1 12 | (b) Comparison of dynamic $R_{ON}$ of HD-GIT with conventional GIT. [13]                                                                                   | 10 |

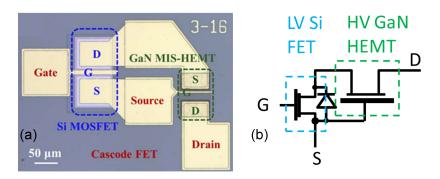

| 1.13 | (a) Optical photograph of fabricated device [79]. (b) Schematic of a typical GaN cascode device [13]                                                       | 10 |

| 1.14 | The output $I_D$ – $V_G$ characteristics of (a) D-mode HV GaN HEMT, (b) E-mode                                                                             |    |

|      | LV Si MOSFET, (c) cascode device, and (d) OFF-state blocking curve of the                                                                                  |    |

|      | cascode device [13].(e)The percentage of $R_{\text{on,ds}}$ from MOSFET compared with                                                                      |    |

|      | GaN devices [15]                                                                                                                                           | 11 |

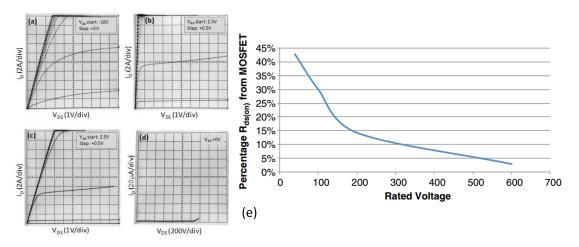

| 1.15 | (a) Schematic of the DCFL circuit (b) Cross sectional of E-mode HEMT gate                                                                                  |    |

|      | definition and plasma treatment and gate pad metallization. (c)Static voltage                                                                              |    |

|      | transfer characteristics for a typical E/D HEMT inverter. The output levels ( $V_{ m OH}$                                                                  |    |

|      | and $V_{\rm OL}$ ), inverter threshold voltage ( $V_{\rm TH}$ ), and static noise margins ( $NM_{\rm L}$ and                                               |    |

|      | $NM_{\rm H}$ ) are defined. [81]                                                                                                                           | 12 |

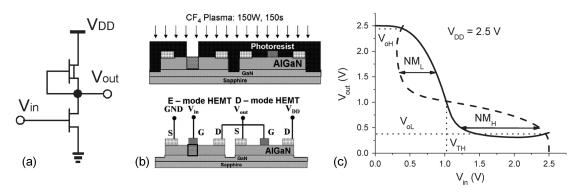

| 1.16 | Static voltage transfer characteristics for a typical E/D HEMT inverter of (a)[81]                                                                         |    |

|      | (b) [85] (c) [86] (d) [87] (e) [88] (f) [89]                                                                                                               | 12 |

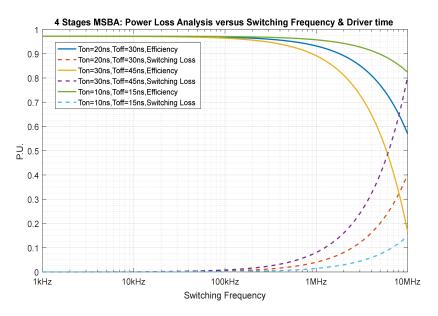

| 1.17 | Power Loss analysis versus switching frequency in a multi-stage boost architec-                                                                            |    |

|      | ture (MSBA)                                                                                                                                                | 13 |

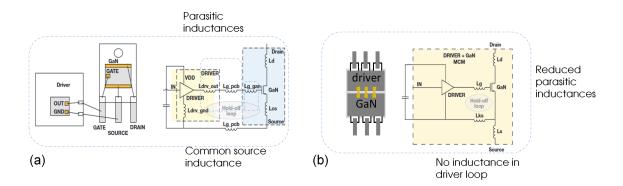

| 1.18 | GaN device-driver connection in (a) a separate package [91] and (b) an integrated                                                                          |    |

|      | GaN/driver package                                                                                                                                         | 14 |

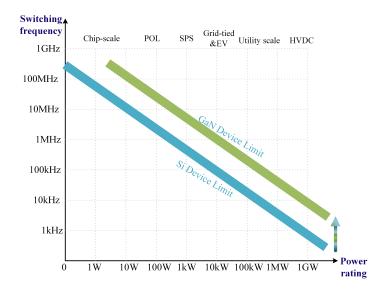

| 1.19 | Comparison of Si devices and GaN devices in terms of power rating versus                                                                                   |    |

|      | switching frequency [93]                                                                                                                                   | 15 |

|      |                                                                                                                                                            |    |

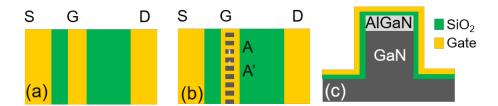

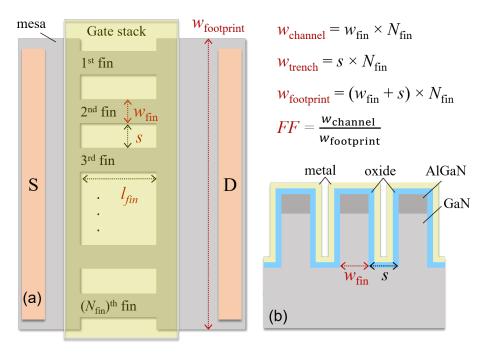

| 2.1  | Top view schematics of (a) planar and (b) tri-gate MOSHEMTs. (c) Cross-                                                                                    |    |

|      | sectional schematic of the tri-gate region along the AA' line                                                                                              | 19 |

| 2.2  | (a) Schematic illustration of nanochannel array (NCA)-HEMT with $L_{\rm g},~L_{\rm gs},$                                                                   |    |

|      | and $L_{\rm gd}$ of 2, 2, and 3 $\mu$ m, respectively. Inset shows a top view SEM image                                                                    |    |

|      | of the NCA structure before gate metalization. (b) Transfer characteristics of                                                                             |    |

|      | conventional HEMT (C-HEMT) and NCA-HEMT at $V_{\rm ds}$ = 8 V, in which $W_{\rm ch}$ of                                                                    |    |

|      | 64 nm. [111]                                                                                                                                               | 20 |

| 2.3  | (a) Top schematic view of tri-gate GaN MOSFET. (b) Cross-sectional schematic                                                                               |    |

|      | of the tri-gate region and important parameters definition [115]                                                                                           | 21 |

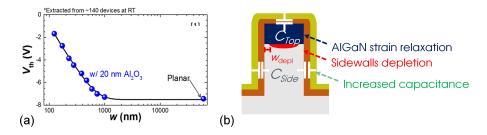

| 2.4  | Average (a) $I_D$ – $V_G$ and (b) $g_m$ – $V_G$ transfer characteristics in tri-gate GaN transistors, measured at $V_D$ = 5 V. The $w_{\rm fin}$ was measured by SEM [115]                                                                                                                                                                                                                                                                                                                           | 22 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | (a) Dependence of $V_{\text{TH}}$ on $w_{\text{fin}}$ . (b) The effect of sidwall depletion in distributing the 2DEG across a fin. [14]                                                                                                                                                                                                                                                                                                                                                              | 22 |

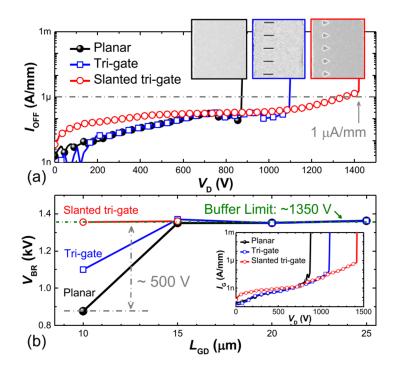

| 2.6  | (a) Breakdown characteristics of GaN transistors with planar gates, tri-gates and slanted tri-gates and (b) their $L_{\rm GD}$ -dependent $V_{\rm BR}$ (at 1 $\mu$ A/mm, $V_{\rm G}$ = 10 V) with a floating substrate. [124]                                                                                                                                                                                                                                                                        | 23 |

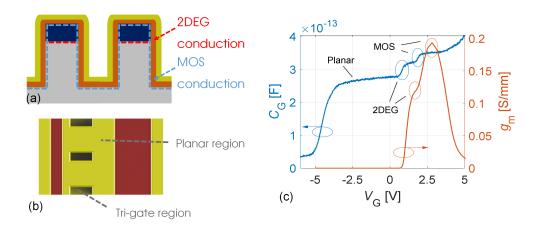

| 2.7  | (a) Cross-sectional view of tri-gate sidewall. (b) Top view of a typical GaN tri-gate transistor. (c) Gate capacitors ( $C_G$ ) and $g_m$ dependence on $V_G$ [113].                                                                                                                                                                                                                                                                                                                                 | 24 |

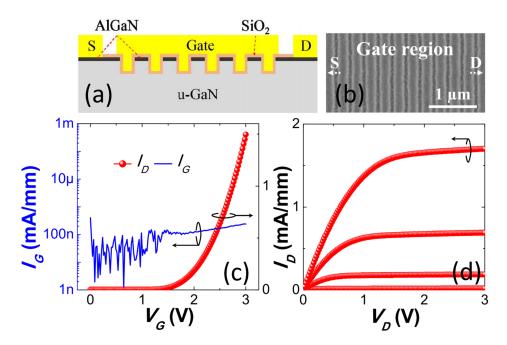

| 2.8  | (a) Cross-sectional view of the periodically gate-recessed MOS transistors. (b) Top view of gate region of the transistors. (c) The transfer and (d) output characteristics of this devices [14]. This work shows the existence of tri-gate trench conduction by J. Ma and E. Matioli                                                                                                                                                                                                                | 25 |

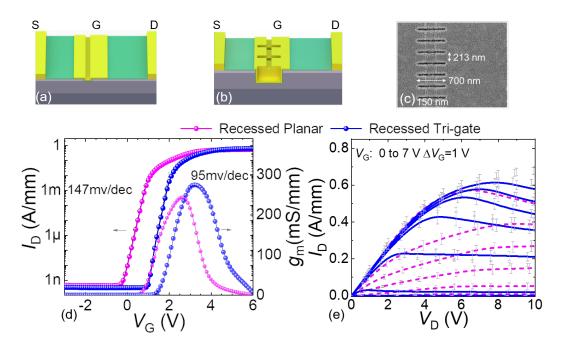

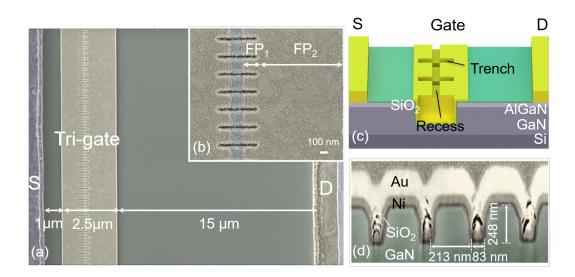

| 2.9  | The schematics of (a) recessed GaN MOSFET and (b) recessed tri-gate GaN MOSFET. (c) Top-view of the observed recessed tri-gate region. Comparison of the (d) transfer and (e) output characteristics of recessed GaN MOSFET and recessed tri-gate GaN MOSFET                                                                                                                                                                                                                                         | 26 |

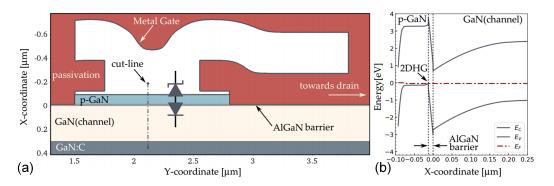

| 2.10 | (a) Detailed cross-section showing the p-GaN gate of an AlGaN/GaN HEMT: the metal itself is left blank and contacts the p-GaN layer. (b) Band diagram at equilibrium along the cut-line as indicated in the left figure [36]                                                                                                                                                                                                                                                                         | 27 |

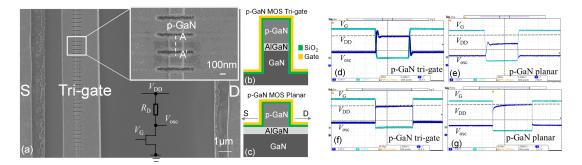

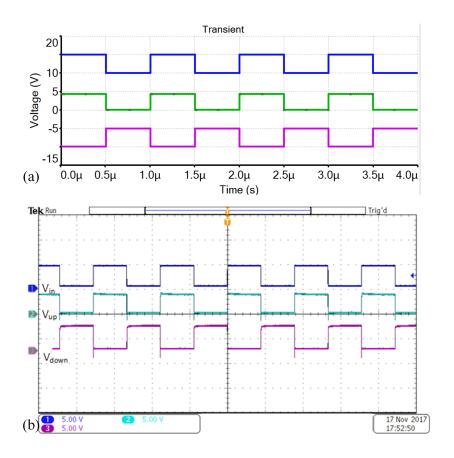

| 2.11 | (a) Top-view and zoomed SEM images of the p-GaN MOS tri-gate. Inset: Schematic of experimental setup of p-GaN test. (b) Cross-sectional schematic of the p-GaN MOS Tri-gate region along the AA' line, and of the (c) p-GaN MOS Planar gate along the source-drain direction. Switching waveform of (d) p-GaN tri-gate MOSHEMT and (e) planar p-GaN MOSHEMT devices at 500 kHz. Switching waveform of (f) p-GaN tri-gate MOSHEMT at 1 kHz and (g) planar p-GaN MOS HEMT devices at 100 Hz            | 28 |

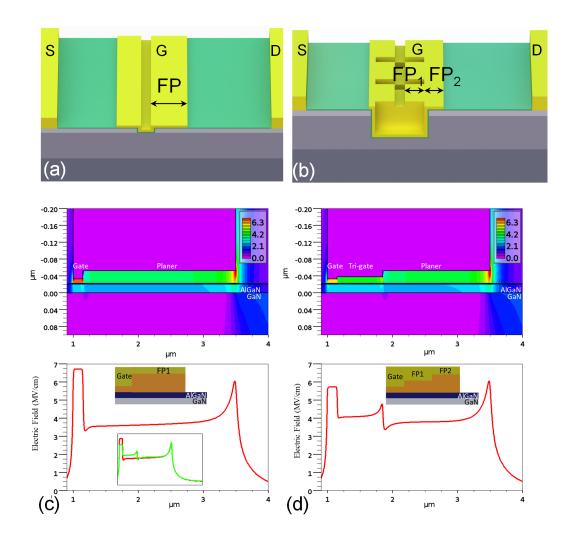

| 2.12 | Schematic of (a) planar transistor with one equivalent field plate and (b) recessed tr-gate transistor with 2 equivalent field plate. Schematic and simulated electric field distribution of (d) 1 $FP$ and (e) 2 $FP$ s, which are representing the recessed planar and recessed tri-gate transistors, respectively under $V_G$ =-11V and $V_D$ =100V. The electric field profiles correspond to the electric filed in the dielectric layer. (Inset) Comparison between the electric field profiles | 29 |

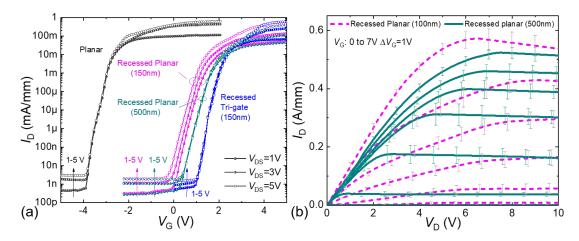

| 2.13 | (a) Transfer characteristics of fabricated devices with different drain-source bias (1V to 5V). (b) Output characteristics of recessed planar device with different recess width                                                                                                                                                                                                                                                                                                                     | 20 |

|      | recess width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30 |

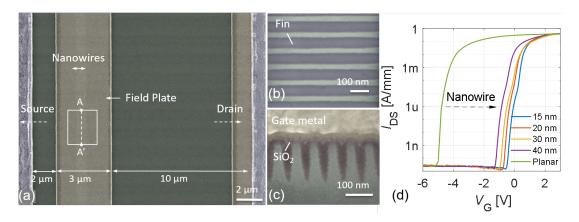

| 3.1 | (a) Top-view image of device access region and the gate region is highlighted. (b) Zoomed SEM image of the nanowire region before gate oxide deposition. (c) Cross-section FIB of the gate nanowires along the AA' line. The fins are covered only by 20 nm ALD $SiO_2$ , on top of which the Ni-Au or Pt-Au gate stacks were deposited. (d) Transfer curve for different fin width for Ni-Au gate stack at $V_{DS}$ =5 V. As the nanowire width decreases, $V_{TH}$ further approaches 0 V.                                                                                                                                                                                                                                                                                                                                                 | 32 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | [113]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 |

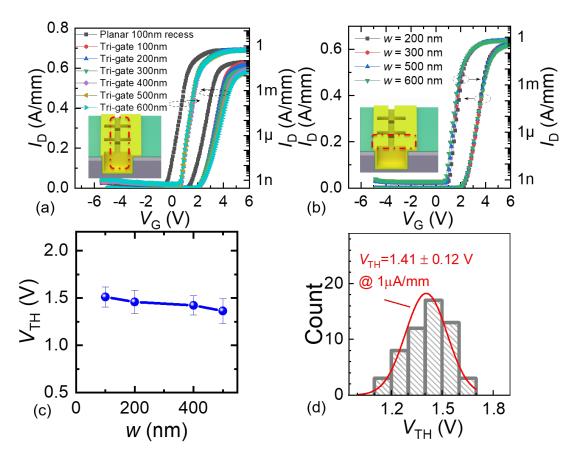

| 3.3 | (a) Comparison of planar recessed transistors with recessed tri-gate under different recess length (100nm to 600 nm). (b) Transfer characteristics of recessed tri-gate with different nanowire width. Inset: Schematic of recessed tri-gate regions.(c) The extracted $V_{\rm TH}$ dependence with tri-gate fin width (d) Distribution of $V_{\rm TH}$ of 56 recessed tri-gate devices                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34 |

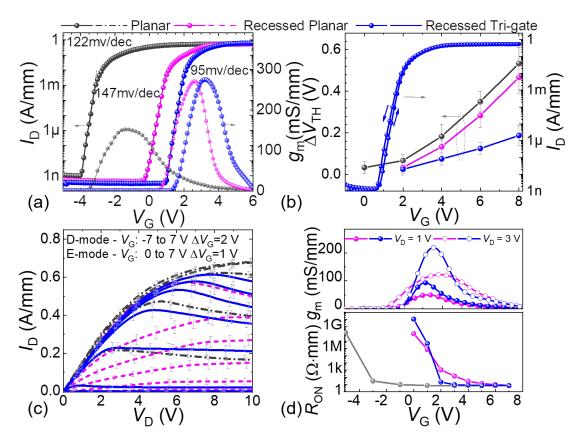

| 3.4 | Comparison of the normally-off recessed tri-gate with planar and recessed devices. (a) Transfer at $V_{\rm D}=5$ V and (b) Measured $V_{\rm G}^{\rm max}$ - $\Delta V_{\rm TH}$ dependence of planar, recessed and recessed tri-gate devices and gate hysteresis up to 8 V of recessed tri-gate transistor. (c) Output characteristics of the three devices with $V_{\rm G}$ up to 7 V. (d) $g_{\rm m}$ of recessed planar and recessed tri-gate MOSFET under $V_{\rm D}$ of 1 V and 3 V and extracted $V_{\rm G}-R_{\rm ON}$ dependence of planar, recessed and recessed tri-gate transistors. The $L_{\rm GS}$ , $L_{\rm G}$ and $L_{\rm GD}$ were 1, 2.5 and 15 $\mu$ m, respectively, and $FF$ was 0.66. Standard deviation bars were determined from the measurement of 8 devices of each type, revealing their consistent performance. | 36 |

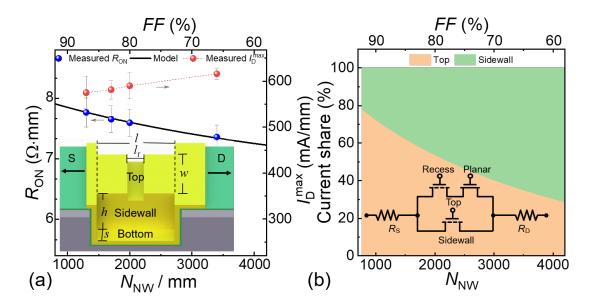

| 3.5 | $R_{\rm ON}$ and $I_{\rm D}^{\rm max}$ of the recessed tri-gate versus the number of nanowires $(N_{NW})$ and fill factor $(FF)$ in the tri-gate region. (b) Current share in the recessed tri-gate region. Insets: Schematic and equivalent circuit of the recessed tri-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37 |

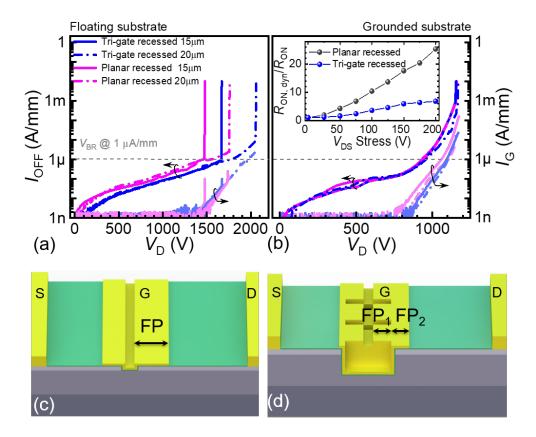

| 3.6 | Breakdown characteristics of the recessed ( $V_G = -1 \text{ V}$ ) and recessed tri-gate ( $V_G = 0 \text{ V}$ ) MOSFETs with $L_{GD} = 15 \text{ m}$ and 20 m, for (a) grounded and (b) floating substrate. Inset: Dynamic $R_{ON}$ of unpassivated recessed planar and recessed tri-gate transistors measured up to a quiescent bias stress of 200V with a pulse width of 50 s and a period of 5ms. Schematic of (c) planar $FP$ and (d) Tri-gate $FP$ s                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

| 3.7 | Benchmarking of (a) $I_{\rm D}^{\rm max}$ and (b) $R_{\rm ON}$ versus $V_{\rm TH}$ (defined at 1 A/mm) of the recessed tri-gate against E-mode GaN-on-Si transistors. For fair comparison, $L_{\rm GD}$ smaller than 10 m were not included (c) $R_{\rm ON,SP}$ versus VBR of the recessed tri-gate against E-mode GaN-on-Si transistors, by defining VBR at IOFF < 1A/mm with floating and grounded substrates. For fair comparison, $L_{\rm GD}$ smaller than 10 m, and literature results with unspecified $R_{\rm ON,SP}$ or IOFF were not included. To calculate $R_{\rm ON,SP}$ , a 1.5 m transfer length for each ohmic contact was taken into account.                                                                                                                                                                               | 39 |

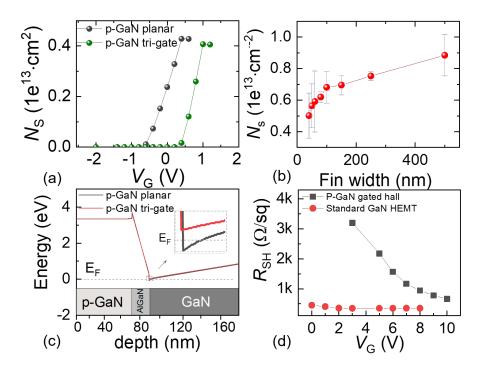

| 4.1 | (a) Simulated electron concentration of p-GaN planar and p-GaN tri-gate devices on p-GaN (75 nm)/Al $_{0.25}$ GaN (20 nm)/GaN epi-structure, under $V_{\rm G}$ from -2 to 2 V. (b) Measured electron concentration with different tri-gate fin widths ( $w$ ) on an AlGaN (20 nm)/GaN structure. (c) Simulated band diagram of p-GaN planar and p-GaN tri-gate devices. (d) Measured sheet resistance by gated hall of a p-GaN and a GaN HEMT structures                                                                                                                                                                                                                                                                                  | 43 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

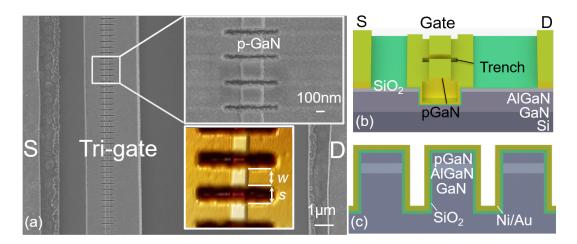

| 4.2 | (a) Top-view SEM image of the p-GaN MOS Tri-gate . Inset: Zoomed-in SEM image of p-GaN MOS Tri-gate region and AFM image of p-GaN on top of trigate nanowire. (b) Schematic of fabricated p-GaN MOS Tri-gate MOSHEMTs and (c) cross-sectional views of p-GaN MOS Tri-gate region                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44 |

| 4.3 | (a) Laser detector of ICP etching. The surface morphology after (b) traditional ICP etching and (c) the selective ICP etching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45 |

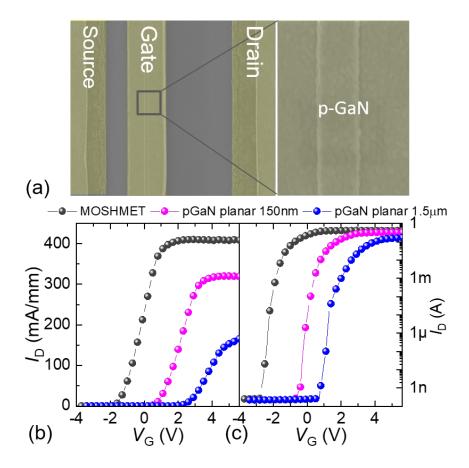

| 4.4 | (a) Top view of planar p-GaN transistors. Transfer characteristics of MOSHEMT and p-GaN MOS Planar in (b) Linear and (c) logarithmic scale for $V_{\rm DS}$ = 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

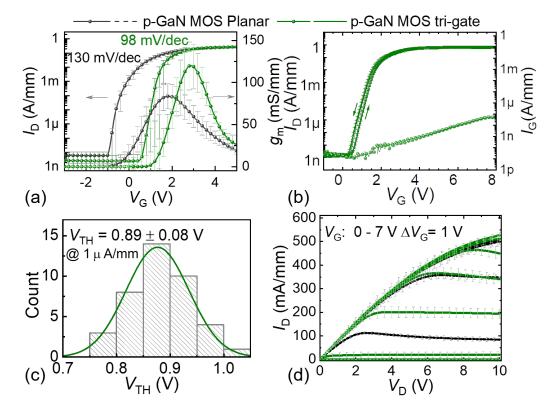

| 4.5 | (a) Comparison of transfer characteristics of the p-GaN MOS Tri-gate and the p-GaN MOS Planar device at $V_{\rm DS}$ = 5 V. The p-GaN length was 200 nm. (b) Double-sweep $I_{\rm D}$ and IG versus $V_{\rm G}$ for the p-GaN MOS Tri-gate. (c) Histogram of $V_{\rm TH}$ measured from 40 p-GaN MOS Tri-gate devices. (d) Output characteristics of the two types of devices with $V_{\rm G}$ up to 7 V. The $L_{\rm GS}$ , $L_{\rm G}$ and $L_{\rm GD}$ were 1, 2.5 and 10 $\mu$ m, respectively, width was 80 $\mu$ m and $FF$ was 0.66. Standard deviation bars were determined from the measurement of 10 devices of each type, revealing                                                                                            | 47 |

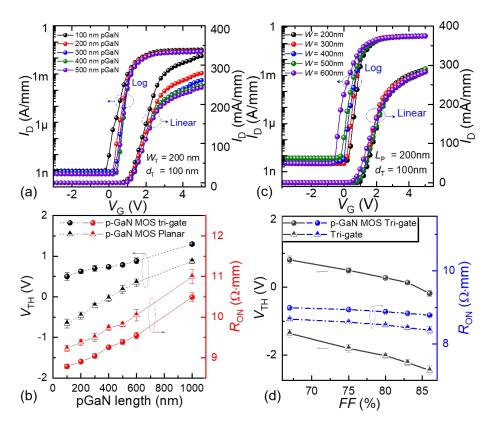

| 4.6 | their consistent performance. The Log and linear transfer characteristics at $V_{\rm DS}=5$ V of normally-off p-GaN MOS Tri-gate with different (a) p-GaN length and (b) Filling factor ( $FF$ ) of Tri-gate ( $w/w+d$ ). The $L_{\rm GS}$ , $L_{\rm G}$ and $L_{\rm GD}$ were 1.5, 2 and 15 $\mu$ m, respectively. Standard deviation bars were determined from the measurement of 6 devices of each type, revealing their consistent performance. (c) The p-GaN length – $V_{\rm TH}$ and $R_{\rm ON}$ dependence of p-GaN MOS Planar and p-GaN MOS Tri-gate devices. (d) $FF-V_{\rm TH}$ and $R_{\rm ON}$ dependence of Tri-gate (Normally-on) and p-GaN MOS Tri-gate (Normally-off) transistors (The p-GaN length is fixed at 200nm). | 48 |

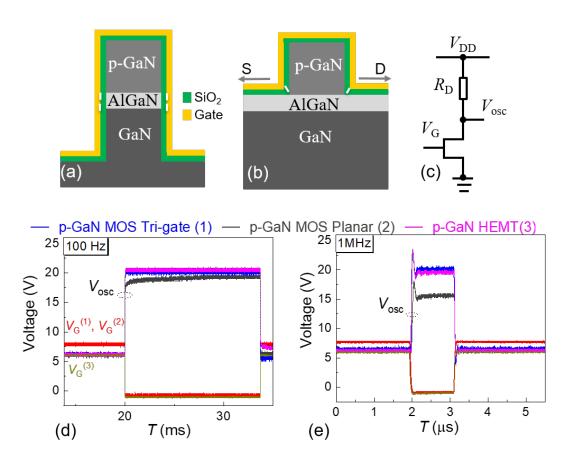

| 4.7 | Cross-sectional schematic of (a) p-GaN MOS tri-gate along with tri-gate region and (b) p-GaN MOS planar gate along with Source and Drain. (c) Schematic of experimental setup of p-GaN devices test. Switching waveform of Switching waveforms of the p-GaN MOS Tri-gate, p-GaN MOS Planar, and p-GaN HEMT at (d) 100 Hz and (e) 1 MHz with $V_{\rm DD} = 20$ V and $V_{\rm G}$ from -1 V to 8 V for p-GaN MOS Tri-gate and p-GaN MOS Planar, while $V_{\rm G}$ from -1 V to 6 V for p-GaN HEMT, due to its lower gate voltage capability                                                                                                                                                                                                 | 49 |

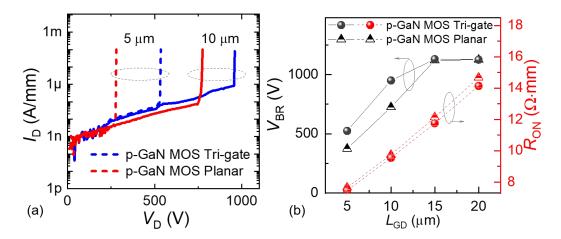

| 4.8 | (a) Breakdown Characteristics of the p-GaN MOS Tri-gate (at $V_G = 0$ V) and p-GaN MOS Planar (at $V_G = -1$ V) with different $L_{GD}$ with grounded substrate.<br>(b) Extracted $V_{BR}$ and $R_{ON}$ dependence on $L_{GD}$ of p-GaN MOS Planar and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ., |

|     | p-GaN MOS Tri-gate. The $V_{\rm BR}$ was defined at IOFF 1 $\mu$ A/mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51 |

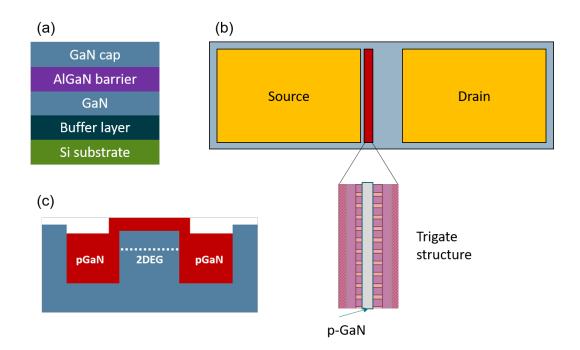

| 4.9        | Illustration of (a) epitaxial heterostructure (b) Top view device geometry and (c) Cross-section of tri-gate trench regrowth with p-GaN            | 52         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

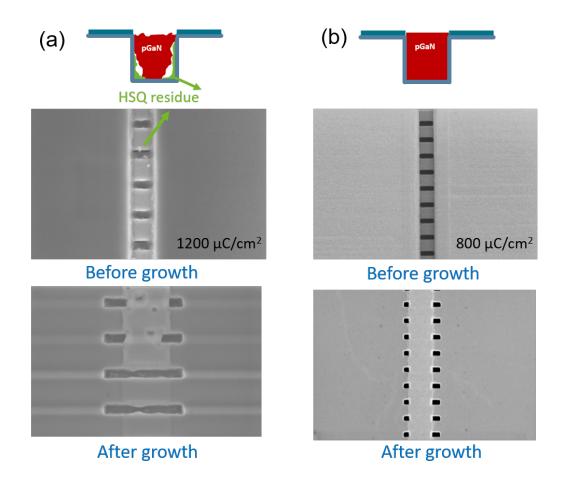

| 4.10       | Illustration and SEM images of tri-gate trenches before and after regrowth of                                                                      |            |

|            | p-type GaN for an e-beam exposure dose of (a) 1200 and (b) 800 $\mu$ C/cm <sup>2</sup> (p-GaN                                                      | <b>5</b> 0 |

|            | length: 400 nm).                                                                                                                                   | 53         |

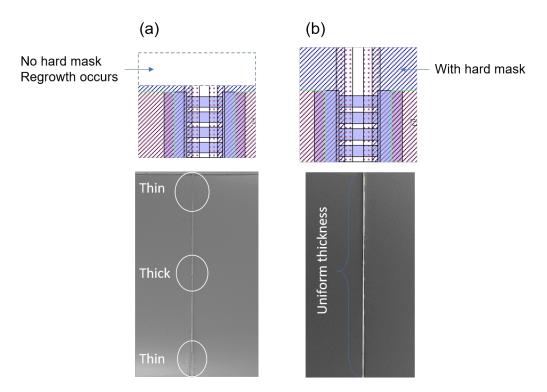

| 4.11       | Illustration of hard mask layout and SEM images for (a) narrow and (b) wide mask widths at the tri-gate edges                                      | 54         |

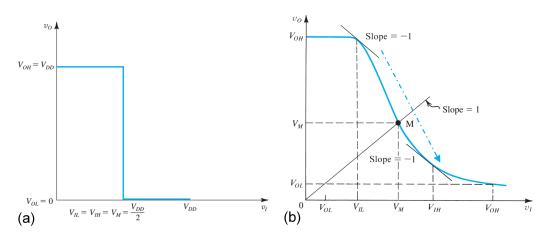

| 5.1        | Voltage transfer characteristics of logic gate of (a) ideal inverter logic circuit and                                                             |            |

|            | (b) practical inverter logic gate circuits [152]                                                                                                   | 58         |

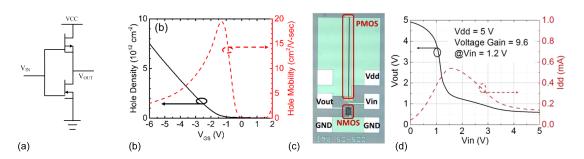

| 5.2        | (a) Schematic of CMOS logics circuit. (b) Channel carrier density and mobility of                                                                  |            |

|            | a PMOS extracted from DC-IV and VC meansurement of FAT-FET structures.(c)                                                                          |            |

|            | Microscopy top view photograph and (d) measured voltage transfer curve of a                                                                        |            |

|            | fabricated GaN CMOS inverter IC. The NMOS and PMOS have a gate width of                                                                            |            |

|            | $50 \ \mu \text{m}$ and $500 \ \mu \text{m}$ , respectively. [84]                                                                                  | 59         |

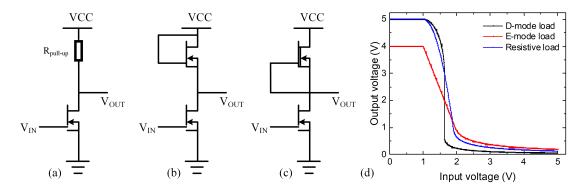

| 5.3        | GaN NMOS inverter with (a) resister load (b) enhancement load (c) depletion                                                                        |            |

|            | load. (d) Simulated VTC of GaN NMOS inverters.                                                                                                     | 60         |

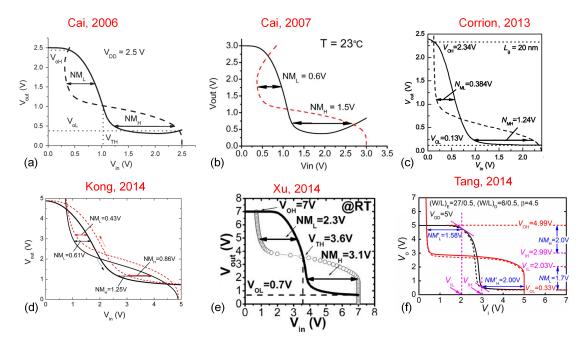

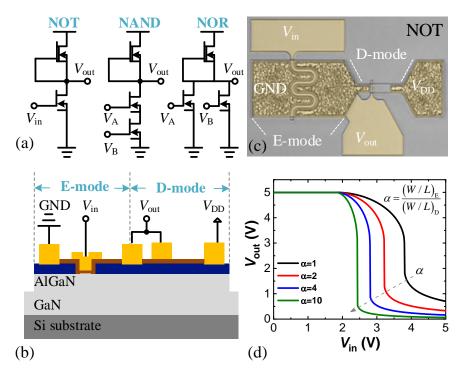

| 5.4        | (a) Equivalent circuits of inverter, NAND and NOR logic gates. (b) Cross-                                                                          |            |

|            | sectional schematic and (c) top view of monolithic integration of E/D-mode                                                                         | <i>c</i> 1 |

|            | MOSHEMTs. (d) Simulated transfer characteristics versus different $\alpha$ ratios                                                                  | 61         |

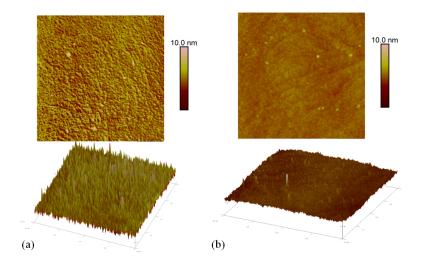

| 5.5        | Surface morphology (a) before and (b) after TMAH treatment                                                                                         | 61         |

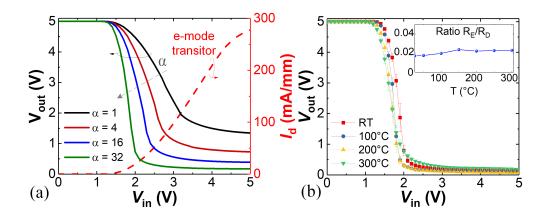

| 5.6        | (a) DCFL VTC versus different $\alpha$ ratio and the transfer characteristics of E-mode                                                            |            |

|            | transistors (b) DCFL VTC under different temperature varied from RT to 300                                                                         |            |

|            | °C. Inset: resistance ratio of E/D-mode logic versus temperature for output logic                                                                  | (2         |

| <i>-</i> - | equal to 0                                                                                                                                         | 62         |

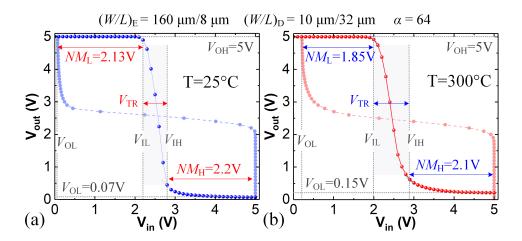

| 5.7        | The VTC of the optimized DCFL inverter with $\alpha = 64$ at (a) 25°C and (b) 300°C                                                                | (2         |

| <b>5</b> 0 | with supply voltage $V_{\rm DD}$ =5V                                                                                                               | 63         |

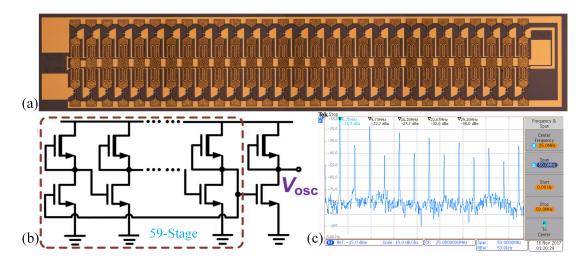

| 5.8        | (a) Top view micrograph and (b) schematic equivalent circuit of the fabricated                                                                     |            |

|            | 59-stage ring oscillator. (c) The measured frequency characteristics of ring oscillator at room temperature when the supply voltage $V_{DD}$ is 5V | 64         |

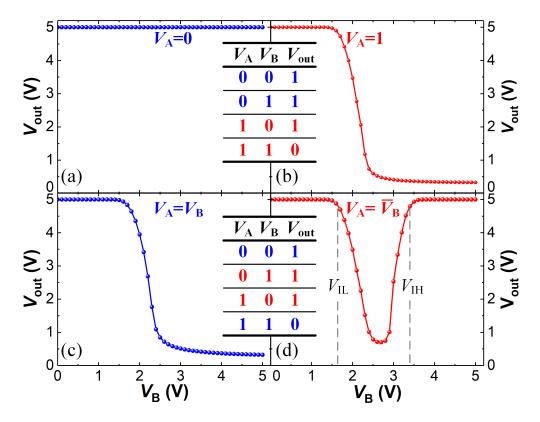

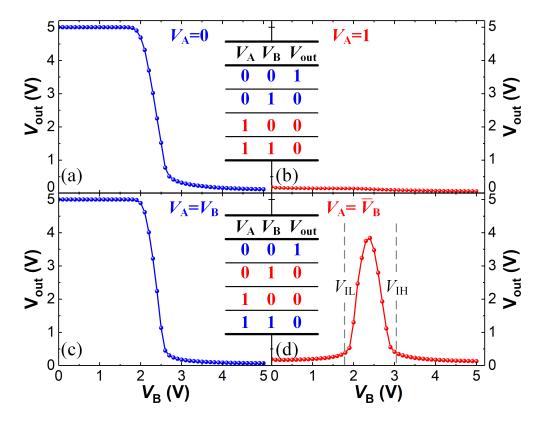

| 5.9        | The VTC of NAND gate logics under different input voltages, where (a) $V_A = 0$ ,                                                                  | 04         |

| 3.9        | (b) $V_A = 1$ , (c) $V_A = V_B$ , and (d) $V_A = \overline{V}_B$ , $V_B$ is sweeping from 0 to 5 V. Insets:                                        |            |

|            | corresponding truth table for NAND logic                                                                                                           | 65         |

| 5 10       | The VTC of NOR gate logics under different input voltages, where (a) $V_A = 0$ ,                                                                   | 03         |

| 3.10       | (b) $V_A = 1$ , (c) $V_A = V_B$ , and (d) $V_A = \overline{V}_B$ , $V_B$ is sweeping from 0 to 5 V. Insets:                                        |            |

|            | corresponding truth table for NOR logic                                                                                                            | 66         |

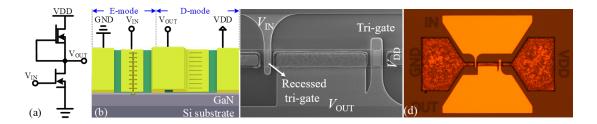

| 5 11       | (a) Equivalent circuits of a typical NOT logic. (b) 3D structure of monolithic                                                                     | 00         |

| 3.11       | integration of E/D-mode tri-gate MOSHEMTs. (c) SEM and (d) top microscopy                                                                          |            |

|            | view of E/D-mode tri-gate logics                                                                                                                   | 68         |

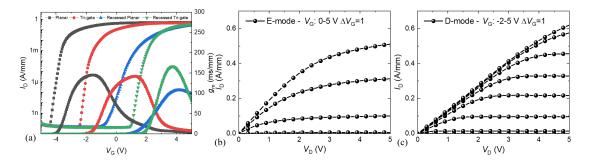

| 5 12       | (a) Transfer characteristics comparison of planar, tri-gate, recessed planar and                                                                   | 00         |

| 5.14       | recessed tri-gate devices. Output characteristics of (b) E-mode recessed tri-gate                                                                  |            |

|            | transistors and (c) D-mode standard tri-gate transistors                                                                                           | 68         |

|            | management and (c) is in our summand in Suite Humanitation.                                                                                        | 55         |

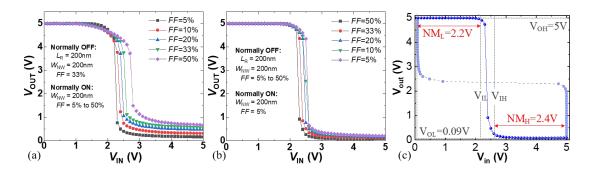

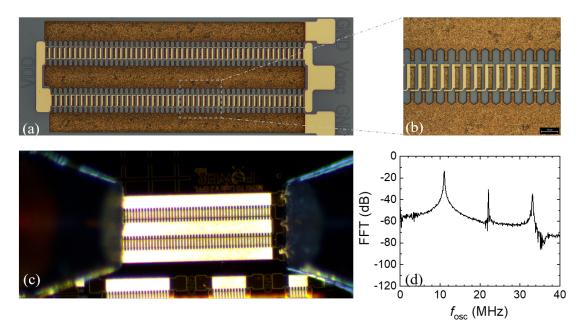

| 5.13         | (a) The VTCs of the tri-gate NMOS inverters with different $FF$ of D-mode tri-gate structure with the fixed nanowire width of $w = 200$ nm. The E-Mode tri-gate structure is fixed with $FF$ =0.33. (b) The VTCs of the tri-gate NMOS inverters with different $FF$ of E-mode tri-gate structure with the fixed nanowire width of $w = 200$ nm. The D-Mode tri-gate structure is fixed with $FF$ =0.05. (c) The VTC of the optimized tri-gate logic inverter. | 69   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.14         | (a) Top view micrograph and (b) zoomed top view of the fabricated 101-stage                                                                                                                                                                                                                                                                                                                                                                                   | 09   |

|              | ROs. (c) Experimental setup of RF probe station for measuring RO oscillation                                                                                                                                                                                                                                                                                                                                                                                  |      |

|              | frequency. (d)The measured frequency characteristics of ring oscillator at room                                                                                                                                                                                                                                                                                                                                                                               |      |

|              | temperature when the supply voltage $V_{DD}$ is 5 V                                                                                                                                                                                                                                                                                                                                                                                                           | 70   |

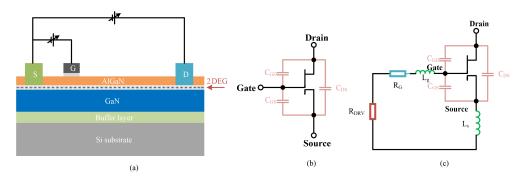

| 5.15         | (a) Schematic of a GaN HEMT cross-section structure. (b) Circuit Model and (c)                                                                                                                                                                                                                                                                                                                                                                                |      |

|              | Driver circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71   |

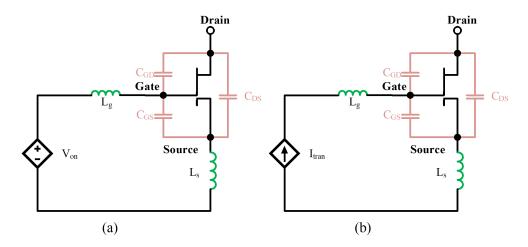

| 5.16         | Ideal gate driver (a) steady state of transistor (b) transient of transistor                                                                                                                                                                                                                                                                                                                                                                                  | 72   |

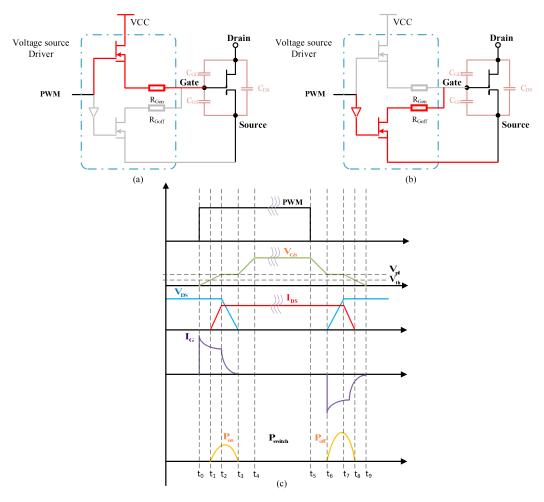

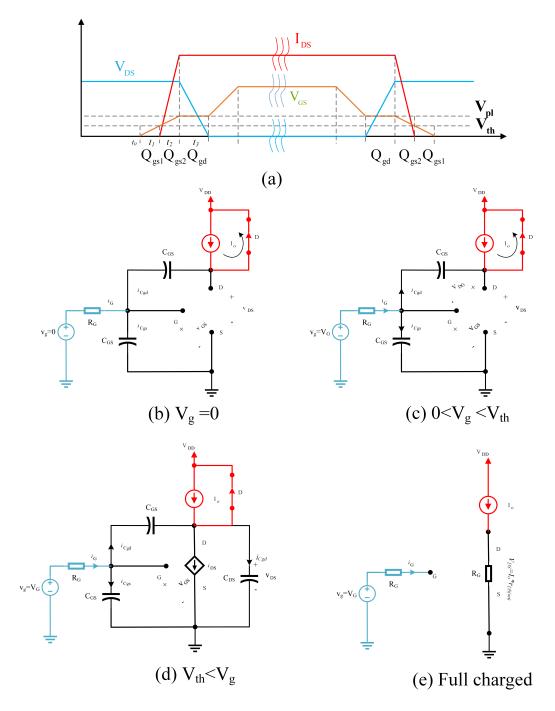

| 5.17         | Conventional voltage source driver (a) turn on transition, (b) turn off transition                                                                                                                                                                                                                                                                                                                                                                            |      |

|              | and (c) Switching waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73   |

| 5.18         | (a) Ideal switching waveform of GaN HEMT in terms of $V_{ds}$ , $V_{gs}$ and $I_{ds}$ versus                                                                                                                                                                                                                                                                                                                                                                  |      |

|              | time during turn-on and turn-off period. Simplified turn-on model of GaN HEMT                                                                                                                                                                                                                                                                                                                                                                                 |      |

|              | with a current source input: (b) GaN HEMT is off when gate voltage is low, (c)                                                                                                                                                                                                                                                                                                                                                                                |      |

|              | GaN HEMT is off before gate voltage reaches $V_{\text{th}}$ , (d) gate keeping charging                                                                                                                                                                                                                                                                                                                                                                       |      |

|              | until input capacitance is full, while $C_{\rm DS}$ is discharging, (e) gate is fully charged.                                                                                                                                                                                                                                                                                                                                                                | 75   |

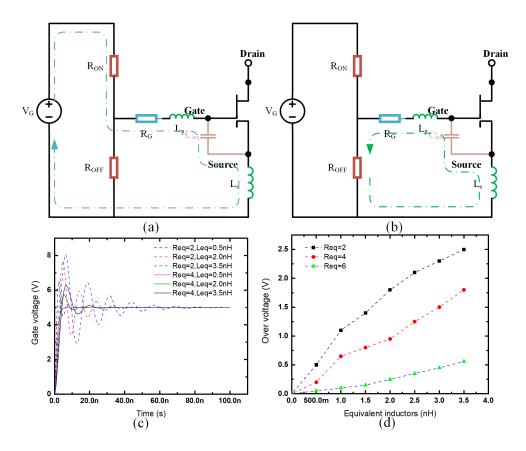

| 5.19         | The relationship between gate driver equivalent resistance $(R_{EQ})$ and the gate                                                                                                                                                                                                                                                                                                                                                                            |      |

|              | loop equivalent inductance $(L_{EQ})$ with the gate overvoltage: (a) turn-on LCR                                                                                                                                                                                                                                                                                                                                                                              |      |

|              | tank, (b) turn-off LCR tank, (c) gate voltage versus $R_{\rm EQ}$ and $L_{\rm EQ}$ and (d) gate                                                                                                                                                                                                                                                                                                                                                               |      |

| <b>5.0</b> 0 | peak overvoltage versus $R_{\text{EQ}}$ and $L_{\text{EQ}}$                                                                                                                                                                                                                                                                                                                                                                                                   | 78   |

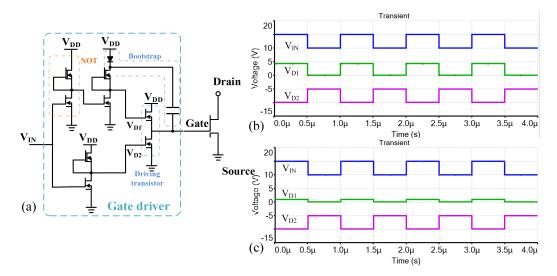

| 5.20         | - (a) Equivalent circuit of VSD for implementation (b) simulated gate signal for                                                                                                                                                                                                                                                                                                                                                                              |      |

|              | the VSD with bootstrap circuits (c) simulated gate signal for the VSD without                                                                                                                                                                                                                                                                                                                                                                                 | 70   |

| 5.01         | bootstrap circuits                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79   |