# P-GaN Tri-Gate MOS structure for Normally-Off GaN Power Transistors

Minghua Zhu, Catherine Erine, Jun Ma, Mohammad Samizadeh Nikoo, Luca Nela, Pirouz Sohi, and Elison Matioli, *Member, IEEE*

Abstract— In this letter, we present a new concept for normallyoff AlGaN/GaN-on-Si MOS-HEMTs based on the combination of p-GaN, tri-gate and MOS structures to achieve high threshold voltage  $(V_{TH})$  and low on-resistance  $(R_{ON})$ . The p-GaN is used to engineer the band structure and reduce the carrier density  $(N_s)$  in the tri-gate structure for a high  $V_{\rm TH}$ . The gate control is mainly achieved from field-effect though the tri-gate sidewalls, and does not rely on injection of gate current. The MOS structure enables much larger gate voltages  $(V_G)$  and the effective sidewall modulation results in excellent switching performance at high switching frequencies. In addition, this concept eliminates the need for thin barriers (typical in p-GaN devices), which combined to the conduction channels formed at the tri-gate sidewalls, resulted in a smaller Ron compared with planar p-GaN structures. The p-GaN length and tri-gate filling factor (FF) were optimized to achieve a good trade-off between high  $V_{\rm TH}$  and low  $R_{\rm ON}$ . The excellent channel control capability offered by the tri-gate structure led to a higher ON/OFF ratio and smaller sub-threshold slope (SS) compared to similar planar p-GaN devices. These results unveil the excellent prospects of p-GaN tri-gate MOS technology for future power electronics applications.

Index Terms— E-mode, p-GaN, MOS HEMT, tri-gate, trench

# I. INTRODUCTION

GAN (MOS)HEMTs offer a huge potential for high-frequency power electronics applications due to their excellent materials' properties, enabling low  $R_{\rm ON}$  and high breakdown voltages ( $V_{\rm BR}$ ) [1], [2]. Normally-off operation in power devices is highly desired to guarantee a safe operation and to be widely adopted by the power electronics industry [3]. Among several techniques reported to achieve normally-off operation, such as barrier-recess [4]–[7] and fluorine-based plasma treatment under the gate [8], [9], one of the most promising and widely adopted methods is based on p-GaN gates [10]. In this method, the conduction band of the AlGaN/AlN/GaN at the channel under the gate is lifted up by the p-doped GaN at the surface, depleting the 2DEG under the gate [3]. The control of the channel conductivity relies on current injected from the p-GaN ohmic or Schottky gate

This work was supported in part by the Swiss National Science Foundation through Assistant Professor (AP) Energy under Grant PYAPP2\_166901, and in part by the ECSEL Joint Undertaking (JU) under grant agreement No 826392. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Austria, Belgium, Germany, Italy, Norway, Slovakia, Spain, Sweden, Switzerland. The authors are with the Power and Wide-band-gap Electronics Research Laboratory (POWERlab), École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland (e-mail: minghua.zhu@epfl.ch; elison.matioli@epfl.ch).

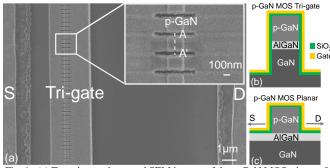

Fig. 1. (a) Top-view and zoomed SEM images of the p-GaN MOS tri-gate (b) Cross-sectional schematic of the p-GaN MOS Tri-gate region along the AA' line, and of the (c) p-GaN MOS Planar gate along the source-drain direction. contacts [11]. However, there is a trade-off between positive  $V_{\rm TH}$  and low sheet resistance ( $R_{\rm S}$ ). On one hand, this is due to the combined effect of the thinner barrier needed for the p-GaN to deplete the channel [3], which increases  $R_{\rm S}$  on the access regions. On the other hand, as shown in this work, it is not possible to fully restore the conductivity of the channel under the p-GaN gate by applying a positive  $V_{\rm G}$ . This indicates that the p-GaN region is still less conductive than the typical access region, even at high  $V_{\rm G}$ . Thus, to reduce the  $R_{\rm ON}$ , a shorter p-GaN and/or a thicker barrier is desired, which however, makes it difficult to reach normally-off behavior.

Tri-gate structures offer an excellent approach to locally adjust the  $N_s$  by etching fins under the gate. This method enables to reach a positive  $V_{TH}$  [12]–[14] while still using thick barriers (~20-25 nm) in the access regions, thus conserving a low access resistance in the un-patterned regions. Etch-induced damages can still be present, however, they are less sensed due to the thicker barrier that yields a larger  $N_s$ . In addition, a significant positive  $V_{TH}$  shift can be achieved by adjusting the tri-gate FF and fin width combined with high work-function gate metals [15].

In this work, we demonstrate the combination of p-GaN, trigate and MOS to form a new device structure that enables to reach positive  $V_{\rm TH}$ , relying on much shorter p-GaN regions with wider tri-gate fins and thicker AlGaN barriers (compared to planar p-GaN gated devices). This yields a significantly smaller  $R_{\rm ON}$  for the same  $V_{\rm TH}$ . In addition, the MOS gate enables a fast control over the channel and much larger  $V_{\rm G}$ , without relying on gate current injection. This also makes them compatible with common gate driver circuits.

© 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for allother uses, in any currentor future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

### II. DEVICE DESIGN AND FABRICATION

Fig.1 illustrates the top-view SEM picture and cross-sectional schematics of the p-GaN tri-gate MOS-HEMTs (p-GaN MOS Tri-gate) (Fig.1 a,b) and p-GaN Planar MOS-HEMTs (p-GaN MOS Planar) (Fig.1c) regions of the fabricated GaN MOS-HEMTs presented in this work. The device fabrication, based on a p-GaN (75 nm)/Al<sub>0.25</sub>Ga<sub>0.75</sub>N (20 nm)/GaN-on-Si wafer, started with the definition of mesa and tri-gate regions by ebeam lithography, followed by Cl<sub>2</sub>-based Inductively Coupled Plasma etch. A major challenge for p-GaN-gated HEMTs is to obtain uniform and low-damage p-GaN etching over the nongated active regions [3], [10], [16]. To this end, the 200 nmwide p-GaN gate region was protected with e-beam lithography resist, followed by a 75 nm-deep low-damage slow-etch-rate Cl<sub>2</sub>/O<sub>2</sub>/Ar-based selective ICP etching recipe [16]–[18]. The high selectivity of 35:1 for p-GaN:AlGaN, combined with O<sub>2</sub> plasma/ HCl treatment is a critical process to minimize surface damages. A surface annealing at 500 °C was performed to further smoothen the surface and recover the dry-etching damages, followed by ohmic contact formation. A 25 nm-thick SiO<sub>2</sub> gate dielectric was deposited by atomic layer deposition (ALD), after surface treatment in 37% HCl for 1 min and 500°C bake for 5 min. Finally, the gate metal was formed by Ni/ Au.

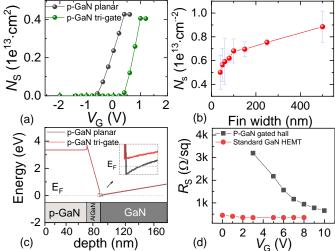

Fig. 2. (a) Simulated electron concentration of p-GaN planar and p-GaN trigate devices on p-GaN (75 nm)/Al<sub>0.25</sub>GaN (20 nm)/GaN epi-structure, under  $V_G$  from -2 to 2 V. (b) Measured electron concentration with different tri-gate fin widths on an AlGaN (20 nm)/GaN structure. (c) Simulated band diagram of p-GaN planar and p-GaN tri-gate devices. (d) Measured sheet resistance by gated hall of a p-GaN and a GaN HEMT structures.

## III. MOTIVATION AND APPROACHES

The thickness and Al molar fraction of the  $Al_xGaN_{I-x}$  barrier are two important parameters influencing the band diagram of the p-GaN/AlGaN/GaN, and the device performance. Traditionally, thin barriers or low Al concentration are used in p-GaN transistors to enable normally-off behavior in equilibrium, as the conduction band edge at the AlGaN/GaN interface should lie above the Fermi level. However, it affects the access regions in the same way, increasing the  $R_s$ . Moreover, etch-induced damages are much more significant on thin barriers, degrading even further the  $R_{on}$ .

In this work, we focus on the use of p-GaN (75 nm-thick) grown on an  $Al_{0.25}GaN$  (20 nm-thick)/GaN epi-structure.

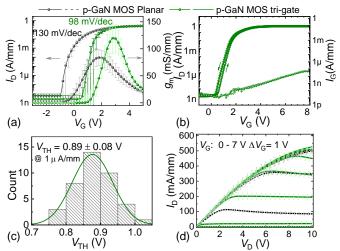

Fig. 3. (a) Comparison of transfer characteristics of the p-GaN MOS Tri-gate and the p-GaN MOS Planar device at  $V_{\rm DS}$  = 5 V. The p-GaN length was 200 nm. (b) Double-sweep  $I_{\rm D}$  and  $I_{\rm G}$  versus  $V_{\rm G}$  for the p-GaN MOS Tri-gate. (c) Histogram of  $V_{\rm TH}$  measured from 40 p-GaN MOS Tri-gate devices. (d) Output characteristics of the two types of devices with  $V_{\rm G}$  up to 7 V. The  $L_{\rm GS}$ ,  $L_{\rm G}$  and  $L_{\rm GD}$  were 1, 2.5 and 10  $\mu$ m, respectively, width was 80  $\mu$ m and FF was 0.66. Standard deviation bars were determined from the measurement of 10 devices of each type, revealing their consistent performance.

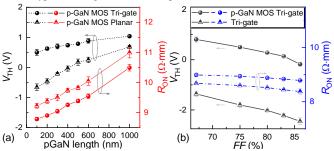

Fig. 4. (a) Dependence of the  $V_{\rm TH}$  and  $R_{\rm ON}$  on the p-GaN length for p-GaN MOS Planar and p-GaN MOS Tri-gate devices. (b)  $V_{\rm TH}$  and  $R_{\rm ON}$  dependence on filling factor (*FF*) of Tri-gate (Normally-on) and p-GaN MOS Tri-gate (Normally-off) transistors (p-GaN length was fixed at 200nm).

Numerical simulations show that the  $N_s$  of p-GaN planar device starts rising at -0.5 V (Fig. 2 (a)), indicating that the p-GaN on such thick barriers is not enough to result in normally-off behavior. Here, this was addressed by adding a tri-gate structure underneath the gate (Fig. 2 (a)). This allows to locally adjust  $N_s$  by the tri-gate fin width (Fig. 2 (b)), while still using a thick barrier for small access resistance. The combined effect of p-GaN and tri-gate lowers the Fermi level farther from the conduction band, as shown in the simulated band diagram of p-GaN planar and p-GaN tri-gate devices (Fig. 2(c)).

Moreover, we compared gated-Hall measurements of  $R_{\rm S}$  between p-GaN and planar HEMTs. This revealed that the channel conductivity under the p-GaN gate is not fully restored even at high  $V_{\rm G}$  (Fig. 2(d)), whereas tri-gate structures cause negligible degradation in  $R_{\rm ON}$  [14]. This shows the importance of reducing the p-GaN length to decrease the overall  $R_{\rm ON}$ . As shown later, a reduction of the p-GaN length without affecting  $V_{\rm TH}$  is possible in tri-gate structures, but not in planar p-GaN MOS-HEMTs.

# IV. RESULTS AND DISCUSSION

In this section, we compare the performance of p-GaN MOS Planar and p-GaN MOS Tri-gate to reveal their operation mechanism. A significant positive shift of 1.5 V in  $V_{\rm TH}$  (at 1

© 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for allother uses, in any currentor futuremedia, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale orredistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

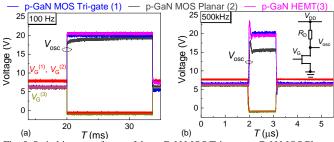

Fig. 5. Switching waveforms of the p-GaN MOS Tri-gate, p-GaN MOS Planar, and p-GaN HEMT at (a) 100 Hz and (b) 500 kHz with  $V_{\rm DD}$  = 20 V and  $V_{\rm G}$  from -1 V to 8 V for p-GaN MOS Tri-gate and p-GaN MOS Planar, while  $V_{\rm G}$  from -1 V to 6 V for p-GaN HEMT, due to its lower gate voltage capability. (Inset) Schematic of experimental setup used to measure the experiment.

μA/mm) was observed from the p-GaN MOS Planar to the p-GaN MOS Tri-gate (Fig. 3(a)), with p-GaN length of 200 nm. The larger  $V_{\text{TH}}$  in the p-GaN MOS Tri-gate is mainly due to the additional strain relaxation of the AlGaN barrier and the sidewall gate modulation [13], [14], [19], [20]. The p-GaN MOS Tri-gate exhibited a larger  $g_m$  of  $124 \pm 18$  mS/mm, with an ON/OFF ratio beyond  $10^9$ , an improved SS of  $98 \pm 5$  mV/dec and lower  $I_{OFF}$  at  $V_G = 0$  V, as compared with the p-GaN MOS Planar, revealing an improved tri-gate control over electrons in the channel. The small hysteresis, below 0.1 V and low gate leakage, below 7×10<sup>-8</sup> A/mm, observed for p-GaN MOS trigate device under V<sub>G</sub> up to 8 V (Fig. 3(b)) indicates a good gateoxide quality. The p-GaN MOS Tri-gate showed a much smaller hysteresis of  $\sim 0.17 \text{ V}$  (at  $V_G^{\text{max}}$  of 8 V), which is also smaller than in the p-GaN Planar (~0.45 V). This is likely due to the better gate control in the Tri-gate, since both devices had the same gate oxide. Moreover, the  $V_{\rm TH}$  histogram from 40 different Tri-gate devices shows a relatively consistent  $V_{\text{TH}}$  of around 0.89 V at 1  $\mu$ A/mm.

The output characteristics of these devices are shown in Fig. 3 (d). The p-GaN MOS Tri-gate presented a good  $I_{\rm D}^{\rm max}$  of 522  $\pm$ 16 mA/mm at  $V_G = 7$  V comparable to the p-GaN MOS Planar (508  $\pm$  18 mA/mm). The high  $I_D^{\text{max}}$  was due to the combined effect of the short p-GaN and the tri-gate structure. The  $R_{ON}$  of the p-GaN MOS Tri-gate and p-GaN MOS Planar, extracted from  $I_D$  -  $V_D$  sweeps in linear region, were  $9.2 \pm 0.26 \ \Omega$ ·mm and  $9.82 \pm 0.29 \ \Omega$ ·mm at  $V_G = 7 \ V$ , respectively. The dependence of  $V_{\rm TH}$  and  $R_{\rm ON}$  on p-GaN gate length was investigated for both devices (Fig. 4(a)). The p-GaN MOS Tri-gate achieved a  $V_{\rm TH}$  of ~0.5 V with a p-GaN length of 100 nm, resulting in a  $R_{\rm ON}$  of  $8.78 \pm 0.05 \ \Omega$ ·mm. On the other hand, the p-GaN MOS Planar devices could only reach a similar  $V_{\text{TH}}$  with p-GaN length of ~1000 nm, thus resulting in an  $R_{\rm ON}$  of 10.99  $\pm$  0.17  $\Omega$ ·mm. For the same p-GaN length, the p-GaN MOS Tri-gate showed a much reduced  $R_{ON}$  compared to the p-GaN MOS Planar.

To reveal the effect of the p-GaN layer, Fig. 4 (b) shows the dependence of  $V_{\rm TH}$  and  $R_{\rm ON}$  on the tri-gate FF for MOS Tri-gate (D-mode) and p-GaN MOS Tri-gate (E-mode) transistors. The trench spacing ( $d_{\rm T}$ ) was fixed at 100 nm and the fin width ( $w_{\rm T}$ ) was varied from 200 nm to 600 nm, which corresponded to FF varying from 0.66 to 0.87. The p-GaN length was fixed at 200 nm. As the FF increased, the  $V_{\rm TH}$  dropped from 0.9 V to -0.2 V for the p-GaN MOS Tri-gate, and from -1.3 V to -2.8 V for the Tri-gate. While the FF had a significant effect on the  $V_{\rm TH}$ , it did

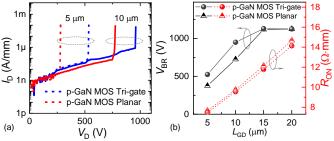

Fig. 6. (a) Breakdown characteristics of the p-GaN MOS Tri-gate (at  $V_{\rm G}=0$  V) and p-GaN MOS Planar (at  $V_{\rm G}=-1$  V) with different  $L_{\rm GD}$  with grounded substrate. (b) Extracted  $V_{\rm BR}$  and  $R_{\rm ON}$  dependence on  $L_{\rm GD}$  of p-GaN MOS Planar and p-GaN MOS Tri-gate. The  $V_{\rm BR}$  was defined at  $I_{\rm OFF}\leq 1~\mu{\rm A/mm}$ .

not affect much the  $R_{\rm ON}$ , presenting only a reduction of 0.2  $\Omega$ ·mm for the p-GaN MOS Tri-gate, and of 0.4  $\Omega$ ·mm for the Tri-gate. Thus a small  $R_{\rm ON}$  and positive  $V_{\rm TH}$  can be designed with a short p-GaN combined with tri-gates with small FF.

The dynamic performance of p-GaN MOS Planar, p-GaN MOS Tri-gate, and p-GaN HEMT was investigated using the device test setup shown in the inset of Fig. 5. At a low frequency of 100 Hz (Fig. 5 (a)), it took a few miliseconds for the p-GaN MOS Planar to be completely turned off, while the p-GaN MOS Tri-gate and p-GaN HEMT turned-off instantaneously. This phenomenon can be seen more clearly at 500 kHz (Fig. 5 (b)). The p-GaN MOS Tri-gate and p-GaN HEMTs can be turned on/off within a few nanoseconds, while the p-GaN MOS Planar could not fully turn off at such frequencies. This shows the effective and fast sidewall gate control of p-GaN MOS Tri-gate, which is more dominant than the top gate control in traditional GaN HEMTs. For the p-GaN MOS planar device, the gate control is mainly through fringing capacitances from the surface to the 2DEG, which is less effective compared with the tri-gate sidewall control.

The comparison of breakdown characteristics between the p-GaN MOS Planar and p-GaN MOS Tri-gate is shown in Fig. 6. The  $V_{\rm BR}$  of p-GaN MOS Tri-gate was extracted for  $V_{\rm G}$  of 0 V with grounded substrate at 1  $\mu$ A/mm (Fig. 6 (a)), resulting in 520 V and 980 V for  $L_{\rm GD}$  of 5  $\mu$ m and 10  $\mu$ m, respectively, compared to 380 V and 750V, for p-GaN MOS planar devices (at  $V_{\rm G}=-1$  V). The observed improvement in  $V_{\rm BR}$  compared with the p-GaN MOS Planar is due to the effective integrated field plates (FP) in the p-GaN tri-gate region [16, 21]. The p-GaN MOS Tri-gate presented lower  $R_{\rm ON}$  for the same  $L_{\rm GD}$  compared with p-GaN MOS Planar devices (Fig. 6 (b)). The low  $R_{\rm ON}$ , larger  $V_{\rm TH}$  and  $V_{\rm BR}$ , together with the effective gate control reveal the significant potential of the p-GaN tri-gate MOS technology for high-performance E-mode GaN devices.

## V. CONCLUSIONS

In this work we have demonstrated normally-off p-GaN trigate GaN-on-Si MOSHEMTs with a combination of tri-gate, p-GaN and MOS structures on the gate. The introduction of the tri-gate enables a reduction of the necessary p-GaN length to reach E-mode operation, resulting in a smaller  $R_{\rm ON}$ . With a selective p-GaN recess, an integrated field plate and an optimized p-GaN structure, p-GaN MOS Tri-gate devices presented  $V_{\rm TH}$  of 0.9 V at 1 $\mu$ A/mm, low  $R_{\rm ON}$  of 9.2  $\Omega$ ·mm and high  $V_{\rm BR}$  of 960 V for  $L_{\rm GD}$  of 10  $\mu$ m, with grounded substrate.

### REFERENCES

- [1] M. Tao, S. Liu, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, K. Cheng, B. Shen, and M. Wang, "Characterization of 880 V Normally Off GaN MOSHEMT on Silicon Substrate Fabricated With a Plasma-Free, Self-Terminated Gate Recess Process," *IEEE Trans. Electron Devices*, vol. 65, no. 4, pp. 1453–1457, Apr. 2018, doi: 10.1109/TED.2018.2808345.

- [2] P. Fiorenza, G. Greco, F. Iucolano, A. Patti, and F. Roccaforte, "Channel Mobility in GaN Hybrid MOS-HEMT Using SiO2as Gate Insulator," *IEEE Trans. Electron Devices*, vol. 64, no. 7, pp. 2893–2899, Jul. 2017, doi: 10.1109/TED.2017.2699786.

- [3] G. Greco, F. Iucolano, and F. Roccaforte, "Review of technology for normally-off HEMTs with p-GaN gate," *Mater. Sci. Semicond. Process.*, Oct. 2017, doi: 10.1016/j.mssp.2017.09.027.

- [4] Z. Xu, J. Wang, Y. Liu, J. Cai, J. Liu, M. Wang, M. Yu, B. Xie, W. Wu, X. Ma, and J. Zhang, "Fabrication of Normally Off AlGaN/GaN MOSFET Using a Self-Terminating Gate Recess Etching Technique," *IEEE Electron Device Lett.*, vol. 34, no. 7, pp. 855–857, Jul. 2013, doi: 10.1109/LED.2013.2264494.

- [5] M. Hua, Z. Zhang, J. Wei, J. Lei, G. Tang, K. Fu, Y. Cai, B. Zhang, and K. J. Chen, "Integration of LPCVD-SiNx gate dielectric with recessedgate E-mode GaN MIS-FETs: Toward high performance, high stability and long TDDB lifetime," in 2016 IEEE Int. Electron Devices Meet. IEDM, Dec. 2016, p. 10.4.1-10.4.4, doi: 10.1109/IEDM.2016.7838388.

- [6] W. B. Lanford, T. Tanaka, Y. Otoki, and I. Adesida, "Recessed-gate enhancement-mode GaN HEMT with high threshold voltage," *Electron. Lett.*, vol. 41, no. 7, pp. 449–450, Mar. 2005, doi: 10.1049/el:20050161.

- [7] J. He, M. Hua, Z. Zhang, and K. J. Chen, "Performance andVTHStability in E-Mode GaN Fully Recessed MIS-FETs and Partially Recessed MIS-HEMTs With LPCVD-SiNx/PECVD-SiNxGate Dielectric Stack," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3185–3191, Aug. 2018, doi: 10.1109/TED.2018.2850042.

- [8] Y. Zhang, M. Sun, S. J. Joglekar, and T. Palacios, "High threshold voltage in GaN MOS-HEMTs modulated by fluorine plasma and gate oxide," in 71st Device Res. Conf., Jun. 2013, pp. 141–142, doi: 10.1109/DRC.2013.6633833.

- [9] L. Yang, B. Hou, M. Mi, Q. Zhu, M. Wu, J. Zhu, Y. Lu, M. Zhang, L. Chen, X. Zhou, L. Lv, X. Ma, and Y. Hao, "High-Performance Enhancement-mode AlGaN/GaN high electron mobility transistors combined with TiN-based Source Contact Ledge and Two-Step Fluorine Treatment," *IEEE Electron Device Lett.*, pp. 1–1, 2018, doi: 10.1109/LED.2018.2864135.

- [10] Y. Zhou, Y. Zhong, H. Gao, S. Dai, J. He, M. Feng, Y. Zhao, Q. Sun, A. Dingsun, and H. Yang, "p-GaN Gate Enhancement-Mode HEMT Through a High Tolerance Self-Terminated Etching Process," *IEEE J. Electron Devices Soc.*, vol. 5, no. 5, pp. 340–346, Sep. 2017, doi: 10.1109/JEDS.2017.2725320.

- [11] B. Bakeroot, S. Stoffels, N. Posthuma, D. Wellekens, and S. Decoutere, "Trading Off between Threshold Voltage and Subthreshold Slope in AlGaN/GaN HEMTs with a p-GaN Gate," in 2019 31st Int. Symp. Power Semicond. Devices ICs ISPSD, May 2019, pp. 419–422, doi: 10.1109/ISPSD.2019.8757629.

- [12] B. Lu, E. Matioli, and T. Palacios, "Tri-Gate Normally-Off GaN Power MISFET," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 360–362, Mar. 2012, doi: 10.1109/LED.2011.2179971.

- [13] S. Liu, Y. Cai, G. Gu, J. Wang, C. Zeng, W. Shi, Z. Feng, H. Qin, Z. Cheng, K. J. Chen, and B. Zhang, "Enhancement-Mode Operation of Nanochannel Array (NCA) AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 354–356, Mar. 2012, doi: 10.1109/LED.2011.2179003.

- [14] J. Ma and E. Matioli, "High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 367–370, Mar. 2017, doi: 10.1109/LED.2017.2661755.

- [15] L. Nela, M. Zhu, J. Ma, and E. Matioli, "High-Performance Nanowire-Based E-Mode Power GaN MOSHEMTs With Large Work-Function Gate Metal," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 439–442, Mar. 2019, doi: 10.1109/LED.2019.2896359.

- [16] Y. Zhong, Y. Zhou, H. Gao, S. Dai, J. He, M. Feng, Q. Sun, J. Zhang, Y. Zhao, A. DingSun, and H. Yang, "Self-terminated etching of GaN with a high selectivity over AlGaN under inductively coupled Cl2/N2/O2 plasma with a low-energy ion bombardment," *Appl. Surf. Sci.*, vol. 420, pp. 817–824, Oct. 2017, doi: 10.1016/j.apsusc.2017.05.185.

- [17] G. Lükens, H. Hahn, H. Kalisch, and A. Vescan, "Self-Aligned Process for Selectively Etched p-GaN-Gated AlGaN/GaN-on-Si HFETs," *IEEE Trans. Electron Devices*, vol. 65, no. 9, pp. 3732–3738, Sep. 2018, doi: 10.1109/TED.2018.2860634.

- [18] S. A. Smith, W. V. Lampert, P. Rajagopal, A. D. Banks, D. Thomson, and R. F. Davis, "Selective etching of GaN over AlN using an inductively coupled plasma and an O2/Cl2/Ar chemistry," *J. Vac. Sci. Technol. Vac. Surf. Films*, vol. 18, no. 3, pp. 879–881, May 2000, doi: 10.1116/1.582270.

- [19] M. Azize and T. Palacios, "Top-down fabrication of AlGaN/GaN nanoribbons," Appl. Phys. Lett., vol. 98, no. 4, p. 042103, Jan. 2011, doi: 10.1063/1.3544048.

- [20] O. Landré, D. Camacho, C. Bougerol, Y. M. Niquet, V. Favre-Nicolin, G. Renaud, H. Renevier, and B. Daudin, "Elastic strain relaxation in GaN/AlN nanowire superlattice," *Phys. Rev. B*, vol. 81, no. 15, p. 153306, Apr. 2010, doi: 10.1103/PhysRevB.81.153306.

- [21] J. Ma, D. C. Zanuz, and E. Matioli, "Field Plate Design for Low Leakage Current in Lateral GaN Power Schottky Diodes: Role of the Pinch-off Voltage," *IEEE Electron Device Lett.*, vol. 38, no. 9, pp. 1298–1301, Sep. 2017, doi: 10.1109/LED.2017.2734644.