### Cryogenic CMOS Integrated Circuits for Scalable Readout of Silicon Quantum Computers

Présentée le 15 mars 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

#### **Andrea RUFFINO**

Acceptée sur proposition du jury

Prof. G. De Micheli, président du jury

Prof. E. Charbon, directeur de thèse

Prof. D. DiVincenzo, rapporteur

Dr M. F. Gonzalez-Zalba, rapporteur

Prof. C. Enz, rapporteur

A mamma, papà e Marco, per essermi sempre vicini anche da lontano...

## Acknowledgements

A Ph.D. is not only a research journey, but also a story, and like every story, it has its own characters. This is the space where I tell my story and thank all the people who made an appearance in it, with a big or small contribution, in a positive or negative way.

First of all, I have to thank my Thesis Director, Prof. Edoardo Charbon, who gave me the chance to join his research group when, honestly, I did not know how to do much. I want to acknowledge the freedom I had in exploring my own solutions to the research problems we faced, and the undoubtedly positive, open-minded and forward-looking approach to research he always showed in our discussions about such research solutions. I want to thank him for the opportunities he gave me to travel, to know, meet and work with amazing researchers in our field. In particular, I want to thank him for giving me the opportunity to spend a research period in the extended group at TU Delft, in what I consider the best research group in the world in our field, cryogenic electronics for quantum computing. Moreover, he also deserves credit for creating such an environment in the first place. I also want to say that, despite the unbelievable amount of commitments he has and how busy he is, he was always available under our strict deadlines.

Secondly, I want to thank Prof. Masoud Babaie and Prof. Fabio Sebastiano, who have been my co-supervisors during my visiting period in Delft. No matter how problematic and "fluid" my stay in Delft was, it has been the turning point in my Ph.D. journey. I have to say it is thanks to them that I learned how to design (some) circuits. I still remember the long time we spent, especially with Masoud, to break down circuits, analyze their problems and build them up again, to come up with new ideas to improve the design. In Delft I learned the process to invent new circuits and it is something I will remember forever. I still recall the feeling when, after several weeks of trials, I came up with the all-pass filter idea for the circulator, combining the influence of several discussions, and it worked in simulation. The accomplishment, although very small in the big picture, was great and the quest for that feeling of realization fueled me for the rest of my Ph.D.. In Delft, thanks to them, I was also constantly reminded that nice things normally come only after hard work, but I later understood that the tough teaching style and very objective judgment of everybody's work was just fair and, in the end, worth it.

Then I want to thank my colleague Dr. Yatao Peng. I have spent the second part of my Ph.D. working in strict collaboration with him as a Scientist in our group at EPFL. It is fair to say that, without him, my Ph.D. would not have been possible. I learned from him how to perform RF measurements and how to design advanced RF circuits and we accomplished great things together. I worked for him and with him, and my work is definitely also his work. Unfortunately, in the last part of our collaboration, everybody was struck by the constant obsession of our laboratory to do as many things as possible,

all together, in the shortest time possible, and this made our collaboration much more difficult, but this does not change all the good moments, especially at the beginning, when there was no additional project, it was just the two of us and things were simpler.

Then, at EPFL, I have to thank Dr. Claudio Bruschini, who helped me, especially in the beginning of my Ph.D., when I was the first and only member of the new AQUA laboratory, and supervised and managed the project MOS-Quito, which was the source of funding for the main part of my Ph.D..

Moreover, I would like to thank Prof. Christian Enz, Dr. Fernando Gonzalez-Zalba, Prof. David DiVincenzo and Prof. Giovanni De Micheli for being members of the Jury for my Oral Exam and for contributing to improve this thesis, but not only.

I am grateful to Prof. Enz for kindly hosting me, together with his whole ICLAB group, as a guest member, especially in the initial part of my Ph.D., when I was the only member in the new AQUA laboratory. This helped me to get introduced to the Ph.D. environment in a smoother way. We also had a fruitful collaboration in the initial part of the Ph.D. within the MOS-Quito project, which was very useful to kick-start my research path. I also want to thank him for lending us all the RF instruments that I have used for every measurement during my Ph.D., without which my Ph.D. would have been impossible.

I want to thank Dr. Gonzalez-Zalba for the great collaboration we had with him and his group in the second part of my Ph.D., which was extremely fruitful both from a scientific and from a human point of view. I greatly admire Fernando for his very calm, confident and knowledgeable way of approaching scientific challenges and I have learned a lot from him, as a person. From the scientific point of view, it was a great opportunity for me to visit Cambridge and have the chance to collaborate with a great group of physicists to learn about quantum measurements in a well-established laboratory.

I would like to thank Prof. David DiVincenzo for the useful discussion we had in Delft about circulators for quantum computing and for the genuine scientific interest and curiosity expressed in the work I was doing.

Finally, thanks to Prof. Giovanni De Micheli, who was a member of my Candidacy Exam and is therefore the ideal person to represent EPFL and its quantum community as the President of the Jury for my Oral Exam.

As the work I did was not only individual work, but frequently a group effort, it is my duty and pleasure to thank all the members of the quantum group in Delft, which I joined for a period, but to which I felt belonging for the whole duration of my Ph.D.. The coolgroup is, as the name suggests, cool indeed and I feel I had the privilege to witness and be part of it at its peak, when the great results that were later published were taking their shape. I was definitely lucky, and I learned so much during that time, in a truly collaborative spirit, hard to be matched. I might or might not have been a complete member of the group, but I definitely felt like it.

I want to thank all my colleagues and friends, from the group founding fathers Harald, Rosario, Bishnu, Jeroen, to the later members Pascal, Jiang, Milad, Gerd and the "Master students" (despite the fact they graduated now) Sriram, Job, Jaco, Edwin and all the others. From Harald I will remember the incredible work ethic and efficiency, accompanied by an admirable personal balance, I am grateful to Rosario because he was very kind and helped me a lot to get introduced to TU Delft, with Bishnu I remember many fun moments during meetings and table soccer games, while from Jeroen I admire how great of a circuit designer he is, but I just can't forget his dull, dead, Dutch lunch meals. From

Pascal I can't forget his clothes scattered all over the office and the many fun moments we definitely had, despite how blunt of a Dutch he is, with Jiang I remember many fun times in the office and many interesting circuit discussions, Milad is simply one of the most talented circuit designers I have met, and Gerd was the last addition before I left. They are all among the most brilliant people I have met, and by being much smarter than me, I had the chance to learn a lot from them. Moreover, we created so many great memories together, among which I think the trip to Portland for the Silicon Quantum Electronics Workshop, to witness the solar eclipse, tops them all.

In Delft, not only "quantum" people deserve a mention, but also the "SPAD" people, with whom I spent great time as well. I want to thank my friends Ting, Esteban, Augusto Carimatto, Augusto Ximenes, Chao, Michel and the other Master students back then. Ting is definitely the funniest, wittiest Chinese I have met, Esteban is a great guy, but he surely needs to work on his table soccer skills and related competitiveness, Augusto Carimatto is a dear friend and I want to thank him for shining some light in many dark, rainy days in the big office in Delft with his contagious laughter, I want to thank Augusto Ximenes for the interesting discussions, Chao for the brilliant life mottos and teachings I still go by today and my friend Michel for being a very smart, wise and extremely balanced person. Another group of people who deserve acknowledgments is the group of Italians at QuTech in Delft. I want to thank Andrea, Marco, Diego, Luca for the fun lunch breaks at QuTech, the discussions about the weirdest plot theories and all the fun.

Finally, I also want to thank Joyce for her help with the administrative issues during my stay in Delft.

Then at EPFL, I have to thank the overwhelming, ever-growing "SPAD" group I have been constantly surrounded by. From the original members Samuel, Scott, to the first new members Arin, Preethi, Francesco, to all the fresher ones Kazu, Andrei, Andrada, Pouyan, Ekin, Utku, Milo, Jiuxuan, Feng, Emanuele and all the other members. They are so many and still growing I will probably always forget someone anyway. I want to thank Samuel for introducing me to the new world of AQUA at the beginning and for showing me what being independent means, I want to thank Scott for the nice discussions we had and for sharing the feeling of what being scattered among several places means, from Arin I will remember his irreproachable work ethic and his subtle, blunt, underrated humor, from Preethi I greatly admire the brilliance of her work and her great charisma, and then I want to thank Francesco and Emanuele for their funny messages during the most inappropriate times. A special mention for my buddies Pouyan and Bedo, for our train station meetings and discussions, and for all the good times together, as well as for the Turkish gang, Ekin and Utku, for the train rides, videogames and nice discussions.

Finally, I want to thank one of the most important people within the AQUA group, Brigitte, a true pillar without which the whole lab would instantly collapse. Thank you for helping with so many problems that go far beyond the administrative tasks and for making life in general simpler.

As much as I have people to thank in the AQUA group at TU Delft and EPFL, I have people to thank in ICLAB. We spent a lot of time together, especially at the beginning of my Ph.D., when all I had was a desk, a chair and a (borrowed) multimeter, since the screens and laptop arrived after a few months. I want to thank the founders Vladimir, Raghav, Jérémy, Vincent, the later members Farzan, Chunmin, Arnout, Sammy, but especially the Italian crew for the long time spent together, the hospitality and the train rides. Thanks to Mattia,

Raffaele, Francesco, Nino, Alessandro, Antonio for the interesting discussions, the table soccer games and fun. In particular, I want to thank Arnout for the fruitful collaboration we established in the first part of my Ph.D., within the project MOS-Quito, and Farzan, for supervising us during that time and for always being kind to me. A special mention goes to my friend Mattia and his girlfriend (now wife) Michela for their hospitality and help during key times in my Ph.D.: also in this case, it is fair to say that without their help, my Ph.D. would not have been possible.

Still at EPFL, I would like to thank Lucie Auberson from EDMI, and all the people from the Doctoral School for their help and support in the process.

In Cambridge, I would like to thank Tsung-Yeh and John for the great collaboration we had.

Apart from all the people I have met during this research journey, I want to deeply thank all my friends and connections at home, in Torino and Barbania, for keeping me well rooted to where I come from and where I belong. I want to thank my dear friend Paolo for always offering a chance of distraction with some nice football banter, my cousin Sara for growing up together, and for being part of my life even now that we have become adults and live far away and my friend Giuliano for cheering me up with his funny, positive approach to life.

Finally, and most importantly, I want to thank my family: mum, dad and my big brother Marco. I want to thank them for being the best people I could ask for, for providing constant support from home, and for always being there to help in all the difficult times during this journey. I learned from them what commitment means and they have been my constant motivation to keep me going along this path. Without them, nothing I have achieved so far, not only this Ph.D., would have been possible.

andrea Ruffins

Lausanne, 15th November 2020

## **Abstract**

Quantum computing promises to revolutionize our lives, achieving unprecedented computational powers and unlocking new possibilities in drug discovery, chemical simulations and cryptography. The fundamental unit of computation of a quantum computer is the quantum bit (qubit). It can be implemented in a number of technologies, such as superconducting qubits, spin qubits, photonic systems, trapped ions and NV-centers. Solid-state superconducting qubits and spin qubits seem to be the most promising ones, as shown by the recent demonstration of quantum supremacy with a superconducting qubit processor. Such quantum processors, to operate in the quantum regime, require very low temperatures around 10 mK, and they are hence kept inside dilution fridges. The electronics required to read out and control such processors is typically realized by discrete components or bulky scientific instruments at room temperature wired into the dilution fridge. Such approach is only feasible until few (< 100) qubits are handled, but it is not scalable for million-qubit processors required for fault-tolerant operation.

In this thesis, readout and control electronics is proposed to be integrated and operated directly at cryogenic temperatures, in close proximity with the qubits and potentially even co-integrated. CMOS technology is advocated for its scalability, compactness and low prototyping cost, to create a comprehensive cryo-CMOS class of fully-integrated transceivers to read out and control solid-state qubits. In particular, the thesis focuses on cryo-CMOS radio-frequency integrated circuits for the readout of silicon quantum computers, looking to integrate the whole readout system, from the quantum layer to the room temperature user interface.

Cryogenic CMOS devices are explored first, to lay the foundations of integrated circuit design. The realization of quantum dots in standard CMOS technology is explored as a platform to realize solid-state qubit arrays, demonstrating functionality at 50 mK and good reproducibility. Moreover, the operation of integrated transistors at 50 mK and 4.2 K is explored to understand their basic cryogenic functionality, through characterization and modeling. Then also integrated passives, such as capacitors, inductors and transformers, are studied and modeled at cryogenic temperatures.

Then, a fully-integrated readout platform spanning across all the blocks needed for dispersive readout is proposed. A fully-integrated matrix of quantum dots with radio-frequency gate-based readout capabilities is demonstrated along with time- and frequency-multiplexing. This quantum-classical circuit shows all the features for a scalable approach and is the core of the platform following it. A cryogenic CMOS circulator based on a new all-pass filter architecture is demonstrated, to be used as integrated replacement for current bulky counterparts; it allows power reduction, insertion loss and bandwidth enhancement with respect to state-of-the-art integrated circulators. The rest of the front-end is also

#### **Abstract**

explored with dedicated test multiplexers, a low noise-amplifier and an oscillator, that are finally merged in a single fully-integrated low-noise receiver with frequency synthesizer operating at 3.5 K for scalable multiplexed readout of silicon qubits.

The platform presented in this thesis, across temperature boundaries, carries all the features required for future scalable silicon quantum computing platforms and could therefore form their core.

**Keywords:** Quantum computer, quantum processor, spin qubit, quantum dot, scalability, cryogenic characterization, modeling, cryo-CMOS, quantum integrated circuit, radio-frequency integrated circuit, gate-based reflectometry, multiplexing, circulator, low-noise amplifier, low-noise receiver.

## **Sommario**

Il calcolo quantistico promette di rivoluzionare le nostre vite, raggiungendo potenze di calcolo mai ottenute finora e aprendo nuove possibilità nella scoperta di medicinali, simulazioni chimiche e crittografia. L'unità di calcolo fondamentale di un calcolatore quantistico è il quantum bit (qubit). Esso può essere realizzato in diverse tecnologie, come i qubit superconduttivi, i qubit di spin, sistemi fotonici, trappole ioniche, o centri azoto-vacanza. I qubit a stato solido superconduttivi o di spin sembrano essere i più promettenti, come indicato dalla recente dimostrazione di supremazia quantistica con un processore quantistico superconduttivo.

Tali calcolatori quantistici, per operare nel regime quantistico, richiedono temperature molto basse, intorno a 10 mK, e pertanto sono tenuti dentro a dei refrigeratori a diluizione. L'elettronica richiesta per leggere e controllare tali processori è di norma realizzata da componenti discreti o voluminosi strumenti scientifici a temperatura ambiente collegati da cavi dentro al refrigeratore a diluizione. Tale approccio è possibile soltanto finchè pochi (< 100) qubit sono trattati, ma non è scalabile a processori da milioni di qubit, come richiesto da un'operazione tollerante agli errori quantistici.

In questa tesi, si propone di integrare l'elettronica di lettura e controllo e di operarla direttamente a temperature criogeniche, a stretto contatto con i qubit e potenzialmente perfino cointegrata. La tecnologia CMOS è raccomandata per la sua scalabilità, compattezza e basso costo di prototipazione, per creare una classe comprensiva di ricetrasmettitori criogenici CMOS completamente integrati per leggere e controllare qubit a stato solido. In particolare, questa tesi si concentra su circuiti criogenici CMOS integrati a radiofrequenza per la lettura di calcolatori quantistici in silicio, nella prospettiva di integrare l'intero sistema di lettura, dal livello quantistico all'interfaccia con l'utente a temperatura ambiente. I dispositivi criogenici CMOS sono esplorati per primi, per porre le basi della progettazione di circuiti integrati criogenici. La realizzazione di punti quantistici in tecnologia standard CMOS è esplorata come piattaforma per realizzare matrici di qubit a stato solido, dimostrandone la funzionalità a 50 mK e buona riproducibilità. Inoltre, l'operazione di transistor integrati a 50 mK e 4.2 K è studiata per caprine la funzionalità criogenica di base, per mezzo di caratterizzazione e modellizzazione. Poi anche i componenti passivi integrati, come condensatori, induttori e trasformatori, sono studiati e modellizzati a temperature criogeniche.

In seguito, viene proposta una piattaforma di lettura completamente integrata che percorre i vari blocchi richiesti dalla tecnica di lettura dispersiva sul gate dei transistor. Una matrice completamente integrata di punti quantistici con capacità di lettura a radiofrequenza sul gate dei transistor è dimostrata insieme alla multiplazione nel dominio del tempo e della frequenza. Questo circuito quantistico-classico mostra tutte le caratteristiche richieste per un approccio scalabile ed è il cuore della piattaforma che lo segue. Un circolatore criogenico in CMOS basato su una nuova architettura di filtri passa-tutto è dimostrato, per essere usato come sostituto integrato delle corrispettive parti discrete; permette riduzione di potenza consumata e di perdita d'inserzione e un aumento di banda rispetto a circolatori integrati allo stato dell'arte. Anche il resto dell'interfaccia frontale è esplorato con dei multiplatori, un amplificatore a basso rumore e un oscillatore, che alla fine sono uniti in un singolo ricevitore a basso rumore completamente integrato con sintetizzatore di frequenza che opera a 3.5 K per la lettura scalabile e multipla di qubit al silicio.

La piattaforma presentata in quesa tesi, attraverso diverse regioni di temperatura, possiede tutte le caratteristiche richieste dalle piattaforme di calcolo quantistico scalabili al silicio e potrebbe pertanto formarne la base in futuro.

**Parole chiave:** Calcolatore quantistico, processore quantistico, qubit di spin, punto quantistico, scalabilità, caratterizzazione criogenica, modellizzazione, CMOS criogenico, circuito integrato quantistico, circuito integrato a radiofrequenza, riflettometria sul gate, multiplazione, circolatore, amplificatore a basso rumore, ricevitore a basso rumore.

## Résumé

L'informatique quantique promet de révolutionner nos vies, en atteignant des puissances de calcul sans précédent et en ouvrant des nouvelles possibilités dans la découverte de médicaments, les simulations chimiques et la cryptographie. L'unité fondamentale de calcul d'un ordinateur quantique est le bit quantique (qubit). Il peut être réalisé avec plusieurs technologies, telles que les qubits supraconducteurs, les qubits de spin, les systèmes photoniques, les ions piégés et les centres azote-lacune. Les qubits à l'état solide supraconducteurs et de spin semblent être les plus prometteurs, comme le montre la récente démonstration de la suprématie quantique avec un processeur de qubits supraconducteurs.

Ces processeurs quantiques, pour fonctionner dans le régime quantique, nécessitent des températures très basses, autour de 10 mK, et ils sont donc conservés dans des réfrigérateurs à dilution. L'électronique nécessaire pour lire et contrôler ces processeurs est généralement réalisée par des composants discrets ou des instruments scientifiques volumineux à température ambiante câblés dans le réfrigérateur à dilution. Une telle approche n'est possible que jusqu'à ce que quelques qubits (< 100) soient traités, mais elle n'est pas extensible pour les processeurs de millions de qubits nécessaires à un fonctionnement tolérant aux erreurs quantiques.

Dans cette thèse, il est proposé d'intégrer et de faire fonctionner l'électronique de lecture et de contrôle directement à des températures cryogéniques, à proximité immédiate des qubits et potentiellement même co-intégrée avec. La technologie CMOS est préconisée pour son extensibilité, sa compacité et son faible coût de prototypage, afin de créer une classe complète d'émetteurs-récepteurs CMOS cryogéniques entièrement intégrés pour lire et contrôler les qubits à l'état solide. La thèse se concentre en particulier sur les circuits intégrés CMOS cryogéniques à radiofréquence pour la lecture des ordinateurs quantiques en silicium, en cherchant à intégrer l'ensemble du système de lecture, de la couche quantique à l'interface utilisateur à température ambiante.

Les dispositifs CMOS cryogéniques sont explorés d'abord, pour jeter les bases de la conception des circuits intégrés. La réalisation de points quantiques dans la technologie CMOS standard est explorée comme une plate-forme pour réaliser des matrices de qubits à l'état solide, démontrant la fonctionnalité à 50 mK et une bonne reproductibilité. En outre, le fonctionnement des transistors intégrés à 50 mK et 4.2 K est exploré pour comprendre leur fonctionnalité cryogénique de base, au moyen de la caractérisation et de la modélisation. Puis, les passifs intégrés, tels que les condensateurs, les inductances et les transformateurs, sont également étudiés et modélisés à des températures cryogéniques.

Ensuite, une plate-forme de lecture entièrement intégrée couvrant tous les blocs nécessaires à la lecture dispersive sur la grille des transistors est proposée. Une matrice

entièrement intégrée de points quantiques avec des capacités de lecture dispersive à radiofréquence sur la grille des transistors est démontrée avec le multiplexage en temps et en fréquence. Ce circuit quantique-classique présente toutes les caractéristiques requises pour une approche extensible et constitue le cœur de la plate-forme qui le suit. Un circulateur CMOS cryogénique basé sur une nouvelle architecture de filtres passe-tout est démontré, pour être utilisé comme remplacement intégré des circulateurs encombrants actuels ; il permet une réduction de la puissance, de la perte d'insertion et une amélioration de la bande passante par rapport aux circulateurs intégrés de pointe. Le reste du circuit frontal est également exploré avec des multiplexeurs de test dédiés, un amplificateur à faible bruit et un oscillateur, qui sont finalement combinés en un seul récepteur à faible bruit entièrement intégré avec un synthétiseur de fréquence fonctionnant à 3.5 K pour une lecture multiplexée extensible des qubits de silicium.

La plate-forme présentée dans cette thèse, à travers différentes régions de température, comporte toutes les caractéristiques requises pour les futures plates-formes de calcul quantique en silicium extensibles et pourrait donc en constituer le cœur.

**Mots-clés :** Ordinateur quantique, processeur quantique, qubit de spin, point quantique, extensibilité, caractérisation cryogénique, modélisation, CMOS cryogénique, circuit intégré quantique, circuit intégré à radiofréquence, réflectométrie sur la grille, multiplexage, circulateur, amplificateur à faible bruit, récepteur à faible bruit.

## Zusammenfassung

Quantencomputer versprechen, unser Leben zu revolutionieren, indem sie eine noch nie dagewesene Rechenleistung erreichen und neue Möglichkeiten in der Medikamentenentwicklung, chemischen Simulationen und Kryptographie erschließen. Die fundamentale Berechnungseinheit eines Quantencomputers ist das Quantenbit (Qubit). Es kann in einer Reihe von Technologien implementiert werden, sowie supraleitenden Qubits, Spin-Qubits, photonischen Systemen, gefangenen Ionen und Stickstoff-Fehlstellen-Zentren. Festkörper supraleitende Qubits und Spin-Qubits scheinen die vielversprechendsten zu sein, wie die jüngste Demonstration der Quantenüberlegenheit mit einem supraleitenden Qubit-Prozessor zeigt.

Solche Quantenprozessoren benötigen, um im Quantenregime zu arbeiten, sehr niedrige Temperaturen, etwa 10 mK, und werden daher in Verdünnungskühlschränken gehalten. Die Elektronik, die zum Auslesen und Steuern solcher Prozessoren benötigt wird, wird typischerweise durch diskrete Komponenten oder sperrige wissenschaftliche Instrumente bei Raumtemperatur realisiert, die mit dem Verdünnungskühlschrank verkabelt sind. Ein solcher Ansatz ist nur bis zu wenigen (< 100) Qubits praktikabel, aber für Millionen-Qubit-Prozessoren, die für einen quantenfehlertoleranten Betrieb benötigt werden, nicht skalierbar.

In dieser Arbeit wird vorgeschlagen, die Auslese- und Steuerelektronik direkt bei kryogenen Temperaturen zu integrieren und zu betreiben, in unmittelbarer Nähe zu den Qubits und möglicherweise sogar ko-integriert. Die CMOS-Technologie wird wegen ihrer Skalierbarkeit, Kompaktheit und niedrigen Prototyping-Kosten befürwortet, um eine umfassende kryo-CMOS Klasse voll integrierter Transceiver zum Auslesen und Steuern von Festkörper-Qubits zu schaffen. Insbesondere konzentriert sich die Arbeit auf kryo-CMOS-Hochfrequenz-integrierte Schaltungen für das Auslesen von Silizium-Quantencomputern, um das gesamte Auslesesystem, von der Quantenschicht bis zur Benutzerschnittstelle bei Raumtemperatur, zu integrieren.

Zunächst werden kryogene CMOS-Bauelemente untersucht, um die Grundlagen für das Design der integrierten Schaltungen zu schaffen. Die Realisierung von Quantenpunkten in Standard-CMOS-Technologie wird als Plattform für die Realisierung von Festkörper-Qubit-Matrizen erforscht, wobei Funktionalität bei 50 mK und gute Reproduzierbarkeit demonstriert werden. Darüber hinaus wird der Betrieb von integrierten Transistoren bei 50 mK und 4.2 K erforscht, um deren grundlegende kryogene Funktionalität durch Charakterisierung und Modellierung zu verstehen. Dann werden auch integrierte passive Bauelemente, wie Kondensatoren, Induktivitäten und Transformatoren, bei kryogenen Temperaturen untersucht und modelliert.

Danach wird eine vollintegrierte Ausleseplattform vorgeschlagen, die alle Blöcke umfasst,

#### Zusammenfassung

die für eine dispersive Gate-basierte Auslese benötigt werden. Eine vollintegrierte Matrix von Quantenpunkten mit hochfrequenten Gate-basierten Auslesemöglichkeiten wird zusammen mit Zeit- und Frequenz-Multiplexing demonstriert. Diese quantenklassische Schaltung zeigt alle Eigenschaften, die für einen skalierbaren Ansatz erforderlich sind, und ist das Herzstück der folgenden Plattform. Ein kryogener CMOS-Zirkulator, der auf einer neuen Allpass-Filter-Architektur basiert, wird demonstriert, um als integrierter Ersatz für die derzeitigen sperrigen Gegenstücke verwendet zu werden; er ermöglicht eine Leistungsreduzierung, Einfügungsdämpfungsreduzierung und Bandbreitenverbesserung im Vergleich zu den modernen integrierten Zirkulatoren. Der Rest des Front-Ends wird ebenfalls mit dedizierten Testmultiplexern, einem rauscharmen Verstärker und einem Oszillator erforscht, die schließlich in einem einzigen vollintegrierten rauscharmen Empfänger mit Frequenzsynthesizer zusammengeführt werden, der bei 3.5 K für das skalierbare gemultiplexte Auslesen von Silizium-Qubits arbeitet.

Die in dieser Arbeit vorgestellte Plattform trägt, über verschiedene Temperaturbereiche, alle Eigenschaften, die für zukünftige skalierbare Silizium-Quantencomputerplattformen erforderlich sind und könnte daher deren Kern bilden.

**Schlüsselwörter:** Quantencomputer, Quantenprozessor, Spin-Qubit, Quantenpunkt, Skalierbarkeit, kryogene Charakterisierung, Modellierung, Kryo-CMOS, integrierte Quantenschaltung, Hochfrequenz integrierte Schaltung, Gate-basierte Reflektometrie, Multiplexing, Zirkulator, rauscharmer Verstärker, rauscharmer Empfänger.

# Contents

| Ac  | know                                          | ledgements                                                                                                                                                |                                          |

|-----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Ab  | stract                                        | : (English/Italiano/Français/Deutsch)                                                                                                                     | `                                        |

| Со  | ntent                                         | s                                                                                                                                                         | xii                                      |

| Lis | t of F                                        | igures                                                                                                                                                    | xvi                                      |

| Lis | t of Ta                                       | ables                                                                                                                                                     | xxv                                      |

| Lis | t of A                                        | cronyms                                                                                                                                                   | xxvi                                     |

| Lis | t of S                                        | ymbols                                                                                                                                                    | ххх                                      |

| 1   | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | Thesis organization                                                                                                                                       | 1<br>3<br>5<br>9<br>12<br>13<br>14<br>15 |

| 2   |                                               | ntum devices in standard CMOS Introduction Devices and experimental setup Quantum dots in standard bulk MOSFETs Quantum dot circuit parameters Conclusion | 19<br>19<br>20<br>21<br>23<br>24         |

| 3   | 3.1<br>3.2                                    | OS transistors at cryogenic and deep-cryogenic temperatures Introduction MOSFETs at deep-cryogenic temperatures 3.2.1 Experimental setup                  | 25<br>25<br>26<br>26                     |

xiii

#### Contents

|    |                     | 3.2.2 Deep-cryogenic measurements                                   | 26              |

|----|---------------------|---------------------------------------------------------------------|-----------------|

|    |                     | 3.2.3 Impact on base temperature circuit design                     | 27              |

|    | 3.3                 | MOSFETs at cryogenic temperatures                                   | 27              |

|    |                     | 3.3.1 Measurement setup                                             | 28              |

|    |                     | 3.3.2 DC characterization of transistor parameters                  | 28              |

|    |                     | 3.3.3 Analog/RF circuit design parameters                           | 30              |

|    |                     | 3.3.4 Compact modeling with simplified EKV model                    | 32              |

|    | 3.4                 | Conclusion                                                          | 33              |

| 4  | _                   | rated passives at cryogenic temperatures                            | 35              |

|    | 4.1                 | Introduction                                                        | 35              |

|    | 4.2                 | Test structures and measurement setup                               | 36              |

|    |                     | MoM capacitor                                                       | 37              |

|    | 4.4                 | Transformer                                                         | 39              |

|    |                     | 4.4.1 Lumped-element model                                          | 40              |

|    | 4.5                 | 4.4.2 EM model                                                      | 42              |

|    | 4.5                 | Impact on RFICs                                                     | 43              |

|    | 4.6                 | Conclusion                                                          | 44              |

| II | Cryog               | genic CMOS circuits                                                 | 47              |

| 5  | A qua               | antum-classical cryo-CMOS readout matrix                            | 49              |

|    | 5.1                 | Introduction                                                        | 49              |

|    | 5.2                 | A fully-integrated DRAM-like readout matrix architecture            | 51              |

|    | 5.3                 | A quantum-classical integrated circuit in CMOS                      | 51              |

|    | 5.4                 | Time-domain measurements                                            | 52              |

|    | 5.5                 | Radio-frequency characterization                                    | 54              |

|    | 5.6                 | Gate-based dispersive readout                                       | 55              |

|    | 5.7                 | Time-multiplexed readout                                            | 57              |

|    | 5.8                 | Frequency-multiplexed readout                                       | 58              |

|    | 5.9                 | Time- and frequency-multiplexed readout                             | 60              |

|    | 5.10                | Conclusion                                                          | 61              |

| 6  |                     | frequency cryogenic CMOS multiplexers                               | 63              |

|    | 6.1                 | Introduction                                                        | 63              |

|    | 6.2                 | Specifications                                                      | 64              |

|    |                     | Circuit design                                                      | 65              |

|    |                     | Test and measurement                                                | 66              |

|    | 6.5                 | Conclusion                                                          | 67              |

| 7  | <b>A</b> cry<br>7.1 | ogenic CMOS radio-frequency circulator Introduction                 | <b>69</b><br>69 |

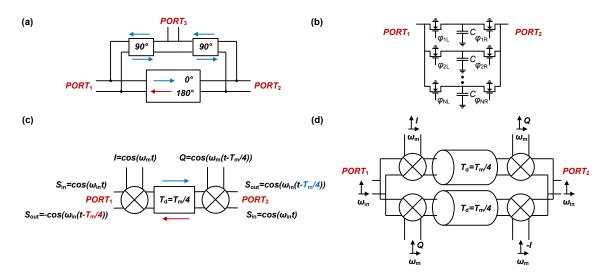

|    | 7.1                 | Wideband low-power staggered commutation circulators                | 71              |

|    | 7.4                 | 7.2.1 <i>N</i> -path filter circulators                             | 71              |

|    |                     | 7.2.1 N-path filter circulators 7.2.2 Broadband gyrator circulators | 72              |

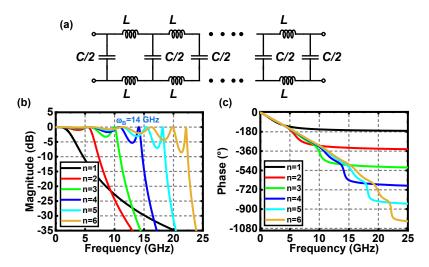

|    |                     | 7.2.3 All-pass filter circulators                                   | 73              |

|    |                     | riero (ili pussi ilitor circulaturs                                 |                 |

|      |        |                                                                     | Contents |

|------|--------|---------------------------------------------------------------------|----------|

|      |        |                                                                     |          |

|      | 7.3    | Circuit design and implementation                                   | 81       |

|      | 7.4    | Cryogenic temperature design and modeling                           | 84       |

|      | 7.5    | Measurements                                                        | 85       |

|      |        | 7.5.1 DC measurements                                               | 85       |

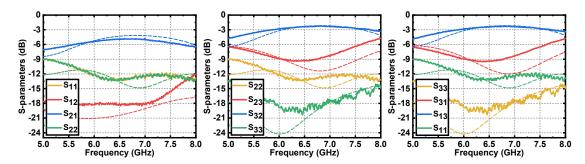

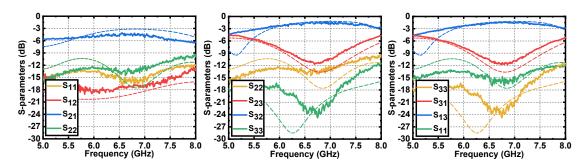

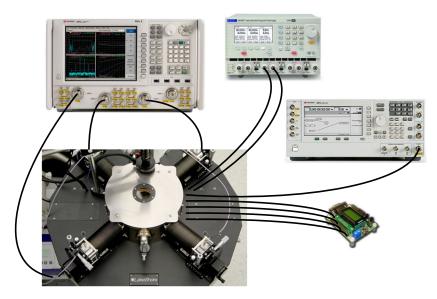

|      |        | 7.5.2 S-parameter measurements                                      | 86       |

|      |        | 7.5.3 Noise measurements                                            | 87       |

|      |        | 7.5.4 Linearity measurements                                        | 89       |

|      | 7.6    | Discussion                                                          | 89       |

|      | /./    | Conclusion                                                          | 90       |

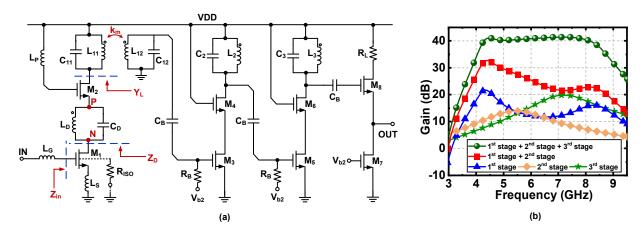

| 8    | •      | -CMOS RF front-end circuits                                         | 93       |

|      |        | Introduction                                                        | 93       |

|      | 8.2    | , 0                                                                 | 98       |

|      |        | 8.2.1 Specifications                                                | 98       |

|      |        | 8.2.2 Cryogenic amplifiers                                          | 100      |

|      |        | 8.2.3 Circuit analysis of a wideband <i>LC</i> -loaded RF amplifier | 100      |

|      |        | 8.2.4 Cryogenic design and implementation                           | 108      |

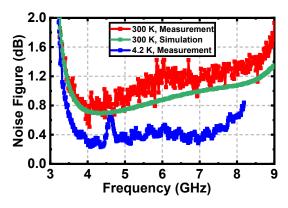

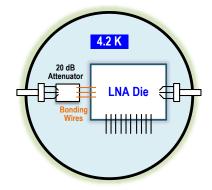

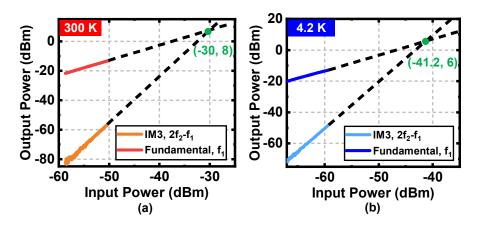

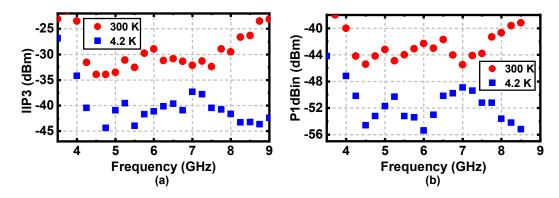

|      |        | 8.2.5 Measurement results                                           | 112      |

|      |        | 8.2.6 Discussion                                                    | 114      |

|      | 8.3    | A cryogenic CMOS LC voltage-controlled oscillator                   | 115      |

|      |        | 8.3.1 Specifications                                                | 115      |

|      |        | 8.3.2 Cryogenic oscillators                                         | 116      |

|      |        | 8.3.3 Circuit design and implementation                             | 117      |

|      |        | 8.3.4 Measurements                                                  | 118      |

|      |        | 8.3.5 Discussion                                                    | 120      |

|      | 8.4    | Conclusion                                                          | 120      |

| 9    | A crv  | vo-CMOS I/Q low-noise low-IF down-conversion RF receiver            | 123      |

|      | 9.1    |                                                                     | 123      |

|      | 9.2    | Circuit design and architecture                                     | 124      |

|      | 9.3    | Measurements                                                        | 128      |

|      | 9.4    | Conclusion                                                          | 131      |

|      |        |                                                                     |          |

| 10   | Conc   | clusions                                                            | 133      |

|      | 10.1   | Outlook                                                             | 133      |

|      | 10.2   | Thesis outcome                                                      | 134      |

|      | 10.3   | Open problems                                                       | 136      |

|      | 10.4   | Future work                                                         | 137      |

| Bib  | liogra | phy                                                                 | 139      |

| List | of Pu  | ublications                                                         | 155      |

| Chi  | p Gall | ery                                                                 | 157      |

| Cııı | riculu | ım Vitae                                                            | 159      |

# List of Figures

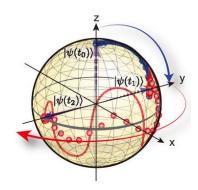

| Figure    | 1.1 | Graphical representation of the wavefunction in the Bloch sphere [4].                                                                                                                                                                                                                                                                                                                                                                                                                           | 2   |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

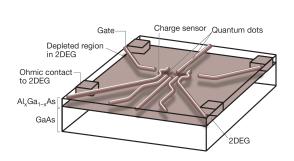

| Figure    | 1.2 | Realization of a quantum dot by means of a 2D electron gas [7].                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4   |

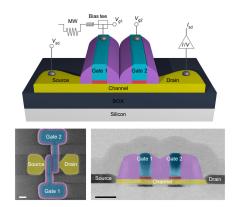

| Figure    |     | A CMOS compatible qubit [11].                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4   |

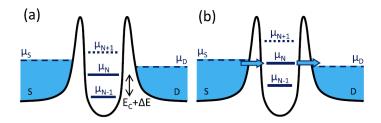

| Figure    |     | Electrochemical potential levels in a quantum dot (a) when transport is prohibited and (b) when transport is allowed [9].                                                                                                                                                                                                                                                                                                                                                                       | 5   |

| Figure    | 1.5 | (a) Conductance peaks and (b) Coulomb diamonds in a charge stability diagram for a quantum dot [9].                                                                                                                                                                                                                                                                                                                                                                                             | 6   |

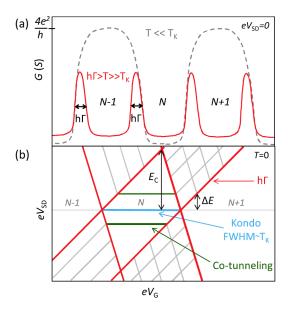

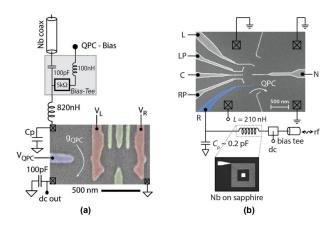

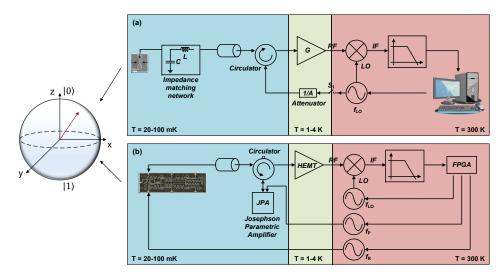

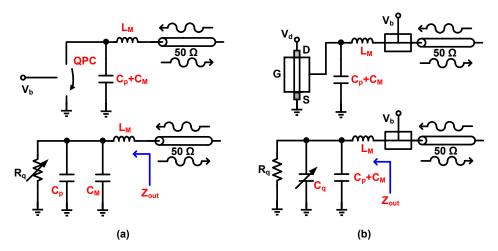

| Figure    | 1.6 | Two techniques for readout of semiconductor quantum dots: (a) RF reflectometry [15], (b) dispersive gate sensing [16].                                                                                                                                                                                                                                                                                                                                                                          | 7   |

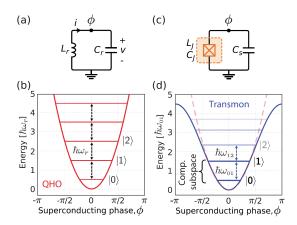

| Figure    |     | (a) Harmonic <i>LC</i> oscillator and (b) its energy levels. (c) Anharmonic <i>LC</i> oscillator and (d) its respective energy levels [19].                                                                                                                                                                                                                                                                                                                                                     | 8   |

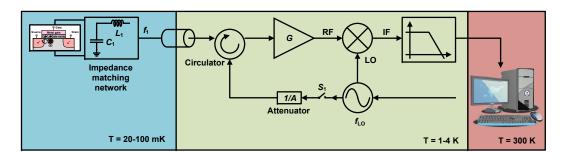

| Figure    | 1.8 | Current implementations of typical qubit readout schemes for (a) spin qubit processors [18] and (b) superconducting qubit processors [20]. The color coding represents temperature variation along the chain, from the base temperature of dilution refrigerators (20-100 mK) in                                                                                                                                                                                                                |     |

| <b>-:</b> | 4.0 | blue, to room temperature (300 K) in red.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10  |

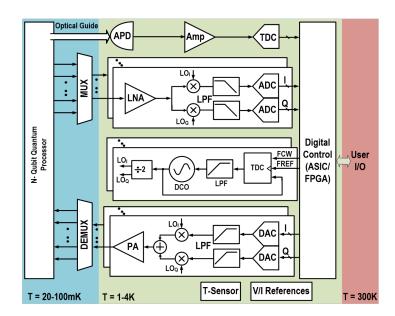

| Figure    | 1.9 | Vision for a fully-integrated cryogenic CMOS RF transceiver, showing the readout and control system architecture for multi-qubit proces-                                                                                                                                                                                                                                                                                                                                                        | 4.4 |

|           |     | sors [24].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11  |

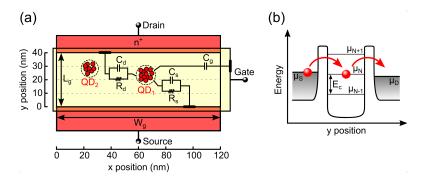

| Figure    | 2.1 | (a) Top view of the MOSFET operated as a quantum device. Red spheres represent charge carriers. (b) Schematic of energy as a function of channel position in the $y$ -axis in (a). $\mu_s$ , $\mu_d$ and $\mu_N$ are the electrochemical potentials of Source, Drain, and QD, respectively. When $V_{\rm ds} = (\mu_{\rm s} - \mu_{\rm d})/e$ is small, $I_{\rm ds}$ only occurs when $\mu_{\rm N}$ is in alignment with the bias window between $\mu_{\rm s}$ and $\mu_{\rm d}$ , meaning that |     |

|           |     | electrons can move from Source to QD to Drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20  |

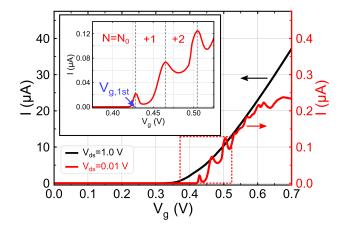

| Figure    | 2.2 | Drain current $I_{ds}$ as a function of gate voltage $V_g$ at 50 mK in the quantum regime. The inset shows a zoom of the red-dotted region,                                                                                                                                                                                                                                                                                                                                                     | 21  |

| Гістис    | 2 2 | while <i>N</i> indicates the number of electrons.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21  |

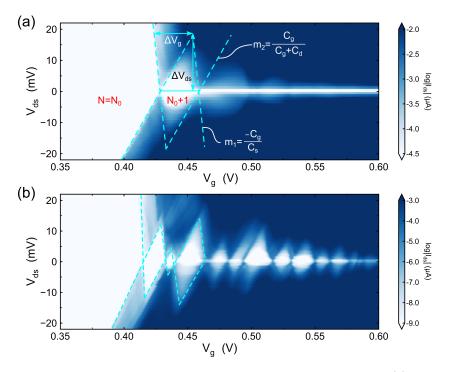

| Figure    |     | Charge stability diagrams as a function of $V_{\rm ds}$ and $V_{\rm g}$ of devices (a) T01 and (b) T07. Measurements are carried out at 50 mK.                                                                                                                                                                                                                                                                                                                                                  | 22  |

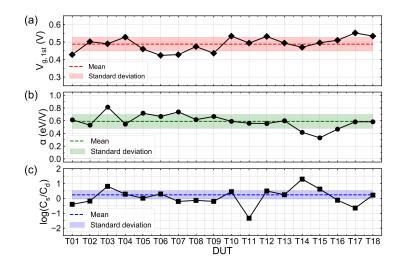

| Figure    | 2.4 | Summary of (a) $V_{g,1st}$ , (b) $\alpha$ and (c) $C_s/C_d$ of all measured DUTs. The dashed lines are mean values, and the shaded areas indicate (mean value $\pm$ standard deviation).                                                                                                                                                                                                                                                                                                        | 23  |

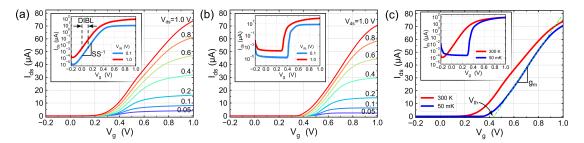

| Figure 3.1 Figure 3.2 | Drain current $I_{\rm ds}$ as a function of $V_{\rm g}$ at various $V_{\rm ds}$ (a) at 300 K and (b) at 50 mK. (c) $I_{\rm ds}$ as a function of $V_{\rm g}$ at 300 K and at 50 mK with $V_{\rm ds}$ = 1.0 V. The insets report data in logarithmic scale. DIBL represents drain-induced barrier lowering, SS is the subthreshold swing, $V_{\rm th}$ is the threshold voltage, and $g_{\rm m}$ is the transconductance. Cryogenic measurements on a 28-nm bulk CMOS technology. (a) Au-                                                                                                                                                                                                                                                                                                                                                                    | 26 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

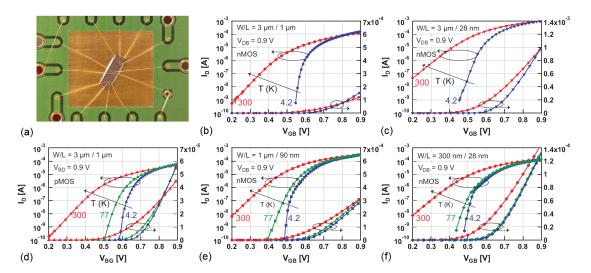

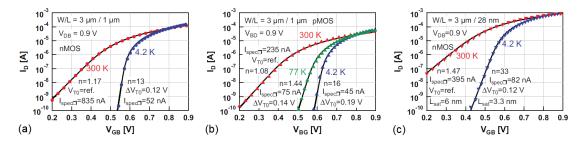

| rigare 0.2            | wire bonded sample chip glued to a standard PCB, before covering with glob-top. (b)-(f) Measured transfer characteristics at 300 K, 77 K and 4.2 K in saturation ( $V_{\rm DB} = 0.9  \rm V$ ). In all measurements the gate voltage is referred to the bulk ( $V_{\rm GB}$ ) and swept from 0.2 V to 0.9 V with a step size of 1 mV. Marker symbols refer to the device type (as shown in Table 3.2). Colors indicate the temperature: red is room temperature (300 K), green is liquid nitrogen temperature (77 K) and blue is liquid helium temperature (4.2 K).                                                                                                                                                                                                                                                                                         | 29 |

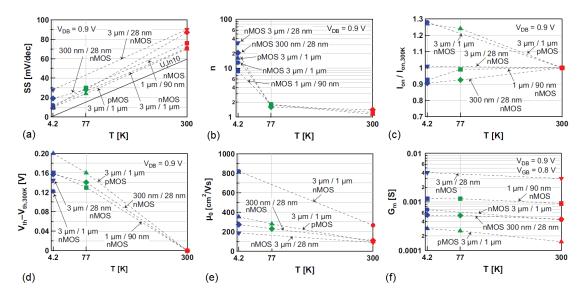

| Figure 3.3            | Extraction of the fundamental physical and technological parameters at 300 K, 77 K and 4.2 K. (a) Subthreshold swing versus temperature. The results at 4.2 K show a strong deviation from the theoretical trend ( $U_T \ln 10$ ), which is expressed by an increase in the slope factor $n$ . (b) Slope factor versus temperature. (c) ON-state current normalized to room temperature values. (d) Shift in threshold voltage at 77 K and 4.2 K with respect to room temperature, extracted from the transconductance in saturation ( $V_{DB} = 0.9  \text{V}$ ) at $V_{GB} = 0.9  \text{V}$ . (e) Low-field mobility versus temperature, extracted using the Y-function method [75]. (f) Transconductance in saturation versus temperature.                                                                                                               | 30 |

| Figure 3.4            | Impact of cryogenic temperatures on analog design parameters. (a) Slope factor versus drain current at 300 K and 4.2 K for nMOS with $W_{\rm g}/L_{\rm g}=3\mu{\rm m}/28{\rm nm}$ . (b) Normalized transconductance efficiency versus inversion coefficient for nMOS with $W_{\rm g}/L_{\rm g}=3\mu{\rm m}/28{\rm nm}$ , showing a decreased velocity saturation effect at 4.2 K. Solid lines: model. (c) Normalized source transconductance versus inversion coefficient. Solid lines: model. (d) Measured output characteristics for long channel nMOS and pMOS with $W_{\rm g}/L_{\rm g}=3\mu{\rm m}/1\mu{\rm m}$ with extracted values for the output conductance and the Early voltage $V_{\rm A}$ . (e) Measured output characteristics for short channel nMOS with $W_{\rm g}/L_{\rm g}=300{\rm nm}/28{\rm nm}$ with extracted values for the output | 30 |

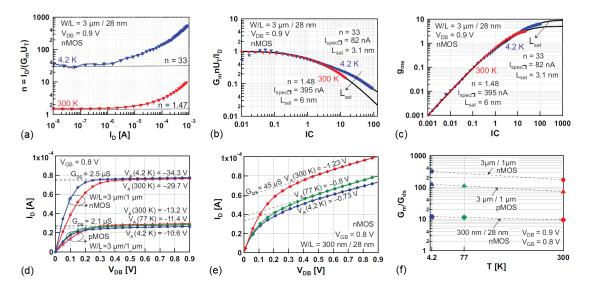

| Figure 3.5            | conductance and $V_A$ . (f) Intrinsic gain at 300 K, 77 K and 4.2 K. Transfer characteristics: measured (markers) and modeled (solid lines) with the simplified EKV long/short channel model for (a) nMOS with $W_g/L_g=3~\mu m/1~\mu m$ at 300 K and 4.2 K, (b) pMOS with $W_g/L_g=3~\mu m/1~\mu m$ at 300 K, 77 K and 4.2 K and (c) nMOS with $W_g/L_g=3~\mu m/28$ nm at 300 K and 4.2 K. For each curve, the model parameters are shown.                                                                                                                                                                                                                                                                                                                                                                                                                 | 31 |

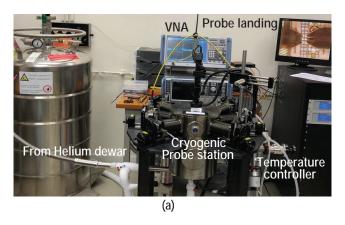

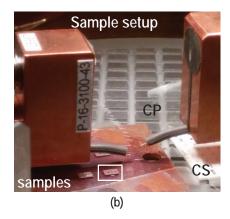

| Figure 4.1            | (a) Cryogenic probe station measurement setup. (b) Sample setup inside the 4.2 K chamber.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |

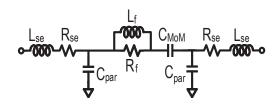

| Figure 4.2            | Lumped-element model of MoM capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

xviii

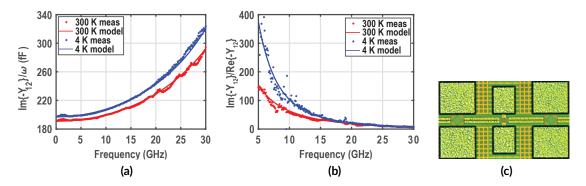

| Figure | 4.3  | Extraction of MoM (a) capacitance and (b) quality factor. (c) MoM micrograph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

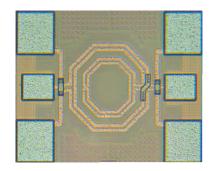

| Figure | 4.4  | Transformer micrograph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39 |

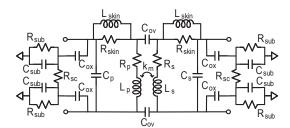

| Figure |      | Transformer model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39 |

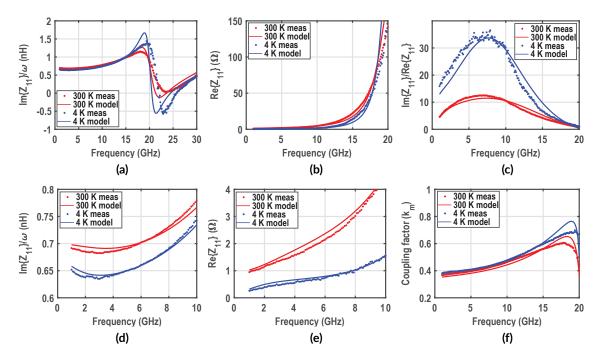

| Figure |      | Extraction of (a) inductance, (b) series resistance, (c) quality factor, (d) inductance (zoomed in), (e) series resistance (zoomed in), (f) coupling factor, from measurement and lumped-element model of the transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40 |

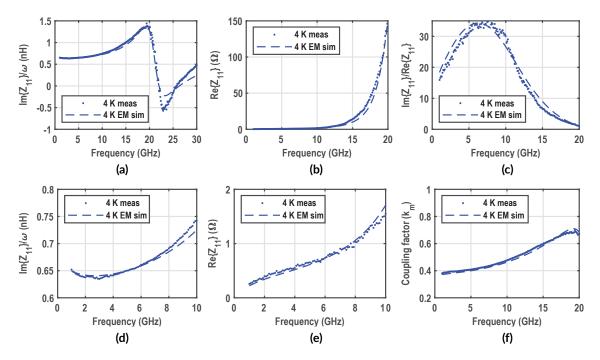

| Figure | 4.7  | Extraction of (a) inductance, (b) series resistance, (c) quality factor, (d) inductance (zoomed in), (e) series resistance (zoomed in), (f) coupling factor, from measurement and EM simulation of the transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

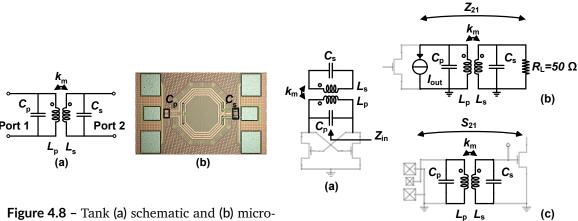

| Figure | 4.8  | Tank (a) schematic and (b) micrograph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

| Figure | 4.9  | Schematic of transformer-based resonator used in (a) oscillator, (b) power amplifier, and (c) low-noise amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

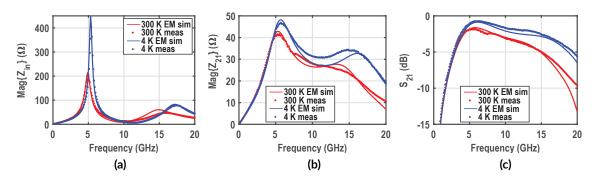

| Figure | 4.10 | Tank (a) input impedance $(Z_{in})$ , (b) trans-impedance $(Z_{21})$ and (c) insertion loss $(S_{21})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |

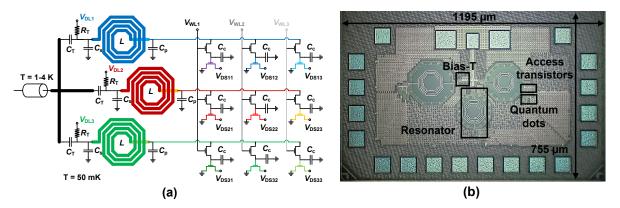

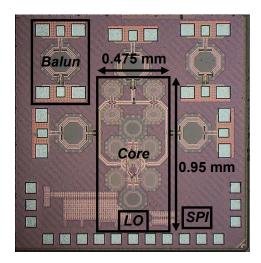

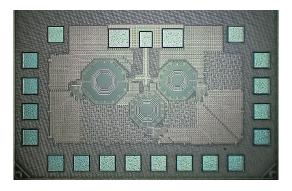

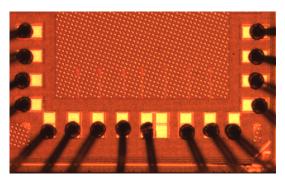

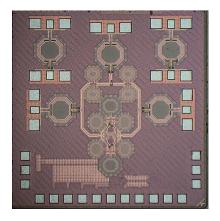

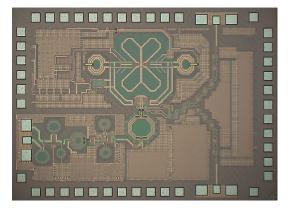

| Figure | 5.1  | (a) Schematic and (b) chip microphotograph of the quantum-classical readout interface, showing the bias-Ts, integrated <i>LC</i> resonators, access transistors and quantum dots.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

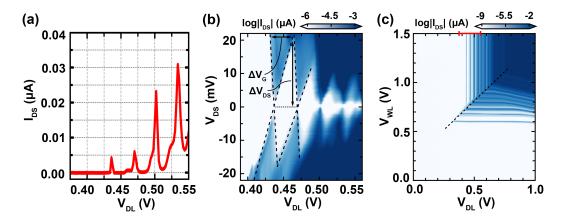

| Figure | 5.2  | Evidence of quantum phenomena at 50 mK. (a) DC transport current measurement for the individual quantum dot device $QD_{33}$ on chip, acquired through the access transistor in the active state, with $V_{WL} = 1.5 \text{ V}$ , $V_{DL} \simeq V_G$ and $V_{DS} = 10 \text{ mV}$ . (b) Coulomb diamonds derived from transport measurements in DC for the quantum dot device $QD_{33}$ . (c) Charge stability diagram $V_{WL}$ - $V_{DL}$ of the quantum dot device-access transistor cell $QD_{33}$ -FET <sub>33</sub> , with $V_{DS} = 10 \text{ mV}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

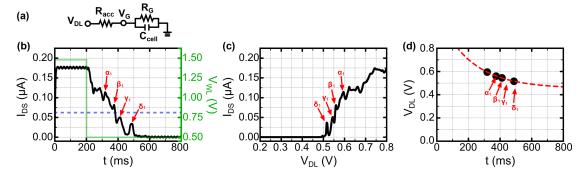

| Figure | 5.3  | Retention time experiment. (a) Equivalent circuit of a single cell, where $V_{\rm DL}$ is the applied data-line voltage, $V_{\rm G}$ is the effective gate voltage of the quantum device, $R_{\rm acc}$ is the channel resistance of the access FET, $R_{\rm G}$ is the gate leakage resistance of the quantum device, and $C_{\rm cell}$ is the equivalent capacitance at the gate of the quantum device. (b) Drain current ( $I_{\rm DS}$ ) as a function of time ( $t$ ) (black line) with the application of $V_{\rm WL,High}=1.49\rm V$ for t=0 to 200 ms and $V_{\rm WL,Low}=0.5\rm V$ afterwards (green line), and a constant $V_{\rm DL}=0.8\rm V$ (blue dashed line). (c) $I_{\rm DS}$ as a function of $V_{\rm DL}$ at $V_{\rm WL}=1.49\rm V$ . (d) Locations of Coulomb blockade peaks $\alpha_1$ , $\beta_1$ , $\gamma_1$ , and $\delta_1$ (see (b)) in time, as a function of the corresponding Coulomb peaks in voltage in (c). The red dashed line is a fit. Measurements are performed at 50 mK on quantum device QD <sub>23</sub> . | 53 |

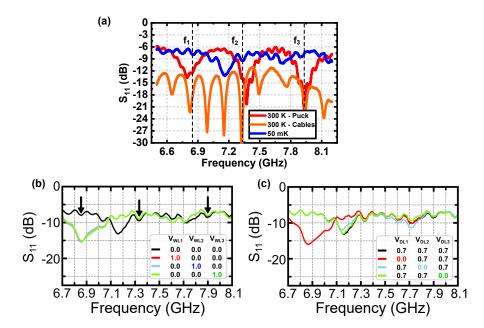

| Figure | 5.4  | (a) Frequency spectrum at 300 K directly at the sample puck and including all the cables and at 50 mK including all the cables. Spectrum at 50 mK for (b) each word line voltage ON, one after the other, with data line voltage $V_{\rm DLi} = 0  \rm V$ , (c) each data line voltage OFF, one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|        |      | after the other, with word line voltage $V_{WLj} = 1.0 \text{V}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54 |

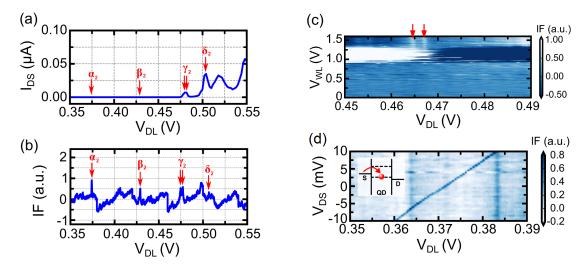

| Figure 5.5 | (a) DC transport measurement: $I_{\rm DS}$ as a function of $V_{\rm DL}$ . (b) Gatebased readout: reflectometry signal as a function of $V_{\rm DL}$ at $V_{\rm WL}=1.5\rm V$ and $V_{\rm DS}=0\rm V$ . (c) Gate-based readout: reflectometry signal as a function of $V_{\rm WL}$ and $V_{\rm DL}$ at $V_{\rm DS}=0\rm V$ . (d) Gate-based readout: reflectometry signal as a function of $V_{\rm DS}$ and $V_{\rm DL}$ at $V_{\rm WL}=1.5\rm V$ . Inset: energy diagram of Source-QD-Drain. The measurements are performed at 50 mK on quantum device QD <sub>13</sub> .                                                                                                                                                                                                                                                  | 56 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

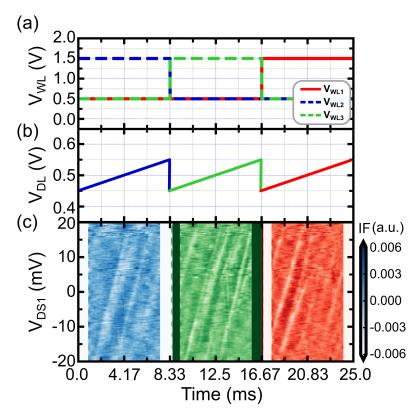

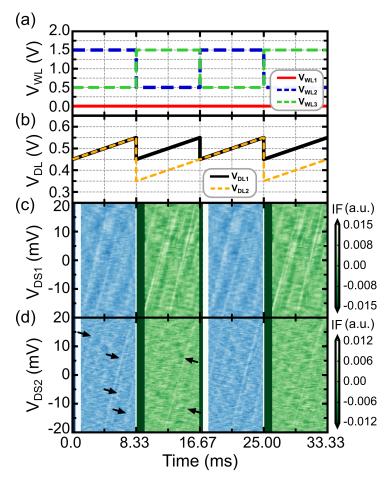

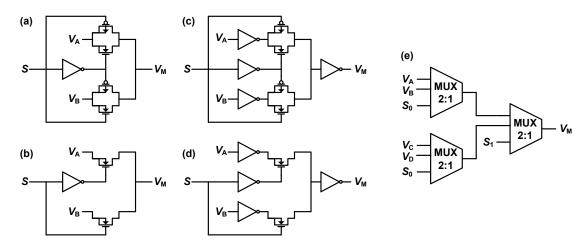

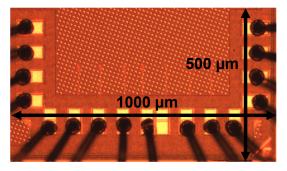

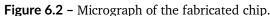

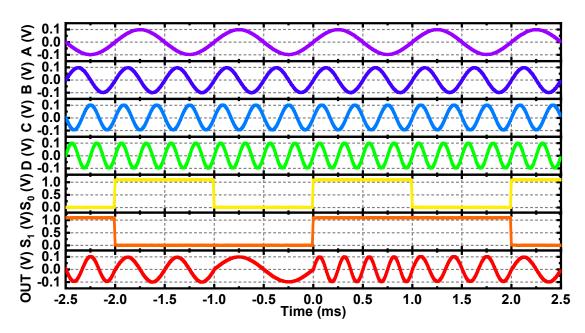

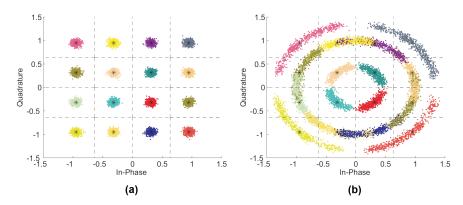

| Figure 5.6 | Sequence of signals to perform time-domain multiplexing reflectometry sensing on $\mathrm{QD}_{12}$ , $\mathrm{QD}_{13}$ and $\mathrm{QD}_{11}$ . While (a) $V_{\mathrm{WL}2}$ (in blue), $V_{\mathrm{WL}3}$ (in green) and $V_{\mathrm{WL}1}$ (in red) follow a square wave between 1.5 V and 0.5 V, (b) $V_{\mathrm{DL}1}$ follows a synchronized triangular wave and ramps up. (c) Stability diagrams for quantum devices $\mathrm{QD}_{12}$ (in blue), $\mathrm{QD}_{13}$ (in green) and $\mathrm{QD}_{11}$ (in red). The shades indicate the location of Coulomb peaks. Measurements are performed at 50 mK.                                                                                                                                                                                                           | 57 |

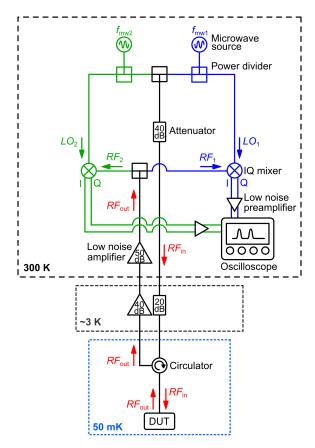

| Figure 5.7 | Experimental measurement setup for the (time- and) frequency-multiplexed gate-based readout experiment. The DUT is placed at 50 mK on the sample stage of the dilution fridge. A cryogenic circulator is placed at the mixing chamber plate and a low-noise amplifier and attenuators are placed at intermediate cryogenic temperatures ( $\sim$ 3 K). At room temperature, two microwave signal sources are power-combined to generate two multiplexed single-tone probing signals $f_{\rm mw1}$ and $f_{\rm mw2}$ , and two I/Q mixers are used to demodulate the reflected signals RF <sub>1</sub> and RF <sub>2</sub> at the two frequencies, by using the microwaves sources as respective local oscillators LO <sub>1</sub> and LO <sub>2</sub> . An oscilloscope acquires the I/Q outputs for each of the two tones. | 59 |

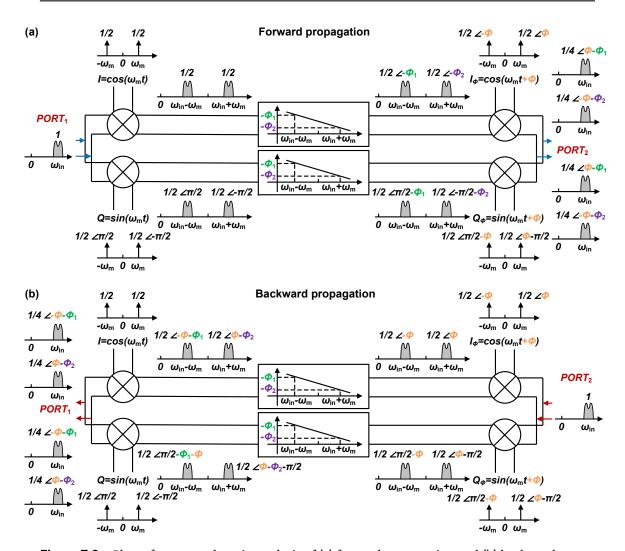

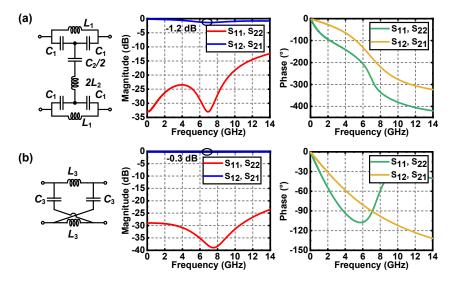

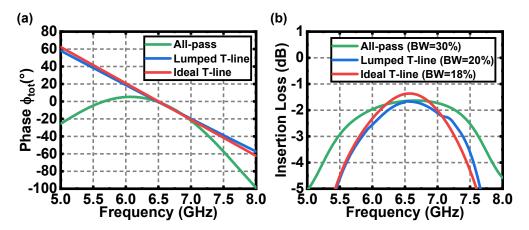

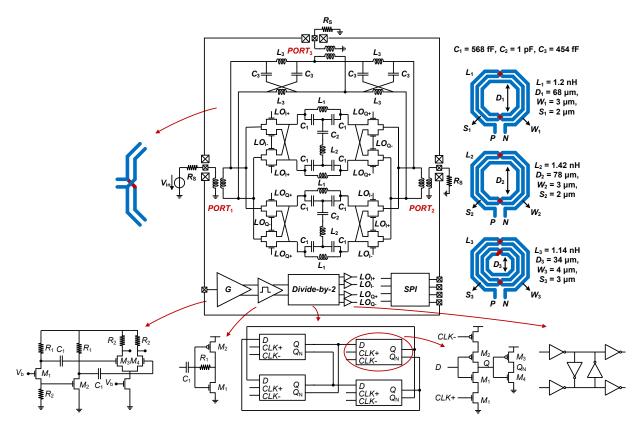

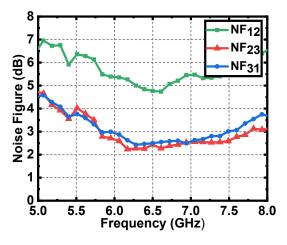

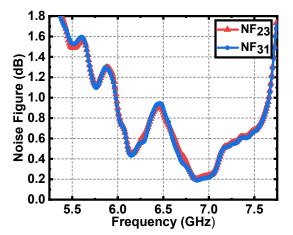

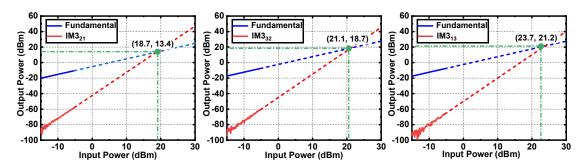

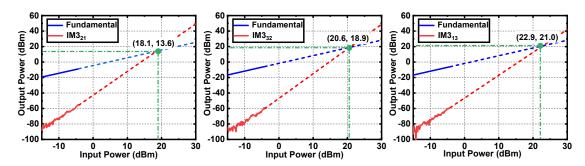

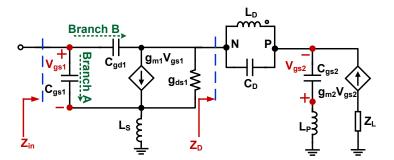

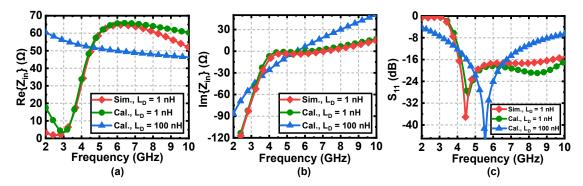

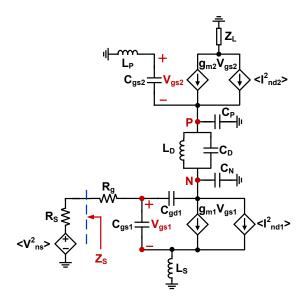

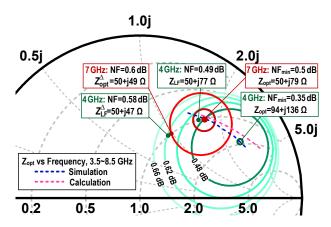

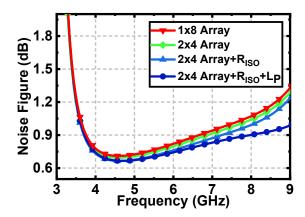

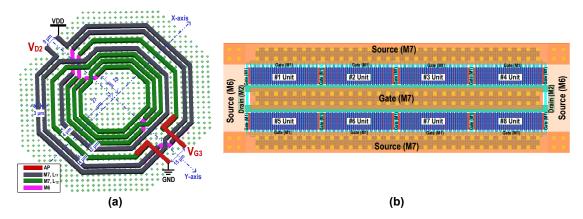

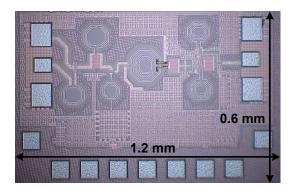

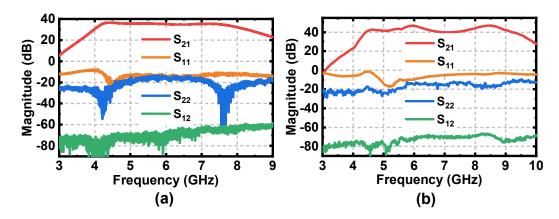

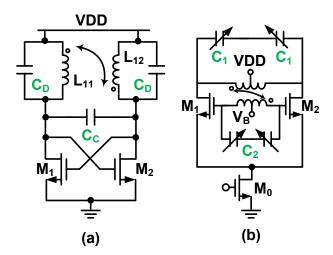

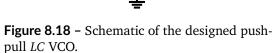

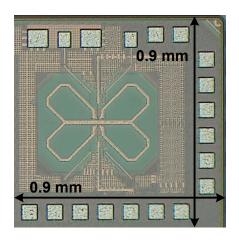

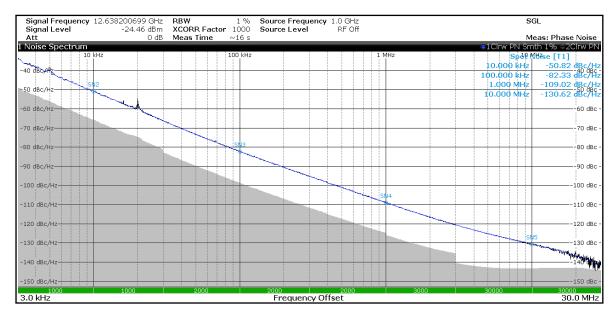

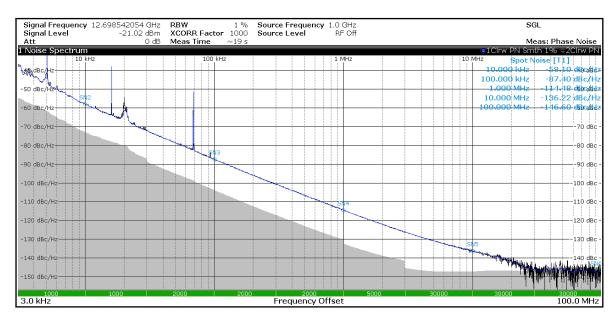

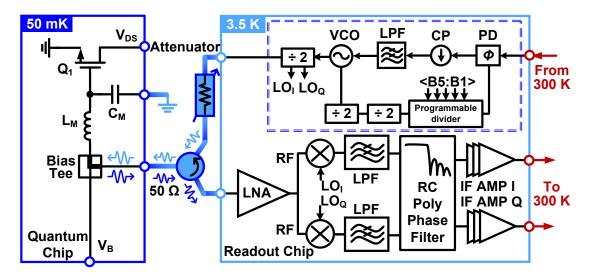

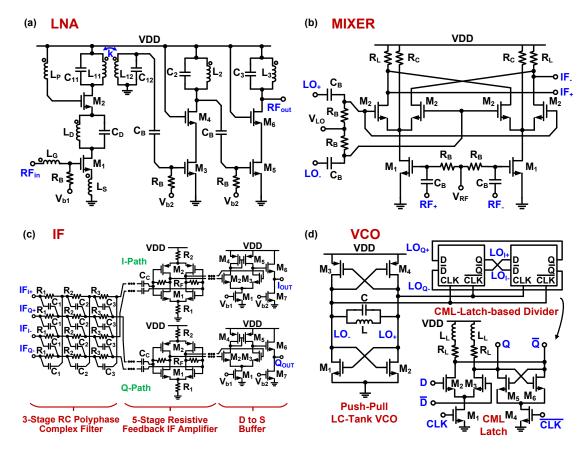

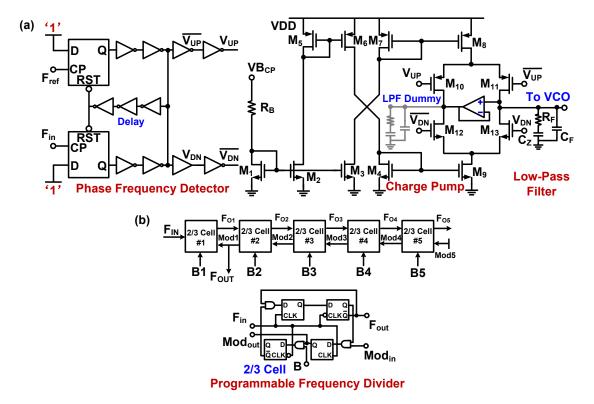

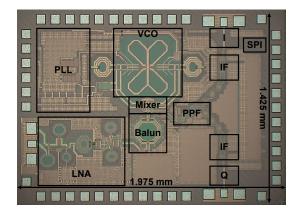

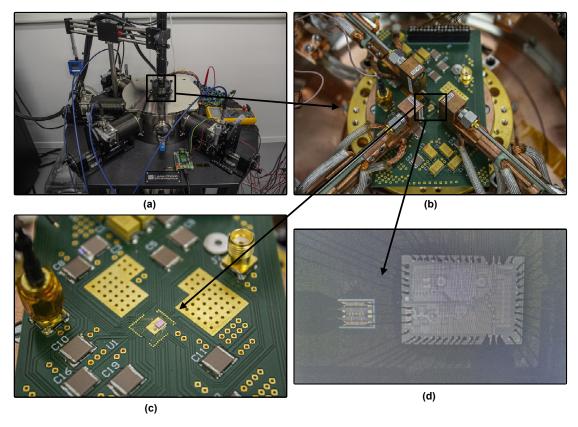

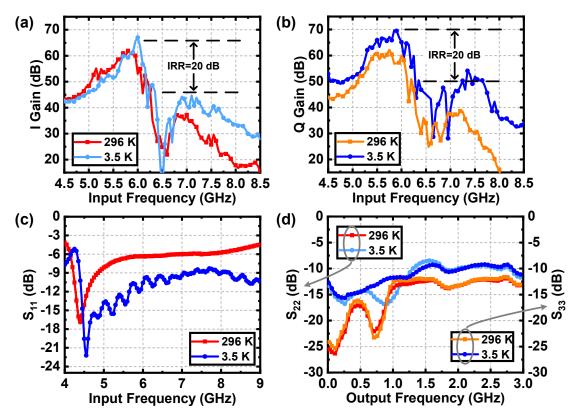

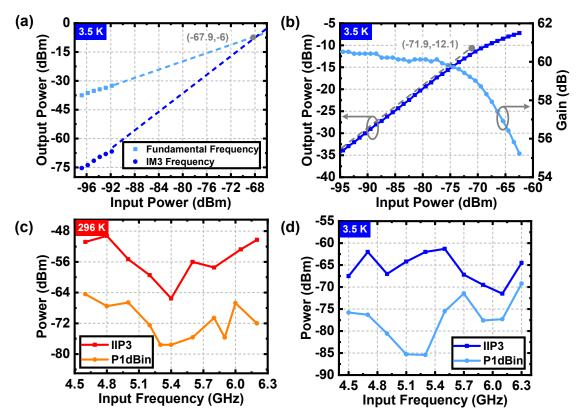

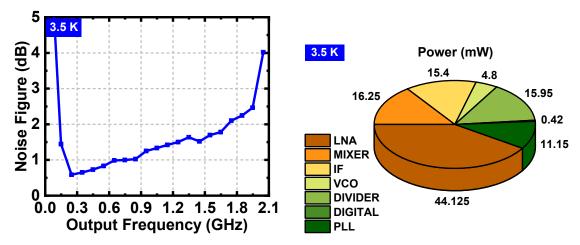

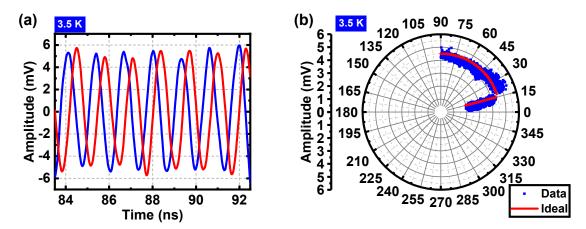

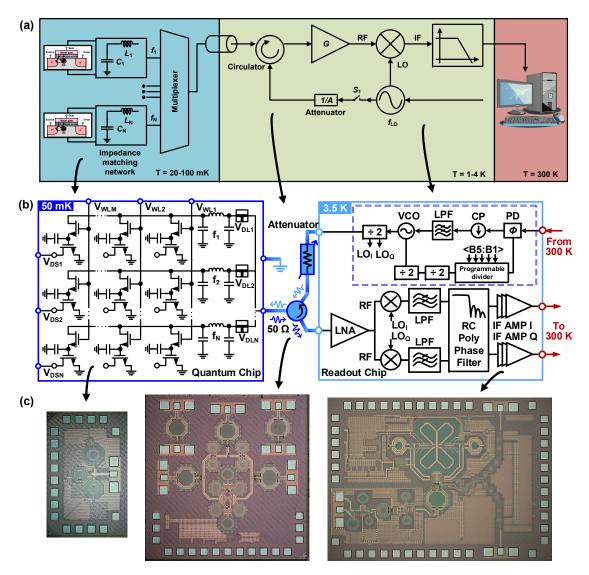

| Figure 5.8 | Sequence of signals to perform time- and frequency-multiplexing reflectometry using the $2 \times 2$ sub-matrix $QD_{12}$ , $QD_{13}$ , $QD_{22}$ and $QD_{23}$ . While (a) $V_{WL2}$ (in blue) and $V_{WL3}$ (in green) follow a square wave between $1.5\mathrm{V}$ and $0.5\mathrm{V}$ , $V_{WL1}$ (in red) is disabled and (b) $V_{DL1}$ and $V_{DL2}$ follow a synchronized triangular wave and ramp up. (c) Stability diagrams for quantum devices $QD_{12}$ (in blue) and $QD_{13}$ (in green) addressed through Resonator 1. (d) Stability diagrams for quantum devices $QD_{22}$ (in blue) and $QD_{23}$ (in green) addressed through Resonator 2. The measurements are performed at $50\mathrm{mK}$ .                                                                                                             | 60 |