# Adaptive Body Biasing in Strong Body Factor Technologies

Présentée le 29 janvier 2021

Faculté des sciences et techniques de l'ingénieur Laboratoire de circuits pour télécommunications Programme doctoral en génie électrique

pour l'obtention du grade de Docteur ès Sciences

par

### **Thomas Christoph MÜLLER**

Acceptée sur proposition du jury

Prof. S. Carrara, président du jury

Prof. A. P. Burg, Dr M. Pons Solé, directeurs de thèse

Prof. J. Rodrigues, rapporteur

Prof. L. Koskinen, rapporteur

Prof. M. Shoaran, rapporteuse

## Acknowledgements

I am very grateful to my thesis supervisor Prof. Andreas Burg for giving me the opportunity to do my PhD at the Telecommunication Circuits Laboratory at EPFL. The countless technical discussions pushed me forward and his valuable comments sharpened this work which would not exist in this form otherwise. Thanks for the continuous unconditional support and guidance as well as for providing such an incredible interdisciplinary lab environment. Further, I would like to express my gratitude to my thesis co-director at CSEM, Dr. Marc Pons Solé: thanks for the dedication in supporting me throughout these years and for all the invaluable advice.

I would like to thank the committee of my thesis defense: Prof. S. Carrara of the Integrated Circuits Laboratory at EPFL who acted as the president of the jury and Prof. Mahsa Shoran from the Integrated Neurotechnologies Laboratory of EPFL who acted as the internal expert. In addition I would like to to thank the two external examiners: Prof. Joachim Rodrigues from the Integrated Electronic Systems group of Lund University and Prof. Lauri Koskinen from the Department of Future Technologies of Turku University.

Further, I would like to express my gratefulness to all my colleagues at CSEM I worked closely with: my supervisor Stéphane Emery, as well as Daniel Séverac, David Ruffieux, Erfan Azarkhish, Ernesto Pérez Serna, Jean-Luc Nagel, Loïc Zahnd, Regis Cattenoz, Stéphane Devise, Themis Mavrogordatos, and Virginie Moser - thanks for all the support and technical discussions. I also would like to thank USJC for providing the funding, silicon, and early technology access for the CSEM project which lead to this thesis.

I wish to show my gratitude to all former and current members of the Telecommunication Circuit Laboritory: Adam Teman, Adrian Schumacher, Alexios Balatsoukas-Stimming, Andrea Bonetti, Andreas Kristensen, Andrew Austin, Christian Senning, Jeremy Constantin, Lorenz Schmid, Matthieu Cotting, Nicholas Preyss, Pascal Giard, Orion Afisiadis, Reza Ghanaatian Jahromi, Robert Giterman, Ricardo Gomez Gomez, Sitian Li, and Shrikanth Ganapathy - without you this time would not have been half as enjoyable and I would not have learned half as much without your incredible talent and knowledge in such diverse fields. A special thanks goes to our secretary Ioanna Paniara for keeping our back free from all the organisational work.

Finally, my family supported and believed in me over all these years of education: I whole-hartedly would like to thank my mother Heike, my father Mathias as well as my brothers Carsten, and Constantin.

Lausanne, December 18, 2020

### **Abstract**

With the advent of intelligent sensor nodes in everyday life, low power aspects of system design become more and more important. Adaptive body biasing is a promising methodology to achieve dynamic adaptation of the tradeoff between performance and energy by shifting the threshold voltage of transistors in a digital design. This approach, in combination with a low supply voltage, provides a strong knob to the designer to rapidly shift the circuits operating point from deep sub threshold operation for slow and low leakage retention, to fast, higher performance operation to for short, but demanding tasks. This thesis concentrates on such designs using the deeply depleted channel technology in which body control is particularly effective.

The first part of this thesis is dedicated to strategies and tools supporting the digital design process of circuits using adaptive body biasing. A methodology to compare a standard cell library characterised in different operating points, defined by supply voltage, process corner, temperature, and bias points is presented first.

Next, we present a methodology to exhaustively and rapidly map out the supply-voltage/bias-voltage design space using a heavily pruned cell library. We extract speed and power of a simple example design across the entire design space and show a methodology to scale the characteristics of the small reference up to a more complex design. In a case study this modelling approach achieves an error of less than 1% on the total power relative to an actual characterisation of the full library at the same design point.

The second part of the thesis analyses three chips implementing different biasing schemes in USJC 55nm DDC. The first two were designed by CSEM with components and measurements contributed from this thesis while the third one was entirely designed for this thesis.

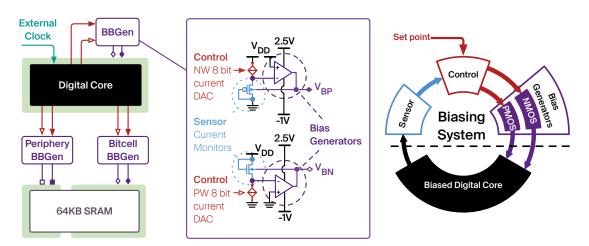

The first chip utilises a biasing scheme based on the first order approximation that the circuit speed is proportional to the on-current which can be driven by PMOS and NMOS transistors. This is implemented using an analog control loop, setting both PMOS and NMOS on-currents equal to a reference current provided by current DAC. The SoC characterisation is presented with the objective of identifying suitable operating modes and bias points, including a reliability and retention analysis of the SRAM. A series of ring oscillators constructed from the most common standard cells has also been integrated and provides measurement support for the first part of the thesis.

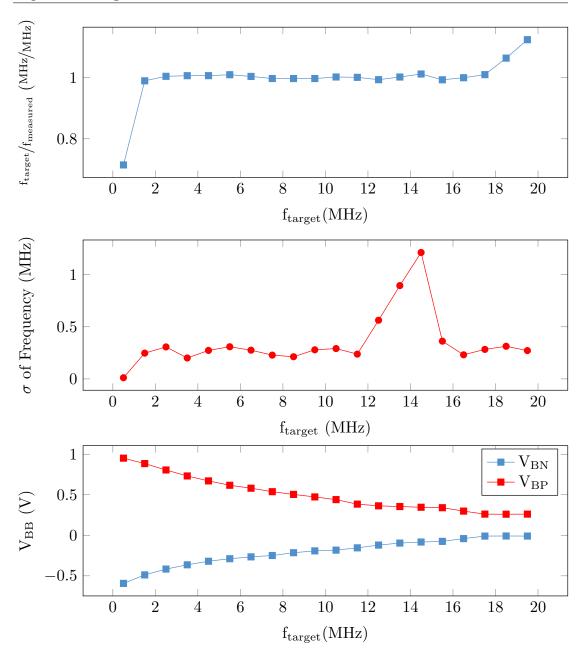

The second chip extends the Calanda biasing scheme with a secondary regulation loop that is based on an FLL, designed in this thesis, in combination with a configurable standard cell based ring oscillator. The user can directly program a target frequency and the biasing system

#### **Abstract**

regulates the current DAC accordingly. We show that this approach effectively overcomes the drawbacks of the current based approach resulting in an effective regulation.

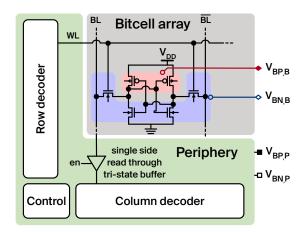

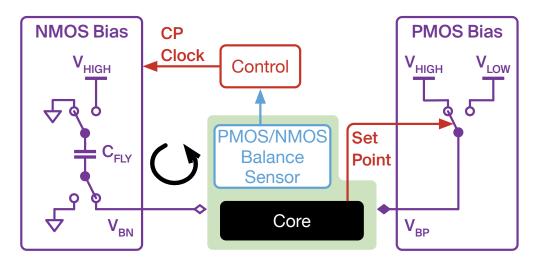

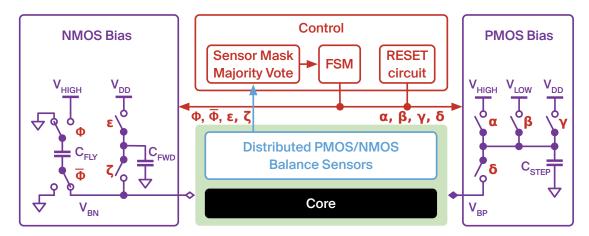

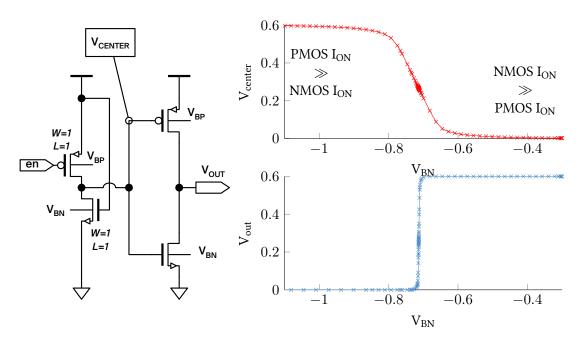

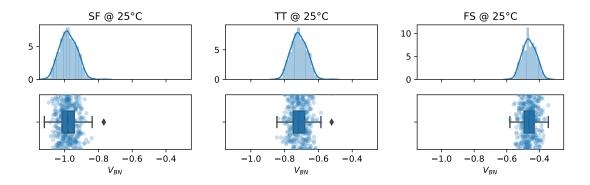

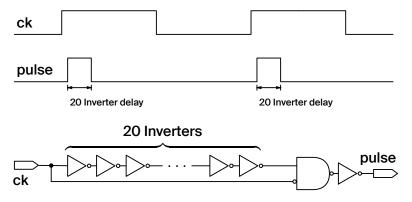

Finally the third chip presents a novel biasing scheme that was designed in this thesis and is tailored toward simplicity. It utilises two constant voltages for the PMOS bias to switch between retention and operation. A charge pump controlled by a standard cell compatible distributed on current balance sensor regulates the NMOS bias such that the on-currents of PMOS and NMOS match. We show that this simple approach, in conjunction with a well chosen operating point, can be efficient across corners.

**Key Words:** Digital VLSI Circuits, Low-Power Design,

Deeply Depleted Channel, Adaptive Body Biasing, PVT Compensation,

Standard Cell Library Analysis, Design Space Exploration, Throughput Scaling, Retention, Bias Generation.

## Zusammenfassung

Mit der Verbreitung von intelligenten Sensor-Knoten im Alltag und den Fortschritten im Feld des maschinellen Lernens wird energiesparendes Systemdesign zunehmend bedeutender. Adaptives Body Biasing ist dabei eine vielversprechende Methode um eine dynamische Anpassung zu erreichen indem die Schwellenspannung der Transistoren im digitalen Design verschoben wird. Dieser Ansatz, zusammen mit einer niedrigen Versorgungsspannung, gibt dem Designer ein mächtiges Werkzeug um den Betriebspunkt schnell von weit unter der Schwellspannung mit niedrigen Leckströmen zu einem Punkt mit höherer Leistung für kurze, aber anspruchsvolle Aufgaben zu verschieben. Diese Arbeit konzentriert sich auf Schaltungen in USJC 55nm DDC wo Body Biasing besonders effektiv ist.

Der erste Teil dieser Arbeit beschäftigt sich mit dem Entwicklungsprozess für digitale Schaltungen unter der Anwendung von Adaptivem Body Biasing. Es wird eine Methode entwickelt um eine Bibliothek von Standardzellen welche unter verschiedenen Betriebspunkten (Temperatur, Versorgungsspannung, Prozess-Corner) charakterisiert wurde gegeneinander zu vergleichen. Als nächstes präsentieren wir eine Methode mit der der Raum der durch die Variation der Bodyund Versorgungsspannung aufgespannt wird unter Verwendung einer stark beschnittenen Zellbibliothek kartiert werden kann. Wir extrahieren mit einem einfachen Refererenzdesign die dynamischen und statischen Ströme über den gesamten Designraum und zeigen eine Methodik zur Skalierung auf ein komplexeres Design. In einer Fallstudie wird einen Fehler von weniger als 1% des Gesamtenergieverbrauchs erreicht.

Der zweite Teil dieser Arbeit beschäftigt sich mit drei Chips die drei verschiedene Biasverfahren implementieren. Die ersten beiden wurden von einem Team innerhalb von CSEM entworfen wobei Teilkomponenten aus dieser Arbeit beigetragen wurden. Der dritte Chip wurde speziell für diese Arbeit entworfen.

Calanda verwendet ein Bias-Verfahren auf Basis der Annäherung das die Schaltgeschwindigkeit proportional zum Sättigungsstrom der PMOS- und NMOS-Transistoren ist. Eine analoge Regelschleife reguliert dabei über den Biaskontakt die PMOS- und NMOS-Ströme auf äquivalent zu einem Referenzstrom der von einem Digital-Analogwandler mit Stromausgang gesetzt wird. SRAM und Core werden mit dem Ziel charakterisiert geeignete Betriebspunkte über einen weiten Betriebsbereich zu finden. Zusätzlich wurde eine Schar von Ringoszillatoren integriert um die Charakterisierung und Modellierung aus dem ersten Teil dieser Arbeit mit Messdaten zu unterfüttern.

Nakayama erweitert das Bias-Verfahren von Calande um eine sekundäre Regelschleife auf Basis einer FLL, welche als Teil dieser Arbeit entworfen wurde, zusammen mit einem Ringoszillator

#### Zusammenfassung

auf Standardzellbasis. Die Regelschleife kontrolliert die DAC-Codes so das eine vom Anwender gesetzte Zielfrequenz erreicht wird. Wir zeigen das dieser Ansatz in der Lage ist die Nachteile des Calanda-Konzeptes zu umgehen und eine effektive Regulierung implementiert.

Snaefellsjokull nutzt ein Biaskonzept welches auf eine besonders simple Implementierung setzt wobei zwei konstante Biasspannungen für die PMOS-Transistoren zwischen einen Haltemodus und Operationsmodus definieren. Eine Ladungspumpe wird von einem Standardzellkompatiblen Strombalance-Sensor kontrolliert um die NMOS-Biasspannung so zu regulieren das der Sättigungsstrom von PMOS und NMOS identisch sind. Wir zeigen das dieser einfache Ansatz zu einer effizienten Regulierung führen kann.

**Schlüsselworte:** Digitale Schaltungen, Low-Power Design, Deeply Depleted Channel, Adaptives Body Biasing, PVT Kompensation, Standardzellbibliothek-Analyse, Design Space Exploration, Durchsatz-Skalierung, Stromspar-Modus, Bias-Generator.

# Contents

| A  | cknov  | vledgements                                                      | i   |

|----|--------|------------------------------------------------------------------|-----|

| Αl | bstrac | et (English/Deutsch)                                             | iii |

| 1  | Intr   | oduction                                                         | 1   |

|    | 1.1    | Low Power Design                                                 | 2   |

|    |        | 1.1.1 Reducing Dynamic Power                                     | 3   |

|    |        | 1.1.2 Reducing Leakage Power                                     | 6   |

|    |        | 1.1.3 Power versus Energy                                        | 6   |

|    | 1.2    | Variation Mitigation Strategies for Low Power Designs            | 6   |

|    | 1.3    | Body Control for Variability Mitigation and Throughput Scaling   | 7   |

|    | 1.4    | Body Control with DDC                                            | 9   |

|    | 1.5    | Thesis Outline and Contributions                                 | 10  |

|    |        | 1.5.1 Part 1: Library Analysis and Design Space Exploration      | 10  |

|    |        | 1.5.2 Part 2: Library Analysis and Design Space Exploration      | 11  |

|    | 1.6    | Third-Party Contributions                                        | 11  |

| Ι  | Lib    | rary Analysis and Design Space Exploration                       | 13  |

| 2  | Star   | ndard Cell Library Analysis and Comparison                       | 15  |

|    | 2.1    | Introduction                                                     | 15  |

|    | 2.2    | Cross Corner Library Comparison Methodology                      | 16  |

|    |        | 2.2.1 Identifying Identical Operating Points Between Two Corners | 17  |

|    |        | 2.2.2 Comparing Individual Timing Arcs                           | 18  |

|    | 2.3    | Dataset                                                          | 19  |

|    | 2.4    | Results                                                          | 19  |

|    | 2.5    | Conclusion                                                       | 22  |

| 3  | Des    | ign Space Evaluation and Low Effort Mapping                      | 25  |

|    | 3.1    | Introduction                                                     | 25  |

|    | 3.2    | Mapping the Design Space                                         | 26  |

|    | 3.3    | Reference circuit                                                | 27  |

|    |        | 3.3.1 Standard Cell Library Characterisation                     | 28  |

#### Contents

|                         |       | 3.3.2    | MEP for the 32 Bit Multiplier Reference Design                |

|-------------------------|-------|----------|---------------------------------------------------------------|

|                         | 3.4   | Scaling  | the Reference Circuit to an Arbitrary Design                  |

|                         |       | 3.4.1    | ADVBB Model 31                                                |

|                         |       | 3.4.2    | Finding the MEP for a Constant Frequency                      |

|                         | 3.5   | Case St  | rudy: 32 Bit Microprocessor                                   |

|                         |       | 3.5.1    | Modelling Accuracy                                            |

|                         |       | 3.5.2    | Process and Temperature Effects                               |

|                         | 3.6   | Conclu   | sion                                                          |

| II                      | Cir   | cuits f  | or Bias Control 37                                            |

| 4                       | Intro | oductio  | n to Biasing Systems 39                                       |

|                         | 4.1   |          | ses of Biasing Systems                                        |

|                         | 4.2   |          | nents of a Biasing System                                     |

|                         |       | 4.2.1    | Sensor                                                        |

|                         |       | 4.2.2    | Bias Generators                                               |

|                         |       | 4.2.3    | Control                                                       |

|                         | 4.3   | Implen   | nentations and Applications                                   |

|                         |       | 4.3.1    | Static Process Compensation                                   |

|                         |       | 4.3.2    | Short Term Retention                                          |

|                         |       | 4.3.3    | Joint Operation with Supply Voltage Scaling                   |

|                         |       | 4.3.4    | Design Time Optimisation with Multiple Bias Partitions        |

|                         | 4.4   | Biasing  | Concepts in this Thesis                                       |

| 5                       | Cala  | ında: Aı | nalog On-Current Regulation 47                                |

| 5.1 System Architecture |       |          |                                                               |

|                         | 5.2   | On-Cu    | rrent based Biasing Concept                                   |

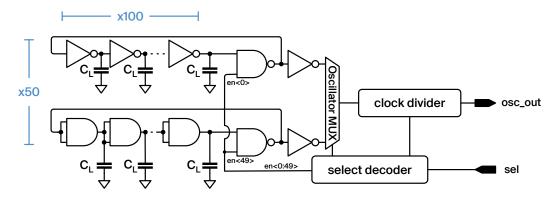

|                         | 5.3   | Standa   | rd Cell Ring Oscillators for Bias System Characterisation 52  |

|                         |       | 5.3.1    | Ring Oscillator Construction                                  |

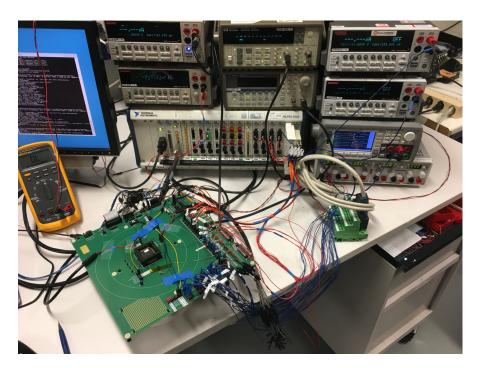

|                         | 5.4   | Chip M   | leasurements                                                  |

|                         |       | 5.4.1    | Measurement Setup                                             |

|                         |       | 5.4.2    | Biasing Design Space                                          |

|                         |       | 5.4.3    | Ring Frequency Across PVT with the Calanda Biasing System 59  |

|                         |       | 5.4.4    | Hardware Verification of the ADVBB Model 63                   |

|                         |       | 5.4.5    | System Results                                                |

|                         | 5.5   | Conclu   | sion                                                          |

| 6                       |       | •        | Analog On-Current Regulation with Secondary FLL based Regula- |

|                         | tion  | Loop     | 77                                                            |

|                         | 6.1   | System   | Architecture                                                  |

|                         |       | 6.1.1    | Core Bias Subsystem                                           |

|                         |       | 612      | Fine Grained Memory Bias Subsystem                            |

|   |     | Cont                                                                                 | ents |

|---|-----|--------------------------------------------------------------------------------------|------|

|   |     |                                                                                      |      |

|   | 6.2 | Biasing Concept Details                                                              | 79   |

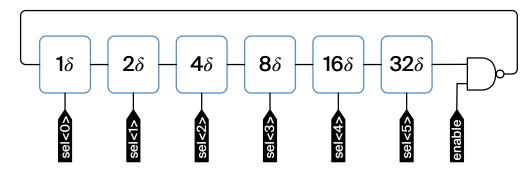

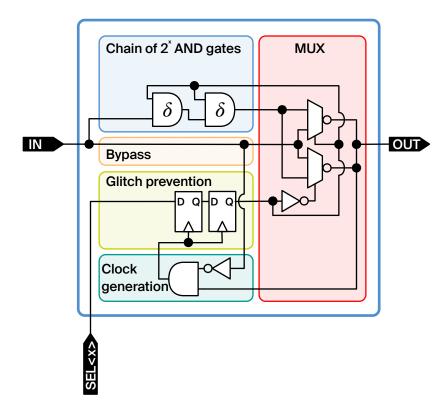

|   | 6.3 | Oscillator Design                                                                    | 82   |

|   | 6.4 | FLL Design                                                                           | 85   |

|   | 6.5 | Chip Measurements                                                                    | 87   |

|   |     | 6.5.1 Measurement Setup                                                              | 88   |

|   |     | 6.5.2 Oscillator Characterisation                                                    | 89   |

|   |     | 6.5.3 FLL Characterisation                                                           | 89   |

|   |     | 6.5.4 System Power                                                                   | 91   |

|   | 6.6 | Conclusion                                                                           | 92   |

| 7 | Sna | nefellsjokull: Worst Case Oriented Body Bias                                         | 95   |

|   | 7.1 | System Architecture                                                                  | 95   |

|   | 7.2 | Biasing Concept                                                                      | 96   |

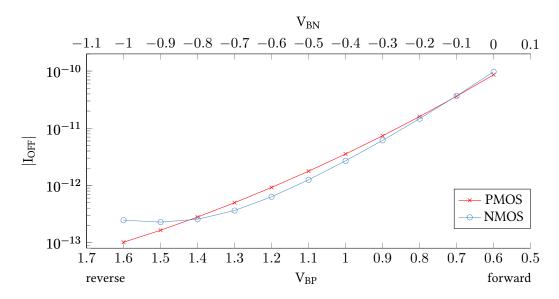

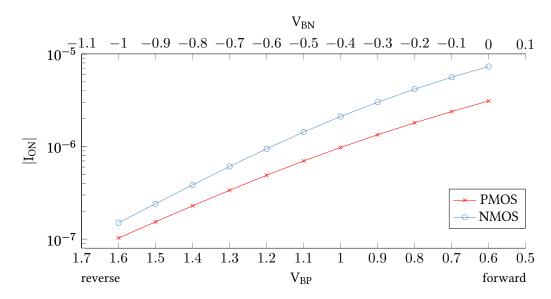

|   |     | 7.2.1 I <sub>ON</sub> and I <sub>OFF</sub> Considerations in Operation and Retention | 97   |

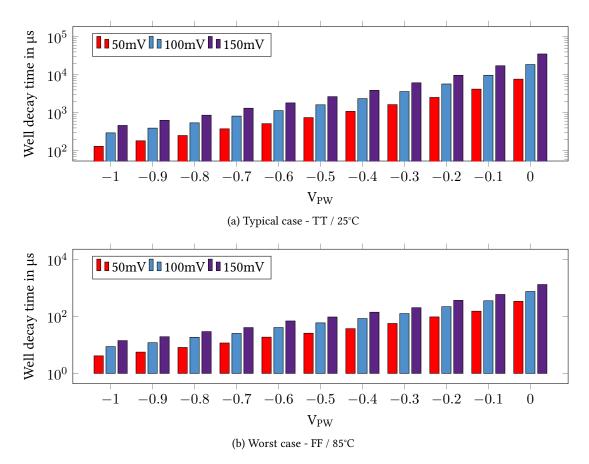

|   |     | 7.2.2 Well Leakage Considerations                                                    | 98   |

|   |     | 7.2.3 Sensing                                                                        | 99   |

|   | 7.3 | Bias System Implementation Details                                                   | 101  |

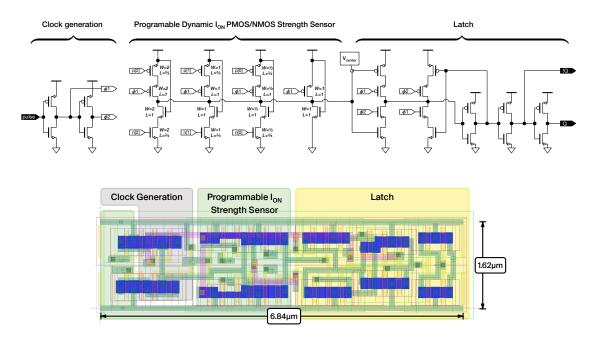

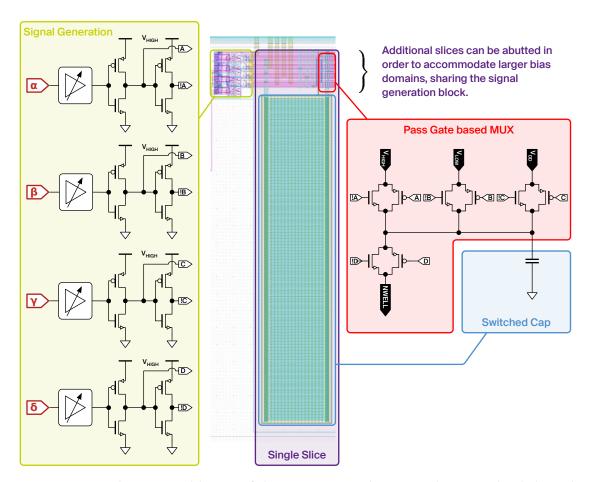

|   |     | 7.3.1 Distributed NMOS/PMOS Balance Sensor                                           | 101  |

|   |     | 7.3.2 PMOS Bias Switch                                                               | 104  |

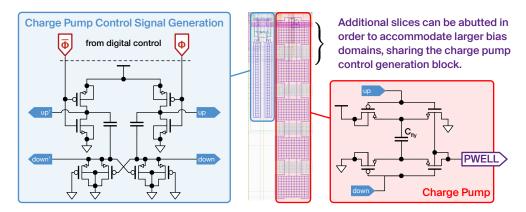

|   |     | 7.3.3 NMOS Bias Charge Pump                                                          | 104  |

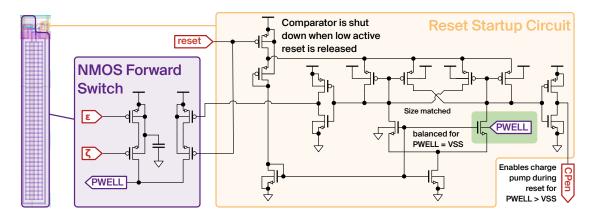

|   |     | 7.3.4 NMOS Forward Switch                                                            | 106  |

|   |     | 7.3.5 Proposed Regulation Loop                                                       | 107  |

|   | 7.4 | Bias System Operation                                                                | 109  |

|   | 7.5 | System Retention Power                                                               | 109  |

7.6

Bibliography

**Curriculum Vitae**

**List of Publications**

**8** Conclusion and Outlook

117

121

139

141

### 1 Introduction

Over the last years the requirements of wireless sensors and actors have shifted significantly. What was once a simple "dumb" sensor is now expected to integrate into smart systems and environments, allowing for an orchestrated control. This development is generally subsumed under the buzzword *Internet of Things*, a term initially coined by Kevin Ashton in the context of using RFID for supply chain tracking [1]. The meaning has since broadened to include all kinds of autonomous devices which are by some method connected to a network. A typical example would be an intelligent heating system using wireless temperature and gas sensors across the apartment together with window sensors to make "clever" decisions on whether to turn on the heating and ventilation or not. Typically these devices are of ubiquitous nature and are operated with a fairly low consciousness on our side: We expect these devices to operate reliably, but stay out of our way when not needed with easy installation, typically meaning that operation is battery powered.

Hence, the key requirement for these sensors is a very low power footprint and autonomous operation over a long time: The direct interaction with these kind of devices is so rare that, contrary to highly interactive devices like smart phones, a frequent recharge or battery replacement is not acceptable.

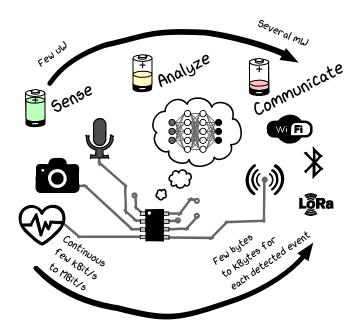

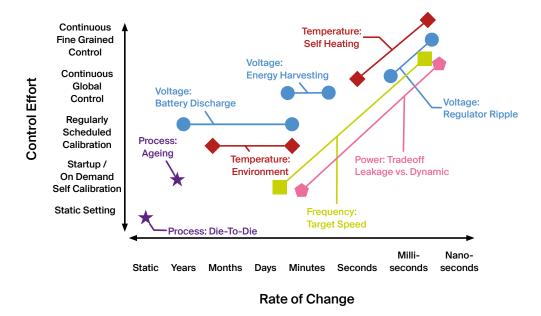

Typically these kind of devices integrate some kind of sensor, together with some ability to preprocess data locally and some wireless protocol for communication. Figure 1.1 illustrates the power profile of these components: Sampling data from the sensor is typically the lowest power contributor while the most power expensive part is active communication [2]. This leaves a nice tradeoff in between where local processing, often applying the pattern matching capabilities from artificial intelligence algorithms, are used whenever possible to reduce the number of necessary transmissions.

A prime example for this kind of architecture is the implementation of voice control: a low power wakeup circuit is capable to detect a keyword (Alexa, Ok Google, Hey Siri,...) which then triggers a transmission of the speech command into the cloud only when necessary.

Figure 1.1 - Cost of interaction: Sensing vs. Analysis vs. Data transmission

#### 1.1 Low Power Design

Achieving the associated ultra low power requirements sets a particular challenge for the SoC designer: the circuit must be able to idle at as low as possible power for the majority of time, but must also be able to achieve the performance necessary to apply the, often demanding [3], filtering or pattern detection algorithms required for its particular task. The answer typically is to add some kind of adaptivity to the circuit, shifting the mode of operation back and forth between a high performance computation mode and an ultra low power idle mode [4]. Circuit power can be broken down into two main components:

**Dynamic Power** is the power due to the switching activity in the chip, comprising the power attributed to the charge and discharge processes of wire and gate capacitances. A first order approximation can be derived as follows:  $V_{DD}$  is the supply voltage and f the operating frequency.  $C_L$  represents the total load capacitance over all switched transistors, which consists mainly of the gate capacitance as well as wire routing capacitances. The switching factor  $\alpha_{sw}$  represents an activity factor, considering that a) not all transistors are switched all the time and b) that energy spent to charge a gate capacitance during a low to high transition will be dissipated again in the next high to low transition.

$$P_{dyn} = \alpha_{sw} \cdot C_L \cdot V_{DD}^2 \cdot f \tag{1.1}$$

Leakage Power, also known as static power, subsumes all components resulting from the

currents I<sub>OFF</sub> that flow even when there is no activity inside the circuit.

$$P_{leak} = V_{DD} \cdot I_{OFF} \tag{1.2}$$

The main contributor for the I<sub>OFF</sub> are residual sub-threshold currents through "closed" MOSFETs, followed by substrate leakages through reversed p-n-junctions used in the construction of the devices [5].

#### 1.1.1 Reducing Dynamic Power

In principle all parameters in (1.1) and (1.2) can be optimisation targets to reduce circuit power. For example, the activity  $\alpha_{sw}$  can be tackled with all kinds of dynamic power management techniques, with the most prominent being clock gating [6]–[8], a design time methodology where logic is introduced into the clock tree in a carefully designed manner to only clock the parts of the circuit that are currently in use. Similarly, the clock frequency f can be adjusted on those to reduce the switching in a given time period. Adjusting the supply voltage  $V_{\rm DD}$  is very promising due to the squared contribution towards  $P_{\rm dyn}$ .

However, the circuit speed is defined by the rate at which the gate capacitances can be charged and discharged which can be modelled in first order approximation by a simple RC model. Taking the simple approximation of the charge- and discharge speed based on the on-resistance [9, p. 200ff.] and, for the sake of simplicity, even further simplifying it by removing the channel length modulation term and assuming the PMOS and NMOS currents are well balanced we can show that the propagation delay is in first order approximation are proportional to the input voltage  $V_{DD}$  and the saturation current  $I_{DSAT}$ . For the purpose of this work we will assume the latter to be closely approximated by the on-current  $I_{ON}$  which we define as the drain source current  $I_{DS}$  imposed by the MOSFET for the case of  $V_{GS} = |V_{DS}| = V_{DD}$ , i.e. the current flowing when we just started the (dis)charge of the output node while also assuming that the gate voltage has completely settled. With this we can formulate the basic model for the propagation delay

$$tp \propto C_L \cdot V_{DD} \cdot \frac{1}{I_{ON}},$$

(1.3)

or, when considering the achievable frequency:

$$f \propto \frac{I_{ON}}{C_L \cdot V_{DD}}.$$

(1.4)

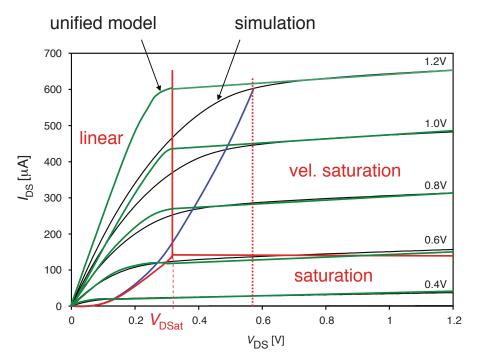

Figure 1.2 – Estimated current  $I_{DS}$  (green) vs. actual current (black) from the spice BSIM-4 model for different gate source voltages. Reproduced from [10, p. 28].

$I_{DS}$  is indeed is a function of the Supply voltage as shown in the unified empirical model described in Rabaey et al. [9, p. 101]:

$$I_{DS} = 0 \text{ for } V_{GT} \le 0$$

(1.5)

$$I_{DS} = k' \frac{W}{L} \left( V_{GT} V_{min} - \frac{V_{min}^2}{2} \right) (1 + \lambda V_{DS}) \text{ for } V_{GT} \ge 0$$

(1.6)

with

$$V_{min} = min(V_{GT}, V_{DS}, V_{DSAT}),$$

(1.7)

and

$$V_{GT} = V_{GS} - V_T$$

(1.8)

The supply voltage appears in this equation mainly as the gate source voltage  $V_{GS}$  (as the input of a digital cell) and as the drain source voltage  $V_{DS}$  for driving the load current. The remaining parameters are the width W and length L of the transistor, the process transconductance k', and the channel length modulation parameter  $\lambda$ . Finally the saturation voltage  $V_{DSAT}$  denotes the point at which the velocity of the current driving carriers no longer linearly increases with the strength of the field imposed by  $V_{GS}$ , but saturates.

This model is simplified, but, as shown in Fig. 1.2, predicts the current  $I_{DS}$  for a large  $V_{DS}$  and  $V_{GS}$  fairly well, which is the region the transistor in a digital CMOS gate operate for a large share of the charge/discharge time [10, p. 28].

For short channel transistors, which are typically used in digital gates due to space constraints,

the current is typically limited by velocity saturation, resulting in a linear relation between  $V_{GS}$  and  $I_{DS}$ . We can observe that in Fig. 1.2, where starting from 600 mV upwards every gate voltage increase of 200 mV results in an increase in current of approximately 170  $\mu A$ . For supply voltages below 600 mV we reach the saturation region where the relationship between  $V_{GS}$  and  $I_{DS}$  becomes quadratic.

While (1.3) on first glance suggests a slowdown with an increased  $V_{DD}$  we observe an effect of  $V_{DD}$  on  $I_{DS}$  which is significantly larger: considering Fig. 1.2 a mere 200 mV step in  $V_{GS}$  from 600 mV to 800 mV results in an increase of current from roughly 100  $\mu$ A to about 270  $\mu$ A. Hence, we can use the drive current  $I_{DS}$  of the MOSFET as a simplified proxy for the circuit speed. As such we can expect a linear dependence between the achievable operating frequency of a circuit and the supply voltage in velocity saturation and a quadratic dependence at lower supply voltage when the transistors are operated mostly in saturation during the charge and discharge of the capacitive load of the gate.

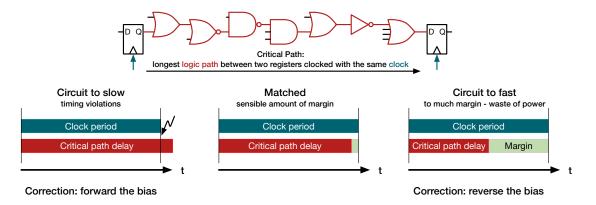

Consequently it is necessary to regulate the supply voltage and clock frequency carefully and jointly to keep a balance between not introducing timing violations and, in the opposite direction, not commencing excessive margins. This adaptive voltage and frequency scaling (ADVFS) approach is very today widely adopted in the industry. As this approach effects both the squared  $V_{\rm DD}$  and the frequency term in (1.1) the designer is left with a very powerful tool for significant power reduction in cases where the workload is lower than the achievable throughput. Not surprisingly this approach is commonly used in high performance CPUs to reduce idle power [11], but has also been used in low power SoC proposals such as [12].

However, once the supply voltage dips below the threshold voltage the current driving capabilities reduce drastically, converging towards, but never reaching the approximation of zero from the unified model in (1.5). Instead, the following model for weak inversion conduction can be used which shows an exponential dependence of the drive current  $I_D$  of the gate source voltage  $V_{GS}$  and the drain source voltage  $V_{DS}$  [9, p. 103]:

$$I_{DS} = I_S \cdot e^{\frac{V_{GS}}{n \cdot kT/q}} \left( 1 - e^{-\frac{V_{DS}}{kT/q}} \right) \text{ for } V_{GT} \le 0$$

(1.9)

Pushing a circuit into this sub-threshold domain can be very effective: Myers et al. [13] show a reduction in active power of more than 5000x when sweeping the supply voltage from 1.2 V to 250 mV at which point it reaches the same order of magnitude as the circuit leakage. The exponential reduction in current driving capability obviously has a massive effect on the propagation delay: the circuit speed reduces from 66 MHz down to 27 kHz, a factor of 2444x. Furthermore, doping variability induced shifts of the threshold voltage between different devices on the same chip result in a significant shift of drive capability on the exponential slope.

#### 1.1.2 Reducing Leakage Power

While the sub-threshold current variation has a significant impact on the speed of circuits operating with a supply voltage below the threshold voltage  $V_T$ , it is also an important factor for circuits operating with above the threshold. In this case, the leakage current consumed when transistors are not switching is determined by (1.9).

This means that just a small amount of shift in either the device threshold voltage or the gate source voltage can result in a substantial shift in leakage current due to the exponential nature of this curve. The result is, that a few particularly bad devices can dominate the overall circuit leakage [5, p. 9].

#### 1.1.3 Power versus Energy

Maximizing the battery life of a design is equal to minimzing the energy consumed by the design. Hence, an operation close to the minimum energy point (MEP)[14] is desirable to maximize the operation time. Power is the rate of energy consumed per time and is typically used for measurements as it can be easily derived from the supply currents and voltage. When the operating frequency of a device varies, power and energy are not the same and the energy minimum point may be significantly different from the minimum power. However, for constant frequency applications with no idle periods (as considered in this thesis), minimizing energy corresponds to minimizing power. Hence, power and energy are used interchangeably in this thesis.

#### 1.2 Variation Mitigation Strategies for Low Power Designs

When aggressively scaling the supply voltage down into the near- and sub-threshold domain the device becomes particularly susceptible for random process, supply voltage, and temperature variation. In [15] Dreslinski et al. show how the gate delay variation due to process degrades from 1.3X at nominal voltage over 5X at near-threshold up to 14X in the sub-threshold domain. While the former can be easily covered by adding margins using a multi mode multi corner (MMMC) approach for the static timing analysis (STA) at design time, the latter two cases introduce highly pessimistic margins that degrade the circuit characteristics for corners other than the worst case.

Those margins can be avoided by adding a control loop that adjusts either the supply voltage or the circuit clock frequency at run-time so that it matches the specific (rather than the worst case) operating conditions. More advanced schemes include even rapid adaptation to the supply voltage ripple of a simple DCDC [16] or even adaptation of the clock frequency to data dependent circuit delay variations [17].

An alternative control approach is the use of body biasing [18]. While aggressive voltage scaling

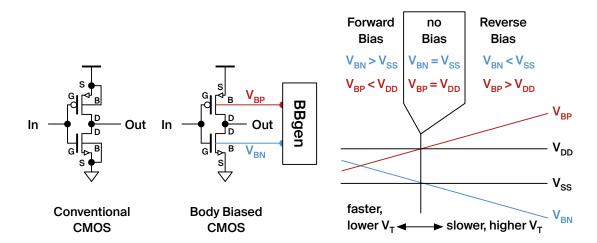

Figure 1.3 – Left: Inverter with conventional CMOS in comparison to an inverter with body biasing. A body bias generator (BBgen) produces the two body voltages  $V_{BP}$  and  $V_{BN}$ , setting the source bulk voltage  $V_{SB}$  of NMOS and PMOS respectively. Right: forward and reverse biasing ranges for NMOS and PMOS.

shifts the circuit supply voltage relative to the threshold voltage, body biasing achieves a similar effect by shifting the threshold voltage relative to the supply by applying a bias voltage to the substrate, resulting in a modulation of the tradeoff between leakage and circuit speed.

The above described dynamic adaptation requires a sensor to identify the circuit speed under the given operating conditions to adjust the available control knobs accordingly. Several sensing approaches have been proposed in literature: The first category tries to estimate the general speed of the die, for example by counting cycles of ring oscillators [19] or measuring the propagation through critical path replicas [20], [21] or canary circuits. The second category follows the concept of in situ timing error detection, introduced by Ernst et al. with "Razor" [22]. The general idea is the detection of late arriving changes on the data pin in relation to the clock pin on registers identified as potential critical paths. If an error is detected the clock period can either bee stretched out, replaying the previous instruction or the overall frequency can be reduced. Over the years a plethora of variations of the concept have been published [23]–[26].

# 1.3 Body Control for Variability Mitigation and Throughput Scaling

Body biasing as a technique has been around for decades and used to be a fairly effective knob to adjust the threshold even in standard CMOS bulk technologies. Adjusting the body voltage directly effects the threshold voltage  $V_T$  as shown in Fig. 1.3 for a simple inverter: when applying a positive voltage to the bulk contact of the NMOS and a voltage smaller than  $V_{DD}$  to the bulk contact of the PMOS the circuit is pushed into a forward bias condition. This decreases the threshold voltage  $V_T$ , resulting in a faster circuit speed and an increased leakage. The other

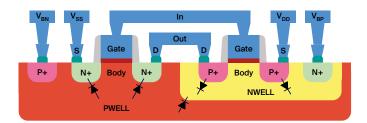

Figure 1.4 – Cross section of the CMOS inverter with the built in diodes.

way around, when applying a negative voltage to the bulk contract of the NMOS and a voltage larger than  $V_{DD}$  to the PMOS bulk we achieve a reverse bias with an increased  $V_{T}$  resulting in a slowdown and reduction in leakage.

The limits of the biasing are defined by the built in diodes shown in the cross section of the CMOS inverter depicted in Fig. 1.4. These have to be kept in a reverse bias condition during operation to guarantee functionality and to prevent excessive leakage. The main limitation is the p-n junction formed by the NWELL floating within the PWELL, resulting in a maximum forward bias just below the threshold voltage of the built in diode which is typically around 0.7 V.

More precisely, the threshold voltage change caused by a change in body voltage of the MOSFET can be modelled as follows:

$$V_T = V_{T0} + \gamma \left( \sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|} \right)$$

(1.10)

The main contributor here is the body factor  $\gamma$ , a process specific parameter modelling the effectiveness of changes in the body voltage  $V_{SB}$  which in the following will be referred to as  $V_{BN}$  and  $V_{BP}$  for NMOS and PMOS respectively.  $V_{T0}$  expresses the threshold voltage for the zero bias case where  $V_{BN}$  is equal to  $V_{SS}$  and  $V_{BP}$  is at the potential of the supply voltage  $V_{DD}$ . The remaining parameter  $\phi_F$  is the Fermi potential.

Unfortunately, with feature sizes scaled down into the nanometer range that knob became less and less effective  $\gamma \approx 0$ , to the point where it is typically no longer considered a useful tool for the designers - to the point where early FDSOI technologies completely removed control due to the thick buried oxide with floating body [10, p. 31].

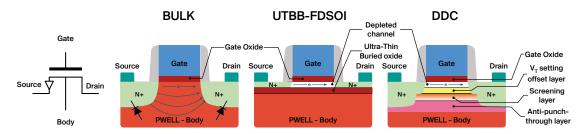

However, in the last decade two technologies have surfaced to counteract this trend - Ultra Thin Body and Box Fully Depleted Silicon on Insulator (UTBB-FDSOI) [27], and Deeply Depleted Silicon on Insulator [28]. Figure 1.5 depicts the general cross section of both devices besides a standard bulk NMOS transistor. Both devices share the common idea to insulate the channel from the bulk. This insulation has two main effects: the electrostatic field becomes more regular and the channel is insulated, removing the bias limitation of the built in diodes, vastly increasing

Figure 1.5 – Device cross section of an NMOS transistor in a) a standard bulk technology, b) Ultra Thin Body and Box Fully Depleted Silicon On Insulator [32] and c) Deeply Depleted Channel [30]

the range of the bias.

Furthermore, both technologies share a depleted channel. With nanoscale devices the dopant atoms in the channel become sparse and hence a handful of randomly assigned discrete number of atoms for each device dictates the performance. Hence, if the technology is able to operate on a depleted channel we can expect a significant reduction in random dopant fluctuations which directly translates into a significant reduction of intra die variation, a property which indeed has been shown in literature [29]–[31].

The main difference between UTBB-FDSOI and DDC is the manufacturing process: FDSOI uses SOI-wafers with a thinned down buried oxide layer as a starting point while the later one implants a stack of layers on a conventional bulk wafer in order to form the insulated and depleted channel with tightly controlled threshold voltages.

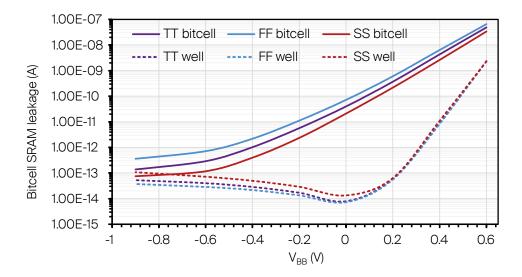

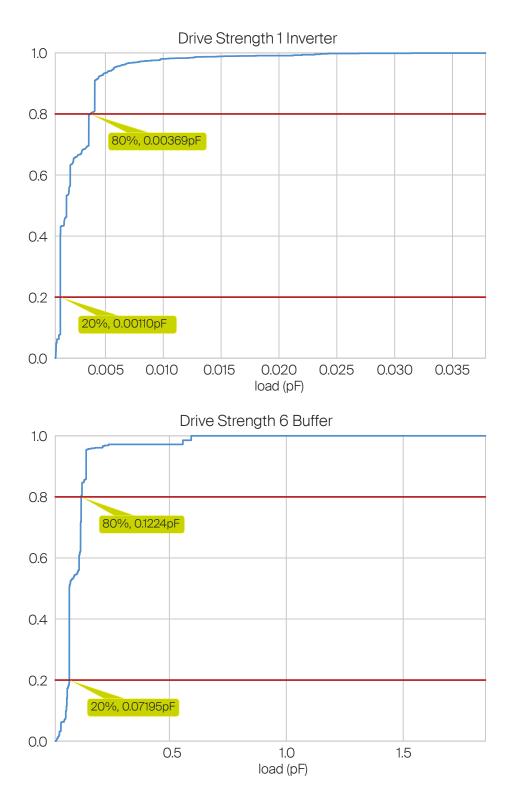

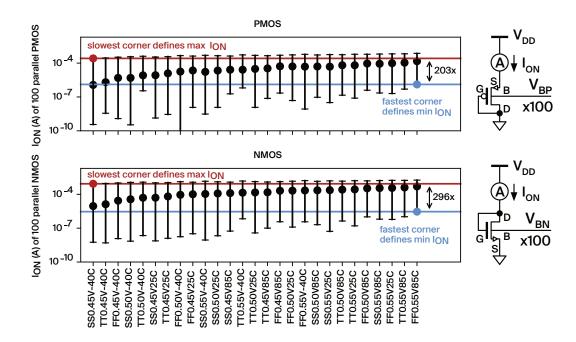

#### 1.4 Body Control with DDC

While UTBB-FDSOI allows for a larger biasing range, its body factor  $\gamma$  is more moderate with around 85 mV/v [33], [34] when compared to the 375 mV/v for 55 nm DDC. The process allows the bias to be adjusted in the range of  $-1 \, \text{V} < \text{V}_{\text{BB}} < 0.6 \, \text{V}$  which, combined with its particularly large body factor results in a remarkable property: *After* using body biasing for full PVT compensation DDC still allows for a change of drive strength by a factor of roughly 200 and 300 for PMOS and NMOS, respectively [35]. This property opens up a large design space for the designer, to play with frequency, supply voltage, and body control jointly to achieve the best power performance for their particular application. However, finding the best combination of these parameters for a particular design is a non trivial task which will be explored throughout this thesis.

#### 1.5 Thesis Outline and Contributions

In this thesis we describe methodologies for design space exploration, exploiting the design space extension through the strong body effect of DDC together with the capabilities of voltage scaling. This thesis is broken down into two major parts:

The first part concentrates on facilitating the muti-dimensional parameter exploration (supply voltage, frequency, body bias) at design time. To this end we focus on standard cell characterisation data to obtain a broad view on the scaling behaviour of a circuit. The intention is to cover the whole variety of different cells as well as transients and load conditions we expect to face in an actual circuit. We then show how to use that data to map the design space in a way which allows for predictions on circuit speed as well as leakage and dynamic power while also providing the necessary bias voltages.

The second part concentrates on actual circuits: Calanda, a test chip designed within CSEM with the goal to prototype an SoC using an on-current based biasing scheme while also integrating some test circuitry to allow for verification of the conclusions from the standard cell characterisation. Nakayama extends the biasing scheme shown in Calanda by integrating a frequency locked loop (FLL) based control on top. Finally, Snaefellsjokull proposes an alternate lightweight direct charge pump based biasing approach using a novel PMOS/NMOS balance sensor for regulation.

#### 1.5.1 Part 1: Library Analysis and Design Space Exploration

Chapter 2, Standard Cell Library Analysis and Comparison, describes a methodology to characterise the quality of a standard cell library before and after compensation based on library characterisation data. We show that body bias based compensation pushes the PVT corners together into a near match, reducing the cross corner median delay variation by two orders of magnitude.

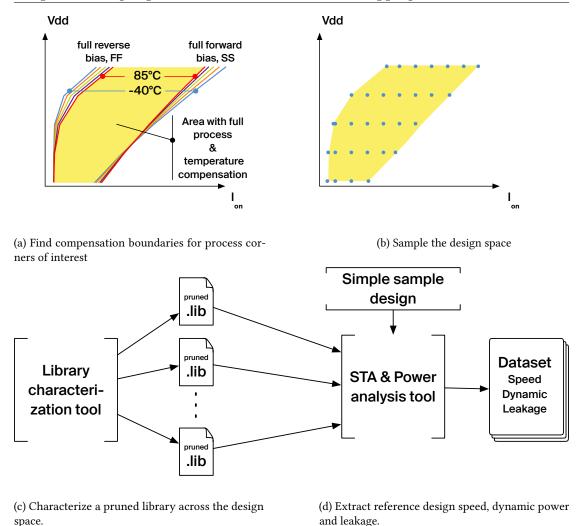

Chapter 3, Design Space Evaluation and Low Effort Mapping, again uses standard cell characterisation data, but this time with the goal of creating a tool for rapid design space exploration. We first identify the design space as the maximum and minimum on currents a transistor can achieve across all process and temperature corners when varying the bias forward and reverse respectively across the supply voltage range. We then sample this design space in equidistant steps by characterising a pruned library which we then use for a 32 bit multiplier as a sample design. The design is then analysed with an STA and power analysis tool in order to extract speed, dynamic power, and leakage at each design point. In the following the data is resampled into a V<sub>DD</sub> vs. frequency grid and interpolation is used in order to allow for intermediate points. We then show that we can derive universal scaling factors for both leakage and dynamic power, allowing to apply the model based on the reference design to arbitrary circuits, using a single point calibration. On the example of a 32 bit microprocessor we achieve

a near perfect match, predicting the total power within an error margin of one percent of the results of the dynamic and leakage estimation using a specifically characterised full standard cell library at the same points.

#### 1.5.2 Part 2: Library Analysis and Design Space Exploration

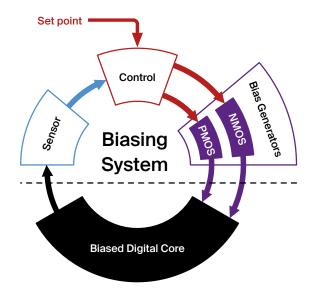

**Chapter 4, Introduction to Biasing Systems**, gives an introduction into biasing systems, followed by a brief literature review. We break down the general components, and explain concepts and use cases.

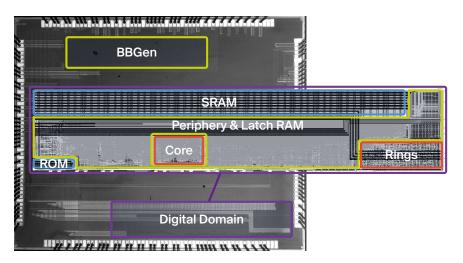

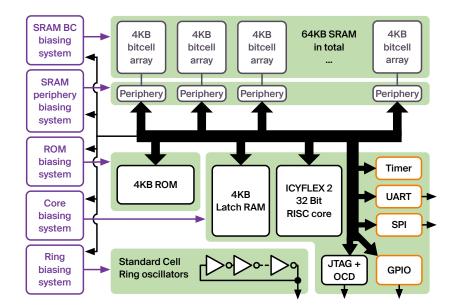

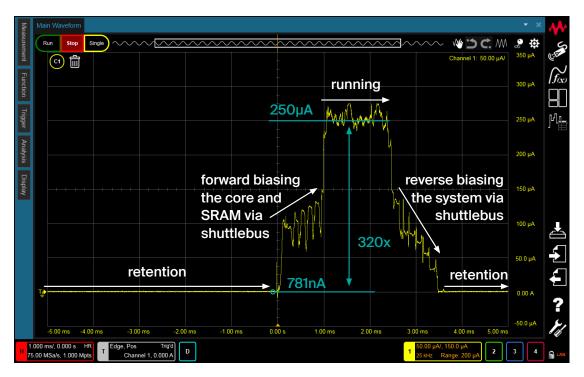

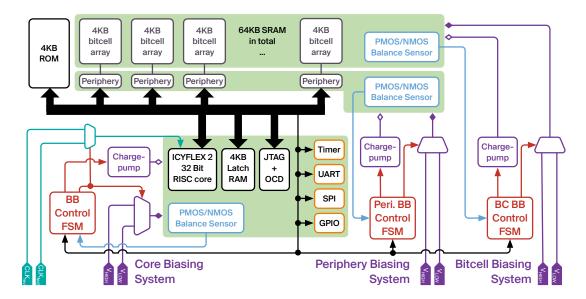

Chapter 5, Calanda: Analog On-Current Regulation, describes the Calanda SoC. Calanda integrates a 32 bit IcyFlex2 RISC core with 64KB SRAM, 4KB of standard cell memory and some standard microcontroller peripherals such as GPIOs, UART, SPI, and JTAG. The Idea of the on-current based bias control concept designed within CSEM is sketched out and we present power measurements of the core and SRAM under body control. Furthermore, the construction of standard cell based ring oscillators is presented. We apply the bias and supply voltages as predicted by the model introduced in Chapter 3 in an open loop fashion and show well matched constant frequencies across the rings when following a constant frequency trajectory through the design space at different predicted operating points. Furthermore, we show that a single point calibration for the static and dynamic power scaling factors achieves a decent match between the power model and measurements.

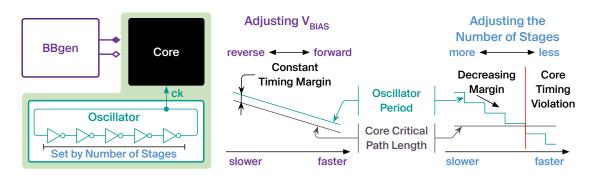

Chapter 6, Nakayama: Analog On-Current Regulation with Secondary FLL based Regulation Loop, describes the Nakayama SoC. The SoC integrates an icyglex 5, a 32 bit RISC-V-compatible core with 256 KB of bias domain banked SRAM, a BLE PHY, DAC/ADC, Timers, SPI, UART, and GPIOs. Nakayama extends on the biasing concept of Calanda by adding a secondary frequency locked loop (FLL) based control loop, allowing the user to set a target frequency rather than a numerical DAC code. We describe the FLL design and construction in detail and show measurement results.

Chapter 7, Snaefellsjokull: Worst Case Oriented Body Bias, describes an alternative approach for a biasing system centred using a light weight concept using a charge pump directly for the well together with a PMOS/NMOS balance system. The design strategy is worst case driven, but we show that the resulting regulation results in decent performance as well for the other cases.

#### 1.6 Third-Party Contributions

The Calanda chip on its own was a team effort with multiple persons working on concept, implementation, and integration. The on current based biasing approach, used for both Calanda and Nakayama, has been designed by a large team within CSEM. My role on this chip was mainly on the digital pre study which became Chapter 2 and the concept of the standard cell

#### **Chapter 1. Introduction**

based oscillators for hardware verification of the library chapter conclusions. Furthermore, I have driven a large share of the chip characterisation, including the memory design space exploration.

For Nakayama, as for Calanda, the actual biasing system has been designed as a group effort within CSEM. The main contribution of this thesis is in the implementation of the secondary FLL control loop, together with the programmable standard cell based oscillator responsible for generating the circuit clock.

# Library Analysis and Design Space Part I **Exploration**

# 2 Standard Cell Library Analysis and Comparison

In this chapter we characterize the cross corner and cell to cell variation of a custom standard cell library (SCL) in USJC 55 nm Deeply Depleted Channel (DDC) technology. Precharacterized Liberty library files are used as a dataset for comparing both the unbiased library against a characterization using adaptive body biasing (ABB) to compensate for process voltage and temperature (PVT) variation.

The chapter is largely based on the following paper:

T. C. Müller, J.-L. Nagel, M. Pons, *et al.*, "PVT compensation in Mie Fujitsu 55 nm DDC: A standard-cell library based comparison", in *2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S)*, Oct. 2017, pp. 1–2. DOI: 10.1109/S3S.2017.8309246,

#### 2.1 Introduction

When implementing an adaptive PVT compensation scheme, the designer is interested in some measure of the effectiveness of the chosen approach. Typically this measure is derived from a simple model of inverters or ring oscillators which is easy to integrate into the workflow typically used by analog designers. The assumption is, that these simple models, often based only on inverters, capture the variability across corners and the impact of changing the bias voltage by some common factor across all corners and for all instances of the digital cells within the circuit.

However, complex digital circuits typically contain a wide spread of cells, instantiated in different load scenarios which will see a wide range of input transitions. This adds additional uncertainty, not following a common factor, potentially resulting in critical path shifts across corners. This complicates multi-corner design-time optimisation and increases margins for run-time PVT compensation.

For the SoC designer it is important to know whether the chosen method of compensation applies identically to all the cells in the employed cell library or whether he needs to apply

Figure 2.1 – Transitions seen in a sample segment of a critical path in two operating corners (blue/red), arbitrary numbers for illustration purpose only.

margin to account for the delay scaling differences between cells during the implementation. If so, finding the right amount of required margin needed is a non trivial task.

Furthermore, designers of a standard cell libraries are interested in an exhaustive sweep of all possible conditions to identify the cases which cope particularly badly with variation. Setting up these kind of simulations in an analog design environment is a tedious task and it is easy to miss cases.

Digital implementation tools however already deal with a similar problem: they need transition and delay data in order to be able to provide an accurate estimate of static timing for the segments of the critical path as illustrated in Fig. 2.1. Hence, characterisation tools have been utilised for years to automatically generate test harnesses around cells in order to characterise the cells running exhaustive spice simulations in order to generate the necessary data.

In the following we will exploit the data generated from such a characterisation tool to extract the efficiency of an adaptive PVT compensation scheme.

#### 2.2 Cross Corner Library Comparison Methodology

When analyzing a circuit across operating corners we observe a scaling of the achieveable clock frequency  $f_{\text{max}}$ . In first order approximation this scaling can be described as a factor  $\alpha^l$  for an operating corner  $b_l$  relative to a reference corner  $b_{\text{ref}}$ .

$$\alpha^{l} = \frac{f_{\text{max}}(\mathbf{b}_{\text{ref}})}{f_{\text{max}}(\mathbf{b}_{l})} \tag{2.1}$$

The actual limiting factor however is the accumulated delay within the most critical path of the actual circuit, built from a specific selection of standard cells. Each cell c is constructed with a different schematic, resulting in minute differences of cross corner scaling. To provide a more

specific characterisation compared to (2.1) we could derive a naïve per cell scaling factor

$$\alpha_c^l = \frac{t_{\rm pd}(\mathbf{b}_l)}{t_{\rm pd}(\mathbf{b}_{\rm ref})} \tag{2.2}$$

based on the cell propagation delay  $t_{\rm pd}$ . This approach however is still too general to be meaningful in the context of an actual circuit. First, when transitioning from one logic input configuration to another one, different parts of the cell schematic will be excited based on the inputs, causing different delays. The most obvious cases are the pull up and pull down networks being responsible for rise and fall transitions respectively. The second, and more severe factor, is the actual environment seen by the cell, defined through the load on the output as well as the steepness of the transition on the input.

#### 2.2.1 Identifying Identical Operating Points Between Two Corners

When comparing the timing (i.e. instance delays and transition times) of a circuit for different PVT conditions we see a significant difference not only in the delay, but also in the transition times determined by the driver of each individual cell as illustrated in Fig. 2.1. Hence, we can not simply use the delay scaling for a given transition time of the individual cells as a proxy for the delay of the overall circuit since the parallel transition time degradation is not reflected properly.

As we would like to extrapolate the circuit delay scaling, including the impact of degraded input transitions, from the delay characteristics of individual cells in the library, we need to compare timing arcs that result from different input transitions.

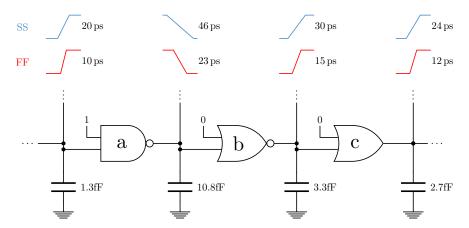

To this end, we first derive characteristic transition times for each load  $C_{in}$  as specified in the library for each considered PVT corner. This characteristic transition time for a given load is obtained from a reference gate—for the purpose of simplicity a buffer—that is replicated in a chain in which each node is loaded with  $C_{in}$  as illustrated in Fig. 2.2. Any reasonable transition applied on the input of the chain quickly converges to a characteristic transition time determined by the load  $C_{in}$  within a few steps. The implementation is a simple iterative table lookup with interpolation until conversion is reached as shown in Alg. 1.

Figure 2.2 – The transition at the output of the chain is characteristic for the combination of load (upper vs. lower chain) as well as operating corner (red vs. blue). The high gain of CMOS process results in a quick recovery of slow transition through a path and thus the output transition can be considered independent from the input transition for a long enough chain. Arbitrary numbers for illustration purpose only.

```

Algorithm 1 Iterative derivation of the characteristic transition for a given load.

```

```

function ExtractTransition(cell,load,corner)

currentT ← centerTransition(cell, load, corner);

while iteration < iterationLimit do

nextT ← transition(currentT,cell, load, corner);

if |nextT − currentT| < ϵ then;

return nextT;

else

currentT ← nextT;

end if

end while

return currentT;

end function

```

We now compare cells and their timing arcs in different PVT corners no longer for the same fixed transition time, but for the corresponding characteristic transition times within the respective corners associated with the same—PVT independent—load. With this approach cell delays are compared based on the equivalent (not equal) transition times in both corners.

#### 2.2.2 Comparing Individual Timing Arcs

In the following we refer to a specific tuple of a cell c, an input configuration p, a load  $C_{\rm load}$ , and an input transition  $t_{\rm rf,in}$  within a standard cell library as a realization  $r=(c,p,t_{\rm rf,in},C_{\rm Load})$ . Thus, we can define a realization specific delay scaling factor  $\alpha_r^l$ .

$$\alpha_r^l = \frac{t_{\rm pd}(r, \mathbf{b}_l)}{t_{\rm pd}(r, \mathbf{b}_{\rm ref})} \tag{2.3}$$

When comparing the values  $\alpha_r^l$  derived from the library across corners without compensation we expect a large spread, reducing the  $t_{\rm pd}$  for either fast process corner, low temperature or higher supply voltage while slow corner, high temperature or lower supply voltage cause an increased  $t_{\rm pd}$  and thus larger  $\alpha_r^l$ . Comparing compensated libraries on the other hand, values of  $\alpha_r^l$  are expected to be found close to one, where the spread around one is a measure for the effectiveness of the compensation (smaller spread is better).

#### 2.3 Dataset

The library analysis has been conducted on a custom standard cell library with 69 cells. It was designed for near threshold operation in USJC 55 nm DDC technology utilizing BB for PVT compensation. The library utilises 90nm channels on ultra low leakage (ULL) transistors in order to reduce the leakage even further and implements PMOS and NMOS transistors of identical size, relying on body control to balance the corresponding drive strengths.

For the uncompensated baseline data set we apply VDD and VSS to the PMOS and NMOS bulk contact respectively. For the compensated data set the bias voltages have been derived using Spice simulations, setting the bias voltages such that we achieve identical on-currents for NMOS and PMOS across the corners. The underlying assumption was that constant on-currents result in identical speed across the corners.

The standard cells have then been characterised for the selected operating corners using Cadence Liberate. The analysis was done on the output files in the Liberty file format, using the non linear delay model (NLDM).

We decided to use the typical process corner at 25  $^{\circ}$ C and 500 mV with some forward biasing as reference corner  $p_{\rm ref}$  for normalization of both the biased and unbiased case to allow for direct comparison.

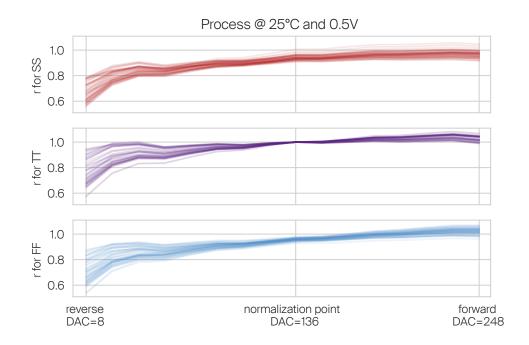

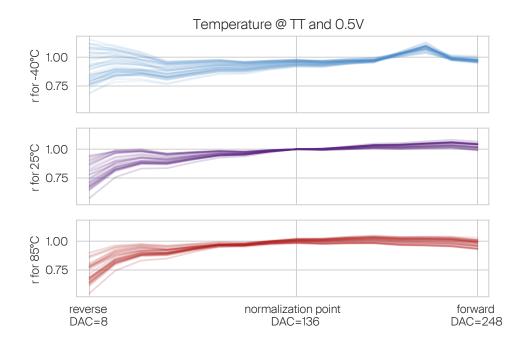

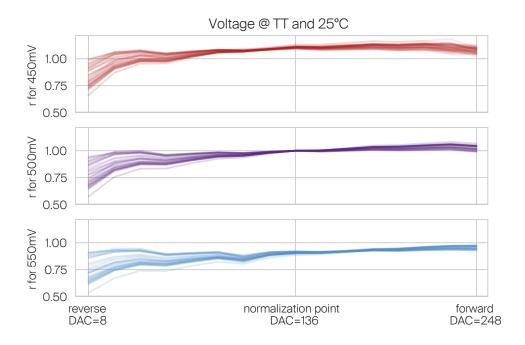

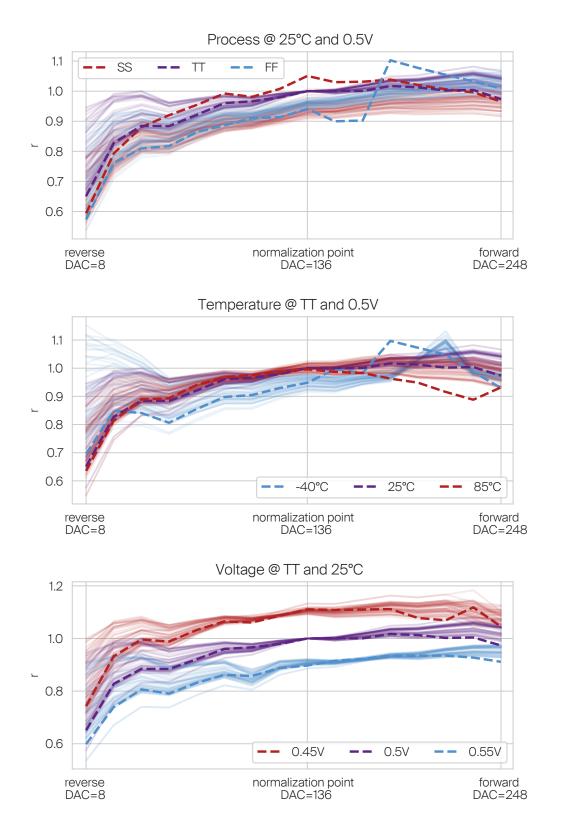

#### 2.4 Results

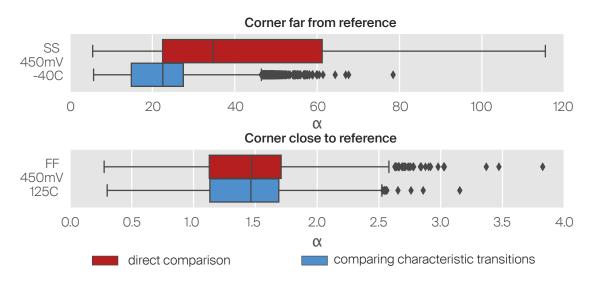

Figure 2.3 shows the necessity of the use of characteristic transitions in order to achieve a fair comparison between corners: the box plots show the variation seen for a corner which is far away from the reference corner as well as for an other one which is fairly close. While the use of characteristic transitions has very little effect on the close corner (median nearly identical, reasonably close match of the upper and lower quartile) the effect is significant on the much slower corner: with the naïve direct comparison of identical input transitions we obtain an overly pessimistic prediction of the factor alpha with a significantly larger spread.

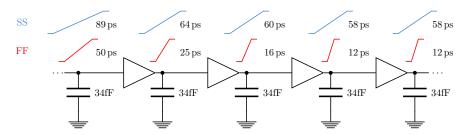

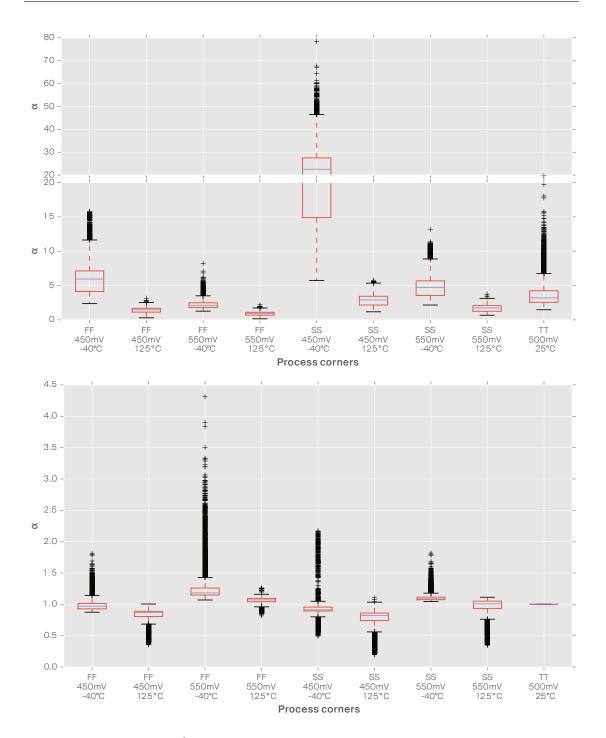

The boxplots in Fig. 2.4 show the distribution of the  $\alpha_r^l$  within each operating corner, before (top) and after compensation (bottom). SS, 450 mV, -40 °C is an extreme case where the circuit drops into deep subthreshold operation if not properly compensated through the biasing system.

Figure 2.3 – Without the use of characteristic transitions to obtain equivalent load based transitions the corners far from the reference corner show an overestimated variation, while the effect vanishes the closer the corners get to each other.

A worst case timing estimate that considers all the outliers (marked with the black crosses) would result in an overly pessimistic setup margin of 7845 % for the unbiased case. With the application of ABB this pessimistic margin shrinks to 431 %.

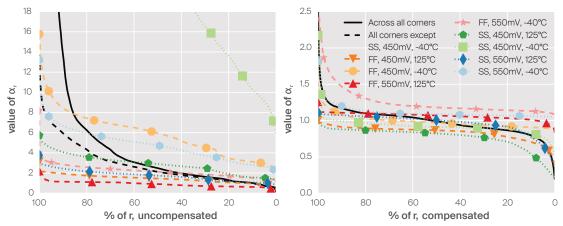

Since these margins are clearly excessive, we next analyze the responsible outliers to remove those that are not relevant in a practical circuit. Figure 2.5 plots the values of  $\alpha_r^l$ , sorted in descending order with and without compensation. We observe a steep drop on the left side of both plots, suggesting that only a small number of synthetic realizations are responsible for the majority of the observed worst-case delay variation. For an actual path within a design we would, however, expect only a few of these outliers if any at all, limiting their potential influence on the overall timing. Thus, for the majority of the designs these outliers can be ignored when discussing practically relevant margins.

We further note that a large share of the outliers are due to extreme input slope and load conditions which are typically prohibited by the design constraints used during implementation: it is therefore unlikely to see for example a minimum sized inverter driving high load net and hence those corner cases can be excluded from the analysis.

Instead, considering the wide plateau of similar values of  $\alpha_r^l$  around the center of Fig. 2.5, a more reasonable estimate for the cross corner performance of a circuit is the median  $\tilde{\alpha}^l$ , marked blue in Fig. 2.4. With compensation this median is pushed from a range of -9% to 2154% towards -18% to 18%, effectively reducing the margins needed to cover cross corner variation.

In order to observe the per corner, cell to cell variation we can remove the cross corner effects

Figure 2.4 – Boxplots of  $\alpha_r^l$  without (top) and with (bottom) compensation. To improve the visualisation the axis has been split at an  $\alpha_r^l$  of 20, showing the upper remainder of the box with a compressed axis.

Figure 2.5 – Sorted  $\alpha_r$ , ordered from slowest to fastest.

Figure 2.6 – Sorted  $\beta_r$ , ordered from slowest to fastest.

by normalizing each  $\alpha_r^l$  with the median  $\tilde{\alpha}^l$  to obtain a within corner scaling factor  $\beta_r^l$

$$\beta_r^l = \frac{\alpha_r^l}{\tilde{\alpha}^l}, \tag{2.4}$$

that reflects the variation across realizations.

The result of the normalization is depicted in Fig. 2.6. We observe that all corners are pushed on top of each other both for the compensated and uncompensated case. This observation shows that the median tracks the global scaling factor very well. Furthermore, we observe a pronounced plateau after compensation, implying even a reduced within-corner variation.

#### 2.5 Conclusion

We were able to exploit standard cell characterisation data in order to compare arbitrary corners against each other for a comprehensive set of timing arcs, transition times and load combinations. We proposed a methodology for a fair "apples-to-apples" comparison of synthetic circuit realizations in order to get a broad idea of the effectiveness of a compensation approach. On the example of a low power standard cell library designed for 55 nm DDC using adaptive body biasing, we showed that ABB is capable of compensating the PVT variation, achieving a reduction of the cross corner median delay variation by two orders of magnitude while also achieving a reduction of per-corner cell to cell variation.

# 3 Design Space Evaluation and Low Effort Mapping

In this chapter a systematic low-power design methodology for technologies that offer a strong body factor is discussed. Specifically, we explore both the body bias voltage and the supply voltage knobs in order to find the MEP (minimum energy point) for a constant target frequency.

The methodology presented accounts for process and temperature (PT) variations while charting the design space for a simple reference design. We then show how to scale the energy data of this reference design to any arbitrary design. A case study of a 32 bit RISC microprocessor achieves an energy estimation match of our significantly less complex estimation methodology within 1% of traditional signoff results.

This chapter is based on the following publication:

C. T. Müller, M. Pons, D. Ruffieux, *et al.*, "Minimum Energy Point in Constant Frequency Designs under Adaptive Supply Voltage and Body Bias Adjustment in 55 nm DDC", in *2019 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME)*, Jul. 2019, pp. 285–288. DOI: 10.1109/PRIME.2019.8787736

#### 3.1 Introduction

Technologies with a strong body factor such as USJC 55 nm deeply depleted channel (DDC) [29] provide the designer with an additional knob for energy optimisation in addition to the widely used adaptive voltage and frequency scaling (AVFS) techniques for which an analytical energy model was presented [38]. The goal of the designer is to operate as close as possible to the operating point where the sum of the leakage energy and the dynamic energy is minimal (MEP). Typically this MEP is located within sub- or near threshold operation, which significantly reduces the maximum operating frequency [14], [39]. However, with the body voltage as an additional knob, adaptive supply and body bias scaling (ASVBB) can be implemented, allowing for MEP tracking at a given constant frequency which is determined only by the application requirements [40]. Recently [41] presented such a scheme to automatically track the MEP at a given frequency by pinning the ratio of leakage to dynamic energy into a predefined range. In

Figure 3.1 – Steps to extract the reference data over the design space.

light of the efficiency of this approach and the need for real-time systems that require a given frequency, there is a need for a methodology to rapidly explore the associated design. Such a methodology rapidly identifies the achievable limits and provides near-optimal settings for adjusting supply voltage and body bias.

# 3.2 Mapping the Design Space

We start by charting the ASVBB design space, which defines the spread of leakage, dynamic energy, and frequency operating points.

Using ASVBB we may vary the supply voltage with the lower limit set by the reliability of the circuit and the upper limit set by the process. The legal body bias range  $\mathcal{V}(V_{dd})$  is set by the supply voltage as well as technology parameters, most notably the structure and forward

voltages of the built-in body diodes between NWELL and PWELL. Furthermore, the valid range under nominal conditions is reduced when PT variations have to be compensated with legal settings. For the USJC 55 nm DDC process used in this work, the strong body factor of 375 mV/V, allows to fully compensate across PT while still retaining a large frequency design space for MEP tracking [35].

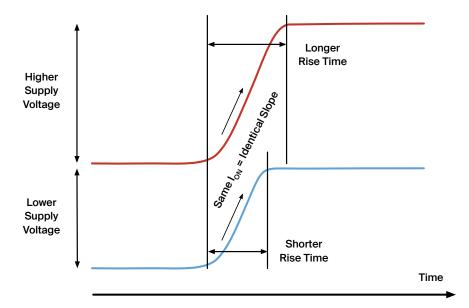

For the purpose of ASVBB design space exploration we use the on-current  $I_{ON}$  as a proxy for frequency, based on the following first order approximation where f denotes the frequency, C the load capacitance, and  $V_{dd}$  the supply voltage.

$$f \propto \frac{I_{ON}}{C \cdot V_{dd}} \tag{3.1}$$

Contrary to the frequency,  $I_{ON}$  can easily be measured and simulated while the PMOS and NMOS strength can be trivially fixed to a constant ratio. Furthermore the  $I_{ON}$  can be kept constant across PT, as the adjustment of the threshold voltage through the body voltage counteracts the effects of variation. The design space limits are then determined through spice simulations of  $I_{ON}$  through a representatively sized transistor under application of the maximum forward ( $V_{bb}^{fwd}=0.6\,\mathrm{V}$ ) and reverse ( $V_{bb}^{rev}=-1\,\mathrm{V}$ ) bias voltages, for the expected operation temperatures  $T\in\{-40\,^\circ\mathrm{C},25\,^\circ\mathrm{C},85\,^\circ\mathrm{C}\}$ , and across the process corners  $P\in\{FF,SS,TT\}$  of interest. The low end of the design space is defined by the highest  $I_{ON}$  for which PT can still be compensated (i.e., maximum reverse bias):

$$I_{ON}^{min}(V_{dd}) = \max_{p \in P, t \in T} \min_{V_{bb} \in \mathcal{V}(V_{dd})} I_{ON}(V_{dd}, V_{bb}, p, t)$$

(3.2)

Similarly, the upper end of the design space is defined by the minimum  $I_{ON}$  for which PT can still be compensated (i.e., maximum forward bias):

$$I_{ON}^{max}(V_{dd}) = \min_{p \in P, t \in T} \max_{V_{bb} \in \mathcal{V}(V_{dd})} I_{ON}(V_{dd}, V_{bb}, p, t)$$

(3.3)

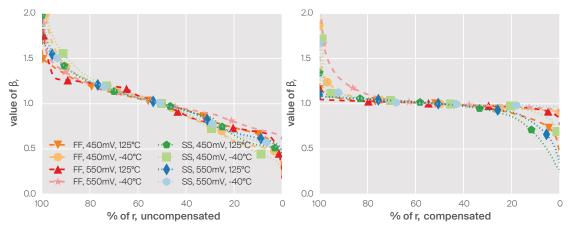

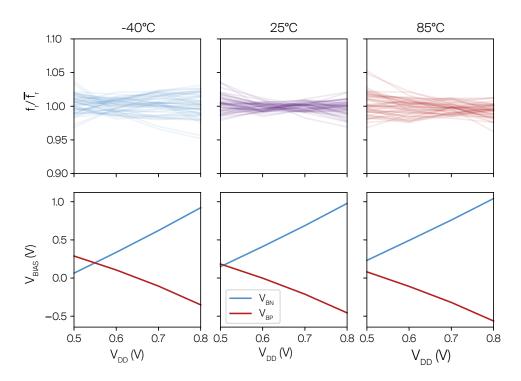

Figure 3.1a shows the boundaries set by the sweep, with the ASVBB design space spanned between the minimum  $I_{ON}$  (3.2) and the maximum (3.3) for each supply voltage. We notice that the design space across corners is very similar to the design space of the individual corners, thanks to the large body factor.

# 3.3 Reference circuit

After defining the boundaries of the ASVBB design space, we proceed to characterize normalized active energy, leakage power, and timing within this valid range. As shown in Fig. 3.1b, we propose to sample the ASVBB design space with a grid defined by sweeping a) the supply voltage and b)  $I_{ON}$  from minimum to maximum. For each grid point PMOS/NMOS bias voltage pairs are obtained. With these bias voltage pairs a standard cell library can be characterized for

each grid-point and for each PT combination. By using these libraries, we can easily search the design space using power and timing analysis for the optimum operating points of the target design.

#### 3.3.1 Standard Cell Library Characterisation

Unfortunately, a full standard cell library characterisation for many operating points is often prohibitive due to long simulation times, in particular if a dense grid is expected for high precision. We therefore propose to limit the analysis to only a few cells, representing a distribution of cells commonly found in a large design. The most significant reduction in characterisation time can be achieved by dropping sequential cells from the library. These need to be characterised for setup and hold constraints which comes with the need of extensive sweeps. With non-sequential cells accountable for the majority of the delay in the critical path of a typical design, the effect of potential scaling differences between sequentials and non sequentials can be considered negligible.

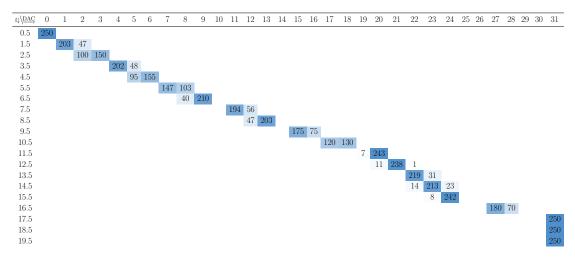

To select a representative subset of cells, a purely combinatoric 32 bit multiplier was synthesized with RTL compiler, constrained to a maximum delay of zero from all inputs to all outputs. The cell distribution was extracted, rarely used cells where pruned, and the circuit was resynthesized using only the top thirteen cells, which cover over 90% of the cells in the original design. This pruning approach reduced the simulation time of our characterisations from slightly short of two hours to less than three minutes, allowing to characterize 55 points across three process corners and five temperatures on a single machine over a weekend. Finally, leakage, dynamic power as well as the frequency can be extracted for the reference design after re-synthesis with only the selected cells.

#### 3.3.2 MEP for the 32 Bit Multiplier Reference Design

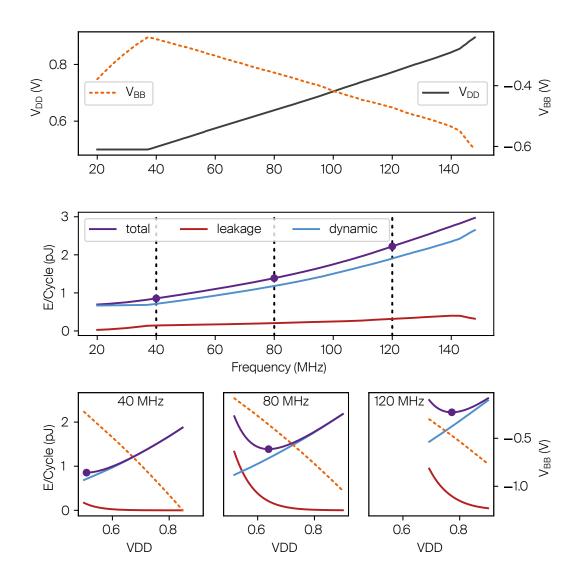

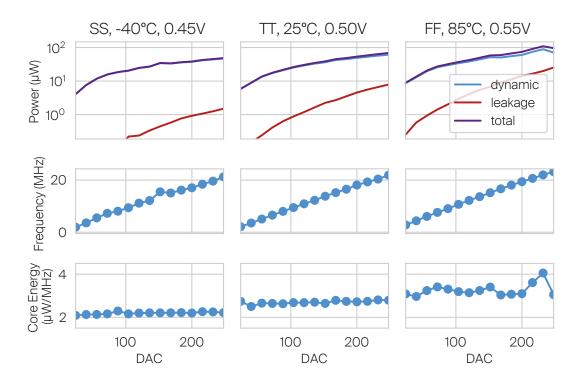

Using interpolation, we can now approximate the dynamic and leakage power across the whole ASVBB design space, which allows us to find the MEP for the operating modes of interest. Figure 3.2 shows the tradeoffs for the multiplier reference design, tracing the minimum energy point across the range of target frequencies from 20 MHz to 140 MHz. On the low end, the minimum supply voltage of our design space is the limiting factor, with the bias as far reverse as possible to still reach the frequency. Subsequently only the bias increases until an inflection point is reached around 50 MHz where the supply voltage starts to increase, causing an inversion of the bias effectively reducing the leakage. At the 80 MHz frequency cut, the typical MEP curve is formed, with the higher forward bias at low supply voltage causing the leakage energy to dominate below 0.6 V and the dynamic energy dominating at a higher supply. At the 120 MHz frequency cut, the design space is limited again, with the speed not being reachable at a supply voltage below 0.7 V.

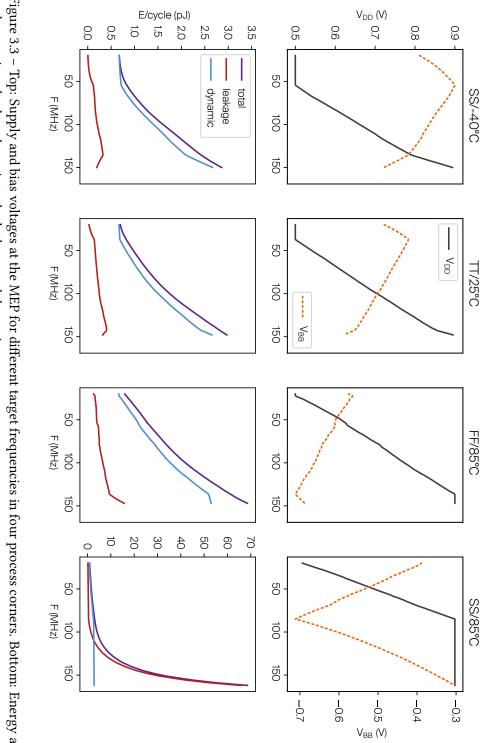

Similarly, Fig. 3.3 shows the shift of the MEP across frequency for different process corners,

Figure 3.2 – Top: The bias and supply voltage pairs for minimum energy across frequency at TT/25  $^{\circ}$ C. Center: The corresponding leakage and dynamic Energy components. Bottom: minimum energy curves for the three marked frequency cuts in the center plot.

at these points, broken down into the leakage and dynamic components. Figure 3.3 - Top: Supply and bias voltages at the MEP for different target frequencies in four process corners. Bottom: Energy across frequency

when adjusting both bias and supply voltage for minimum energy at each frequency step. Note that, as long as a tradeoff exists, the absolute energy values for MEP are almost constant over PT for constant frequency, as the same  $I_{ON}$  results in the same dynamic energy while the leakage is kept under control. However, when the edge of the design space is reached as illustrated by the SS/85 °C case in Fig. 3.3 only biasing remains for frequency adjustment causing the leakage to explode.

# 3.4 Scaling the Reference Circuit to an Arbitrary Design

Obviously, the MEP and the associated optimal supply voltage and body bias are highly design dependent since the share between leakage and dynamic energy is determined by the activity and the critical path length [39]. Hence the analysis has to be done for each design as well as for each utilisation profile. We propose to use the small reference design with a limited number of cells to calibrate a model that can then be used to extract the MEP and the associated ASVBB settings for different target frequencies. In the following we discuss the corresponding scaling model.

#### 3.4.1 ADVBB Model

The per cycle energy of a design can be split into the sum of the dynamic contribution  $E_{dyn}$  and the leakage contribution  $E_{leak}$  so that  $E_{tot} = E_{dyn} + E_{leak}$ . The two energy components are obtained with the following first order approximations in which  $\alpha_{sw}$  denotes the design specific switching activity,  $C_L$  the total load capacitance,  $I_{OFF}$  the leakage current,  $V_{DD}$  the supply voltage, and  $t_p$  the cycle time:

$$E_{dyn} = \alpha_{sw} \cdot C_L \cdot V_{DD}^2 \tag{3.4}$$

$$E_{leak} = V_{DD} \cdot I_{OFF} \cdot t_p. \tag{3.5}$$

The dynamic energy ratio  $r_{dyn}$  between the dynamic energy of the target design  $E_{dyn}^{target}$  and the dynamic energy of the reference design design  $E_{dyn}^{ref}$  is defined as

$$r_{dyn} = \frac{E_{dyn}^{target}}{E_{dyn}^{ref}} = \frac{\alpha_{sw}^{target} \cdot C_{tot}^{target}}{\alpha_{sw}^{ref} \cdot C_{tot}^{ref}}, \tag{3.6}$$

where  $\alpha_{sw}^{target}$ , and  $C_{tot}^{target}$  as well as  $\alpha_{sw}^{ref}$ , and  $C_{tot}^{ref}$  denote the load and activity of the target and reference design, respectively.

Similarly, we define the leakage energy ratio between the leakage of the target design  $E_{target}^{ref}$

and the leakage of the reference design  $E_{leak}^{ref}$  as

$$r_{leak} = \frac{E_{leak}^{target}}{E_{leak}^{ref}} = \frac{g_{target} \cdot \overline{I_{OFF}^{target}} \cdot t_p^{target}}{g_{ref} \cdot \overline{I_{OFF}^{ref}} \cdot t_p^{ref}}$$

(3.7)

The precise off currents  $I_{OFF}^{target}$  and  $I_{OFF}^{ref}$  depend on the threshold voltage  $V_t$  which is a function of  $V_{bb}$  and the specific schematics of the gates used. However, the off currents of larger circuits can be approximated well by the number of gates  $g_{target}$  and  $g_{ref}$  and the average cell leakage currents  $\overline{I_{OFF}^{target}}$  and  $\overline{I_{OFF}^{target}}$  in the two designs. In fact, our results will show that with a sufficiently representative reference design, with reasonable constraints and a comparable cell distribution to the target design we can assume  $\overline{I_{OFF}^{target}} \approx \overline{I_{OFF}^{ref}}$  across the full range of supply and bias conditions to justify

$$r_{leak} = \frac{g_{target} \cdot t_p^{target}}{g_{ref} \cdot t_p^{ref}}.$$

(3.8)

While the *minimum* cycle times  $t_p^{target}$  and  $t_p^{ref}$  in (3.8) depend on  $V_{DD}$  and  $V_{bb}$ , we note that we are only interested in optimizing for a given cycle time  $t_p^{target}$  for the target design. Further, the cycle time  $t_p^{ref}$  for the reference design at the characterization points is anyway known. Hence, the scaling of the reference design in (3.7) and (3.8) becomes independent from  $V_{DD}$  and  $V_{bb}$  which is the foundation for the subsequent target-design specific optimization.

# 3.4.2 Finding the MEP for a Constant Frequency

To scale the reference design dynamic and leakage characteristics to the target design, the latter is first synthesized at any valid  $V_{DD}$  and  $V_{bb}$  combination for the desired target frequency. At this point we then extract its dynamic and the leakage energy and compute the corresponding scaling factors  $r_{dyn}$  and  $r_{leak}$  relative to the reference design at the same supply and bias voltages. With  $r_{dyn}$  and  $r_{leak}$  only depending on design specific properties, they can be used to directly scale the dynamic and leakage energy from the reference design for any other point in the iso-frequency design space.

$$E_{target}(V_{dd}, V_{bias}) \approx r_{leak} \cdot E_{leak}^{ref}(V_{dd}, V_{bias})$$

$$+ r_{dyn} \cdot E_{dyn}^{ref}(V_{dd}, V_{bias})$$

(3.9)

A straightforward exhaustive search based on (interpolated) characterization data from the reference design yields the MEP  $\min\{E_{target}(V_{DD},V_{bb})\}$  and the corresponding voltages.

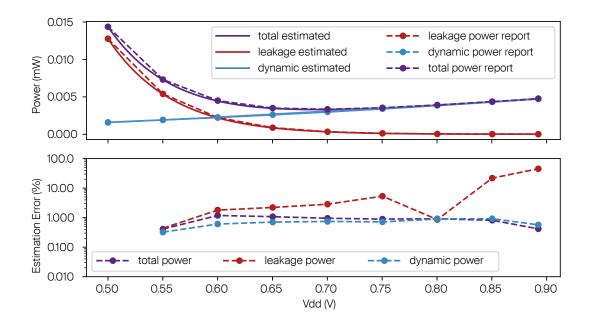

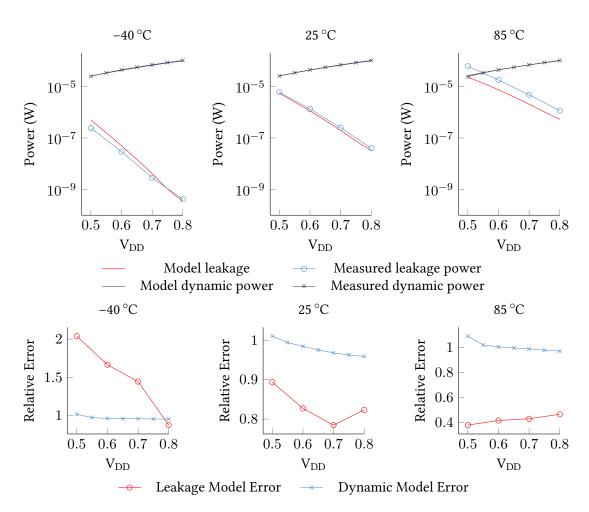

Figure 3.4 – 32 Bit RISC processor: Constant frequency power estimation based on the 32 bit multiplier reference design vs. power report of the design at a given point (circle).

# 3.5 Case Study: 32 Bit Microprocessor

Our target design is a 32 bit RISC microprocessor, synthesized for a relaxed clock of 8 MHz in order to allow for a sufficiently large design space.

#### 3.5.1 Modelling Accuracy

First, we evaluate the accuracy of the scaling approach. The microprocessor is implemented at 0.5 V with forward bias to achieve the target frequency. The leakage and dynamic power are extracted and the scaling factors are derived. At constant frequency, the supply/bias tradeoff power curve is then sampled in 50 mV steps at which the full library is charcterized in order to allow for power reports. This curve is shown in Fig. 3.4. The circles denote the energy derived from the power reports and the contineous solid lines denote the estimate based on the scaled ASVBB model. The error in terms of total energy is on the order of 1% over the full voltage range (for a constant frequency). Only the error on leakage increases as the design shifts towards higher supply voltages. However, in these operating points, the leakage impact on the total power becomes negligible as dynamic energy dominates the total power. The leakage mismatch is likely due to numeric effects or lack of precession when reporting.

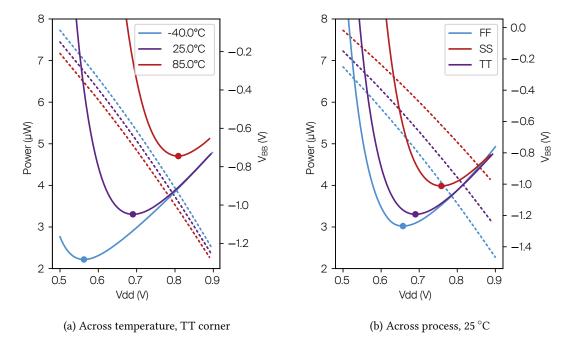

Figure 3.5 – Power estimation for the 32 bit RISC processor when sweeping the supply voltage across a constant frequency trajectory, trading of supply voltage against bias. Solid: power curves. Dashed: the corresponding body bias  $V_{BB}$ .

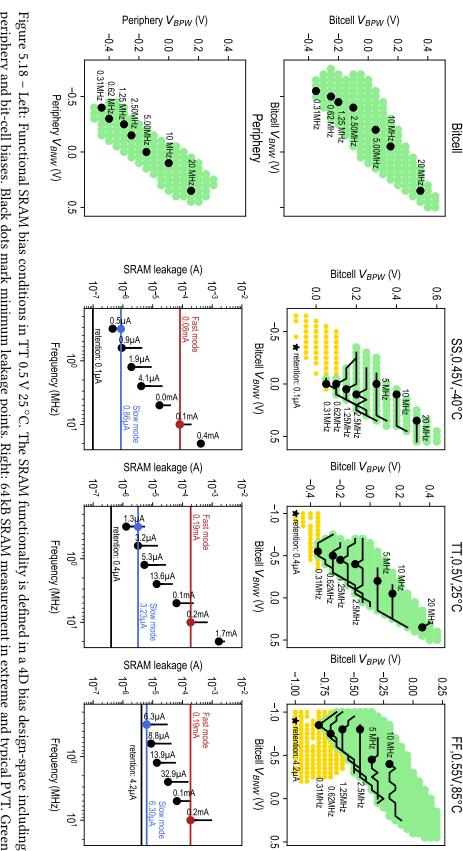

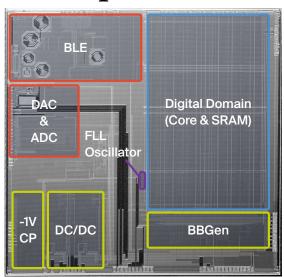

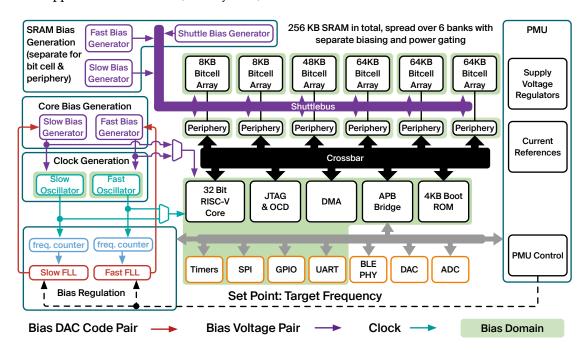

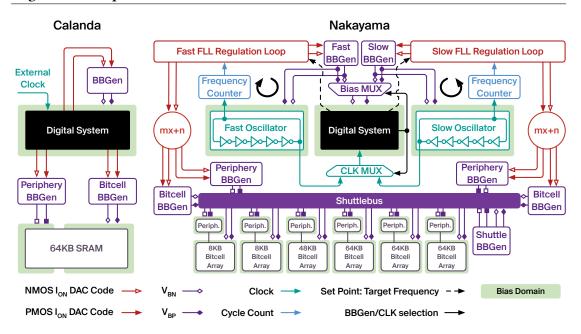

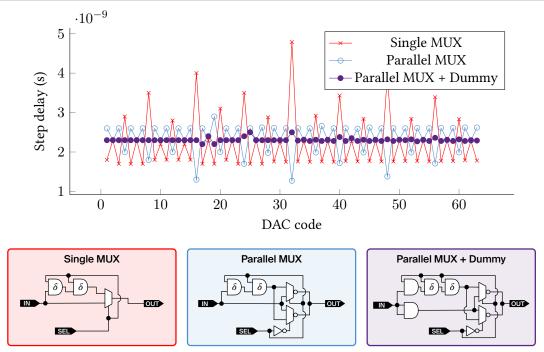

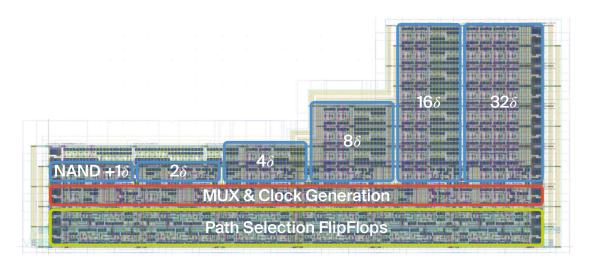

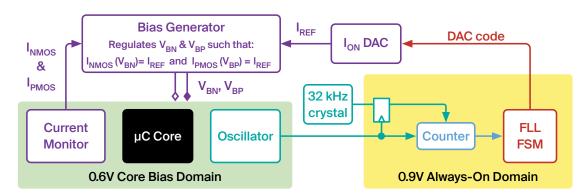

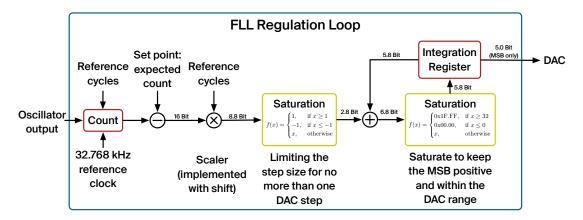

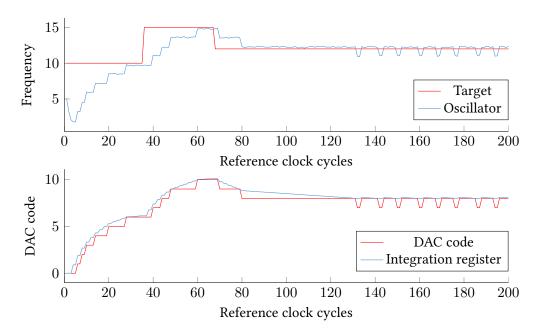

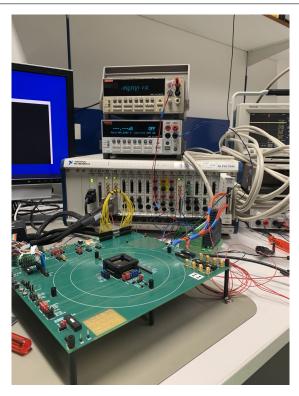

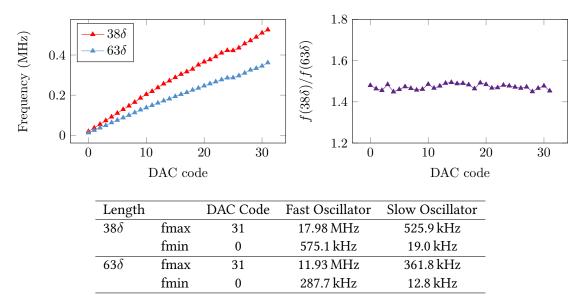

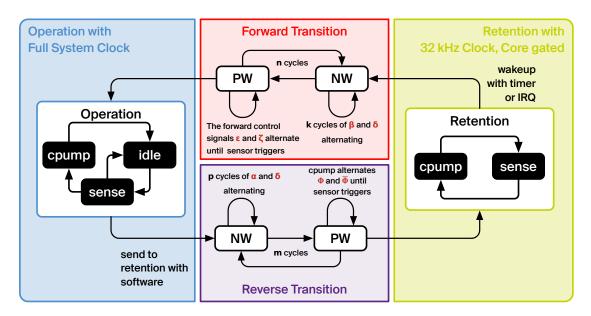

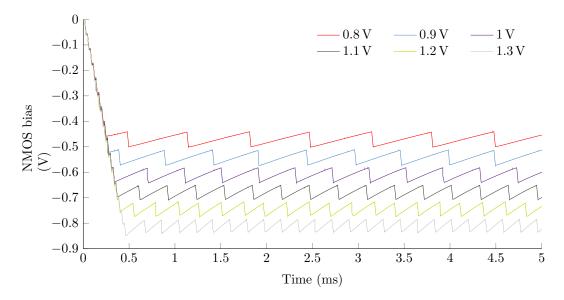

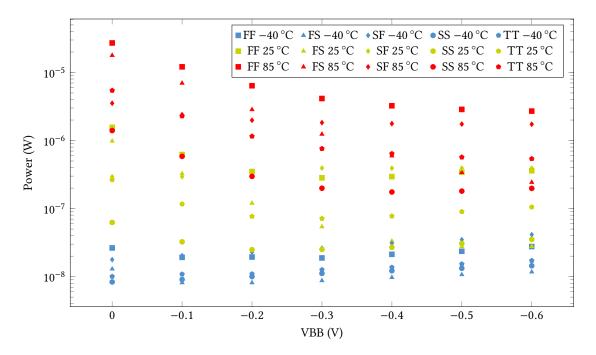

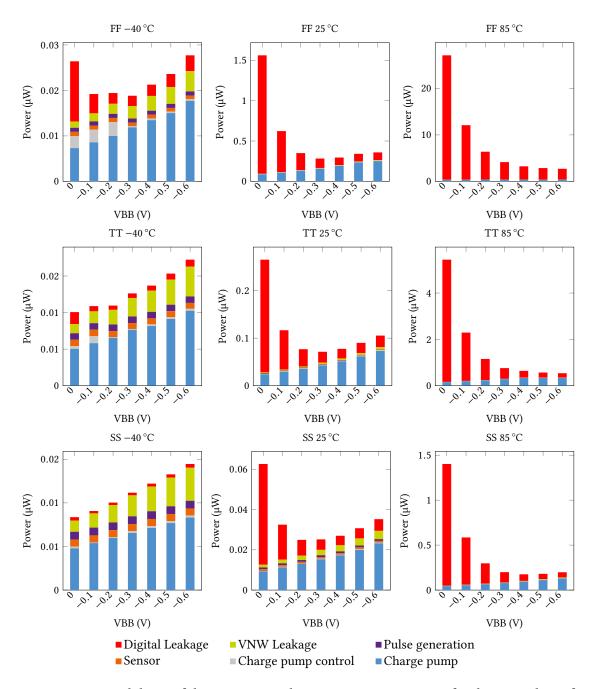

# 3.5.2 Process and Temperature Effects