Thèse n° 8231

# EPFL

# Direct time-of-flight SPAD image sensors for light detection and ranging

Présentée le 15 janvier 2021

à la Faculté des sciences et techniques de l'ingénieur Laboratoire d'architecture quantique Programme doctoral en microsystèmes et microélectronique

pour l'obtention du grade de Docteur ès Sciences

par

### Preethi PADMANABHAN

Acceptée sur proposition du jury

Prof. D. Atienza Alonso, président du jury Prof. E. Charbon, directeur de thèse Dr D. Stoppa, rapporteur Dr J. Hurwitz, rapporteur Prof. A. P. Burg, rapporteur

École polytechnique fédérale de Lausanne

2021

Thinking should become your capital asset, no matter whatever ups and downs you come across in your life. — A. P. J. Abdul Kalam

## Acknowledgements

It definitely feels like time flew in the blink of an eye as this journey towards finishing a PhD is coming to an end. This journey would not be as fruitful and rewarding if it was not for the many wonderful people I met. Their help and support cannot be quantified, however, I would like to express it here as my memento in writing.

I would like to express my gratitude to my advisor, Prof. Edoardo Charbon, without whom I would not have embarked on this journey. For giving me this excellent opportunity to work on challenging, yet exciting projects, I will always be grateful. I will be thankful for the freedom he gave to explore bold ideas which helped broaden my own creativity as a designer.

At this point, I would like to express my heartfelt gratitude to Dr. Claudio Bruschini. Although, he was not officially part of my PhD project, he still ensured to keep in touch with my research regularly. Next, I would like to thank Dr. Shouleh Nikzad and Dr. Bruce Hancock from NASA's JPL where I had also previously interned. I spent early months of my PhD characterizing a readout circuit I had designed for their GaN detectors. Many thanks go to Shouleh who ensured I had a thoroughly enriching experience throughout the project timeline. I would like to thank Bruce for his valuable insights on circuit design, from theory to practice, all of which helped me approach problems systematically.

Special mention and my huge thanks will go to those colleagues of mine with whom I spent a lot of time during my PhD. From my Master thesis up until 2 years of my PhD, I worked with Augusto Ximenes. I co-designed my first DTOF sensor along with him. I am grateful to him for helping me kick-start on that project, to show me what a good layout was and also for being available to hold interesting discussions on design. My next heartfelt gratitude goes to Chao Zhang, who had a significant contribution in my entire PhD. I have had the most interesting discussions with him on aspiring to design the next-best DTOF sensor. His calm demeanor even when time-crunched always inspired me. I cannot forget how he spotted a calibration error, just moments before submitting our work to a conference and also ended up fixing it without panicking. I learnt a lot of digital design from him. He has been involved in my first and last projects and provided me the best possible co-working experience. Next, I would like to thank Marco Cazzaniga for his timely help in the implementation of the TDC in my second sensor and as well, for his patience and calmness throughout our collaboration. I would like to thank Baris Can Efe for helping me out during the measurement of my last chip.

Augusto Carimatto, another colleague of mine, once told me, 'You don't expect your colleagues to become your friends. But if they do, its a bonus!' Well, I was glad to receive that bonus and Augusto Carimatto became my first friend in the lab. I am always motivated by his ever-positive attitude,

#### Acknowledgements

famous laughter and experienced insights on digital design.

I would like to thank Scott Lindner for the interesting discussions we've had on a wide range of topics – from as technical as biasing a pixel circuit to as socially relevant as literacy. I will always be grateful for the time he offered to brainstorm along with me during the debug of my most recent sensor. For the nights singing karaoke in Hiroshima and Snowbird to hopping places looking for good food, I'd like to thank him for his company inside and outside of work.

Thanks to all the wonderful colleagues, PhD became an enjoyable journey even during challenging times. When I started out in Delft, I was the only girl in the lab, not that I was complaining, in fact I had the best times in Delft. But soon after Andrada Muntean, joined our lab, it definitely felt like a team. Together with Andrei Ardelean, we went restaurant-hunting in Switzerland, especially in the last days of my PhD. I wish to thank them both for the lovely times in Neuchâtel, inside and outside of work. I would like to thank Pouyan Keshavarzian for his significant contribution in helping me compile content for the Image Sensor Europe conference. I remember he had just joined the lab and he enthusiastically agreed to help me with the slides. I would like to thank Jad Benserhir for helping me write the French translation of the abstract.

I would like to thank Michel Antolovic for being a great office mate. His calm attitude and timemanagement skills will always inspire me. I would like to thank Esteban Venialgo for being a great colleague as well as for introducing me to soccer table. I will always reminisce the fun times of our trip to Stockholm with all other lab members.

I would also like to express my thanks to the past and current members of AQUA lab who have contributed to my work in a way or another- Arin Ülkü, Andrea Ruffino, Francesco Gramuglia, Kazuhiro Morimoto, Bedirhan Ilik, Jiuxuan Zhao, Ming-Lo Wu, Ekin Kizilkan, Utku Karaca, Simone Frasca, Paul Mos, Samuel Burri, Feng Liu and, Emanuele Ripiccini. I would like to express my warmest gratitude to Brigitte Khan, who kindly took care of all the administrative and organizational issues for us, making it smooth sail during the entire PhD. For as well inspiring conversations on Yoga and life, for insisting that I take breaks out of my work, I will be very thankful to her.

I would like to thank all the research institutes and companies I happened to collaborate with during the timeline of my PhD which opened up various opportunities and thereby, added value to my projects. I would like to thank the jury of my thesis- Prof. Andreas Burg, Prof. David Atienza, Dr. David Stoppa, Dr. Jed Hurwitz, for their time and valuable feedback on my thesis.

I would like to thank my friends outside of lab – Sukanya, Chethana, Nithin, Mohit, Shravan, Sangram, Maneesha, Kunal, and, Harshal, who despite their individual pressures, helped me relax and stay distracted outside of work. I would like to thank my remote friends- Rahul, Uday, and, Priyanka for standing by me and encouraging me at all times.

Finally and most importantly, I would like to thank my family- my mom and my best friend, Anu, for her unconditional support, my brother, Balaji, for being there to motivate me and, my father for the tolerance he indirectly taught me. My mom's unshakeable strength and my brother's humor are daily fuel to my survival. Staying very far from them, I carry various life lessons that help me take on challenges while I hope to reunite with them soon.

Neuchâtel, December 15, 2020

Preethi Padmanabhan

# Abstract

Depth sensing is an increasingly important feature in many applications of consumer, automotive, augmented/virtual reality (AR-VR), space and bio-medical imaging. Long range, high depth resolution, high spatial resolution, and high frame rates are often conflicting requirements and difficult to be simultaneously achieved due to extreme operating conditions. Direct time-of-flight (DTOF) has evolved to becoming a powerful technique to perform light detection and ranging (LiDAR). Thanks to advances in low-jitter optical detectors, such as single-photon avalanche diodes (SPADs), and accurate chronometers like time-to-digital converters (TDCs), picosecond timing resolution is possible, thus enabling millimetric depth resolutions.

High ambient light is an inevitable challenge in LiDAR applications, whose levels may exceed up to 100 klux on a bright sunny day, making it particularly challenging to detect a target submerged within an overwhelming noise floor. High ambient light operation can be accommodated by means of optical filtering, a higher laser power or temporal filtering techniques. Optical filtering is often restricted to a narrow, 10-50 nm bandwidth, insufficient at high ambient light levels. Higher laser power is not always possible, due to eye safety regulations and power constraints. Temporal filtering such as time gating and coincidence detection can thus be powerful tools to cope with high ambient light.

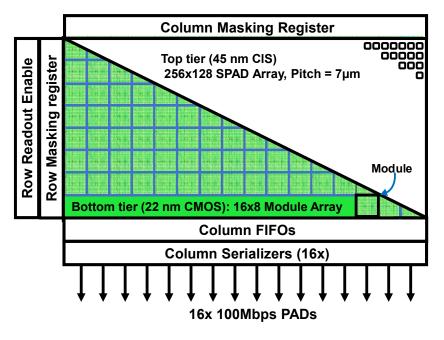

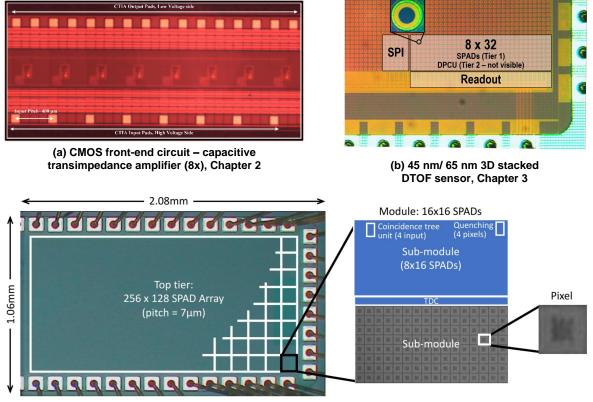

This thesis focuses on the design of DTOF sensors for LiDAR. To that end, two SPAD-based DTOF sensors are designed. The first sensor is designed in a 3D-stacked 45/65 nm CMOS technology, thus, enabling a modular architecture where the module itself comprises of 8×16 pixels. With a 60 ps-resolution TDC at its core, the sensor provides centimetric accuracy up to 300 m range in free space. The second sensor, named *Jatayu*, advances the previous design by hosting 256×128 pixels, thereby, significantly improving on its spatial resolution. While retaining its modularity, *Jatayu* also enables multi-level coincidence detection and progressive time-gating to suppress background light. To the best of the author's knowledge, progressive gating has been implemented in a LiDAR for the first time in this thesis. Designed in a 3D-stacked 45/22 nm CMOS technology, the sensor achieves under 7 cm accuracy over 100 m ranging and 10 klux background light. With its capability of acquiring 128×128, 3D depth maps of high dynamic range scenes, *Jatayu* is highly suitable for a variety of imaging applications in many different scenarios.

Key words: LiDAR, depth sensing, time-of-flight (TOF), CMOS image sensors, single-photon avalanche diode (SPAD), background illumination reduction, coincidence detection, progressive gating

## Résumé

La détection en profondeur s'avère importante dans différentes applications : de l'automotive, réalité augmentée et virtuelle (AR et VR), le spatial ainsi que l'imagerie biomédicale. Longue portée, haute définition spatiale ainsi que fréquences d'images élevées sont souvent difficiles à atteindre simultanément vu les conditions de fonctionnement extrêmes. Répondant aux exigences de la résolution de la portée et de la profondeur, l'imagerie à résolution temporelle et, en particulier, le temps de vol direct (DTOF) a évolué pour devenir une puissante technique de détection et de télémétrie de la lumière (LiDAR). Un capteur DTOF se compose d'une source d'éclairage pulsée telle qu'un laser, éclairant une cible d'intérêt et les photons réfléchis rebondissant sur la cible sont ensuite horodatés par des détecteurs optiques. Grâce aux avancées en matière de détecteurs optiques à haute précision, tels que les diodes d'avalanche mono-photon (SPADs), et les chronomètres précis comme les convertisseurs temps-numérique (TDCs), la résolution de synchronisation picoseconde est possible, permettant ainsi des résolutions de profondeurs millimétriques. La lumière ambiante élevée est un défi inévitable dans les applications LiDAR, dont les niveaux peuvent dépasser 100 klux pendant une journée ensoleillée, ce qui rend particulièrement difficile la détection d'une cible immergée dans un plancher sonore accablant. La détection en présence de lumière de fond élevée peut être atténuée par des moyens de filtrage optique, une puissance laser plus élevée ou des techniques de filtrage temporel. Le filtrage optique est souvent limité à une bande passante étroite de 10 à 50 nm, insuffisante à des niveaux de lumière ambiante élevés. Une puissance laser plus élevée n'est pas toujours possible, en raison de la réglementation sur la sécurité oculaire et contraintes de puissance. Le filtrage temporel comme la synchronisation temporelle et la détection de coïncidences peuvent être des outils puissants pour faire face à la lumière ambiante élevée. Cette thèse se concentre sur la conception de capteurs DTOF qui maintiennent les exigences LiDAR à l'avant-garde tout en faisant progresser l'état de l'art. À cette fin, deux capteurs DTOF basés sur SPAD sont conçus. Le premier capteur est conçu dans une technologie CMOS 3D empilée de 45/65 nm, permettant ainsi une architecture modulaire où le module lui-même se composait de 8×16 pixels. Avec une résolution de 60 ps TDC à son centre, le capteur fournit une résolution de profondeur centimétrique tout en démontrant jusqu'à 300 m de télémétrie dans l'espace libre. Le second capteur, nommé Jatayu, fait progresser la conception précédente en implementant 256×128 pixels, améliorant considérablement sa résolution spatiale. Tout en conservant sa modularité, Jatayu permet également la détection de coïncidences multi-niveaux et la synchronisation temporelle progressive pour supprimer de l'illumination de fond. À la connaissance de l'auteur, la mise en œuvre progressive de la synchronisation est la première à être effectuée pour un scénario LiDAR au sein de cette thèse. Conçu dans une technologie CMOS empilée en 3D de 45/22 nm, le capteur

#### Résumé

atteint une précision inférieure à 7 cm sur une portée de 100 m et une lumière de fond de 10 klux. Avec sa capacité à acquérir 128×128, des cartes de profondeur 3D de scènes à plage dynamique élevée, *Jatayu* est parfaitement adapté à une variété d'applications d'imagerie dans de nombreux scénarios différents.

Mots clés : LIDAR, Détection de profondeur, temps de vol (TOF), capteurs d'image CMOS, diode avalanche mono-photonique (SPAD), réduction du bruit de fond, détection des coïncidences, synchronisation progressive.

# Contents

| Ac | knov  | wledgements                                             | i    |

|----|-------|---------------------------------------------------------|------|

| At | ostra | ct (English/Français)                                   | iii  |

| Li | st of | Figures                                                 | xi   |

| Li | st of | Tables                                                  | xvii |

| 1  | Intro | oduction                                                | 1    |

|    | 1.1   | Time-resolved imaging                                   | 1    |

|    | 1.2   | Time-of-flight (TOF) for LiDAR                          | 1    |

|    | 1.3   | LiDAR application challenges                            | 5    |

|    |       | 1.3.1 Background noise suppression                      | 5    |

|    |       | 1.3.2 Optical power budget and safety regulations       | 5    |

|    |       | 1.3.3 Laser interference                                | 6    |

|    |       | 1.3.4 High-dynamic range scenes                         | 6    |

|    |       | 1.3.5 Adverse weather phenomena                         | 7    |

|    |       | 1.3.6 Detector sensitivity                              | 7    |

|    |       | 1.3.7 Improving timing statistics                       | 9    |

|    |       | 1.3.8 Data rate                                         | 10   |

|    | 1.4   | LiDAR implementation- scanning vs. flash                | 10   |

|    | 1.5   | Thesis contributions                                    | 11   |

|    | 1.6   | Thesis organization                                     | 12   |

| RE | EFER  | RENCES                                                  | 14   |

| 2  | Dete  | ector technologies                                      | 19   |

|    | 2.1   | III-Nitride semiconductor detector technology           | 19   |

|    | 2.2   | CMOS interface circuit design                           | 21   |

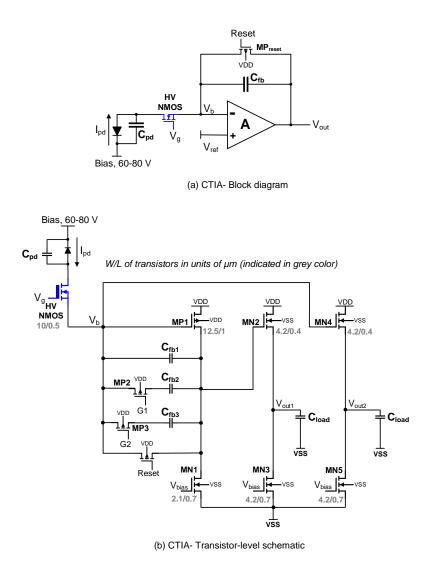

|    |       | 2.2.1 Capacitive Transimpedance Amplifier (CTIA)        | 22   |

|    |       | 2.2.2 Design challenge- high bias voltage and quenching | 23   |

|    |       | 2.2.3 Noise analysis                                    | 26   |

|    | 2.3   | Measurement results                                     | 27   |

|    |       | 2.3.1 CTIA characterization results                     | 28   |

|    |      | 2.3.2 GaN + CMOS measurement results- demonstration of UV sensitivity | 32 |

|----|------|-----------------------------------------------------------------------|----|

|    |      | 2.3.3 Noise measurement                                               | 33 |

|    | 2.4  | Next-generation readout improvements                                  | 35 |

|    |      | 2.4.1 Hybrid integration of GaN APDs                                  | 36 |

|    | 2.5  | Geiger mode APD- a single photon detector                             | 37 |

|    | 2.6  | SPADs implemented in 3D stacked technology                            | 39 |

|    |      | 2.6.1 3D stacked SPADs in 45 nm BSI CIS technology                    | 39 |

|    |      | 2.6.2 From individual SPAD detectors to functional pixels             | 42 |

|    | 2.7  | Conclusions                                                           | 45 |

| RE | EFER | ENCES                                                                 | 46 |

| 3  | Res  | ource sharing in DTOF sensors                                         | 49 |

|    | 3.1  | Per-pixel and shared architectures                                    | 49 |

|    |      | 3.1.1 Power consumption in shared architectures                       | 50 |

|    |      | 3.1.2 Sensitivity and saturation                                      | 52 |

|    | 3.2  | A shared approach towards a DTOF sensor                               | 54 |

|    |      | 3.2.1 Decision tree                                                   | 55 |

|    |      | 3.2.2 Time-to-digital converter (TDC)                                 | 56 |

|    |      | 3.2.3 Digital processing and communication unit (DPCU)                | 59 |

|    |      | 3.2.4 Laser signature                                                 | 61 |

|    | 3.3  | Characterization results                                              | 62 |

|    |      | 3.3.1 SPAD characterization                                           | 63 |

|    |      | 3.3.2 Depth measurements                                              | 63 |

|    |      | 3.3.3 Laser signature                                                 | 65 |

|    |      | 3.3.4 3D image reconstructions                                        | 66 |

|    | 3.4  | Challenges with decision-tree based DTOF sensor                       | 69 |

|    |      | 3.4.1 Analytical model of a DTOF Sensor in a flash LiDAR              | 69 |

|    | 3.5  | Conclusions                                                           | 75 |

| RE | EFER | ENCES                                                                 | 77 |

| 4  | Coiı | ncidence-based noise-resilient DTOF sensor                            | 79 |

|    | 4.1  | Overview– coincidence detection                                       | 79 |

|    | 4.2  | Proposed DTOF sensor based on coincidence                             | 80 |

|    | 4.3  | Simulation results                                                    | 85 |

|    |      | 4.3.1 Single-point ranging                                            | 85 |

|    |      | 4.3.2 3D imaging with wide dynamic range targets                      | 89 |

|    |      | 4.3.3 3D imaging and multiple timestamping                            | 93 |

|    |      | 4.3.4 3D imaging and time-gating                                      | 94 |

|    | 4.4  | Conclusions                                                           | 96 |

| RE | EFER | ENCES                                                                 | 98 |

#### Contents

| 5   | A 25                            | 6×128 DTOF sensor with coincidence detection and progressive gating | 99  |  |

|-----|---------------------------------|---------------------------------------------------------------------|-----|--|

|     | 5.1                             | Mutually-coupled TDC array                                          | 99  |  |

|     |                                 | 5.1.1 Non-linear modeling                                           | 101 |  |

|     |                                 | 5.1.2 SPICE-compatible model                                        | 105 |  |

|     | 5.2                             | Mutually-coupled TDC array                                          | 107 |  |

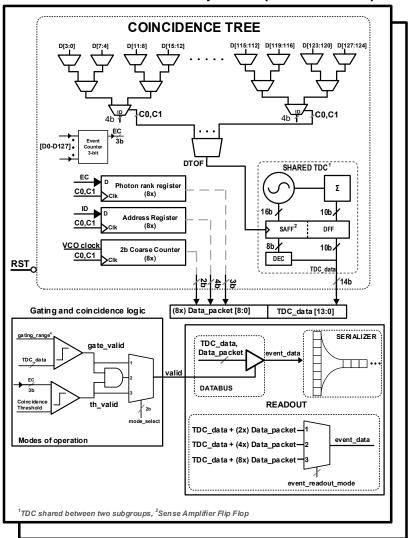

|     | 5.3                             | Jatayu – A 256×128 DTOF sensor for flash LiDAR                      | 112 |  |

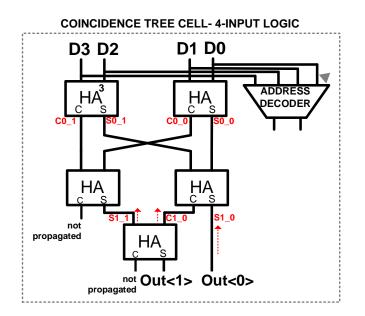

|     | 5.4                             | Coincidence tree cell                                               | 115 |  |

|     | 5.5                             | Coarse counter (CC)                                                 | 116 |  |

|     | 5.6                             | Progressive gating control                                          | 117 |  |

|     | 5.7                             | Time-to-digital-converter (TDC)                                     | 119 |  |

|     | 5.8                             | Characterization results                                            | 120 |  |

|     |                                 | 5.8.1 Single-point ranging and linearity                            | 122 |  |

|     |                                 | 5.8.2 Gating measurement                                            | 123 |  |

|     |                                 | 5.8.3 Flash LiDAR measurements                                      | 124 |  |

|     |                                 | Power consumption                                                   | 125 |  |

|     |                                 | State-of-the-art comparison                                         | 126 |  |

|     | 5.11                            | Conclusions                                                         | 128 |  |

| RE  | FER                             | ENCES                                                               | 129 |  |

| 6   | Con                             | clusions and future work                                            | 131 |  |

|     | 6.1                             | Conclusions                                                         | 131 |  |

|     | 6.2                             | Recommendations for future work                                     | 133 |  |

| Cł  | nip ga                          | illery                                                              | 135 |  |

|     |                                 |                                                                     | 137 |  |

| Lis | List of publications and awards |                                                                     |     |  |

| At  | About the author 1              |                                                                     |     |  |

| 1.1  | Classification of optical depth sensing techniques.                                           | 2  |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.2  | Conceptual representation of ITOF sensors- (a) Modulated ITOF and (b) Pulsed ITOF.            | 3  |

| 1.3  | High-level block diagram of a DTOF sensing system                                             | 4  |

| 1.4  | Laser interference scenario- Pictorial representation with two LiDAR systems with             |    |

|      | Lambertian targets as example.                                                                | 7  |

| 1.5  | Comparison of imager architectures- (a) 2D array, per-pixel architecture, (b) column-         |    |

|      | parallel architecture and (c) 3D-stacked architecture.                                        | 8  |

| 1.6  | PDP comparison of state-of-the-art back-illuminated SPADs [45]                                | 9  |

| 1.7  | Flash vs. scanning LiDAR conceptual representation.                                           | 10 |

| 2.1  | Device geometry of a GaN APD used [5];                                                        | 20 |

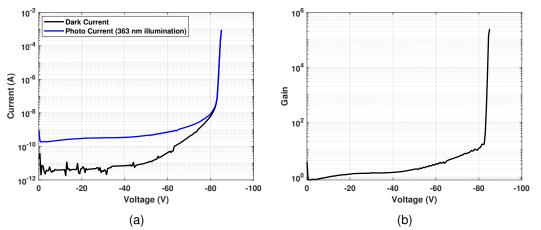

| 2.2  | GaN APDs developed at JPL : typical I–V characteristics (a) and (b) avalanche gain            |    |

|      | (redrawn from [5])                                                                            | 20 |

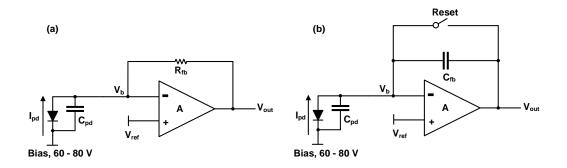

| 2.3  | (a) Resistive transimpedance amplifier (RTIA); and (b) capacitive transimpedance              |    |

|      | amplifier (CTIA).                                                                             | 21 |

| 2.4  | CTIA block diagram.                                                                           | 22 |

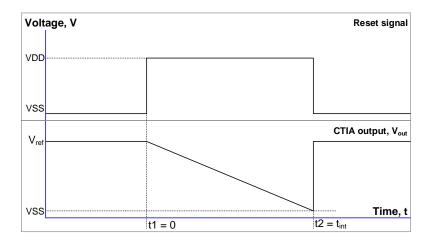

| 2.5  | CTIA typical waveforms                                                                        | 23 |

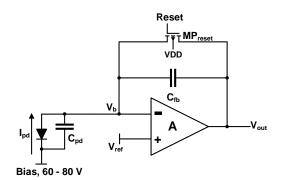

| 2.6  | (a) CTIA block diagram with HV NMOS transistor; and (b) CTIA transistor-level                 |    |

|      | schematic.                                                                                    | 24 |

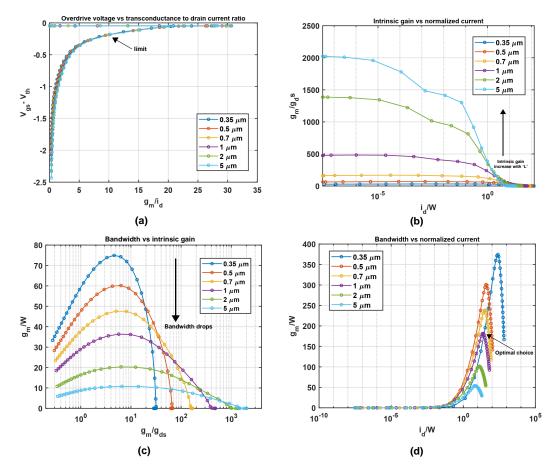

| 2.7  | Simulation results- PMOS transistor characterization over increasing length, L; used          |    |

|      | for appropriate sizing of transistors in Figure 2.6b.                                         | 25 |

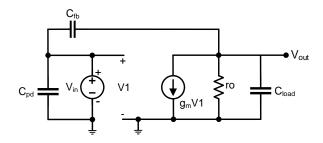

| 2.8  | CTIA small-signal model- PMOS input transistor                                                | 27 |

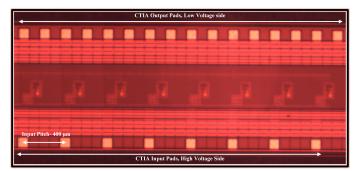

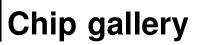

| 2.9  | Chip photomicrograph: Eight CTIA unit cells can be identified with their input pads on        |    |

|      | the bottom side and output pads on the top.                                                   | 28 |

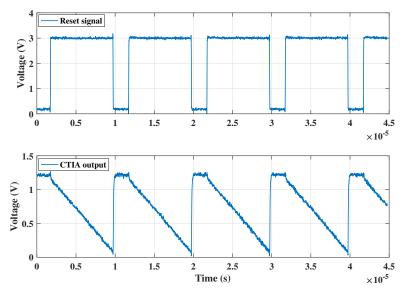

| 2.10 | Typical CTIA operation: Reset signal and CTIA output voltage waveforms                        | 28 |

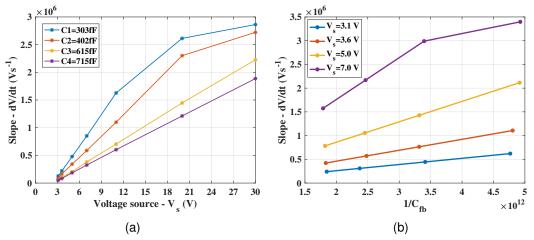

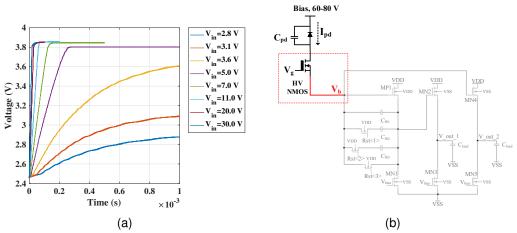

| 2.11 | CTIA transient behavior : (a) slope versus voltage source, $V_s$ ; and (b) slope versus       |    |

|      | 1/C <sub>fb</sub>                                                                             | 29 |

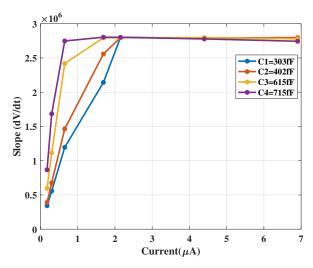

| 2.12 | CTIA slope under higher input currents                                                        | 30 |

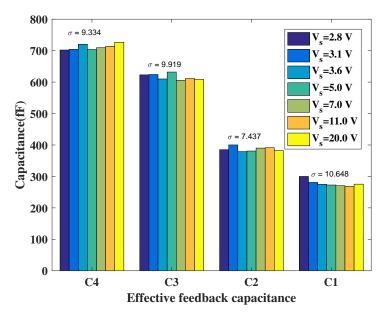

| 2.13 | Variation in measured feedback capacitances (labels as mentioned in Section 2.2.2)            | 31 |

| 2.14 | Voltage limiting functionality: (a) rise in the CTIA input node V <sub>b</sub> ; and (b) CTIA |    |

|      | schematic- input node, V <sub>b</sub> , highlighted.                                          | 32 |

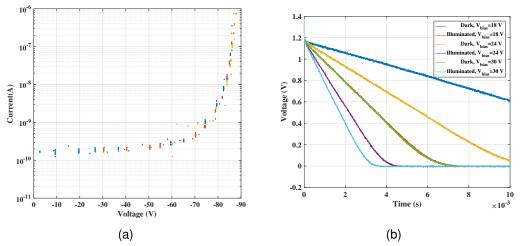

| 2.15 | Characteristics of GaN sensor obtained using the CMOS readout circuit : (a) extracted         |    |

|      | I–V curve of a GaN APD; and (b) CTIA oscilloscope waveforms.                                  | 32 |

|      |                                                                                               |    |

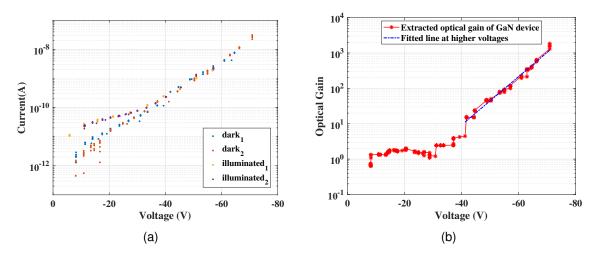

| 2.16 | GaN sensor characteristics under UV illumination. (a) It can be seen that, for lower voltages, the dark current is lower than the photocurrent by a factor of 10, while, for higher voltages (>40 V), the dark current also increases as the APD starts |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | avalanching. This characteristic is similar to results shown in Figure 2.2b. (a) $I-V$                                                                                                                                                                  |     |

|      | curve under UV illumination; and (b) optical gain estimated from Figure 2.16a                                                                                                                                                                           | 33  |

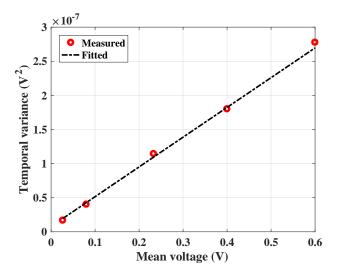

| 2.17 | Temporal variance versus mean output voltage extracted from measurement                                                                                                                                                                                 | 34  |

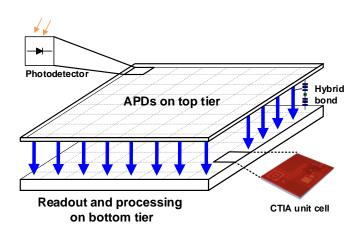

| 2.18 | Conceptual representation of 3D stacking.                                                                                                                                                                                                               | 36  |

| 2.19 | (a) Cross-section view of a P+/N-well SPAD device [20] and (b) typical I-V character-                                                                                                                                                                   |     |

|      | istics of a reverse-biased photodiode.                                                                                                                                                                                                                  | 37  |

| 2.20 | (a) Passive quenching and recharge of a P+/N-well SPAD device using a ballast resistor, R and (b) I-V characteristics of the SPAD in the Geiger mode (redrawn from                                                                                      |     |

|      | [22])                                                                                                                                                                                                                                                   | 38  |

| 2.21 | Typical cross-sections of 3D-stacked technology– (a) Front-side illuminated (FSI) and                                                                                                                                                                   | ~ ~ |

|      | (b) back-side illuminated (BSI) [23].                                                                                                                                                                                                                   | 39  |

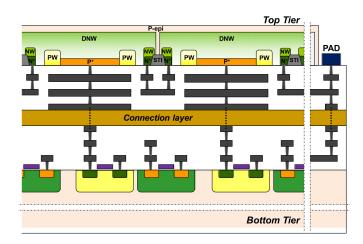

|      | Cross-section of BSI 3D-stacked SPAD in 45 nm CIS technology [2].                                                                                                                                                                                       | 40  |

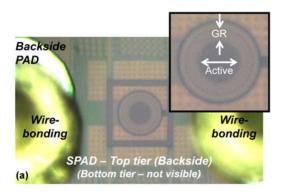

| 2.23 | Micrograph of the BSI 3D-integrated SPAD. The inset shows a magnification of active and guard-ring (GR) areas. [2].                                                                                                                                     | 40  |

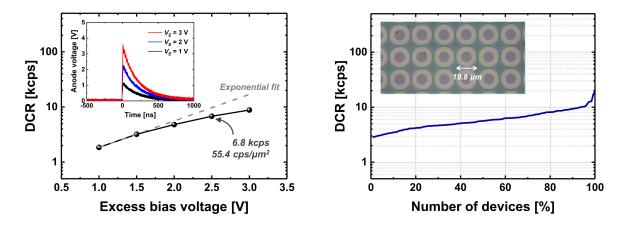

| 2.24 | (a) DCR as a function of the excess bias voltage, $V_E$ , at room temperature where the                                                                                                                                                                 | 40  |

| 2.24 | inset shows the output pulses of the SPAD as a function of time and (b) cumulative                                                                                                                                                                      |     |

|      | DCR distribution of 128 SPADs. The inset shows a micrograph of the BSI 3D-stacked                                                                                                                                                                       |     |

|      | SPAD arrays used for this DCR distribution test [2].                                                                                                                                                                                                    | 41  |

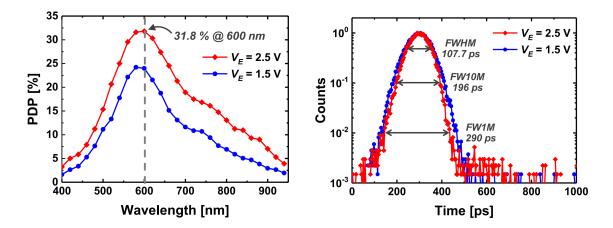

| 2.25 | (a) PDP at excess bias voltages of 1.5 V and 2.5 V and (b) timing jitter results using                                                                                                                                                                  |     |

|      | a 637 nm laser                                                                                                                                                                                                                                          | 41  |

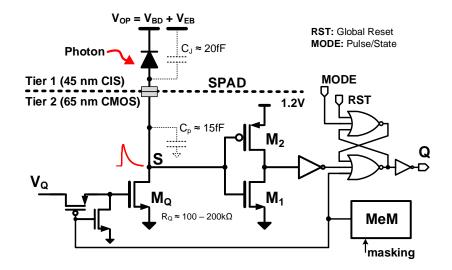

| 2.26 | Pixel circuit schematic for P+/N-well SPAD– Passive quenching and recharge along                                                                                                                                                                        |     |

|      | with masking block.                                                                                                                                                                                                                                     | 43  |

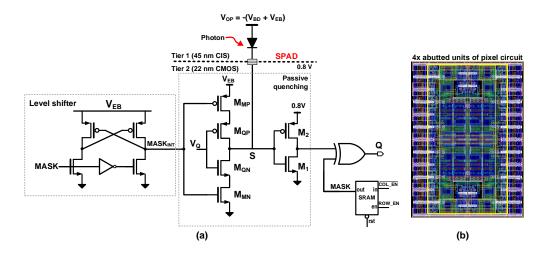

| 2.27 | (a) Bidirectional pixel circuit- dual passive quenching and recharge along with mask-                                                                                                                                                                   |     |

|      | ing block and (b) Layout showing four abutted units of the pixel circuit                                                                                                                                                                                | 44  |

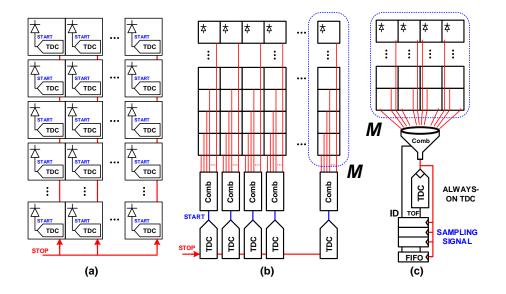

| 3.1  | TDC-pixel arrangement- (a) Per-pixel, event-driven, (b) column-wise, event-driven                                                                                                                                                                       |     |

|      | and, (c) always-on, shared TDC concept.                                                                                                                                                                                                                 | 50  |

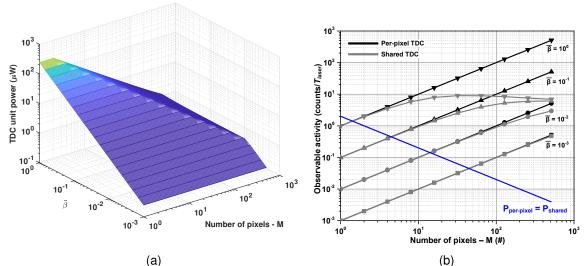

| 3.2  | Relationship between power consumption, activity, and number of pixels. (a) Average                                                                                                                                                                     |     |

|      | power per TDC unit; (b) $\overline{\beta}$ compression due to combination dead time, within a laser                                                                                                                                                     |     |

|      | pulse ( <i>T<sub>laser</sub></i> ) of 5 ns                                                                                                                                                                                                              | 53  |

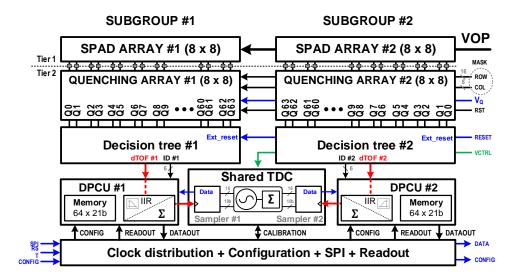

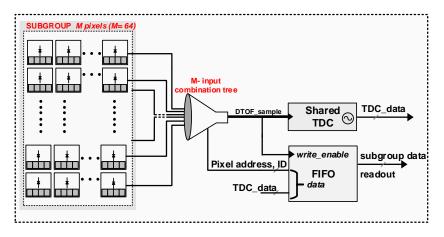

| 3.3  | Block diagram– A module comprised of two subgroups of 8 x 8 pixels (SPADs), shared                                                                                                                                                                      |     |

|      | TDC, in-locus digital processing and communication unit (DPCU), and memory                                                                                                                                                                              | 54  |

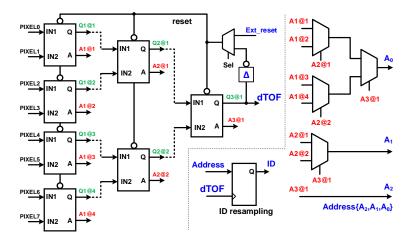

| 3.4  | Decision tree concept for 8 pixel inputs.                                                                                                                                                                                                               | 55  |

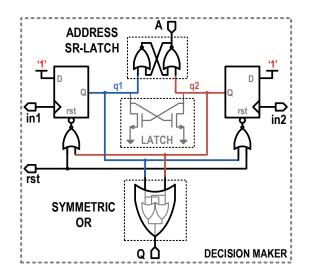

| 3.5  | Decision maker schematic.                                                                                                                                                                                                                               | 56  |

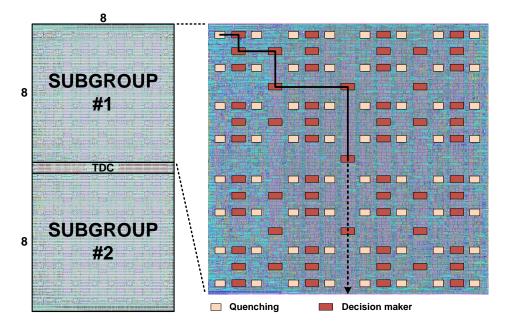

| 3.6  | Layout of a module consisting two subgroups obtained after place and route                                                                                                                                                                              | 57  |

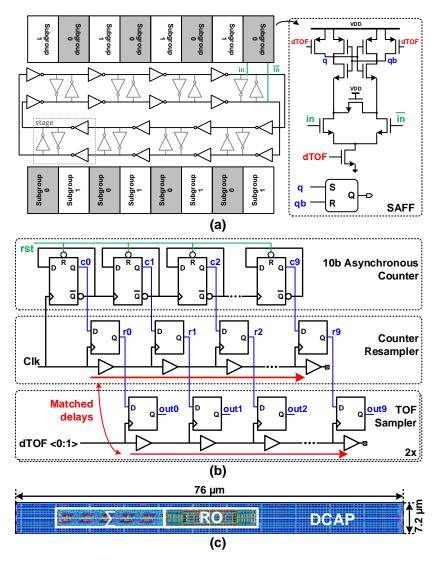

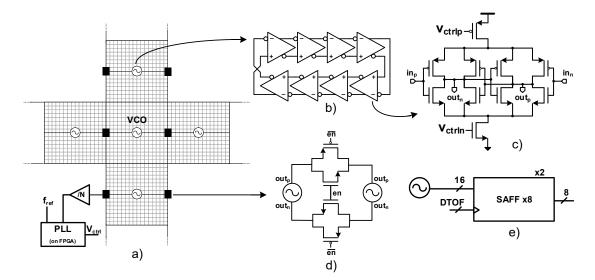

| 3.7  | TDC block diagram. (a) Pseudo-differential stages and SAFF arrangement for the                                                                                                                                                                          |     |

|      | two subgroups, (b) Counter schematic, (c) Layout                                                                                                                                                                                                        | 59  |

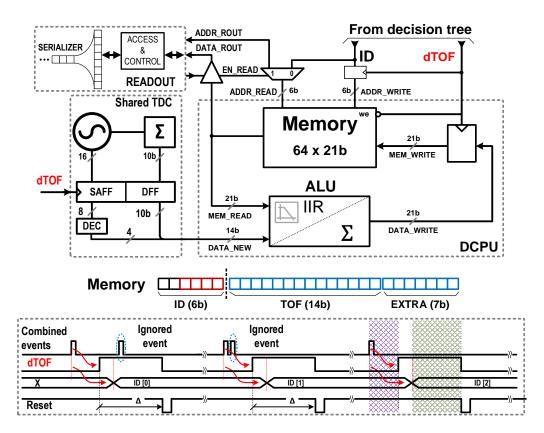

| 3.8  | DPCU block diagram for subgroup with the shared TDC and timing diagram                                                                                                                                                                                  | 60  |

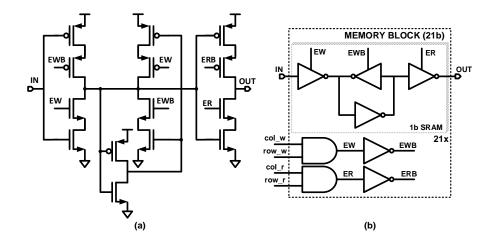

| 3.9   | Custom-designed pixel memory- (a) single-ended, tri-state SRAM and (b) 21-bit block memory per pixel.                                                                                 | 61 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

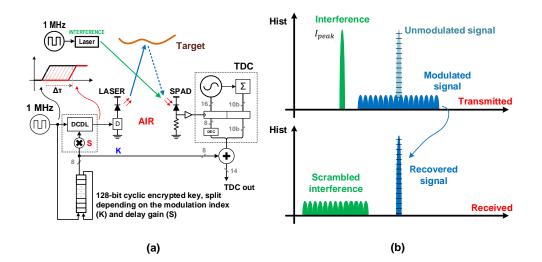

| 3.10  | (a) Laser signature concept- Implementation via encrypted key, divided according to modulation index and directly combined with digital TDC output and (b) Laser signature histogram. | 61 |

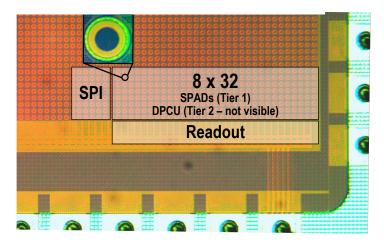

| 3 1 1 | Photomicrograph of the sensor                                                                                                                                                         | 63 |

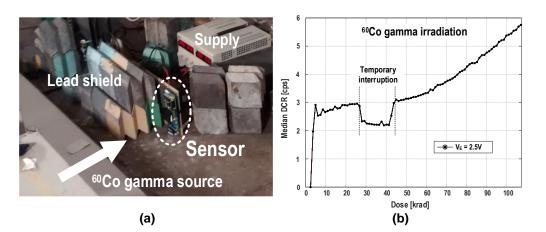

| 3.12  | Irradiation measurement, (a) setup and (b) DCR increase with accumulated dose                                                                                                         | 64 |

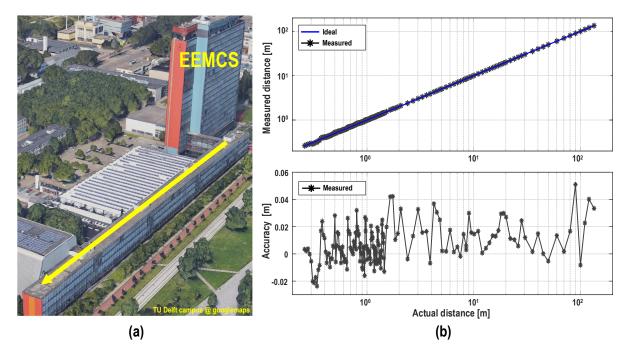

| 3.13  | High-resolution range measurement- (a) aerial view of measurement location and (b)<br>Measured distance and accuracy.                                                                 | 64 |

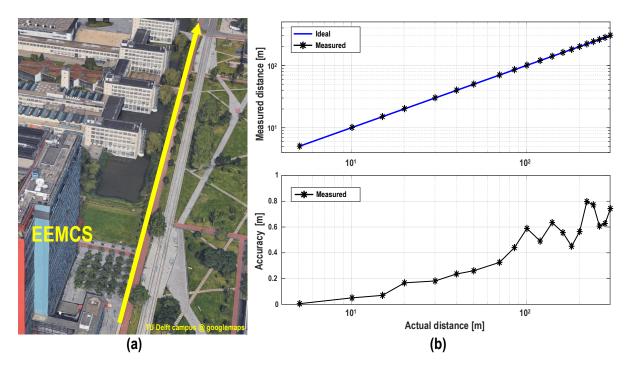

| 3.14  | High-resolution range measurement- (a) aerial view of measurement location and (b)                                                                                                    |    |

|       | Measured distance and accuracy.                                                                                                                                                       | 65 |

| 3.15  | Laser signature measurement- (a) no background illumination and (b) 3 klux back-<br>ground illumination.                                                                              | 66 |

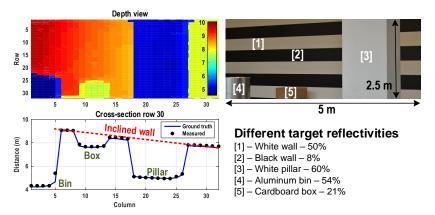

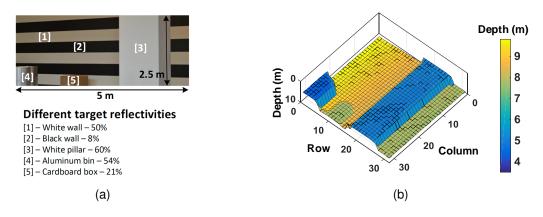

| 3 16  | A 32×32 image featuring multiple targets with different reflectivities.                                                                                                               | 67 |

|       | A 256×256 depth data superimposed with intensity image.                                                                                                                               | 67 |

|       | A block diagram of a DTOF sensor in a shared architecture.                                                                                                                            | 69 |

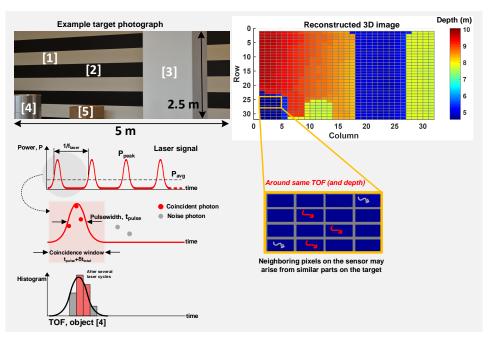

|       | Flash LiDAR operation.                                                                                                                                                                | 70 |

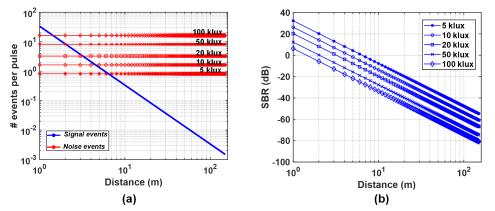

|       | Simulation results of ( <b>a</b> ) the number of events per pixel per laser pulse at different                                                                                        |    |

|       | background noise levels and ( <b>b</b> ) the SBR for 1–150 m target distances, $d$ .                                                                                                  | 72 |

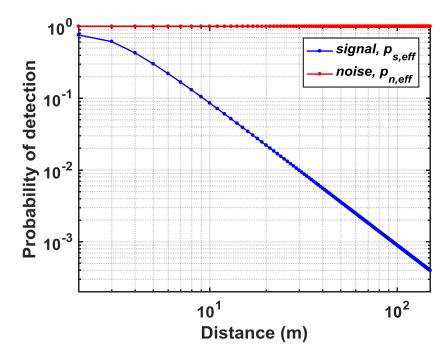

| 3.21  | Probability of detecting signal and noise events in a flash scenario using DT-based                                                                                                   |    |

|       | DTOF scheme.                                                                                                                                                                          | 75 |

| 4.1   | Conceptual representation of coincidence detection.                                                                                                                                   | 80 |

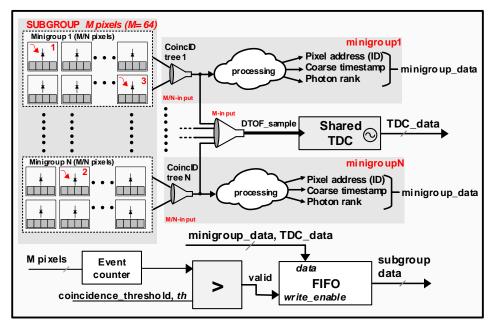

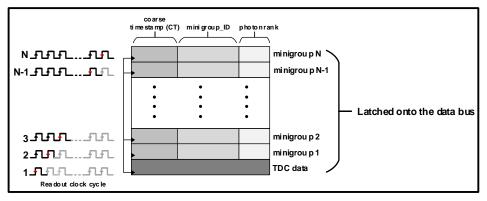

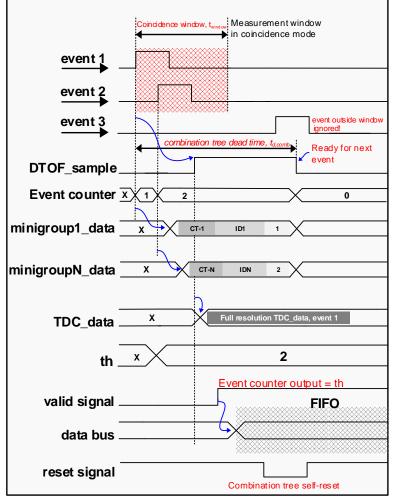

| 4.2   | (a) A block diagram of a DTOF sensor adapted to detect coincidence and (b) description of data from subgroup, that is, minigroups and TDC data.                                       | 81 |

| 4.3   | Simplified timing diagram showing the operation of the proposed architecture                                                                                                          | 82 |

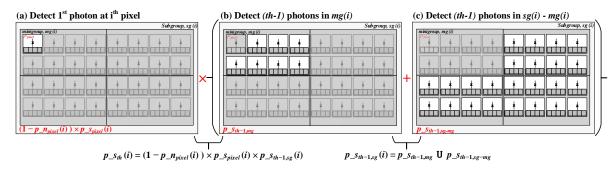

| 4.4   | Subgroup, $sg(i)$ , demarcated to show various probabilities under coincidence mode to detect ( <i>th</i> ) number of signal photons.                                                 | 84 |

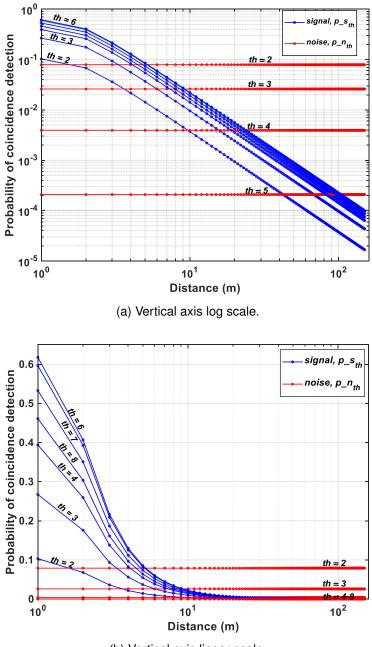

| 4.5   | Flash LiDAR operation.                                                                                                                                                                | 85 |

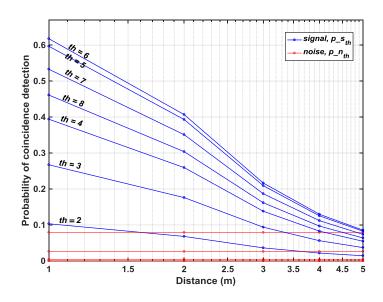

| 4.6   | Probability of signal and noise detection at different coincidence thresholds- (a) log                                                                                                |    |

| . –   | scale and (b) linear scale.                                                                                                                                                           | 86 |

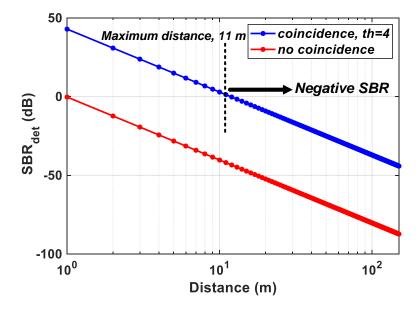

| 4.7   | SBR achieved after detection without and with coincidence with $th = 4$                                                                                                               | 87 |

| 4.8   | DTOF system block diagram- red arrows indicate the feedback between the sensor<br>and the illumination control.                                                                       | 88 |

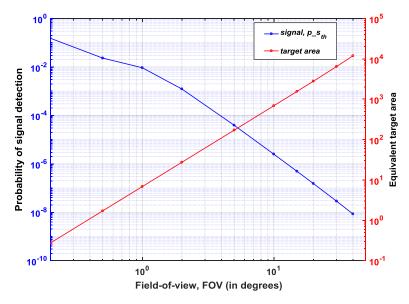

| 4.9   | Probability of detection at $d = 150$ m (left vertical axis) and equivalent target area                                                                                               | 00 |

| 4.5   | (right vertical axis) at varying FOV (horizontal axis). $\dots \dots \dots$           | 88 |

| 4.10  | (a) Photograph of the example target scene and (b) $32 \times 32$ image reconstructed in a                                                                                            | 00 |

|       | scanning LiDAR setup [7].                                                                                                                                                             | 89 |

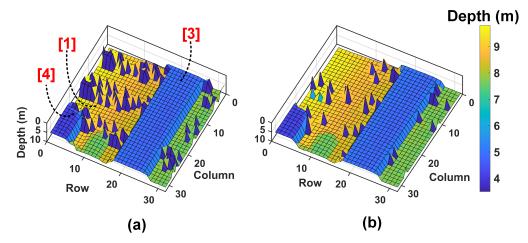

| 4.11  | (a) Simulated result of the 3D image reconstructed through DT-based scheme and                                                                                                        |    |

|       | (b) coincidence-based proposed architecture.                                                                                                                                          | 90 |

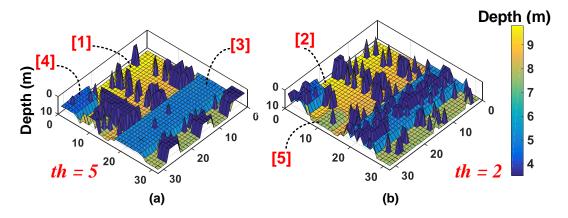

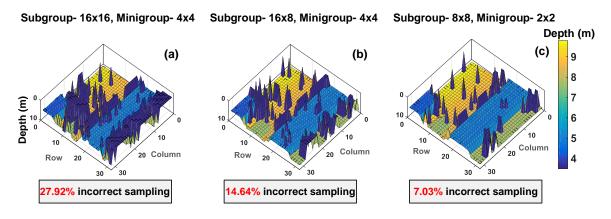

| 4.12  | Simulated result of the 3D image reconstructed through proposed DTOF model (a)                                                                                                        |    |

|       | coincidence threshold, $th = 5$ and (b) coincidence threshold, $th = 2$ .                                                                                                             | 91 |

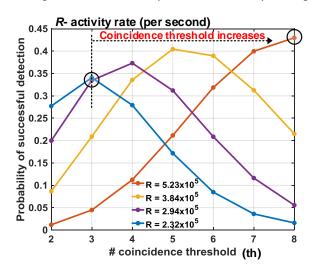

| 4.13         | The relationship between coincidence threshold and the incoming activity rate, <i>R</i> , received per second.                                                                                                                                                              | 92       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4 1 4        | Probability of signal detection in Figure 4.6b selected to show threshold dependence.                                                                                                                                                                                       | 92       |

|              | The proposed grouping scheme illustrated for different subgroup and minigroup sizes.                                                                                                                                                                                        | 93       |

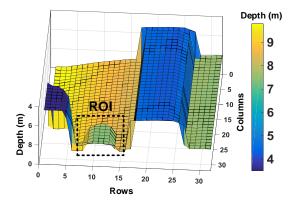

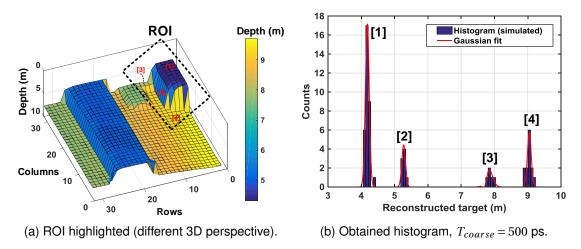

|              | 3D image input highlighted with the region of interest (ROI).                                                                                                                                                                                                               | 93       |

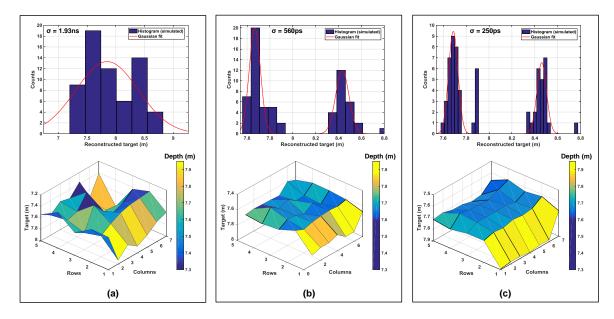

|              | Minigroup timestamping feature ( <b>a</b> ) no timestamping, uncertainty $\approx t_{window}$ , ( <b>b</b> ) minigroup timestamping with a resolution, $T_{coarse} \approx 500$ ps and ( <b>c</b> ) minigroup timestamping with a resolution, $T_{coarse} \approx 200$ ps.  | 93<br>94 |

| / 18         | Minigroup timestamping feature for up to four peaks.                                                                                                                                                                                                                        | 95       |

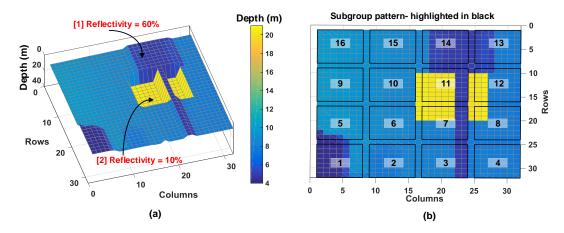

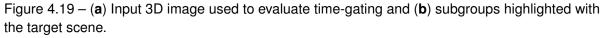

|              | (a) Input 3D image used to evaluate time-gating and (b) subgroups highlighted with the target scene.                                                                                                                                                                        | 95       |

| 4.20         | Histogram of $sg_{11}$ ( <b>a</b> ) without gating and ( <b>b</b> ) with gating.                                                                                                                                                                                            | 96       |

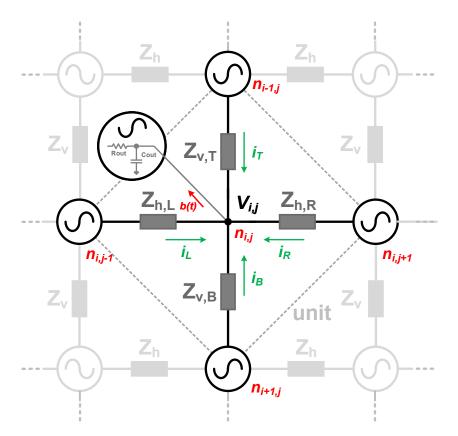

| 5.1<br>5.2   | Generic mutually coupling oscillators concept                                                                                                                                                                                                                               | 100      |

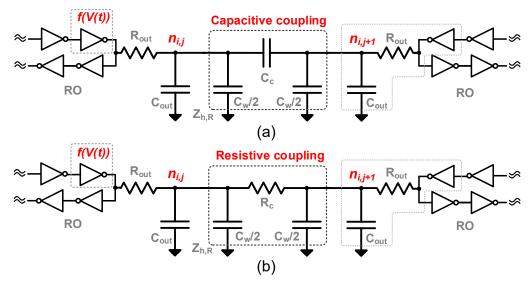

| 5.3          | tors (ROs) (only $Z_{h,R}$ shown)                                                                                                                                                                                                                                           | 101      |

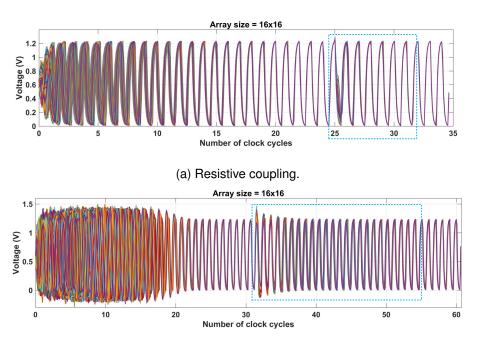

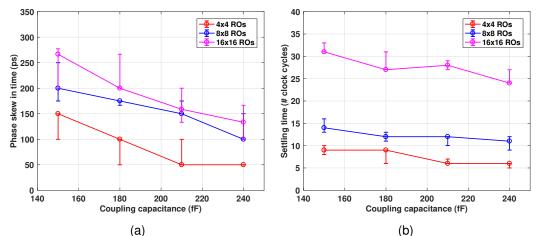

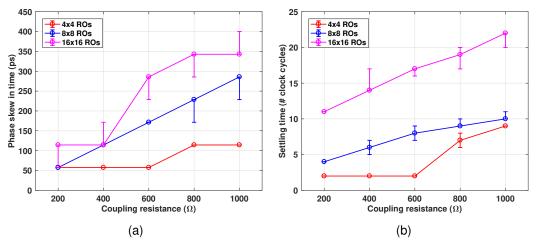

|              | coupling with $R_c = 250 \ \Omega$ and (b) capacitive coupling with $C_c = 240 \ \text{fF.}$                                                                                                                                                                                | 103      |

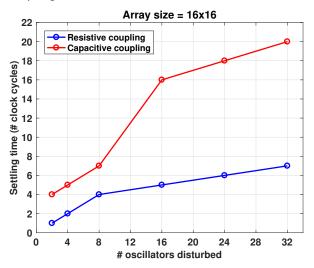

| 5.4          | Steady state recovery time (in cycles), after different number of ROs disturbed                                                                                                                                                                                             | 103      |

| 5.5          | (a) Steady state phase skew and (b) Settling time for different network sizes and coupling capacitance. Settling time is defined by the phase mismatch below 1/(67%)                                                                                                        | 100      |

| 5.6          | of value obtained in (a); vertical bars indicate variation due to $\pm 10\%$ mismatch in $C_c$ .<br>Steady state (a) phase skew and (b) settling time, for different network sizes and coupling resistance. Settling time is defined by the phase mismatch below 1/(67%) of | 104      |

|              | value obtained in (a); vertical bars indicate variation due to $\pm 10\%$ mismatch in $R_c$ .                                                                                                                                                                               | 104      |

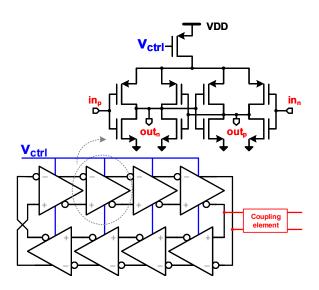

| 5.7          | Current-starved 8-stage pseudo-differential RO.                                                                                                                                                                                                                             | 106      |

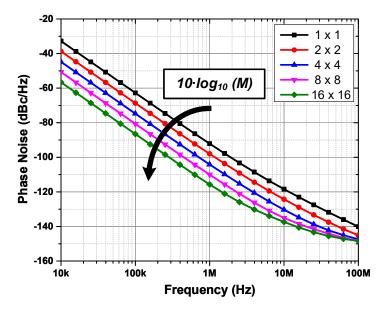

| 5.8          | Simulation of phase noise reduction from 1 $(1 \times 1)$ to 256 $(16 \times 16)$ mutually-coupled ROs.                                                                                                                                                                     | 106      |

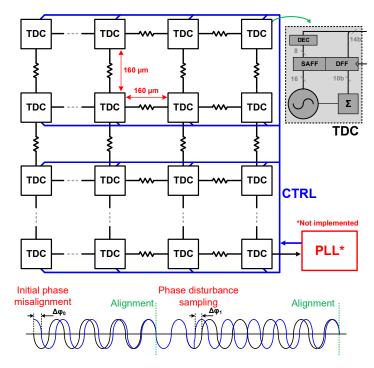

| 5.9          | Implemented 8 × 8 mutually-coupled TDC architecture and RO phase misalignment                                                                                                                                                                                               | 100      |

| 0.0          | self-correction. PLL: phase-locked loop.                                                                                                                                                                                                                                    | 107      |

| 5 10         | Transmission gate as resistive coupling element                                                                                                                                                                                                                             | 108      |

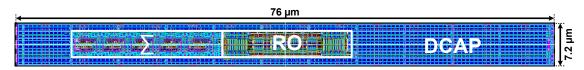

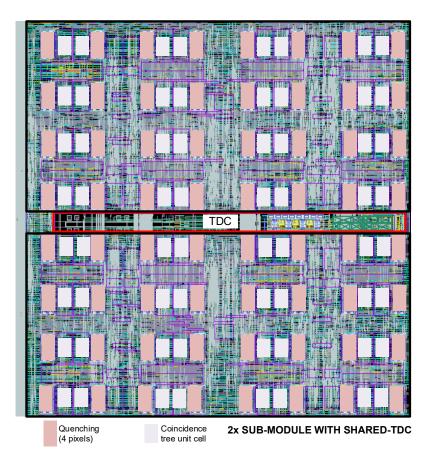

|              | TDC layout.                                                                                                                                                                                                                                                                 | 108      |

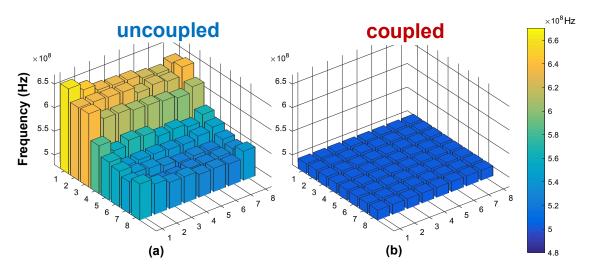

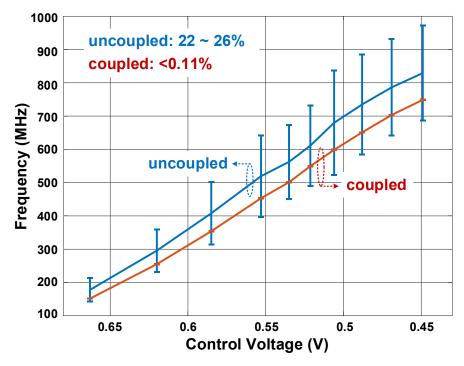

|              | Individual frequencies of uncoupled and coupled modes.                                                                                                                                                                                                                      | 109      |

|              | Frequency variation of coupled and uncoupled modes, for different average frequen-                                                                                                                                                                                          | 103      |

| 5.15         |                                                                                                                                                                                                                                                                             | 109      |

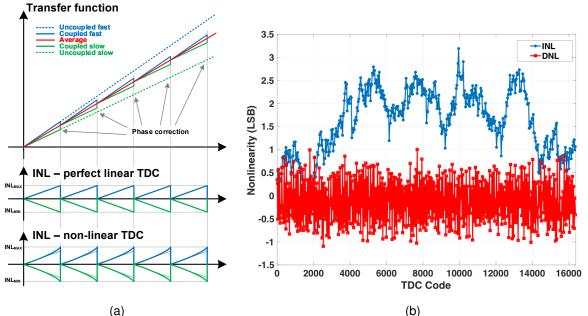

| 5.14         | TDC non-linearity effects: (a) Local INL due to phase correction, for a perfectly linear                                                                                                                                                                                    |          |

| <b>-</b> / - | TDC and a non-linear TDC; (b) Uncoupled TDC INL and DNL, without calibration.                                                                                                                                                                                               | 110      |

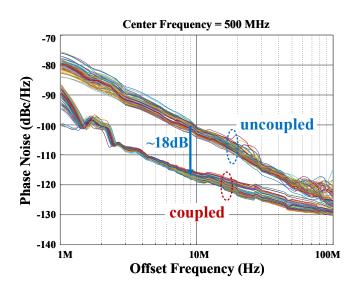

| 5.15         | Measured phase noise comparison, for uncoupled and coupled conditions, for all 64                                                                                                                                                                                           |          |

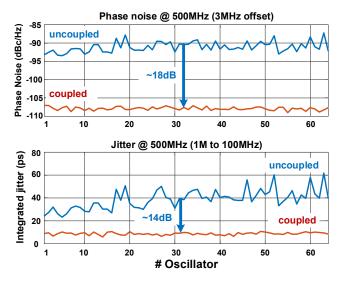

|              | ROs at 500 MHz center frequency.                                                                                                                                                                                                                                            | 111      |

| 5.16         | Phase noise and integrated root mean square (RMS) jitter comparison for uncoupled and coupled modes, for all 64 ROs at 500 MHz center frequency.                                                                                                                            | 111      |

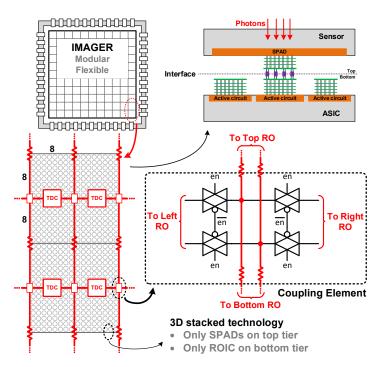

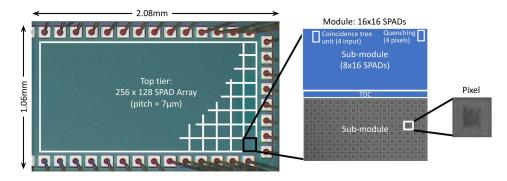

| 5.17 | High-level visualization of the sensor.                                                  | 112 |

|------|------------------------------------------------------------------------------------------|-----|

| 5.18 | Block-diagram of a module- 2×16×8                                                        | 113 |

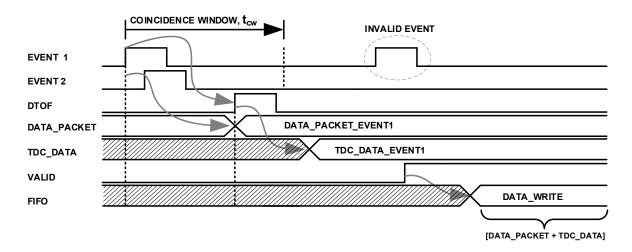

| 5.19 | Timing diagram of coincidence detection for an example case where threshold, $th = 2$ .  | 114 |

| 5.20 | Coincidence tree unit cell for 4-inputs                                                  | 115 |

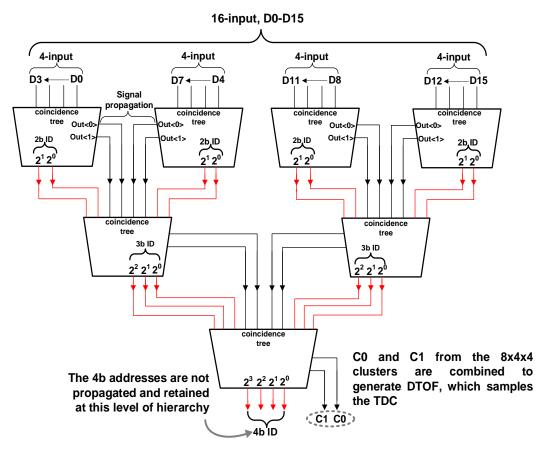

| 5.21 | 16-input coincidence tree                                                                | 116 |

| 5.22 | Dedicated coarse counter for a cluster of $4 \times 4$ pixels                            | 117 |

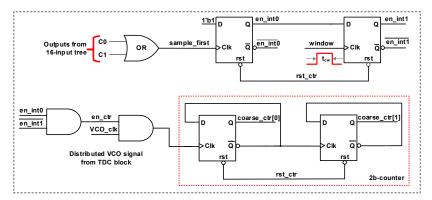

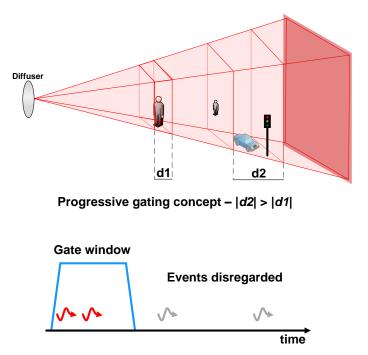

| 5.23 | Pictorial representation of progressive gating.                                          | 117 |

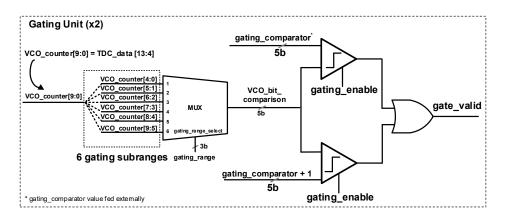

| 5.24 | Gating control unit per sub-module of $16 \times 8$ pixels                               | 119 |

| 5.25 | (a) Mutual coupling of TDCs, (b) pseudo-differential ring oscillator, (c) schematic of a |     |

|      | pseudo-differential stage, (d) Transmission gate element used for coupling and, (e)      |     |

|      | sense-amplifier flip-flop (SAFF) block.                                                  | 119 |

| 5.26 | Layout of a module consisting of two sub-modules.                                        | 120 |

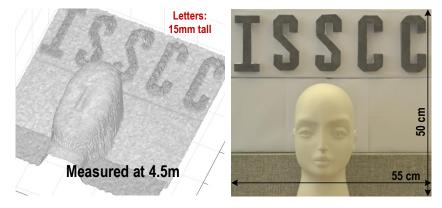

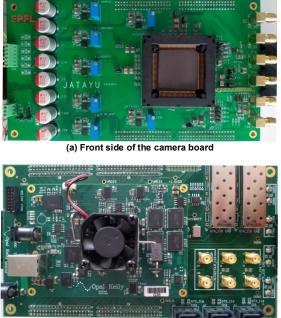

| 5.27 | Chip photomicrograph.                                                                    | 121 |

| 5.28 | Jatayu camera system- (a) Front side of the board hosting the sensor and (b) back        |     |

|      | side of the board hosting the FPGA.                                                      | 121 |

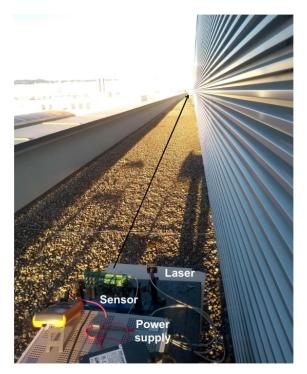

| 5.29 | Outdoor setup for telemetry measurement.                                                 | 122 |

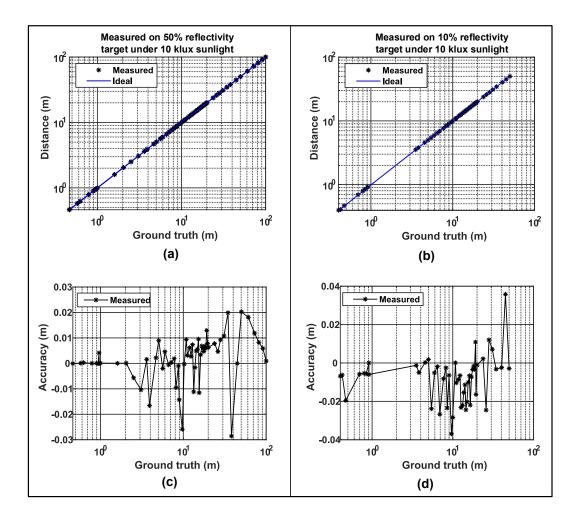

| 5.30 | Telemetry measurements- (a) and (c) Measured distance and accuracy vs ground             |     |

|      | truth on 50 % reflectivity target, (b) and (d) Measured distance and accuracy vs         |     |

|      | ground truth on 10 % reflectivity target.                                                | 123 |

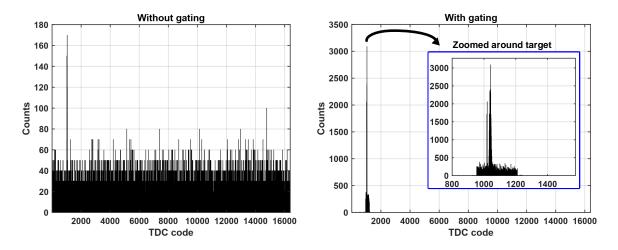

|      | Histograms of a target (a) without and (b) with gating                                   | 124 |

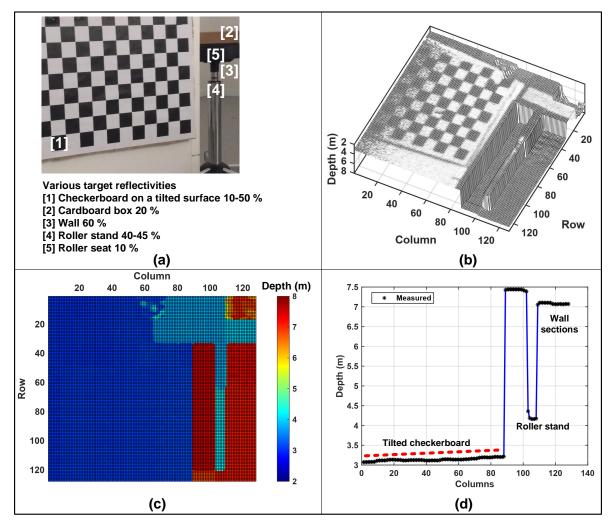

| 5.32 | 3D imaging of multiple targets with different reflectivity- (a) Photograph of the scene, |     |

|      | (b) Superimposed depth and intensity image, (c) color-coded depth data and, (d)          |     |

|      | Cross-section of depth across row 71                                                     | 125 |

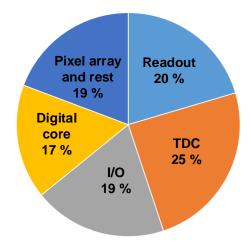

| 5.33 | Pie chart indicating power consumption of various blocks                                 | 126 |

# List of Tables

| 2.1 | Performance summary                                            | 36  |

|-----|----------------------------------------------------------------|-----|

| 2.2 | State-of-the-art comparison of 3D-stacked BSI SPADs            | 42  |

| 3.1 | Performance comparison of state-of-the-art DTOF sensors (2018) | 68  |

| 3.2 | Simulation parameters                                          | 72  |

| 5.1 | Performance comparison of state-of-the-art DTOF sensors (2020) | 127 |

## 1 Introduction

This chapter introduces time-resolved imaging and in particular, time-of-flight (TOF) for light detection and ranging (LiDAR) applications. Taxonomy of depth sensing techniques is presented where the primary discussion is held on direct-TOF sensors which is the focus of this thesis. The reader is acquainted with various challenges in a LiDAR application, which thereby set the premise for this thesis. Finally, significant contributions of this work are described, which along with the thesis organization, provide the necessary context for this work.

### 1.1 Time-resolved imaging

Time-resolved imaging is a composition of techniques which exploits the temporal information of photons to infer a scene of interest. This information itself can be of various types depending on the application. With its vast scope, time-resolved imaging can be applied in a number of areas including but not limited to consumer, automotive, computer vision, gaming, augmented (and virtual) reality (AR-VR), space and bio-medical applications [1, 2, 3, 4, 5]. High timing resolution on the order of picoseconds is attainable in today's time-resolved image sensors, thereby, opening new pathways in 3D vision and sensing in consumer applications. Time-of-flight (TOF) is a key depth-sensing technique where the travel time of photons is used to estimate the distance of targets and reconstruct them over a scene of interest. In both, consumer and automotive applications, TOF can be used to extract information such as distance and in turn, reconstruct a 3D point cloud of a scene. Practical examples can be found in today's smart phones, in advanced driver assistance systems (ADAS) and autonomous driving, while in biomedical applications, time-resolved imaging may be used to extract the lifetime of fluorophores in fluorescence lifetime imaging (FLIM) and time of arrival of gamma photons in positron emission tomography (PET).

### 1.2 Time-of-flight (TOF) for LiDAR

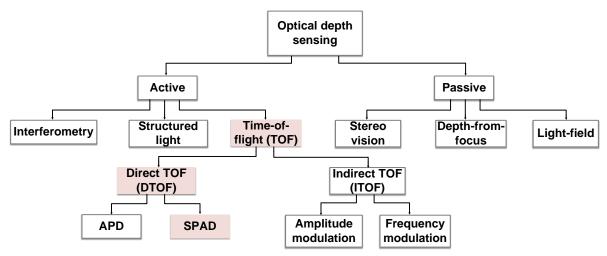

Light detection and ranging (LiDAR) is a method for measuring distances using light. Various depth sensing techniques enable this measurement, a broad classification of which is shown in Figure 1.1,

#### **Chapter 1. Introduction**

where the focus of this thesis is highlighted (DTOF). Optical depth sensing techniques are broadly classified in their active and passive forms. Advantages of passive systems are that they do not need any active illumination. For example, a typical stereo vision system functions with just two cameras separated by a known distance where it simulates a human binocular vision and uses sophisticated computer algorithms to reconstruct 3D images. Naturally, the downfall is its heavy dependence on computationally intensive processing. Depth-from-focus calculates distances by modeling the quality of images by optimally choosing the camera focal setting for every point in the scene to capture the best possible image [6]. The only major advantage is the presence of a single camera when compared to a stereo vision system employing two cameras. The major drawback of both methods however is inability to detect in scenes of poor contrast, i.e., it does not work on blank walls or in the dark. In another passive technique, called, light-field, a main lens is chosen to select the desired field-of-view (FOV) and create an intermediate image in front of a micro camera array where each micro camera in the image sensor sees a slightly different perspective of the target. The images generated by the camera in this setup are processed using software algorithms to calculate the depth of the scene. An important concern however is the dependence of depth resolution on the depth-of-field, which in turn depends on the focal length of the main lens[7, 6].

Active depth sensing techniques, as the name suggests, employ an active illumination source to perform 3D imaging. Interferometry is an active technique which provides depth resolution on the order of nanometers, where the interference fringe of the backscattered laser beam is measured with respect to a reference beam. The technique is however limited in the achievable range which is on the order of millimeters. Furthermore, the dependence of laser wavelength on the environmental conditions introduces additional burden on calibration [8, 9].

Figure 1.1 – Classification of optical depth sensing techniques.

Structured light is another active technique where a pattern (of dots or stripes) is projected onto a target and its deformation is used to reconstruct the depth and the target shape. A recent example of this technique is the Face ID feature on Apple's iPhone [10]. While guaranteeing high accuracy over short distances, the disadvantage of structured light is for medium-long-range measurements where the deformation of the projected pattern may not be perceived easily. Furthermore, high

background noise from ambient light may also interfere with the projected pattern, additionally making it challenging to acquire data from the target. As a result of this, structured light technique is popularly used for distances under 1–2 m.

Another active method, time-of-flight (TOF), as briefly introduced before, relies on the travel time of light (pulses or waves) bouncing off a target to measure distances. TOF sensors are basically categorized into their indirect (ITOF) and direct (DTOF) forms.

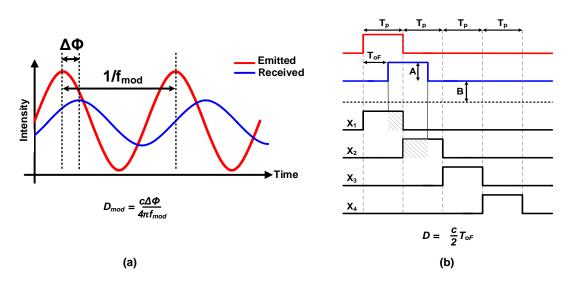

In the (amplitude-)modulated (AM) ITOF operation, the emitted signal is a continuous-wave signal modulated in time, which is usually a sinusoidal signal. The phase difference between the emitted and received light signals, is used to measure the distance traveled by the light, from the sensor to the target and back again as seen in Figure 1.2a. Consequently, the distance,  $D_{mod}$ , can be expressed as,

$$D_{mod} = \frac{c\Delta\Phi}{4\pi f_{mod}},\tag{1.1}$$

where,  $f_{mod}$  is the modulated frequency and c is the speed of light. Pulsed method is one of the other ways to perform an ITOF measurement- a concept of which is shown in Figure 1.2b. An example case with 4 windows is shown where the measurement is based on the gated integration of the optical pulses over time [11], where multiple windows allow measurement of the signal (A in Figure 1.2b) and background noise level (B in Figure 1.2b) separately. All the measurements have a duration equal to that of the emitted pulse and 4 windows are used to determine the phase shift. Like in the modulated method, the distance, D, can be calculated as follows,

$$D = \frac{cT_{oF}}{2}.$$

(1.2)

Figure 1.2 – Conceptual representation of ITOF sensors- (a) Modulated ITOF and (b) Pulsed ITOF. In a frequency-modulated (FM) ITOF system, the optical frequency is modulated in time where,

#### **Chapter 1. Introduction**

a frequency difference between the emitted and reflected signal is processed to determine the distance of a target [12, 13]. In addition to measuring distances, this technique can also provide a velocity measurement using Doppler effect, which can be particularly useful in automotive LiDAR applications. Unlike AM technique, FM-based method is able to cope with multi-path reflections by resolving the multiple beat tones in the frequency domain.

ITOF sensors have been implemented in a number of consumer applications for ranging and depth mapping. However, continuously growing demand for higher spatial resolutions (VGA – MP) and operation over wide FOV ( $50^{\circ} - 120^{\circ}$ ) have limited their applications to short ranges [14, 15, 16, 17]. A class of ITOF sensors based on short-pulse modulation and multi-tap lock-in pixels is becoming an attractive candidate due to higher achievable range resolution [18], however, it is currently limited to distances under 10 m [19]. Another drawback of ITOF sensors is their limited ability to distinguish two nearby objects (multi-path interference) [20].

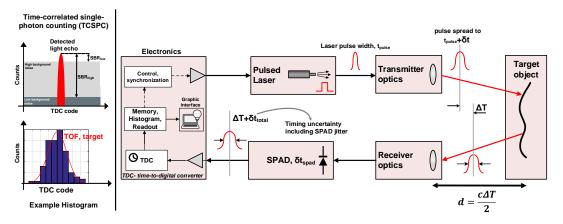

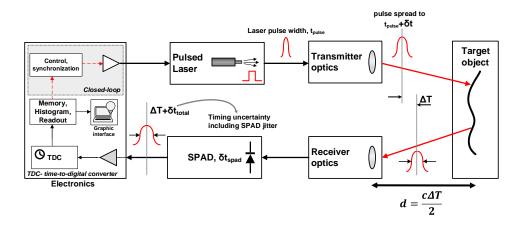

DTOF sensors, on the other hand, are able to mitigate these challenges with detection ranges reaching up to several hundred meters [21, 22], principally determined by the available optical power and their innate ability to discriminate multiple echoes easily [23]. The main focus of this thesis is on the analysis and design of DTOF sensors for LiDAR applications and therefore, the subsequent sections will be dedicated to depth sensing based on DTOF only. The high-level block diagram of a DTOF sensors for system is shown in Figure 1.3.

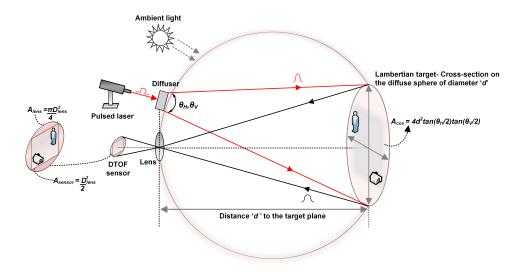

Figure 1.3 – High-level block diagram of a DTOF sensing system

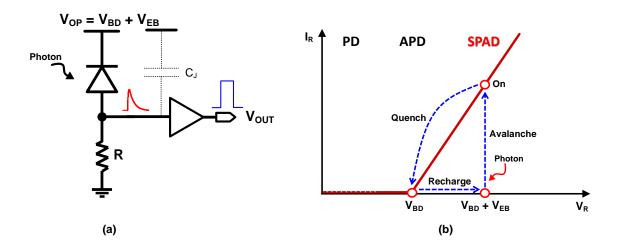

A DTOF sensor consists of a pulsed illumination source which may be a LED, a laser diode or a VCSEL (vertical cavity surface-emitting laser) array, operating at the desired repetition rate which is usually dictated by the maximum distance required to be measured. This source is illuminated on a scene of interest with the target and the reflected photons from the target are then detected by an appropriate photodetector, typically an avalanche photodiode (APD) or a single-photon avalanche diode (SPAD). The time-of-arrival of these photons is then measured by a time-stamping electronic circuit. In DTOF sensors, time-to-digital converters (TDCs) are typically used for this purpose [24, 25, 22, 26, 27, 28]. On combining timing information with the speed of light, *c*, the distance of the target from the sensor is determined as shown in Figure 1.3. A typical example is a commercial range-finder where single-point timing information is utilized to measure ranges up several tens of

meters. When such a single-point timing measurement is spatially extended over more number of points over a given field-of-view (FOV), a 3D image can then be reconstructed of the scene within the FOV.

### 1.3 LiDAR application challenges

A LiDAR system, depending on whether it is employed outdoor or indoor, requires a sensor capable of measuring ranges between 10 – 100 m. A close-in LiDAR may require accuracies down to a few millimeters while long-distance LiDARs can as well work with accuracies on the order of a few centimeters. [14, 21, 29]. Nonetheless, accuracy and range requirements must be met over a wide range of operating conditions. The following sections briefly discuss some of them.

#### 1.3.1 Background noise suppression

Time-correlated single-photon counting (TCSPC) is a common method utilized in DTOF systems to acquire large number of detections where the detected signal is represented as a histogram corresponding to the time-of-arrival of individual photons incident on the photodetector [30, 24, 23, 25, 29]. Under an ideal condition where the background noise is low, the target peak can be easily distinguished on the measured histogram. However, most often, high background noise from ambient sunlight is a primary challenge in LiDAR applications. Depending on whether the system is indoor or outdoor, the background noise may range around 1 klux in a well-lit indoor environment while reaching up to 100 klux on a bright sunny day outdoor [31]. As a result of this, often, the returning target peak in a DTOF system is submerged under an overwhelming noise floor (see Figure 1.3), thus making it extremely difficult to detect the signal. Another implication of high background noise is distortion in the measured histogram due to pile-up [30], which results in large depth errors. Therefore, it is paramount to address the high background noise challenge to maintain a signal-to-background noise-ratio (SBR) high enough to allow quality depth measurement. Incorporating noise-filtering techniques, both, optically, by using optical bandpass filters and electrically, by smart sensor design are both valuable in this regard.

#### 1.3.2 Optical power budget and safety regulations

An ideal and convenient solution to coping with high background noise is to increase the power of the illumination source. However, the maximum permissible optical power of the laser will be dictated by eye-safety regulations which are in turn governed by various other system parameters such as the laser beam size and divergence, the illumination wavelength, exposure time, the FOV, optical filter, lens etc. In pulsed laser systems, as is the case in this thesis, pulse energy, pulse repetition rate, beam size and divergence are all accounted for while defining the allowable optical power from a laser source. Most often, the constraints become stringent for visible and near-infrared (IR) wavelengths, where the human eye is more sensitive to and consequently, is prone to more harm at higher optical powers. Hence, wavelengths beyond near-IR (> 1500 nm) or in the UV

region ( 200 - 350 nm) can permit higher optical powers. Maximum permissible exposure (MPE) is a term commonly used to indicate the highest power or energy density (in W/cm<sup>2</sup> or J/cm<sup>2</sup>) of a light source that is considered safe or has a negligible probability for creating damage. A calculation of MPE is important to account for eye-safety. IR wavelengths beyond 1500 nm are absorbed by the transparent parts of the eye before reaching the retina. As a result of this, MPE for these wavelengths can be higher than for visible light, thus, making them favorable for LiDAR applications. Furthermore, with an average solar radiation on the earth's atmosphere of around 1361 W/m<sup>2</sup>, the solar irradiance is higher at visible wavelengths while starting to significantly drop from 900 nm ( $\geq$  near-IR wavelengths) [32]. This factor further motivates the choice of near-IR to IR lasers for LiDARs as they help improve the overall system SBR. Nevertheless, depending on the exposure time and the wavelength, MPE can be used to calculate the permissible optical power on the laser. While it is not in the scope of this thesis to discuss this further, however, it is noteworthy to regard MPE as an important factor while implementing LiDAR systems. The reader is directed to [33] for more information on laser safety regulations published by American National Standards Institute (ANSI).

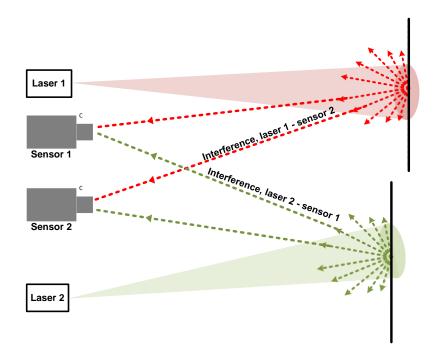

#### 1.3.3 Laser interference

A pulsed-LiDAR system relies on the reflected laser pulse to estimate the time-of-arrival of photons from the target. There is often a possibility of blinding the sensor with undesired photons which return to the sensor. Also, since most TOF sensors are designed to detect the first return, blinding effect could easily prevent any further legitimate detection. Further, multiple LiDAR systems can coexist while appearing as interferences to each other. A pictorial representation of such a scenario is shown in Figure 1.4, where, in the worst case, two laser sources from two different LiDAR systems could have the same repetition rate (and/or synchronized) leading to depth errors. It is important to enable the sensor to deal with such scenarios so that the target return can still be correctly estimated. Prior solutions include techniques based on code-division multiple-access techniques (CDMA) [34] and using pseudo-random sequences of the illumination to improve robustness in a multi-camera environment [35]. This thesis introduces a simpler method based on digital pulse-position modulation, the details of which will be covered in Chapter 3.

#### 1.3.4 High-dynamic range scenes

In any DTOF-based LiDAR system, the timestamp of the photons bouncing off a target is used to reconstruct a depth map. A given FOV may contain multiple targets with various (and wide range) surface reflectivity. Due to the nature of detection, a target with higher reflectivity is bound to return more number of photons when compared to target with lower reflectivity, thereby favoring the detection of the former over a given measurement window. However, in a scenario such as this, it is important to capture all the objects in the scene without causing depth errors. An outdoor example of such a scenario is seen in an automotive LiDAR system where the presence of retro-reflectors and traffic signs must be detected along with other objects (such as pedestrian walking or a lamp post) within the FOV. Therefore, a DTOF system should be equipped to handle the dynamic range

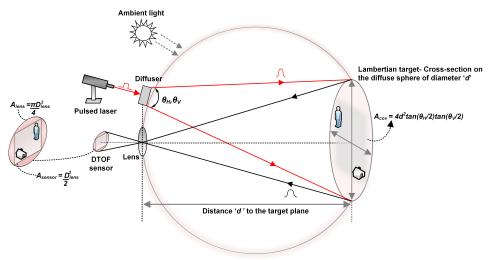

Figure 1.4 – Laser interference scenario- Pictorial representation with two LiDAR systems with Lambertian targets as example.

of a given scene in the presence of ambient light over different operating distances.

#### 1.3.5 Adverse weather phenomena

In addition to imaging under bright sunlight, other weather phenomena such as the presence of rain, fog or cloud, also adds to the detection challenge due to their scattering and absorption properties. In particular, interaction of light with suspended particles can manifest itself differently from the background noise which appears more as a uniform distribution on the histogram. Therefore, scattering effects need to be modeled and appropriate sensor solutions need to be developed. The non-uniform temporal distribution [36, 37] of particles in fog or cloud may reflect as distinct peaks in the acquired histogram, causing depth errors sometimes. Gated imaging is one way to selectively eliminate unwanted peaks occluded by suspended matter in light propagation path [38]. Furthermore, gating can enable range-selective detection while retaining high SBR around the target of interest. Exploiting the benefits of gating, this thesis also proposes a new method based on progressive gating as a way to improve SBR; more details will be discussed in Chapter 4.

#### 1.3.6 Detector sensitivity

Photodetectors capable of measuring single photons have existed for several decades in timeresolved systems implemented out of photomultiplier tubes (PMTs) and micro-channel plates (MCPs) [39]. However, owing to their bulky nature, vacuum-based operation, complexities due to their high

#### Chapter 1. Introduction

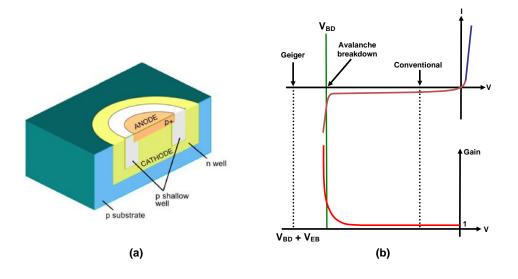

voltage requirements (several kVs) and high costs, their applications have become limited over the years. Today, time-resolved systems have evolved into their solid-state forms and to that front, Geiger-mode single-photon avalanche diodes (SPADs) have emerged as promising photodetectors in such systems [40, 41]. High speed and picosecond timing resolution achievable in SPADs make them popular candidates for DTOF sensors which require accurate timing measurements.

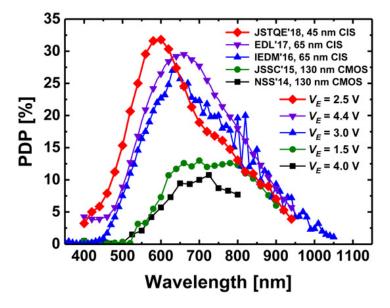

The performance of the DTOF sensor is primarily dictated by the SPAD performance. Therefore, with respect to sensitivity, the most important SPAD parameter is the photon detection probability (PDP), which represents the probability of producing an avalanche in the device in response to the photon absorption at a given wavelength. In CMOS SPADs, the PDP usually peaks in the visible region reaching up to 70% for single devices [42, 43]. However, as discussed before, for a LiDAR application, a near-IR/IR sensitivity is favored due to lower constraints on the permissible optical power of the illuminator and also, potentially higher SBR.

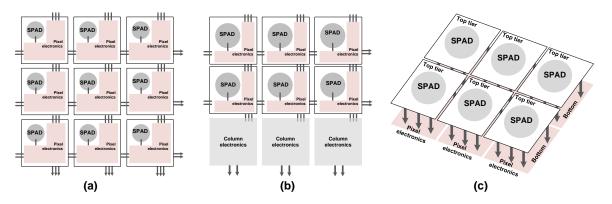

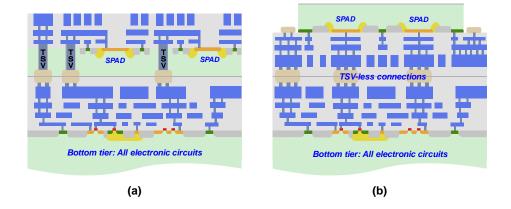

Moving from individual SPADs to image sensors introduces other parameters to be considered to enhance sensitivity. Fill factor is one such factor, which represents the ratio of photosensitive area to the total pixel area. The SPAD's fill factor directly affects the overall photon sensitivity, given that it is multiplied by the PDP to give the overall photon detection efficiency (PDE). Fill-factor effects are more pronounced in a monolithic (2D) implementation of sensors, where the active area is also shared with pixel-circuitry thus reducing the achievable fill-factor, as pictorially seen in Figure 1.5a,b.

Figure 1.5 – Comparison of imager architectures- (a) 2D array, per-pixel architecture, (b) columnparallel architecture and (c) 3D-stacked architecture.

The advent of 3D-stacked technology has however, helped circumvent this issue to a large extent. In particular, today's 3D-stacked sensors enable much higher fill-factor (and therefore, PDE), by dedicating separate tiers optimized for SPADs and electronics independently, see Figure 1.5c. Consequently, a more advanced sensor functionality is possible without compromise on the fill-factor. Furthermore, a much better near-IR sensitivity, reaching between 10–15 % around 850 nm, makes them very suitable for LiDAR applications [44, 45, 28]. Figure 1.6 shows the PDP of some state-of-the-art 3D stacked SPADs to given an overview of the achievable PDP spectra in BSI SPADs.

Another LiDAR-relevant SPAD parameter is the dark count rate (DCR) which denotes the uncorre-

lated avalanche events recorded in the absence of light, usually represented in counts/second (cps). As long as the DCR is lower than the background noise rate incident on the SPAD, it is usually not a major issue. Most often the background noise events per pixel is orders of magnitude (at least 2–3 orders of magnitude) higher than the DCR.

Figure 1.6 – PDP comparison of state-of-the-art back-illuminated SPADs [45].

Furthermore, it is always desirable to have high dynamic range, particularly required in high background noise scenario seen in LiDAR. Consequently, low SPAD dead times are favored to allow more number of detections. However, achieving lower dead times can be aimed for, so long as it does not significantly increase the afterpulsing effect, which refers to the triggering of avalanches due to release of trapper carriers at a later time, which results in false correlations in the measurement [46].

In summary, all the relevant SPAD characteristics should already be optimized for during the design phase based on the application.

#### 1.3.7 Improving timing statistics

As mentioned earlier, SPADs exhibit a timing response characterized by a low timing jitter, usually expressed as full width at half maximum (FWHM). State-of-the-art 3D-stacked SPADs achieve FWHM on the order of 100 ps [47, 44], thus, enabling them for millimetric precision required in LiDAR applications. In addition to the aforementioned SPAD jitter, DTOF systems usually face, multiple other timing uncertainties (see Figure 1.3). A chronometer, like a TDC, used in a DTOF system timestamps the detected photons with a timing uncertainty determined by its root-mean-square (RMS) quantization error ( $\sigma_{TDC} = TDC_{res}/\sqrt{12}$ ). The computed histogram after TCSPC is representative of all the sources of timing uncertainties (shown as offsets or delays,  $\Delta T + \delta t_{total}$  in Figure 1.3) arising from the laser pulse, the SPAD and any electrical circuit through the propagation of the detected event. The total timing uncertainty,  $\sigma_{total}$ , is then given by the summation of the

RMS values of the individual contributors assuming that they are all statistically independent.

$$\sigma_{total} = \sqrt{\sigma_{laser}^2 + \sigma_{SPAD}^2 + \sigma_{TDC}^2 + \sigma_{other}^2},$$

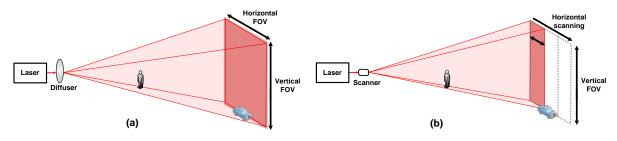

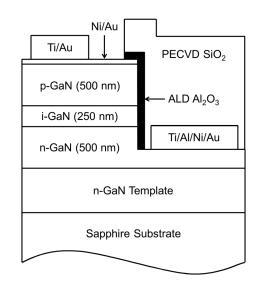

(1.3)