Thèse n° 8445

# EPFL

## Protection Coordination in Marine DC Power Distribution Networks

Présentée le 4 décembre 2020

à la Faculté des sciences et techniques de l'ingénieur Laboratoire d'électronique de puissance Programme doctoral en énergie

pour l'obtention du grade de Docteur ès Sciences

par

## Seongil KIM

Acceptée sur proposition du jury

Prof. K. A. J. Mulleners, présidente du jury Prof. D. Dujic, directeur de thèse Prof. S. Sul, rapporteur Dr J. Steinke, rapporteur Dr S.-R. Cherkaoui, rapporteur

École polytechnique fédérale de Lausanne

2020

École Polytechnique Fédérale de Lausanne Power Electronics Laboratory Station 11 1015 Lausanne, Switzerland https://www.epfl.ch/labs/pel © 2020 by Seongil Kim

Dedicated to my family with love

## Abstract

The increasing penetration of renewable energy sources, energy storage systems (ESSs), and DC loads (e.g., data center, electric vehicles, and home appliances) has opened the door to DC technology to pave its way into future grids. The shift has been more obvious in the marine domain supported by track records of installed onboard DC solutions since 2013. This new type of power system comes with technical challenges in protection coordination due to no natural current zero-crossing and low fault ride-through capability of power converters. This thesis has focused on the technical challenges tied to protection coordination in DC power distribution networks (PDNs). While marine applications are mainly considered for target DC PDNs, the work is not limited to this area alone.

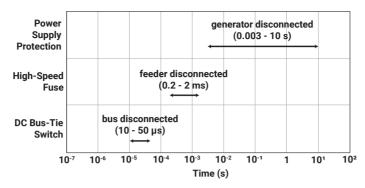

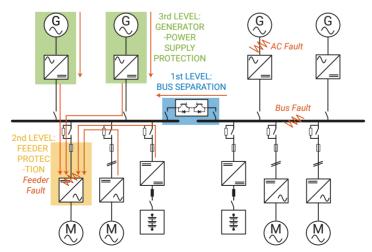

The thesis starts with the state-of-the-art analysis of marine DC PDN protection. The analysis shows that three-level protection, which consists of three-different time frame protections: fast action - bus separation; medium action - feeder protection; and slow action - power supply protections, has become the dominant trend for marine low-voltage DC PDNs selected for the main research field in the thesis. Along with the analysis, each protection measure is investigated by extensive simulation studies in terms of fault tolerance of equipment against fault energy limited by each measure. In these studies, additional bus capacitance (ABC) and artificial short-circuit methods have been proposed for extending selectivity of feeder protection and protecting voltage source converters (VSCs). The ABC method ensures the fault clearing by a reliable fuse operation that is assisted by the additional energy from the ABC only to the fuse on the faulty feeder. As an alternative to the fuse solution for the VSC protection, the artificial short-circuit method, which blocks the fault current to the rectifier by providing a low impedance path on the AC side, is verified by in-depth simulation studies.

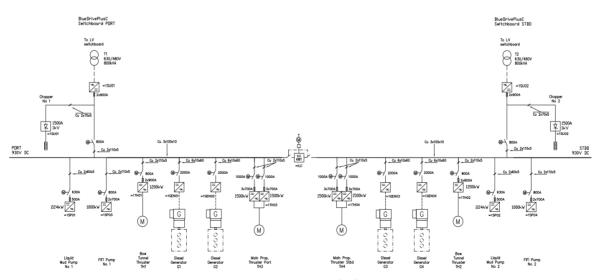

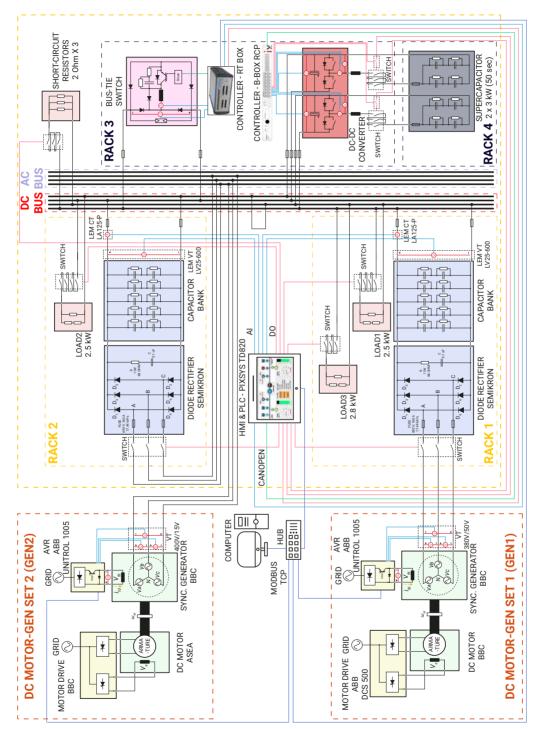

Two-bus DC PDNs rated for 35 kW and 500 V have been implemented for experimental studies. The DC PDNs consist of two DC motor-synchronous generator sets, two diode rectifier systems, a solidstate bus-tie switch, two supercapacitor banks, resistive loads, busbars, and a central controller. In the DC PDNs, the power supply protection method by generator deexcitation is characterized by comprehensive experimental tests for various system parameters. The analytical solution on the fault current during the deexcitation event is newly introduced for rectifier sizing and protection coordination. Apart from the protection topic, a wide range of DC PDN operations have been demonstrated in the implemented DC PDNs, ranging from basic to advanced operations: basic - DC voltage regulation and power sharing control, advanced - soft start (smoothly charging bus potential to the nominal level), seamless transition (transiting islanded and grid-connected modes), load leveling (flattening generator loads by ESSs), transient mitigation (mitigating sudden load changes by ESSs), and zero-emission (powering the marine networks by ESSs near a city or a port).

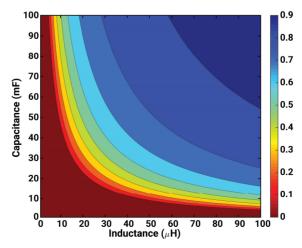

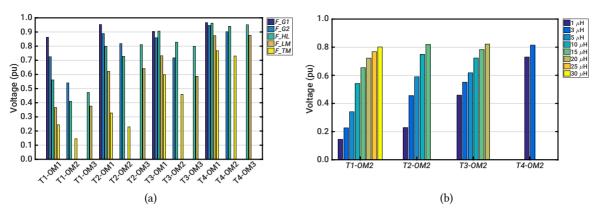

As the last work in the thesis, a protection scheme based on the three-level protection has been implemented in the DC PDNs. The influences of the system inductance and capacitance are investigated for the bus separation by the bus-tie switch to ensure its proper operation as well as the continuous operation of the adjacent healthy loads after the fault clearing by the fuse. Each protection measure and its settings are thoroughly coordinated from the investigation and the implemented protection scheme is verified by bus and feeder faults artificially generated in the networks. The results prove that the system protection can successfully isolate the faults from the networks with the correct operation of protection measures and enough time margins between the different protections.

**Keywords** DC microgrids, marine DC power distribution networks, fuse, generator deexcitation, protection coordination, protection scheme, solid-state circuit breaker, three-level protection

# Résumé

Le taux croissant des sources d'énergie renouvelables, des systèmes de stockage d'énergie et des charges en courant continu (par exemple, les centres de données, les véhicules électriques et les appareils ménagers) a ouvert la porte aux technologies en courant continu pour ouvrir la voie aux futurs réseaux. Le changement a été plus évident dans le domaine marin, soutenu par les nombreuses applications en courant continu installées à bord depuis 2013. Ce nouveau type de système d'alimentation présente des défis techniques dans la coordination de la protection dûs à l'absence de passage naturel de courant par zéro et à la faible capacité des convertisseurs de puissance à fournir l'alimentation sans panne. Cette thèse se porte sur les défis techniques liés à la coordination de la protection dans les réseaux de distribution d'énergie continue. Bien que les principales applications envisagées pour les réseaux de distribution d'énergie continue en courant continu sont les applications marines, le travail ne se limite pas que à ce domaine.

La thèse commence par l'analyse de l'état de l'art des systèmes de protection des réseaux de distribution d'énergie continue en courant continu. L'analyse montre que la protection à trois niveaux est devenue la tendance dominante pour les réseaux de distribution d'énergie continue en courant continu à basse tension dans les applications marines. Ce type de protection comporte trois protections temporelles différentes: action rapide - séparation de jeux de barres; action moyenne - protection du départ de ligne ; et action lente - les protections d'alimentation électrique. Ainsi la protection à trois niveaux a été sélectionnée comme le principal sujet de recherche de cette thèse. L'analyse de chaque mesure de protection est accompagnée de simulations approfondies qui étudient la tolérance des équipements aux pannes par rapport à l'énergie par défaut limitée par la mesure. Dans ces études, des méthodes de capacité supplémentaire de jeux de barres et de court-circuit artificiel ont été proposées pour étendre la sélectivité de la protection des départs des lignes et protéger les convertisseur à source de tension. La méthode de capacité supplémentaire de jeux de barres garantit l'élimination des défauts par un fonctionnement fiable des fusibles qui est assisté par l'énergie supplémentaire de la capacité supplémentaire de jeux de barres uniquement vers le fusible sur le départ des lignes défectueux. En alternative à la solution fusible pour la protection des convertisseur à source de tension, la méthode des courts-circuits artificiels, qui bloque le courant de défaut vers le redresseur en fournissant un chemin à faible impédance côté courant alternatif, est vérifiée par des études en utilisant des simulations approfondies.

Deux réseaux de distribution d'énergie continue en courant continu à deux bus cotés pour 35 kW et 500 V ont été mis en œuvre pour des études expérimentales. Les réseaux de distribution d'énergie continue en courant continu se consistent en deux groupes électrogènes synchrones à moteur en courant continu, de deux systèmes de redressement à diodes, d'un interrupteur de liaison de départ des lignes à semi-conducteurs, de deux batteries avec des supercondensateurs, de charges résistives, de jeux de barres et d'un contrôleur central. Dans les réseaux de distribution d'énergie continue, la méthode d'alimentation par désexcitation du générateur est caractérisée par des tests expérimentaux complets pour divers paramètres du système. La solution analytique sur le courant de défaut pendant l'événement de désexcitation est nouvellement introduite pour le dimensionnement du redresseur et la coordination de la protection. Outre le sujet de la protection, une large gamme d'opérations des réseaux de distribution d'énergie continue a été démontrée dans les réseaux de distribution d'énergie continue implémentés, allant des opérations basiques aux opérations avancées: de base - régulation de tension en courant continu et le contrôle de partage de puissance, avancé - démarrage progressif (charge en douceur du potentiel du bus au niveau nominal), transition transparente (transit des modes ilotés et connectés au réseau), nivellement de la charge (aplatissement des charges des générateurs

par les systèmes de stockage d'énergie), atténuation des transitoires (atténuation des changements de charge soudains par les systèmes de stockage d'énergie) et zéro émission (alimentation des réseaux marins par les systèmes de stockage d'énergie à proximité d'un ville ou un port).

En tant que dernier travail de la thèse, un schéma de protection basé sur la protection à trois niveaux a été implémenté dans les réseaux de distribution d'énergie continue en courant continu. L'influence de l'inductance et de la capacité du système est étudiée pour la séparation de jeux des barres par le commutateur de couplage de jeux des barres pour assurer son bon fonctionnement ainsi que le fonctionnement continu des charges saines adjacentes après la suppression du défaut par le fusible. Chaque mesure de protection et ses paramètres sont parfaitement coordonnés à partir de l'étude approfondie et le schéma de protection mis en œuvre est vérifié par des défauts de jeux des barres et de départ des lignes générés artificiellement dans les réseaux. Les résultats prouvent que la protection du système peut isoler avec succès les défauts des réseaux avec le bon fonctionnement des mesures de protection et des marges de temps suffisantes entre les mesures de protection.

**Keywords** réseaux en courant continu, réseaux de distribution d'énergie en courant continu marins, fusible, désexcitation du générateur, coordination de la protection, schéma de protection, disjoncteur à semi-conducteurs, protection à trois niveaux

# Acknowledgments

The big bird flies against the wind, the alive fish swims upstream against the current. Gu Kim

On the day of my turning 40, I am putting an end to my academic journey I have taken since the first day of 2017. As my PhD could be finalized with direct and indirect support from all the people around me, I would like to take this opportunity to express my gratitude and appreciation to them.

First of all, I wish to pay my special regards to my supervisor, Prof. Drazen Dujic, who persistently provided professional academic guidance and practical support during the entire period. He gave me lots of freedom in research which assisted me to fully explore my research interests. With his support, I had many chances to extend my networks by academic trips which also include several memorable trips with him, Niigata, Nuremberg, Yongin, and Seoul. I would like again to thank him and I am proud to have been a member of the power electronics laboratory (PEL).

The financial and technical assistance of Hyundai Electric & Energy Systems (HE) is truly appreciated. My PhD could have reached its goal with the support of my superiors in HE and I wish to express my deepest gratitude to them, Mr. Youngkeol Joo (former CEO), Mr. Myungrim Jung (former CEO), Dr. Jinsoo Park (former CTO), Mr. Joonyeob Lee (head of R&D), Mr. Ducksu Lee (team leader), and, special thanks to my HE supervisor, Dr. Soo-Nam Kim (department leader).

I wish to thank the committee members, Prof. Seung Ki Sul (Seoul National University, South Korea), Dr. Rachid Cherkaoui (EPFL, Switzerland), Dr. Jürgen Steinke (Hitachi ABB Power Grids, Switzerland), and Prof. Karen Mulleners (EPFL, Switzerland), who took their time to assess both my PhD thesis and examination with valuable feedbacks that helped me to improve the quality of the thesis.

My PhD cannot be completed without experimental tests, supported by my PEL colleagues, Mr. Roland Wetter, Mr. Gabriele Ulissi, and Dr. Jakub Kucka. I really enjoyed laboratory infrastructure implemented by Roland, a solid-state bus-tie switch by Gabriele, and DC-DC converters for supercapacitor banks by Jakub. Together with them, I would say thanks to all PEL members. It was my great pleasure to work with you and also have nice memories, Gaeta, Niigata, Nuremberg, Yongin, Seoul, Mon-Soleil, Champery, and various activities. I wish all the best to you.

I wish to show my gratitude to my master supervisor, Emeritus Prof. Jayoon Koo (Hanyang University, South Korea), and my senior laboratory colleague, Prof. Bang-Wook Lee (Hanyang University, South Korea), for providing me with valuable advice.

It was great to meet my friends, my colleagues, Korean association members, and football members. All the best in your future endeavours.

I wish to acknowledge the support and great love of my family, my wife, Ha Na; my daughters, Ryuna and Ria; my mother, Younghee; my sisters, Eunjoo and Myeongseo; and my parents in law, Minyong and Kyungja. I wish it would be great to enjoy my graduation with my father, Younggu.

Lausanne, September 26, 2020

# List of Abbreviations

| ABC     | additional bus capacitance                               |

|---------|----------------------------------------------------------|

| AC      | alternating-current                                      |

| AVR     | automatic voltage regulator                              |

|         |                                                          |

| DC      | direct-current                                           |

| DP      | dynamic positioning                                      |

|         |                                                          |

| EBL     | electronic bus link                                      |

| EEDI    | energy efficiency design index                           |

| EMTP-RV | electromagnetic transient program – restructured version |

| ESL     | equivalent series inductance                             |

| ESR     | equivalent series resistance                             |

| ESSs    | energy storage systems                                   |

|         |                                                          |

| HMI     | human machine interface                                  |

| HVDC    | high-voltage direct-current                              |

|         |                                                          |

| IED     | intelligent electronic device                            |

| IGBT    | insulated-gate bipolar transistor                        |

| ILC     | intelligent load controller                              |

| IMO     | International Maritime Organization                      |

|         |                                                          |

| KVL     | Kirchhoff's voltage law                                  |

|         |                                                          |

| LVDC    | low-voltage direct-current                               |

|         |                                                          |

| MMC     | modular multilevel converter                             |

| MOV     | metal oxide varistor                                     |

| MVDC    | medium-voltage direct-current                            |

|         |                                                          |

| РСВ     | printed circuit board                                    |

|         |                                                          |

| PDNs    | power distribution networks                 |

|---------|---------------------------------------------|

| PLC     | programmable logic controller               |

| PLL     | phase-locked loop                           |

| PMSG    | permanent magnet synchronous generator      |

| PSV     | platform support vessel                     |

| pu      | per unit                                    |

| PWM     | pulse width modulation                      |

|         |                                             |

| RB-IGCT | reverse blocking-integrated gate-commutated |

|         | thyristor                                   |

| RESs    | renewable energy sources                    |

| RMS     | root mean square                            |

|         |                                             |

| SA      | surge arrester                              |

| SEEMP   | ship energy efficiency management plan      |

| SFOC    | specific fuel oil consumption               |

| SG      | synchronous generator                       |

| SSCB    | solid-state circuit breaker                 |

|         |                                             |

| TCC     | time-current curve                          |

|         |                                             |

| VOC     | volatile organic compound                   |

| VSC     | voltage source converter                    |

# List of Symbols

| $C_{DC}$                     | DC-link capacitance                                                        |

|------------------------------|----------------------------------------------------------------------------|

| $I^2 t_D$                    | limiting load integral                                                     |

| $I^2 t_F$                    | fault current energy                                                       |

| I <sub>C</sub>               | collector current                                                          |

| $I_{cm}$                     | rated short-circuit making capacity                                        |

| I <sub>cs</sub>              | rated service short-circuit breaking capacity                              |

| $I_{F(AV)M}$                 | max. average forward current                                               |

| I <sub>FSM</sub>             | max. surge forward current                                                 |

| $I_p$                        | peak let-through current                                                   |

| $I_{T(AV)M}$                 | max. average forward current                                               |

| $I_{TSM}$                    | max. surge forward current                                                 |

|                              |                                                                            |

| $R_a$                        | stator winding resistance                                                  |

| $R_f$                        | fault resistance                                                           |

|                              |                                                                            |

| $T_a$                        | armature short-circuit time constant                                       |

| $t_d$                        | time delay                                                                 |

| $T_d'$<br>$T_d''$            | direct axis transient time constant                                        |

|                              | direct axis subtransient time constant                                     |

| $T_e$                        | exciter time constant                                                      |

|                              |                                                                            |

| $V_{CE}$                     | collector emitter voltage                                                  |

| $V_{DRM}$                    | max. repetitive peak forward blocking voltage                              |

| $V_{RRM}$                    | max. repetitive peak reverse blocking voltage                              |

| V                            |                                                                            |

| $X_d$ $X'_d$ $X''_d$ $X''_q$ | direct axis synchronous reactance                                          |

| $X_d$<br>X''                 | direct axis transient reactance                                            |

| v                            | 1 1                                                                        |

| $\Lambda_d$                  | direct axis subtransient reactance<br>quadrant axis subtransient reactance |

# Contents

| Ał | ostrac  | t                                                                             | i   |

|----|---------|-------------------------------------------------------------------------------|-----|

| Ré | sume    | é                                                                             | iii |

| Ac | knov    | vledgments                                                                    | v   |

| Li | st of A | Abbreviations                                                                 | vii |

| Li | st of S | Symbols                                                                       | ix  |

| 1  | Intr    | oduction                                                                      | 1   |

|    | 1.1     | Motivation                                                                    | 3   |

|    | 1.2     | Objectives and Contributions                                                  | 7   |

|    | 1.3     | Thesis Outline                                                                | 9   |

|    | 1.4     | List of Outcomes                                                              | 10  |

| 2  | State   | e-of-the-art                                                                  | 13  |

|    | 2.1     | Introduction                                                                  | 13  |

|    | 2.2     | General Overview of DC Protection                                             | 14  |

|    |         | 2.2.1 Fault Detection                                                         | 14  |

|    |         | 2.2.2 Fault Localization                                                      | 15  |

|    |         | 2.2.3 Fault Isolation                                                         | 15  |

|    |         | 2.2.4 Backup Protection                                                       | 17  |

|    | 2.3     | Protection Schemes                                                            | 18  |

|    |         | 2.3.1 Zonal Protection                                                        | 18  |

|    |         | 2.3.2 Differential and Directional Protections                                | 19  |

|    |         | 2.3.3 Three-Level Protection                                                  | 19  |

|    |         | 2.3.4 Earth Fault Protection                                                  | 21  |

|    | 2.4     | Application Cases of the Three-Level Protection                               | 21  |

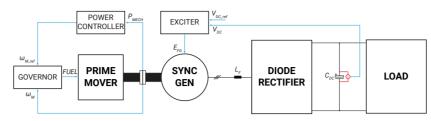

|    |         | 2.4.1 Diode Rectifier-Based PDNs                                              | 22  |

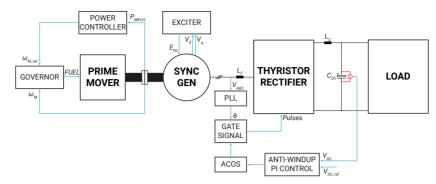

|    |         | 2.4.2 Thyristor Rectifier-Based PDNs                                          | 24  |

|    |         | 2.4.3 VSC-Based PDNs                                                          | 25  |

|    |         | 2.4.4 Summary                                                                 | 26  |

| 3  | Exte    | ending Selectivity for Feeder Protection Utilizing Additional Bus Capacitance | 27  |

|    | 3.1     | Introduction                                                                  | 27  |

|    | 3.2     | Study Considerations                                                          | 28  |

|    |         | 3.2.1 DC PDN Modeling                                                         | 28  |

|    |         | 3.2.2 System Parameters and Conditions                                        | 30  |

|    | 3.3     | Proposed ABC Method                                                           | 32  |

|    |         | 3.3.1 Effect of ABC Method on Bus Separation Failure                          | 32  |

|    |         | 3.3.2 Effect of ABC Method on Feeder Protection                               | 34  |

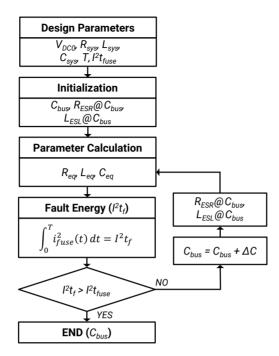

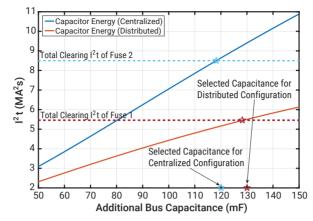

|    |         | 3.3.3 Sizing of ABC                                                           | 35  |

|    | 3.4     | Verification                                                                  | 36  |

|   |      | 3.4.1 Bus                          | Separation Failure                                            | 37              |

|---|------|------------------------------------|---------------------------------------------------------------|-----------------|

|   |      | 3.4.2 Feed                         | ler Protection                                                | 38              |

|   | 3.5  | Conclusion                         |                                                               | 41              |

| 4 | Inve | stigation on                       | the Power Supply Protection for Different Types of Rectifiers | 43              |

|   | 4.1  | Introduction                       |                                                               | 43              |

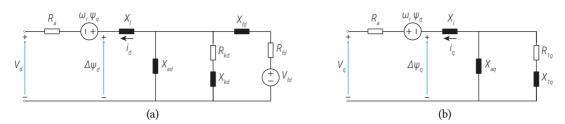

|   | 4.2  | System Mod                         |                                                               | 44              |

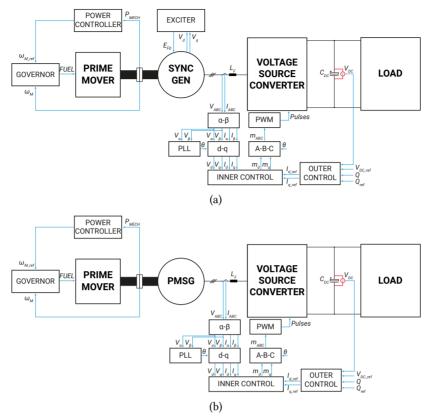

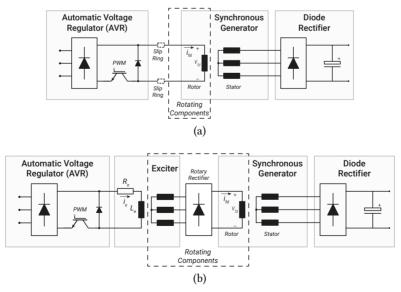

|   |      |                                    | el Engine-Driven Synchronous Generator                        | 44              |

|   |      | 1                                  | er Distribution Lines and Filters                             | 47              |

|   |      | 1 0                                | l and Fault                                                   | 48              |

|   |      |                                    | le Rectifier                                                  | 48              |

|   |      | •                                  | ristor Rectifier                                              | 49              |

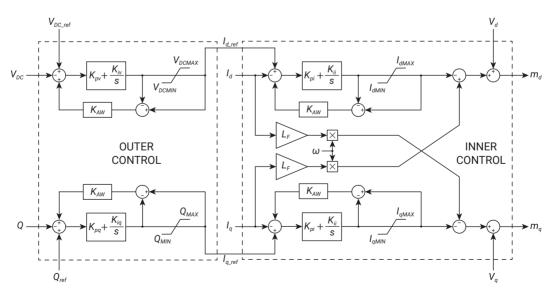

|   |      |                                    | age Source Converter                                          | 49              |

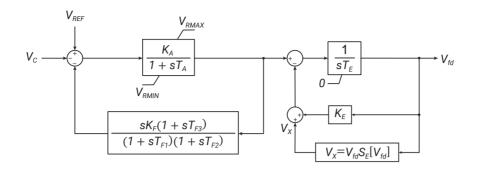

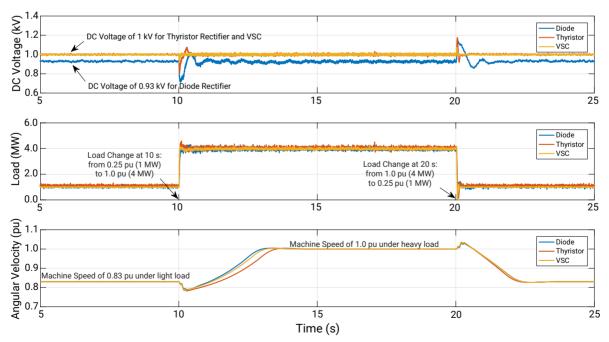

|   |      | 1 /                                | ulation Model Verification                                    | 51              |

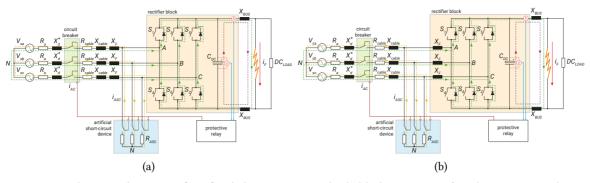

|   | 4.3  | Proposed Ai                        | rtificial Short-Circuit Method                                | 52              |

|   |      | 4.3.1 Wor                          | king Principle of the Proposed Method                         | 52              |

|   |      | 4.3.2 Sizir                        | ng of Artificial Short-Circuit Resistance                     | 53              |

|   | 4.4  | Protection N                       | Nethod Assessment                                             | 54              |

|   |      | 4.4.1 Stud                         | ly Conditions                                                 | 54              |

|   |      | 4.4.2 Gen                          | erator Deexcitation for Diode Rectifier                       | 55              |

|   |      | 4.4.3 Fold                         | -Back Protection Control for Thyristor Rectifier              | 56              |

|   |      | 4.4.4 Arti                         | ficial Short-Circuit for VSC                                  | 57              |

|   | 4.5  | Conclusion                         |                                                               | 59              |

| 5 | Imp  | act of Synch                       | ronous Generator Deexcitation Dynamics on Diode Rectifier Pro | otec-           |

|   | tion |                                    |                                                               | 61              |

|   | 5.1  | Introduction                       | 1                                                             | 61              |

|   | 5.2  | Theoretical                        | Considerations                                                | 62              |

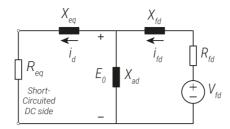

|   |      | 5.2.1 DC                           | Short-Circuit in Six-Pulse Diode Rectifier                    | 62              |

|   |      | 5.2.2 Trar                         | nsient Phenomena in Synchronous Generator                     | 63              |

|   |      | 5.2.3 Dee:                         | xcitation of Synchronous Generator                            | 64              |

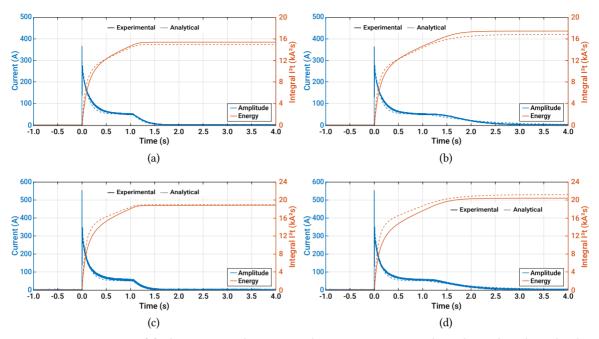

|   |      | 5.2.4 Veri                         | fication of the Analytical Expression                         | 66              |

|   |      | 5.2.5 Disc                         | russion on the Rectifier Sizing                               | 67              |

|   | 5.3  | Deexcitation                       | n Characteristics                                             | 68              |

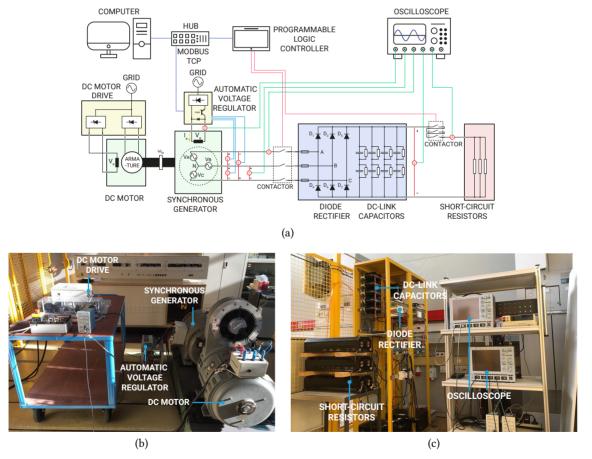

|   |      | 5.3.1 Stud                         | ly Parameters and Test Setup                                  | 69              |

|   |      | 5.3.2 DC                           | Fault Behaviour                                               | 70              |

|   |      | 5.3.3 Influ                        | ience of Subtransient Reactance                               | 71              |

|   |      | 5.3.4 Influ                        | ience of Fault Resistance                                     | 72              |

|   |      | 5.3.5 Influ                        | ience of DC-link Capacitance                                  | 73              |

|   |      | 5.3.6 Influ                        | ience of Different Exciter Types                              | 74              |

|   |      | 5.3.7 Influ                        | ience of Time Delay                                           | 75              |

|   | 5.4  | Conclusion                         |                                                               | 76              |

|   | 0 1  |                                    |                                                               |                 |

| 6 |      | onstration                         | of Flexible DC Power Distribution Network Operations          | 79              |

| 6 |      | <b>ionstration</b><br>Introduction | -                                                             | <b>79</b><br>79 |

|   |      | 6.2.1 DC Motor-Synchronous Generator Set                                 | 80  |

|---|------|--------------------------------------------------------------------------|-----|

|   |      | 6.2.2 Rectifier Systems                                                  | 83  |

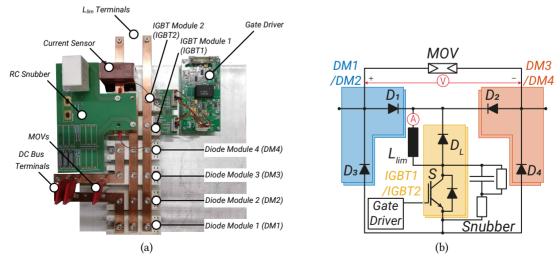

|   |      | 6.2.3 Solid-State Bus-Tie Switch                                         | 84  |

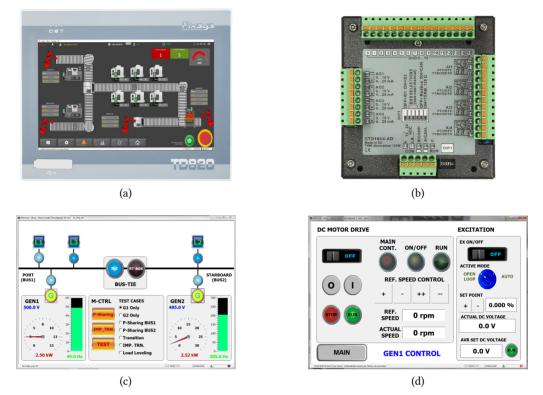

|   |      | 6.2.4 Programmable Logic Controller                                      | 86  |

|   | 6.3  | Two-Bus DC System Control                                                | 87  |

|   |      | 6.3.1 DC Voltage Regulation                                              | 87  |

|   |      | 6.3.2 Power Sharing Control                                              | 88  |

|   |      | 6.3.3 Soft Start                                                         | 90  |

|   |      | 6.3.4 Seamless Transition                                                | 90  |

|   | 6.4  | Experimental Results                                                     | 91  |

|   |      | 6.4.1 Voltage Regulation and Soft Start                                  | 92  |

|   |      | 6.4.2 Power Sharing                                                      | 94  |

|   |      | 6.4.3 Seamless Transition                                                | 95  |

|   | 6.5  | Conclusion                                                               | 96  |

| 7 | DC   | Power Distribution Networks with Integrated Energy Storage               | 97  |

|   | 7.1  | Introduction                                                             | 97  |

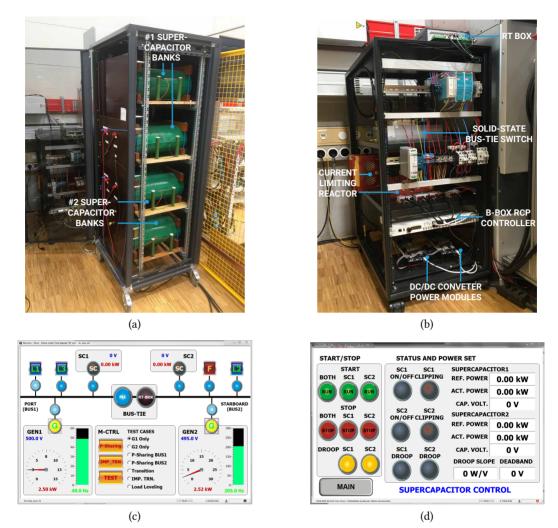

|   | 7.2  | Supercapacitor-Based Energy Storage Systems                              | 98  |

|   | 7.3  | Supercapacitor Bank Control                                              | 100 |

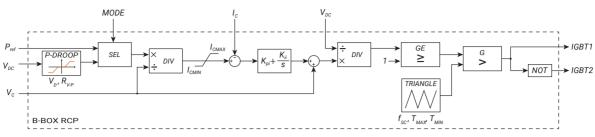

|   |      | 7.3.1 DC-DC Converter Control                                            | 101 |

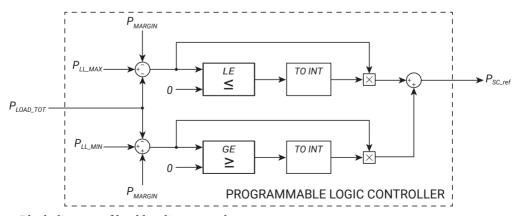

|   |      | 7.3.2 Load Leveling                                                      | 101 |

|   |      | 7.3.3 Power Droop                                                        | 102 |

|   | 7.4  | Experimental Results                                                     | 102 |

|   |      | 7.4.1 Load Leveling                                                      | 103 |

|   |      | 7.4.2 Transient Mitigation                                               | 104 |

|   |      | 7.4.3 Zero-Emission                                                      | 105 |

|   | 7.5  | Conclusion                                                               | 106 |

| 8 | Inte | grated Protection Scheme for DC Power Distribution Networks              | 107 |

|   | 8.1  | Introduction                                                             | 107 |

|   | 8.2  | Implementation of Protection Scheme                                      | 108 |

|   |      | 8.2.1 Protective Devices and Scheme                                      | 108 |

|   |      | 8.2.2 Influence of the Current Limiting Inductance on the Bus Separation | 110 |

|   |      | 8.2.3 Influence of the DC-Link Capacitance                               | 111 |

|   | 8.3  | Protection for Bus Faults                                                | 112 |

|   | 8.4  | Protection for Feeder Faults                                             | 114 |

|   | 8.5  | Conclusion                                                               | 117 |

| 9 |      | clusions and Future Works                                                | 119 |

|   | 9.1  | Summary and Contributions                                                | 119 |

|   | 9.2  | Overall Conclusion                                                       | 121 |

|   | 9.3  | Future Works                                                             | 121 |

|   |      | 9.3.1 Protection Scheme for MVDC PDNs                                    | 121 |

|   |      | 9.3.2 Hybrid AC-DC Protection Coordination                               | 121 |

|   |      | 9.3.3 Development of Cost-Effective DC Circuit Breakers                  | 122 |

| Ap | pend | lices                          | 123 |

|----|------|--------------------------------|-----|

| A  | DC S | Short-Circuit Current Equation | 125 |

| В  | Tim  | e Domain Simulation Models     | 129 |

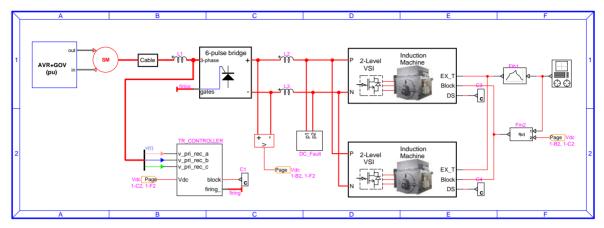

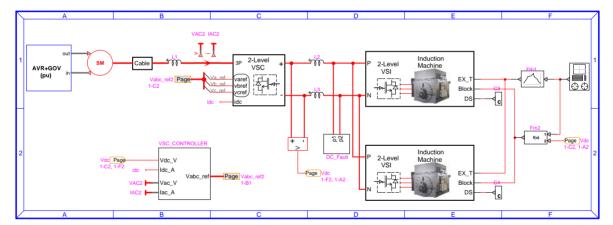

|    | B.1  | Diode Rectifier-Based PDNs     | 129 |

|    | B.2  | Thyristor Rectifier-Based PDNs | 130 |

|    | B.3  | VSC-Based PDNs                 | 130 |

# **1** Introduction

On December 31, 1879, the first power distribution networks (PDNs) for incandescent light bulbs were demonstrated by the form of direct-current (DC) [1]. It was followed by the widespread use of the electricity based on the application of DC, which had reached its application in lighting by 1887, powering 103 central stations with 311,400 lamps in the US [2]. This technology was also employed in marine domain. The first electrical installation in marine PDNs was made by DC on the American passenger and freight ship, *SS Columbia*, in 1880 [see **Fig. 1.1(a**)] [3]. Shortly thereafter, this new technology was broadly accepted by both military and commercial vessels, e.g., the German ferry, *Elektra*, in 1886 [see **Fig. 1.1(b)**], the Spanish submarine, *Peral*, in 1888, the American cruiser, *USS Brooklyn*, in 1896, and so forth [3]–[5].

The glory days of the DC power systems were ended with the emergence of the alternating-current (AC) transformer and the AC induction motor in commercial use. With an increase in electrical power demands, the main drawbacks of the DC power system became unequivocally clear in the early 1900s. Compared to AC, it was heavier, larger, and, most importantly, it was difficult to change a voltage level which caused higher power losses and voltage drops for long-distance distribution. Consequently, DC had been gradually losing its dominant position not only in electrical power grids but also in marine PDNs. It is the well-known story of "War of the Currents".

To date, present power systems have been mostly based on the AC technology. The evolution of power electronics technologies, however, allows us to focus on the DC technology again for both power grids and ship networks. Some said this new movement as "Edison's Revenge" or "the Second War of the Currents" [6]. Now, the transition has become reality in modernized electrical grids and marine networks in which power electronics play an important role.

**Fig. 1.1** (a) *SS Columbia*, an excursion steamboat [7] and (b) *Elektra*, an electric boat at the international electrical engineering fair in Frankfurt [8].

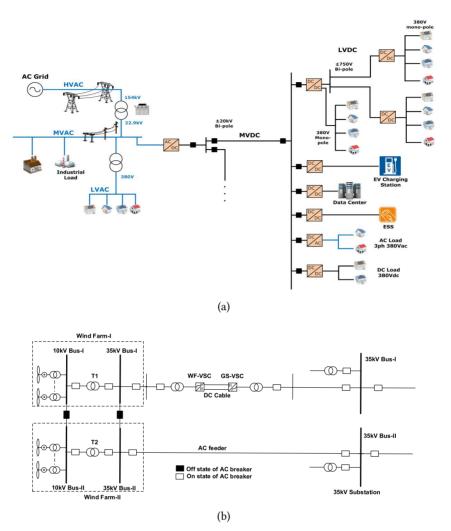

**Fig. 1.2** (a) Example of DC grid configuration in South Korea [9] and (b) network topology of Shanghai Nanhui DC project in China [10].

Conventionally, electricity is transmitted from bulky power plants to consumers through complex electrical networks. During the transmission and the distribution, step-up and step-down voltage conversions are crucially required to minimize power losses. Those have been mostly done by the AC transformers, becoming a key component for voltage coordination. Recently, however, the rapid expansion of renewable energy sources (RESs), energy storage systems (ESSs), and DC loads (e.g., data center, electric vehicles, and home appliances), which are connected through power converters and/or have the DC nature, has opened the door to the DC technology to integrate these new types of power sources and loads more easily or efficiently into the grids, as shown in **Fig. 1.2**. This change has also extended DC PDNs from point-to-point to meshed multi-terminal links [11].

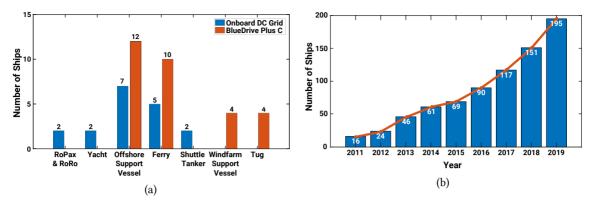

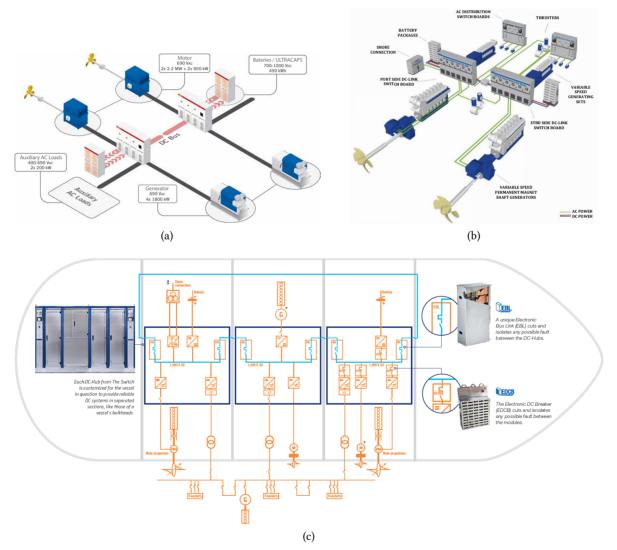

The shift has been observed more obviously in the marine domain. In April 2013, ABB delivered the first platform support vessel (PSV), *Dina Star*, built by its solution 'Onboard DC Grid' [12]. In October of the same year, Siemens also delivered the DC-powered PSV, *Edda Ferd*, equipped with 'BlueDrive Plus C' [13]. The last six years have witnessed outstanding growth of DC-powered dynamic

**Fig. 1.3** (a) DC ships built by 'Onboard DC Grid' and 'BlueDrive Plus C' since 2013 [15], [16] and (b) ships with installed battery energy storage systems [17].

positioning (DP) and passenger vessels. There are 48 ships and more constructed by the two solutions for this period, as shown in **Fig. 1.3(a)**. Moreover, the increase in the battery integration on a ship [see **Fig. 1.3(b)**] shows that the ship network towards DC PDNs due to its DC nature. The representative ship is the world's first large-size battery-powered Norwegian car ferry, *Ampere*, in 2015 [14]. With these trends, it could be stated that the DC technology has been becoming one of the prominent options for some types of vessels.

### 1.1 Motivation

According to [18], international shipping emitted more than 2.2% of the total  $CO_2$  emission in 2012. Furthermore, it is expected that the emission level will rise 50% to 250% by 2050 depending on future economic growth and energy consumption. As the global standard-setting authority, in 2011, the International Maritime Organization (IMO) adopted mandatory energy efficiency regulations [e.g., energy efficiency design index (EEDI) and ship energy efficiency management plan (SEEMP)] to control the greenhouse gas emissions from the shipping sector. In accordance with the EEDI as presented in **Tab. 1.1**, newly constructed ships of 400 gross tonnages and above have to increase the energy efficiency to meet the reduction rates, consisting of the three phases. Finally, by 2025, the ships have to be designed to have 30% less energy consumption than those built in 2004.

|                            | Phase o             | Phase 1             | Phase 2             | Phase 3              |

|----------------------------|---------------------|---------------------|---------------------|----------------------|

| Ship Type                  |                     |                     |                     | 5                    |

|                            | Jan 2013 - Dec 2014 | Jan 2015 - Dec 2019 | Jan 2020 - Dec 2024 | Jan 2025 and onwards |

| Bulk carrier               | 0                   | 10                  | 20                  | 30                   |

| Gas carrier                | 0                   | 10                  | 20                  | 30                   |

| Tanker                     | 0                   | 10                  | 20                  | 30                   |

| Container ship             | 0                   | 10                  | 20                  | 30                   |

| General cargo ship         | 0                   | 10                  | 15                  | 30                   |

| Refrigerated cargo carrier | 0                   | 10                  | 15                  | 30                   |

| Combination carrier        | 0                   | 10                  | 20                  | 30                   |

**Tab. 1.1** Reduction factors in percentage for EEDI. Data from [19].

A ship is an off-grid stand-alone system (or a microgrid) without the need to comply with strict utility grid codes, which allows for the flexibility to utilize a new concept of power systems. This is one of the reasons why the movement toward DC has been proceeding actively in the marine sector. The other reason is more importantly that the DC technology could improve the vessel's fuel efficiency with the following advantages:

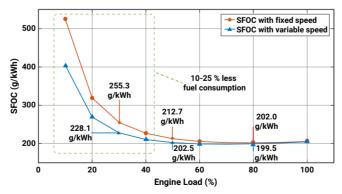

**Fuel saving with variable-speed generators.** Typical marine engines are designed to have the optimum specific fuel oil consumption (SFOC) in the 60-80% load range with the rated rotational speed [20]. On the other hand, reduced rotational speeds are required to minimize the fuel consumption at lower engine loads, as shown in **Fig. 1.4**. While the machine rotational speed in AC PDNs has to be a constant to maintain system frequency at any engine loads, DC permits the use of variable-speed generators because AC of any frequency is converted to DC in DC PDNs. With the variable-speed generator, fuel savings achieved are about 25% at 10% loading and about 10% at 40% loading, respectively, in the calculated case (see **Fig. 1.4**).

**Easy integration of ESSs.** To integrate ESSs in AC PDNs, at least one AC-DC converter is necessary between the system and the ESSs which have their terminals with DC. Depending on output voltages of ESSs and types of AC-DC converters, a DC-DC converter may be additionally requested. By contrast, ESSs can be connected to DC PDNs through a DC-DC converter or directly (without any converters). The fewer conversion stages help to cut down converter cost and power losses. To conclude, ESSs could be more easily integrated in DC PDNs. The benefits with the ESS installation are: zero-emission operation at harbours, running fewer engines, running engines at optimal loads, avoiding transient engine loads, and facilitating energy harvesting [21].

**Weight and footprint reduction in electrical installations.** First of all, with the freedom from dependency on a constant AC frequency, high-density high-speed machines, which have smaller weight and volume compared to the fixed systems, can be applied in DC PDNs. Secondly, bulky transformers, which are essential for voltage coordination and harmonics mitigation in AC PDNs, are not needed in DC PDNs. Lastly, the use of AC switchgear can be avoided in DC PDNs with new protection schemes, not relying on conventional mechanical breakers and relays. [23] provides a weight comparison example for a PSV. The weight reduction is about 26% compared to the traditional AC concept.

**Fig. 1.4** Comparison of SFOC between fixed-speed and variable-speed generators. The SFOC is calculated by the data from [22].

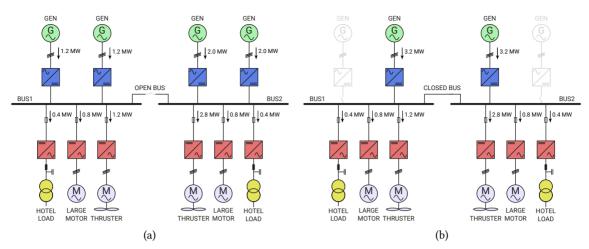

Fig. 1.5 Example of power generation and consumption in DP vessels: (a) open bus and (b) closed bus.

**Tab. 1.2** Comparison of fuel consumption between open-bus and closed-bus operations in DP vessels. The SFOC values are taken from **Fig. 1.4** at 30%, 50% and 80% load conditions. For the power generation of 6.4 MWh, the conditions assumed are: open bus - two generators at 30% load and two generators at 50% load [see **Fig. 1.5(a**)] and closed bus - two generators at 80% load [see **Fig. 1.5(b**)].

| Generator Type | SF     | SFOC (g/kWh) |        | Fuel Consumption at 6.4 MWh (kg) |            | Fuel Saving (%) |  |

|----------------|--------|--------------|--------|----------------------------------|------------|-----------------|--|

| Generator Type | at 30% | at 50%       | at 80% | Open Bus                         | Closed Bus | Fuel Saving (%) |  |

| Fixed speed    | 255.3  | 212.7        | 202.0  | 1463.6                           | 1292.5     | 11.7            |  |

| Variable speed | 228.1  | 202.5        | 199.5  | 1357.7                           | 1276.8     | 6.0             |  |

**Optimization of running engines by closed-bus operation.** During the DP mode, a bus-tie switch, which is a device to connect and disconnect two bus sections (see **Fig. 1.5**), should be normally open due to the safety in AC PDNs [24]. To provide electric power needed in this mode, almost all generators should be in operation for heavy as well as light load conditions and this makes DP ships inefficient [see Fig. 1.5(a)] [25]. This limitation can be overcome by using DC PDNs based on solid-state technologies. With solid-state bus-tie switches operated within several tens of microseconds, the closed-bus operation, which allows for reducing the number of running engines, is possible without the safety issue in the DP mode [see **Fig. 1.5(b)**] [26]. An example of the fuel saving with the running engine optimization is provided in **Tab. 1.2**.

The attractive new systems bring with technical challenges in protection coordination, a result of no natural current zero-crossing, very low fault withstand capability of power converters, hybrid AC-DC protection coordination, and no standard for system configurations and protection schemes. The details of the challenges are as follows:

**No natural current zero-crossing**. When a fault is detected in AC systems, a circuit breaker interrupts the fault current by actuating the moving contact backwards from the fixed contact. Initially, although the two contacts are separated mechanically, they are connected electrically through the arc. In AC, the arc is extinguished at every current zero-crossing. If the dielectric strength between the two contacts is higher than the recovery voltage at the instant of the zero-crossing, the current could be finally interrupted in the time ranges about 3-5 cycles (60 - 100 ms at 50 Hz) [28].

Contrarily, there is no polarity change in the DC fault current. To extinguish the current without the zero-crossing, mechanical DC circuit breakers are based on a high volume of arc chutes [29]. When the contacts are open, the arc is established and then the arc moves to the arc chute. The reversal arc voltage, which is proportional to the arc distance, is built up and the current is quenched if the arc voltage is higher than the source voltage. When the solid-state technologies are employed alone or in combination with mechanical elements (a hybrid circuit breaker), the increase in cost cannot be avoided due to the increasing number of components requested. Additionally, these circuit breakers will lead to additional operational cost caused by on-state power losses in semiconductors. To sum up, the DC fault characteristics make the development of DC circuit breakers difficult or costly compared to conventional AC circuit breakers.

**Very low overloading capability of power converters**. Conventional AC equipment is designed to sustain the maximum fault current over several hundreds of milliseconds [30], [31]. Taking a power transformer as an example, the maximum fault current under the worst condition is calculated during the design phase. Based on this current, the electrical and mechanical design of the transformer is conducted to withstand the current as well as the electromotive force generated by the current for 500 ms [30]. This high overloading capability provides an enough time to proceed all the process of system protection, i.e., fault detection, fault localization, fault isolation, and backup protection.

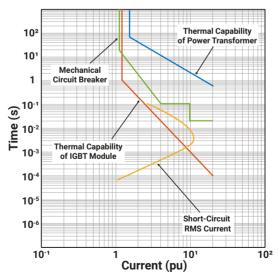

Differently with the AC protection, such a time frame in order of several hundreds of milliseconds is unavailable for the DC protection. The fault in DC PDNs should be typically cleared within the range of several milliseconds [32]. This is because a power converter based on semiconductors has very low overloading capability (see **Fig. 1.6**). This implies multiple things. First, fast circuit interrupters are indispensable to handle the fault current within a given time. Secondly, the DC protection should be much faster than the AC protection. Lastly, additional devices (e.g., current limiting inductors) or oversized semiconductors are needed if the protection is not operated for the time range of semiconductor overloading capability.

**Fig. 1.6** Time-current curve (TCC) comparison of AC and DC devices against root mean square (RMS) shortcircuit current [27]. This exemplary TCC shows that the power transformer can be protected by the mechanical circuit breaker, while the failure of the insulated-gate bipolar transistor (IGBT) module cannot be avoided.

**Tab. 1.3** Generator-rectifier combination matrix and multi-phase multi-pulse power supply configurations [33]. While a synchronous generator (SG) can be combined with four different rectifiers, a permanent magnet synchronous generator (PMSG) can be only coupled with active rectifiers [e.g., conventional voltage source converter (VSC) and modular multilevel converter (MMC)] due to lack of its excitation control. Note that a recent work of [34] has proposed the combination of a PMSG and a diode rectifier.

| Gene           | rator-Rect     | tifier Combin | Nya-Phase Ny | v6-Pulse Power Supply |               |                                  |  |  |

|----------------|----------------|---------------|--------------|-----------------------|---------------|----------------------------------|--|--|

| Generator Type | Rectifier Type |               |              |                       |               | Nx3-Phase Nx6-Pulse Power Supply |  |  |

| Generator Type | Diode          | Thyristor     | VSC          | MMC                   | Configuration | Remarks                          |  |  |

| SG             | 1              | 1             | 1            | 1                     | Parallel      | Constant V & Increasing I        |  |  |

| PMSG           |                |               | 1            | 1                     | Series        | Increasing V & Constant I        |  |  |

**Hybrid AC-DC protection coordination**. While the distribution network is formed with DC, the power generation and consumption have still relied on mature and economic AC technologies. The protection of the conventional AC protection should consequently be coordinated with the newly employed DC protection. For the reliable hybrid AC-DC protection coordination, several differences between both systems have to be taken into account: equipment overloading capabilities, fault characteristics, protection schemes, and protective devices.

**No standards for system configurations and protection schemes**. At this early stage of DC PDNs, the standard configurations and protections, widely accepted or internationally standardized, are not established. Currently, industrial manufacturers have pushed the market forward with their solutions, having different configurations and protections. On the other hand, the design and protection of DC PDNs are more complicated by the use of solid-state technologies in contrast to AC PDNs. Power supply systems in DC PDNs are a representative example. There are various combinations of generators and rectifiers, as provided in **Tab. 1.3**. Furthermore, multi-phase multipulse power supply systems can be configured in series and parallel [33]. This complexity in the combination and the configuration is one of the main barriers to establish the standard configurations and the protection schemes for DC PDNs.

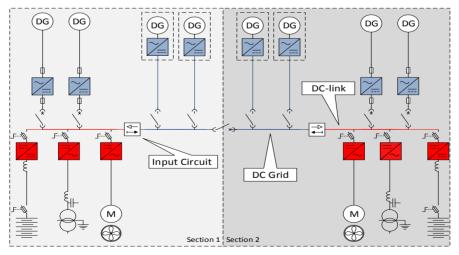

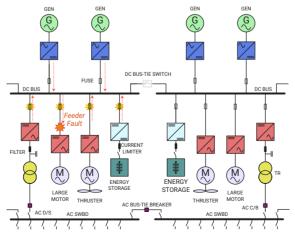

## 1.2 Objectives and Contributions

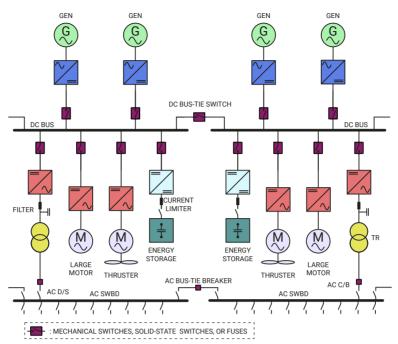

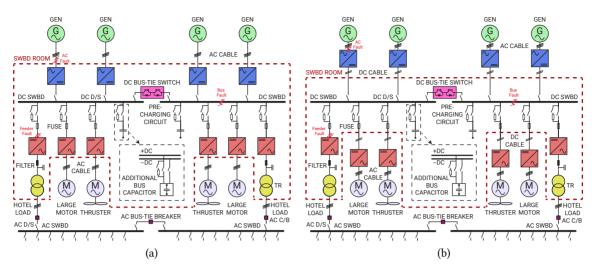

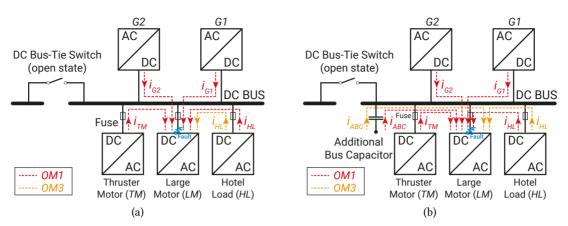

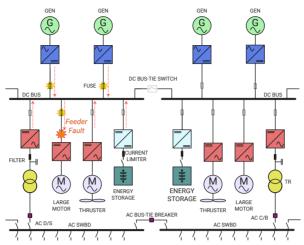

In the view of the above discussions, this thesis focuses on the technical challenges tied to protection coordination in DC PDNs, predominantly focusing on marine applications, but not limited to, which could represent DC microgrids (off-grid stand-alone grids) including power supplies, distribution systems, loads, and ESSs, as shown in **Fig. 1.7**. The two-bus DC PDNs considered for all case studies presented in the thesis consist of two supplies, a thruster, a large motor, and a hotel load (connected through AC switchboard) at each bus. Both DC buses are connected through a DC bus-tie switch based on solid-state technology. Also, synchronous generators coupled with diode, thyristor, and active rectifiers are taken into account for the power supply systems.

Based on the two-bus DC PDNs, the thesis aims to extend an up-to-date protection method (three-level protection, as discussed later), commercially adopted, for marine DC PDNs. The objectives selected to achieve the main goal are as follows:

Fig. 1.7 Considered DC microgrids consisting of power supplies, distribution systems, loads, and ESSs.

- Improvement of feeder protection by fuse technology in terms of selectivity and sensitivity.

- Examination of power supply protection concerning overloading capabilities of rectifiers.

- Characterization of the impacts of synchronous generator deexcitation during fault events

- Demonstration of flexible DC grid operations with solid-state technologies and ESSs.

- Verification of integrated three-level protection extended in this work.

Taking the three-level protection as the fundamental protection scheme, the main contribution of this thesis is the extension of the three-level protection for reliable protection coordination. Further detailed contributions of the thesis are summarized hereafter.

- An additional bus capacitance (ABC) method is proposed for the feeder protection based on high-speed fuses, aiming to provide selectivity and sensitivity under any fault conditions. The performance of the ABC method is verified by simulation studies and experimental tests.

- Overloading capabilities of a diode rectifier, a thyristor rectifier, and VSCs are analyzed against DC short-circuit currents limited by each power supply protection. As a new solution, an artificial short-circuit method is proposed for the VSC protection, which currently relies on the fuse technology.

- Dynamic behaviours of the synchronous generator deexcitation are investigated with analytical and experimental approaches. Furthermore, for the deexcitation, comprehensive system studies are provided for different subtransient reactance, fault resistance, DC-link capacitance, fault resistance, exciter response, and time delay.

- Flexible operating modes of DC PDNs are demonstrated with the solid-state DC bus-tie switch, which has a smooth potential charging function, and the supercapacitor-based ESSs. The operating modes demonstrated are: automatic DC voltage regulation, power sharing function, soft start, seamless transition, load leveling, transient mitigation, and zero-emission.

- A protection scheme based on the three-level protection is implemented in the DC PDNs. Each protection measure and its settings are thoroughly coordinated and the implemented protection scheme is verified by bus and feeder faults artificially generated in the networks. The results prove that the system protection can successfully isolate the faults from the networks with the correct operation of protection measures.

## 1.3 Thesis Outline

This thesis is organized in 9 chapters.

**Chapter 2** provides an overview of the general protection technologies in DC power distribution networks as well as the state-of-the-art protection schemes in marine DC power distribution networks. The analysis shows that the three-level protection, which consists of three-different time frame protections: fast action - bus separation; medium action - feeder protection; and slow action - power supply protections, has become the dominant trend for marine low-voltage DC power distribution networks selected for the main research field in the thesis.

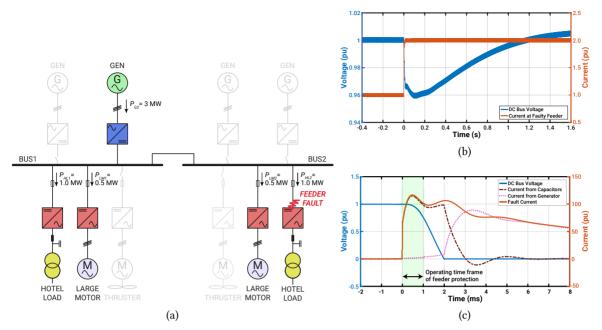

**Chapter 3** presents the feeder protection by high-speed fuses. The additional bus capacitance method, which can supply the additional energy only to the fuse on the faulty feeder during a fault event, is proposed to ensure the fault interruption by a reliable fuse operation with the consideration of selectivity and sensitivity. The performance of the proposed method is verified by extensive simulation studies under various conditions.

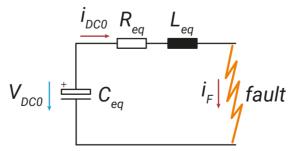

**Chapter 4** investigates the performance of power supply protection methods with various case studies. The modeling of three-different low-voltage DC power distribution networks is carried out with the discussions on their configurations, design considerations, and controls. The performance of each protection method is analyzed by comparing the fault energy limited by the protection method and the overloading capability of rectifiers. Moreover, an artificial short-circuit method, which limits the fault current to the rectifier by providing a low impedance path on the AC side, is proposed for the voltage source converter protection.

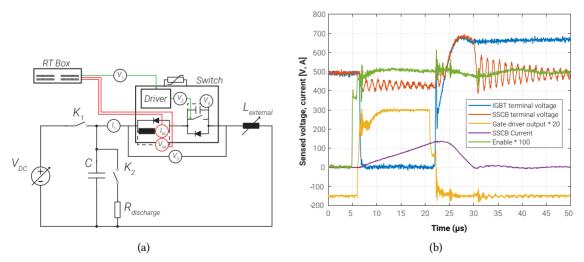

**Chapter 5** presents the impacts of synchronous generator deexcitation dynamics on the diode rectifier protection. The analytical expression of a DC short-circuit current is introduced considering a circuit topology, transient generator dynamics, and generator deexcitation. The DC fault currents under the deexcitation are comprehensively examined for different system factors: subtransient reactance, fault resistance, DC-link capacitance, exciter response, and time delay. Results are collected from a scaled-down experimental test setup.

**Chapter 6** demonstrates flexible operating modes of two-bus DC power distribution networks, consisting of two generators operated at different frequencies. First, automatic DC voltage regulation of each power supply is verified by step-load changes. Secondly, power sharing function is implemented and validated with two different tests. Lastly, two operating modes for the DC power distribution

networks are demonstrated with new functions of the solid-state bus-tie switch: soft start - smoothly charging bus potential to the nominal level; and seamless transition - promptly supplying electric power to the bus experienced a power outage during the open-bus operation.

**Chapter 7** presents extended DC system operating modes with energy storage systems. For the energy storage systems, two supercapacitor banks  $(2 \times 2F)$  are integrated into the lab-scaled test setup through DC-DC converters. The potential benefits of energy storage inside the DC power distribution networks are examined with the demonstration of the following operating modes: transient mitigation - supporting transient demands by energy storage with short time constants; load leveling (peak shaving) - operating generators at optimal loads by storing energy during light load conditions and providing it during too heavy load conditions; and zero-emission operation - turning *OFF* generators and powering the networks by energy storage when a ship is entering or exiting a port.

**Chapter 8** validates an integrated protection scheme in two-bus DC power distribution networks. The three-level protection is implemented in the lab-scaled test setup (fast action - bus separation by a solid-state bus-tie switch, medium action - feeder protection by a high-speed fuse, and slow action - generator deexcitation). The protection scheme is evaluated by testing actual operating times of the three actions and the fault energies limited by those. Bus and feeder faults are artificially generated in the networks, and the system protection successfully isolates the faults from the networks with the correct operation of protection measures and enough time margins between the actions.

**Chapter 9** summarizes the main findings and the contributions of the thesis. In addition to the summaries, future research perspectives in this topic are outlined.

## 1.4 List of Outcomes

The scientific outcomes in conjunction with the PhD thesis are:

Journal papers:

- J1. **S. Kim**, G. Ulissi, S.-N. Kim, and D. Dujic, "Protection coordination for reliable marine dc power distribution networks," *IET Electric Power Applications*, pp. 1–8, 2020 (Under Review)

- J2. G. Ulissi, **S. Kim**, and D. Dujic, "Solid-state technology for shipboard power distribution networks," *IEEE Transactions on Industrial Electronics*, pp. 1–8, 2020 (Under Review)

- J3. **S. Kim**, J. Kucka, G. Ulissi, S.-N. Kim, and D. Dujic, "Solid-state technologies for flexible and efficient marine dc microgrids," *IEEE Transactions on Smart Grid*, pp. 1–8, 2020 (Under Review)

- J4. **S. Kim**, S.-N. Kim, and D. Dujic, "Impact of synchronous generator deexcitation dynamics on the protection in marine DC power distribution networks," *IEEE Transactions on Transportation Electrification*, pp. 1–10, 2020 (Early Access)

- J5. **S. Kim**, S.-N. Kim, and D. Dujic, "Extending protection selectivity in DC shipboard power systems by means of additional bus capacitance," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 5, pp. 3673–3683, May 2020

Conference papers:

- C1. S. Kim, J. Kucka, S.-N. Kim, and D. Dujic, "Improving energy efficiency in dc microgrids with integrated energy storage," in *The 26th international conference and exhibition on electricity distribution (CIRED 2021)*, Jun. 2021 (Under Review)

- C2. **S. Kim**, S.-N. Kim, and D. Dujic, "Deexcitation characterization for power supply protection in DC shipboard power systems," in *2020 IEEE Transportation Electrification Conference and Expo (ITEC)*, Jun. 2020, pp. 1-6 (Student Paper Award)

- C3. **S. Kim**, S.-N. Kim, and D. Dujic, "Protection coordination in DC shipboard power systems: Challenges, current status and new technologies," in *The 25th international conference and exhibition on electricity distribution (CIRED 2019)*, Jun. 2019, pp. 1–5

- C4. S. Kim, G. Ulissi, S.-N. Kim, and D. Dujic, "Marine DC power distribution networks," in *PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management,* May 2019, pp. 1–8

- C5. **S. Kim**, D. Dujic, and S.-N. Kim, "Achieving protection selectivity in DC shipboard power systems employing additional bus capacitance," in *IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society*, Oct. 2018, pp. 3377–3382

- C6. S. Kim, D. Dujic, and S.-N. Kim, "Review of protection coordination technologies in DC distribution systems," in 24th International Conference on Electrical Engineering (ICEE 2018), Jun. 2018, pp. 1–6

- C7. S. Kim, D. Dujic, and S.-N. Kim, "Protection schemes in low-voltage dc shipboard power systems," in PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Jun. 2018, pp. 1–7

- C8. Y. Park, **S. Kim**, H. Jeong, S.-N. Kim, W. Lee, and D. Won, "Fault current characteristics and protection scheme of LVDC microgrids," in *KIEE Summer Annual Conference Proceedings*, Jul. 2017, pp. 1–6

Patent:

P1. S. Kim, Y. Park, D. Lee, S.-N. Kim, and D. Dujic, *DC shipboard power system*, KR Patent 10-2018-0116473, filed Sep. 2018, and issued May 2020

Invited talk:

T1. **S. Kim** and D. Dujic, "Technologies and applications of DC grids in Europe," in *Korea-Europe Collaboration Workshop for Energy Transition - BIXPO 2018*, Nov. 2018

Other outcomes, not directly related to the scope of the thesis:

Conference papers:

C1. Y. Park, **S. Kim**, and S.-N. Kim, "A comparative study on the topology of high power solid state transformer for MVDC to LVDC link," in *24th International Conference on Electrical Engineering* (*ICEE 2018*), Jun. 2018, pp. 1–11

- C2. J. Heo, S. Kim, J. Kim, and S.-N. Kim, "An improved modeling of transformer inrush current for voltage drop analysis," in 24th International Conference on Electrical Engineering (ICEE 2018), Jun. 2018, pp. 1–10

- C3. D. Lee, Y. Park, **S. Kim**, and S.-N. Kim, "Study on analysis of wye-delta open transition current for motor starting and molded case circuit breaker selection," in *24th International Conference on Electrical Engineering (ICEE 2018)*, Jun. 2018, pp. 1–13

Patents:

- P1. Y. Park, S. Ryu, S.-N. Kim, S. Kim, S. Milovanovic, and D. Dujic, *Power converting apparatus having scott transformer*, International Patent 2019-005262, filed Nov. 2019 (Pending)

- P2. Y. Park, S. Ryu, S.-N. Kim, S. Kim, S. Milovanovic, and D. Dujic, *Power converting apparatus having scott transformer*, KR Patent 10-2018-0050472, filed May 2018 (Pending)

Technical brochure:

B1. CIGRE WG A3.38, "Shunt capacitor switching in distribution and transmission systems," *CIGRE Technical Brochure*, 2020 (Main Contribution: Chapter 6. Switching of filter banks) (Will be published soon)

# 2 State-of-the-art

This chapter provides an overview of the general protection technologies in DC power distribution networks as well as the state-of-the-art protection schemes in marine DC power distribution networks. The analysis shows that the three-level protection, which consists of three-different time frame protections: fast action - bus separation; medium action - feeder protection; and slow action - power supply protections, has become the dominant trend for marine low-voltage DC power distribution networks selected for the main research field in the thesis.

### 2.1 Introduction

Protection in electrical power systems is to minimize the impact of any system faults. The fundamental concepts of the system protection are [35]:

- reliability correct operation of system protection

- selectivity the maximum system availability with the minimum area disconnection

- speed fast operation to reduce equipment damage and avoid system instability

- · simplicity the minimum number of protective devices and associated components

- · economical efficiency high functionality with the minimum cost

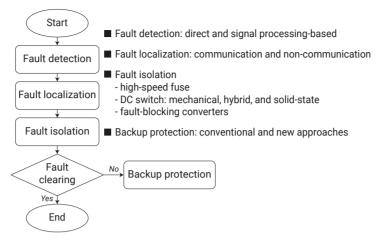

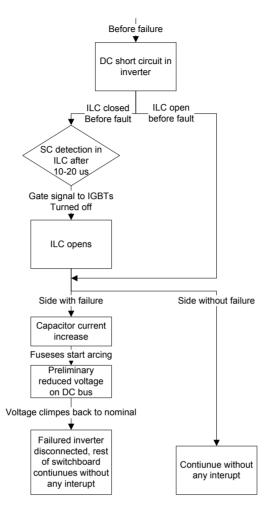

With the consideration of the fundamental protection concepts, the general procedure shown in **Fig. 2.1** is used for DC system protection [36]. First, when a fault occurs in DC PDNs, it has to be identified promptly. One important thing for the detection is that the fault has to be distinguished from any normal transients to avoid an abnormal operation of system protection. For the reliable DC fault detection, signal processing-based methods have been proposed in addition to conventional direct measurement methods [37]–[43].

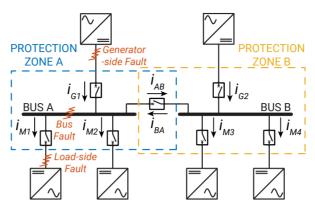

Secondly, fault localization is necessary to continuously supply electric power to healthy parts by selectively isolating faulty parts. The fault impedance calculated by transient voltage and current provides the information on a fault location. For long-distance point-to-point DC networks, the amplitude of the calculated fault impedance represents the fault location without any communication. Low fault impedance (high current increase and voltage drop) means a near fault, while high fault impedance (low current increase and voltage drop) indicates a far fault, including higher line impedance [44]. However, it is a challenge to determine the fault location only with the fault impedance in short-distance and complex DC networks. It is for this reason that there are approaches to employ communication-based fault locating methods [39], [45].

Fig. 2.1 Procedure of DC power system protection.

Thirdly, to prevent damages of any other equipment, the fault should be interrupted rapidly by protective devices: high-speed fuses, DC switches (or circuit breakers), and fault-blocking converters. Although a fuse has notable disadvantages, e.g., manual replacement of the fuse if it blows and low reliability in protection compared to circuit breakers, it is still an attractive solution because of its high breaking capability at low cost. A switch or a circuit breaker is a primary element in the protection with its functions of reliable operation and selective interruption. A wide range of research activities have been performed for three different types of DC switches: mechanical, hybrid, and solid-state [46]–[49]. Otherwise, a few converters, e.g., thyristor converter and full-bridge MMC, can handle the DC fault current [50], [51]. It contributes to open the possibility of breakerless systems.

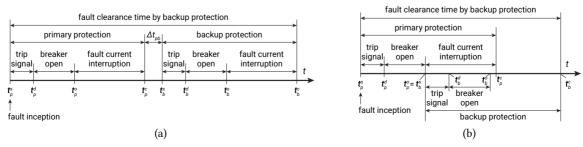

Lastly, backup protection can be considered for a primary protection failure to increase the reliability of the protection system. The issue of backup protection in the DC networks is how to quickly initiate backup protection without the maloperation and with the minimum impact.

### 2.2 General Overview of DC Protection

An overview of each protection procedure is provided with the short discussions on benefits and limitations of approaches, currently employed and/or recently proposed for DC protection.

#### 2.2.1 Fault Detection

There are two main categories for the fault protection: direct measurement methods and signal processing-based methods, as given in **Tab. 2.1**. A fault in electrical systems can be characterized by an increase in current and a decrease in voltage. The current flow may also be different from normal conditions depending on fault locations. The first category directly uses the characteristics of measured voltage and current such as their amplitudes, derivatives, and directions. These methods provide fast fault identification with low computational resources. However, they are highly sensitive to noise and it may make these detection methods less reliable. The second is based on signal processing techniques, e.g., wavelet analysis and travelling wave analysis. There are lots of works on

| Category                | Fault Detection                              | Main Benefit     | Main Limitation  |  |

|-------------------------|----------------------------------------------|------------------|------------------|--|

|                         | Undervoltage (amplitude) [37]                |                  |                  |  |

|                         | Voltage & current derivatives [38], [55]     |                  | Less reliable    |  |

| Direct measurement      | Overcurrent (amplitude) [39], [56]           | Faster detection |                  |  |

|                         | Current difference (or direction) [40], [57] |                  |                  |  |

|                         | Impedance (or distance) [41], [58]           |                  |                  |  |

| Signal processing based | Wavelet analysis [38], [42], [52], [54]      |                  | Slower detection |  |

| Signal processing-based | Travelling-wave analysis [43], [52], [53]    | Higher accuracy  | Slower detection |  |

Tab. 2.1 Fault detection techniques.

the signal processing approach [38], [42], [43], [52]–[54]. The works report that the signal processing approach is superior than the direct approach in terms of fault detection and localization. However, the signal processing approach also brings negative impacts on detection time and implementation.

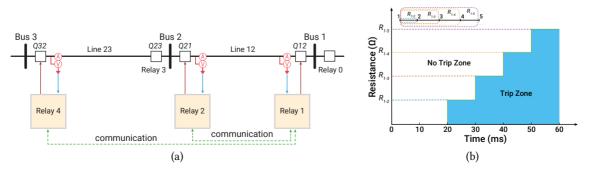

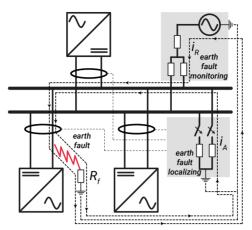

#### 2.2.2 Fault Localization

Fault localization is required to minimize the impact of the fault by selectively removing a faulty part. Fault localization based on communication [see **Fig. 2.2(a)**], which has been reported to provide high accuracy in fault locating, is based on the data transferring between several adjacent local relays or the data gathering into a central controller [45], [59]. Therefore, it is not possible to avoid a certain time delay. By contrast, non-communication measures can rapidly operate local circuit breakers when measured signals are higher than preselected thresholds. In this way, fault localization between different protection zones is given by time-inverse methods, selecting different operating times depending on amplitudes of fault current, voltage dip, or impedance [39], [58], [60] [see **Fig. 2.2(b)**]. However, providing selectivity with these time-inverse methods is a challenging issue in DC networks due to low DC cable impedance and fast fault-clearing requirement.

#### 2.2.3 Fault Isolation

Fault isolation methods are classified into four groups: (a) high-speed fuse with DC isolator, (b) fault-blocking converter with DC isolator, (c) conventional converter with AC circuit breaker, and (d)

Fig. 2.2 Fault localization: (a) communication-based [59] and (b) non-communication [60].

conventional converter with DC circuit breaker.

The fuse is made up of a metallic wire or strip that is melt down by an overcurrent. With this simple configuration, the fuse is an economic solution and convenient to employ. Furthermore, high-rupturing capacity fuses can be applied to high-power systems with their very high-interrupting ratings. Those are the reasons why the fuses are widely accepted into various industrial applications. On the other hand, the blown fuse has to be manually replaced with a new fuse, while circuit breakers are simply resettable after the breaking operation. It is also difficult to achieve the fuse discrimination between upstream and downstream feeders unless the fuses have significant difference in breaking ratings. It means that the use of the fuse installed at the supply side makes the system less reliable.

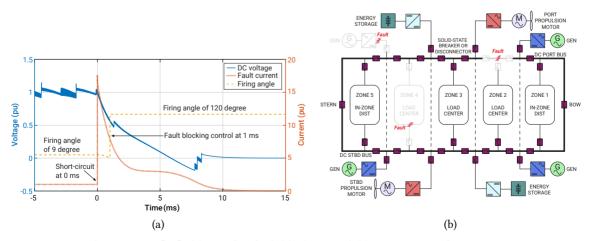

The fault-blocking converter, e.g., a thyristor rectifier and a full-bridge MMC, can handle the fault current by itself without any circuit breakers. Once the fault is detected, a controller of a thyristor rectifier forces the firing angle to 120° to extinguish the fault current by reversing the DC voltage polarity, using so-called fold-back protection control [50]. With this control, the thyristor rectifier has a competitive advantage in the system protection. The full-bridge MMC can also make the DC voltage to zero as well as to negative during the fault event. The disadvantages of the MMC are its high cost and high conduction losses, and the fact that it is suited for MVDC and HVDC applications.

The approach by means of the conventional converter with AC CB is proposed in [61]. In this way, the protection technology is already mature and there are lots of commercial products to implement this protection scheme with the expected installation cost. However, this method requires to install a very high AC coupling reactor or an oversized converter to sustain the fault current for a long interrupting time of AC circuit breakers (3–5 cycles).

As the last approach for the isolation, there are three types of DC switches: mechanical, hybrid (a mechanical circuit breaker combined with solid-state technology), purely solid-state circuit breakers (SSCB). SSCBs have been proposed and employed for the marine LVDC PDNs due to the ability of ultra-fast fault clearing compared to mechanical and hybrid circuit breakers. However, the use of

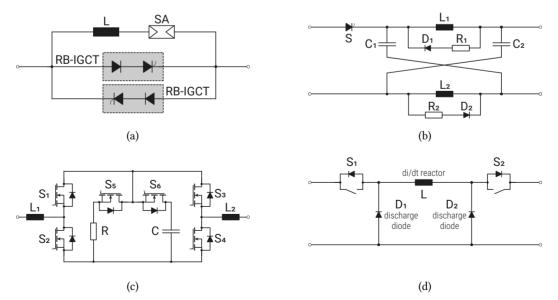

Fig. 2.3 SSCB topologies: (a) interrupting [46], (b) resonant [47], (c) resistive [48], and (d) limiting [49].

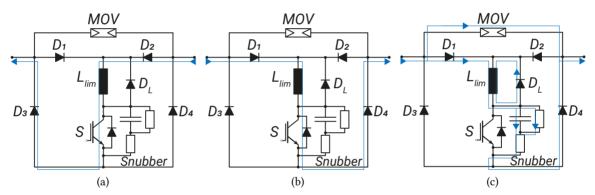

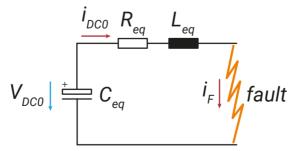

SSCBs is generally limited to the bus-tie purpose due to their high cost. In the aspect of a circuit topology, SSCBs commonly include semiconductors to interrupt the overcurrent, inductors to limit the rate of rise of the overcurrent, and protection circuits to dissipate inductive energy and mitigate overvoltage [46]–[49]. These SSCBs can be classified by ways to interrupt the current and dissipate inductive energy stored in the system during the interruption: interrupting, resonant, resistive, and limiting topologies, as illustrated in **Fig. 2.3**. The operational principle of each topology is briefly summarized.

- Interrupting topology [**Fig. 2.3(a**)]: the current in the circuit is interrupted by reverse blocking semiconductors (e.g., RB-IGCT) and the stored energy is dissipated by a surge arrester (*SA*) installed in parallel that can also reduce overvoltage on the semiconductors.

- Resonant topology [Fig. 2.3(b)]: when the fault current flows through the SSCB, the resonant circuit creates an artificial current zero without any active circuits. During this current zero, the thyristor (*S*) is turned *OFF* and the energy in inductances ( $L_1$  and  $L_2$ ) is dissipated in the respective anti-parallel diode and resistor.

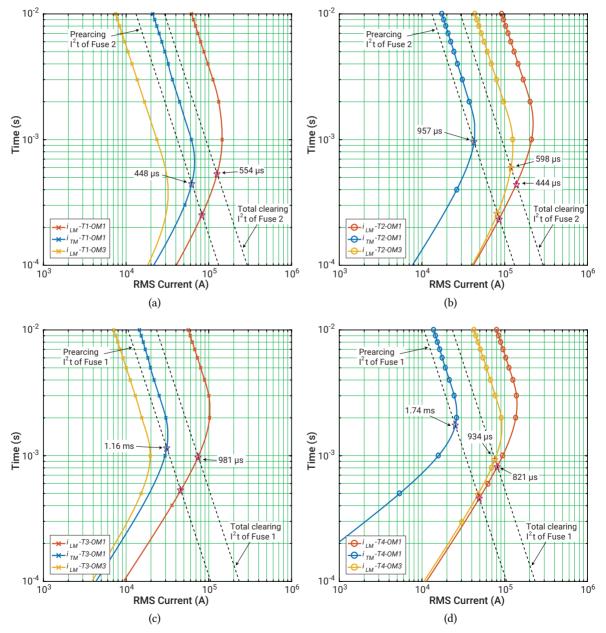

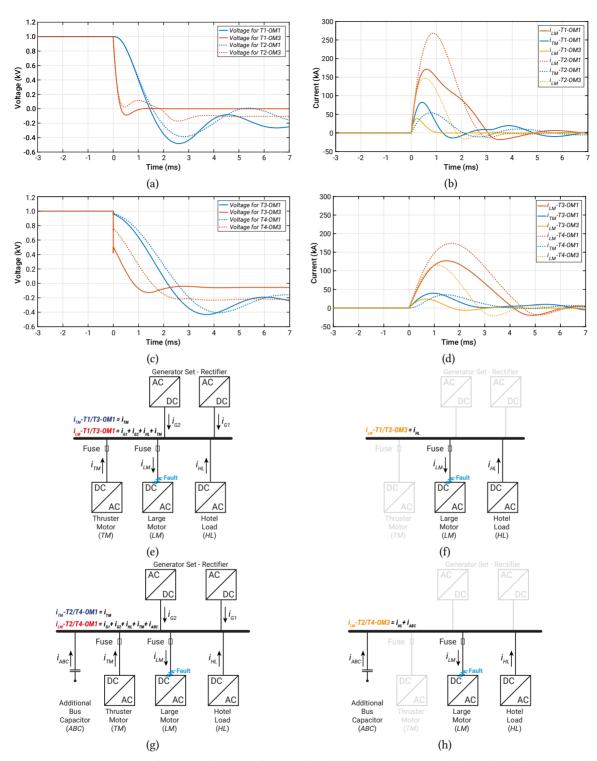

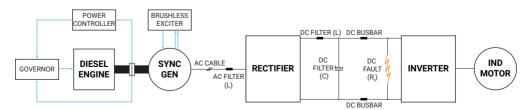

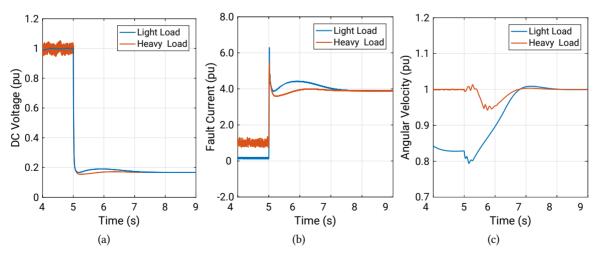

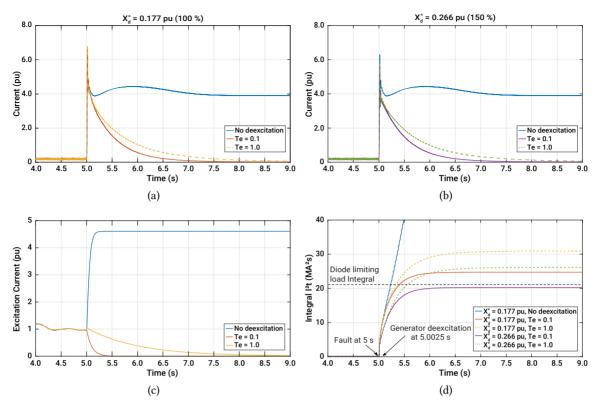

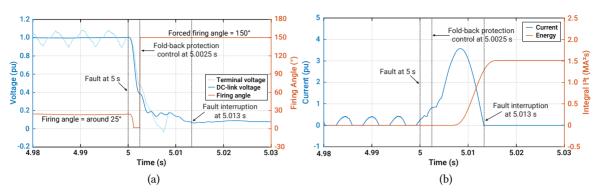

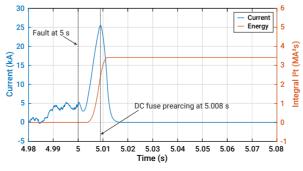

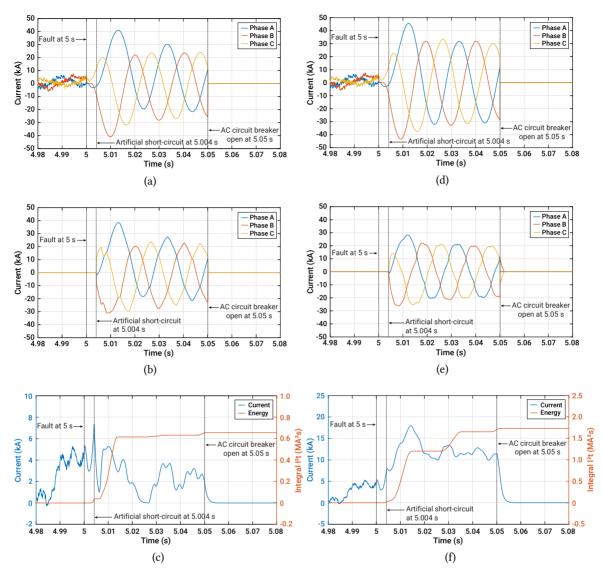

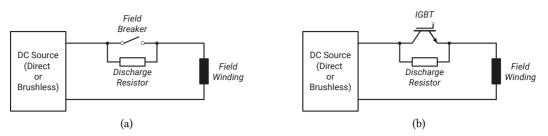

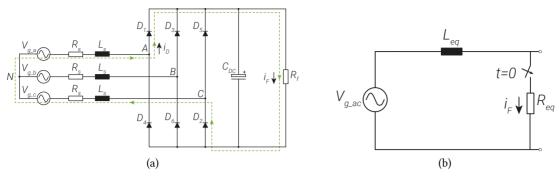

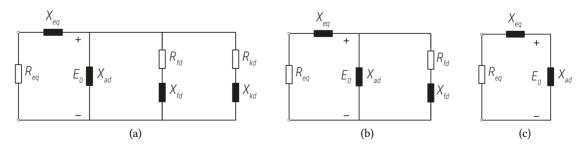

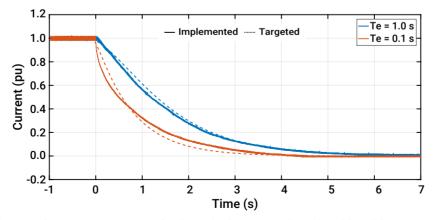

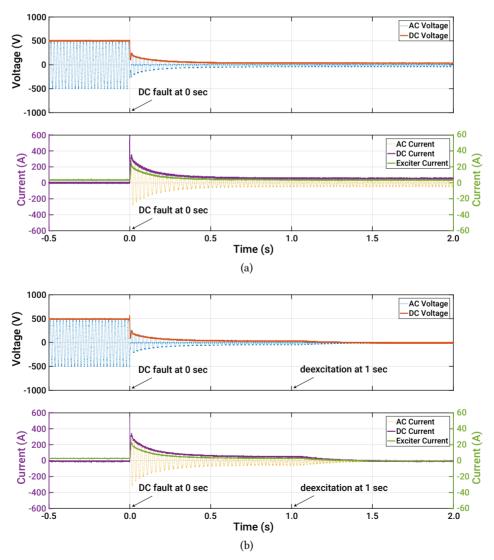

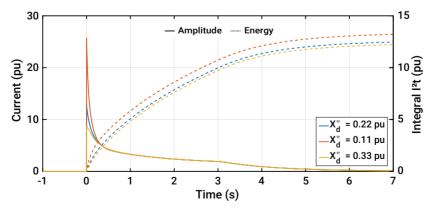

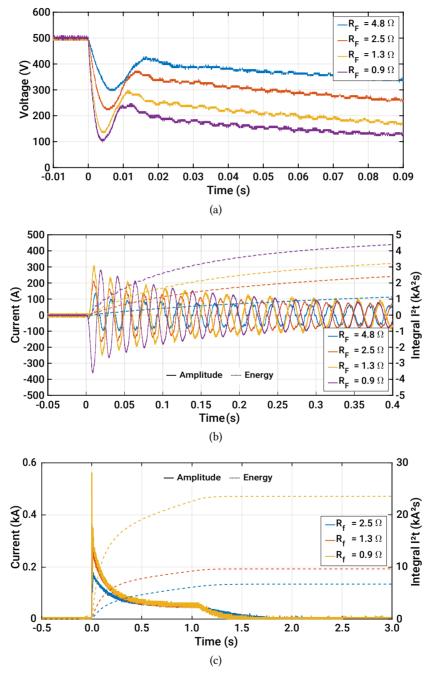

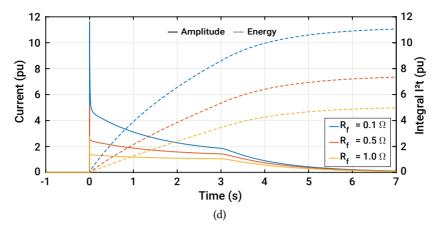

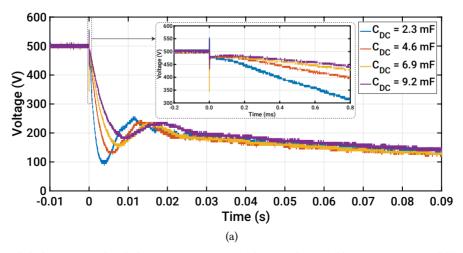

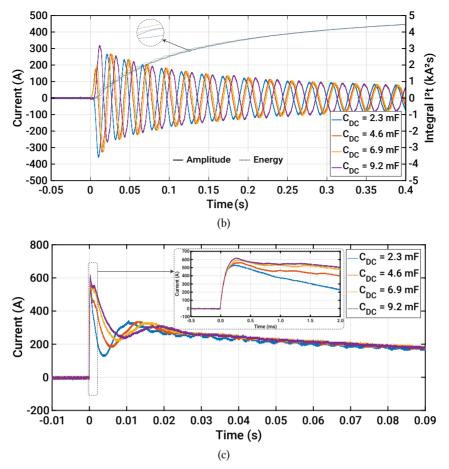

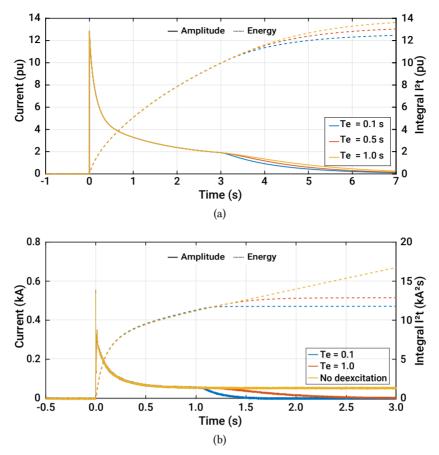

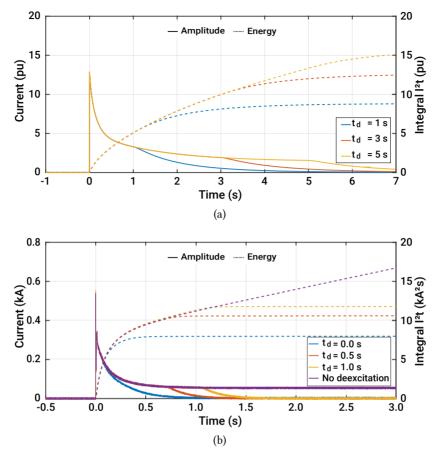

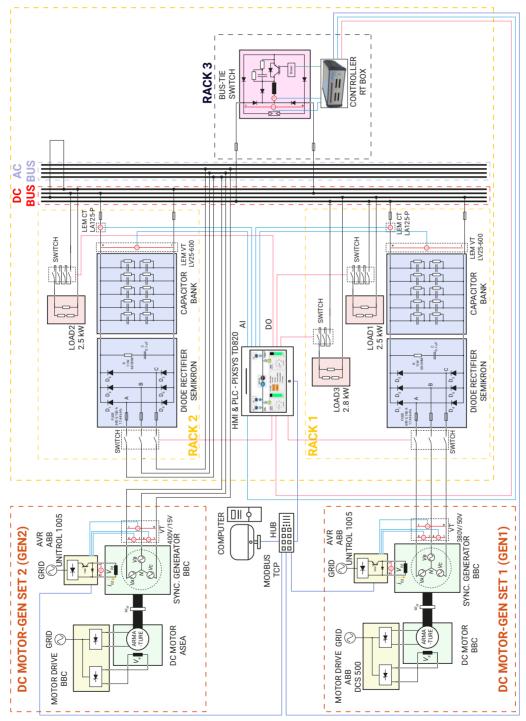

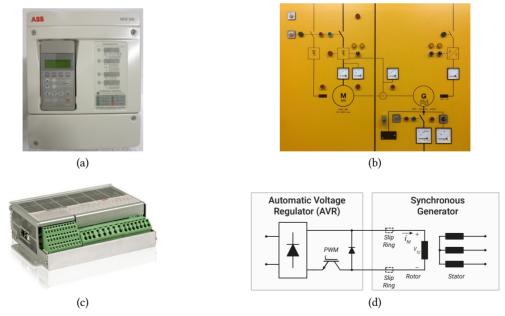

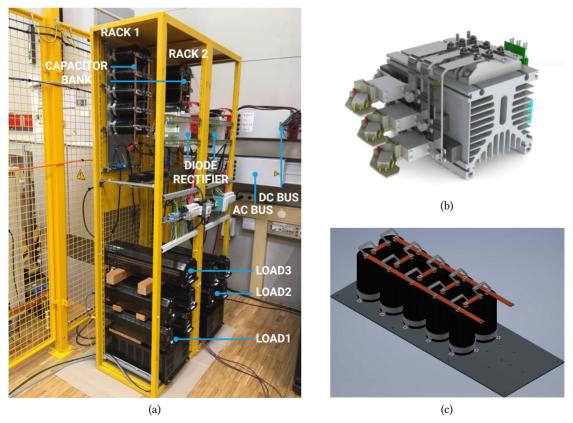

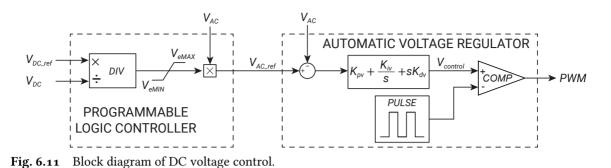

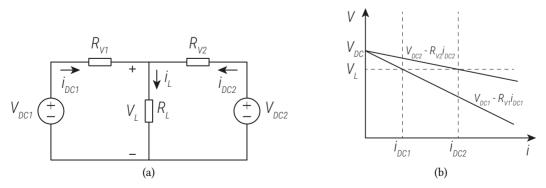

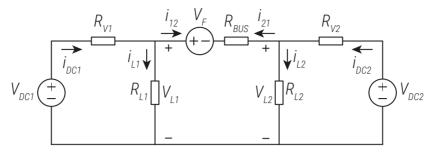

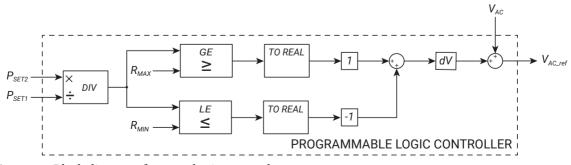

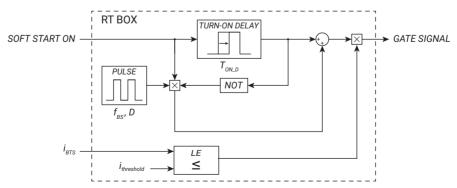

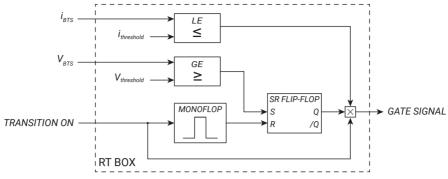

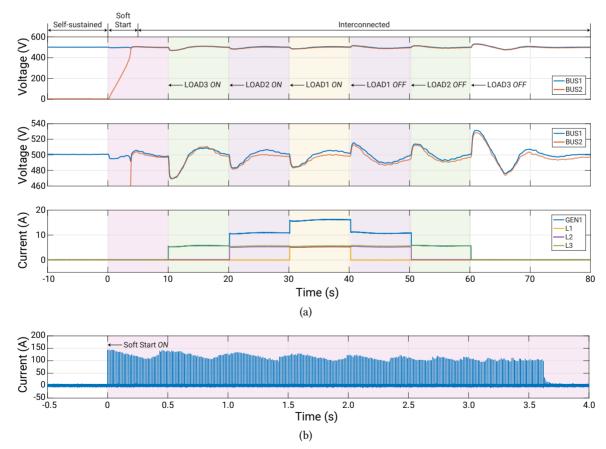

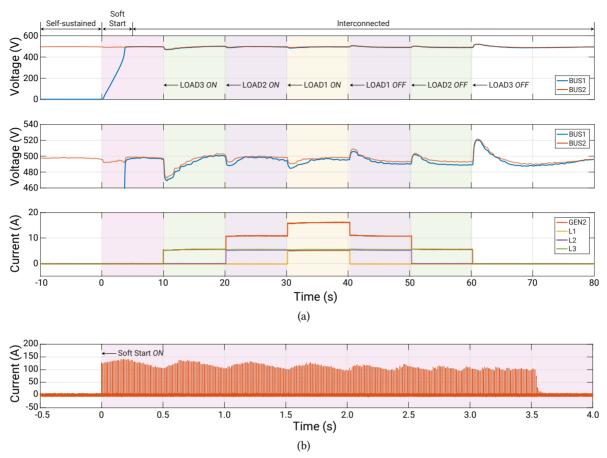

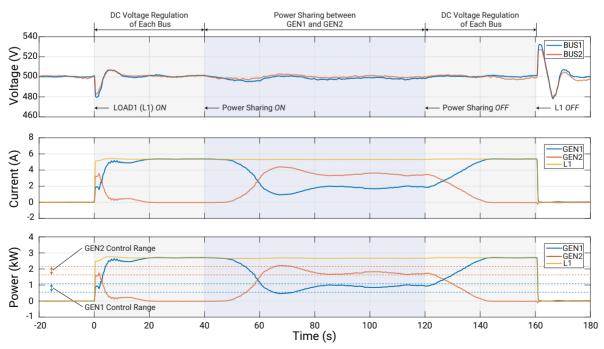

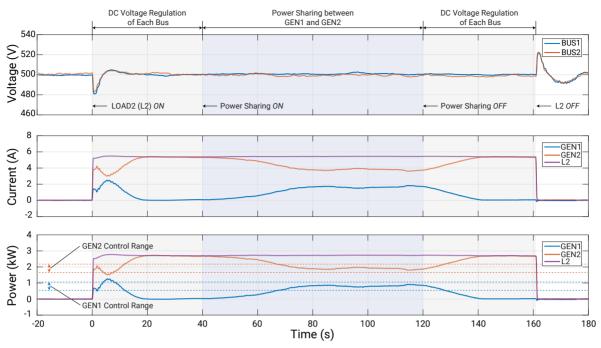

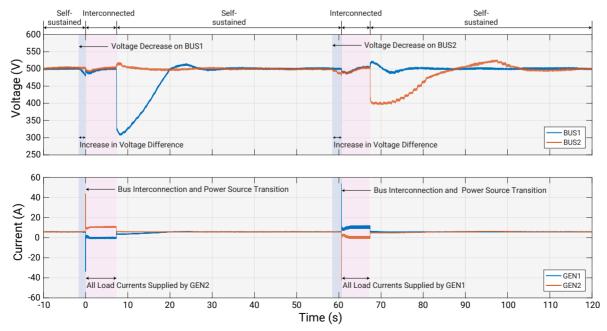

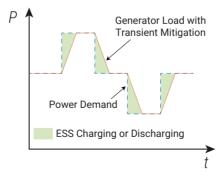

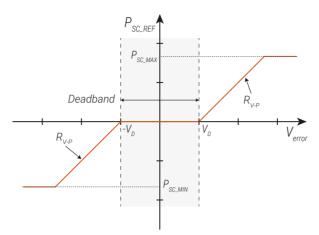

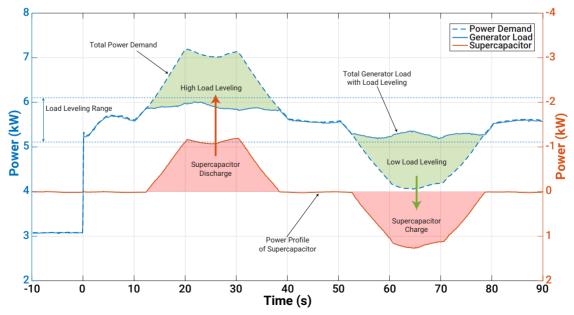

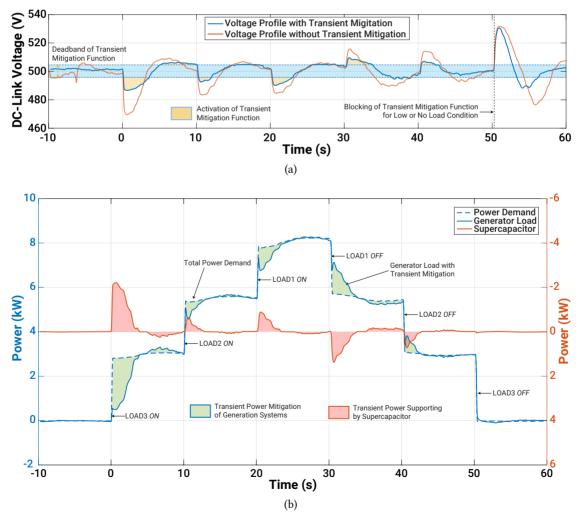

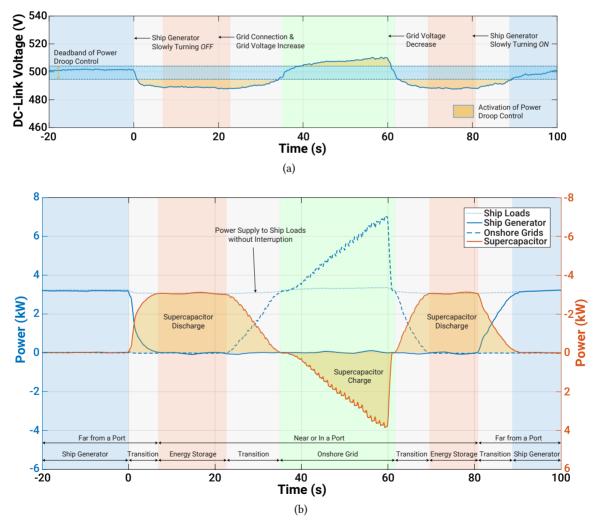

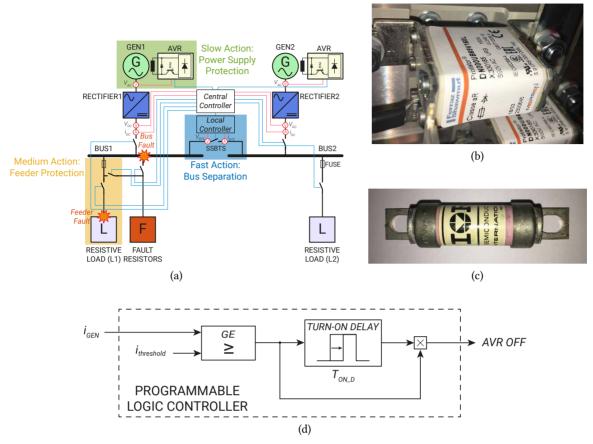

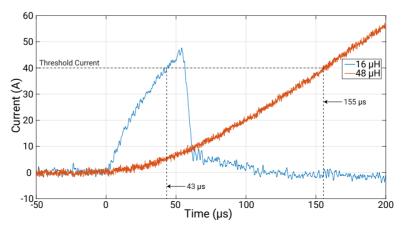

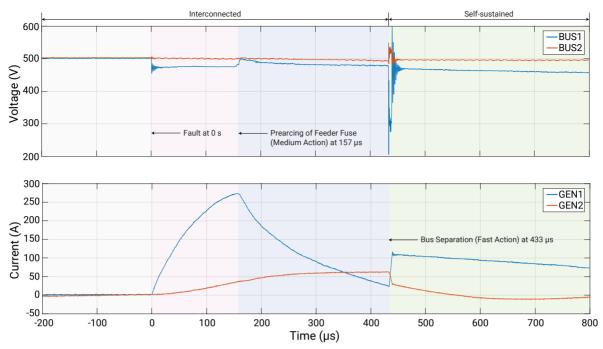

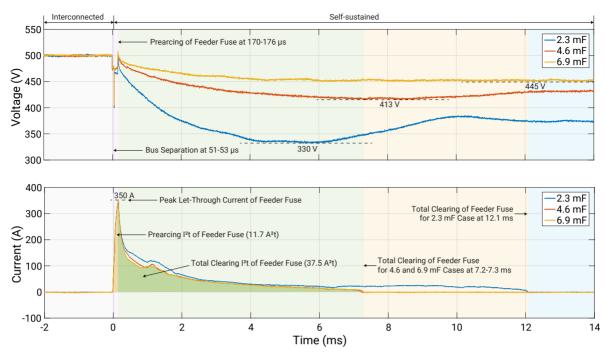

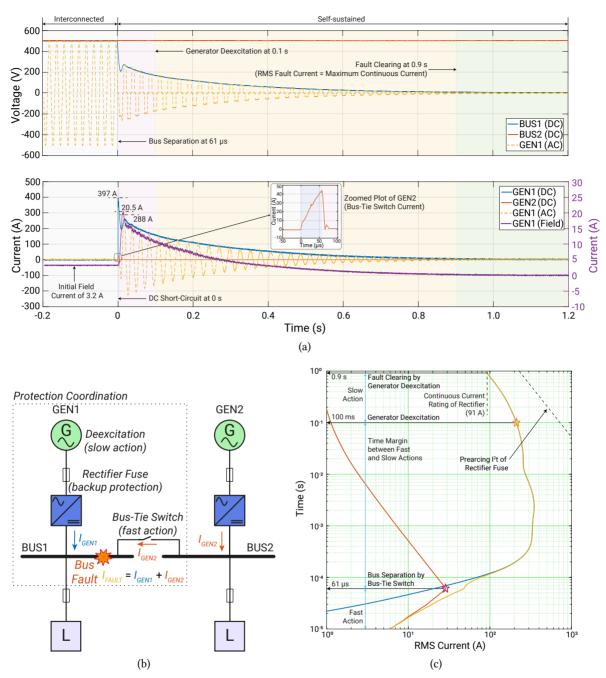

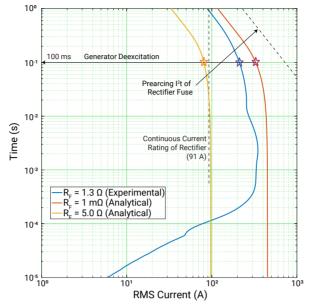

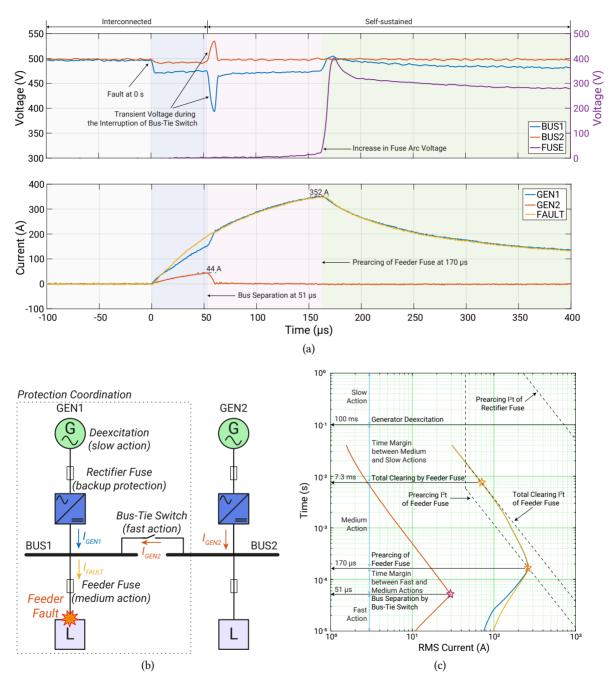

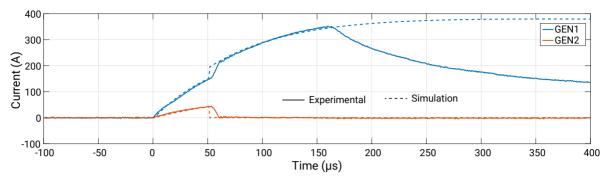

- Resistive topology [Fig. 2.3(c)]: when the main current path is interrupted by turning *OFF*  $S_2$  and  $S_3$ , the current is directed to the capacitor (*C*). If the voltage on the capacitor exceeds a threshold level, the stored fault energy is discharged by the resistor (*R*) with turning *ON*  $S_5$  and  $S_6$ . The capacitor charge and discharge actions by the resistor are repeated until the current is driven to zero.